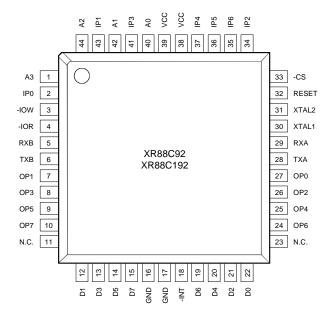

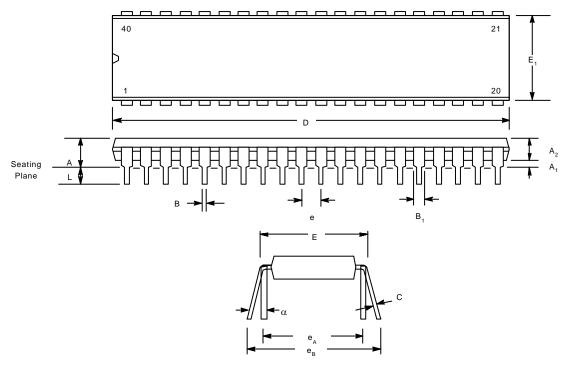

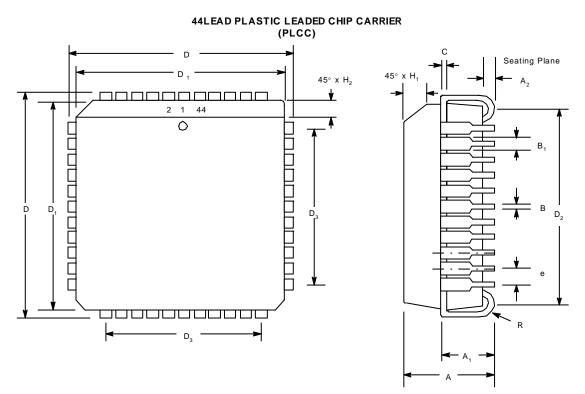

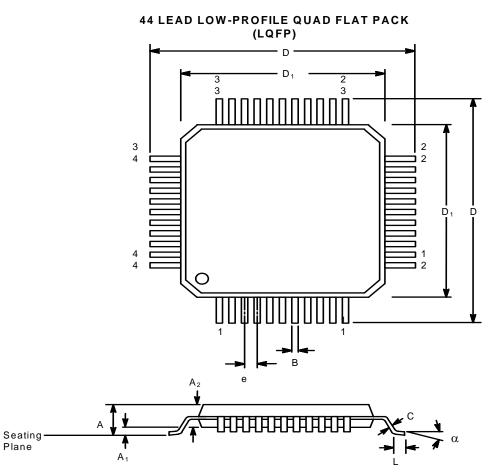

**Package Description**

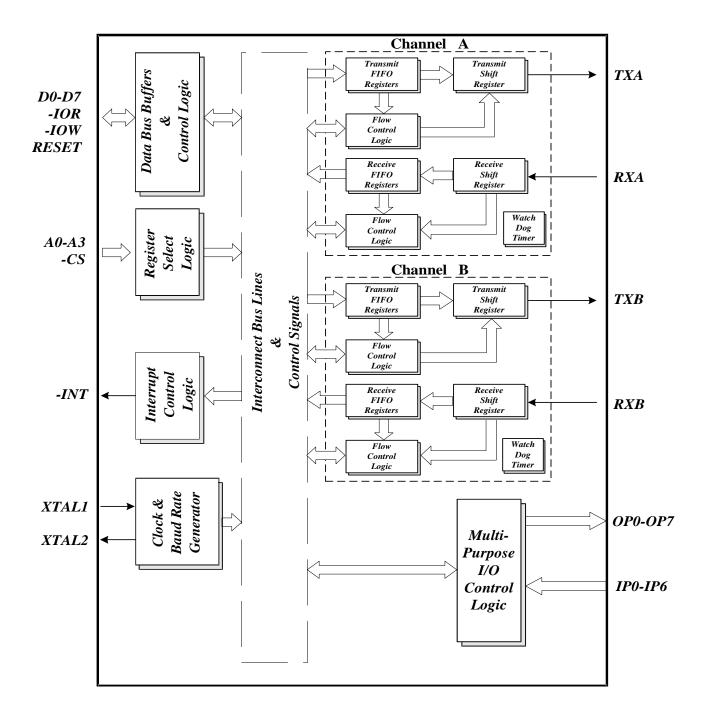

### **Block Diagram**

Downloaded from Arrow.com.

### **SYMBOL DESCRIPTION** (\* 44 pin LQFP)

| Symbol   | 44    | Pin | 44*  | Signal<br>type | Pin Description                                                                                                                                                                                                                                             |

|----------|-------|-----|------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXA, RXB | 35,11 |     | 29,5 | I              | Serial data input. The serial information (data) received from<br>serial port to XR88C92/192 receive input circuit. A mark (high)<br>is logic one and a space (low) is logic zero. This input must<br>be held at logic one when idle and during power down. |

| TXA, TXB | 33,13 |     | 28,6 | 0              | Serial data output. The serial data is transmitted via this pin<br>with additional start, stop and parity bits. This output will be<br>held in mark (high) state during reset, local loop back mode<br>or when the transmitter is disabled.                 |

| RESET    | 38    |     | 32   | I              | Master Reset (active high). A high on this pin will reset all the outputs and internal registers. The transmitter output and the receiver input will be disabled during reset time.                                                                         |

| OP0      | 32    |     | 27   | ο              | Multi-purpose output. General purpose output or Channel A Request-To-Send (-RTSA active low).                                                                                                                                                               |

| OP1      | 14    |     | 7    | ο              | Multi-purpose output. General purpose output or Channel B<br>Request-To-Send (-RTSB active low).                                                                                                                                                            |

| OP2      | 31    |     | 26   | ο              | Multi-purpose output. General purpose output or one of the following functions can be selected for this output pin by programming the Output Port Confiuration Register bits 1,0;                                                                           |

|          |       |     |      |                | <b>TxAClk1</b> -Transmit 1X clock.<br><b>TxAClk16</b> -Transmit 16X clock<br><b>RxAClk1</b> -Receive 1X clock                                                                                                                                               |

| OP3      | 15    |     | 8    | ο              | Multi-purpose output. General purpose output or one of the following functions can be selected for this output pin by programming the Output Port Confiuration Register bits 3,2;                                                                           |

|          |       |     |      |                | <b>C/T</b> -Counter timer output (Open drain output)<br><b>TxBCIk1</b> -Transmit 1X clock<br><b>RxBCIk1</b> -Receive 1X clock                                                                                                                               |

| OP4      | 30    |     | 25   | ο              | Multi-purpose output. General purpose output or one of the following functions can be selected for this output pin by programming the Output Port Confiuration Register bit 4;                                                                              |

|          |       |     |      |                | - <b>RxARDY</b> -Receive ready signal (Open drain output)<br>- <b>RxAFULL</b> - Receive FIFO full signal (Open drain output)                                                                                                                                |

### **SYMBOL DESCRIPTION** (\* 44 pin LQFP)

| Symbol | 44          | Pin | 44*            | Signal<br>type | Pin Description                                                                                                                                                                                                                                                                                                                   |

|--------|-------------|-----|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OP5    | 16          |     | 9              | 0              | Multi-purpose output. General purpose output or one of the following functions can be selected for this output pin by programming the Output Port Confiuration Register bit 5;                                                                                                                                                    |

|        |             |     |                |                | - <b>RxBRDY</b> - Receive ready signal (Open drain output)<br>- <b>RxBFULL</b> - Receive FIFO full signal (Open drain output)                                                                                                                                                                                                     |

| OP6    | 29          |     | 24             | 0              | Multi-purpose output. General purpose output or Transmit A holding register empty interrupt ( <b>-TxARDY</b> Open drain output).                                                                                                                                                                                                  |

| OP7    | 17          |     | 10             | 0              | Multi-purpose output. General purpose output or Transmit B holding register empty interrupt ( <b>-TxBRDY</b> Open drain output)                                                                                                                                                                                                   |

| A0-A3  | 2,4,<br>6,7 |     | 40,42,<br>44,1 | I              | Address select lines. To select internal registers.                                                                                                                                                                                                                                                                               |

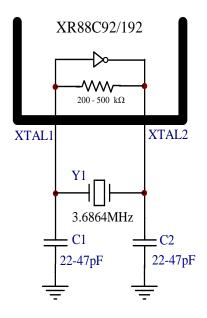

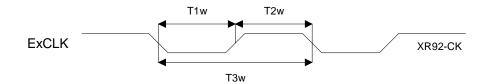

| XTAL1  | 36          |     | 30             | Ι              | Crystal input 1 or external clock input. A crystal can be<br>connected between this pin and XTAL2 pin to utilize the<br>internal oscillator circuit. An external clock can be used to<br>clock internal circuit and baud rate generator for custom<br>transmission rates.                                                         |

| XTAL2  | 37          |     | 31             | 0              | Crystal input 2 or buffered clock output. See XTAL1.                                                                                                                                                                                                                                                                              |

| GND    | 22          |     | 16,17          | Pwr            | Signal and power ground.                                                                                                                                                                                                                                                                                                          |

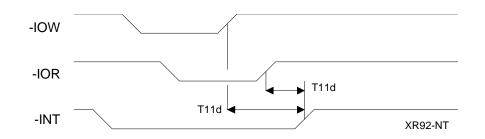

| -INT   | 24          |     | 18             | 0              | Interrupt output (open drain, active low) This pin goes low<br>upon occurrence of one or more of eight maskable interrupt<br>conditions (when enabled by the interrupt mask register).<br>CPU can read the interrupt status register to determine the<br>interrupting condition(s). This output requires a pull-up resis-<br>tor. |

| IP0    | 8           |     | 2              | I              | Multi-purpose input or Channel A Clear-To-Send (-CTSA active low).                                                                                                                                                                                                                                                                |

| IP1    | 5           |     | 43             | I              | Multi-purpose input or Channel B Clear-To-Send (-CTSB active low).                                                                                                                                                                                                                                                                |

| IP2    | 40          |     | 34             | I              | Multi-purpose input or Timer/Counter External clock input.                                                                                                                                                                                                                                                                        |

Rev. 1.33

### SYMBOL DESCRIPTION (\* 44 pin LQFP)

| Symbol | 44                               | Pin | 44*                              | Signal<br>type | Pin Description                                                                                                                                                                                                            |

|--------|----------------------------------|-----|----------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IP3    | 3                                |     | 41                               | I              | Multi-purpose input or Channel A transmit external clock port<br>input. The transmit data is clocked on the falling edge of the<br>clock.                                                                                  |

| IP4    | 43                               |     | 37                               | I              | Multi-purpose input or Channel A receive external clock input.<br>The transmit data is clocked on the rising edge of the clock.                                                                                            |

| IP5    | 42                               |     | 36                               | I              | Multi-purpose input or Channel B Transmit external clock input. The transmit data is clocked on the falling edge of the clock.                                                                                             |

| IP6    | 41                               |     | 35                               | I              | Multi-purpose input or Channel B receive external clock input.<br>The transmit data is clocked on the rising edge of the clock.                                                                                            |

| -CS    | 39                               |     | 33                               | I              | Chip select (active low). A low at this pin enables the serial port / CPU data transfer operation.                                                                                                                         |

| D0-D7  | 28,18<br>27,19<br>26,20<br>25,21 |     | 22,12<br>21,13<br>20,14<br>19,15 | I/O            | Bi-directional data bus. Eight bit, three state data bus to<br>transfer information to or from the CPU. D0 is the least<br>significant bit of the data bus and the first serial data bit to be<br>received or transmitted. |

| -IOW   | 9                                |     | 3                                | I              | Write strobe (active low). A low on this pin will transfer the contents of the CPU data bus to the addressed register.                                                                                                     |

| -IOR   | 10                               |     | 4                                | I              | Read strobe (active low). A low on this pin will transfer the contents of the XR88C92/192 register to CPU data bus.                                                                                                        |

| VCC    | 44                               |     | 38,39                            | Pwr            | Power supply input, 2.97V to 5.5V.                                                                                                                                                                                         |

| N.C.   | 1,12<br>23,34                    |     | 11,23                            |                | No Connection.                                                                                                                                                                                                             |

|        |                                  |     |                                  |                |                                                                                                                                                                                                                            |

Rev. 1.33

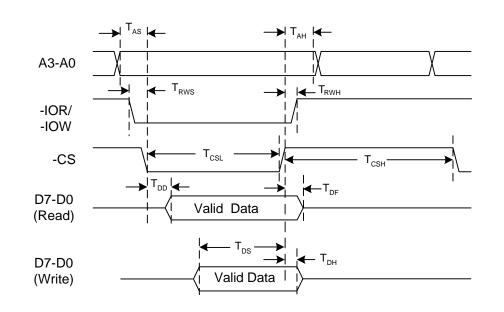

#### INTERNAL CONTROL LOGIC

The internal control logic of the XR88C92/192 receives operation commands from the central processing unit (CPU) and generates appropriate signals to the internal sections to control device operation. The internal control logic takes in the following inputs:

- -CS, which is the XR88C92/192 chip-select;

- -IOR (read) and -IOW (write), which allow data transfers between the CPU and XR88C92/192 via the data bus (D0 to D7);

- four register-select lines (A0 through A3) which are decoded to allow access to the registers within the XR88C92/192;

- RESET (reset), which initializes or resets all outputs and internal registers.

#### **COMMUNICATION CHANNELS A AND B**

Each communication channel includes a full-duplex asynchronous receiver/transmitter (UART). The operating frequency for each receiver and each transmitter can be selected independently from the baud rate generator, the Counter/Timer (C/T), or from an external clock. The transmitter accepts parallel data from the CPU, converts it to a serial bit stream in the form of a character and outputs it on the Transmit Data output pin (TXA, TXB). The character consists of start, stop, and optional parity bits, The receiver accepts serial data on the Receive Data input pin (RXA, RXB), converts this serial input to parallel format, checks for a start bit, stop bit, parity bit (if any), framing error, overrun or break condition, and transfers the data byte to the CPU during read operations.

#### **TIMING LOGIC**

The timing logic consists of

• a crystal oscillator,

Rev. 1.33

- a baud rate generator (BRG),

- · clock selector logic, and

- a programmable 16-bit counter/timer (C/T).

The *crystal oscillator* operates directly from a 3.6864 MHz crystal connected across the XTAL1 and XTAL2 inputs or from an external clock of the appropriate frequency connected to XTAL1. The XTAL1 clock serves as the basic timing reference for the baud rate generator, the C/T, and other internal circuits.

The *baud rate generator* operates from the XTAL1 clock input and can generate 28 commonly used data communication baud rates (if a 3.6864MHz crystal or clock is used) ranging from 50 to 230.4kbps by producing internal clock outputs at 16 times the actual baud rate. In addition, other baud rates can be derived by connecting 16X or 1X clocks to multi-purpose input port pins IP3 - IP6 that have alternate functions as receiver or transmitter clock inputs.

*Clock selector logic* consists of the clock selector register (CSRA, CSRB), bits 0 & 2 of Mode Register 0 (MR0A, MR0B) and bit-7 of Auxilliary Control Register (ACR). These allow various combinations of these baud rates for receiver and transmitter of each channel. See Baud Rate Table on page 18 for more details.

The programmable 16-bit counter/timer (C/T) can produce a 16X clock for other baud rates by counting down its programmed clock source. Users can program the 16 bit C/T within the XR88C92/192 to use one of several clock sources as its input. The output of the C/T is available to the internal clock selectors and can also be programmed to appear at output OP3. In the timer mode, the C/T acts as a programmable divider and can generate a square-wave output at OP3. In the counter mode, the C/T can be started and stopped under program control. When stopped, the CPU can read its contents. The counter counts down the number of pulses stored in the concatenation of the C/T upper register and C/T lower register and produces an interrupt. This is a system-oriented feature that can be used to record timeouts when implementing various application protocols.

#### INTERRUPT CONTROL LOGIC

The following registers are associated with the interrupt control logic:

- Interrupt Mask Register (IMR)

- · Interrupt Status Register (ISR)

- Auxiliary Control Register (ACR)

A single active-low interrupt output (-INT) can notify the CPU that any of eight internal events has occurred. These eight events are described in the discussion of the interrupt status register (ISR). User can program the interrupt mask register (IMR) to allow only certain conditions to cause -INT to be asserted while the CPU can read the ISR to determine all currently active interrupting conditions. In addition, users can program

Downloaded from Arrow.com.

the parallel outputs OP3 through OP7 to provide discrete interrupt outputs for the transmitters, the receivers, and the C/T. See 'Configuring Multi-purpose Outputs' section for details.

#### DATA BUS BUFFER (D0-D7)

The data bus buffer provides the interface between the external and internal data buses. It is controlled by the internal control logic to allow read and write data transfer operations to occur between the controlling CPU and XR88C92/192 by way of the eight parallel data lines (D0 through D7).

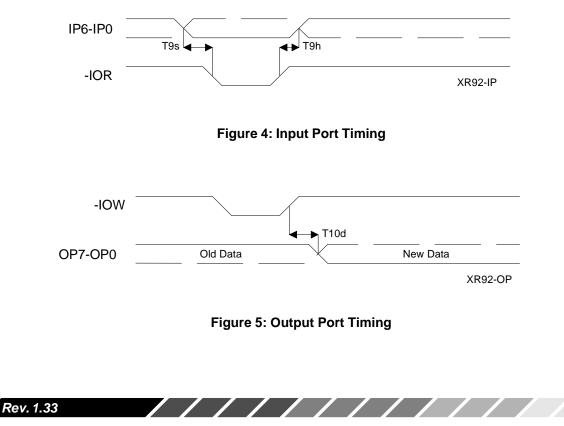

#### MULTI-PURPOSE INPUTS (IP0 - IP6)

The states of the seven multi-purpose inputs (IP0 through IP6) can be read from the internal register IPR (address 0x0D). The bits in this register are the complements of the actual inputs - for example, if the IP0 is low, the corresponding bit in the IPR, bit-0 is a logic '1'. Each of these inputs also has an alternate control function capability. The alternate functions can be enabled/ disabled on a bit-by-bit basis. The following table shows how each of these inputs is configured for its special function:

| Input | Function     | Programming                  |

|-------|--------------|------------------------------|

| IP0   | -CTSA        | Set MR2A bit-4 = 1           |

| IP1   | -CTSB        | Set MR2B bit-4 = 1           |

| IP2   | C/T Ext. Clk | Set ACR[6:4] = 000           |

| IP3   | TxA Ext. Clk | Set CSRA[3:0] = 1110 or 1111 |

| IP4   | RxA Ext. Clk | Set CSRA[7:4] = 1110 or 1111 |

| IP5   | TxB Ext. Clk | Set CSRB[3:0] = 1110 or 1111 |

| IP6   | RxB Ext. Clk | Set CSRB[7:4] = 1110 or 1111 |

Four change-of-state detectors are associated with inputs IP0, IP1, IP2, and IP3. If a high-to-low or low-tohigh transition occurs on any of these inputs, the corresponding bit in the input port change register (IPCR - address 0x04) will be set accordingly. The sampling clock of the change detectors is the XTAL1/ 96 tap of the baud rate generator, which is 38.4kHz if XTAL1 is 3.6864MHz. A new input level must be sampled on two consecutive sampling clocks to detect a change. Also, users can program the XR88C92/192 to allow a change of state in any of the inputs IP0 through IP3 to generate an interrupt to the CPU. See description of the Interrupt Status Register (ISR, address 0x05) for details. The IPCR bits are cleared when the CPU reads the register. Also see the Baud Rate Table on page 18.

#### MULTI-PURPOSE OUTPUTS (OP0 - OP7)

The eight output pins (OP0 - OP7) can either be used as general purpose outputs or can be used for alternate functions representing various conditions using - Mode Registers 1 and 2 (MR1A, MR1B, MR2A, MR2B)

- Output Port Configuration Register (OPCR)

- Set Output Port Register (SOPR), and

- Reset Output Port Register (ROPR).

#### OP0 and OP1:

The output OP0 can function as the channel A requestto-send (-RTSA) output for either the transmitter (MR2A bit-5 = 1) or the receiver (MR1A bit-7 = 1). Note that only one of these bits should be set to '1' at a given time. See the description of the transmitter RTS and receiver RTS in the 'Transmitter' and 'Receiver' sections of this datasheet respectively. The output OP1 acts as the channel B request-to-send (-RTSB) output and is controlled in a similar way by the channel B registers.

**Figure 1: Crystal Connection**

Rev. 1.33

#### OP2 - OP7:

The other outputs (OP2 - OP7) are configured via the OPCR. Please see the description under the OPCR register for the details.

#### CRYSTAL INPUTS (XTAL1 & XTAL2)

If a crystal is used, it is connected between XTAL1 and XTAL2, in which case a capacitor of approximately 22 to 47 pF should be connected from each of these pins to ground. If an external CMOS-level clock is used, the pin XTAL2 must be left open.

NOTE: The terms assertion and negation will be used extensively to avoid confusion when dealing with a mixture of "active low" and "active high" signals. The term assert or assertion indicates that a signal is active or true, independent of whether that level is represented by a high or low voltage. The term negate or negation indicates that a signal is inactive or false.

#### **RESET(RESET)**

The XR88C92/192 can be reset by asserting the RESET signal or by programming the appropriate internal registers. A hardware reset (assertion of RESET) clears the following registers:

- · Status Registers A and B (SRA and SRB)

- · Interrupt Mask Register (IMR)

- · Interrupt Status Register (ISR)

- Output Port Configuration Register (OPCR)

RESET also performs the following operations:

- · Places the outputs OP0 through OP7 in the high state

- Places the counter/timer in counter mode

- Places channels A and B in the inactive state with the transmitter serial-data outputs (TXA and TXB) in the mark (high) state.

Reset commands can be programmed through the command registers to reset the receiver, transmitter, error status, or break-change interrupts for each channel.

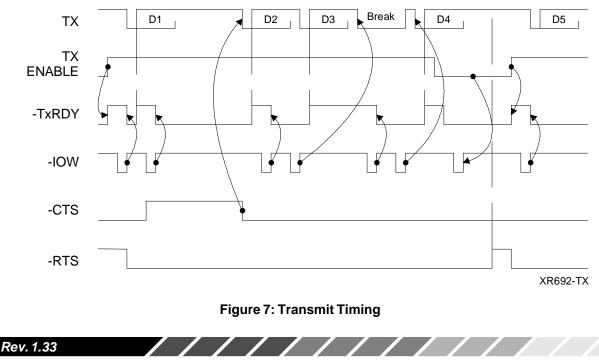

#### TRANSMITTER

The transmitter converts the parallel data from the CPU to a serial bit stream on the transmitter output pin (TXA, TXB). It automatically sends a start bit followed by the programmed number of data bits, an optional parity bit, and the programmed number of stop bits. The least-significant bit is sent first. Data is shifted out the transmit serial data output pin (TXA, TXB) on the falling

edge of the programmed clock source (XTAL1, IP3 or IP5: see CSR bits 3:0). After the transmission of the stop bits, and a new character is not available in the transmit FIFO, the transmitter serial data output (TXA, TXB) remains high. Transmission resumes when the CPU loads a new character into the transmit FIFO. If the transmitter receives a disable command (CRA, CRB bits 3:2), it will continue operating until the character in the transmit shift register is completely sent out. Other characters in the FIFO are neither sent nor discarded, but will be sent when the transmitter is re-enabled.

*TX RTS Control:* Users can program the transmitter to automatically negate the request-to-send (RTS) output (alternate function of OP0 and OP1 for channels A and B respectively) on completion of a message transmission (using MR2A, MR2B bit-5). If the transmitter is programmed to operate with RTS control, the RTS output must be manually asserted before each message is transmitted. Also, the transmitter needs to be disabled after all the required data are loaded into the FIFO. Then, the RTS output will be automatically negated when the transmit-shift register and the TX FIFO are both empty. In automatic RTS mode, no more characters can be written to the FIFO after the transmitter is disabled.

If auto clear-to-send (CTS) control is enabled (using MR2A, MR2B bit-4), the CTS input (alternate function of IP0 and IP1 for channels A and B respectively) must be asserted (low) in order for the character to be transmitted. If it gets negated (high) in the middle of a transmission, the character in the shift register is transmitted and the transmit data output (TXA, TXB) then remains in the marking state until CTSA, CTSB gets asserted again.

The transmitter can also be forced to send a continuous low (space) condition by issuing the start-break command (see CRA, CRB bits 7:4). The state of CTS is ignored by the transmitter when it is set to send a break. A start-break is deferred as long as the transmitter has characters to send, but if normal character transmission is inhibited by CTS, the start-break will proceed. The start-break must be terminated by a stop-break or a TX disable + TX reset before normal character transmission can resume.

The channel A and B transmitters are enabled for data transmission through their respective command registers (see CRA, CRB bits 3:2). The transmit FIFO trigger levels (see MR0A, MR0B bits 4 and 5) are used to generate an interrupt request to the CPU on the -INT pin.

Rev. 1.33

This is also reflected in the Interrupt Status Register, ISR bit-0 for channel A and bit-4 for channel B. This is different from the TxRDY bit in the status register.

The TxRDY bit in the status register (SRA, SRB bit-2) indicates if the TX FIFO has at least one empty location. This can also be programmed to appear at the output pin OP6/OP7. The TxEMT bit (SRA, SRB bit-3) indicates if both the TX FIFO and the TX Shift Register are empty.

The transmitter can be reset through a software command (CRA, CRB bits 7:4). If it is reset, operation ceases immediately and must be enabled through the command register before resuming operation. Reset also discards any characters in the FIFO.

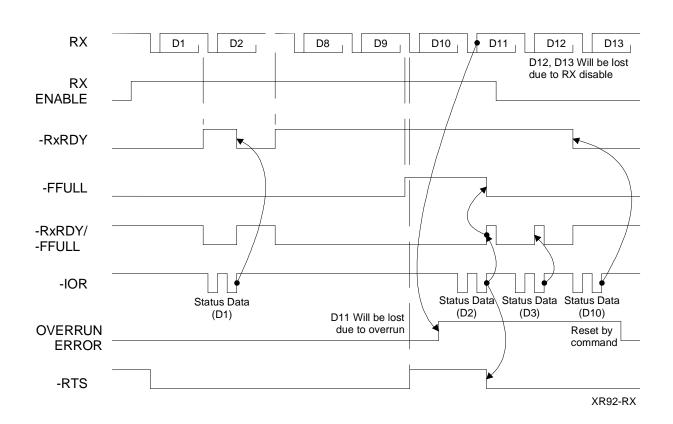

#### RECEIVER

The channel A and B receivers are enabled for data reception through the respective channels command register (CRA, CRB bits 1:0). The channels receiver looks for the high-to-low (mark-to-space) transition of a start bit on the receiver serial-data input pin. If operating in 16X clock mode, the serial input data is re-sampled on the next 7 clocks. If the receiver serial data is sampled high, the start bit is invalid and the search for a valid start bit begins again. If receiver serial data is still low, a valid start bit is assumed and the receiver continues to sample the input at one bit time intervals (at the theoretical center of the bit) until the proper number of data bits and the parity bit (if any) have been assembled and one stop bit has been detected. If an 1X clock is used, data is sampled at one bit time intervals throughout, including the start bit. Data on the receiver serial data input pin is sampled on the rising edge of the programmed clock source (XTAL1, IP4 or IP6: see CSR bits 7:4).

In this process, the least significant bit is received first. The receiver buffer is composed of the FIFO (8/16 locations in XR88C92/192 respectively) and a receive shift register connected to the receiver serial-data input. Data is assembled in the shift register and loaded into the bottom most empty FIFO location. If the character length is less than eight bits, the most significant unused bits are set to zero.

If the stop bit is sampled as a 1, the receiver will immediately look for the next start bit. However, if the stop bit is sampled as a 0, either a framing error or a received break has occurred. If the stop bit is 0 and the data and parity (if any) are not all zero, it is a framing error. The damaged character is transferred to the FIFO with the framing error flag set. If the receiver serial data remains low for one-half of the bit period after the stop bit was sampled, the receiver operates as if a new start bit transition has been detected. If the stop bit is 0 and the data and parity (if any) bits are also all zero, it is a break. A character consisting of all zeros will be loaded into the the FIFO with the received-break bit (but not the framing error bit) set to one. The receiver serial-data input must return to a high condition for at least one-half bit time before a search for the next start bit begins. Also, at this time, the received break bit is reset.

The receiver can detect a break that starts in the middle of a character provided the break persists completely through the next character time or longer. When the break begins in the middle of a character, the receiver will place the damaged character in the FIFO with the framing error bit set. Then, provided the break persists through the next character time, the receiver will also place an all-zero character in the FIFO with the received-break bit set. The parity error, framing error, overrun error, and received-break conditions (if any) set error and break flags in the status register at the received character boundary and are valid only when the receiver-ready bit (RXRDY) in the status register is set.

The receiver-ready bit in the status register (SRA, SRB bit-0) is set whenever one or more characters are available to be read by the CPU. A read of the receiver buffer produces an output of data from the top of the FIFO stack. After the read cycle, the data at the top of the FIFO stack and its associated status bits are "popped" and new data can be added at the bottom of the stack by the receive shift register. The FIFO-full status bit (SRA, SRB bit-1) is set if all 8 (or 16) stack positions are filled with data. Either the receiver-ready or the FIFO-full status bits can be selected to cause an interrupt (see MR1A, MR1B bit-6).

In addition to the data byte, three status bits (parity error, framing error, and received break) are appended to each data character in the FIFO (overrun is not). By programming the error-mode control bit (MR1A, MR1B bit-5), status can be provided for "character" or "block" modes. In the "character" mode, the status register (SRA, SRB) is updated on a character-by-character basis and applies only to the character at the top of the FIFO. Thus, the status must be read before the character is read. Reading the character pops the data byte and its error flags off the FIFO. In the "block" mode, the status provided in the status register for the parity error,

Rev. 1.33

framing error, and received-break conditions are the logical OR of these respective bits, for all the data bytes in the FIFO stack since the last reset error command (see CRA, CRB bits 7:4) was issued. That is, beginning immediately after the last reset-error command was issued, a continuous logical-OR function of corresponding status bits is produced in the status register as each character enters the FIFO.

The block mode is useful in applications requiring the exchange of blocks of information where the software overhead of checking each character's error flags cannot be tolerated. In this mode, entire messages can be received and only one data integrity check is performed at the end of each message. Although data reception in this manner has speed advantages, there are also disadvantages. If an error occurs within a message the error will not be recognized until the final check is performed. Also, there is no indication of which character(s) is in error within the message.

Reading the status register (SRA, SRB) does not affect the FIFO. The FIFO is "popped" only when the receive buffer is read. If the FIFO is full when a new character is received, that character is held in the receive shift register until a FIFO position is available. If an additional character is received while this state exists, the contents of the FIFO are not affected, but the character previously in the shift register is lost and the overrunerror status bit will be set upon receipt of the start bit of the new overrunning character.

To support flow control, a receiver can automatically negate and reassert the request-to-send (RTS) output (RX RTS control - see MR1A, MR1B bit-7). The requestto-send output (at OP0 or OP1 for channel A or B respectively) will automatically be negated by the receiver when a valid start bit is received and the FIFO stack is full. When a FIFO position becomes available, the request-to-send output will be reasserted automatically by the receiver. Connecting the request-to-send output to the clear-to send (CTS) input of a transmitting device prevents overrun errors in the receiver. The RTS output must be manually asserted the first time. Thereafter, the receiver will control the RTS output.

If the FIFO stack contains characters and the receiver is then disabled, the characters in the stack can still be read but no additional characters can be received until the receiver is again enabled. If the receiver is disabled while receiving a character, or while there is a character in the shift register waiting for a FIFO opening, these characters are lost. If the receiver is reset, the FIFO stack and all of the receiver status bits, the corresponding output ports, and the interrupt request are reset. No additional characters can be received until the receiver is again enabled.

#### LOOPBACKMODES

Besides the normal operation mode in which the receiver and transmitter operate independently, each XR88C92/192 channel can be configured to operate in various looping modes (see MR2A, MR2B bits 7:6) that are useful for local and remote system diagnostic functions.

#### **AUTOMATIC ECHO MODE**

In this mode, the channel automatically retransmits the received data on a bit-by-bit basis. The local CPU-to-receiver communication continues normally but the CPU-to-transmitter link is disabled.

#### LOCAL LOOPBACK MODE

In this mode, the transmitter output is internally connected to the receiver input. The external TX pin is held in the mark (high) state in this mode. By sending data to the transmitter and checking that the data assembled by the receiver is the same data that was sent, proper channel operation can be assured. In this mode the CPU-to-transmitter and CPU-to-receiver communications continue normally.

#### **REMOTE LOOPBACK MODE**

In this mode, the channel automatically retransmits the received data on a bit-by-bit basis. The local CPU-to-receiver and CPU-to-transmitter links are disabled. This mode is useful in testing the receiver and transmitter operation of a remote channel. This mode requires the remote channel receiver to be enabled.

#### MULTIDROP MODE - Enhanced with Extra A/D Tag Storage

Users can program the channel to operate in a wakeup mode for Multidrop applications. In this mode of operation (set MR1A, MR1B bits 4:3 = 11), the XR88C92/192, as a master station channel connected to several slave stations (a maximum of 256 unique slave stations), transmits an address character followed by a block of data characters targeted for one or more of the slave stations. The channel receivers within the slave stations are disabled, but they continuously monitor the data stream sent out from the master

Rev. 1.33

/ / /

# **XPEXAR**

station. When the slave stations' receivers detect an address character, each receiver notifies its respective CPU by setting receiver ready (-RXRDY) and generating an interrupt, if programmed to do so. Each slave station CPU then compares the received address to its station address and enables its receiver if the addresses match. Slave stations that are not addressed, continue monitoring the data stream for the next address character. An address character marks the beginning of a new block of data. After receiving a block of data, the slave stations CPU may disable the channel receiver and reinitiate the process.

A transmitted character from the master station consists of a start bit, the programmed number of data bits, an address/data (A/D) bit tag (replacing the parity bit used in normal operation), and the programmed number of stop bits. The A/D tag indicates to the slave stations channel whether the character should be interpreted as an address character or a data character. The character is interpreted as an address character if the A/D tag is set to a '1' or interpreted as a data character if it is set to a '0'. The polarity of the transmitted A/D tag is selected by programming MR1A, MR1B bit-2 to a '1' for an address character and to a '0' for data characters. Users should program the mode register prior to loading the corresponding data or address characters into the transmit buffer.

As a slave station, the XR88C92/192 receiver continuously monitors the received data stream regardless of whether it is enabled or disabled. If the receiver is disabled, it sets the receiver ready status bit and loads the character into the FIFO receive holding register stack provided the received A/D tag is a '1' (address tag). The received character is discarded if the received address/data bit is a '0' (data tag). If the receiver is enabled, all received characters are transferred to the CPU during read operations. In either case, the data bits are loaded into the data portion of the FIFO stack while the address/data bit is loaded into the status portion of the FIFO stack normally used for parity error (SRA, SRB bit-5). Framing error, overrun error, and break-detection operate normally regardless of whether the receiver is enabled or disabled. The address/data (A/D) tag takes the place of the parity bit and parity is neither calculated nor checked for characters in this mode.

**Extra Storage For The A/D Tag:** The unique feature of XR88C92/192 is that the the user need not wait at all in order to change the A/D tag from address to data

(whereas in the case of SC26C92, a wait of at least 2 bittimes is required before changing the A/D tag). This allows the user to possibly load the entire polling packet data to the TX FIFO.

#### WATCHDOG TIMER

Each of the two receivers (channel A & B) has its own 'watchdog timer' which is separate from and independent of the Counter/Timer. The watchdog timer is used to generate a receive ready time-out interrupt. When it is enabled, a counter is started everytime a character is transferred from the receive shift register to the receive FIFO and times out after 64 bit-times, at which point it will generate a receive interrupt. This is a useful feature especially when the incoming data is not a continous stream of data. For example, if RX trigger levels are used and the last set of characters is smaller than the trigger level, a receive time-out interrupt is generated instead of a regular receive interrupt. The watchdog timer, however, is not accurate as it uses the incoming data for its timing. For more accurate timing, the time-out mode in Counter/Timer should be used (see below).

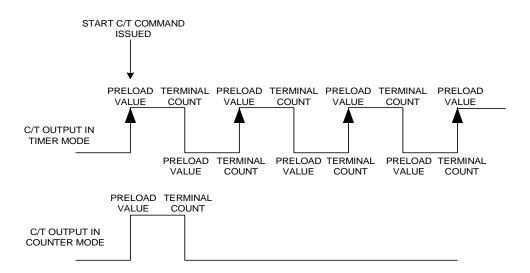

#### COUNTER/TIMER

The 16-bit counter/timer (C/T) can operate in a counter mode or a timer mode. In either mode, users can program the C/T input clock source to come from several sources (see ACR bits 6:4) and program the C/T output to appear on output port pin OP3 (see OPCR bits 3:2). The value (pre-load value) stored in the concatenation of the C/T upper register (CTPU, address 0x6) and the C/T lower register (CTPL, address 0x7) can be from 0x0001 through 0xFFFF and can be changed at any time. At power-up and after reset, the C/ T operates in counter mode.

#### COUNTER MODE

In counter mode, the CPU can start and stop the C/T. This mode allows the C/T to function as a system stopwatch or a real-time single interrupt generator. In this mode, the C/T counts down from the pre-load value using the programmed counter clock source. When a read at the start counter command register (address 0xE) is performed, the counter is initialized to the preload value and begins a countdown sequence. When the counter counts from 0x0001 to 0x0000 (terminal count), the C/T-ready bit in the interrupt status register (ISR Bit-3) is set.

Rev. 1.33

Users can program the counter to generate an interrupt request for this condition on the -INT output by unmasking the bit-3 in the Interrupt Mask Register (IMR, address 0x5). After 0x0000 the count becomes 0xFFFF, and the counter continues counting down from there. If the CPU changes the pre-load value, the counter will not recognize the new value until it receives the next start counter command (and is reinitialized). When a read at the stop counter command register (address 0xF) is performed, the counter stops the countdown sequence and clears ISR Bit-3. The count value should only be read while the counter is stopped because only one of the count registers (either CUR, at address 0x6 or CLR, at address 0x7) can be read at a time. If the counter is running, a decrement of CLR that requires a borrow from the CUR could take place between the two register reads. Figure 2 shows the C/T output in the counter mode. OP3 can be programmed to show the C/T output.

In addition to the watch dog timer described above, the C/T can be used for receive timeout function (see description under CRA, CRB in the registers section also). The C/T is more accurate and the timeout period is programmable unlike the watchdog timer. However, only one channel can use the C/T for receive timeout at any given time. The C/T timeout mode uses the received data stream to start the counter. Each time a character is shifted from the receive shift register to the receive FIFO, the C/T is reloaded with the programmed value in CTPU and CTPL and it restarts on the next C/T clock.

If a new character is not received before the C/T reaches terminal count (= 0x0000), a counter ready interrupt (ISR bit-3) is generated. The user can appropriately program the CTPU and CTPL for the desired timeout period. Typically this is slightly more than one character time. Note that if C/T is used for receiver timeout, a counter ready interrupt is generated whereas if the watchdog timer is used, a receiver ready interrupt is generated.

#### TIMER MODE

In the timer mode, the C/T runs continuously once the start command is issued (by reading the start C/T command register) and the CPU cannot stop it. When the stop command is issued (by reading the stop C/T command register), the CPU only resets the C/T interrupt. This mode allows the C/T to be used as a programmable clock source for channels A and B (see CSRA, CSRB register), and/or a periodic interrupt generator. In this mode, the C/T generates a square-wave output (see Figure 2) derived from the programmed timer input clock source. The square wave generated by the timer has a period of 2 X (pre-load value) X (period of clock source) and is available as a clock source for both channels A and B. Since the timer cannot be stopped, the values in the registers (CUR:CLR) should not be read. See description of ACR register to see how to choose clock source for the C/T.

When the start counter command register (STCR,

Figure 2: C/T output in Timer and Counter modes.

address 0xE) is read, the C/T terminates the current countdown sequence and sets its output to a '1' (OP3 can be programmed to show this output). The C/T is then initialized to the pre-load value, and begins a new countdown sequence. When the terminal count is reached (0x0000), the C/T sets its output to a '0'. Then, it gets re-initialized to the pre-load value and repeats the countdown sequence. See Figure 2 for the resulting waveform.

The timer sets the C/T-ready bit in the interrupt status register (ISR Bit-3) every other time it reaches the terminal count (at every rising edge of the output). Users can program the timer to generate an interrupt request for this condition (every second countdown cycle) on the -INT output. If the CPU changes the pre-load value, the timer will not recognize the new value until either (a) it reaches the next terminal count and is reinitialized

automatically, or

(b) it is forced to re-initialize by a start command.

When a read at the stop counter command address is performed, the timer clears ISR Bit-3 but does not stop. Because in timer mode the C/T runs continuously, it should be completely configured (pre-load value loaded and start counter command issued) before programming the timer output to appear on OP3.

#### **OTHER PROGRAMMING REMARKS**

/ / / / / / / / /

The contents of internal registers should not be changed during receiver/transmitter operation as certain changes can produce undesired results. For example, changing the number of bits per character while the transmitter is active will result in transmitting an incorrect character. The contents of the clock-select register (CSR) and ACR Bit-7 should only be changed after the receiver(s) and transmitter(s) have been issued software RX and TX reset commands. Similarly, changes to the auxiliary control register (ACR Bits 4-6) should only be made while the counter/timer (C/T) is not used.

The mode registers of each channel MR0, MR1 and MR2 are accessed via an auxiliary pointer. The pointer is set to mode register one (MR1) by RESET. It can be set to MR0 or MR1 by issuing a "reset pointer" command (0xB0 or 0x10 respectively) via the channel's command register. Any read or write of the mode register switches the pointer to next mode register. All accesses subsequent to reading/writing MR1 will address MR2 unless the pointer is reset to MR0 or MR1 as described above. The mode, command, clock-select, and status registers are duplicated for each channel to allow independent operation and control (except that both channels are restricted to baud rates that are in the same set).

| A3                                                             | A2                                                   | <b>A1</b>                                            | <b>A0</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | READ Operation                                                                                                                                                                                                                                                                                                                                          | WRITE Operation                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A3<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1 | A2<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>0<br>0<br>0 | A1<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1 | A0<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>0<br>1<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | READ Operation<br>Mode Register A (MR0A, MR1A, MR2A)<br>Status Register A (SRA)<br>Reserved<br>Receiver Buffer A (RXA)<br>Input Port Change Register (IPCR)<br>Interrupt Status Register (ISR)<br>Counter/Timer Upper Register (CUR)<br>Counter/Timer Lower Register (CLR)<br>Mode Register B (MR0B, MR1B, MR2B)<br>Status Register B (SRB)<br>Reserved | WRITE Operation<br>Mode Register A (MR0A, MR1A, MR2A)<br>Clock-Select Register A (CSRA)<br>Command Register A (CRA)<br>Transmitter Buffer A (TXA)<br>Auxiliary Control Register (ACR)<br>Interrupt Mask Register (IMR)<br>C/T Preload value Upper Register (CTPU)<br>C/T Preload value Lower Register (CTPL)<br>Mode Register B (MR0B, MR1B, MR2B)<br>Clock-Select Register B (CSRB)<br>Command Register B (CRB) |

| 1<br>1<br>1<br>1<br>1                                          | 0<br>1<br>1<br>1                                     | 1<br>0<br>0<br>1                                     | 1<br>0<br>1<br>0<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Receiver Buffer B (RXB)<br>General Purpose Register (GPR)<br>Input Port Register (IPR)<br>Start C/T Command (STCR)<br>Stop C/T Command (SPCR)                                                                                                                                                                                                           | Transmitter Buffer B (TXB)<br>General Purpose Register (GPR)<br>Output Port Configuration Register (OPCR)<br>Set Output Port Register (SOPR)<br>Reset Output Port Register (ROPR)                                                                                                                                                                                                                                |

#### INTERNAL REGISTER DESCRIPTIONS

Rev. 1.33

| A3     | A2     | A1     | A0     | Register<br>[Default] | BIT-7                      | BIT-6                      | BIT-5                      | BIT-4                      | BIT-3                 | BIT-2                  | BIT-1                   | BIT-0                  |

|--------|--------|--------|--------|-----------------------|----------------------------|----------------------------|----------------------------|----------------------------|-----------------------|------------------------|-------------------------|------------------------|

| 0      | 0      | 0      | 0      | MRA0[00]              | Watch<br>dog timer         | RX<br>trigger<br>level [1] | TX<br>trigger<br>level [1] | TX<br>trigger<br>level [0] | Not<br>used           | Baud<br>rate<br>ext. 2 | Factory<br>test<br>mode | Baud<br>rate<br>ext. 1 |

| 1      | 0      | 0      | 0      | MRB0[00]              | Watch<br>dog timer         | RX<br>trigger<br>level [1] | TX<br>trigger<br>level [1] | TX<br>trigger<br>level [0] | Not<br>used           | Not<br>used            | Not<br>used             | Not<br>used            |

| 0<br>1 | 0<br>0 | 0<br>0 | 0<br>0 | MRA1[00]<br>MRB1[00]  | RX<br>RTS<br>control       | RX<br>trigger<br>level [0] | Error<br>mode              | Parity<br>mode             | Parity<br>mode        | Parity<br>type         | Word<br>length          | Word<br>length         |

| 0<br>1 | 0<br>0 | 0<br>0 | 0<br>0 | MRA2[00]<br>MRB2[00]  | Loopback<br>mode<br>select | Loopback<br>mode<br>select | TX<br>RTS<br>control       | Auto<br>CTS<br>control     | Stop<br>bit<br>length | Stop<br>bit<br>length  | Stop<br>bit<br>length   | Stop<br>bit<br>length  |

| 0<br>1 | 0<br>0 | 0<br>0 | 1<br>1 | SRA[00]<br>SRB[00]    | Received<br>break          | Framing<br>error           | Parity<br>error            | Overrun<br>error           | Tx<br>empty           | Tx<br>ready            | Rx FIFO<br>full         | Rx<br>ready            |

| 0<br>1 | 0<br>0 | 0<br>0 | 1<br>1 | CSRA[00]<br>CSRB[00]  | RX<br>clock                | RX<br>clock                | RX<br>clock                | RX<br>clock                | TX<br>clock           | TX<br>clock            | TX<br>clock             | TX<br>clock            |

| 0<br>1 | 0<br>0 | 1<br>1 | 0<br>0 | CRA[00]<br>CRB[00]    | Misc.<br>command           | Misc.<br>command           | Misc.<br>command           | Misc.<br>command           | TX<br>disable         | TX<br>enable           | RX<br>disable           | RX<br>enable           |

| 0<br>1 | 0<br>0 | 1<br>1 | 1<br>1 | RXA[XX]<br>RXB[XX]    | Bit-7                      | Bit-6                      | Bit-5                      | Bit-4                      | Bit-3                 | Bit-2                  | Bit-1                   | Bit-0                  |

| 0<br>1 | 0<br>0 | 1<br>1 | 1<br>1 | TXA[XX]<br>TXB[XX]    | Bit-7                      | Bit-6                      | Bit-5                      | Bit-4                      | Bit-3                 | Bit-2                  | Bit-1                   | Bit-0                  |

| 0      | 1      | 0      | 0      | IPCR[00]              | Delta<br>IP3               | Delta<br>IP2               | Delta<br>IP1               | Delta<br>IP0               | IP3<br>input          | IP2<br>input           | IP1<br>input            | IP0<br>input           |

| 0      | 1      | 0      | 0      | ACR[00]               | Baud<br>rate set<br>select | C/T<br>mode                | C/T<br>mode                | C/T<br>mode                | Delta<br>IP3<br>int.  | Delta<br>IP2<br>int.   | Delta<br>IP1<br>int.    | Delta<br>IP0<br>int.   |

| 0      | 1      | 0      | 1      | ISR[00]               | Input<br>port<br>change    | Delta<br>break B           | RxB<br>ready               | TxB<br>ready               | C/T<br>ready          | Delta<br>break A       | RxA<br>ready            | TxA<br>ready           |

| 0      | 1      | 0      | 1      | IMR[00]               | Input<br>port<br>change    | Delta<br>break B           | RxB<br>ready               | TxB<br>ready               | C/T<br>ready          | Delta<br>break A       | RxA<br>ready            | TxA<br>ready           |

| 0      | 1      | 1      | 0      | CTPU[00]<br>CUR[00]   | Bit-15                     | Bit-14                     | Bit-13                     | Bit-12                     | Bit-11                | Bit-10                 | Bit-9                   | Bit-8                  |

| 0      | 1      | 1      | 1      | CTPL[00]<br>CLR[00]   | Bit-7                      | Bit-6                      | Bit-5                      | Bit-4                      | Bit-3                 | Bit-2                  | Bit-1                   | Bit-0                  |

| 1      | 1      | 0      | 0      | GPR[00]               | Bit-7                      | Bit-6                      | Bit-5                      | Bit-4                      | Bit-3                 | Bit-2                  | Bit-1                   | Bit-0                  |

| 1      | 1      | 0      | 1      | IPR[XX]               | Not<br>Used                | IP6                        | IP5                        | IP4                        | IP3                   | IP2                    | IP1                     | IP0                    |

|        |        | 0      | 1      | OPCR[00]              | OP7                        | OP6                        | OP5                        | OP4                        | OP3                   | OP3                    | OP2                     | OP2                    |

| 1      | 1      | 1      | 0      | STCR[XX]              | Х                          | Х                          | Х                          | Х                          | Х                     | Х                      | Х                       | Х                      |

| 1      | 1      | 1      | 0      | SOPR[00]              | Bit-7                      | Bit-6                      | Bit-5                      | Bit-4                      | Bit-3                 | Bit-2                  | Bit-1                   | Bit-0                  |

| 1      | 1      | 1      | 1      | SPCR[XX]              | х                          | x                          | x                          | Х                          | Х                     | x                      | x                       | х                      |

| 1      | 1      | 1      | 1      | ROPR[00]              | Bit-7                      | Bit-6                      | Bit-5                      | Bit-4                      | Bit-3                 | Bit-2                  | Bit-1                   | Bit-0                  |

Rev. 1.33

# **XPEXAR**

#### MODE REGISTER 0 (MR0A, MR0B)

This register is accessed only when command is applied via CRA, CRB register (upper nibble = 0xB). After reading or writing to MR0A (or MR0B) register, the mode register pointer will point to MR1A (or MR1B) register.

#### MR0A Bit-0:

Extended baud rate table selection for both channels.

0 = Normal baud rate tables

1 = Extended baud rate tables 1

MR0A Bit-1: Special Function.

0 = Normal

1 = Factory test mode

MR0A Bit-2:

Extended baud rate table selection for both channels. 0 = Normal baud rate tables 1 = Extend baud rate tables 2

MR0A Bit-3, MR0B Bits 3-0: Not Used. Any write to this bit is ignored.

MR0A, MR0B Bits 5-4: Transmit trigger level select.

| <u>Bit-5</u>                | <u>Bit-4</u>                     | XR88C92                                                                                                                     |

|-----------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 0                           | 0                                | 8 FIFO locations empty (default)                                                                                            |

| 0                           | 1                                | 4 FIFO locations empty                                                                                                      |

| 1                           | 0                                | 6 FIFO locations empty                                                                                                      |

| 1                           | 1                                | 1 FIFO location empty                                                                                                       |

| <u>Bit-5</u><br>0<br>1<br>1 | <u>Bit-4</u><br>0<br>1<br>0<br>1 | XR88C192<br>16 FIFO locations empty (default)<br>6 FIFO locations empty<br>12 FIFO locations empty<br>1 FIFO location empty |

MR0A, MR0B Bit-6:

Receive trigger level select. This bit is associated with MR1 Bit-6.

| <u>MR0 Bit-6</u><br>0<br>1<br>1 | <u>MR1 Bit-6</u><br>0<br>1<br>0<br>1 | XR88C92<br>1 byte in FIFO (default)<br>3 bytes in FIFO<br>6 bytes in FIFO<br>8 bytes in FIFO    |

|---------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------|

| <u>MR0 Bit-6</u><br>0<br>1<br>1 | <u>MR1 Bit-6</u><br>0<br>1<br>0<br>1 | XR88C192<br>1 byte in FIFO (default)<br>6 bytes in FIFO<br>12 bytes in FIFO<br>16 bytes in FIFO |

MR0A, MR0B Bit-7: Receive time-out (watch dog timer). 0 = Disabled (default) 1 = Enabled See description under 'Watchdog Timer'.

#### MODE REGISTER 1 (MR1A, MR1B)

MR1A, MR1B are accessed after reset or by command applied via CRA, CRB register (upper nibble = 0x1). After reading or writing to MR1A (or MR1B) register, the mode register pointer will point to MR2A (or MR2B) register.

MR1A, MR1B Bits 1-0: Character Length  $0 \ 0 = 5$  (default) 1 (  $0 \ 1 = 6$  1

1 0 = 7 1 1 = 8

MR1A, MR1B Bit-2: In non-Multidrop mode, this bit selects the parity. 0 = Even Parity (default) 1 = Odd Parity

In Multidrop mode, this bit is the Address/Data flag. 0 = Data (default)

0 = Data (def)1 = Address

MR1A, MR1B Bit 4-3: Parity mode.

00 = With parity (default)10 = No parity01 = Force parity11 = Multidrop mode

MR1A, MR1B Bit-5: Data error mode. 0 = Single Character mode (default) 1 = Block (FIFO) mode

MR1A, MR1B Bit-6.

Receive trigger levels. See description under MR0 bit-6.

MR1A, MR1B Bit-7: Receive RTS flow control. 0 = No RX RTS control function (default) 1 = Auto RX RTS control function The output OP0 (OP1) serves as the -RTS signal for channel A (channel B). Note that MR2 A/B bit-5 also controls OP0 (OP1). Only one of MR1 bit-7 or MR2 bit-5 should be set to '1'.

#### MODE REGISTER 2 (MR2A, MR2B)

This register is accessed after any read or write operation to MR1A (or MR1B) register is performed. Any read or write to MR2A (or MR2B) does not change the mode register pointer. User should use one of the two reset MR pointer command (see Command

Rev. 1.33

Register) to reset the pointer to MR0 or MR1.

| MR2A, MR2B Bits 3-0:   | Stop bit length. |

|------------------------|------------------|

| 0000 = 0.563 (default) | 1000 = 1.563     |

| 0001 = 0.625           | 1001 = 1.625     |

| 0010 = 0.688           | 1010 = 1.688     |

| 0011 = 0.750           | 1011 = 1.750     |

| 0100 = 0.813           | 1100 = 1.813     |

| 0101 = 0.875           | 1101 = 1.875     |

| 0110 = 0.938           | 1110 = 1.938     |

| 0111 = 1.000           | 1111 = 2.000     |

MR2A, MR2B Bit-4: Auto CTS Flow control. 0 = No Auto CTS flow control (default) 1 = Auto CTS flow control enabled

MR2A, MR2B Bit-5: Auto Transmit RTS control. 0 = No Auto TX RTS control (default) 1 = Auto Transmit RTS function enabled The output OP0 (OP1) serves as the -RTS signal for channel A (channel B). Note that only one of MR1 bit-7 or MR2 bit-5 should be set to '1'.

MR2A, MR2B Bit 7-6: Loopback mode select.

- 0 0 = No loopback (default)

- 0 1 = Automatic Echo

- 1 0 = Local Loopback

- 1 1 = Remote Loopback

#### STATUS REGISTER (SRA, SRB)

#### SRA, SRB Bit-0: Receive Ready.

This bit indicates that one or more character(s) has been received and is waiting in the FIFO for the CPU to read them. It is set when the first character is transferred from the receive shift register to the empty FIFO, and cleared when the CPU reads the receiver buffer and there are no more characters in the FIFO after the read.

#### SRA, SRB Bit-1: Receive FIFO Full.

This bit is set when a character is transferred from the receive shift register to the receiver FIFO and the transfer fills the FIFO. All eight (or 16 in XR88C192) FIFO locations are occupied. It is cleared when the CPU reads the receiver buffer, unless another character is in the receive shift register waiting for an empty FIFO location.

#### SRA, SRB Bit-2: Transmit Ready.

This bit (when set) indicates that the transmit FIFO is not full. Transmitter ready bit is set when the transmit FIFO has at least one empty location. This bit is cleared when the transmit FIFO is full. SRA, SRB Bit-3: Transmit Empty.

This bit will be set when the channel's transmitter is empty. It indicates that both the transmit FIFO and the transmit shift register are empty. It is set after transmission of the last stop bit of the last character in the TX FIFO. It is cleared when the CPU loads a character into the transmit FIFO or when the transmitter is disabled.

#### SRA, SRB Bit-4: Overrun Error.

This bit is set when one or more characters in the received data stream have been lost. It is set on receipt of a valid start bit when the FIFO is full and a character is already in the receive shift register waiting for an empty FIFO position. When this occurs, the character in the receive shift register (and its break detect, parity error, and framing error status, if any) is overwritten. A reset error status command clears this bit.

#### SRA, SRB Bit-5: Parity Error.

This bit is set when the "with parity" or "force parity" mode is programmed by MR1A (or MR1B) and an incoming character is received with incorrect parity. In the Multidrop mode, the parity error bit position stores the received address/data tag. This bit is valid only when the RxRDY bit is set (SRA, SRB bit-0 = 1).

#### SRA, SRB Bit-6: Framing Error.

This bit is set when a stop bit was not detected when the corresponding data character in the FIFO was received. The stop bit check is made in the middle of the first stop bit position. At least one bit in the received character (data or parity) must have been a "1" to signal a framing error. After a framing error, the receiver does not wait for the line to return to the marking state (high). If the line remains low for 1/2 a bit time after the stop bit sample (that is, the nominal end of the first stop bit), the receiver treats it as the beginning of a new start bit. This bit is valid only when the RxRDY bit is set (SRA, SRB Bit-0 = 1).

#### SRA, SRB Bit-7: Received Break.

This bit indicates a character with all data bits being zero has been received without a stop bit. This bit is valid only when the RxRDY bit is set (SRA, SRB Bit-0 = 1). Only a single FIFO position is occupied when a break is received; for longer break signals, additional entries to the FIFO are inhibited until the channel A/B receiver serial data input line returns to the marking state. The break-detect circuitry can detect a break that starts in the middle of a received character however, the break condition must persist completely through the end of the current character and the next character time to be recognized as a break signal.

Rev. 1.33

Baud Rate Table for a 3.6864MHz clock. Data rates would double for a 7.3728MHz clock.

/ / / / / / / / / / / / /

|                                       |                         | 0A Bits<br>0=0          | Bit-2                   | ABit-0=1<br>=0<br>ed table 1) | Bi                      | A Bit-0=0<br>t-2=1<br>d table 2) |

|---------------------------------------|-------------------------|-------------------------|-------------------------|-------------------------------|-------------------------|----------------------------------|

| CSRA, CSRB<br>Bits 7:4 or<br>Bits 3:0 | SET-1<br>ACR<br>Bit-7=0 | SET-2<br>ACR<br>Bit-7=1 | SET-1<br>ACR<br>Bit-7=0 | SET-2<br>ACR<br>Bit-7=1       | SET-1<br>ACR<br>Bit-7=0 | SET-2<br>ACR<br>Bit-7=1          |

| 0000 (default)                        | 50                      | 75                      | 300                     | 450                           | 4800                    | 7200                             |

| 0001                                  | 110                     | 110                     | 110                     | 110                           | 880                     | 880                              |

| 0010                                  | 134.5                   | 134.5                   | 134.5                   | 134.5                         | 1076                    | 1076                             |

| 0011                                  | 200                     | 150                     | 1200                    | 900                           | 19.2k                   | 14.4k                            |

| 0100                                  | 300                     | 300                     | 1800                    | 1800                          | 28.8k                   | 28.8k                            |

| 0101                                  | 600                     | 600                     | 3600                    | 3600                          | 57.6k                   | 57.6k                            |

| 0110                                  | 1200                    | 1200                    | 7200                    | 7200                          | 115.2k                  | 115.2k                           |

| 0111                                  | 1050                    | 2000                    | 1050                    | 2000                          | 1050                    | 2000                             |

| 1000                                  | 2400                    | 2400                    | 14.4k                   | 14.4k                         | 57.6k                   | 57.6k                            |

| 1001                                  | 4800                    | 4800                    | 28.8k                   | 28.8k                         | 4800                    | 4800                             |

| 1010                                  | 7200                    | 1800                    | 7200                    | 1800                          | 57.6k                   | 14.4k                            |

| 1011                                  | 9600                    | 9600                    | 57.6k                   | 57.6k                         | 9600                    | 9600                             |

| 1100                                  | 38.4k                   | 19.2k                   | 230.4k                  | 115.2k                        | 38.4k                   | 19.2k                            |

| 1101                                  | Timer                   | Timer                   | Timer                   | Timer                         | Timer                   | Timer                            |

| 1110*                                 | IP3-16                  | X (CSRA 3:0), IF        | P4-16X (CSRA            | 7:4), IP5-16X (C              | SRB 3:0), IP6-          | 16X (CSRB 7:4)                   |

| 1111*                                 | IP3-1X                  | (CSRA 3:0), IF          | 24-1X (CSRA 7           | :4), IP5-1X (CS               | SRB 3:0), IP6-7         | 1X (CSRB 7:4)                    |

\* Baud Rate is independent of MR0 bit-0 & bit-2 and ACR bit-7 settings.

#### CLOCK SELECT REGISTER (CSRA, CSRB)

Transmit / Receive baud rates for channels A, B can be selected via this register.

CSRA, CSRB Bits 3-0.

Transmit clock select(see baud rate table).

CSRA, CSRB Bits 7-4.

Receive clock select (see baud rate table).

#### **COMMAND REGISTER (CRA, CRB)**

CRA, CRB register is used to supply commands to A, B channels respectively. Multiple commands can be specified in a single write to CRA, CRB as long as commands are non-conflicting.

- CRA, CRB Bits 1-0: Receiver Commands.

- 0 0 = No Action, Stays in Present Mode (default)

- 01 = Receiver Enabled

- 1 0 = Receiver Disabled

- 1 1 = Don't Use

Rev. 1.33

CRA, CRB Bits 3-2: Transmitter Commands.

- 0 0 = No Action, Stays in Present Mode (default)

- 01 = Transmitter Enabled

- 1 0 = Transmitter Disabled

- 1 1 = Don't Use

- CRA, CRB Bits 7-4: Miscellaneous Commands.

- $0\ 0\ 0\ 0 = No Command (default).$

- 0 0 0 1 = Reset MR Pointer to MR1.

- 0 0 1 0 = Reset Receiver. Receiver is disabled and FIFO is flushed.

- 0 0 1 1 = Reset Transmitter. Transmitter is disabled and FIFO is flushed.

- 0 1 0 0 = Reset Error Status. Clears channel A/B, break, parity, and over-run error bits in the status register.

- 0 1 0 1 = Reset Channel's Break-Change Interrupt. Clears channel A/B break detect change bit in the interrupt status register (ISR bit-2 for channel A and ISR bit-6 for channel B).

- 0 1 1 0 = Start Break. Forces the transmitter output to go low and stay low. If transmitter is empty the start of the break condition will be delayed up to two bit times. If transmitter is active, all the characters in the FIFO are transmitted before break signal is sent. Transmitter must to be enabled for this command to work.

- 0 1 1 1 = Stop Break. Transmit output will go high within two bit times.

- $1 \ 0 \ 0 \ 0 =$  Set -RTS output to low (assertion).

- 1 0 0 1 = Reset -RTS output to high (negation).

- 1 01 0 = Set Timeout Mode On. The receiver in this channel will restart the C/T as each receive character is transferred from the shift register to the receive FIFO. The C/T is placed in the counter mode, the START/STOP counter commands are disabled, the counter is stopped, and the Counter Ready Bit, ISR Bit-3 is reset. (See also Watchdog timer description)

- $1 \ 0 \ 1 \ 1 =$  Set MR pointer to MR0.

- 1 1 0 0 = Disable Timeout Mode. This command returns control of the C/T to the regular Start/ Stop counter commands. It does not stop the counter or clear any pending interrupts. After disabling the timeout mode, a "Stop Counter" command should be issued to force a reset of the ISR Bit-3.

- $1 \ 1 \ 0 \ 1 =$  Not used.

- 1 1 1 0 = Enable Power Down Mode. In this mode, the DUART oscillator is stopped and all functions requiring this clock are suspended. The execution of commands other than disable power down mode (1111) requires a XTAL1. While in the power down mode, do not issue any commands to the CRA or CRB except the disable power down mode command. The contents of all registers will be saved while in this mode. It is recommended that the transmitter and receiver be disabled prior to placing the DUART into power down mode. **This command is in CRA only.**

- 1 1 1 1 = Disable Power Down Mode. This command restarts the oscillator. After invoking this command, wait for the oscillator to start up before writing further commands to the CR A/ B. For maximum power reduction all input pins should be at GND or VCC. *This command is in CRA only.*

#### **RECEIVE BUFFER (RXA, RXB)**

The receive buffer consists of a 8-characters deep FIFO in XR88C92 and 16-characters deep FIFO in XR88C192. The received characters are transferred from the shift register one at a time to the FIFO and are stored there until read by the CPU or flushed by a reset receiver command.

#### TRANSMIT BUFFER (TXA, TXB)

The transmit buffer consists of a 8-characters deep FIFO in XR88C92 and 16-characters deep FIFO in XR88C192. Once loaded in the FIFO, the characters are transferred to the transmit shift register one at a time and transmitted unless the transmitter is disabled.

#### INPUT PORT CHANGE REGISTER (IPCR)

This is a read-only register which gives the state and the change-of-state information of the multi-purpose inputs IP0, IP1, IP2 and IP3.

IPCR Bits 3-0: Levels of IP3 - IP0.

These show the current state of IP3, IP2, IP1 and IP0 respectively.

- 0 = Low

- 1 = High

IPCR Bits 7-4: Transitions of IP3 - IP0.

These indicate if there has been a change of state in IP3, IP2, IP1 and IP0 respectively. They are cleared when the register is read by the CPU.

0 = No

1 = Yes

#### AUXILIARY CONTROL REGISTER (ACR)

#### ACR Bits 3-0: