# **Table of Contents**

| 1 | Orde  | ering Info | ormation3                                      |   |       | 4.3.7     | NFC                                                     | 61 |

|---|-------|------------|------------------------------------------------|---|-------|-----------|---------------------------------------------------------|----|

| 2 | MPC   | 5125 B     | lock Diagrams                                  |   |       | 4.3.8     | FEC                                                     | 63 |

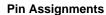

| 3 | Pin A | Assignm    | nents5                                         |   |       | 4.3.9     | USB ULPI                                                | 66 |

|   | 3.1   | 324-b      | all TEPBGA Pin Assignments 5                   |   |       | 4.3.10    | MMC/SD/SDIO Card Host Controller (SDHC) .               | 67 |

|   | 3.2   | Pin M      | uxing and Reset States                         |   |       |           | DIU                                                     |    |

|   |       |            | Power and Ground Supply Summary                |   |       | 4.3.12    | CAN                                                     | 71 |

| 4 | Elect | trical an  | d Thermal Characteristics                      |   |       | 4.3.13    | I <sup>2</sup> C                                        | 71 |

|   | 4.1   | DC El      | ectrical Characteristics                       |   |       | 4.3.14    | J1850                                                   | 72 |

|   |       | 4.1.1      | Absolute Maximum Ratings36                     |   |       | 4.3.15    | PSC                                                     | 72 |

|   |       | 4.1.2      | Recommended Operating Conditions               |   |       | 4.3.16    | GPIOs and Timers                                        | 79 |

|   |       | 4.1.3      | DC Electrical Specifications37                 |   |       | 4.3.17    | Fusebox                                                 | 79 |

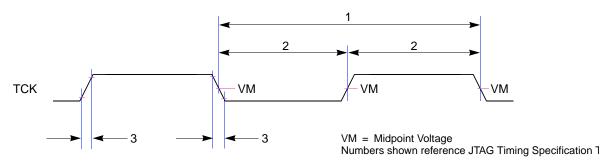

|   |       | 4.1.4      | Electrostatic Discharge                        |   |       | 4.3.18    | IEEE 1149.1 (JTAG)                                      | 80 |

|   |       | 4.1.5      | Power Dissipation                              | 5 | Syste | em Desi   | gn Information                                          | 82 |

|   |       | 4.1.6      | Thermal Characteristics                        |   | 5.1   | Power     | Up/Down Sequencing                                      | 82 |

|   | 4.2   | Oscilla    | ator and PLL Electrical Characteristics        |   | 5.2   | Systen    | n and CPU Core AV <sub>DD</sub> Power Supply Filtering. | 82 |

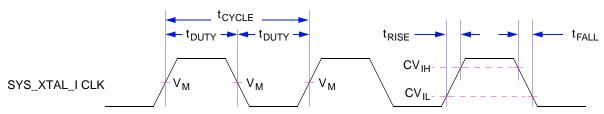

|   |       | 4.2.1      | System Oscillator Electrical Characteristics44 |   | 5.3   | Conne     | ction Recommendations                                   | 82 |

|   |       | 4.2.2      | RTC Oscillator Electrical Characteristics 44   |   | 5.4   | Pullup/   | Pulldown Resistor Requirements                          | 83 |

|   |       | 4.2.3      | System PLL Electrical Characteristics45        |   |       | 5.4.1     | Pulldown Resistor Requirements for TEST Pin             | 83 |

|   |       | 4.2.4      | e300 Core PLL Electrical Characteristics 45    |   | 5.5   | JTAG .    |                                                         | 83 |

|   | 4.3   | AC Ele     | ectrical Characteristics46                     |   |       | 5.5.1     | JTAG_TRST                                               | 83 |

|   |       | 4.3.1      | Overview                                       |   |       |           | e300 COP/BDM Interface                                  |    |

|   |       | 4.3.2      | AC Operating Frequency Data                    | 6 | Pack  | age Info  | ormation                                                | 87 |

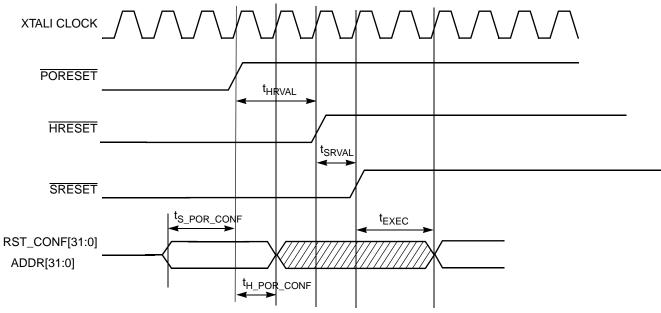

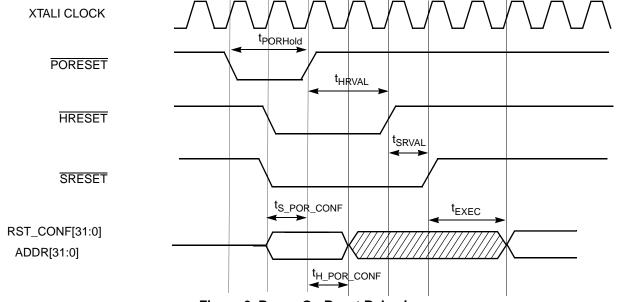

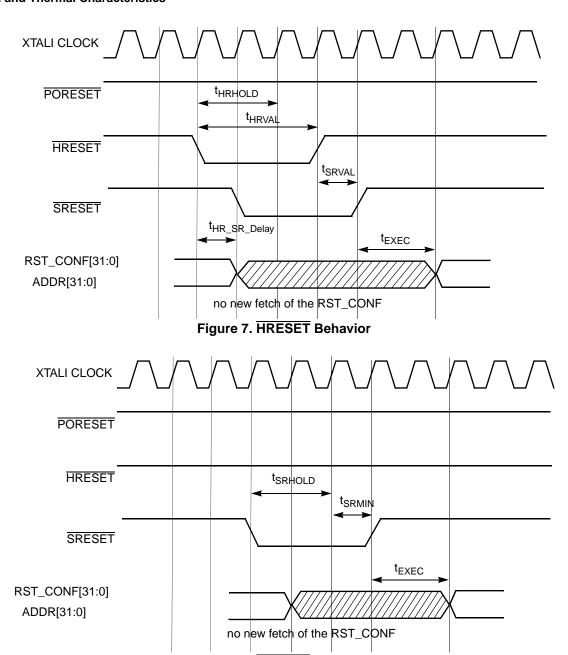

|   |       | 4.3.3      | Resets                                         |   | 6.1   | Packag    | ge Parameters                                           | 87 |

|   |       | 4.3.4      | External Interrupts                            |   | 6.2   | Mecha     | ınical Dimensions                                       | 88 |

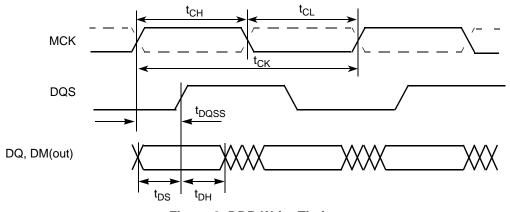

|   |       | 4.3.5      | SDRAM (DDR)50                                  | 7 | Produ | uct Doc   | umentation                                              | 91 |

|   |       | 4.3.6      | LPC                                            | 8 | Revis | sion Hist | tory                                                    | 91 |

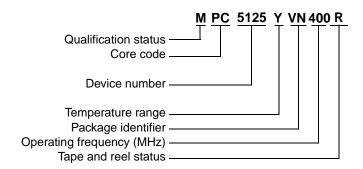

# 1 Ordering Information

Temperature Range Y = -40 °C to 125 °C, junction

Package Identifier VN = 324 TEPBGA Pb-free

Operating Frequency 400 = 400 MHz Tape and Reel Status R = Tape and reel (blank) = Trays

**Qualification Status**

P = Pre qualification

M = Fully spec. qualified, general market flow S = Fully spec. qualified, automotive flow

Note: Not all options are available on all devices. Refer to Table 1.

Figure 1. MPC5125 Orderable Part Number Description

Table 1 shows the orderable part numbers for the MPC5125.

**Table 1. MPC5125 Orderable Part Numbers**

| Freescale Part Number <sup>1</sup> | Package Description                             | Speed (MHz)                          | Operating T           | emperature <sup>2</sup> |

|------------------------------------|-------------------------------------------------|--------------------------------------|-----------------------|-------------------------|

| Treescale Fait Number              | i ackage bescription                            | Max <sup>3</sup> (f <sub>MAX</sub> ) | Min (T <sub>L</sub> ) | Max (T <sub>H</sub> )   |

| MPC5125YVN400                      | MPC5125 324TEPBGA package<br>Lead-free (PbFree) | 400 MHz core<br>200 MHz bus          | −40 °C                | 125 °C                  |

#### NOTES:

All packaged devices are PPC5125, rather than MPC125, until product qualifications are complete.

<sup>&</sup>lt;sup>2</sup> The lowest ambient operating temperature (T<sub>A</sub>) is referenced by T<sub>L</sub>; the highest junction temperature is referenced by T<sub>H</sub>.

<sup>&</sup>lt;sup>3</sup> Maximum speed is the maximum frequency allowed including frequency modulation (FM).

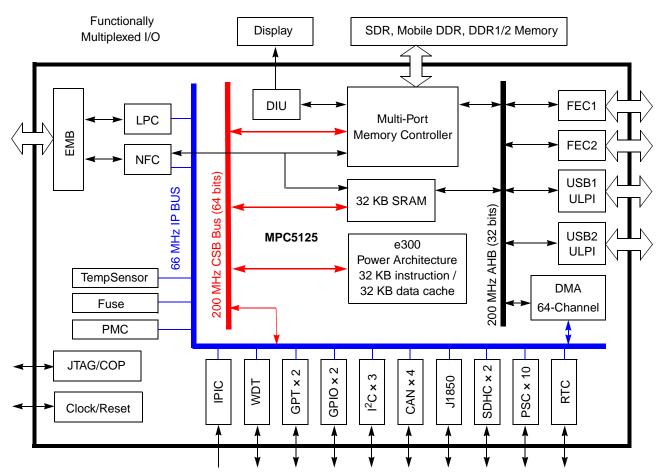

# 2 MPC5125 Block Diagrams

Figure 2 shows a simplified MPC5125 block diagram.

Figure 2. Simplified MPC5125 Block Diagram

This section details pin assignments.

# 3.1 324-ball TEPBGA Pin Assignments

Figure 3 shows the 324-ball TEPBGA pin assignments.

|    |                     |                | 1              | 1                   | 1              | 1               |                |                |                 |                                |               |              |              | ı            |              |              |                | ı            |                |                | 1              |       |

|----|---------------------|----------------|----------------|---------------------|----------------|-----------------|----------------|----------------|-----------------|--------------------------------|---------------|--------------|--------------|--------------|--------------|--------------|----------------|--------------|----------------|----------------|----------------|-------|

|    | 1                   | 2              | 3              | 4                   | 5              | 6               | 7              | 8              | 9               | 10                             | 11            | 12           | 13           | 14           | 15           | 16           | 17             | 18           | 19             | 20             | 21             | 22    |

| Α  | VSS                 | VSS            | EMB_A<br>D01   | EMB_A<br>D00        | GPIO01         | GPIO02          | RTC_X<br>TALO  | RTC_X<br>TALI  | SYS_X<br>TALI   | SYS_X<br>TALO                  | AVDD_<br>SPLL | PSC0_<br>1   | PSC0_<br>2   | VDD_I<br>O   | PSC1_<br>4   | CAN2_<br>TX  | HRESE<br>T_B   | SRESE<br>T_B | I2C1_S<br>DA   | MCAS_<br>B     | MWE_B          | VSS   |

| В  | VSS                 | EMB_A<br>D05   | EMB_A<br>D03   | EMB_A<br>D02        | J1850_<br>TX   | GPIO00          | VSS            | CAN2_<br>RX    | VDD_I<br>O      | AVSS_<br>OSC_T<br>MPS_S<br>PLL | AVSS_<br>CPLL | VDD_I<br>O   | PSCO_<br>3   | PSC1_        | CAN1_<br>TX  | TDO          | VDD_I<br>O     | I2C1_S<br>CL | VDD_I<br>O_MEM | MA15           | MA14           | MA11  |

| С  | EMB_A<br>D11        | EMB_A<br>D09   | EMB_A<br>D07   | EMB_A<br>D06        | VDD_I<br>O     | J1850_<br>RX    | GPIO03         | HIB_M<br>ODE_B | CAN1_<br>RX     | AVDD_<br>OSC_T<br>MPS          | PSC0_<br>0    | PSC1_<br>0   | PSC1_<br>1   | VDD_I<br>O   | TDI          | TCK          | PORES<br>ET_B  | MCKE         | MRAS_<br>B     | MA12           | VDD_I<br>O_MEM | MA09  |

| D  | TMPS_<br>ANAVIZ     | EMB_A<br>D10   | VDD_I<br>O     | AVDD_<br>FUSEW<br>R | EMB_A<br>D04   | PSC_M<br>CLK_IN | VSS            | VBAT           | SPLL_A<br>NAVIZ | AVDD_<br>CPLL                  | PSC0_<br>4    | VSS          | PSC1_<br>3   | TEST         | TMS          | TRST_<br>B   | VDD_I<br>O_MEM | MCS_B        | VDD_I<br>O_MEM | MA13           | MA08           | MA06  |

| Е  | EMB_A<br>D15        | EMB_A<br>D13   | EMB_A<br>D12   | EMB_A<br>D08        |                |                 |                |                |                 |                                |               |              |              |              |              |              |                |              | MA10           | MA07           | MA04           | MA03  |

| F  | EMB_A<br>D21        | VDD_I<br>O     | EMB_A<br>D16   | VSS                 |                |                 |                |                |                 |                                |               |              |              |              |              |              |                |              | MA02           | MA05           | VSS            | MA01  |

| G  | EMB_A<br>D25        | EMB_A<br>D18   | EMB_A<br>D17   | VDD_I<br>O          |                |                 |                |                |                 | TOF                            | DO/           | VN VI        | EW           |              |              |              |                |              | VDD_I<br>O_MEM | MA00           | MBA2           | MCK_B |

| н  | EMB_A<br>D28        | VDD_I<br>O     | EMB_A<br>D20   | EMB_A<br>D14        |                |                 |                |                |                 |                                |               |              |              |              |              |              |                |              | MBA0           | MBA1           | VDD_I<br>O_MEM | мск   |

| J  | EMB_A<br>D31        | EMB_A<br>D26   | EMB_A<br>D23   | EMB_A<br>D19        |                |                 |                |                | VSS             | VDD                            | VDD           | VDD          | VDD          | VSS          |              |              |                |              | MODT           | MDQ31          | MDQ30          | MDQ29 |

| К  | EMB_A<br>X00        | VSS            | EMB_A<br>D24   | EMB_A<br>D22        |                |                 |                |                | VSS             | VSS                            | VSS           | VSS          | VSS          | VDD          |              |              |                |              | MVTT3          | MDQ28          | VSS            | MDM3  |

| L  | LPC_A<br>X03        | EMB_A<br>X02   | EMB_A<br>D29   | VSS                 |                |                 |                |                | VDD             | VSS                            | VSS           | VSS          | VSS          | VDD          |              |              |                |              | VSS            | MDQ26          | MDQ27          | MDQS3 |

| М  | LPC_C<br>S0_B       | VDD_I<br>O     | EMB_A<br>D30   | EMB_A<br>D27        |                |                 |                |                | VDD             | VSS                            | VSS           | VSS          | VSS          | VDD          |              |              |                |              | MVTT2          | MDQ23          | MDQ24          | MDQ25 |

| N  | NFC_R<br>B          | LPC_O<br>E_B   | LPC_R<br>WB    | EMB_A<br>X01        |                |                 |                |                | VSS             | VSS                            | VSS           | VSS          | VSS          | VDD          |              |              |                |              | MVREF          | MDQ20          | VSS            | MDQ22 |

| Р  | NFC_C<br>E0_B       | VSS            | LPC_A<br>CK_B  | VSS                 |                |                 |                |                | VSS             | VDD                            | VDD           | VDD          | VDD          | VSS          |              |              |                |              | VDD_I<br>O_MEM | MDQ18          | MDQS2          | MDQ21 |

| R  | SDHC1<br>_D2        | SDHC1<br>_D3   | VDD_I<br>O     | LPC_C<br>LK         |                |                 |                |                |                 |                                |               |              |              |              |              |              |                |              | MVTT1          | MDQ16          | VDD_I<br>O_MEM | MDM2  |

| Т  | SDHC1<br>_CLK       | SDHC1<br>_CMD  | SDHC1<br>_D0   | SDHC1<br>_D1        |                |                 |                |                |                 |                                |               |              |              |              |              |              |                |              | VDD_I<br>O_MEM | MDQ13          | MDQ17          | MDQ19 |

| U  | FEC1_<br>CRS        | VSS            | FEC1_<br>COL   | I2C2_S<br>DA        |                |                 |                |                |                 |                                |               |              |              |              |              |              |                |              | MDQ07          | MDQS1          | VSS            | MDQ15 |

| ٧  | FEC1_<br>MDC        | FEC1_<br>MDIO  | VDD_I<br>O     | I2C2_S<br>CL        |                |                 |                |                |                 |                                |               |              |              |              |              |              |                |              | VDD_I<br>O_MEM | MDQ10          | MDM1           | MDQ14 |

| w  | FEC1_<br>TX_CL<br>K | FEC1_<br>TX_ER | FEC1_<br>TXD_1 | FEC1_<br>TXD_0      | VDD_I<br>O     | USB1_<br>STOP   | USB1_<br>DIR   | VSS            | USB1_<br>DATA1  | VSS                            | DIU_HS<br>YNC | VSS          | DIU_LD<br>08 | DIU_LD<br>13 | VDD_I<br>O   | DIU_LD<br>21 | VSS            | MVTT0        | VDD_I<br>O_MEM | MDQ06          | MDQ11          | MDQ12 |

| Υ  | FEC1_<br>TXD_3      | VSS            | FEC1_<br>TX_EN | FEC1_<br>RXD_2      | FEC1_<br>RX_ER | USB1_<br>DATA6  | USB1_<br>DATA5 | USB1_<br>CLK   | USB1_<br>DATA0  | DIU_LD<br>01                   | DIU_LD<br>03  | DIU_LD<br>07 | DIU_LD<br>10 | DIU_LD<br>14 | DIU_LD<br>17 | DIU_LD<br>22 | DIU_VS<br>YNC  | MDQ01        | MDM0           | MDQ05          | VDD_I<br>O_MEM | MDQ09 |

| AA | FEC1_<br>TXD_2      | FEC1_<br>RXD_3 | FEC1_<br>RXD_1 | VDD_I<br>O          | USB1_<br>NEXT  | VSS             | USB1_<br>DATA4 | DIU_DE         | VDD_I<br>O      | DIU_LD<br>02                   | DIU_LD<br>04  | VDD_I<br>O   | DIU_LD<br>11 | VDD_I<br>O   | DIU_LD<br>16 | VDD_I<br>O   | DIU_LD<br>23   | VSS          | MDQ02          | MDQS0          | MDQ04          | MDQ08 |

| АВ | VSS                 | FEC1_<br>RXD_0 | FEC1_<br>RX_DV | FEC1_<br>RX_CL<br>K | USB1_<br>DATA7 | USB1_<br>DATA3  | USB1_<br>DATA2 | DIU_CL<br>K    | DIU_LD<br>00    | DIU_LD<br>05                   | DIU_LD<br>06  | DIU_LD<br>09 | DIU_LD<br>12 | DIU_LD<br>15 | DIU_LD<br>18 | DIU_LD<br>19 | DIU_LD<br>20   | VDD_I<br>O   | MDQ00          | VDD_I<br>O_MEM | MDQ03          | VSS   |

Figure 3. Ball Map for the MPC5125 324 TEPBGA Package

MPC5125 Microcontroller Data Sheet, Rev. 4

Freescale Semiconductor 5

# Pin Muxing and Reset States

Table 2 provides the pinout listing for the MPC5125.

Table 2. MPC5125 Pin Multiplexing

|   | Pin                                                                    | B6                                                         | A5                                                         | A6                                                         | C7                                                         | A8                           | A7                           | C8                                                                                            |                       |

|---|------------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------|------------------------------|------------------------------|-----------------------------------------------------------------------------------------------|-----------------------|

|   | Notes                                                                  | Dedicated input can be used to receive an external wakeup. | Dedicated input can be used to receive an external wakeup. | Dedicated input can be used to receive an external wakeup. | Dedicated input can be used to receive an external wakeup. | I                            |                              | In Hibernation mode , this pin<br>provides a signal to shut down<br>an external power supply. |                       |

|   | Power Domain                                                           | VBAT                                                       | VBAT                                                       | VBAT                                                       | VBAT                                                       | VBAT                         | VBAT                         | VBAT                                                                                          |                       |

| ı | I/O<br>Direction                                                       | -                                                          | -                                                          | -                                                          | -                                                          | -                            | 0                            | 0                                                                                             |                       |

|   | Peripheral <sup>5</sup>                                                | GPI01<br><br>                                              | GPI01<br> -<br> -                                          | GPI01<br>—<br>—                                            | GPI01<br><br>                                              | RTC<br>                      | RTC<br>                      | RTC                                                                                           | Analog Visible Signal |

|   | Functions <sup>4</sup>                                                 | GPI000                                                     | GPI001                                                     | GPI002<br> -<br> -                                         | GPI003<br> -<br> -                                         | RTC_XTALI                    | RTC_XTALO<br> -<br> -        | HIB_MODE<br>                                                                                  | Analog \              |

| • | Alternate<br>Function <sup>3</sup>                                     | ALTO<br>ALT1<br>ALT2<br>ALT3                               | ALTO<br>ALT1<br>ALT2<br>ALT3                               | ALTO<br>ALT1<br>ALT2<br>ALT3                               | ALT0<br>ALT1<br>ALT2<br>ALT3                               | ALTO<br>ALT1<br>ALT2<br>ALT3 | ALTO<br>ALT1<br>ALT2<br>ALT3 | ALTO<br>ALT1<br>ALT2<br>ALT3                                                                  |                       |

|   | Pad I/O<br>Control<br>Register <sup>1</sup><br>and Offset <sup>2</sup> | 1                                                          | 1                                                          | 1                                                          | 1                                                          | 1                            | 1                            | 1                                                                                             |                       |

|   | Pin                                                                    | 0PIO00                                                     | GPI001                                                     | GPI002                                                     | GPI003                                                     | RTC_XTALI                    | RTC_XTALO                    | HIB_MODE                                                                                      |                       |

Table 2. MPC5125 Pin Multiplexing (continued)

| Pin         | Pad I/O<br>Control<br>Register <sup>1</sup><br>and Offset <sup>2</sup> | Alternate<br>Function <sup>3</sup> | Functions <sup>4</sup> | Peripheral <sup>5</sup>                        | I/O<br>Direction | Power Domain      | Notes | Pin |

|-------------|------------------------------------------------------------------------|------------------------------------|------------------------|------------------------------------------------|------------------|-------------------|-------|-----|

| SPLL_ANAVIZ | I                                                                      | ALTO<br>ALT1<br>ALT2<br>ALT3       | SPLL_ANAVIZ            |                                                | 111              | I                 | I     | 60  |

| TMPS_ANAVIZ | I                                                                      | ALTO<br>ALT1<br>ALT2<br>ALT3       | TMPS_ANAVIZ            | 111                                            | 111              | I                 | I     | 70  |

| SYS_XTALI   | I                                                                      | ALTO<br>ALT1<br>ALT2<br>ALT3       | SYS_XTALI              | SysClock — — — — — — — — — — — — — — — — — — — | -                | SYS_PLL_<br>_AVDD | I     | A9  |

| SYS_XTALO   | I                                                                      | ALTO<br>ALT1<br>ALT2<br>ALT3       | SYS_XTALO              | SysClock — — — — — — — — — — — — — — — — — — — | 0                | SYS_PLL           | I     | A10 |

| MCS         | 0x00<br>IO_CON-<br>TROL_MEM                                            | ALTO<br>ALT1<br>ALT2<br>ALT3       | MCS0                   | DRAM<br> -<br> -                               | 0                | VDD_IO_MEM        | I     | D18 |

| MCAS        | 0x00<br>IO_CON-<br>TROL_MEM                                            | ALTO<br>ALT1<br>ALT2<br>ALT3       | MCAS                   | DRAM                                           | 0                | VDD_IO_MEM        | I     | A20 |

| MRAS        | 0x00<br>IO_CON-<br>TROL_MEM                                            | ALTO<br>ALT1<br>ALT2<br>ALT3       | MRAS —                 | DRAM<br><br>                                   | 0                | VDD_IO_MEM        |       | C19 |

| MVREF       | I                                                                      | ALT0<br>ALT1<br>ALT2<br>ALT3       | MVREF                  | DRAM — — — — — — — — — — — — — — — — — — —     | -                | VDD_IO_MEM        | I     | N19 |

|             |                                                                        |                                    |                        |                                                |                  |                   |       |     |

Table 2. MPC5125 Pin Multiplexing (continued)

| Pin                                                                    | W18                                                                                                                           | R19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | M19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | X<br>9<br>13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | A21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | AB19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Y18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | AA19                                       |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Notes                                                                  | I                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                            |

| Power Domain                                                           | VDD_IO_MEM                                                                                                                    | VDD_IO_MEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VDD_IO_MEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | VDD_IO_MEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | VDD_IO_MEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VDD_IO_MEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VDD_IO_MEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VDD_IO_MEM                                 |

| I/O<br>Direction                                                       | -                                                                                                                             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0.                                         |

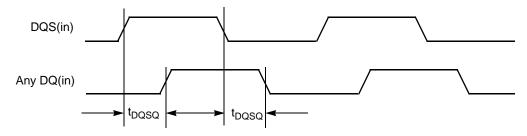

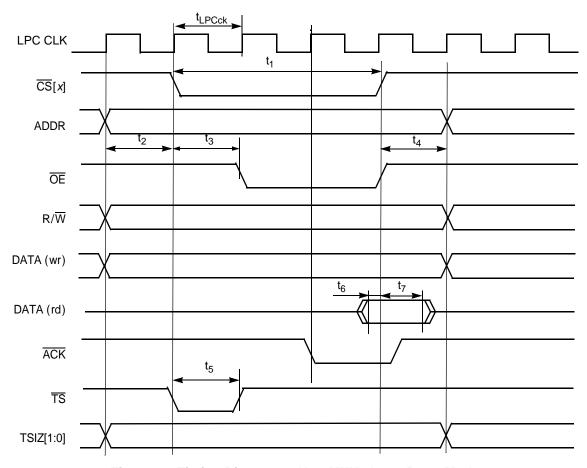

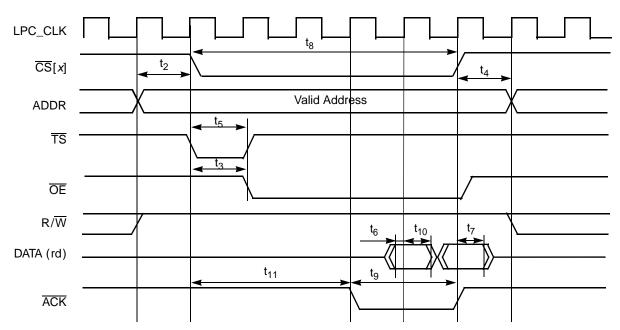

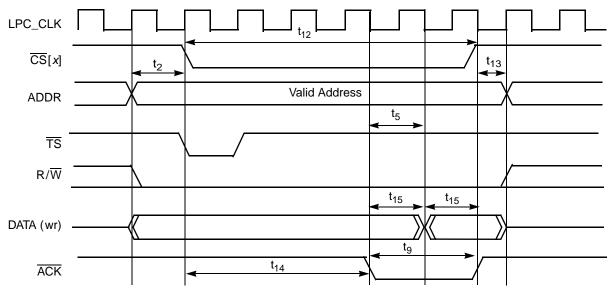

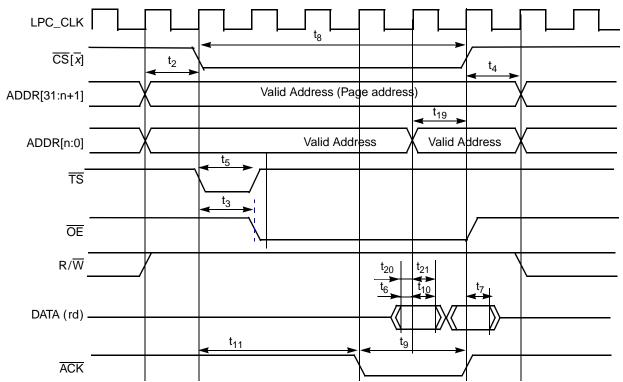

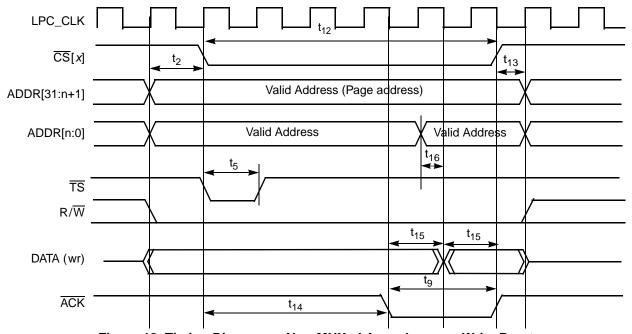

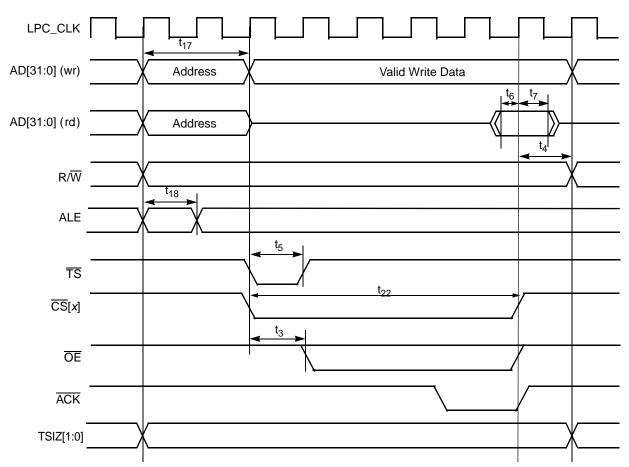

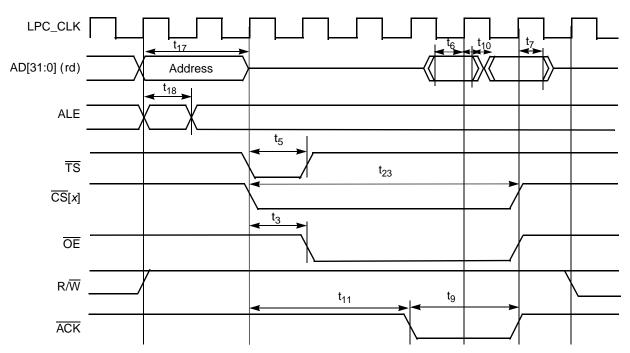

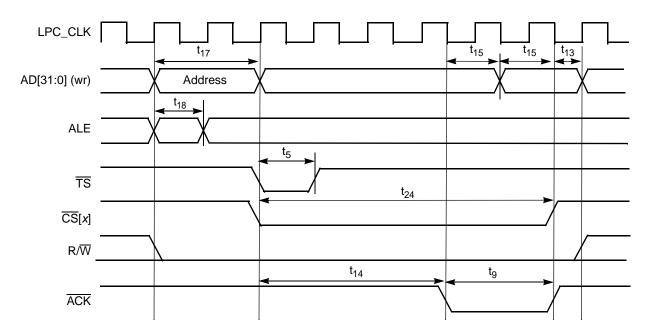

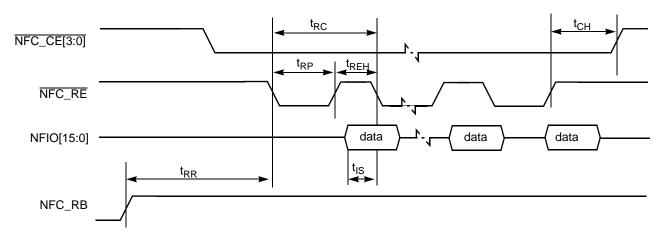

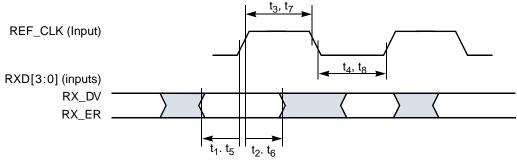

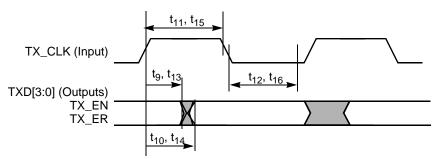

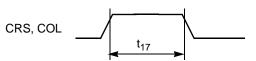

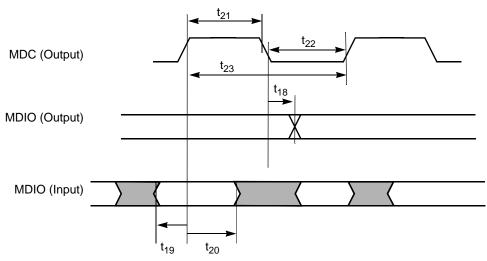

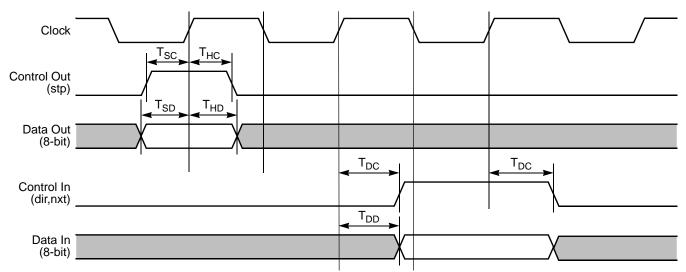

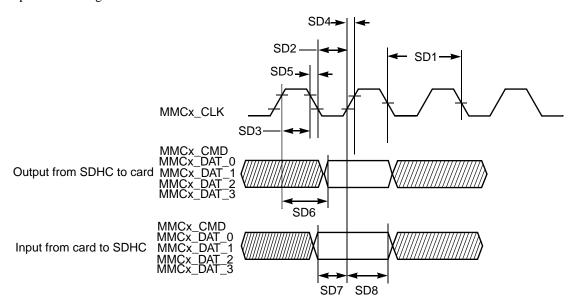

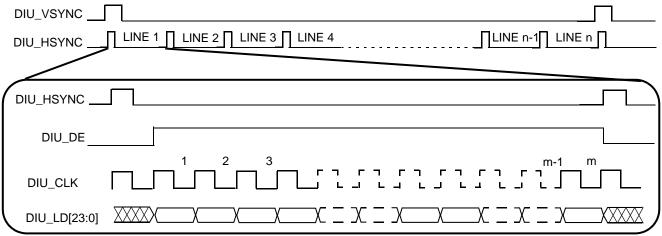

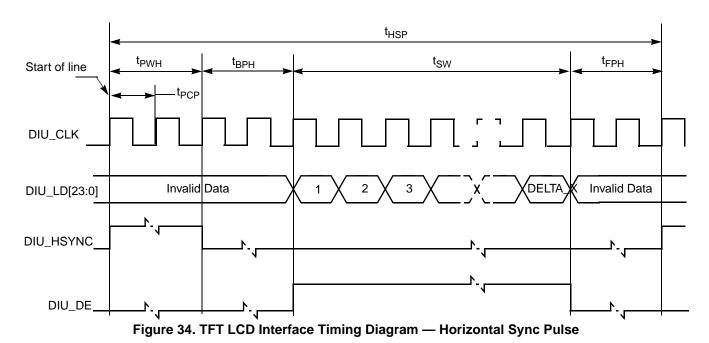

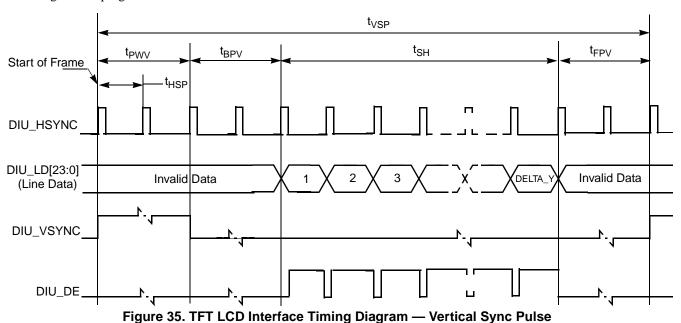

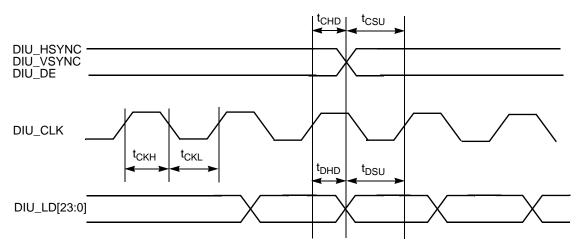

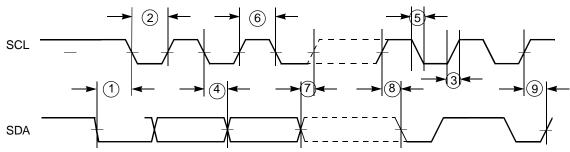

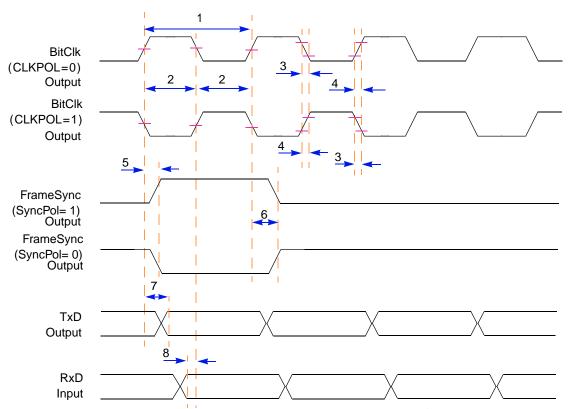

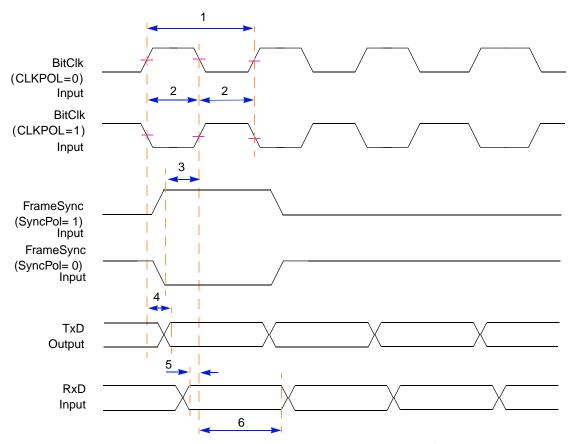

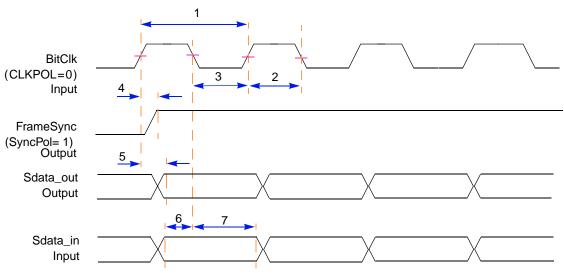

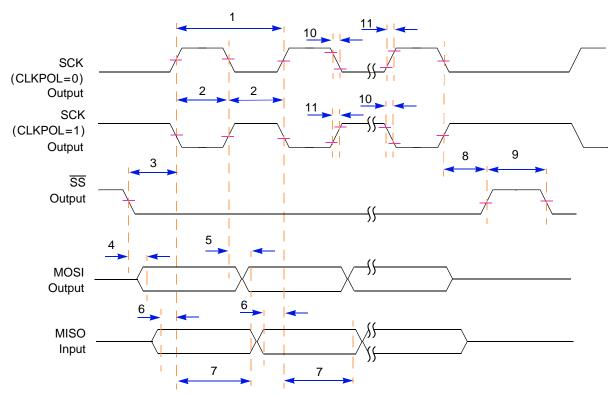

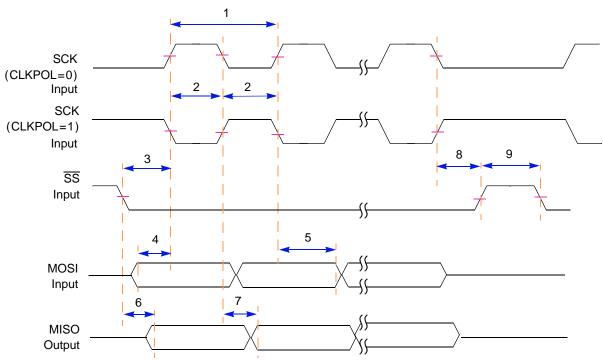

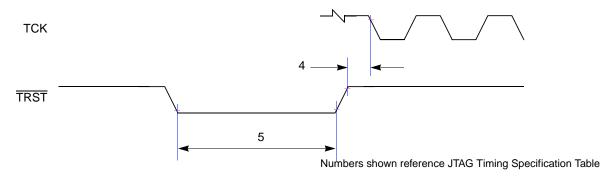

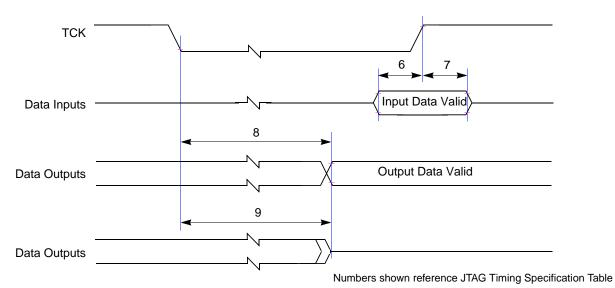

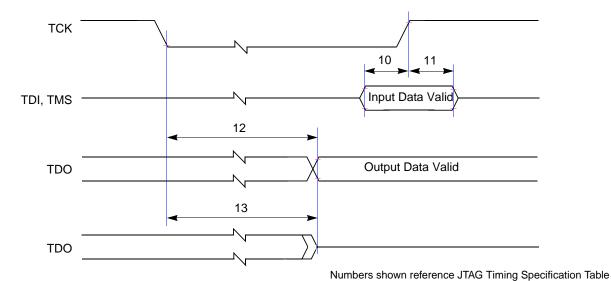

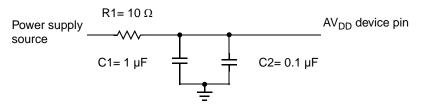

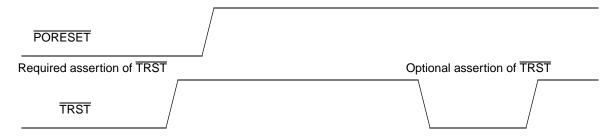

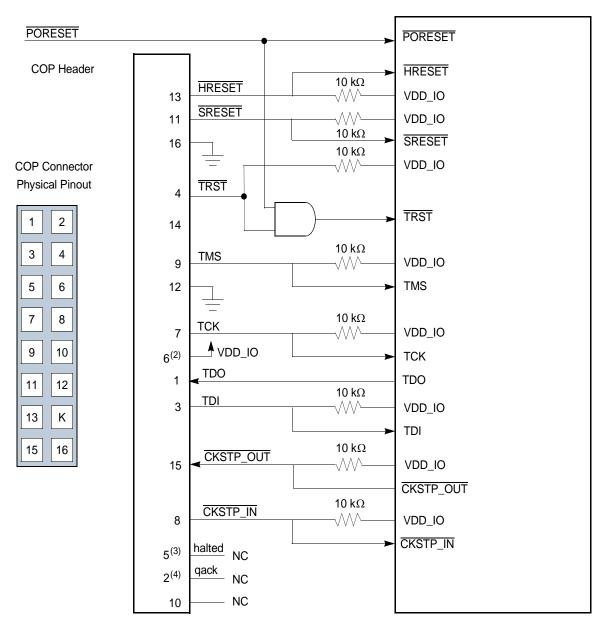

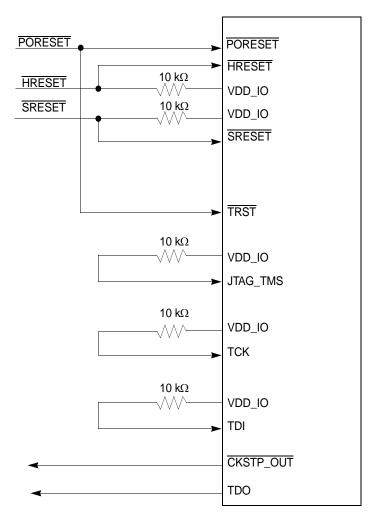

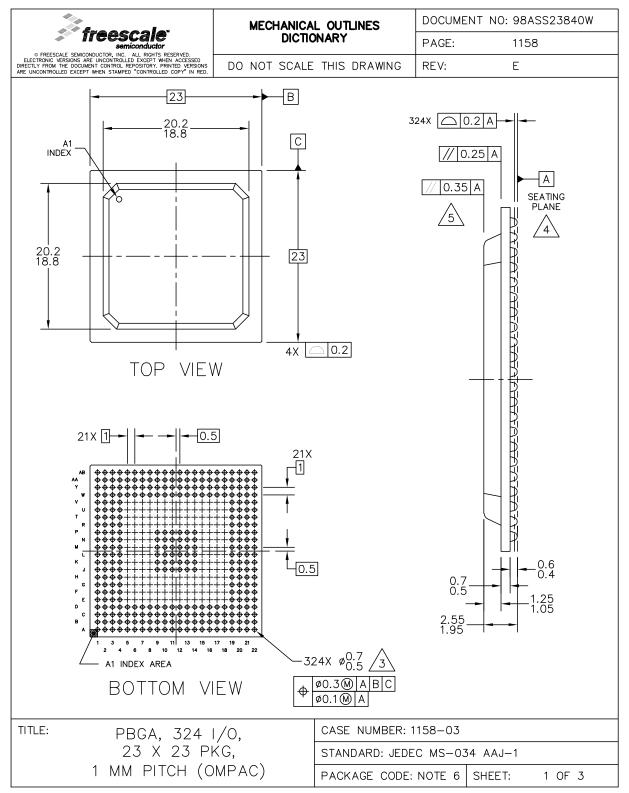

| Peripheral <sup>5</sup>                                                | DRAM<br><br>                                                                                                                  | DRAM<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DRAM<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DRAM<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DRAM<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DRAM — — — — — — — — — — — — — — — — — — — |