# 1 Block diagram

ANALOG BLOCK

VREF

VMPP-REF

OVERCURRENT

OVERTEMPERATURE

CONTROL

REVERSE POLARITY

DAC CODE

DAC CODE

NPP-SET

NPP-SET

NOTE

NPP-SET

VOUT

VOUT

VOUT

VMPP-REF

VMPP-REF

VMPP-REF

VMPP-REF

VMPP-SET

NOTE

NPP-SET

VOUT

VMPP-REF

VMPP-SET

VOUT

VMPP-REF

VMPP-SET

VOUT

VMPP-REF

VMPP-SET

VOUT

VMPP-SET

VOUT

VMPP-SET

VOUT

VMPP-SET

VOUT

VMPP-SET

VOUT

VMPP-SET

VOUT

VOUT

VMPP-SET

VOUT

VMPP-SET

VOUT

VOUT

VMPP-REF

VMPP-SET

VOUT

VOUT

VOUT

VOUT

VOUT

VMPP-REF

VMPP-SET

VOUT

VOUT

VOUT

VOUT

VOUT

VMPP-REF

VMPP-SET

VOUT

VOUT

VOUT

VMPP-SET

VOUT

VOUT

VOUT

VOUT

VOUT

VOUT

VMPP-SET

VOUT

VOUT

VOUT

VMPP-SET

VMPP-SET

VMPP-SET

VOUT

VMPP-SET

VOUT

VMPP-SET

VVCTRL

VMPP-SET

VMPP-S

Figure 1. Block diagram

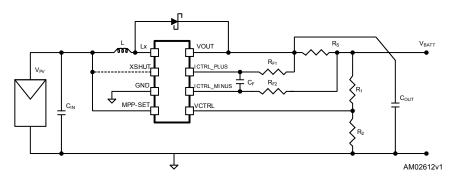

Figure 2. Simplified application circuit

VREF

In order to set up the application and simulate the related test results please go to www.st.com.

DS6991 - Rev 9 page 2/16

page 3/16

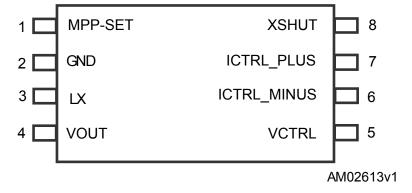

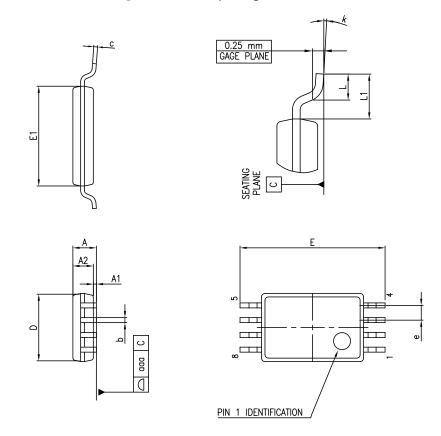

# Pin description

**Table 1. Pin description**

| Pin | Name        | Туре   | Description                                                                                                |

|-----|-------------|--------|------------------------------------------------------------------------------------------------------------|

| 1   | MPP-SET     | I      | Non-inverting input to sense the PV cell voltage. It cannot be left floating.                              |

| 2   | GND         | Ground | Power ground reference.                                                                                    |

| 3   | LX          | I      | Booster inductor connection.                                                                               |

| 4   | VOUT        | 0      | Booster output voltage.                                                                                    |

| 5   | VCTRL       | I      | Inverting input of constant Voltage control loop. It cannot be left floating.                              |

| 6   | ICTRL_MINUS | I      | Inverting input of constant current control loop.  Connect to GND if not used: cannot be left floating.    |

| 7   | ICTRL_PLUS  | 1      | Non-inverting input of constant current control loop. Connect to GND if not used: cannot be left floating. |

| 8   | XSHUT       | I      | Shutdown input pin: XSHUT = low, the device in power off mode.  XSHUT = high, the device is                |

|     |             |        | enabled for operating mode. This pin cannot be left floating.                                              |

Figure 3. Pin connection top view

DS6991 - Rev 9

page 4/16

# 3 Electrical ratings

Table 2. Absolute maximum ratings

| Symbol                    | Parameter                                         | Value        | Unit |

|---------------------------|---------------------------------------------------|--------------|------|

| VOUT                      | VOUT pin voltage range                            | [-0.3, 5.5]  |      |

| LX                        | LX pin voltage range                              | [-5.5, VOUT] |      |

| VOUT-V <sub>LX</sub>      | Maximum voltage drop between VOUT and LX pins     | [5.5]        |      |

| MPP-SET                   | Analog input                                      | [-5.5, VOUT] |      |

| VOUT-V <sub>MPP-SET</sub> | Maximum voltage drop between VOUT and MPPT pins   | [5.5]        |      |

| XSHUT                     | Analog input                                      | [-5.5, VOUT] | V    |

| VOUT-V <sub>XSHUT</sub>   | Maximum voltage drop between VOUT and X-SHUT pins | [5.5]        |      |

| ICTRL_PLUS                | Analog input                                      | [-0.3, VOUT] |      |

| ICTRL_MINUS               | Analog input                                      | [-0.3, VOUT] |      |

| VCTRL                     | Analog input                                      | [-0.3, VOUT] |      |

| GND                       | Ground                                            | 0            |      |

Table 3. Thermal data

| Symbol               | Parameter                               | Value      | Unit |

|----------------------|-----------------------------------------|------------|------|

| R <sub>thj-amb</sub> | Thermal resistance, junction-to-ambient | 135        | °C/W |

| T <sub>jop</sub>     | Junction operating temperature          | -40 to 125 | °C   |

| T <sub>stg</sub>     | Storage temperature                     | -40 to 150 | °C   |

Note:  $R_{thJA}$  has been measured on a 2-layer PCB: FR4, 35  $\mu$ m Cu thickness, 2.8 cm<sup>2</sup>

DS6991 - Rev 9

Downloaded from Arrow.com.

### 4 Electrical characteristics

VMPP-SET = 0.5 V,  $V_{CTRL}$  =  $I_{ctrl+}$  =  $I_{ctrl-}$  = GND, XSHUT = 0.5 V,  $T_{J}$  = -40 °C to 125 °C, unless otherwise specified.

**Table 4. Electrical characteristics**

| Symbol                 | Parameter                                                                         | Test<br>conditions                                                                | Min. | Тур. | Max.               | Unit |

|------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------|------|--------------------|------|

| Input source s         | section                                                                           |                                                                                   |      |      |                    |      |

| V <sub>MPP-SET</sub>   | Low boost voltage threshold                                                       | V <sub>OUT</sub> = 3.3 V                                                          | 0.4  | 0.45 | 0.50               | V    |

| Iq                     | Quiescent<br>current                                                              | I <sub>LOAD</sub> = 0 mA,<br>V <sub>CTRL</sub> = 2 V,<br>V <sub>OUT</sub> = 3.3 V |      | 60   | 80                 |      |

| I <sub>SD</sub>        | Shutdown<br>current                                                               | $V_{OUT}$ = 3.3 V,<br>$V_{CTRL}$ = 2 V,<br>$I_{LOAD}$ = 0 mA,<br>XSHUT = GND      |      | 0.7  | 5                  | μΑ   |

| I <sub>rev</sub>       | Reverse input source current                                                      | V <sub>MPP-SET</sub> = -4<br>V, V <sub>OUT</sub> = 1.5 V                          |      | 1    | 5                  |      |

| V                      | Undervoltage<br>lockout<br>threshold for<br>turn ON @V <sub>OUT</sub><br>= 3.3 V  | V <sub>MPP-SET</sub> increasing                                                   |      | 0.27 | 0.34               | V    |

| Vuvlo                  | Undervoltage<br>lockout<br>threshold for<br>turn OFF<br>@V <sub>OUT</sub> = 3.3 V | V <sub>MPP-SET</sub> decreasing                                                   | 0.14 | 0.24 |                    | V    |

| Power section          | 1                                                                                 |                                                                                   |      |      |                    |      |

| R <sub>DS(on)</sub> -N | N-channel<br>power switch<br>ON resistance                                        |                                                                                   |      |      | 120                |      |

| R <sub>DS(on)</sub> -P | P-channel<br>synchronous<br>rectifier ON<br>resistance                            | V <sub>CTRL</sub> = 2 V                                                           |      |      | 140                | mΩ   |

| Control section        | on                                                                                |                                                                                   |      |      |                    |      |

| V <sub>MPPT-THR</sub>  | MPPT-mode threshold                                                               | V <sub>OUT</sub> increasing, V <sub>MPP-SET</sub> = 1.5 V                         | 1.7  | 1.8  | 2                  | V    |

| V <sub>OUT</sub>       | Output voltage range                                                              | V <sub>MPP-SET</sub> ≥ 1.5<br>V                                                   | 2    |      | 5.2 <sup>(1)</sup> | V    |

| P <sub>OUT</sub> (2)   | Maximum output power                                                              | V <sub>MPP-SET</sub> ≥ 1.5<br>V                                                   |      |      | 3                  | W    |

| I <sub>LX</sub>        | Maximum inductor current peak                                                     |                                                                                   | 1.5  | 1.65 | 1.8                | А    |

DS6991 - Rev 9 page 5/16

| Symbol                | Parameter                                    | Test<br>conditions                                           | Min. | Тур. | Max. | Unit |  |

|-----------------------|----------------------------------------------|--------------------------------------------------------------|------|------|------|------|--|

| F <sub>PWM</sub>      | PWM signal frequency                         |                                                              | 70   | 100  | 130  | kHz  |  |

| V <sub>REF</sub>      | Internal V <sub>CTRL</sub> reference voltage | V <sub>OUT</sub> ≥ 1.8 V,<br>V <sub>CTRL</sub><br>increasing | 1.2  | 1.25 | 1.3  | V    |  |

| V <sub>ICTRL</sub>    | Sensing current offset                       | I <sub>CTRL+</sub> - I <sub>CTRL-</sub><br>decreasing        | 40   | 50   | 60   | mV   |  |

| XSHUT                 | XSHUT logic low                              | XSHUT increasing                                             |      | 0.27 | 0.34 |      |  |

| ASHUT                 | XSHUT logic<br>High                          | XSHUT decreasing                                             | 0.14 | 0.24 |      | V    |  |

| Thermal shutdo        | own                                          |                                                              |      |      |      |      |  |

| _                     | Overtemperatur e threshold for turn OFF      | Temperature increasing                                       |      | 155  |      | 20   |  |

| T <sub>shutdown</sub> | Overtemperatur e threshold for turn ON       | Temperature decreasing                                       |      | 130  |      | °C   |  |

- 1. According to the absolute maximum ratings the output charge voltage cannot be above 4.8 V but if a higher VOUT up to 5.2 V is needed, a Schottky diode must be placed between the L<sub>x</sub> and VOUT pins as shown in Figure 1. In such way the Schottky diode in parallel to the embedded P-channel MOSFET reduces the voltage drop between the VLX pin and the VOUT pin determined by the body diode when the internal PMOS is OFF from 0.7 V down to 0.3 V.

- Given T<sub>j</sub> = T<sub>a</sub> + R<sub>thJA</sub> x P<sub>D</sub>, and assuming R<sub>thJA</sub> = 135 °C/W, and that in order to avoid device destruction T<sub>jmax</sub> must be ≤ 125 °C, and that in the worst conditions T<sub>A</sub> = 85 °C, the power dissipated inside the device is given by: P<sub>D</sub> ≤ T<sub>J</sub>-T<sub>A</sub>/ R<sub>thJA</sub>=295 mW. Therefore, if in the worst case the efficiency is assumed to be 90%, then P<sub>IN-MAX</sub> = 3.3 W and P<sub>OUT-MAX</sub> = 3 W.

DS6991 - Rev 9 page 6/16

# 5 Typical characteristics

**Table 5. Typical Conversion Efficiency**

| V <sub>IN</sub> [V] | P <sub>IN</sub> [W] | P <sub>OUT</sub> /P <sub>IN</sub> [%] |

|---------------------|---------------------|---------------------------------------|

| 1.50                | 0.25 to 2.0         | 80% to 90%                            |

| 2.00                | 0.25 to 2.5         | 80% to 95%                            |

| 2.50                | 0.25 to 3.0         | 80% to 95%                            |

Test conditions (ref to Figure 1):

$10uH \le L \le 100uH (L_{DCR} \le 0.3\Omega);$

RS =  $0\Omega$ ; RF1, RF2 and CF unmounted;

ICTRL+ = ICTRL-= GND

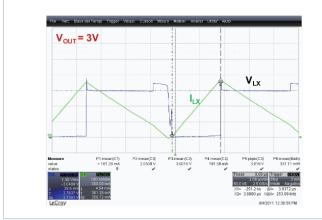

Figure 4.  $V_{LX}$  and  $I_{LX}$  waveforms - D = 39%

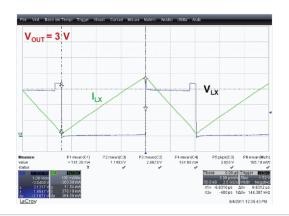

Figure 5.  $V_{LX}$  and  $I_{LX}$  waveforms - D = 68%

### 6 Detailed description

The SPV1040 is a monolithic, high efficiency, low voltage, self-powered DC-DC converter that operates over a 0.3 V to 5.5 V DC input voltage range and provides a single output voltage. The device provides regulated output voltage and current by sensing the VCTRL feedback of the external resistor divider and the voltage drop on the external sense resistor Rs, respectively. High efficiency is ensured by low power consumption in any working mode and by the embedded perturb and observe MPPT algorithm. The SPV1040 guarantees its own safety and application safety by stopping the N-channel power switch in case of overcurrent or overtemperature conditions.

#### 6.1 Soft-start

In order to guarantee the power-up even when VOUT is very low (battery completely discharged), a proper start-up strategy has been implemented. Taking into account that the device is powered by the VOUT voltage, If VOUT is lower than 0.8 V, the device moves from power off to soft-start mode and the current flows from the input to output through the intrinsic body diode of the synchronous rectifier. In this condition VOUT follows the LX voltage. The IC exits start-up mode when VOUT reaches 0.8 V.

#### 6.2 Start-up mode

When VOUT goes above 0.8 V but it is still lower than 2 V, a proper biasing of both MOSFETs is not guaranteed yet. In such conditions, the N-channel power switch is forced ON with a fixed duty cycle and the energy is transferred to the load via the intrinsic body diode of the P-channel synchronous switch. If the shutdown overcurrent limit is exceeded, the power switch is immediately turned OFF. The SPV1040 leaves start-up mode as soon as VOUT goes above 2 V.

#### 6.3 MPPT mode

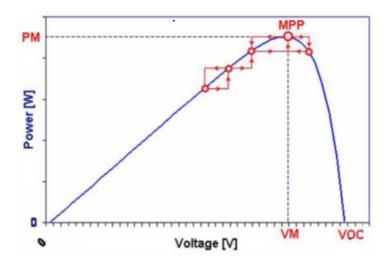

Once the device has exited start-up mode, the SPV1040 enters MPPT mode to search for the maximum power point. The perturb and observe algorithm is based on monitoring either the voltage or the current supplied by the DC power source unit so that the PWM signal duty cycle is increased or decreased step-by-step according to the input power trend. Refer to Figure 6, which illustrates the MPPT working principle.

#### 6.4 Constant voltage regulation

The constant voltage control loop consists of an internal voltage reference, an op-amp and an external resistor divider that senses the battery voltage and fixes the voltage regulation set-point at the value specified by the user.

#### 6.5 Constant current regulation

The constant current control loop consists of an op-amp and an external sense resistor that feeds the current sensing circuit with a voltage proportional to the DC output current. This resistor determines the current regulation set-point and must be adequately rated in terms of power dissipation. It provides the capability to fix the maximum output current to protect the battery.

#### 6.6 Overcurrent protection (OVC)

When the current that flows through the inductor reaches 1.8 A (overcurrent shutdown limit), the N-channel power switch is immediately forced OFF and the P-channel synchronous rectifier is switched ON. Once the overcurrent condition has expired (the inductor current goes below 1.8  $A_{pk}$ ) the N-channel power switch is turned back ON.

#### 6.7 Overtemperature protection

When the temperature sensed at silicon level reaches 155  $^{\circ}$ C (overtemperature shutdown limit), the N-channel power switch is immediately forced OFF and the P-channel synchronous rectifier is switched ON. The device becomes operative again as soon as the silicon temperature goes below 130  $^{\circ}$ C.

DS6991 - Rev 9 page 8/16

#### 6.8 Shutdown mode

The XSHUT pin low shuts OFF all internal circuitry, achieving the lowest power consumption mode.

#### 6.9 Undervoltage lockout

In order to prevent batteries from over-discharging, the device turns OFF in case of MPPSET voltage is lower than 0.24 V (no irradiation). A hysteresis has been implemented to avoid unpredictable ON-OFF switching.

#### 6.10 Reverse polarity

In order to avoid damage to the device and battery discharge when the solar panel connection is reverse-inserted, a dedicated protection circuit has been implemented. In such condition, the SPV1040 stays OFF until the panel is inserted correctly.

Figure 6. MPPT working principle

#### 6.11 Burst mode

When the output voltage reaches the battery charge voltage, the MPP-SET voltage drops below 450 mV, or the output current reaches the output maximum current limit, the duty cycle D drops down to 10% and the device evolves from operating mode to burst mode. The converter no longer works at constant frequency, but at frequencies gradually lower (1  $T_{ON}$  over 1 PWM cycle, 1  $T_{ON}$  over 2 PWM cycles, ...,1  $T_{ON}$  over 16 PWM cycles) prior to entering sleep-in mode.

#### 6.12 Sleep-in mode

Once sleep-in mode has been entered, no current is provided to the load. The device exits this mode once the cause, which forced it into this state, is no longer present.

DS6991 - Rev 9 page 9/16

## 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com.

ECOPACK® is an ST trademark.

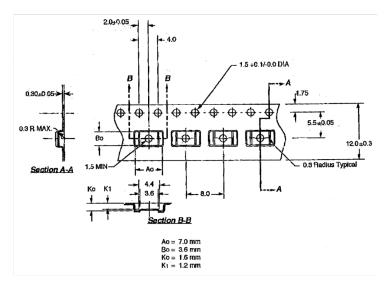

### 7.1 TSSOP8 package information

Figure 7. TSSOP8 package outline

Table 6. TSSOP8 package mechanical data

| Dim.   | mm   |      |      |  |  |

|--------|------|------|------|--|--|

| Dilli. | Min. | Тур. | Max. |  |  |

| Α      |      |      | 1.20 |  |  |

| A1     | 0.05 |      | 0.15 |  |  |

| A2     | 0.80 | 1.00 | 1.05 |  |  |

| b      | 0.19 |      | 0.30 |  |  |

| С      | 0.09 |      | 0.20 |  |  |

| D      | 2.90 | 3.00 | 3.10 |  |  |

| E      | 6.20 | 6.40 | 6.60 |  |  |

| E1     | 4.30 | 4.40 | 4.50 |  |  |

DS6991 - Rev 9 page 10/16

| Dim  | mm   |      |      |  |  |

|------|------|------|------|--|--|

| Dim. | Min. | Тур. | Max. |  |  |

| е    |      | 0.65 |      |  |  |

| L    | 0.45 | 0.60 | 0.75 |  |  |

| L1   |      | 1.00 |      |  |  |

| L2   |      | 0.25 |      |  |  |

| k    | 0    |      | 8    |  |  |

| aaa  |      |      | 0.10 |  |  |

Note:

Dimensions D does not include mold flash or protrusions. Mold flash or protrusions do not exceed 0.15 mm per side.

Dimension E1 does not include interlead flash or protrusions. Interlead flash or protrusions do not exceed 0.25 mm per side.

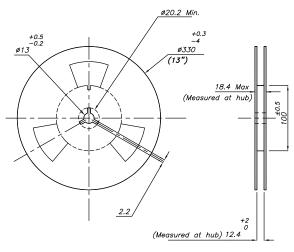

### 7.2 TSSOP8 packing information

Figure 8. TSSOP8 carrier tape outline

Figure 9. TSSOP8 reel outline

page 12/16

## **Revision history**

**Table 7. Document revision history**

| Date        | Revision | Changes                                                                                       |

|-------------|----------|-----------------------------------------------------------------------------------------------|

| 08-Oct-2010 | 1        | First release.                                                                                |

| 06-Apr-2011 | 2        | Updated the cover page, DFN8 information deleted, Chapter 3, Chapter 4 and Chapter 6.         |

| 04-Oct-2011 | 3        | <ul><li>Updated Figure 1, Figure 2, Table 2 and Table 5</li><li>Minor text changes.</li></ul> |

| 25-Jul-2012 | 4        | Updated Figure 4, Figure 5, Figure 6, Figure 7, Figure 8, and Figure 9.                       |

| 21-Mar-2013 | 5        | Updated Figure 1 and note 1 in Table 5.                                                       |

| 26-Sep-2016 | 6        | Added Section 7.2: "Packing information".                                                     |

| 06-Feb-2017 | 7        | Update TSSOP8 package information.                                                            |

| 17-Jan-2020 | 8        | Figures from 4 to 9 replaced by Table 5; minor text changes.                                  |

| 2-Feb-2021  | 9        | Updated Table 1. Pin description and Table 2. Absolute maximum ratings                        |

### **Contents**

| 1     | Bloc   | k diagram                    | 2  |

|-------|--------|------------------------------|----|

| 2     | Pin c  | description                  | 3  |

| 3     | Elect  | trical ratings               | 4  |

| 4     | Elect  | trical characteristics       | 5  |

| 5     | Туріс  | cal characteristics          | 7  |

| 6     | Deta   | iled description             | 8  |

|       | 6.1    | Soft-start                   | 8  |

|       | 6.2    | Start-up mode                | 8  |

|       | 6.3    | MPPT mode                    | 8  |

|       | 6.4    | Constant voltage regulation  | 8  |

|       | 6.5    | Constant current regulation  | 8  |

|       | 6.6    | Overcurrent protection (OVC) | 8  |

|       | 6.7    | Overtemperature protection   | 8  |

|       | 6.8    | Shutdown mode                | 9  |

|       | 6.9    | Undervoltage lockout         | 9  |

|       | 6.10   | Reverse polarity             | 9  |

|       | 6.11   | Burst mode                   | 9  |

|       | 6.12   | Sleep-in mode                | 9  |

| 7     | Pack   | age information              | 10 |

|       | 7.1    | TSSOP8 package information   | 10 |

|       | 7.2    | TSSOP8 packing information   | 11 |

| Rev   | ision  | history                      | 12 |

| Con   | tents  |                              | 13 |

| List  | of tab | oles                         | 14 |

| l ist | of fig | ures                         | 15 |

## **List of tables**

| Table 1. | Pin description                | 3  |

|----------|--------------------------------|----|

| Table 2. | Absolute maximum ratings       | 4  |

| Table 3. | Thermal data                   | 4  |

| Table 4. | Electrical characteristics     | 5  |

| Table 5. | Typical Conversion Efficiency  | 7  |

| Table 6. | TSSOP8 package mechanical data | 10 |

| Table 7. | Document revision history      | 12 |

# **List of figures**

| Figure 1. | Block diagram                                           | 2  |

|-----------|---------------------------------------------------------|----|

| Figure 2. | Simplified application circuit                          |    |

| Figure 3. | Pin connection top view                                 | 3  |

| Figure 4. | V <sub>LX</sub> and I <sub>LX</sub> waveforms - D = 39% | 7  |

| Figure 5. | V <sub>LX</sub> and I <sub>LX</sub> waveforms - D = 68% | 7  |

| Figure 6. | MPPT working principle                                  | ć  |

| Figure 7. | TSSOP8 package outline                                  |    |

| Figure 8. | TSSOP8 carrier tape outline                             | 11 |

| Figure 9. | TSSOP8 reel outline                                     | 11 |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2021 STMicroelectronics - All rights reserved

DS6991 - Rev 9 page 16/16