### **SP510**

### **ULTRA HIGH SPEED MULTIPROTOCOL TRANSCEIVER**

REV. 1.0.1

### **ABSOLUTE MAXIMUM RATINGS**

These are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

| Supply Voltage (Vcc)+ 7.0V                              |

|---------------------------------------------------------|

| $Logic\text{-Interface Voltage }(V_L)V_L \leq Vcc$      |

| Input voltage at TTL input pins 0.3V to $V_L + 0.5 V_L$ |

| Receiver Input voltage±15.5V                            |

| Driver output (from Ground)7.5V to +12.5V               |

| Short Circuit Duration, TxOUT to GND, Continuous        |

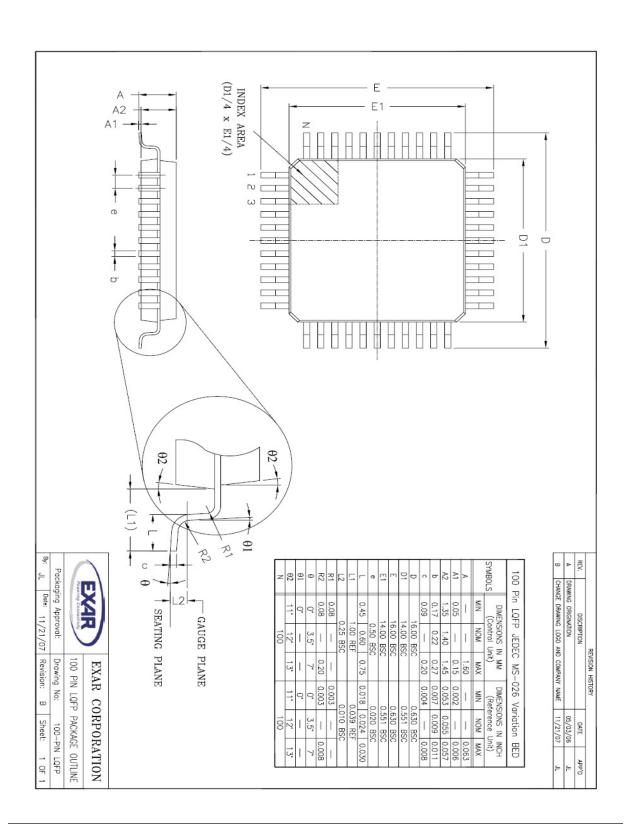

| Continuous Power Dissi  | pation at Ta = +70° C   |

|-------------------------|-------------------------|

| 100-Pin QFP             | 1520 mW                 |

| (derate 19.0 mW / °C ab | ove 70° C)              |

| ⊕JA 5                   | 52.7 °C/W, ⊚JC 6.5 °C/W |

| Storage Temperature     | 65°C to +150°C          |

| Lead Temperature (sold  | ering, 10s) 300° C      |

#### **RECOMMENDED OPERATING CONDITIONS**

| Supply Voltage (Vcc) 4.75V to 5.25V |            |         |                        |    |  |  |  |  |

|-------------------------------------|------------|---------|------------------------|----|--|--|--|--|

| Logic-Interface 5.25V               | Supply     | Voltage | (V <sub>L</sub> )1.65V | to |  |  |  |  |

| Operating Temp                      | oerature F | Range   | 40° C to +85°          | С  |  |  |  |  |

TABLE 1: DC ELECTRICAL CHARACTERISTICS

| PARAMETERS                               | SYMBOL            | TEST CONDITIONS                                      | MIN.                    | TYP   | MAX                  | Unit |

|------------------------------------------|-------------------|------------------------------------------------------|-------------------------|-------|----------------------|------|

| Vcc Supply Voltage                       | V <sub>CC</sub>   |                                                      | 4.75                    |       | 5.25                 | V    |

| Logic Interface Voltage                  | V <sub>L</sub>    | $V_{CC} \ge V_L$                                     | 1.65                    |       | 5.25                 | V    |

| I <sub>CC</sub> Shutdown                 | I <sub>CCSD</sub> |                                                      |                         | 200   |                      | μΑ   |

| I <sub>CC</sub> Supply Current           | I <sub>CC</sub>   |                                                      |                         |       | 300                  | mA   |

|                                          | DRIV              | ER INPUT AND LOGIC INPUT PINS                        | <u>'</u>                |       |                      |      |

| Logic Input High                         | V <sub>IH</sub>   |                                                      | 2.0                     |       |                      | V    |

| Logic Input Low                          | V <sub>IL</sub>   |                                                      |                         |       | 0.4                  | V    |

|                                          |                   | RECEIVER OUTPUTS                                     | <u>'</u>                |       |                      |      |

| Receiver Logic Output Low                | V <sub>OL</sub>   | I <sub>OUT</sub> = -3.2 mA                           |                         |       | 0.4                  | V    |

| Receiver Logic Output High               | V <sub>OH</sub>   | I <sub>OUT</sub> = 1 mA                              | I <sub>OUT</sub> = 1 mA |       | V <sub>L</sub> + 0.3 | V    |

| Receiver Output Short-Circuit<br>Current | I <sub>OSS</sub>  | 0V < V <sub>O</sub> < V <sub>CC</sub>                |                         | ±20   | ±60                  | mA   |

| Receiver Output Leakage Cur-<br>rent     | I <sub>OZ</sub>   | Receivers disabled.<br>0.4V < V <sub>O</sub> < 5.25V |                         | ±0.05 | ±1                   | μΑ   |

|                                          | l                 | V.28 / RS-232 DRIVERS                                |                         |       |                      |      |

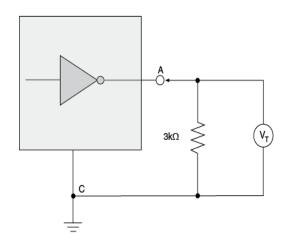

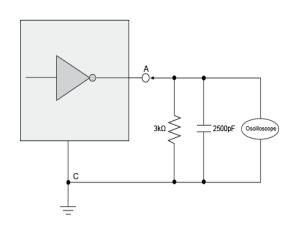

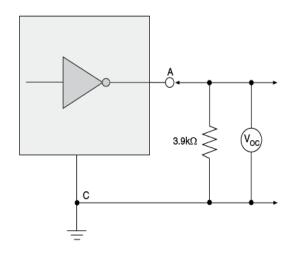

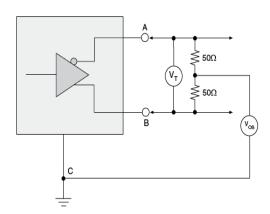

| Output Voltage Swing                     | V <sub>T</sub>    | Output load = $3k\Omega$ to GND Fig. 3               | ±5.0                    | ±6.0  | ±15.0                | V    |

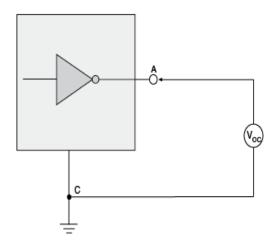

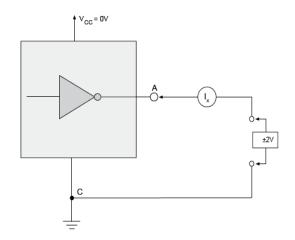

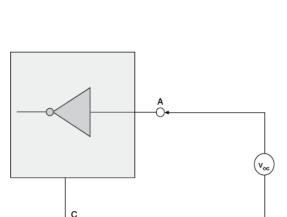

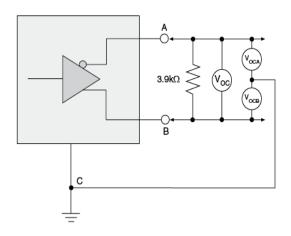

|                                          | V <sub>oc</sub>   | Output load = Open Circuit Fig.2                     |                         |       | ±15.0                | V    |

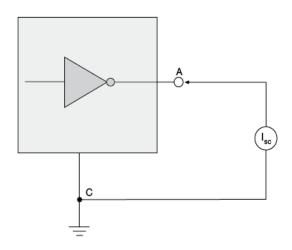

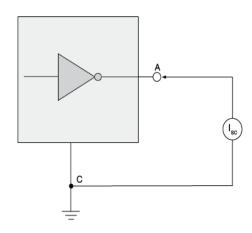

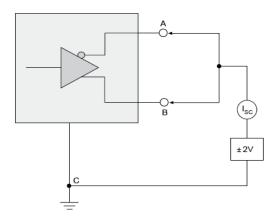

| Short Circuit Current                    | I <sub>SC</sub>   | V <sub>OUT</sub> = 0V, Fig 5                         |                         |       | ±100                 | mA   |

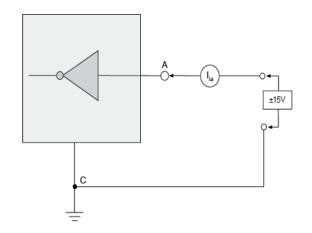

| Power-Off Impedance                      |                   | Fig. 6                                               | 300                     |       |                      | Ω    |

|                                          | '                 | V.28 / RS-232 RECEIVERS                              | <del>- '</del>          |       | <u>'</u>             |      |

| Input Voltage Range                      |                   |                                                      | -15                     |       | 15                   | V    |

| Input Threshold Low                      |                   |                                                      | 0.8                     | 1.2   |                      | V    |

| Input Threshold High                     |                   |                                                      |                         | 1.7   | 3.0                  | V    |

| Input Hysteresis                         |                   |                                                      |                         | 500   |                      | mV   |

| Input Resistance                         |                   | Fig. 8                                               | 3                       | 5     | 7                    | kΩ   |

| Open Circuit Bias                        | V <sub>oc</sub>   | Fig. 9                                               |                         |       | ±2.0                 | V    |

REV. 1.0.1

## DC ELECTRICAL CHARACTERISTICS

| PARAMETERS                     | SYMBOL                                                   | TEST CONDITIONS                                    | Min.                | Түр | Max                 | Unit |

|--------------------------------|----------------------------------------------------------|----------------------------------------------------|---------------------|-----|---------------------|------|

|                                |                                                          | V.10 / RS-423 DRIVERS                              |                     |     |                     |      |

| Open Circuit Voltage           | V <sub>OC</sub>                                          | Fig.10                                             | ±4.0                |     | ±6.0                | V    |

| Test Terminated Voltage        | V <sub>T</sub>                                           | Fig. 11                                            | 0.9 V <sub>OC</sub> |     |                     | V    |

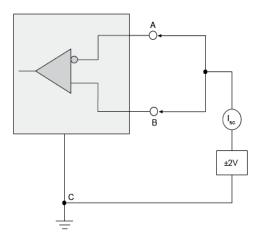

| Short Circuit Current          | I <sub>SC</sub>                                          | Fig. 12                                            |                     |     | ±150                | mA   |

| Power-Off Current              |                                                          | Fig. 13                                            |                     |     | ±100                | μΑ   |

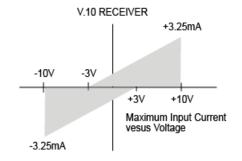

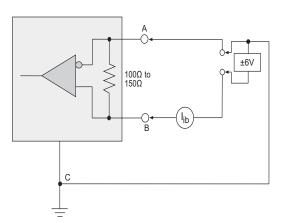

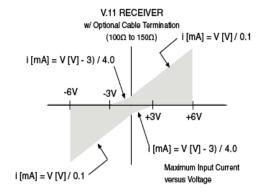

|                                | ,                                                        | V.10 / RS-423 RECEIVERS                            | l l                 |     | <u> </u>            |      |

| Input Current                  | I <sub>IA</sub>                                          | Fig. 15 and 16                                     | -3.25               |     | +3.25               | mA   |

| Input Impedance                |                                                          |                                                    | 4                   | 15  |                     | kΩ   |

| Sensitivity                    |                                                          |                                                    |                     |     | ±0.2                | V    |

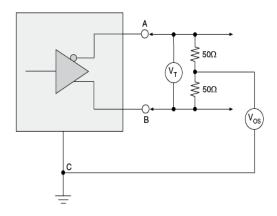

|                                |                                                          | V.11 / RS-422 DRIVERS                              |                     |     |                     |      |

| Open Circuit Voltage           | V <sub>OC</sub> , V <sub>OCA</sub> ,<br>V <sub>OCB</sub> | Fig. 17                                            |                     |     | ±6.0                | V    |

| Test Terminated Voltage        | V <sub>T</sub>                                           | Fig. 18                                            | ±2.0                |     |                     | V    |

| Balance                        | $\Delta V_{T}$                                           | Fig. 18                                            |                     |     | ±0.4                | V    |

| Driver DC Offset               | V <sub>OS</sub>                                          | Fig. 18                                            |                     |     | +3.0                | V    |

| Offset Balance                 | ΔV <sub>OS</sub>                                         | Fig. 18                                            |                     |     | ±0.4                | V    |

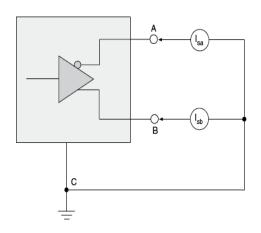

| Short Circuit Output Current   | I <sub>SA,</sub> I <sub>SB</sub>                         | Fig. 19                                            |                     |     | ±150                | mA   |

| Power-Off Current              |                                                          | Fig. 20                                            |                     |     | ±100                | μΑ   |

|                                | ,                                                        | V.11 / RS-422 RECEIVERS                            |                     |     |                     |      |

| Receiver Input Range           | V <sub>CM</sub>                                          |                                                    | -7                  |     | +7                  | V    |

| Input Current                  | $I_{IA,}I_{IB}$                                          | Fig. 21 and 23                                     |                     |     | ±3.25               | mV   |

| Input Current with Termination | I <sub>IA,</sub> I <sub>IB</sub>                         | Fig. 24 and 25                                     |                     |     | ±60.75              | mA   |

| Receiver Input Impedance       | R <sub>IN</sub>                                          | -10V ≤ V <sub>CM</sub> ≤ +10V                      | 4                   | 15  |                     | kΩ   |

| Receiver Sensitivity           | V <sub>TH</sub>                                          |                                                    |                     |     | ±200                | mV   |

| Receiver Input Hysteresis      | $\Delta V_{TH}$                                          | V <sub>CM</sub> = 0 V                              |                     | 15  |                     | mV   |

| V.3                            | 5 DRIVERS (AL                                            | L VALUES MEASURE WITH TERM                         | _OFF = '0')         |     | <u>'</u>            |      |

| Test Terminated Voltage        | V <sub>T</sub>                                           | Fig. 26                                            | ±0.44               |     | ±0.66               | V    |

| Offset                         | V <sub>OS</sub>                                          | Fig. 26                                            |                     |     | ±0.6                | V    |

| Output Overshoot               |                                                          | Fig. 26, V <sub>ST</sub> = Steady State<br>Voltage | -0.2V <sub>ST</sub> |     | +0.2V <sub>ST</sub> | V    |

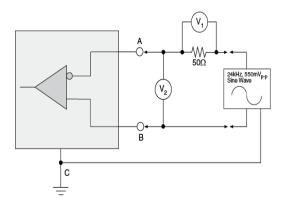

| Source Impedance               |                                                          | Fig. 29, $Z_S = V_2 / V_1 \times 50\Omega$         | 50                  |     | 150                 | Ω    |

| PARAMETERS                      | SYMBOL       | TEST CONDITIONS                            | MIN.      | Түр  | MAX  | Unit |

|---------------------------------|--------------|--------------------------------------------|-----------|------|------|------|

| Short Circuit Impedance         |              | Fig. 28                                    | 135       |      | 165  | Ω    |

| V.35 I                          | RECEIVERS (A | LL VALUES MEASURE WITH TERM                | _OFF = '0 | ')   |      |      |

| Sensitivity                     |              |                                            |           | ±100 | ±200 | mV   |

| Source Impedance                |              | Fig. 30, $Z_S = V_2 / V_1 \times 50\Omega$ | 90        |      | 110  | Ω    |

| Short-Circuit Impedance         |              | Fig. 31                                    | 135       |      | 165  | Ω    |

|                                 | Tra          | NSCEIVER LEAKAGE CURRENT                   |           |      |      |      |

| Driver Output 3-state Current   |              | Drivers disabled, per Fig. 32              |           | 500  |      | μΑ   |

| Receiver Output 3-state Current |              | Tx and Rx Disabled,<br>0.4V - Vo - 2.4V    |           | 1    | 10   | μΑ   |

### TABLE 2: AC TIMING CHARACTERISTICS

# TIMING CHARACTERISTICS

$V_{CC}$  = +4.75 to 5.25V, C1-C4 = 1µF;  $T_{AMB}$  =  $T_{MIN}$  to  $T_{MAX}$ , unless noted. Typical values are at  $T_{AMB}$  = +25°C.

| PARAMETERS                                               | SYMBOL                                   | TEST CONDITIONS                                        | MIN. | ТҮР | Max | Unit |

|----------------------------------------------------------|------------------------------------------|--------------------------------------------------------|------|-----|-----|------|

|                                                          |                                          | V.28 / RS-232                                          |      |     |     |      |

| Maximum Transmission Rate                                |                                          | Fig. 7                                                 | 250  |     |     | kbps |

| Driver Propagation Delay                                 | t <sub>DPHL</sub> ,<br>t <sub>DPLH</sub> |                                                        | 0.5  | 1   | 5   | μs   |

| Transition Time                                          |                                          | +3V to -3V, -3V to +3V per<br>Fig. 7                   | 0.2  |     | 1.5 | μs   |

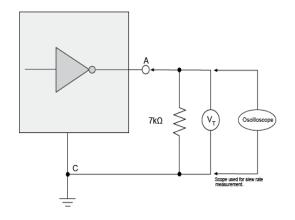

| Instantaneous Slew Rate                                  |                                          | +3V to -3V, -3V to +3V per<br>Fig. 4                   | 4    |     | 30  | V/µs |

| Driver Skew                                              |                                          | t <sub>DPHL</sub> - t <sub>DPLH</sub> at zero crossing |      | 100 | 800 | ns   |

| Driver Channel to Channel Skew                           |                                          |                                                        |      | 20  |     | ns   |

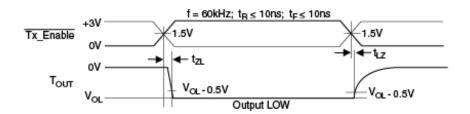

| Driver Output Enable Time<br>Tri-state to output Low     | t <sub>ZL</sub>                          | C <sub>L</sub> = 100 pF, Fig. 34 and 40,<br>S1 closed  |      |     | 2.0 | μs   |

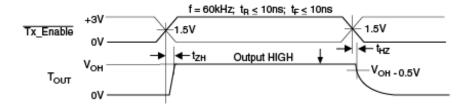

| Driver Output Enable Time<br>Tri-state to output High    | t <sub>ZH</sub>                          | C <sub>L</sub> = 100 pF, Fig. 34 and 40,<br>S2 closed  |      |     | 2.0 | μs   |

| Driver Output Disable Time<br>Output Low to Tri-state    | t <sub>LZ</sub>                          | C <sub>L</sub> = 15 pF, Fig. 34 and 40,<br>S1 closed   |      |     | 2.0 | μs   |

| Driver Output Disable Time<br>Output High to Tri-state   | t <sub>HZ</sub>                          | C <sub>L</sub> = 15 pF, Fig. 34 and 40,<br>S2 closed   |      |     | 20  | μs   |

| Receiver Propagation Delay                               | t <sub>PHL</sub> , t <sub>PLH</sub>      | R_IN to R_OUT, $C_L = 15 pF$                           | 50   | 100 | 500 | ns   |

| Receiver Skew                                            |                                          | t <sub>PHL</sub> - t <sub>PLH</sub> at 1.5V            |      | 50  |     | ns   |

| Receiver Output Rise / Fall Time                         | t <sub>R</sub> , t <sub>F</sub>          | C <sub>L</sub> = 15 pF                                 |      | 15  |     | ns   |

| Receiver Output Enable Time<br>Tri-state to output Low   | t <sub>ZL</sub>                          | C <sub>L</sub> = 100 pF, Fig. 35 and 40,<br>S1 closed  |      |     | 2.0 | μs   |

| Receiver Output Enable Time<br>Tri-state to output High  | t <sub>ZH</sub>                          | C <sub>L</sub> = 100 pF, Fig. 35 and 40,<br>S2 closed  |      |     | 2.0 | μs   |

| Receiver Output Disable Time<br>Output Low to Tri-state  | t <sub>LZ</sub>                          | C <sub>L</sub> = 15 pF, Fig. 35 and 40,<br>S1 closed   |      |     | 2.0 | μs   |

| Receiver Output Disable Time<br>Output High to Tri-state | t <sub>HZ</sub>                          | C <sub>L</sub> = 15 pF, Fig. 35 and 40,<br>S2 closed   |      |     | 2.0 | μs   |

| Charge Pump Rise Time                                    |                                          | Shutdown to normal operation                           |      |     | 2   | ms   |

|                                                          |                                          | V.10 / RS-423                                          |      |     |     |      |

| Maximum Transmission Rate                                |                                          |                                                        | 250  |     |     | kbps |

REV. 1.0.1

# TIMING CHARACTERISTICS

$V_{CC}$  = +4.75 to 5.25V, C1-C4 = 1 $\mu$ F;  $T_{AMB}$  =  $T_{MIN}$  to  $T_{MAX}$ , unless noted. Typical values are at  $T_{AMB}$  = +25°C.

| PARAMETERS                                               | SYMBOL                                   | TEST CONDITIONS                                          | MIN.     | Түр             | Max | Unit |

|----------------------------------------------------------|------------------------------------------|----------------------------------------------------------|----------|-----------------|-----|------|

| Driver Propagation Delay                                 | t <sub>PHL</sub> , t <sub>PLH</sub>      |                                                          | 30       | 150             | 500 | ns   |

| Driver Rise / Fall Time                                  | t <sub>R</sub> , t <sub>F</sub>          | 10% to 90% - Fig. 14                                     |          |                 | 500 | ns   |

| Driver Skew                                              |                                          | t <sub>DPHL</sub> - t <sub>DPLH</sub>   at zero crossing |          |                 | 100 | ns   |

| Driver Output Enable Time<br>Tri-state to Output Low     | t <sub>ZL</sub>                          | C <sub>L</sub> = 100 pF, Fig. 34 and 40,<br>S1 closed    |          |                 | 2   | μs   |

| Driver Output Enable Time<br>Tri-state to Output High    | t <sub>ZH</sub>                          | C <sub>L</sub> = 100 pF, Fig. 34 and 40,<br>S2 closed    |          |                 | 2   | μs   |

| Driver Output Disable Time<br>Output Low to Tri-state    | t <sub>LZ</sub>                          | C <sub>L</sub> = 15 pF, Fig. 34 and 40,<br>S1 closed     |          |                 | 2   | μs   |

| Driver Output Disable Time<br>Output High to Tri-state   | t <sub>HZ</sub>                          | C <sub>L</sub> = 15 pF, Fig. 34 and 40,<br>S2 closed     |          |                 | 2   | μs   |

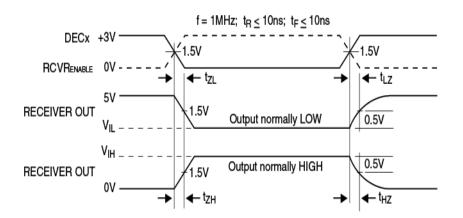

| Receiver Propagation Delay                               | t <sub>PHL</sub> , t <sub>PLH</sub>      |                                                          |          | 100             | 500 | ns   |

| Receiver Output Enable Time<br>Tri-state to output Low   | t <sub>ZL</sub>                          | C <sub>L</sub> = 100 pF, Fig. 35 and 40,<br>S1 closed    |          |                 | 2   | μs   |

| Receiver Output Enable Time<br>Tri-state to output High  | t <sub>ZH</sub>                          | C <sub>L</sub> = 100 pF, Fig. 35 and 40,<br>S2 closed    |          |                 | 2   | μs   |

| Receiver Output Disable Time<br>Output Low to Tri-state  | t <sub>LZ</sub>                          | C <sub>L</sub> = 15 pF, Fig. 35 and 40,<br>S1 closed     |          |                 | 2   | μs   |

| Receiver Output Disable Time<br>Output High to Tri-state | t <sub>HZ</sub>                          | C <sub>L</sub> = 15 pF, Fig. 35 and 40,<br>S1 closed     |          |                 |     |      |

| Receiver Output Rise / Fall Time                         | t <sub>R</sub> , t <sub>F</sub>          | C <sub>L</sub> = 15 pF                                   |          | 15              |     | ns   |

| Receiver Skew                                            |                                          | t <sub>PHL</sub> - t <sub>PLH</sub>   at 1.5V            |          | 5               |     | ns   |

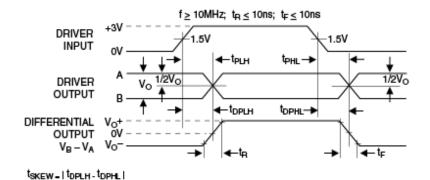

| High S                                                   | PEED V.11 / R                            | S-422 (DRIVERS 1, 2 & 3, RECEIV                          | ERS 1, 2 | <b>&amp;</b> 3) |     | l    |

| Maximum Bit Rate                                         |                                          | NRZI Encoding                                            | 52       |                 |     | Mbps |

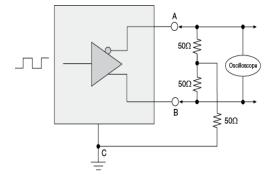

| Driver Rise and Fall Time                                | t <sub>R</sub> , t <sub>F</sub>          | Fig. 22 and 36, 10-90%                                   | 0.5      |                 | 6   | ns   |

| Propagation Delay Time                                   | t <sub>DPHL</sub> ,<br>t <sub>DPLH</sub> | Fig. 33 and 36, C <sub>L</sub> = 50 pF                   |          | 5               | 25  | ns   |

| Differential Skew                                        |                                          | t <sub>DPHL</sub> - t <sub>DPLH</sub>                    |          |                 | 3.8 | ns   |

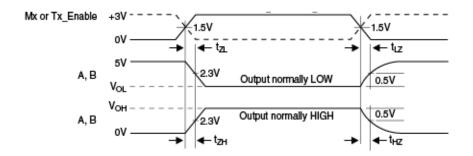

| Driver Output Enable Time<br>Tri-state to Output Low     | t <sub>ZL</sub>                          | C <sub>L</sub> = 100 pF, Fig. 34 and 37,<br>S1 closed    |          |                 | 100 | ns   |

| Driver Output Enable Time<br>Tri-state to Output High    | t <sub>ZH</sub>                          | C <sub>L</sub> = 100 pF, Fig. 34 and 37,<br>S2 closed    |          |                 | 100 | ns   |

| Driver Output Disable Time<br>Output Low to Tri-state    | t <sub>LZ</sub>                          | C <sub>L</sub> = 15 pF, Fig. 34 and 37,<br>S1 closed     |          |                 | 100 | ns   |

REV. 1.0.1

# TIMING CHARACTERISTICS

| $V_{CC}$ = +4.75 to 5.25V, C1-C4 = 1 $\mu$ l             | ı                                        | 1                                                                                                                                               | values ar  | 1         |     | I    |

|----------------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|-----|------|

| PARAMETERS                                               | SYMBOL                                   | TEST CONDITIONS                                                                                                                                 | Min.       | ТҮР       | MAX | Unit |

| Driver Output Disable Time<br>Output High to Tri-state   | t <sub>HZ</sub>                          | C <sub>L</sub> = 15 pF, Fig. 34 and 37,<br>S2 closed                                                                                            |            |           | 100 | ns   |

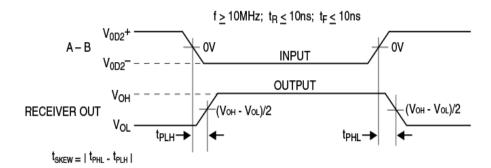

| Receiver Propagation Delay                               | t <sub>PHL</sub> , t <sub>PLH</sub>      | Fig. 33, 36<br>C <sub>L</sub> = 50 pF                                                                                                           |            | 20        | 50  | ns   |

| Receiver Skew                                            |                                          | t <sub>PHL</sub> - t <sub>PLH</sub>   Fig. 33, 36<br>C <sub>L</sub> = 50 pF                                                                     |            |           | 3.8 | ns   |

| Receiver Output Enable Time<br>Tri-state to Output Low   | t <sub>ZL</sub>                          | C <sub>L</sub> = 100 pF, Fig. 35 and 39,<br>S1 closed                                                                                           |            |           | 100 | ns   |

| Receiver Output Enable Time Tri-state to Output High     | t <sub>ZH</sub>                          | C <sub>L</sub> = 100 pF, Fig. 35 and 39,<br>S2 closed                                                                                           |            |           | 100 | ns   |

| Receiver Output Disable Time<br>Output Low to Tri-state  | t <sub>LZ</sub>                          | C <sub>L</sub> = 15 pF, Fig. 35 and 39,<br>S1 closed                                                                                            |            |           | 100 | ns   |

| Receiver Output Disable Time<br>Output High to Tri-state | t <sub>HZ</sub>                          | C <sub>L</sub> = 15 pF, Fig. 35 and 39,<br>S2 closed                                                                                            |            |           | 100 | ns   |

| Receiver Output Rise / Fall Time                         | t <sub>R</sub> , t <sub>F</sub>          | $3.0 \text{ V} < \text{V}_{\text{L}} < 5.5 \text{V}$<br>$1.65 \text{ V} < \text{V}_{\text{L}} < 3.0 \text{V}$<br>$C_{\text{L}} = 50 \text{ pF}$ | 0.5        |           | 6   | ns   |

| Channel to channel Skew                                  |                                          |                                                                                                                                                 |            | 2         |     | ns   |

| V.11 / RS-4                                              | 22 Handshak                              | E SIGNALS (DRIVERS 4, 5 & 6, RI                                                                                                                 | ECEIVERS 4 | 4, 5 & 6) |     | l    |

| Maximum Transmission Rate                                |                                          | Fig. 33                                                                                                                                         | 10         |           |     | Mbps |

| Driver Rise and Fall Time                                | t <sub>R</sub> , t <sub>F</sub>          | Fig. 22 and 36                                                                                                                                  |            | 2         | 10  | ns   |

| Propagation Delay Time                                   | t <sub>DPHL</sub> ,<br>t <sub>DPLH</sub> | Fig. 33 and 36, C <sub>L</sub> = 50 pF                                                                                                          |            | 20        | 50  | ns   |

| Driver Propagation Delay Skew                            |                                          | t <sub>DPHL</sub> - t <sub>DPLH</sub>                                                                                                           |            |           | 10  | ns   |

| Driver Channel to Channel Skew                           |                                          |                                                                                                                                                 |            | 2         |     | ns   |

| Driver Output Enable Time Tri-state to Output Low        | t <sub>ZL</sub>                          | C <sub>L</sub> = 100 pF, Fig. 34 and 37,<br>S1 closed                                                                                           |            |           | 100 | ns   |

| Driver Output Enable Time<br>Tri-state to Output High    | t <sub>ZH</sub>                          | C <sub>L</sub> = 100 pF, Fig. 34 and 37,<br>S2 closed                                                                                           |            |           | 100 | ns   |

| Driver Output Disable Time<br>Output Low to Tri-state    | t <sub>LZ</sub>                          | C <sub>L</sub> = 15 pF, Fig. 34 and 37,<br>S1 closed                                                                                            |            |           | 100 | ns   |

| Driver Output Disable Time<br>Output High to Tri-state   | t <sub>HZ</sub>                          | C <sub>L</sub> = 15 pF, Fig. 34 and 37,<br>S2 closed                                                                                            |            |           | 100 | ns   |

| Receiver Propagation Delay                               | t <sub>PHL</sub> , t <sub>PLH</sub>      | Fig. 33, 36<br>C <sub>L</sub> = 50 pF                                                                                                           |            | 20        | 50  | ns   |

### TIMING CHARACTERISTICS

$V_{CC}$  = +4.75 to 5.25V, C1-C4 = 1µF;  $T_{AMB}$  =  $T_{MIN}$  to  $T_{MAX}$ , unless noted. Typical values are at  $T_{AMB}$  = +25°C.

| PARAMETERS                                              | ERS SYMBOL TEST CONDITIONS               |                                                                                | MIN. | ТҮР      | Max      | Unit |

|---------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------|------|----------|----------|------|

| Receiver Skew                                           |                                          | t <sub>PHL</sub> - t <sub>PLH</sub>   Fig. 33, 36<br>C <sub>L</sub> = 50 pF    |      |          | 10       | ns   |

| Receiver Output Enable Time<br>Tri-state to Output Low  | t <sub>ZL</sub>                          | C <sub>L</sub> = 100 pF, Fig. 35 and 39,<br>S1 closed                          |      |          | 100      | ns   |

| Receiver Output Enable Time<br>Tri-state to Output High | t <sub>ZH</sub>                          | C <sub>L</sub> = 100 pF, Fig. 35 and 39,<br>S2 closed                          |      |          | 100      | ns   |

| Receiver Output Disable Time<br>Output Low to Tri-state | $t_{LZ}$                                 | C <sub>L</sub> = 15 pF, Fig. 35 and 39,<br>S1 closed                           |      |          | 100      | ns   |

| Receiver Output Disable Time<br>Output Low to Tri-state | t <sub>HZ</sub>                          | C <sub>L</sub> = 15 pF, Fig. 35 and 39,<br>S2 closed                           |      |          | 100      | ns   |

| Receiver Output Rise / Fall Time                        | t <sub>R</sub> , t <sub>F</sub>          |                                                                                | 1    |          | 20       | ns   |

| Channel to Channel Skew                                 |                                          |                                                                                |      | 2        |          | ns   |

|                                                         | V.35 (DRI                                | L<br>VERS 1, 2 & 3, RECEIVERS 1, 2 &                                           | 3)   | <u> </u> | <u> </u> |      |

| Maximum Transmission Rate                               |                                          | Fig. 33, f <sub>MAX</sub> = 20 MHz                                             | 40   |          |          | Mbps |

| Driver Rise and Fall Time                               | t <sub>R</sub> , t <sub>F</sub>          | Fig. 29                                                                        |      |          | 10       | ns   |

| Propagation Delay Time                                  | t <sub>DPHL</sub> ,<br>t <sub>DPLH</sub> | Fig. 33 and 36, C <sub>L</sub> = 50 pF                                         |      | 20       | 50       | ns   |

| Driver Differential Skew                                |                                          | t <sub>DPHL</sub> - t <sub>DPLH</sub>   Fig. 33 and 36                         |      |          | 5.0      | ns   |

| Driver Channel to Channel Skew                          |                                          |                                                                                |      | 2        |          | ns   |

| Driver Output Enable Time<br>Tri-state to Output Low    | t <sub>ZL</sub>                          | C <sub>L</sub> = 100 pF, Fig. 34 and 37,<br>S1 closed                          |      |          | 200      | ns   |

| Driver Output Enable Time<br>Tri-state to Output High   | t <sub>ZH</sub>                          | C <sub>L</sub> = 100 pF, Fig. 34 and 37,<br>S2 closed                          |      |          | 200      | ns   |

| Driver Output Disable Time<br>Output Low to Tri-state   | t <sub>LZ</sub>                          | C <sub>L</sub> = 15 pF, Fig. 34 and 37,<br>S1 closed                           |      |          | 200      | ns   |

| Driver Output Disable Time<br>Output High to Tri-state  | t <sub>HZ</sub>                          | C <sub>L</sub> = 15 pF, Fig. 34 and 37,<br>S2 closed                           |      |          | 200      | ns   |

| Receiver Propagation Delay                              | t <sub>PHL</sub> , t <sub>PLH</sub>      | Fig. 33, 38<br>C <sub>L</sub> = 50 pF                                          |      | 18       | 30       | ns   |

| Receiver Skew                                           |                                          | t <sub>PHL</sub> - t <sub>PLH</sub>   Fig. 33 and 38<br>C <sub>L</sub> = 50 pF |      | 5.0      | ns       |      |

| Receiver Output Enable Time<br>Tri-state to Output Low  | t <sub>ZL</sub>                          | C <sub>L</sub> = 100 pF, Fig. 35 and 39,<br>S1 closed                          |      |          | 200      | ns   |

# SP510

# ULTRA HIGH SPEED MULTIPROTOCOL TRANSCEIVER

REV. 1.0.1

## TIMING CHARACTERISTICS

$V_{CC}$  = +4.75 to 5.25V, C1-C4 = 1 $\mu$ F;  $T_{AMB}$  =  $T_{MIN}$  to  $T_{MAX}$ , unless noted. Typical values are at  $T_{AMB}$  = +25°C.

| PARAMETERS                                               | SYMBOL          | TEST CONDITIONS                                       | MIN. | Түр | Max | Unit |

|----------------------------------------------------------|-----------------|-------------------------------------------------------|------|-----|-----|------|

| Receiver Output Enable Time<br>Tri-state to Output High  | t <sub>ZH</sub> | C <sub>L</sub> = 100 pF, Fig. 35 and 39,<br>S2 closed |      |     | 200 | ns   |

| Receiver Output Disable Time<br>Output Low to Tri-state  | t <sub>LZ</sub> | C <sub>L</sub> = 15 pF, Fig. 35 and 39,<br>S1 closed  |      |     | 200 | ns   |

| Receiver Output Disable Time<br>Output High to Tri-state | t <sub>HZ</sub> | C <sub>L</sub> = 15 pF, Fig. 35 and 39,<br>S2 closed  |      |     | 200 | ns   |

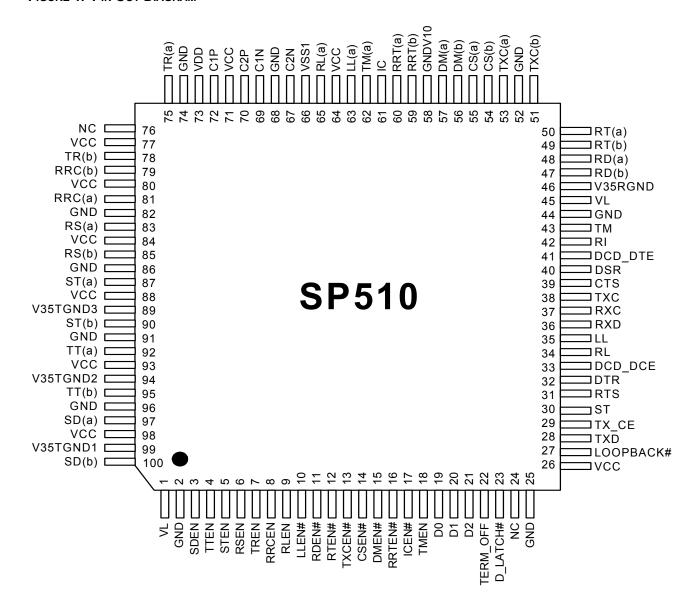

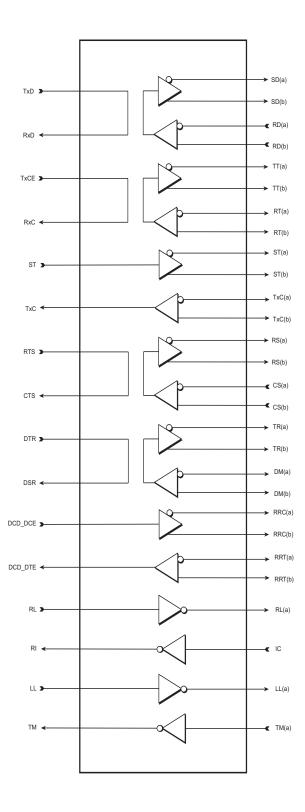

FIGURE 1. PIN OUT DIAGRAM

TABLE 3: PIN DESCRIPTIONS BY FUNCTION

| Pin Name             | Pin Number | I/O |            | DESCRIPTION                                                            |  |  |  |  |  |

|----------------------|------------|-----|------------|------------------------------------------------------------------------|--|--|--|--|--|

| DIFFERENTIAL DRIVERS |            |     |            |                                                                        |  |  |  |  |  |

| TxD                  | 28         | I   | TTL        | TxD Driver Input                                                       |  |  |  |  |  |

| SD(b) / SD(a)        | 100, 97    | 0   | TTL        | Differential Transmit data non-inverting (b) and inverting (a) outputs |  |  |  |  |  |

| V35TGND1             | 99         | I   |            | SD Termination Reference                                               |  |  |  |  |  |

| SDEN                 | 3          | I   | TTL        | TxD Driver Enable                                                      |  |  |  |  |  |

| TxCE                 | 29         | I   | TTL        | TxCE Driver Input                                                      |  |  |  |  |  |

| TT(b) / TT(a)        | 95, 92     | 0   | TTL        | Differential TxCE non-inverting (b) and inverting (a) outputs          |  |  |  |  |  |

| V35TGND2             | 94         | I   |            | TT Termination Reference                                               |  |  |  |  |  |

| TTEN                 | 4          | I   | TTL        | TxCE Driver Enable                                                     |  |  |  |  |  |

| ST                   | 30         | I   | TTL        | ST Driver Input                                                        |  |  |  |  |  |

| ST(b) / ST(a)        | 90, 87     | 0   | TTL        | Differential ST non-inverting (b) and inverting (a) outputs            |  |  |  |  |  |

| V35TGND3             | 89         | I   |            | ST Termination Reference                                               |  |  |  |  |  |

| STEN                 | 5          | I   | TTL        | ST Driver Enable                                                       |  |  |  |  |  |

| RTS                  | 31         | I   | TTL        | RTS Driver Input                                                       |  |  |  |  |  |

| RS(b) / RS(a)        | 85, 83     | 0   | TTL        | Differential RTS non-inverting (b) and inverting (a) outputs           |  |  |  |  |  |

| RSEN                 | 6          | I   | TTL        | RTS Driver Enable                                                      |  |  |  |  |  |

| DTR                  | 32         | I   | TTL        | DTR Driver Input                                                       |  |  |  |  |  |

| TR(b) / TR(a)        | 78, 75     | 0   | TTL        | Differential DTR non-inverting (b) and inverting (a) outputs           |  |  |  |  |  |

| TREN                 | 7          | I   | TTL        | DTR Driver Enable                                                      |  |  |  |  |  |

| DCD_DCE              | 33         | I   | TTL        | DCD_DCE Driver Input                                                   |  |  |  |  |  |

| RRC(b) / RRC(a)      | 79, 81     | 0   | TTL        | Differential DCD non-inverting (b) and inverting (a) outputs           |  |  |  |  |  |

| RRCEN                | 8          | I   | TTL        | DCD Driver Enable                                                      |  |  |  |  |  |

|                      |            |     | SINGLE END | DED DRIVERS                                                            |  |  |  |  |  |

| RL                   | 34         | I   | TTL        | RL Driver Input                                                        |  |  |  |  |  |

| RL(a)                | 65         | 0   | TTL        | RL Driver Output                                                       |  |  |  |  |  |

| RLEN                 | 9          | I   | TTL        | RL Driver Enable                                                       |  |  |  |  |  |

| LL                   | 35         | I   | TTL        | LL Driver Input                                                        |  |  |  |  |  |

| LL(a)                | 63         | 0   | TTL        | LL Driver Output                                                       |  |  |  |  |  |

| LLEN#                | 10         | I   | TTL        | LL Driver Enable, active low                                           |  |  |  |  |  |

| Pin Name        | Pin Number | I/O   |              | DESCRIPTION                                                     |

|-----------------|------------|-------|--------------|-----------------------------------------------------------------|

|                 |            |       | DIFFERENTIAL | RECEIVERS                                                       |

| RxD             | 36         | 0     | TTL          | RxD Receiver Output                                             |

| RD(b) / RD(a)   | 47, 48     | I     | TTL          | Differential RXD non-inverting (b) and inverting (a) inputs     |

| RDEN#           | 11         | I     | TTL          | RxD Receiver Enable, active low                                 |

| RxC             | 37         | 0     | TTL          | RxC Receiver Output                                             |

| RT(b) / RT(a)   | 49, 50     | I     | TTL          | Differential RXC non-inverting (b) and inverting (a) inputs     |

| RTEN#           | 12         | I     | TTL          | RxC Receiver Enable, active low                                 |

| TxC             | 38         | 0     | TTL          | TxC Receiver Output                                             |

| TxC(b) / TxC(a) | 51, 53     | I     | TTL          | Differential TxC non-inverting (b) and inverting (a) inputs     |

| TxCEN#          | 13         | I     | TTL          | TxC Receiver Enable, active low                                 |

| CTS             | 39         | 0     | TTL          | CTS Receiver Output                                             |

| CS(b) / CS(a)   | 54, 55     | I     | TTL          | Differential CTS non-inverting (b) and inverting (a) inputs     |

| CSEN#           | 14         | I     | TTL          | CTS Receiver Enable, active low                                 |

| DSR             | 40         | 0     | TTL          | DSR Receiver Output                                             |

| DM(b) / DM(a)   | 56, 57     | I     | TTL          | Differential DSR non-inverting (b) and inverting (a) inputs     |

| DMEN#           | 15         | I     | TTL          | DSR Receiver Enable, active low                                 |

| DCD_DTE         | 41         | 0     | TTL          | DCD_DTE Receiver Output                                         |

| RRT(b) / RRT(a) | 59, 60     | I     | TTL          | Differential DCD_DTE non-inverting (b) and inverting (a) inputs |

| RRTEN#          | 16         | I     | TTL          | DCD_DTE Receiver Enable, active low                             |

|                 |            |       | SINGLE ENDE  | D RECEIVERS                                                     |

| IC              | 61         | I     | TTL          | RI Receiver Input                                               |

| RI              | 42         | 0     | TTL          | RI Receiver Output                                              |

| ICEN#           | 17         | I     | TTL          | RI Receiver Enable, active low                                  |

| TM(a)           | 62         | I     | TTL          | TM Receiver Input                                               |

| TM              | 43         | 0     | TTL          | TM Receiver Output                                              |

| TMEN            | 18         | I     | TTL          | TM Receiver Enable                                              |

|                 |            | Proto | DCOL MODE S  | ELECTION SIGNALS                                                |

| D2, D1, D0      | 21, 20, 19 | I     | TTL          | Mode Select - Refer to Table 5 and Table 6                      |

REV. 1.0.1

| Pin Name                | Pin Number                                  | I/O |                                                                                     | DESCRIPTION                                                                            |  |  |

|-------------------------|---------------------------------------------|-----|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|

|                         |                                             |     | Charge Pur                                                                          | np Signals                                                                             |  |  |

| C1P, C1N                | 72, 69                                      | 1   | Charge Pump Capacitor 1 +/- inputs. Connect a 1 capacitor between C1P and C1N pins. |                                                                                        |  |  |

| C2P, C2N                | 70, 67                                      | I   |                                                                                     | Charge Pump Capacitor 2 +/- inputs. Connect a 1 μF capacitor between C2P and C2N pins. |  |  |

| VSS1                    | 66                                          | I   |                                                                                     | -2xVCC Charge Pump                                                                     |  |  |

| VDD                     | 73                                          | I   |                                                                                     | 2xVCC Charge Pump                                                                      |  |  |

| GENERAL CONTROL SIGNALS |                                             |     |                                                                                     |                                                                                        |  |  |

| LOOPBACK#               | 27                                          | I   | TTL                                                                                 | Loopback mode enable, active low                                                       |  |  |

| D_LATCH#                | 23                                          | 1   |                                                                                     | Decoder Latch, active low                                                              |  |  |

| TERM_OFF                | 22                                          | I   |                                                                                     | Termination disable                                                                    |  |  |

|                         |                                             |     | Reserve                                                                             | ED PINS                                                                                |  |  |

| NC                      | 24, 76                                      |     |                                                                                     | No Connect                                                                             |  |  |

|                         |                                             | Po  | WER AND GR                                                                          | OUND SIGNALS                                                                           |  |  |

| VCC                     | 26, 64, 71, 77,<br>80, 84, 88, 98           | I   |                                                                                     | 5V supply.                                                                             |  |  |

| VL                      | 1, 45                                       | I   |                                                                                     | Logic I/O Power Supply Input                                                           |  |  |

| GND                     | 2, 25, 44, 52,<br>68, 74, 82, 86,<br>91, 96 | I   |                                                                                     | Ground.                                                                                |  |  |

| GNDV10                  | 58                                          | I   |                                                                                     | V.10 Receiver Ground Reference                                                         |  |  |

| V35RGND                 | 46                                          | 0   |                                                                                     | Receiver Termination Reference                                                         |  |  |

*Note:* Pin type: I = Input, O = Output, I/O = Input/output.

### TABLE 4: PIN DESCRIPTIONS BY PIN NUMBER

|    | PIN DESCRIPTIONS BY PIN NUMBER |                               |                        |         |                                |  |  |  |

|----|--------------------------------|-------------------------------|------------------------|---------|--------------------------------|--|--|--|

| 1  | VL                             | Logic I/O Power Supply Input  | 32                     | DTR     | DTR Driver TTL Input           |  |  |  |

| 2  | GND                            | Ground                        | 33                     | DCD_DCE | DCD_DCE Driver TTL Input       |  |  |  |

| 3  | SDEN                           | TxD Driver Enable Input       | 34 RL RL Driver TTL In |         | RL Driver TTL Input            |  |  |  |

| 4  | TTEN                           | TxCE Driver Enable Input      | 35                     | LL      | LL Driver TTL Input            |  |  |  |

| 5  | STEN                           | ST Driver Enable Input        | 36                     | RxD     | RxD Receiver TTL Output        |  |  |  |

| 6  | RSEN                           | RTS Driver Enable Input       | 37                     | RxC     | RxC Receiver TTL Output        |  |  |  |

| 7  | TREN                           | DTR Driver Enable Input       | 38                     | TxC     | TxC Receiver TTL Output        |  |  |  |

| 8  | RRCEN                          | DCD Driver Enable Input       | 39                     | CTS     | CTS Receiver TTL Output        |  |  |  |

| 9  | RLEN                           | RL Driver Enable Input        | 40                     | DSR     | DSR Receiver TTL Output        |  |  |  |

| 10 | LLEN#                          | LL Driver Enable Input        | 41                     | DCD_DTE | DCD_DTE Receiver TTL Output    |  |  |  |

| 11 | RDEN#                          | RxD Receiver Enable Input     | 42                     | RI      | RI Receiver TTL Output         |  |  |  |

| 12 | RTEN#                          | RxC Receiver Enable Input     | 43                     | TM      | TM Receiver TTL Output         |  |  |  |

| 13 | TxCEN#                         | TxC Receiver Enable Input     | 44                     | GND     | Ground                         |  |  |  |

| 14 | CSEN#                          | CTS Receiver Enable Input     | 45                     | VL      | Logic I/O Power Supply Input   |  |  |  |

| 15 | DMEN#                          | DSR Receiver Enable Input     | 46                     | V35RGND | Receiver Termination Reference |  |  |  |

| 16 | RRTEN#                         | DCD_DTE Receiver Enable Input | 47                     | RD(b)   | RXD Non-Inverting Input        |  |  |  |

| 17 | ICEN#                          | RI Receiver Enable Input      | 48                     | RD(a)   | RXD Inverting Input            |  |  |  |

| 18 | TMEN                           | TM Receiver Enable Input      | 49                     | RT(b)   | RxC Non-Inverting Input        |  |  |  |

| 19 | D0                             | Mode Select Input - Bit 0     | 50                     | RT(a)   | RxC Inverting Input            |  |  |  |

| 20 | D1                             | Mode Select Input - Bit 1     | 51                     | TxC(b)  | TxC Non-Inverting Input        |  |  |  |

| 21 | D2                             | Mode Select Input - Bit 2     | 52                     | GND     | Ground                         |  |  |  |

| 22 | TERM_OFF                       | Termination Disable Input     | 53                     | TxC(a)  | TxC Inverting Input            |  |  |  |

| 23 | D_LATCH#                       | Decoder Latch Input           | 54                     | CS(b)   | CTS Non-Inverting Input        |  |  |  |

| 24 | NC                             | No Connect                    | 55                     | CS(a)   | CTS Inverting Input            |  |  |  |

| 25 | GND                            | Ground                        | 56                     | DM(b)   | DSR Non-Inverting Input        |  |  |  |

| 26 | Vcc                            | Power Supply Input            | 57                     | DM(a)   | DSR Inverting Input            |  |  |  |

| 27 | LOOP-<br>BACK#                 | Loopback Mode Enable Input    | 58                     | GNDV10  | V.10 Rx Ground Reference       |  |  |  |

| 28 | TxD                            | TxD Driver TTL Input          | 59                     | RRT(b)  | DCD_DTE Non-Inverting Input    |  |  |  |

| 29 | TxCE                           | TxCE Driver TTL Input         | 60                     | RRT(a)  | DCD_DTE Inverting Input        |  |  |  |

| 30 | ST                             | ST Driver TTL Input           | 61                     | IC      | RI Receiver Input              |  |  |  |

| 31 | RTS                            | RTS Driver TTL Input          | 62                     | TM(a)   | TM Receiver Input              |  |  |  |

|    | PIN DESCRIPTIONS BY PIN NUMBER |                          |     |          |                           |  |  |

|----|--------------------------------|--------------------------|-----|----------|---------------------------|--|--|

| 63 | LL(a)                          | LL Driver Output         | 82  | GND      | Ground                    |  |  |

| 64 | VCC                            | Power Supply Input       | 83  | RS(a)    | RTS Inverting Output      |  |  |

| 65 | RL(a)                          | RL Driver Output         | 84  | VCC      | Power Supply Input        |  |  |

| 66 | VSS1                           | -2xVCC Charge Pump       | 85  | RS(b)    | RTS Non-Inverting Output  |  |  |

| 67 | C2N                            | Charge Pump Capacitor    | 86  | GND      | Ground                    |  |  |

| 68 | GND                            | Ground                   | 87  | ST(a)    | ST Inverting Output       |  |  |

| 69 | C1N                            | Charge Pump Capacitor    | 88  | VCC      | Power Supply Input        |  |  |

| 70 | C2P                            | Charge Pump Capacitor    | 89  | V35TGND3 | ST Termination Reference  |  |  |

| 71 | VCC                            | Power Supply Input       | 90  | ST(b)    | ST Non-Inverting Output   |  |  |

| 72 | C1P                            | Charge Pump Capacitor    | 91  | GND      | Ground                    |  |  |

| 73 | VDD                            | 2xVCC Charge Pump        | 92  | TT(a)    | TxCE Inverting Output     |  |  |

| 74 | GND                            | Ground                   | 93  | VCC      | 5V Power Supply           |  |  |

| 75 | TR(a)                          | DTR Inverting Output     | 94  | V35TGND2 | TT Termination Reference  |  |  |

| 76 | NC                             | No Connect               | 95  | TT(b)    | TxCE Non-Inverting Output |  |  |

| 77 | VCC                            | Power Supply Input       | 96  | GND      | Ground                    |  |  |

| 78 | TR(b)                          | DTR Non-Inverting Output | 97  | SD(a)    | TxD Inverting Output      |  |  |

| 79 | RRC(b)                         | DCD Non-Inverting Output | 98  | VCC      | 5V Power Supply           |  |  |

| 80 | VCC                            | Power Supply Input       | 99  | V35TGND1 | SD Termination Reference  |  |  |

| 81 | RRC(a)                         | DCD Inverting Output     | 100 | SD(b)    | TxD Non-Inverting Output  |  |  |

## TABLE 5: DRIVER MODE SELECTION

| DRIVER OUTPUT<br>PIN  | V.35<br>Mode | EIA-530<br>MODE | RS-232<br>MODE<br>(V.28) | EIA-<br>530A<br>MODE | RS-449<br>MODE<br>(V.36) | X.21<br>MODE<br>(V.11) | SHUT-<br>DOWN | Suggested<br>Signal |

|-----------------------|--------------|-----------------|--------------------------|----------------------|--------------------------|------------------------|---------------|---------------------|

| MODE (D0, D1,<br>D2)  | 001          | 010             | 011                      | 100                  | 101                      | 110                    | 111           |                     |

| T <sub>1</sub> OUT(a) | V.35         | V.11            | V.28                     | V.11                 | V.11                     | V.11                   | High-Z        | TxD(a)              |

| T <sub>1</sub> OUT(b) | V.35         | V.11            | High-Z                   | V.11                 | V.11                     | V.11                   | High-Z        | TxD(b)              |

| T <sub>2</sub> OUT(a) | V.35         | V.11            | V.28                     | V.11                 | V.11                     | V.11                   | High-Z        | TxCE(a)             |

| T <sub>2</sub> OUT(b) | V.35         | V.11            | High-Z                   | V.11                 | V.11                     | V.11                   | High-Z        | TxCE(b)             |

| T <sub>3</sub> OUT(a) | V.35         | V.11            | V.28                     | V.11                 | V.11                     | V.11                   | High-Z        | TxC_DCE(a)          |

| T <sub>3</sub> OUT(b) | V.35         | V.11            | High-Z                   | V.11                 | V.11                     | V.11                   | High-Z        | TxC_DCE(b)          |

| T <sub>4</sub> OUT(a) | V.28         | V.11            | V.28                     | V.11                 | V.11                     | V.11                   | High-Z        | RTS(a)              |

| T <sub>4</sub> OUT(b) | High-Z       | V.11            | High-Z                   | V.11                 | V.11                     | V.11                   | High-Z        | RTS(b)              |

| T <sub>5</sub> OUT(a) | V.28         | V.11            | V.28                     | V.10                 | V.11                     | V.11                   | High-Z        | DTR(a)              |

| T <sub>5</sub> OUT(b) | High-Z       | V.11            | High-Z                   | High-Z               | V.11                     | V.11                   | High-Z        | DTR(b)              |

| T <sub>6</sub> OUT(a) | V.28         | V.11            | V.28                     | V.11                 | V.11                     | V.11                   | High-Z        | DCD_DCE(a)          |

| T <sub>6</sub> OUT(b) | High-Z       | V.11            | High-Z                   | V.11                 | V.11                     | V.11                   | High-Z        | DCD_DCE(b)          |

| T <sub>7</sub> OUT(a) | V.28         | V.10            | V.28                     | V.10                 | V.10                     | High-Z                 | High-Z        | RL                  |

| T <sub>8</sub> OUT(a) | V.28         | V.10            | V.28                     | V.10                 | V.10                     | High-Z                 | High-Z        | LL                  |

TABLE 6: RECEIVER MODE SELECTION

| RECEIVER INPUT<br>PIN | V.35<br>Mode | EIA-530<br>MODE | RS-232<br>MODE<br>(V.28) | EIA-<br>530A<br>MODE | RS-449<br>MODE<br>(V.36) | X.21<br>Mode<br>(V.11) | SHUT-<br>DOWN | SUGGESTED<br>SIGNAL |

|-----------------------|--------------|-----------------|--------------------------|----------------------|--------------------------|------------------------|---------------|---------------------|

| MODE (D0, D1, D2)     | 001          | 010             | 011                      | 100                  | 101                      | 110                    | 111           |                     |

| R <sub>1</sub> IN(a)  | V.35         | V.11            | V.28                     | V.11                 | V.11                     | V.11                   | High-Z        | RxD(a)              |

| R <sub>1</sub> IN(b)  | V.35         | V.11            | High-Z                   | V.11                 | V.11                     | V.11                   | High-Z        | RxD(b)              |

| R <sub>2</sub> IN(a)  | V.35         | V.11            | V.28                     | V.11                 | V.11                     | V.11                   | High-Z        | RxCE(a)             |

| R <sub>2</sub> IN(b)  | V.35         | V.11            | High-Z                   | V.11                 | V.11                     | V.11                   | High-Z        | RxCE(b)             |

| R <sub>3</sub> IN(a)  | V.35         | V.11            | V.28                     | V.11                 | V.11                     | V.11                   | High-Z        | TxC_DTE(a)          |

| R <sub>3</sub> IN(b)  | V.35         | V.11            | High-Z                   | V.11                 | V.11                     | V.11                   | High-Z        | TxC_DTE(b)          |

| R <sub>4</sub> IN(a)  | V.28         | V.11            | V.28                     | V.11                 | V.11                     | V.11                   | High-Z        | CTS(a)              |

| R <sub>4</sub> IN(b)  | High-Z       | V.11            | High-Z                   | V.11                 | V.11                     | V.11                   | High-Z        | CTS(b)              |

| R <sub>5</sub> IN(a)  | V.28         | V.11            | V.28                     | V.10                 | V.11                     | V.11                   | High-Z        | DSR(a)              |

| R <sub>5</sub> IN(b)  | High-Z       | V.11            | High-Z                   | High-Z               | V.11                     | V.11                   | High-Z        | DSR(b)              |

| R <sub>6</sub> IN(a)  | V.28         | V.11            | V.28                     | V.11                 | V.11                     | V.11                   | High-Z        | DCD_DTE(a)          |

| R <sub>6</sub> IN(b)  | High-Z       | V.11            | High-Z                   | V.11                 | V.11                     | V.11                   | High-Z        | DCD_DTE(b)          |

| R <sub>7</sub> IN(a)  | V.28         | V.10            | V.28                     | V.10                 | V.10                     | High-Z                 | High-Z        | RI                  |

| R <sub>8</sub> IN(a)  | V.28         | V.10            | V.28                     | V.10                 | V.10                     | High-Z                 | High-Z        | TM                  |

**TABLE 7: V.11 & V.35 DRIVERS**

| INP    | UTS   | Оитритѕ |       |  |

|--------|-------|---------|-------|--|

| Tx_EN# | Tx_IN | TX(A)   | Tx(B) |  |

| 1      | 1     | 0       | 1     |  |

| 1      | 0     | 1       | 0     |  |

TABLE 8: V.11 & V.35 RECEIVERS

| INPUTS         | Оитритѕ |  |  |

|----------------|---------|--|--|

| Rx(a) - Rx(b)  | RO      |  |  |

| ≥ 200 mV       | 1       |  |  |

| ≤ –200 mV      | 0       |  |  |

| Open / shorted | 1       |  |  |

TABLE 11: V.10 DRIVERS

| INP    | UTS   | Оитритѕ |         |  |

|--------|-------|---------|---------|--|

| Tx_EN# | Tx_IN | TX(A)   | Тх(в)   |  |

| 1      | 1     | < -4V   | > 30 kΩ |  |

| 1      | 0     | > +4V   | > 30 kΩ |  |

TABLE 12: V.10 RECEIVERS

| INPUTS          | Оитритѕ |

|-----------------|---------|

| Rx(a) - Rx(b)   | RO      |

| ≥ <b>+</b> 0.3V | 0       |

| ≤-0.3V          | 1       |

| Open / ground   | 1       |

TABLE 9: V.28 DRIVERS

| INP    | UTS   | Оитритѕ |         |  |

|--------|-------|---------|---------|--|

| Tx_EN# | Tx_IN | TX(A)   | Tx(B)   |  |

| 1      | 1     | < -5V   | > 30 kΩ |  |

| 1      | 0     | > +5V   | > 30 kΩ |  |

TABLE 10: V.28 RECEIVERS

| INPUTS        | Outputs |

|---------------|---------|

| Rx(a) - Rx(b) | RO      |

| ≥ <b>+</b> 3V | 0       |

| ≤-3V          | 1       |

| Open / ground | 1       |

REV. 1.0.1

FIGURE 2. V.28 DRIVER OUTPUT OPEN CIRCUIT VOLTAGE

FIGURE 3. V.28 DRIVER OUTPUT LOADED VOLTAGE

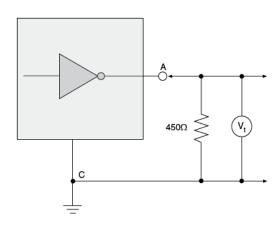

FIGURE 4. V.28 DRIVER OUTPUT SLEW RATE

FIGURE 5. V.28 DRIVER OUTPUT SHORT CIRCUIT CURRENT

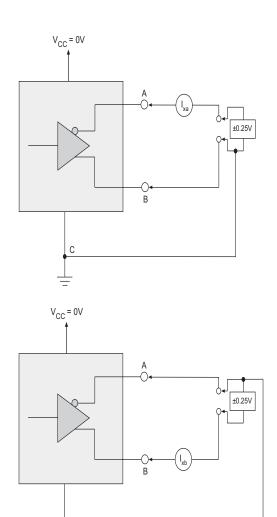

FIGURE 6. V.28 DRIVER OUTPUT POWER-OFF IMPEDANCE

FIGURE 7. V.28 DRIVER OUTPUT RISE/FALL TIME

FIGURE 8. V.28 RECEIVER INPUT IMPEDANCE

FIGURE 9. V.28 RECEIVER INPUT OPEN-CIRCUIT BIAS

FIGURE 10. V.10 DRIVER OUTPUT OPEN-CIRCUIT VOLTAGE

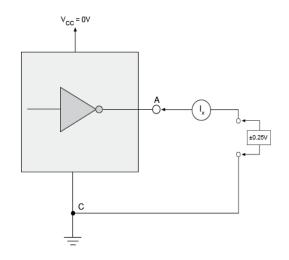

FIGURE 11. V.10 DRIVER OUTPUT TEST TERMINATED VOLTAGE

FIGURE 12. V.10 DRIVER OUTPUT SHORT-CIRCUIT CURRENT

FIGURE 13. V.10 DRIVER OUTPUT POWER-OFF IMPED-ANCE

FIGURE 14. V.10 DRIVER OUTPUT TRANSITION TIME

A A 450Ω Socillocope

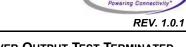

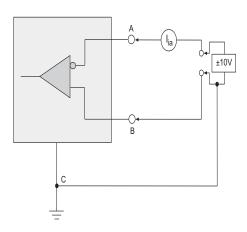

FIGURE 15. V.10 RECEIVER INPUT CURRENT

FIGURE 16. V.10 RECEIVER INPUT IV GRAPH

FIGURE 17. V.11 DRIVER OUTPUT TEST TERMINATED VOLTGE

FIGURE 18. V.11 DRIVER OUTPUT TEST TERMINATED VOLTAGE

FIGURE 19. V.11 DRIVER OUTPUT SHORT-CIRCUIT CURRENT

FIGURE 20. V.11 DRIVER OUTPUT POWER-OFF CURRENT

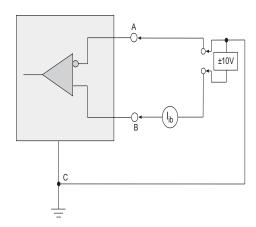

FIGURE 21. V.11 RECEIVER INPUT CURRENT

FIGURE 24. V.11 RECEIVER INPUT CURRENT WITH TER-MINATION

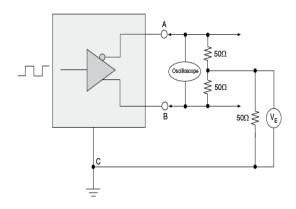

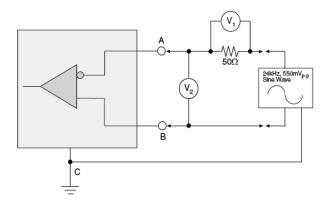

FIGURE 22. V.11 DRIVER OUTPUT RISE/FALL TIME

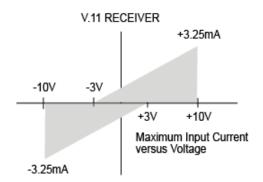

FIGURE 23. V.11 RECEIVER INPUT IV GRAPH

### FIGURE 25. V.11 RECEIVER INPUT IV GRAPH WITH TERMINATION

FIGURE 26. V.35 DRIVER OUTPUT TEST TERMINATED VOLTAGE

FIGURE 27. V.35 DRIVER OUTPUT SOURCE IMPEDANCE

### FIGURE 28. V.35 DRIVER OUTPUT SHORT-CIRCUIT IMPEDANCE

FIGURE 29. V.35 DRIVER OUTPUT RISE/FALL TIME

FIGURE 30. V.35 RECEIVER INPUT SOURCE IMPEDANCE

### FIGURE 31. V.35 RECEIVER INPUT SHORT-CIRCUIT IMPEDANCE

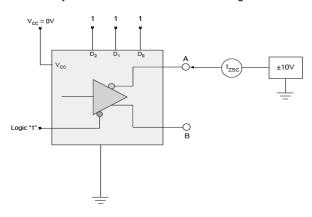

FIGURE 32. DRIVER OUTPUT CURRENT LEAKAGE TEST

Any one of the three conditions for disabling the driver.

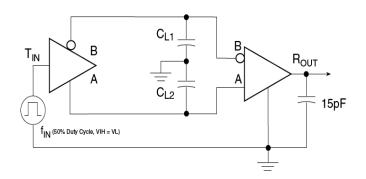

FIGURE 33. DRIVER / RECEIVER TIMING TEST CIRCUIT

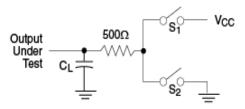

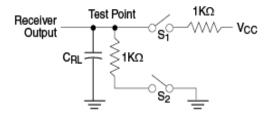

### FIGURE 34. DRIVER TIMING TEST LOAD CIRCUIT

FIGURE 35. RECEIVER TIMING TEST LOAD CIRCUIT

FIGURE 36. DRIVER PROPAGATON DELAYS

28

### FIGURE 37. DRIVER ENABLE AND DISABLE TIMES

FIGURE 38. RECEIVER PROPAGATION DELAYS

FIGURE 39. RECEIVER ENABLE AND DISABLE TIMES

FIGURE 40. V.28 (RS-232) AND V.10 (RS-423) DRIVER ENABLE AND DISABLE TIMES

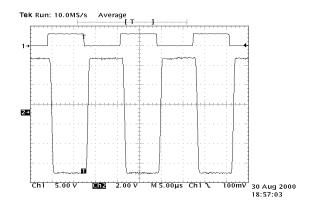

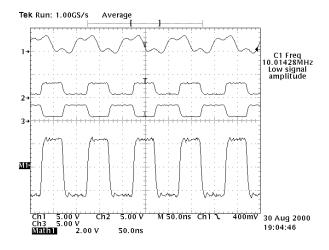

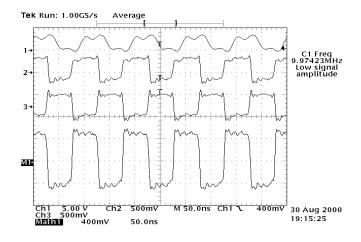

FIGURE 41. TYPICAL V.28 DRIVER OUTPUT WAVEFORM

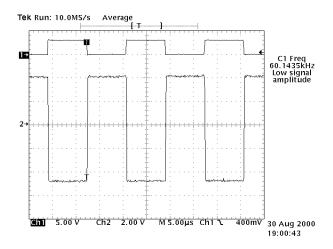

#### FIGURE 42. TYPICAL V.10 DRIVER OUTPUT WAVEFORM

FIGURE 43. TYPICAL V.11 DRIVER OUTPUT WAVEFORM

FIGURE 44. TYPICAL V.35 DRIVER OUTPUT WAVEFORM

RRCEN

RL

RL(a)

RLEN

LL(a)

LLEN

LL

34

35

10

V.35 DRIVER TERMINATION NETWORK

V.10-GND

TX ENABLE 3

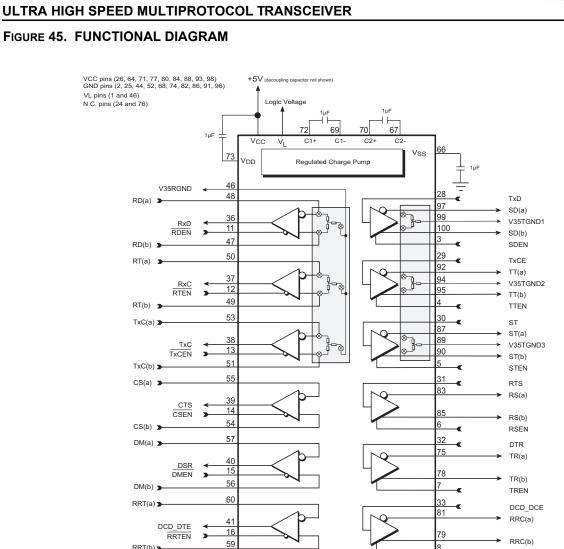

### FIGURE 45. FUNCTIONAL DIAGRAM

RRT(b)

IC >

TM(a) **>**

ICEN

RECEIVER TERMINATION NETWORK

TM ◀

61

17

62

18

19 20

21 D2 23

22

D1

D-LATCH

TERM-OFF LOOPBACK

SP510

GND

## FIGURE 46. SP510 LOOPBACK PATH

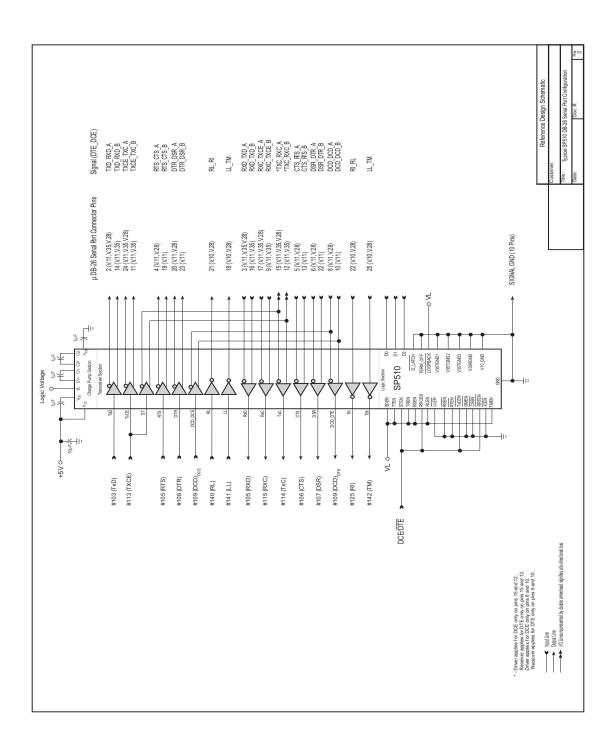

FIGURE 47. TYPICAL OPERATING CONFIGURATION TO SERIAL PORT CONNECTOR WITH DCE/DTE PROGRAMMABILITY

#### Thermal Considerations

High speed devices like the SP510 dissipate heat during normal operation. Actual power dissipation is a function of the switching frequency and loading. For maximum system performance and reliability designers should ensure sufficient air flow. Other commonly used methods for managing heat include heat sinks for higher powered devices, forced air flow (fans) and lower density board stuffing.

#### PCB Design

The use of multi layer printed circuit boards is recommended to provide both a better ground plane and a thermal path for heat dissipation. If possible, the ground plane should face the bottom of the package to form the thermal conduction plane. Two-sided printed circuit boards may be used where board dimensions and package count are small, but multi-layer boards allow for improved signal routing as well as improved signal integrity. A multi layer board allows the use of microstrip line techniques to provide for high speed signal interconnections. On multi-layer boards route the high speed signal lines on the inner layers.

#### REVISION HISTORY

| DATE          | Revision  | DESCRIPTION                                                               |

|---------------|-----------|---------------------------------------------------------------------------|

| December 2009 | Rev 1.0.0 | Final datasheet.                                                          |

| June 2011     | Rev 1.0.1 | Correct type error on mode select tables and update ordering information. |

#### NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 2011 EXAR Corporation

Datasheet June 2011.

Send your serial transceiver technical inquiry with technical details to hotline: serialtechsupport@exar.com.

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.