# **Table of Contents**

| 1. | Feature List                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 4                                                                                     |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 2. | Ordering Guide                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 5                                                                                     |

| 3. | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                              | . 6                                                                                     |

|    | 3.1 Ambient Light Sensing                                                                                                                                                                                                                                                                                                                                                                                                                           | . 8                                                                                     |

|    | 3.2 Proximity Sensing                                                                                                                                                                                                                                                                                                                                                                                                                               | . 8                                                                                     |

|    | 3.3 Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                               | .10                                                                                     |

|    | 3.4 Host Interface                                                                                                                                                                                                                                                                                                                                                                                                                                  | .11                                                                                     |

| 4. | Operational Modes                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 13                                                                                    |

|    | 4.1 Off Mode                                                                                                                                                                                                                                                                                                                                                                                                                                        | .13                                                                                     |

|    | 4.2 Initialization Mode                                                                                                                                                                                                                                                                                                                                                                                                                             | .13                                                                                     |

|    | 4.3 Standby Mode                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |

|    | 4.4 Forced Conversion Mode                                                                                                                                                                                                                                                                                                                                                                                                                          | .13                                                                                     |

|    | 4.5 Automated Operation Mode                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |

| 5. | User to Sensor Communication                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |

|    | 5.1 Basic I <sup>2</sup> C Operation                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                         |

|    | 5.2 Relationship Between I <sup>2</sup> C Registers and Parameter Table                                                                                                                                                                                                                                                                                                                                                                             |                                                                                         |

|    | 5.3 I <sup>2</sup> C Command Register Operation                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                         |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                         |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                         |

|    | 5.3.1 Accessing the Parameter Table (PARAM_QUERY & PARAM_SET Commands)                                                                                                                                                                                                                                                                                                                                                                              | .19                                                                                     |

|    | 5.3.1 Accessing the Parameter Table (PARAM_QUERY & PARAM_SET Commands)                                                                                                                                                                                                                                                                                                                                                                              | .19<br>.19<br>.19                                                                       |

|    | 5.3.1 Accessing the Parameter Table (PARAM_QUERY & PARAM_SET Commands)                                                                                                                                                                                                                                                                                                                                                                              | .19<br>.19<br>.19<br>.19                                                                |

|    | 5.3.1 Accessing the Parameter Table (PARAM_QUERY & PARAM_SET Commands)                                                                                                                                                                                                                                                                                                                                                                              | .19<br>.19<br>.19<br>.19                                                                |

|    | 5.3.1 Accessing the Parameter Table (PARAM_QUERY & PARAM_SET Commands)                                                                                                                                                                                                                                                                                                                                                                              | .19<br>.19<br>.19<br>.19<br>.20                                                         |

|    | 5.3.1 Accessing the Parameter Table (PARAM_QUERY & PARAM_SET Commands)                                                                                                                                                                                                                                                                                                                                                                              | .19<br>.19<br>.19<br>.19<br>.20<br>.20                                                  |

|    | 5.3.1 Accessing the Parameter Table (PARAM_QUERY & PARAM_SET Commands)                                                                                                                                                                                                                                                                                                                                                                              | .19<br>.19<br>.19<br>.20<br>.20<br>.21<br>.21                                           |

|    | 5.3.1 Accessing the Parameter Table (PARAM_QUERY & PARAM_SET Commands) 5.3.2 Sensor Operation Initiation Commands 5.3.3 RESET_CMD_CTR Command 5.3.4 RESET Command 5.4.1 PART_ID 5.4.1 PART_ID 5.4.2 HW_ID 5.4.3 REV_ID 5.4.3 REV_ID 5.4.4 INFO0 5.4.5 INFO1                                                                                                                                                                                         | .19<br>.19<br>.19<br>.20<br>.20<br>.21<br>.21                                           |

|    | 5.3.1 Accessing the Parameter Table (PARAM_QUERY & PARAM_SET Commands) 5.3.2 Sensor Operation Initiation Commands 5.3.3 RESET_CMD_CTR Command 5.3.4 RESET Command 5.4 I <sup>2</sup> C Register Summary 5.4.1 PART_ID 5.4.2 HW_ID 5.4.3 REV_ID 5.4.4 INFO0 5.4.5 INFO1 5.4.6 HOSTINO                                                                                                                                                                | .19<br>.19<br>.19<br>.20<br>.20<br>.21<br>.21<br>.21                                    |

|    | 5.3.1 Accessing the Parameter Table (PARAM_QUERY & PARAM_SET Commands) 5.3.2 Sensor Operation Initiation Commands 5.3.3 RESET_CMD_CTR Command 5.3.4 RESET Command 5.3.4 PART_ID 5.4.1 PART_ID 5.4.2 HW_ID 5.4.3 REV_ID 5.4.4 INFO0 5.4.5 INFO1 5.4.6 HOSTIN0 5.4.7 COMMAND                                                                                                                                                                          | .19<br>.19<br>.19<br>.20<br>.20<br>.21<br>.21<br>.21<br>.22                             |

|    | 5.3.1 Accessing the Parameter Table (PARAM_QUERY & PARAM_SET Commands) 5.3.2 Sensor Operation Initiation Commands 5.3.3 RESET_CMD_CTR Command 5.3.4 RESET Command 5.4 I <sup>2</sup> C Register Summary 5.4.1 PART_ID 5.4.2 HW_ID 5.4.3 REV_ID 5.4.4 INFO0 5.4.5 INFO1 5.4.6 HOSTINO                                                                                                                                                                | .19<br>.19<br>.19<br>.20<br>.21<br>.21<br>.21<br>.21<br>.22<br>.22                      |

|    | 5.3.1 Accessing the Parameter Table (PARAM_QUERY & PARAM_SET Commands) 5.3.2 Sensor Operation Initiation Commands 5.3.3 RESET_CMD_CTR Command 5.3.4 RESET Command 5.4 I <sup>2</sup> C Register Summary 5.4.1 PART_ID 5.4.2 HW_ID 5.4.3 REV_ID 5.4.4 INFO0 5.4.5 INFO1 5.4.6 HOSTIN0 5.4.6 HOSTIN0 5.4.7 COMMAND 5.4.8 IRQENABLE 5.4.9 RESPONSE1 5.4.10 RESPONSE0                                                                                   | .19<br>.19<br>.19<br>.20<br>.21<br>.21<br>.21<br>.22<br>.22<br>.22<br>.22               |

|    | 5.3.1 Accessing the Parameter Table (PARAM_QUERY & PARAM_SET Commands) 5.3.2 Sensor Operation Initiation Commands 5.3.3 RESET_CMD_CTR Command 5.3.4 RESET Command  5.4 I <sup>2</sup> C Register Summary 5.4.1 PART_ID 5.4.2 HW_ID 5.4.2 HW_ID 5.4.3 REV_ID 5.4.4 INFO0 5.4.5 INFO1 5.4.6 HOSTIN0 5.4.6 HOSTIN0 5.4.7 COMMAND 5.4.8 IRQENABLE 5.4.9 RESPONSE1 5.4.10 RESPONSE0 5.4.11 IRQ_STATUS                                                    | .19<br>.19<br>.19<br>.20<br>.21<br>.21<br>.21<br>.22<br>.22<br>.22<br>.22               |

|    | 5.3.1 Accessing the Parameter Table (PARAM_QUERY & PARAM_SET Commands) 5.3.2 Sensor Operation Initiation Commands 5.3.3 RESET_CMD_CTR Command 5.3.4 RESET Command  5.4 I <sup>2</sup> C Register Summary 5.4.1 PART_ID 5.4.2 HW_ID 5.4.3 REV_ID 5.4.4 INFO0 5.4.5 INFO1 5.4.6 HOSTIN0 5.4.7 COMMAND 5.4.7 COMMAND 5.4.8 IRQENABLE 5.4.9 RESPONSE1 5.4.10 RESPONSE0 5.4.11 IRQ_STATUS 5.4.12 HOSTOUTX                                                | .19<br>.19<br>.19<br>.20<br>.21<br>.21<br>.21<br>.22<br>.22<br>.22<br>.22<br>.23<br>.24 |

| 6. | 5.3.1 Accessing the Parameter Table (PARAM_QUERY & PARAM_SET Commands) 5.3.2 Sensor Operation Initiation Commands 5.3.3 RESET_CMD_CTR Command 5.3.4 RESET Command 5.4 I <sup>2</sup> C Register Summary 5.4.1 PART_ID 5.4.2 HW_ID 5.4.3 REV_ID 5.4.4 INFO0 5.4.5 INFO1 5.4.6 HOSTIN0 5.4.7 COMMAND 5.4.8 IRQENABLE 5.4.9 RESPONSE1 5.4.10 RESPONSE0 5.4.11 IRQ_STATUS 5.4.12 HOSTOUTX  Measurement: Principle of Operation                          | .19<br>.19<br>.19<br>.20<br>.21<br>.21<br>.21<br>.22<br>.22<br>.22<br>.23<br>.24<br>.24 |

| 6. | 5.3.1 Accessing the Parameter Table (PARAM_QUERY & PARAM_SET Commands) 5.3.2 Sensor Operation Initiation Commands 5.3.3 RESET_CMD_CTR Command 5.3.4 RESET Command 5.3.4 RESET Command 5.4.1 PART_ID 5.4.1 PART_ID 5.4.2 HW_ID 5.4.3 REV_ID 5.4.4 INFO0 5.4.5 INFO1 5.4.6 HOSTIN0 5.4.7 COMMAND 5.4.8 IRQENABLE 5.4.9 RESPONSE1 5.4.10 RESPONSE0 5.4.11 IRQ_STATUS 5.4.12 HOSTOUTx  Measurement: Principle of Operation 6.1 Output Field Utilization | .19<br>.19<br>.19<br>.20<br>.21<br>.21<br>.21<br>.22<br>.22<br>.22<br>.23<br>.24<br>.24 |

| 6. | 5.3.1 Accessing the Parameter Table (PARAM_QUERY & PARAM_SET Commands) 5.3.2 Sensor Operation Initiation Commands 5.3.3 RESET_CMD_CTR Command 5.3.4 RESET Command 5.4 I <sup>2</sup> C Register Summary 5.4.1 PART_ID 5.4.2 HW_ID 5.4.3 REV_ID 5.4.4 INFO0 5.4.5 INFO1 5.4.6 HOSTIN0 5.4.7 COMMAND 5.4.8 IRQENABLE 5.4.9 RESPONSE1 5.4.10 RESPONSE0 5.4.11 IRQ_STATUS 5.4.12 HOSTOUTX  Measurement: Principle of Operation                          | .19<br>.19<br>.19<br>.20<br>.21<br>.21<br>.21<br>.22<br>.22<br>.22<br>.23<br>.24<br>.24 |

|    | 6.4 Interrupt Operation                                  |

|----|----------------------------------------------------------|

|    | 6.5 Timing of Channel Measurements                       |

| 7. | Parameter Table                                          |

|    | 7.1 Global Area of the Parameter Table                   |

|    | 7.2 Channel Specific Setup Areas of the Parameter Table. |

|    | 7.3 Photodiode Selection                                 |

| 8. | Electrical Specifications                                |

| 9. | Pin Descriptions                                         |

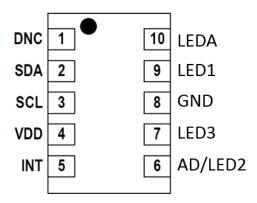

|    | 9.1 DFN Pin Description                                  |

|    | 9.2 Module Pin Description                               |

| 10 | D. Package Outline...............................55      |

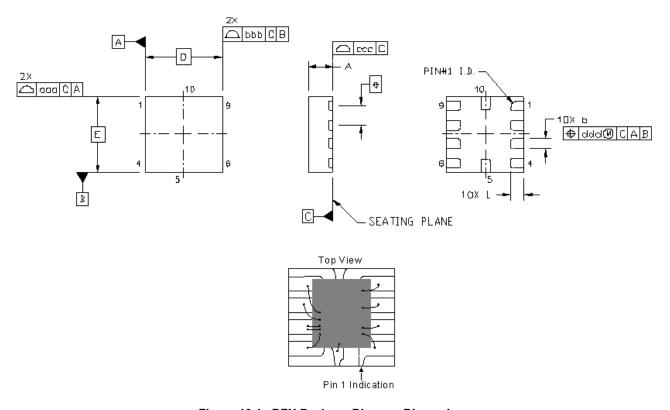

|    | 10.1 10-Pin 2x2 mm DFN                                   |

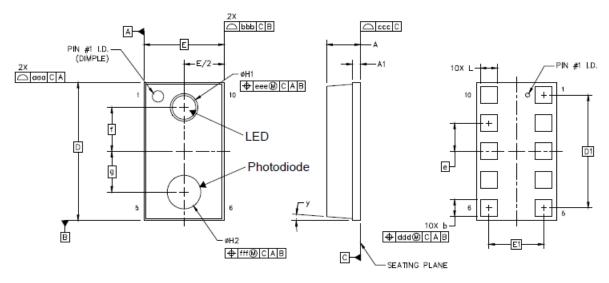

|    | 10.2 10-Pin LGA Module                                   |

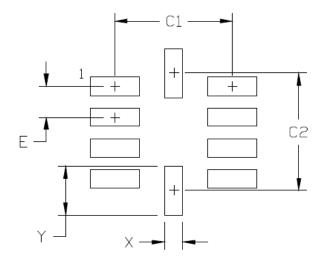

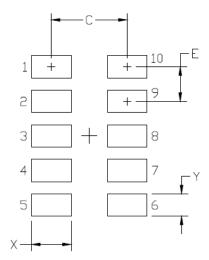

| 11 | I. Land Patterns                                         |

|    | 11.1 2x2 mm DFN Land Pattern                             |

|    | 11.2 10-Pin LGA Module                                   |

| 15 | Pavision History 60                                      |

#### 1. Feature List

- · Proximity detector

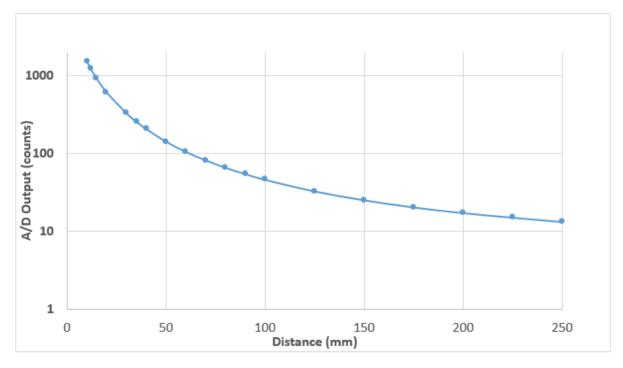

- From under 1 cm to 50 cm without additional lensing.

- From under 1 cm to 200 cm with additional lensing (e.g., 5 mm hemispherical lens).

- · Up to three independent LED drivers.

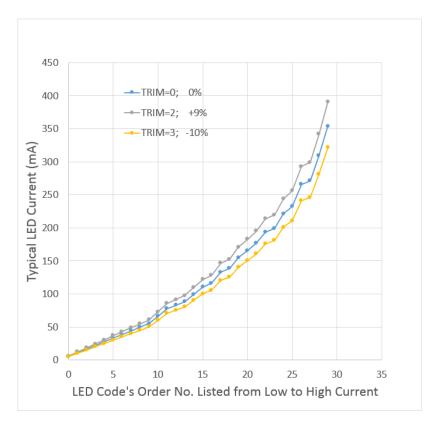

- 30 current settings from 5.6 mA to 360 mA for each LED driver.

- Operates in direct sunlight with optional on-die 940 nm passband filter.

- On die 940 bandpass filter that rejects unwanted visible light and IR from daylight and other sources (Si115x- AB09/ AB9X).

- · Ambient light sensor

- <100 mlx resolution possible, allowing operation under dark glass.

- Up to 128 klx dynamic range possible across two ADC range settings.

- · Industry's lowest power consumption

- 1.62 to 3.6 V supply voltage

- 9 μA average current (LED pulsed 24.4 μs every 800 ms at 180 mA plus 3 μA Si115x supply)

- <500 nA standby current</li>

- 24.4 µs LED "on" time keeps total power consumption duty cycle low without compromising performance or noise community

- · Internal and external wake support

- · Built-in voltage supply monitor and power-on reset controller

- Trimmable internal oscillator with typical 1% accuracy

- I<sup>2</sup>C Serial communications

- · Up to 400 k data rate

- · Slave mode hardware address decoding

- · Two package options:

- 10-lead 2 x 2 x 0.65 mm DFN

- 10-lead 2.9 x 4.9 x1.2 mm LGA module with integrated 940 nm LED

- Temperature Range: -40 to +85 °C

## 2. Ordering Guide

Table 2.1. Ordering Guide

| Family | OPNs            | Package                     | ALS | 940 nm<br>Filter | Proximity<br>(# of LED Driv-<br>ers) | # of LEDs Included |

|--------|-----------------|-----------------------------|-----|------------------|--------------------------------------|--------------------|

| Si1151 | Si1151-AB00-GMR | 2 x 2 mm DFN                | Y   |                  | 1                                    | 0                  |

| Si1151 | Si1151-AB09-GMR | 2 x 2 mm DFN                |     | Y                | 1                                    | 0                  |

| Si1152 | Si1152-AB00-GMR | 2 x 2 mm DFN                | Y   |                  | 2                                    | 0                  |

| Si1152 | Si1152-AB09-GMR | 2 x 2 mm DFN                |     | Y                | 2                                    | 0                  |

| Si1153 | Si1153-AB00-GMR | 2 x 2 mm DFN                | Y   |                  | 3                                    | 0                  |

| Si1153 | Si1153-AB09-GMR | 2 x 2 mm DFN                |     | Y                | 3                                    | 0                  |

| Si1153 | Si1153-AB9x-GMR | 2.85 x 4.9 mm<br>LGA Module |     | Y                | 3                                    | 1                  |

### 3. Functional Description

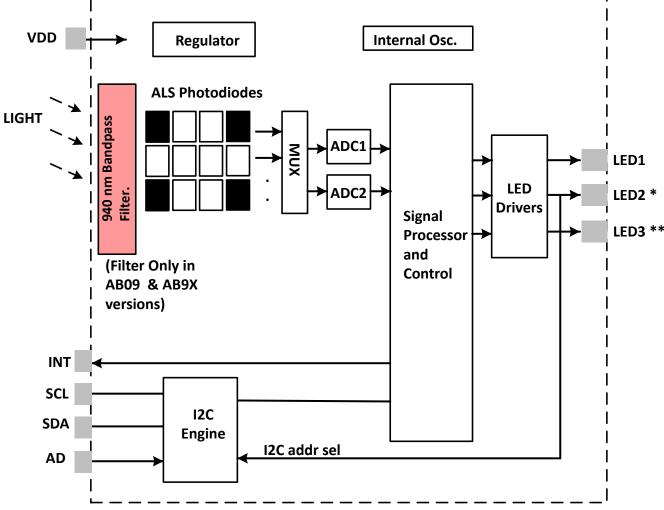

The Si115x is an active optical reflectance proximity detector, with ambient light sensors whose operational state is controlled through registers accessible through the I2C interface. The host can command the Si115x to initiate on-demand Ambient Light or proximity measurements. The host can also place the Si115x in an autonomous operational state where it performs measurements at set intervals and interrupts the host either after each measurement is completed or whenever the sample is larger/smaller than a set threshold value or exits/enters a set threshold window. This results in overall system power saving, allowing the host controller to operate longer in its sleep state instead of polling the Si115x.

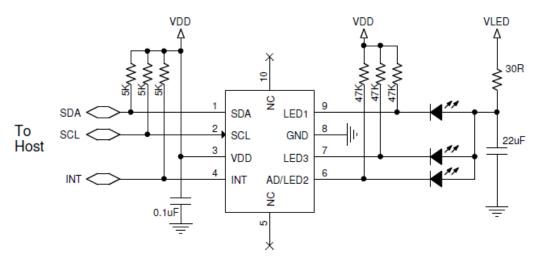

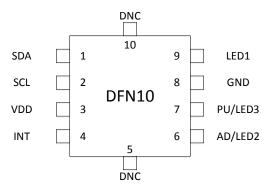

<sup>\*</sup> Pull up to VDD with 47 kOhm resistor to select primary I2C address (0x53), or down to GND for alt I2C address 0x52. LED2 driving capabilities only available on Si1152 and Si1153.

Figure 3.1. Functional Block Diagram

<sup>\*\*</sup> Pull up to VDD with 47 kOhm resistor. LED3 driving capabilities only available on Si1153.

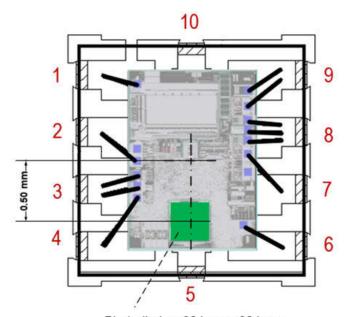

Figure 3.2. Si115x DFN Package Basic Application

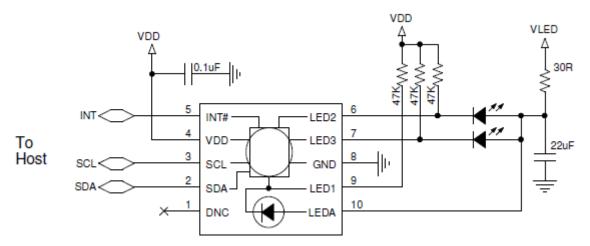

Figure 3.3. Si115x LGA Module Basic Application

#### 3.1 Ambient Light Sensing

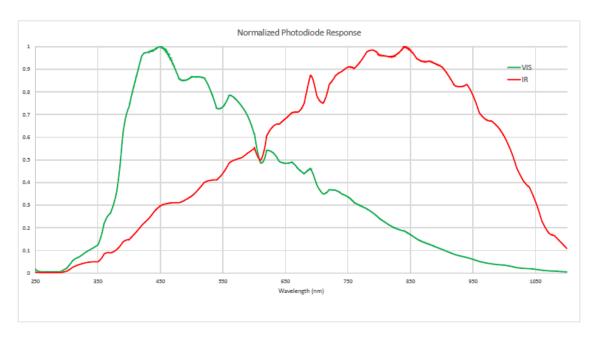

The Si115x has photodiodes capable of measuring visible and infrared light. However, the visible photodiode is also influenced by infrared light. The measurement of illuminance requires the same spectral response as the human eye. If an accurate lux measurement is desired, the extra IR response of the visible-light photodiode must be compensated. Therefore, to allow the host to make corrections to the infrared light's influence, the Si115x reports the infrared light measurement on a separate channel. The separate visible and IR photodiodes lend themselves to a variety of algorithmic solutions. The host can then take these two measurements and run an algorithm to derive an equivalent lux level as perceived by a human eye. Having the IR correction algorithm running in the host allows for the most flexibility in adjusting for system-dependent variables. For example, if the glass used in the system blocks visible light more than infrared light, the IR correction needs to be adjusted. Si115x parts with the bandpass 940 nm filter cannot be used for ambient light sensing.

If the host is not making any infrared corrections, the infrared measurement can be turned off in the CHAN LIST parameter.

By default, the measurement parameters are optimized for indoor ambient light levels, where it is possible to detect low light levels. For operation under direct sunlight, the ADC can be programmed to operate in a high signal operation so that it is possible to measure direct sunlight without overflowing.

For low-light applications, it is possible to increase the ADC integration time. Normally, the integration time is 24.4 µs. By increasing this integration time, the ADC can detect light levels as low as 100 mlx. The ADC integration time for the Visible Light Ambient measurement can be programmed independently of the ADC integration time of the Infrared Light Ambient measurement. The independent ADC parameters allow operation under glass covers having a higher transmittance to Infrared Light than Visible Light.

When operating in the lower signal range, or when the integration time is increased, it is possible to saturate the ADC when the ambient light suddenly increases. Any overflow condition will have the corresponding data registers report a value of 0xFFddFF for 16-bit mode and 0x7FFFFF for 24-bit mode. The host can adjust the ADC sensitivity to avoid an overflow condition. If the light levels return to a range within the capabilities of the ADC, the corresponding data registers begin to operate normally.

The Si115x can initiate ALS measurements either when explicitly commanded by the host or periodically through an autonomous process. Refer to Section 4. Operational Modes for additional details.

Two ADCs can be used for simultaneous readings of the visible or proximity photodiode and black dark current reference photodiode. When subtracted, these differential measurements remove dark current, reducing noise that enables lower light sensitivity.

#### 3.2 Proximity Sensing

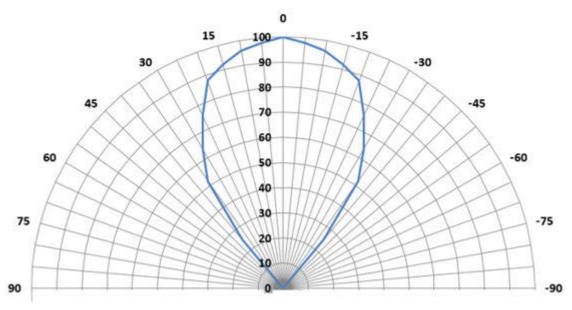

The Si115x has been optimized for use as either a dual-port or single-port active reflection proximity detector. Over distances of less than 50 cm, the dual-port active reflection proximity detector has significant advantages over single-port, motion-based infrared systems, which are only good for triggered events. Motion-based infrared detectors identify objects within proximity, but only if they are moving. Single-port motion-based infrared systems are ambiguous about stationary objects even if they are within the proximity field. The Si115x can reliably detect an object entering or exiting a specified proximity field, even if the object is not moving or is moving very slowly. However, beyond about 30–50 cm, even with good optical isolation, single-port signal processing may be required due to static reflections from nearby objects, such as tables, walls, etc. If motion detection is acceptable, the Si115x can achieve ranges of up to 50 cm, through a single product window.

For small objects, the drop in reflectance is as much as the fourth power of the distance. This means that there is less range ambiguity than with passive motion-based devices. For example, a sixteen fold change in an object's reflectance means only a fifty-percent drop in detection range.

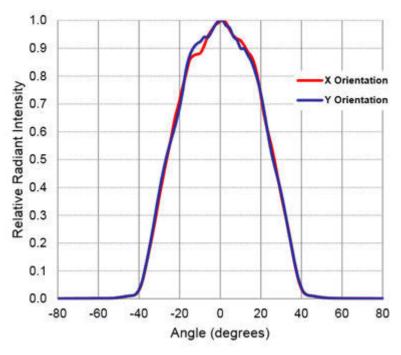

The Si115x can drive up to three separate infrared LEDs. When the three infrared LEDs are placed in an L-shaped configuration, it is possible to triangulate an object within the three-dimensional proximity field. Thus, a touchless user interface can be implemented with the aid of host software.

The Si115x can initiate proximity sense measurements when explicitly commanded by the host or periodically through an autonomous process.

Whenever it is time to make a PS measurement, the Si115x makes up to six measurements, depending on what is enabled in the CHLIST parameter. Other ADC parameters for these measurements can also be modified to allow proper operation under different ambient light conditions.

The LED choice is programmable for each of these six measurements. Each measurement can select which combination of 3 LEDs are turned on and which of two LED current setting banks are used to set the LED currents. Optionally, each proximity measurement can be compared against a host-programmable threshold. With threshold settings for each PS channel, it is also possible for the Si115x to notify the host whenever the sample is larger/smaller than the threshold. In addition, a threshold window can be built by the host to trigger the interrupt whenever the sampler enters/exits the window. This reduces the number of interrupts to the host, aiding in efficient software algorithms.

The Si115x can also generate an interrupt after a complete set of proximity measurements, ignoring any threshold settings.

To support different power usage cases dynamically, the LED current of each output is independently programmable. The current can be programmed anywhere from 5.5 to 354 mA. (See Table 8.8 Typical LED Current vs. LED Code on page 49.) Therefore, the host can optimize for proximity detection performance or for power saving dynamically. This feature can be useful since it allows the host to reduce the LED current once an object has entered a proximity sphere, and the object can still be tracked at a lower current setting. Finally, the flexible current settings make it possible to control the infrared LED currents with a controlled current sink, resulting in higher precision. The ADC properties are programmable. For indoor operation, the ADC should be configured for low signal range for best reflectance sensitivity. When under high ambient conditions, the ADC should be configured for high signal level range operation.

When operating in the lower signal range, it is possible to saturate the ADC when the ambient light level is high. Any overflow condition is reported with a value of 0xFFFF for 16-bit mode and 0x7FFFFF for 24-bit mode. The host can then adjust the ADC sensitivity to avoid an overflow condition. If the light levels return to a range within the capabilities of the ADC, the corresponding data registers begin to operate normally.

The Si115x can be configured with three different sizes of proximity photodiode to enable the highest sensitivity without saturation.

Proximity detection ranges beyond 50 cm can be achieved with lensing and by selecting a longer integration time. The detection range may be increased further, even with high ambient light, by averaging multiple measurements.

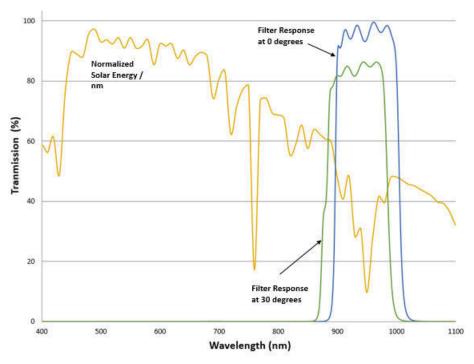

The Si115x-AB09 version of the Si115x is designed with an on die 940 nm bandpass filter. It is designed to reject sunlight and to pass as much of the LED excitation energy as possible. 940 nm is selected as the operating wavelength since it corresponds to a dip in the energy of the solar spectrum.

Figure 3.4. Typical Si115x-AB09 Filter Response Compared to the Sunlight Energy Spectrum

#### 3.3 Power Consumption

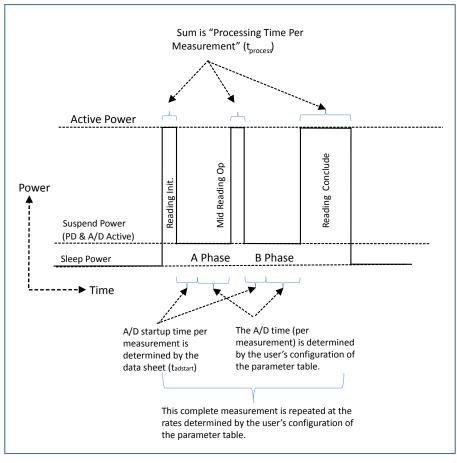

The Si115x alternates between three power consumption states: Active, Suspend, and Sleep. (See the diagram below for an illustratation of each of these states.) The total power consumed by the part depends heavily on the measurement rate, measurement mode, and measurement gain for the various channels enabled. The power levels for the three modes, as well as the Active Power time per reading, are provided in this document. The Suspend time (where the A/D and PD are operating) has two parts. One is determined by the user setup and can be determined by the DECIM\_RATE and HW\_GAIN setup information in Section 7.2 Channel Specific Setup Areas of the Parameter Table, while the other (A/D Startup time) is determined by tadstart, shown in Table 8.2 Electrical Performance Characteristics on page 43.

Figure 3.5. Power Consumption States During a Reading

Every A/D conversion has three periods:

155 µs at 4.5 mA (setup time by internal controller)

48.8  $\mu$ s at 525  $\mu$ A (setup time by A/D)

48.8 µs \* (2<sup>HW\_GAIN[3:0]</sup>) at 525 µA (Actual A/D time that will vary with integration time)

#### 3.4 Host Interface

The host interface to the Si115x consists of three pins:

- · SCL

- SDA

- INT

SCL and SDA are standard open-drain pins as required for  $I^2C$  operation. The Si115x asserts the INT pin to interrupt the host processor. The INT pin is an open-drain output. A pull-up resistor is needed for proper operation. As an open-drain output, it can be shared with other open-drain interrupt sources in the system.

For proper operation, the Si115x is expected to fully complete its Initialization Mode prior to any activity on the I2C.

The default I2C address of the Si115x can be changed by pulling the LED pin to ground. This changes the I2C address to 0x52 (the default value is 0x53).

The INT, SCL, and SDA pins are designed so that it is possible for the Si115x to enter the Off Mode by software command without interfering with normal operation of other I<sup>2</sup>C devices on the bus.

Conceptually, the I<sup>2</sup>C interface allows access to the Si115x internal registers.

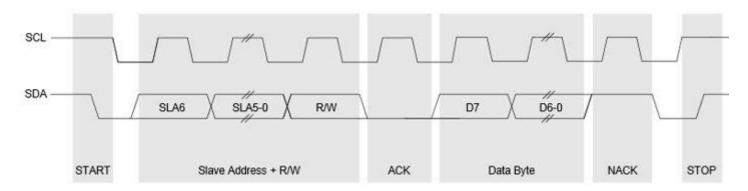

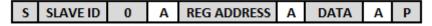

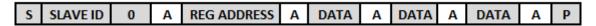

An  $I^2C$  write access always begins with a start (or restart) condition. The first byte after the start condition is the  $I^2C$  address and a read-write bit. The second byte specifies the starting address of the Si115x internal register. Subsequent bytes are written to the Si115x internal register sequentially until a stop condition is encountered. An  $I^2C$  write access with only two bytes is typically used to set up the Si115x internal address in preparation for an  $I^2C$  read.

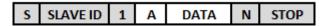

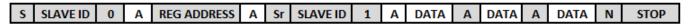

The  $I^2C$  read access, like the  $I^2C$  write access, begins with a start or restart condition. In an  $I^2C$  read, the  $I^2C$  master then continues to clock SCK to allow the Si115x to drive the  $I^2C$  with the internal register contents. The Si115x also supports burst reads and burst writes. The burst read is useful in collecting contiguous, sequential registers. The Si115x register map was designed to optimize for burst reads for interrupt handlers, and the burst writes are designed to facilitate rapid programming of commonly used fields, such as thresholds registers.

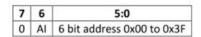

The internal register address is a six-bit (bit 5 to bit 0) plus an Auto increment Disable (on bit 6). The Auto increment Disable is turned off by default. Disabling the auto incrementing feature allows the host to poll any single internal register repeatedly without having to keep updating the Si115x internal address every time the register is read.

It is recommended that the host should read performance measurements (in the  $I^2C$  Register Map) when the Si115x asserts INT. Although the host can read any of the Si115x's  $I^2C$  registers at any time, care must be taken when reading 2-byte measurements outside the context of an interrupt handler. The host could be reading part of the 2-byte measurement when the internal sequencer is updating that same measurement coincidentally. When this happens, the host could be reading a hybrid 2-byte quantity whose high byte and low byte are parts of different samples. If the host must read these 2-byte registers outside the context of an interrupt handler, the host should "double-check" a measurement if the measurement deviates significantly from a previous reading.

Figure 3.6. I<sup>2</sup>C Bit Timing Diagram

Figure 3.7. Host Interface Single Write

Figure 3.8. Host Interface Single Read

Figure 3.9. Host Interface Burst Write

Figure 3.10. Host Interface Burst Read

Figure 3.11. Si115x REG ADDRESS Format

The following notes apply for the figures above:

- 1. Gray boxes are driven by the host to the Si115x.

- 2. White boxes are driven by the Si115x.

- 3. A = ACK or "acknowledge".

- 4. N = NACK or "no acknowledge".

- 5. S = START condition.

- 6. Sr = repeat START condition.

- 7. P = STOP condition.

- 8. AI = Disable Auto Increment when set.

### 4. Operational Modes

The Si115x can be in one of many operational modes at any time. It is important to consider the operation mode, since the mode has an impact on the overall power consumption of the Si115x. The various modes are:

- · Off Mode

- · Initialization Mode

- · Standby Mode

- · Forced Conversion Mode

- · Autonomous Mode

#### 4.1 Off Mode

The Si115x is in the Off Mode when  $V_{DD}$  is either not connected to a power supply or if the  $V_{DD}$  voltage is below the stated VDD\_OFF voltage described in the electrical specifications. As long as the parameters stated in Table 8.7 Absolute Maximum Ratings on page 48 are not violated, no current will flow through the Si115x. In the Off Mode, the Si115x SCL and SDA pins do not interfere with other  $I^2C$  devices on the bus. Ensure that none of the pins have a voltage larger than the voltage on the VDD pin. If  $V_{DD}$  is grounded, for example, then current flows from system power to system ground through the SCL, SDA, and INT pull-up resistors and the ESD protection devices. Allowing  $V_{DD}$  to be less than VDD\_OFF is intended to serve as a hardware method of resetting the Si115x without a dedicated reset pin.

The Si115x can also re-enter the Off Mode upon receipt of a software reset sequence. Upon entering Off Mode, the Si115x proceeds directly from the Off Mode to the Initialization Mode.

#### 4.2 Initialization Mode

When power is applied to  $V_{DD}$  and is greater than the minimum  $V_{DD}$  Supply Voltage stated in the electrical specification table, the Si115x enters its Initialization Mode. In the Initialization Mode, the Si115x performs its initial startup sequence. Since the  $I^2C$  may not yet be active, it is recommended that no  $I^2C$  activity occur during this brief Initialization Mode period. The "Start-up time" specification in the electrical specification table is the minimum recommended time the host needs to wait before sending any  $I^2C$  accesses following a power-up sequence. After Initialization Mode has completed, the Si115x enters Standby Mode. During the Initialization mode, the  $I^2C$  address selection is made according to whether LED2 is pulled up or down.

#### 4.3 Standby Mode

The Si115x spends most of its time in Standby Mode. After the Si115x completes the Initialization Mode sequence, it enters Standby Mode. While in Standby Mode, the Si115x does not perform any Ambient Light measurements or Proximity Detection functions. However, the I<sup>2</sup>C interface is active and ready to accept reads and writes to the Si115x registers. The internal Digital Sequence Controller is in its sleep state and does not draw much power. In addition, the INT output retains its state until it is cleared by the host.

I<sup>2</sup>C accesses do not necessarily cause the Si115x to exit the Standby Mode. For example, reading Si115x registers is accomplished without needing the Digital Sequence Controller to wake from its sleep state.

#### 4.4 Forced Conversion Mode

The Si115x can operate in Forced Conversion Mode under the specific command of the host processor. The Forced Conversion Mode is entered when the FORCE command is sent. Upon completion of the conversion, the Si115x can generate an interrupt to the host if the corresponding interrupt is enabled. It is possible to initiate both a proximity and ALS measurement.

#### 4.5 Automated Operation Mode

The Si115x can be placed in the Autonomous Operation Mode where measurements are performed automatically without requiring an explicit host command for every measurement. The START command is used to place the Si115x in the Autonomous Operation Mode.

The Si115x updates the I<sup>2</sup>C registers for proximity and ALS automatically. The host can also choose to be notified when these new measurements are available by enabling interrupts. The conversion frequency for autonomous operation is set up by the host prior to the START command.

The Si115x can also interrupt the host when the proximity or ALS measurement reach a pre-set threshold. For detailed threshold-based interrupt usage, see Section 6.4 Interrupt Operation. To assist in the handling of interrupts the registers are arranged so that the interrupt handler can perform an I<sup>2</sup>C burst read operation to read the necessary registers, beginning with the interrupt status register, and cycle through the various output registers.

#### 5. User to Sensor Communication

### 5.1 Basic I<sup>2</sup>C Operation

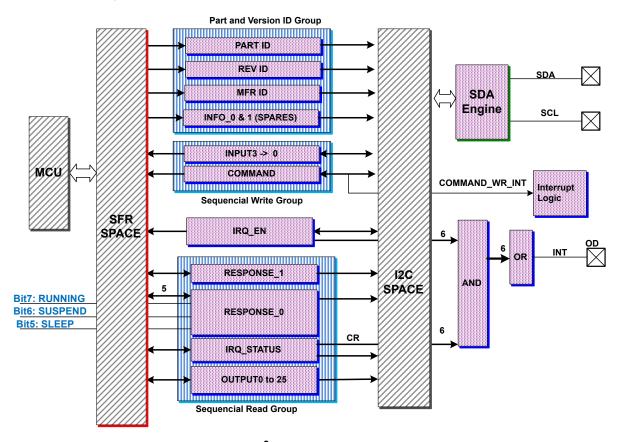

$I^2C$  operation is dependent on serial  $I^2C$  reads and writes to an addressable bank of memory referred to as  $I^2C$  space. The diagram below outlines the registers used, some functionality and the direction of data flow. The  $I^2C$  address is initially fixed but can be programmed to a new value. This new value is volatile and reverts to the old value on hardware or software reset. Only 7-bit  $I^2C$  addressing is supported; 10-bit  $I^2C$  addressing is not supported. The Si115x responds to the  $I^2C$  address of 0x53 or to an alternate address of 0x52.

Figure 5.1. I<sup>2</sup>C Interface Block Diagram

#### 5.2 Relationship Between I<sup>2</sup>C Registers and Parameter Table

Note that most of the Si115x configuration is accomplished through 'Parameters'. The Si115x has an internal MCU with SRAM. The Parameters are stored in the Si115x Internal MCU SRAM. The I<sup>2</sup>C Registers can be viewed as mailbox registers that form an interface between the host and the internal MCU. The figure below shows the relationship between some of the key interface registers to the internal Parameters managed by the internal MCU.

- The I<sup>2</sup>C registers are directly accessible by the host.

- · The parameter table is:

- · Accessible indirectly via the command register (and others).

- Used during setup to fix the operating modes of the Si115x.

- 0x2C bytes long and is read and written indirectly, one bye at a time, via the command register.

The data stored in the parameter table is volatile and is lost when the part is powered down or software reset command is sent to the part via the  $I^2C$  part.

Sensor Parameter Table.

#### **I2C Registers Directly Indirectly Accessible by Host Accessible by Host** Parameter Address NAME 0x00 I2C ADDR I2C Register Name WRT CHAN\_LIST 0x01 Address Host 0x02 ADCCONFIG0 PART ID 0 ΙN 0x03 ADCSENS0 REV ID IN 0x04 ADCPOST0 MFR ID 2 IN 0x05 MEASCONFIG0 INF00 3 IN 0x06 ADCCONFIG1 INFO1 4 IN 0x07 ADCSENS1 HOSTIN3 IN/OUT 0x08 ADCPOST1 IN/OUT HOSTIN2 8 Fields used to write 9 IN/OUT to Parameter Table 0x09 MEASCONFIG1 HOSTIN1 HOSTIN0 0A IN/OUT 0x0A ADCCONFIG2 0B COMMAND IN/OUT 0x0B ADCSENS2 IRQ\_ENABLE 0F IN/OUT 0x0C ADCPOST2 RESPONSE1 10 IN 0x0D MEASCONFIG2 RESPONSE0 IN 11 0x0E ADCCONFIG3 IRQ STATUS IN 12 0x0F ADCSENS3 HOSTOUT0 13 ΙN 0x10 ADCPOST3 HOSTOUT1 14 ΙN 0x11 MEASCONFIG3 HOSTOUT2 15 IN 0x12 ADCCONFIG4 HOSTOUT3 16 ΙN 0x13 ADCSENS4 IN HOSTOUT4 17 0x14 ADCPOST4 HOSTOUT5 18 ΙN 0x15 MEASCONFIG4 HOSTOUT6 19 IN 0x16 ADCCONFIG5 HOSTOUT7 1A IN ADCSENS5 0x17 HOSTOUT8 1B IN 0x18 ADCPOST5 HOSTOUT9 1C ΙN 0x19 MEASCONFIG5 1D IN HOSTOUT10 0x1A MEASRATE H HOSTOUT11 1E IN 0x1B MEASRATE L HOSTOUT12 1F IN 0x1C MEASCOUNT0 HOSTOUT13 20 IN 0x1D MEASCOUNT1 HOSTOUT14 21 IN MEASCOUNT2 0x1E HOSTOUT15 22 ΙN 0x1F LED1 A HOSTOUT16 23 IN 0x20 LED1\_B HOSTOUT17 24 IN HOSTOUT18 25 IN 0x21 LED3 A 0x22 HOSTOUT19 26 ΙN LED3\_B 27 HOSTOUT20 IN 0x23 LED2 A HOSTOUT21 28 IN 0x24 LED2\_B 29 IN HOSTOUT22 0x25 THRESHOLDO H HOSTOUT23 2A ΙN 0x26 THRESHOLDO\_L 2B IN HOSTOUT24 0x27 THRESHOLD1 H HOSTOUT25 2C IN 0x28 THRESHOLD1 L 0x29 UPPER THRESHOLD H UPPER\_THRESHOLD\_L 0x2A 0x2B **BURST** 0x2C LOWER\_THRESHOLD\_H 0x2D LOWER THRESHOLD L

Figure 5.2. Accessing Parameters through I<sup>2</sup>C Registers

#### 5.3 I<sup>2</sup>C Command Register Operation

Writing the codes shown below in the command summary table signals the sensor to undertake one of several complex operations.

These operations take time and all commands should be followed by a read of the RESPONSE0 register to confirm the operation is complete by examining the counter and to check for an error in the error bit. The error bit is set in the RESPONSE0 register's command counter if there is an error in the previous command (e.g., attempt to write to an illegal address beyond the parameter table, or a channel and /or burst configuration that exceeds the size of the output field (26 bytes)). If there is no such error, then the counter portion of the command counter will be incremented.

The RESPONSE\_0 register should be read after every command to determine completion and to check for an error. If an error is found, which should not happen except for a host SW bug, the host should clear the error with a RESET command or a RESET\_CMD\_CTR command.

One operating option is to do a RESET\_CMD\_CTR command before every command.

Two of the commands imply another I<sup>2</sup>C register contains an argument.

- STORE\_NEW\_I2C ADDR command implies a new address has been loaded in the parameter table location I2CID PARAMETER.

- PARAM\_SET command implies a byte has been stuffed into INPUT0 register.

- The three CHAN\_LIST commands imply the CHAN\_LIST location in the parameter table has been configured. A valid CHAN\_LIST implies other configuration areas in the parameter table are correctly setup as well.

Two of the commands result in another I<sup>2</sup>C register containing return arguments (aside from incrementing RESPONSE0).

- PARAM\_SET results in the write data being copied in to I2C RESPONSE1 register.

- PARAM\_QUERY results in read data in the I2C RESPONSE1 register.

### Table 5.1. Command Summary

| Command Register Commands                                                                                                                                                               | Code       | Input to Sensor | Output of Sensor   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------|--------------------|

| RESET_CMD_CTR                                                                                                                                                                           | 0x00       |                 |                    |

| Resets RESPONSE0 CMMND_CTR field to 0.                                                                                                                                                  |            |                 |                    |

| RESET_SW                                                                                                                                                                                | 0x01       |                 |                    |

| Forces a Reset, Resets RESPONSE0 CMMND_CTR field to 0xXXX01111.                                                                                                                         |            |                 |                    |

| FORCE                                                                                                                                                                                   | 0x11       |                 |                    |

| Initiates a set of measurements specified in CHAN_LIST parameter. A FORCE command will only execute the measurements which do not have a meas counter index configured in MEAS-CONFIGX. |            |                 |                    |

| PAUSE                                                                                                                                                                                   | 0x12       |                 |                    |

| Pauses autonomous measurements specified in CHAN_LIST.                                                                                                                                  |            |                 |                    |

| START                                                                                                                                                                                   | 0x13       |                 |                    |

| Starts autonomous measurements specified in CHAN_LIST. A START autonomous command will only start the measurements which has a counter index selected in MEASCONFIGx.                   |            |                 |                    |

| PARAM_QUERY                                                                                                                                                                             | 0b01xxxxxx |                 | RESPONSE1 = result |

| Reads Parameter xxxxxx and store results in RE-SPONSE1.xxxxxx is a 6 bit Address Field (64 bytes).                                                                                      |            |                 |                    |

| PARAM_SET                                                                                                                                                                               | 0b10xxxxxx | INPUT0          | RESPONSE1 = INPUT0 |

| Writes INPUT0 to the Parameter xxxxxxxxxxx is a 6 bit Address Field (64 bytes).                                                                                                         |            |                 |                    |

### Notes:

- 1. The successful completion of all commands except RESET\_CMD\_CTR and RESET\_SW causes an increment of the CMD\_CTR field of the RESPONSE0 register (bits [3:0].

- 2. Resets RESPONSE0 CMMND\_CTR field to 0.

- 3. Forces a Reset, Resets RESPONSE0 CMMND\_CTR field to 0xXXX01111.

- 4. Uses CHAN\_LIST in Parameter Space.

- 5. "xxxxxx" is a 6-bit Address Field (64 bytes).

#### 5.3.1 Accessing the Parameter Table (PARAM\_QUERY & PARAM\_SET Commands)

The parameter table is written to by writing the INPUT\_0 I2C register and the PARAM\_SET command byte to the Command I<sup>2</sup>C register. The format of the PARAM\_SET word is such that the 6 LSBits contain the location of the target byte in the parameter table.

**Example:** To transfer 0xA5 to parameter table location 0b010101.

Read RESPONSE0 (address 0x11) and store the CMMND CTR field.

Write 0xA5 to INPUT0 (address 0x0A).

Write 0b10010101 to COMMAND (address 0x0B).

Read RESPONSE0 (address 0x11) and check if the CMMND\_CTR field incremented.

If there is no increment or error, repeat the "read the RESPONSE0" step until the CMMND\_CTR has incremented. If there is an error send a RESET or a RESET CMD CTR command.

The two write commands (to INPUT0 and COMMAND) can be in the same I<sup>2</sup>C transaction.

**Example:** To read data from the parameter table location 0b010101.

Read the RESPONSE0 (address 0x11) and store the CMMND CTR field.

Write 0b01010101 to the COMMAND (address 0x0B).

Read RESPONSE0 (address 0x11) and check if the CMMND CTR field incremented.

If there is no increment or error, repeat the "read RESPONSE0" step until the CMMND CTR has incremented.

Read RESPONSE1 (address 0x10) this gives the read result. If there is an error send RESET or a RESET CMD CTR com-

mand.

The last two read commands (from RESPONSE0 and RESPONSE1) should not be in the same I<sup>2</sup>C transaction.

#### 5.3.2 Sensor Operation Initiation Commands

The FORCE, PAUSE, and START commands make use of the information in CHAN\_LIST. Configure CHAN\_LIST prior to using any of these commands.

#### 5.3.3 RESET\_CMD\_CTR Command

Resets RESPONSE0 CMMND\_CTR field and does nothing else.

#### 5.3.4 RESET Command

Resets the sensor and puts it into the same state as when powering up. The parameter table and all  $I^2C$  registers are reset to their default values.

### 5.4 I<sup>2</sup>C Register Summary

The content of the three MSBits of Response0 after reset will depend on the running state (see the Response0 write up).

Table 5.2. I2C Registers

| Register Name | I2C Address | Direction WRT<br>Host | Function                                                                                                                       | Value after Reset<br>(Hard or Soft) | Direction WRT Sensor |

|---------------|-------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------|

| PART_ID       | 0x00        | IN                    | Returns DEVID                                                                                                                  | PART_ID                             | OUT                  |

|               |             |                       | (0x51 for the Si1151,                                                                                                          |                                     |                      |

|               |             |                       | 0x52 for the Si1152,                                                                                                           |                                     |                      |

|               |             |                       | 0x53 for the Si1153)                                                                                                           |                                     |                      |

| HW_ID         | 0x01        | IN                    | Returns Hardware ID.                                                                                                           | HW_ID                               | OUT                  |

| REV_ID        | 0x02        | IN                    | Hardware Rev<br>(0xMN).                                                                                                        | REV_ID                              | OUT                  |

| HOSTIN0       | 0x0A        | IN/OUT                | Data for parameter table on PAR-AM_SET write to COMMAND register.                                                              | 0x00                                | IN                   |

| COMMAND       | 0x0B        | IN/OUT                | Initiated action in<br>Sensor when specif-<br>ic codes written<br>here.                                                        | 0x00                                | IN                   |

| IRQENABLE     | 0x0F        | IN/OUT                | The six least significant bits enable Interrupt Operation.                                                                     | 0x00                                | IN                   |

| RESPONSE1     | 0x10        | IN                    | Contains the read-<br>back value from a<br>param query or a<br>param set com-<br>mand.                                         | 0x00                                | IN/OUT               |

| RESPONSE0     | 0x11        | IN                    | The 5 <sup>th</sup> MSB of the counter is an error indicator, with the 4 LSBits indicating the error code when the MSB is set. | 0xXXXX1111                          | IN/OUT               |

| IRQ_STATUS    | 0x12        | IN                    | The six least significant bits show the interrupt status.                                                                      | 0x00                                | IN/OUT               |

| HOSTOUT0      | 0x13        | IN                    | Captured Sensor                                                                                                                | 0x00                                | IN/OUT               |

| to            | to          | 114                   | Data.                                                                                                                          | 0,000                               | 110,001              |

| HOSTOUT25     | 0x2C        |                       |                                                                                                                                |                                     |                      |

### 5.4.1 PART\_ID

### I2C Address = 0x00;

Contains Part ID, e.g., 0x53 for Si115x.

### 5.4.2 HW\_ID

### I2C Address = 0x01;

Contains the Hardware information.

BITS4:0 = Filter, LED & Module code

BITS7:5 = Silicon HW rev (Steps with silicon mask change)

| Part Number | Features                         | BITS4:0 code |

|-------------|----------------------------------|--------------|

| Si1151-AB00 | 1 LED driver                     | 0x03         |

| Si1151-AB09 | 940 nm filter with 1 LED driver  | 0x04         |

| Si1152-AB00 | 2 LED drivers                    | 0x05         |

| Si1152-AB09 | 940 nm filter with 2 LED drivers | 0x06         |

| Si1153-AB00 | 3 LED drivers                    | 0x00         |

| Si1153-AB09 | 940 nm filter                    | 0x01         |

| Si1153-ABX9 | Module with 940 nm filter & LED  | 0x02         |

### 5.4.3 REV\_ID

#### I2C Address = 0x02;

Contains the product revision, in a 0xMN format where "M" is the major rev and "N" the minor rev.

**Table 5.3.**

| Part Number | Major Revision | Minor Revision | REV_ID |

|-------------|----------------|----------------|--------|

| Si115x-AAxx | 1              | 0              | 0x10   |

| Si115x-ABxx | 1              | 1              | 0x11   |

#### 5.4.4 INFO0

### I2C Address = 3;

Contains 0 after a hard reset or a RESET Command.

#### 5.4.5 INFO1

### I2C Address = 4;

Contains 0 after a hard reset or a RESET Command.

#### **5.4.6 HOSTIN0**

| Name    |             |  |  |  | I2C Address |  |  |  |  |

|---------|-------------|--|--|--|-------------|--|--|--|--|

| HOSTIN0 |             |  |  |  | 0x0A        |  |  |  |  |

| Bit     | Bit 7 6 5 4 |  |  |  | 4 3 2 1 0   |  |  |  |  |

| Name    | HOSTIN0     |  |  |  |             |  |  |  |  |

| Туре    | R/W         |  |  |  |             |  |  |  |  |

| Reset   | 0           |  |  |  |             |  |  |  |  |

| Bit | Name    | Function                                                         |

|-----|---------|------------------------------------------------------------------|

| 7:0 | HOSTIN0 | This Register is the Input to the Sensor and Output of the Host. |

Contain 0 after a hard reset or a RESET Command.

#### 5.4.7 COMMAND

### I2C Address = 0x0B;

Contains 0 after a hard reset or a RESET Command.

#### 5.4.8 IRQENABLE

### I2C Address = 0x0F;

Contains 0 after a hard reset or a RESET Command.

### 5.4.9 RESPONSE1

#### I2C Address = 0x10;

| Bit   | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----------------|---|---|---|---|---|---|---|

| Name  | RESPONSE1[7:0] |   |   |   |   |   |   |   |

| Туре  | R              |   |   |   |   |   |   |   |

| Reset | 0              | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | Name           | Function                                                                                                                                                                                                    |

|-----|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | RESPONSE1[7:0] | The sensor mirrors the data byte written to the parameter table here for the user to verify the write was successful.  A parameter read command results in the byte read being available here for the host. |

### 5.4.10 RESPONSE0

### I2C Address = 0x11;

| Bit   | 7       | 6       | 5     | 4       | 3            | 2 | 1 | 0 |

|-------|---------|---------|-------|---------|--------------|---|---|---|

| Name  | RUNNING | SUSPEND | SLEEP | CMD_ERR | CMD_CTR[4:0] |   |   |   |

| Туре  | R       | R       | R     | R       | R            | R | R | R |

| Reset | N/A     | N/A     | N/A   | 0       | 1            | 1 | 1 | 1 |

| Bit | Name      |                            |                                                                                                                                                                                                                                                                                                             | Function                                                                                                              |  |  |

|-----|-----------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| 7   | RUNNING   | Indicator of MCU state.    | Indicator of MCU state.                                                                                                                                                                                                                                                                                     |                                                                                                                       |  |  |

| 6   | SUSPEND   | Indicator of MCU state.    |                                                                                                                                                                                                                                                                                                             |                                                                                                                       |  |  |

| 5   | SLEEP     | Indicator of MCU state.    |                                                                                                                                                                                                                                                                                                             |                                                                                                                       |  |  |

| 4   | CMD_ERR   | It is cleared by a hardwar | re reset (power up                                                                                                                                                                                                                                                                                          | o) or a RESET command or a RESET_CMD_CTR.                                                                             |  |  |

|     |           | It is set by a bad comman  | nd. E.g., an attem                                                                                                                                                                                                                                                                                          | pt to write beyond the parameter table.                                                                               |  |  |

|     |           | If it is set, the CMMND_C  | CTR field is the en                                                                                                                                                                                                                                                                                         | ror code.                                                                                                             |  |  |

| 3:0 | CMMND_CTR | IF CMD_ERR = 0             | A counter that increments on every GOOD command (success I <sup>2</sup> C Command Register write and sensor execution of the command).  It is reset to 0 by the RESET_CMD_CTR command.  It is set to 0b1111 on Power Up or a RESET command. This is a user can detect a fresh SW reset or a power up event. |                                                                                                                       |  |  |

|     |           | IF CMD_ERR = 1             | Code                                                                                                                                                                                                                                                                                                        | Meaning                                                                                                               |  |  |

|     |           |                            | 0x10                                                                                                                                                                                                                                                                                                        | Invalid command.                                                                                                      |  |  |

|     |           |                            | 0x11                                                                                                                                                                                                                                                                                                        | Parameter access to an invalid location.                                                                              |  |  |

|     |           |                            | 0x12 Saturation of the ADC or overflow of accumu                                                                                                                                                                                                                                                            |                                                                                                                       |  |  |

|     |           |                            | 0x13                                                                                                                                                                                                                                                                                                        | Output buffer overflow—this can happen when Burst mode is enabled and configured for greater than 26 bytes of output. |  |  |

The RESPONSE0 register will show "RUNNING" immediately after reset and then "SLEEP" after initialization is complete.

### 5.4.11 IRQ\_STATUS

### I2C Address = 0x12;

| Bit   | 7  | 6  | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|----|----|------|------|------|------|------|------|

| Name  | _  | _  | IRQ5 | IRQ4 | IRQ3 | IRQ2 | IRQ1 | IRQ0 |

| Туре  | RS | VD | CR   | CR   | CR   | CR   | CR   | CR   |

| Reset |    |    | 0    | 0    | 0    | 0    | 0    | 0    |

| Bit | Name   | Function                                         |

|-----|--------|--------------------------------------------------|

| 7:6 | UNUSED | Unused. Read = 00b; Write = Don't Care.          |

| 5   | IRQ5   | Enables an IRQ for channel 5 result being ready. |

| 4   | IRQ4   | Enables an IRQ for channel 4 result being ready. |

| 3   | IRQ3   | Enables an IRQ for channel 3 result being ready. |

| 2   | IRQ2   | Enables an IRQ for channel 2 result being ready. |

| 1   | IRQ1   | Enables an IRQ for channel 1 result being ready  |

| 0   | IRQ0   | Enables an IRQ for channel 0 result being ready. |

### 5.4.12 HOSTOUTx

This section covers the twenty-six I2C Host Output Registers. These registers are the output of the sensor and input to the host.

| Name      | I2C Address |

|-----------|-------------|

| HOSTOUT0  | 0x13        |

| to        | to          |

| HOSTOUT25 | 0x2C        |

| Bit   | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----------|---|---|---|---|---|---|---|

| Name  | HOSTOUTx |   |   |   |   |   |   |   |

| Туре  | R        |   |   |   |   |   |   |   |

| Reset | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | HOSTOUTX | These registers are the output of the MCU and input to the host. The results of the CHAN_LIST enabled "active channel" readings are located sequentially in this table. Each channel may use 2 or 3 bytes depending on the setup.  The validity of the various channel outputs located in this table is determined by other factors. Data is valid when an IRQ status says that it is and remains valid until another reading happens. This is why it is imperative to service the interrupt before the next measurement cycle begins (Autonomous Mode), unless forced mode is used. |

### 6. Measurement: Principle of Operation

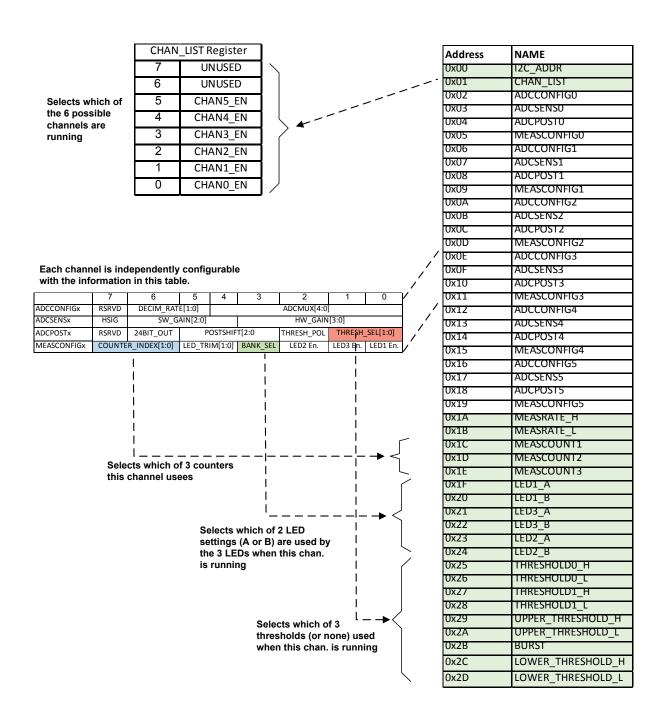

Operation is based on the concept of channels. Channels are essentially tasks that have been setup by the user.

To setup these channels, the channel specific areas of the parameter table need to be loaded with the correct information as well as the global area of this table.

The channels' specific areas are described below, including:

- · ADC gain

- · The photodiode selected

- · The counter selected to time

- · How often to make a measurement

- . The format of the output (16 vs. 24 bits)

- · And other areas

The global area includes global information that affects all tasks, such as:

- · The list of channels that are enabled.

- The setup of the two counters that can be used by the channels.

- The two light thresholds that can be selected from by the channels.

- The setup of the threshold window that can be used by the channels.

The list of channels, CHAN\_LIST, in the global area determines what operations are run and how the results are packed in the output fields.

The packing of the result data in the output fields is totally determined by the enabled channels as they are packed sequentially from the lowest enabled channel to the highest in the output field (I2C space- HOSTOUT0 to HOSTOUT25). The amount of space used by each channel is determined by the 16 vs. 24 bit selection made in the channel setup.

Although space in the output buffer is reserved by the CHAN\_LIST, the data validity is determined by the IRQ\_STATUS register in Autonomous Mode and by elapsed time in Forced Mode. In Burst Mode, a subset of Autonomous Mode, all the expected data is valid.

#### 6.1 Output Field Utilization

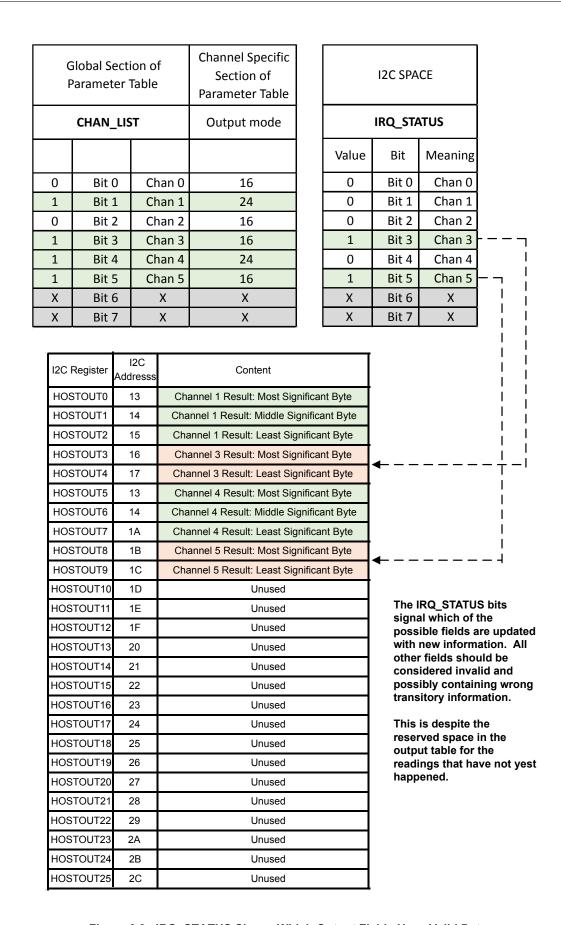

In all modes, the CHAN\_LIST configuration determines how the data is stacked in the 26 byte output field. It is done on a first-come first-served basis, with the enabled lower channels taking up the lower addresses. When burst is enabled, the channel arrangement is just repeated to higher and higher addresses. See the example below.

|   | ilobal Secti<br>arameter T | Channel Specific<br>Section of<br>Parameter Table |    |

|---|----------------------------|---------------------------------------------------|----|

|   | CHAN_LI                    | Output mode                                       |    |

|   |                            |                                                   |    |

| 0 | Bit 0                      | Chan 0                                            | 16 |

| 1 | Bit 1                      | Chan 1                                            | 24 |

| 0 | Bit 2                      | Chan 2                                            | 16 |

| 1 | Bit 3                      | Chan 3                                            | 16 |

| 1 | Bit 4                      | Chan 4                                            | 24 |

| 1 | Bit 5                      | Chan 5                                            | 16 |

| Χ | Bit 6                      | Х                                                 | Х  |

| Х | Bit 7                      | Х                                                 | X  |

| I2C Register | I2C<br>Addresss | Content                                   |

|--------------|-----------------|-------------------------------------------|

| HOSTOUT0     | 13              | Channel 1 Result: Most Significant Byte   |

| HOSTOUT1     | 14              | Channel 1 Result: Middle Significant Byte |

| HOSTOUT2     | 15              | Channel 1 Result: Least Significant Byte  |

| HOSTOUT3     | 16              | Channel 3 Result: Most Significant Byte   |

| HOSTOUT4     | 17              | Channel 3 Result: Least Significant Byte  |

| HOSTOUT5     | 13              | Channel 4 Result: Most Significant Byte   |

| HOSTOUT6     | 14              | Channel 4 Result: Middle Significant Byte |

| HOSTOUT7     | 1A              | Channel 4 Result: Least Significant Byte  |

| HOSTOUT8     | 1B              | Channel 5 Result: Most Significant Byte   |

| HOSTOUT9     | 1C              | Channel 5 Result: Least Significant Byte  |

| HOSTOUT10    | 1D              | Unused                                    |

| HOSTOUT11    | 1E              | Unused                                    |

| HOSTOUT12    | 1F              | Unused                                    |

| HOSTOUT13    | 20              | Unused                                    |

| HOSTOUT14    | 21              | Unused                                    |

| HOSTOUT15    | 22              | Unused                                    |

| HOSTOUT16    | 23              | Unused                                    |

| HOSTOUT17    | 24              | Unused                                    |

| HOSTOUT18    | 25              | Unused                                    |

| HOSTOUT19    | 26              | Unused                                    |

| HOSTOUT20    | 27              | Unused                                    |

| HOSTOUT21    | 28              | Unused                                    |

| HOSTOUT22    | 29              | Unused                                    |

| HOSTOUT23    | 2A              | Unused                                    |

| HOSTOUT24    | 2B              | Unused                                    |

| HOSTOUT25    | 2C              | Unused                                    |

Packing of of these four channels in the output table is determined by the four enabled channels in the CHANNEL list above. This is independent of the IRQ\_ENABLE and IRQ\_STATUS

Figure 6.1. Output Table Data Packing

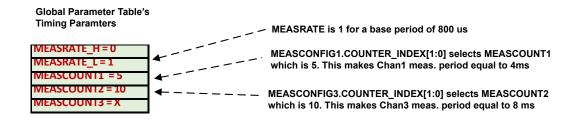

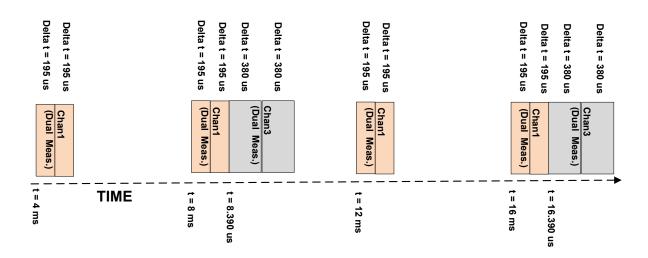

#### 6.2 Autonomous and Forced Modes