# 1 Orderable parts

This section describes the part numbers available to be purchased along with their differences. Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to <a href="http://www.nxp.com">http://www.nxp.com</a> and perform a part number search for the following device numbers.

Table 1. Orderable part variations

| Part number                                                             | Temperature (T <sub>A</sub> ) | Package             | Description                                                                                                                                                                                                                                           | Notes |  |  |  |

|-------------------------------------------------------------------------|-------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|

| 34SB0800 octal valves and pump controller system on chip for industrial |                               |                     |                                                                                                                                                                                                                                                       |       |  |  |  |

| MC34SB0800AE                                                            | -40 °C to 125 °C              | 10 x 10, 64 LQFP-EP | <ul> <li>Four PWMed valve controls and four current regulated valve controls</li> <li>Safe switch control</li> <li>Pump motor control up to 500 Hz</li> <li>High-side driver for general purpose</li> <li>Low-side FET for resistive loads</li> </ul> | (1)   |  |  |  |

#### Notes

1. To order parts in Tape & Reel, add the R2 suffix to the part number.

# **Table of Contents**

| 1 | Orderable parts                        | . 2 |

|---|----------------------------------------|-----|

| 2 | Internal block diagram                 | . 4 |

| 3 | Pin connections                        | . 5 |

|   | 3.1 Pinout diagram                     | . 5 |

|   | 3.2 Pin definitions                    | . 6 |

| 4 | General product characteristics        | . 8 |

|   | 4.1 Maximum ratings                    | . 8 |

|   | 4.2 Operating conditions               | . 9 |

|   | 4.3 Supply currents                    | 10  |

|   | 4.4 Thermal ratings                    | 10  |

|   | 4.5 Logical inputs and outputs         | 11  |

| 5 | General description                    | 12  |

|   | 5.1 Block diagram                      | 12  |

|   | 5.2 Functional description             | 12  |

|   | 5.3 Features                           | 12  |

| 6 | Functional block description           | 14  |

|   | 6.1 Error handling                     | 14  |

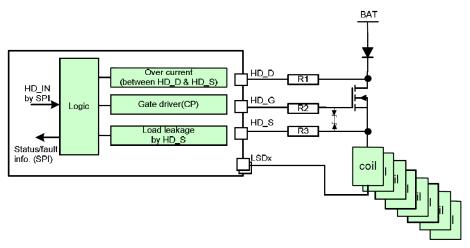

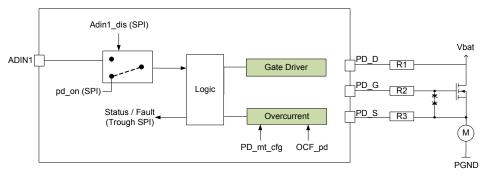

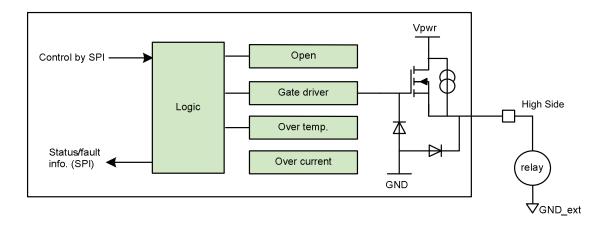

|   | 6.2 High-side driver                   | 16  |

|   | 6.3 Pump motor pre-driver              | 17  |

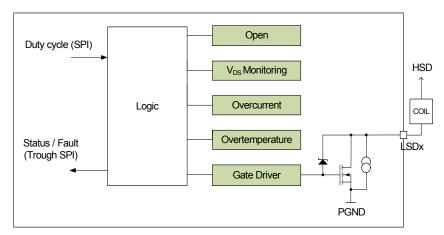

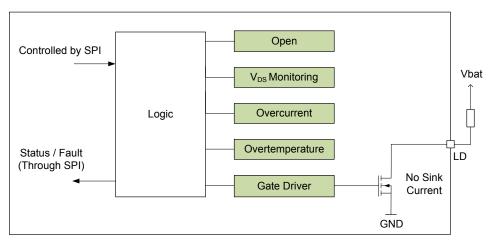

|   | 6.4 Low-side driver                    | 19  |

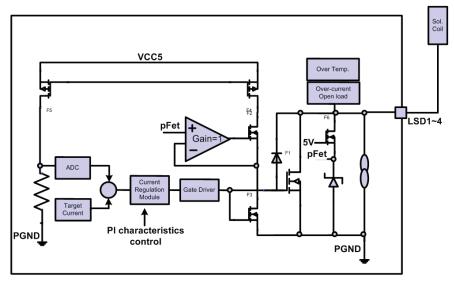

|   | 6.5 Low-side driver for resistive load | 24  |

|   | 6.6 Analog to digital converter (x3ch) | 26  |

|   | 6.7 High-side                          | 27  |

|   | 6.8 Monitoring module                  | 29  |

|   | 6.9 Supervision                        | 31  |

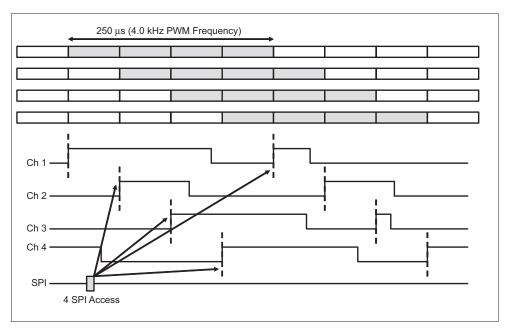

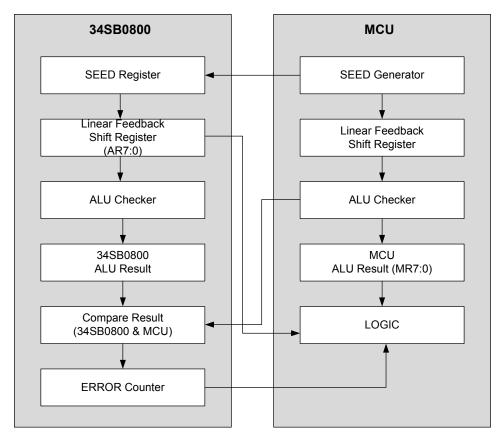

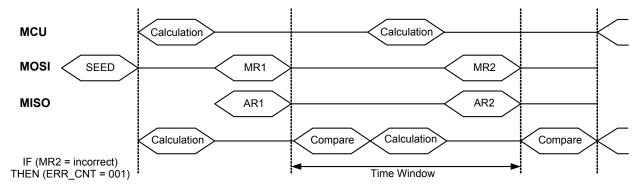

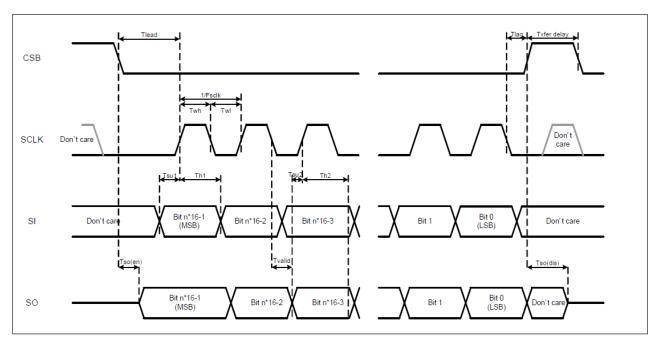

|   | 6.10 SPI and data register             | 37  |

| 7 | Typical applications                   | 62  |

|   | 7.1 Application diagrams               | 62  |

| 8 | Packaging                              | 63  |

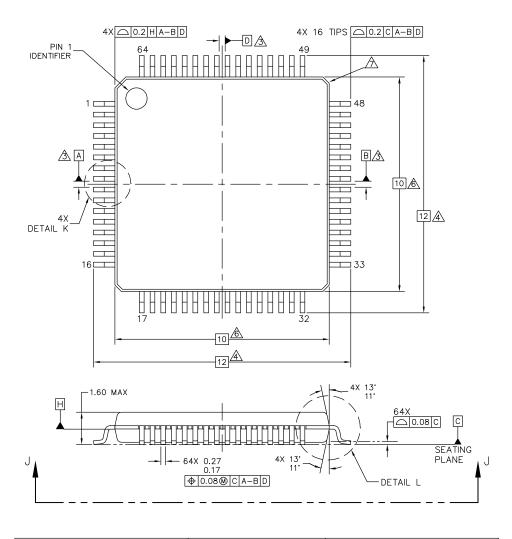

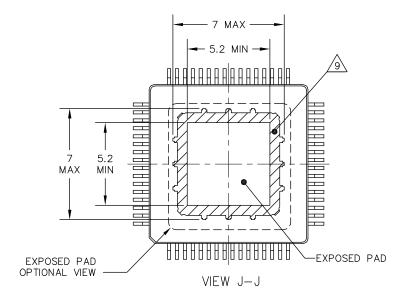

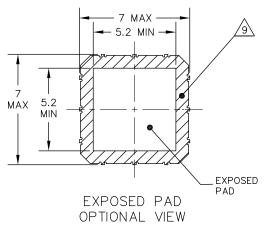

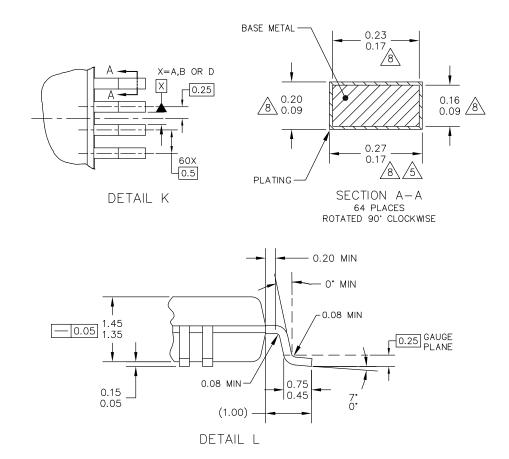

|   | 8.1 Package mechanical dimensions      | 63  |

| 0 | Povision history                       | 67  |

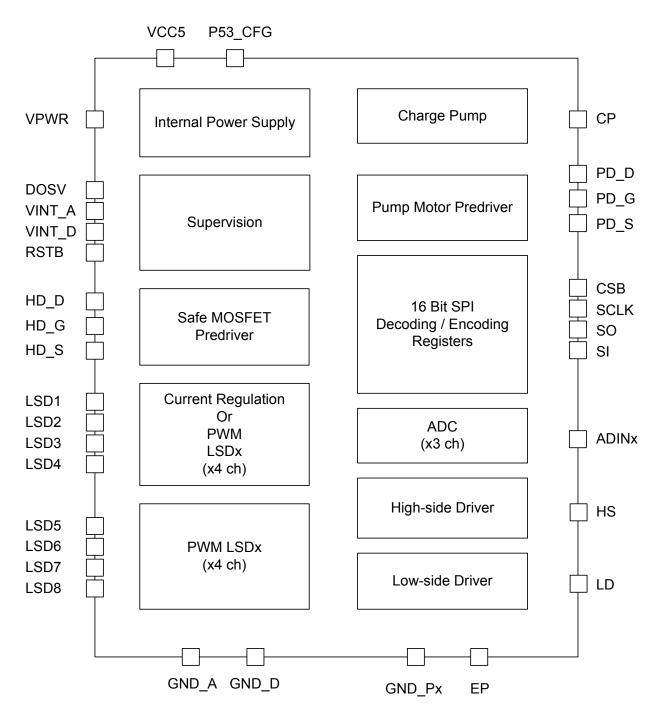

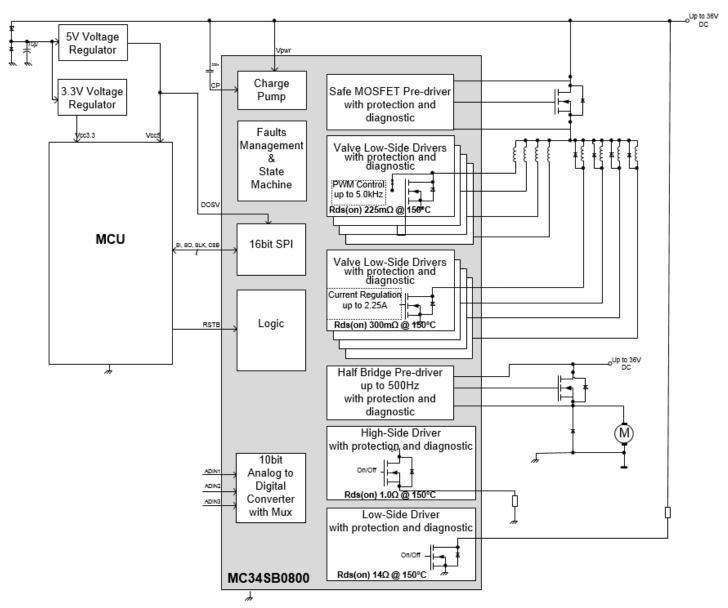

# 2 Internal block diagram

Figure 2. SB0800 simplified internal block diagram

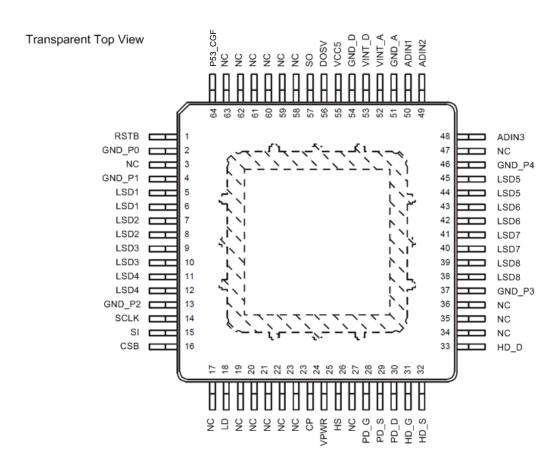

# 3 Pin connections

# 3.1 Pinout diagram

Figure 3. SB0800 64-pin LQFP-EP pinout diagram

# 3.2 Pin definitions

Table 2. SB0800 pin definitions

| Pin<br>number         | Pin name | Pin function                                         | Definition                                                                            | DOSV = 5.0 V | DOSV = 3.3 V | Notes |

|-----------------------|----------|------------------------------------------------------|---------------------------------------------------------------------------------------|--------------|--------------|-------|

| 1                     | RSTB     | Reset                                                | Reset PIN                                                                             | externa      | pull-up      |       |

| 2                     | GND_P0   | Supply                                               | Power Ground 0 <sup>(4)</sup>                                                         | no           | no           |       |

| 4                     | GND_P1   | Supply                                               | Power Ground 1                                                                        | no           | no           | (4)   |

| 5, 6                  | LSD1     | Low-side Driver for Current Regulated & PWMed Valves | Open Drain Output for Low-side Driver 1                                               | no           | no           | (2)   |

| 7, 8                  | LSD2     | Low-side Driver for Current Regulated & PWMed Valves | Open Drain Output for Low-side Driver 2                                               | no           | no           | (2)   |

| 9, 10                 | LSD3     | Low-side Driver for Current Regulated & PWMed Valves | Open Drain Output for Low-side Driver 3                                               | no           | no           | (2)   |

| 11, 12                | LSD4     | Low-side Driver for Current Regulated & PWMed Valves | Open Drain Output for Low-side Driver 4                                               | no           | no           | (2)   |

| 13                    | GND_P2   | Supply                                               | Power Ground 2                                                                        | no           | no           | (4)   |

| 14                    | SCLK     | SPI                                                  | SPI Interface Clock Input                                                             | no           | no           |       |

| 15                    | SI       | SPI                                                  | SPI Interface Digital Input                                                           | no           | no           |       |

| 16                    | CSB      | SPI                                                  | SPI Interface Chip Interface                                                          | no           | no           |       |

| 18                    | LD       | Low-side Driver                                      | Open Drain Output for Low-side                                                        | no           | no           |       |

| 24                    | СР       | Charge Pump                                          | Charge Pump Output. For internal use, connect a storage capacitor of > 68 nF to VPWR. | no           | no           |       |

| 25                    | VPWR     | Supply                                               | Supply PIN connect to battery through reverse diode                                   | no           | no           |       |

| 26                    | HS       | High-side Driver for General Purpose (optional)      | High-side driver for general purpose                                                  | no           | no           |       |

| 28                    | PD_G     | Motor Pump Driver                                    | Gate Output to Control Pump Motor FET Connect to gate of external pump motor FET      | no           | no           |       |

| 29                    | PD_S     | Motor Pump Driver                                    | Source Feedback Pump Motor FET Connect to source of external pump motor FET           | no           | no           |       |

| 30                    | PD_D     | Motor Pump Driver                                    | Drain Feedback Pump Motor FET Connect to drain of external pump motor FET             | no           | no           |       |

| 31                    | HD_G     | High-side Driver for Valve's Fail-safe FET           | Gate Output to Control High-side FET Connect to gate of external pump motor FET       | no           | no           |       |

| 32                    | HD_S     | High-side Driver for Valve's Fail-safe FET           | Source Feedback High-side FET Connect to source of external High-side FET             | no           | no           |       |

| 33                    | HD_D     | High-side Driver for Valve's Fail-safe FET           | Drain Feedback High-side FET Connect to drain of external High-side FET               | no           | no           |       |

| 37                    | GND_P3   | Supply                                               | Power Ground 3                                                                        | no           | no           | (4)   |

| 38, 39 <sup>(2)</sup> | LSD8     | Low-side Driver for PWMed Valves                     | Open Drain Output for Low-side Driver 8                                               | no           | no           |       |

| 40, 41 (2)            | LSD7     | Low-side Driver for PWMed Valves                     | Open Drain Output for Low-side Driver 7 no no                                         |              | no           |       |

| 42, 43 <sup>(2)</sup> | LSD6     | Low-side Driver for PWMed Valves                     | On an Paris Outrat ford any side Privat C                                             |              | no           |       |

| 44, 45 <sup>(2)</sup> | LSD5     | Low-side Driver for PWMed Valves                     | Open Drain Output for Low-side Driver 5                                               | no           | no           |       |

| 46                    | GND_P4   | Supply                                               | Power Ground 4                                                                        | no           | no           | (4)   |

| 48                    | ADIN3    | ADC                                                  | Analog to Digital Input 3                                                             | no           | no           | (+)   |

| 70                    | ADINO    |                                                      |                                                                                       | 110          | 110          |       |

Table 2. SB0800 pin definitions (continued)

| Pin<br>number                            | Pin name | Pin function      | Definition                                                | DOSV = 5.0 V | DOSV = 3.3 V | Notes |

|------------------------------------------|----------|-------------------|-----------------------------------------------------------|--------------|--------------|-------|

| 49                                       | ADIN2    | ADC               | Analog to Digital Input 2                                 | no           | no           |       |

| 50                                       | ADIN1    | ADC               | Analog to Digital Input 1                                 | no           | no           |       |

| 51                                       | GND_A    | Supply            | Analog Ground                                             | no           | no           |       |

| 52                                       | VINT_A   | Internal Function | 2.5 V internal supply for analog                          | no           | no           | (2)   |

| 53                                       | VINT_D   | Internal Function | 2.5 V internal supply for digital                         | no           | no           | (2)   |

| 54                                       | GND_D    | Supply            | Digital Ground                                            | no           | no           |       |

| 55                                       | VCC5     | Supply            | 5.0 V Supply PIN                                          | 5V           | 5V           |       |

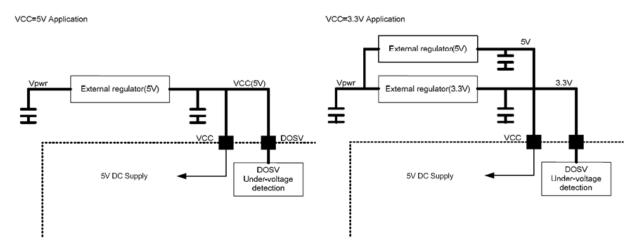

| 56                                       | DOSV     | Supply            | Digital Output Voltage Supply, DOSV under voltage reset   | 5V           | 3.3V         |       |

| 57                                       | SO       | SPI               | SPI Interface Digital Output                              | DOSV         | / bias       |       |

| 64                                       | P53_CFG  | Supply            | Input to select output voltage at DOSV (5.0 V/ 3.3 V) no  |              | no           |       |

| 20, 21, 22,<br>23, 58, 59,<br>60, 61, 62 | NC       | Not connected     | Pin used for production tests and must not be grounded no |              | no           |       |

| 3, 17, 19,<br>27, 34, 35,<br>36, 47, 63  | NC       | Not connected     | Pin used for production tests and must be grounded no no  |              | no           |       |

| Exposed pad                              | GND_P5   | Supply            | Power Ground 5 no no                                      |              | no           | (4)   |

#### Notes

- 2. Pins must be shorted together

- 3. 220 nF/10 V capacitor needed

- 4. All GND\_Px pins must be shorted together at the PCB level.

#### **General product characteristics** 4

#### **Maximum ratings** 4.1

Table 3. Maximum ratings

Voltage parameters are absolute voltages referenced to GND\_A, GND\_D and flag (tied together internally). Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol               | Description (rating)                        | Min.                             | Max.                           | Unit | Notes |

|----------------------|---------------------------------------------|----------------------------------|--------------------------------|------|-------|

| Supply               |                                             |                                  |                                |      |       |

| V <sub>VPWR</sub>    | Analog Power supply voltage                 | -0.3                             | 40                             | V    |       |

| V <sub>DOSV</sub>    | Digital Output Supply Voltage               | -0.3                             | 7.0                            | V    |       |

| V <sub>P53_CFG</sub> | Selection of 5.0 V or 3.3 V for the digital | -0.3                             | 7.0                            | V    |       |

| V <sub>VCC5</sub>    | Digital power supply voltage                | -0.3                             | 7.0                            | V    |       |

| V <sub>GND_A</sub>   | Ground analog                               | -0.3                             | 0.3                            | V    |       |

| V <sub>GND_D</sub>   | Ground digital                              | -0.3                             | 0.3                            | V    |       |

| V <sub>GND_P</sub>   | Ground exposed pad                          | -0.3                             | 0.3                            | V    |       |

| Internal function    | 1                                           |                                  |                                |      |       |

| V <sub>VINT_A</sub>  | Internal regulator analog power supply      | -0.3                             | 3.0                            | V    |       |

| V <sub>VINT_D</sub>  | Internal regulator digital power supply     | -0.3                             | 3.0                            | V    |       |

| Charge pump          |                                             |                                  |                                |      |       |

| V <sub>CP</sub>      | Internal charge pump                        | -0.3 or<br>V <sub>PWR</sub> -0.3 | V <sub>PWR</sub> +15           | V    |       |

| High-side driver     | r for general purpose                       | •                                |                                |      | •     |

| $V_{HS}$             | High-side driver                            | -0.3                             | 40 or V <sub>PWR</sub><br>+0.3 | V    |       |

| High-side driver     | r for valve's fail-safe FET                 | -                                |                                |      |       |

| $V_{HD\_G}$          | Gate of the high-side predriver             | -20                              | 55                             | V    |       |

| V <sub>HD_S</sub>    | Source of the high-side predriver           | -0.3                             | 40                             | V    |       |

| V <sub>HD_D</sub>    | Drain of the high-side predriver            | -0.3                             | 40                             | V    |       |

| Motor pump driv      | ver                                         |                                  |                                |      |       |

| V <sub>PD_G</sub>    | Gate of the Motor Pump predriver            | -0.3                             | 55                             | V    |       |

| V <sub>PD_S</sub>    | Source of the Motor Pump predriver          | -0.3                             | 40                             | V    |       |

| V <sub>PD_D</sub>    | Drain of the Motor Pump predriver           | -0.3                             | 40                             | V    |       |

| Reset                |                                             | ,                                | · '                            |      |       |

| V <sub>RSTB</sub>    | Reset pin                                   | -0.3                             | 7.0                            | V    |       |

| A to D converte      | r                                           | <u>.</u>                         |                                |      |       |

| V <sub>ADINx</sub>   | Input analog to digital                     | -0.3                             | 7.0                            | V    |       |

#### Table 3. Maximum ratings (continued)

Voltage parameters are absolute voltages referenced to GND\_A, GND\_D and flag (tied together internally). Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                 | Description (rating)                                              | Min.         | Max.         | Unit | Notes |

|------------------------|-------------------------------------------------------------------|--------------|--------------|------|-------|

| PI                     |                                                                   | 1            | l            |      | 1     |

| V <sub>SO</sub>        | Serial peripheral interface slave output                          | -0.3         | DOSV +0.3    | V    |       |

| V <sub>SI</sub>        | Serial peripheral interface slave input                           | -0.3         | 7.0          | ٧    |       |

| V <sub>CSB</sub>       | Serial peripheral interface chip select                           | -0.3         | 7.0          | V    |       |

| V <sub>SCLK</sub>      | Serial peripheral interface clock                                 | -0.3         | 7.0          | ٧    |       |

| ow-side driver         | for valves (LSD1-8)                                               | <u>.</u>     | <u>'</u>     |      | •     |

| V <sub>LSDx</sub>      | Low-side driver for valves                                        | <u>Table</u> | active clamp |      |       |

| ow-side driver         | •                                                                 | •            |              |      | •     |

| $V_{LD}$               | Low-side driver                                                   | -100 mA      | 40           | V    |       |

| nergy capabilit        | ty                                                                | •            |              |      | •     |

| E <sub>LSD1—4</sub>    | Energy capability (EAR) at 125 °C • LSD1—4, with 20 mH load       | _            | 30           | mJ   |       |

| E <sub>LSD5—8</sub>    | Energy capability (EAR) at 125 °C • LSD5—8, with 20 mH load       | _            | 40           | mJ   |       |

| E <sub>HS</sub>        | Energy capability (EAR) at 125 °C • HS, with 20 mH load           | _            | 13           | mJ   |       |

| urrents                |                                                                   | 1            | l            |      | 1     |

| I <sub>LSDX(POS)</sub> | Drain continuous current; during on state • LSDx                  | _            | 5.0          | Α    |       |

| I <sub>LSDX(NEG)</sub> | Maximum negative current for 5.0 ms without being destroyed  LSDx | -6.0         | _            | А    |       |

| I <sub>DIG</sub>       | Input current • P53_CFG, SI, CSB, SCLK, RSTB                      | -20          | 20           | mA   |       |

# 4.2 Operating conditions

This section describes the operating conditions and the current consumptions. Conditions apply to all the following data, unless otherwise noted.

#### Table 4. Operating conditions

Voltage parameters are absolute voltages referenced to GND. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol            | Description (rating)                                                                            | Min. | Тур. | Max. | Unit | Notes |

|-------------------|-------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| V <sub>PWR</sub>  | Functional operating supply voltage. Device is fully functional.  • All features are operating  | 6.0  | _    | 36   | V    |       |

| V <sub>CC5</sub>  | Functional operating supply voltage. Device is fully functional.  • All features are operating. | 4.75 | _    | 5.25 | V    |       |

| V <sub>DOSV</sub> | Functional operating supply voltage. Device is fully functional.  • All features are operating. | 3.13 | _    | 5.25 | V    |       |

# 4.3 Supply currents

This section describes the operating conditions and the current consumptions. Conditions apply to all the following data, unless otherwise noted.

#### Table 5. Supply currents

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  36 V, 4.75 V  $\leq$  V<sub>CC5</sub>  $\leq$  5.25 V, 3.13 V  $\leq$  V<sub>DOSV</sub>  $\leq$  5.25 V, -40 °C  $\leq$  T<sub>J</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol             | Description (rating)                                               | Min. | Тур. | Max. | Unit | Notes |

|--------------------|--------------------------------------------------------------------|------|------|------|------|-------|

| VPWR current c     | onsumptions                                                        |      | +    | +    | -    | +     |

| I <sub>QVPWR</sub> | Quiescent current of VPWR measured at 36 V, V <sub>CC5</sub> = 0 V | _    | _    | 30   | μΑ   |       |

| I <sub>VPWR</sub>  | Current of VPWR in operating mode, V <sub>CC5</sub> = 5.0 V        | _    | 20   | _    | mA   |       |

| VCC5 current co    | nsumptions                                                         |      | •    | •    |      |       |

| I <sub>VCC5</sub>  | Current of VCC5 pin in operating mode (SPI frequency at 10 MHz)    | _    | 10   | _    | mA   |       |

| DOSV current co    | POSV current consumptions                                          |      |      |      |      |       |

| I <sub>DOSV</sub>  | Current of DOSV pin in operating mode (SPI frequency at 10 MHz)    | _    | _    | 10   | mA   |       |

# 4.4 Thermal ratings

#### Table 6. Thermal data

| Symbol            | Description (rating)                                                            | Min. | Тур. | Max.   | Unit | Notes  |

|-------------------|---------------------------------------------------------------------------------|------|------|--------|------|--------|

| T <sub>J</sub>    | Operational junction Temperature                                                | -40  | _    | 150    | °C   |        |

| T <sub>STG</sub>  | Storage Temperature                                                             | -65  | _    | 150    | °C   |        |

| $R_{\theta JC}$   | R0JC, Thermal Resistance, Junction to Case (Package exposed pad) - Steady state | _    | _    | 2.0    | °C/W |        |

| T <sub>PPRT</sub> | Peak Package Reflow Temperature During Reflow                                   | _    | _    | Note 7 | °C   | (5)(6) |

#### Notes

- 5. Lead soldering temperature limit is for 10 seconds maximum duration. Lead soldering can be done twice. Device must be delivered in dry pack.

- 6. NXP's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.nxp.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

# 4.5 Logical inputs and outputs

#### Table 7. Logical inputs/outputs

$V_{PWR}$  = 6.0 to 36 V, VCC5 = 4.75 to 5.25 V, DOSV = 3.13 to 5.25 V,  $T_{J}$  = -40 to 125 °C, unless otherwise specified.

| Symbol            | Description (rating)                                                   | Min.       | Max. | Unit | Notes |

|-------------------|------------------------------------------------------------------------|------------|------|------|-------|

| ogical inputs     |                                                                        |            |      |      |       |

| $V_{IH\_X}$       | Input High-voltage • P53_CFG, RSTB, SI, CSB, SCLK, ADIN1, ADIN2, ADIN3 | _          | 2.0  | V    |       |

| $V_{IL_{X}}$      | Input Low-voltage • P53_CFG, RSTB, SI, CSB, SCLK, ADIN1, ADIN2, ADIN3  | 0.8        | _    | V    |       |

| ogical outputs.   |                                                                        |            |      |      |       |

| V <sub>OH_X</sub> | Input High-voltage, with 1.0 mA • SO                                   | 0.8 x DOSV | _    | V    |       |

| $V_{OL\_X}$       | Input Low-voltage, with 1.0 mA • SO                                    | _          | 0.4  | V    |       |

| VOL_RSTB          | RSTB Low-voltage, with 1.0 mA • RSTB                                   | _          | 0.4  | V    |       |

# 5 General description

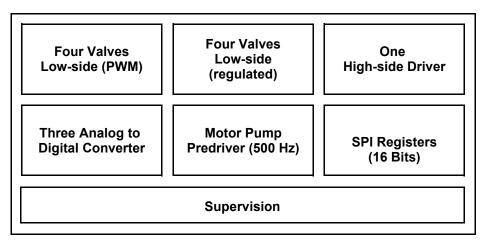

# 5.1 Block diagram

Figure 4. SB0800 functional block diagram

# 5.2 Functional description

The SB0800 device is a valves and pump controller, designed for use in harsh industrial environments, requiring few external components. The SB0800 eight high-current low-side drivers for use with solenoid valves, and high-side gate drivers for controlling two external N-channel MOSFETs for use with a pump motor and master relay for a solenoid coil. In conjunction with this primary functionality, the SB0800 has one low-side driver to control a resistive load. The SB0800 boosts an internal charge-pump, allowing the high-side drivers to use inexpensive N-channel MOSFETs. The digital I/O pins can be configured for both 5.0 V and 3.3 V levels for easy connection to any microprocessor. Also, the device integrated three Analog to Digital converters. The SB0800 uses standard SPI protocol for communication.

### 5.3 Features

This section presents the detailed features of SB0800.

Table 8. Device features set

| Function                                                                                                                                                           | Description                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High-side Driver for Fail-safe FET                                                                                                                                 | High-side Fail-safe FET driver     Overcurrent shutdown     Load leakage detection                                                                                                                                         |

| High-side Driver for general purpose                                                                                                                               | <ul> <li>High-side switch connected to VPWR (1.0 Ω max Rds(on) at 125 °C)</li> <li>Open load detection</li> <li>V<sub>DS</sub> state monitoring</li> <li>Overcurrent shutdown</li> <li>Overtemperature shutdown</li> </ul> |

| Pump Driver  Pump motor driver up to 500 Hz PWM frequency controllable through SPI command or a digital Overcurrent shutdown between external FET drain and source |                                                                                                                                                                                                                            |

Table 8. Device features set (continued)

| Function                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low-side solenoid driver (x4)    | <ul> <li>Solenoid driver (300 mΩ max. R<sub>DS(on)</sub> at 125 °C) works either as current regulator or as PWM</li> <li>Current regulation deviation: ±2.0%</li> <li>Configurable PWM frequency from 3.0 kHz to 5.0 kHz</li> <li>PWM duty cycle 10-bit resolution</li> <li>Open load detection</li> <li>V<sub>DS</sub> state monitoring</li> <li>Overcurrent shutdown</li> <li>Overtemperature shutdown</li> <li>Send current regulation error flag (only for current regulation modules)</li> </ul> |

| Low-side solenoid driver (x4)    | <ul> <li>Solenoid driver (225 mΩ max R<sub>DS(ON)</sub> at 125 °C) are PWM low-side driver</li> <li>Configurable PWM frequency from 3.0 kHz to 5.0 kHz</li> <li>PWM duty cycle resolution 0.39%</li> <li>Open load detection</li> <li>V<sub>DS</sub> state monitoring</li> <li>Overcurrent shutdown</li> <li>Overtemperature shutdown</li> <li>Max switch-off energy 40 mJ</li> </ul>                                                                                                                 |

| Low-side resistive Driver        | <ul> <li>Low-side driver (20 mA max, R<sub>DS(on)</sub> 8.0 Ω)</li> <li>Open load detection</li> <li>V<sub>DS</sub> state monitoring</li> <li>Overcurrent shutdown</li> <li>Overtemperature shutdown</li> </ul>                                                                                                                                                                                                                                                                                       |

| Low-side Driver                  | <ul> <li>Low-side driver (350 mA max, R<sub>DS(on)</sub> 1.0 Ω)</li> <li>Open load detection</li> <li>V<sub>DS</sub> state monitoring</li> <li>Overcurrent shutdown</li> <li>Overtemperature shutdown</li> </ul>                                                                                                                                                                                                                                                                                      |

| Analog to Digital Converter (x3) | <ul> <li>10-bit ADC</li> <li>External ADINx pins</li> <li>Internal voltages and temperature information</li> <li>Allow to control the pump by a MCU</li> <li>Allow to control the low-side resistive driver by a MCU</li> </ul>                                                                                                                                                                                                                                                                       |

| Supervision                      | VINT_x undervoltage (internal regulator) VCC5 & DOSV undervoltage (supply voltage from external) Watchdog fault ALU check counter overflow External reset fault VPWR undervoltage and overvoltage detections Mismatch MAIN-AUX OSC CLK Temperature warning SPI failure Charge pump issue GND supervision                                                                                                                                                                                              |

# 6 Functional block description

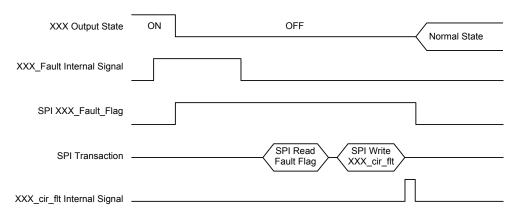

# 6.1 Error handling

Table 9. Error handling

| Type of error                                     | Detection condition              | Action                                                      | Clear SPI flag                                      | Restart condition                                                                        | Notes |

|---------------------------------------------------|----------------------------------|-------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------|-------|

| High-side driver                                  |                                  |                                                             | L                                                   |                                                                                          | I     |

| Overcurrent between external FET Drain and Source | ON                               | HD_G Off + SPI fault flag (HD_oc)                           | Write 1 to HD_clr_flt 1                             | Write 1 to HD_clr_ fit and then turn on by SPI command (hd_ on)                          |       |

| Load leakage                                      | hd_on rise-<br>edge (SPI<br>bit) | Ignore hd_on rise-edge command<br>+ SPI fault flag (HD lkg) | Write 1 to HD_clr_flt                               | Write 1 to HD_clr_flt and then turn on by SPI command (hd_on)                            |       |

| Pump motor PWM driver                             |                                  |                                                             |                                                     |                                                                                          |       |

| Overcurrent between external FET Drain and Source | ON                               | PD_G Off+ SPI fault flag (PD_oc)                            | Write 1 to PD_clr_flt                               | Write 1 to PD_clr_flt and then turn-on by SPI command (pd on)                            |       |

| LSDx                                              |                                  |                                                             |                                                     |                                                                                          | •     |

| Open Load                                         | OFF                              | SPI flag only (LSDx_op)                                     | Read diagnosis                                      | No                                                                                       |       |

| V <sub>DS</sub> state monitoring                  | ON/OFF                           | Read V <sub>DS</sub> state by SPI (vds_LSDx)                | update with min filter time (T1) rise and fall edge | No                                                                                       |       |

| Overcurrent                                       | ON                               | OFF fault FET only + SPI fault flag (LSDx_oc)               | Write 1 to LSD_clr_flt                              | Write 1 to LSD_clr_flt and turn on by SPI command (LSDx duty cycle or current set point) |       |

| Overtemperature                                   | ON                               | OFF fault FET only + SPI fault flag (LSDx_ot)               | Write 1 to LSD_clr_flt                              | Write 1 to LSD_clr_flt and turn on by SPI command (LSDx duty cycle or current set point) |       |

| Current regulation error (only for LSD1-4)        | ON                               | Read SPI flag only (LSDx_crer)                              | Read diagnosis                                      | No                                                                                       |       |

| LDx                                               |                                  |                                                             | 1                                                   | -                                                                                        | I     |

| Open Load                                         | OFF                              | SPI flag only (LDx_op)                                      | Read diagnosis                                      | No                                                                                       |       |

| V <sub>DS</sub> state monitoring                  | ON/OFF                           | Send V <sub>DS</sub> state by SPI (V <sub>DS_LD</sub> )     | update with min filter time (T1) rise and fall edge | No                                                                                       |       |

| Overcurrent                                       | ON                               | OFF fault FET only + SPI fault flag (LD_oc)                 | Write 1 to LD_clr_flt                               | Write 1 to LD_clr_flt and turn on by SPI command (LD_on)                                 |       |

| Overtemperature                                   | ON                               | OFF fault FET only + SPI fault flag (LD_ot)                 | Write 1 to LD_clr_flt                               | Write 1 to LD_clr_flt and turn on by SPI command (LD_on)                                 |       |

| HS                                                |                                  |                                                             |                                                     |                                                                                          |       |

| Open Load                                         | OFF                              | SPI flag only (HS_ op)                                      | Read diagnosis                                      | No                                                                                       |       |

| V <sub>DS</sub> state monitoring                  | ON/OFF                           | Send V <sub>DS</sub> state by<br>SPI (V <sub>DS_HS</sub> )  | update with min filter time                         | No                                                                                       |       |

| Overcurrent                                       | ON                               | OFF fault FET only + SPI fault flag (HS_oc)                 | Write 1 to HS_clr_flt                               | Write 1 to HS_clr_flt and then turn on by SPI command (HS_ on)                           |       |

#### Table 9. Error handling (continued)

| Detection condition             | Action                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Clear SPI flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Restart condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ON                              | OFF fault FET only + SPI fault flag (HS_ot)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Write 1 to HS_clr_flt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Write 1 to HS_clr_flt and then turn on by SPI command (HS_on)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| All except<br>Sleep mode        | SPI register reset & Vint_uv go to High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Read Vint_uv bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| All except<br>Sleep mode        | SPI register reset except VCC5_uv go to High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Wait undervoltage reset filter time T1 (see <u>Table 19</u> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | See <u>Table 19</u> ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |