### ABSOLUTE MAXIMUM RATINGS (Note 1)

| C0 $-0.3V$ to 8V         C12 $-0.3V$ to 75V         Cn (Note 5) $-0.3V$ to Min (8 • n, 75V)         Sn (Note 5) $-0.3V$ to Min (8 • n, 75V)         All Other Pins $-0.3V$ to 7V         Voltage Between Inputs $-0.3V$ to 8V         Cn to Cn - 1 $-0.3V$ to 8V         Sn to Cn - 1 $-0.3V$ to 8V         C12 to C8 $-0.3V$ to 25V         C8 to C4 $-0.3V$ to 25V         C4 to C0 $-0.3V$ to 25V | Total Supply Voltage (V <sup>+</sup> to V <sup>-</sup> )75V<br>Input Voltage (Relative to V <sup>-</sup> ) |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Cn (Note 5) $-0.3V$ to Min (8 • $n$ , 75V) $Sn$ (Note 5) $-0.3V$ to Min (8 • $n$ , 75V)         All Other Pins $-0.3V$ to 7V         Voltage Between Inputs $-0.3V$ to 8V $Sn$ to $Cn - 1$ $-0.3V$ to 8V $Sn$ to $Cn - 1$ $-0.3V$ to 25V         C8 to C4 $-0.3V$ to 25V                                                                                                                             |                                                                                                            |

| Sn (Note 5) $-0.3V$ to Min (8 • n, 75V)         All Other Pins $-0.3V$ to 7V         Voltage Between Inputs $-0.3V$ to 8V         Sn to Cn - 1 $-0.3V$ to 8V         C12 to C8 $-0.3V$ to 25V         C8 to C4 $-0.3V$ to 25V                                                                                                                                                                        | C120.3V to 75V                                                                                             |

| Sn (Note 5) $-0.3V$ to Min (8 • n, 75V)         All Other Pins $-0.3V$ to 7V         Voltage Between Inputs $-0.3V$ to 8V         Sn to Cn - 1 $-0.3V$ to 8V         C12 to C8 $-0.3V$ to 25V         C8 to C4 $-0.3V$ to 25V                                                                                                                                                                        | Cn (Note 5)–0.3V to Min (8 • n, 75V)                                                                       |

| Voltage Between Inputs $Cn$ to $Cn - 1$ $Sn$ to $Cn - 1$ $-0.3V$ to $8V$ $C12$ to $C8$ $-0.3V$ to $25V$ $C8$ to $C4$                                                                                                                                                                                                                                                                                 |                                                                                                            |

| Cn to Cn - 1                                                                                                                                                                                                                                                                                                                                                                                         | All Other Pins                                                                                             |

| Sn to Cn – 1 –0.3V to 8V<br>C12 to C8–0.3V to 25V<br>C8 to C4–0.3V to 25V                                                                                                                                                                                                                                                                                                                            | Voltage Between Inputs                                                                                     |

| C12 to C80.3V to 25V<br>C8 to C40.3V to 25V                                                                                                                                                                                                                                                                                                                                                          |                                                                                                            |

| C8 to C40.3V to 25V                                                                                                                                                                                                                                                                                                                                                                                  | S <i>n</i> to C <i>n</i> – 1–0.3V to 8V                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                      | C12 to C80.3V to 25V                                                                                       |

| C4 to C00.3V to 25V                                                                                                                                                                                                                                                                                                                                                                                  | C8 to C4–0.3V to 25V                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                      | C4 to C00.3V to 25V                                                                                        |

| Operating Temperature Range |               |

|-----------------------------|---------------|

| LTC6803I                    | 40°C to 85°C  |

| LTC6803H                    | 40°C to 125°C |

| Specified Temperature Range |               |

| LTC6803I                    | 40°C to 85°C  |

| LTC6803H                    | 40°C to 125°C |

| Junction Temperature        | 150°C         |

| Storage Temperature Range   | 65°C to 150°C |

| Note: <i>n</i> = 1 to 12    |               |

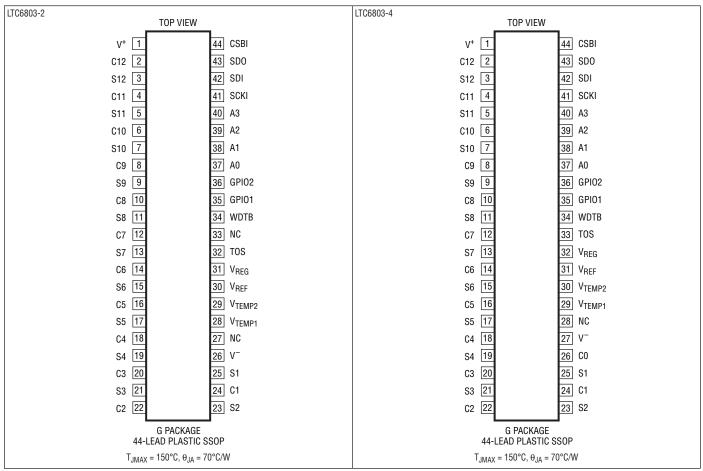

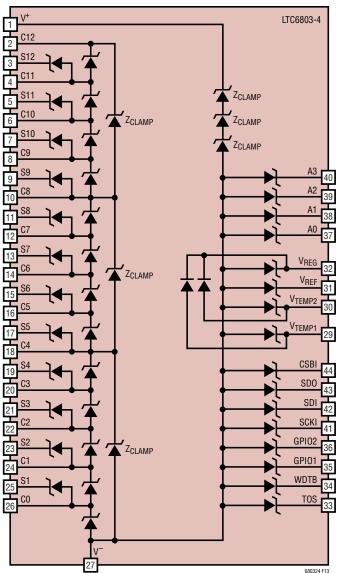

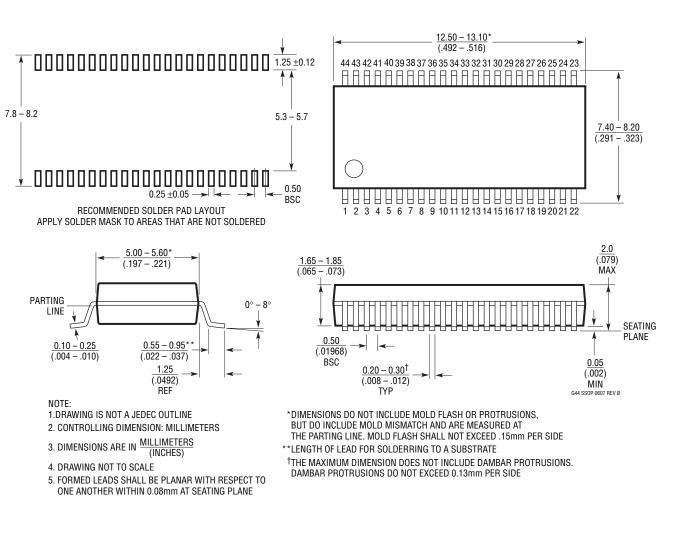

### PIN CONFIGURATION

### **ORDER INFORMATION**

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION  | SPECIFIED TEMPERATURE RANGE |

|------------------|-------------------|---------------|----------------------|-----------------------------|

| LTC6803IG-2#PBF  | LTC6803IG-2#TRPBF | LTC6803G-2    | 44-Lead Plastic SSOP | –40°C to 85°C               |

| LTC6803IG-4#PBF  | LTC6803IG-4#TRPBF | LTC6803G-4    | 44-Lead Plastic SSOP | -40°C to 85°C               |

| LTC6803HG-2#PBF  | LTC6803HG-2#TRPBF | LTC6803G-2    | 44-Lead Plastic SSOP | -40°C to 125°C              |

| LTC6803HG-4#PBF  | LTC6803HG-4#TRPBF | LTC6803G-4    | 44-Lead Plastic SSOP | -40°C to 125°C              |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sup>+</sup> = 43.2V, V<sup>-</sup> = 0V, unless otherwise noted.

| SYMBOL            | PARAMETER                                                        | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | MIN                                                                    | ТҮР        | MAX                                                          | UNITS                                                          |

|-------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------------------------------------------------------------|------------|--------------------------------------------------------------|----------------------------------------------------------------|

| DC Specifi        | ications                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 1                                                                      |            |                                                              |                                                                |

| V <sub>S</sub>    | Supply Voltage, V <sup>+</sup> Relative to V <sup>-</sup>        | V <sub>ERR</sub> Specification Met<br>Timing Specification Met                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | • | 10<br>4                                                                |            | 55<br>55                                                     | V<br>V                                                         |

| V <sub>LSB</sub>  | Measurement Resolution                                           | Quantization of the ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | • |                                                                        | 1.5        |                                                              | mV/Bit                                                         |

|                   | ADC Offset                                                       | (Note 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | • | -0.5                                                                   |            | 0.5                                                          | mV                                                             |

|                   | ADC Gain Error                                                   | (Note 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | • | -0.12<br>-0.22                                                         |            | 0.12<br>0.22                                                 | %<br>%                                                         |

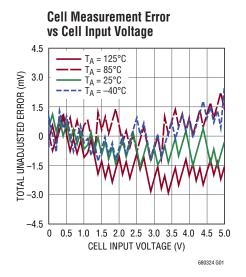

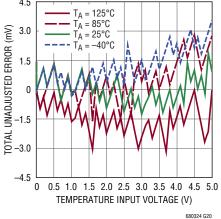

| V <sub>ERR</sub>  | Total Measurement Error                                          | $ \begin{array}{l} \mbox{(Note4)} \\ \mbox{V}_{CELL} = -0.3V \\ \mbox{V}_{CELL} = 2.3V \\ \mbox{V}_{CELL} = 2.3V \\ \mbox{V}_{CELL} = 3.6V \\ \mbox{V}_{CELL} = 3.6V \\ \mbox{V}_{CELL} = 3.6V \\ \mbox{U}_{CELL} = 3.6V \\ \mbox{U}_{CELL} = 3.6V \\ \mbox{U}_{CELL} = 4.2V \\ \mbox{V}_{CELL} = 4.2V \\ \mbox{V}_{CELL} = 4.2V \\ \mbox{U}_{CELL} = 4.2V \\ \mbox{U}_{CELL} = 4.2V \\ \mbox{U}_{CELL} = 4.2V \\ \mbox{U}_{CELL} = 5V \\ \mbox{U}_{CSU} = 5V \\ \mbox{U}_{CSU} < V_{TEMP} < 4.2V \\ \mbox{U}_{CEN} = 4.2V \\ \mbox{U}_{CEN} = 5V \\ \mbox{U}_{CSU} < V_{TEMP} < 4.2V \\ \mbox{U}_{CEN} = 50 \\ \mbox{U}_{CSU} < V_{TEMP} < 4.2V \\ \mbox{U}_{CEN} = 50 \\ \mbox{U}_{CSU} < V_{TEMP} < 4.2V \\ \mbox{U}_{CEN} = 50 \\ \mbox{U}_{CSU} < 0.5 \\ \mbox{U}_{CSU} <$ | • | -2.8<br>-5.1<br>-4.3<br>-7.9<br>-9<br>-5<br>-9.2<br>-10<br>-9.2<br>-10 | ±2.5<br>±3 | 2.8<br>5.1<br>4.3<br>7.9<br>9<br>5<br>9.2<br>10<br>9.2<br>10 | mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV |

| V <sub>CELL</sub> | Cell Voltage Range                                               | Full-Scale Voltage Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | -0.3                                                                   |            | 5                                                            | V                                                              |

| V <sub>CM</sub>   | Common Mode Voltage Range<br>Measured Relative to V <sup>-</sup> | Range of Inputs $Cn < 0.25\%$ Gain Error,<br>n = 2 to 11, LTC6803IG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | • | 1.8                                                                    |            | 5 • <i>n</i>                                                 | V                                                              |

|                   |                                                                  | Range of Inputs CO, C1 < 0.25% Gain Error,<br>LTC6803IG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | • | 0                                                                      |            | 5                                                            | V                                                              |

|                   |                                                                  | Range of Inputs $Cn < 0.5\%$ Gain Error,<br>n = 2 to 11, LTC6803HG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | • | 1.8                                                                    |            | 5 • <i>n</i>                                                 | V                                                              |

|                   |                                                                  | Range of Inputs CO, C1 < 0.5% Gain Error,<br>LTC6803HG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | • | 0                                                                      |            | 5                                                            | V                                                              |

|                   | Die Temperature Measurement Error                                | Error in Measurement of 125°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |                                                                        | 5          |                                                              | C°                                                             |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sup>+</sup> = 43.2V, V<sup>-</sup> = 0V, unless otherwise noted.

| SYMBOL             | PARAMETER                                    | CONDITIONS                                                                                                                                                                                                                    |   | MIN                            | ТҮР                            | MAX                               | UNITS                   |

|--------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------------------|--------------------------------|-----------------------------------|-------------------------|

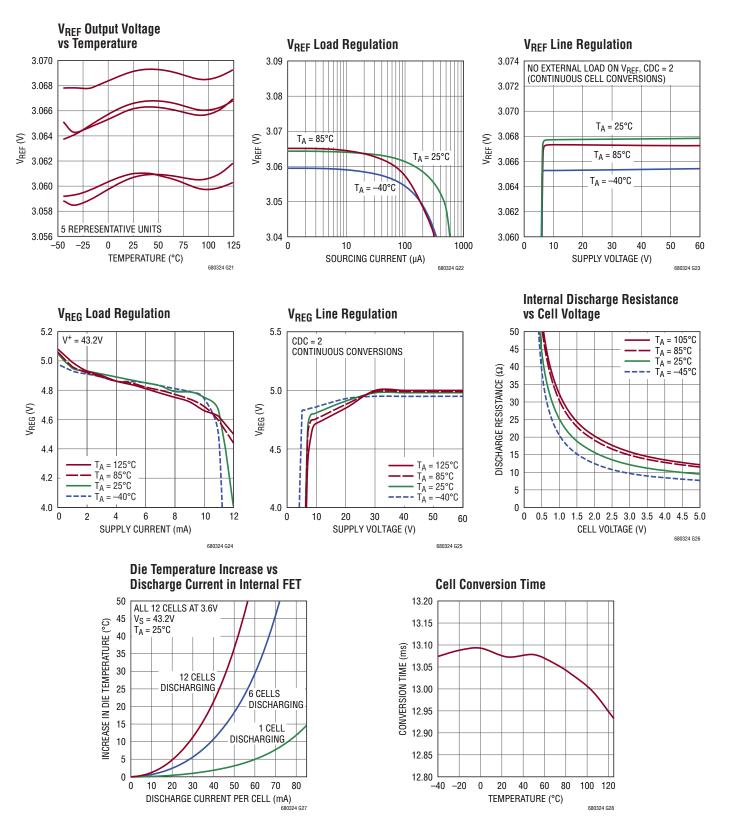

| V <sub>REF</sub>   | Reference Pin Voltage                        | $R_{LOAD} = 100k \text{ to } V^-$                                                                                                                                                                                             | • | 3.020<br>3.015                 | 3.065<br>3.065                 | 3.110<br>3.115                    | V<br>V                  |

|                    | Reference Voltage Temperature<br>Coefficient |                                                                                                                                                                                                                               |   |                                | 8                              |                                   | ppm/°C                  |

|                    | Reference Voltage Thermal Hysteresis         | 25°C to 85°C and 25°C to –40°C                                                                                                                                                                                                |   |                                | 100                            |                                   | ppm                     |

|                    | Reference Voltage Long-Term Drift            |                                                                                                                                                                                                                               |   |                                | 60                             |                                   | ppm/√kHr                |

| V <sub>REF2</sub>  | 2nd Reference Voltage                        |                                                                                                                                                                                                                               | • | 2.25<br>2.1                    | 2.5<br>2.5                     | 2.75<br>2.9                       | V<br>V                  |

| V <sub>REG</sub>   | Regulator Pin Voltage                        | 10V < V <sup>+</sup> < 50V, No Load<br>I <sub>LOAD</sub> = 4mA                                                                                                                                                                | • | 4.5<br>4.5                     | 5.0<br>5.0                     | 5.5                               | V<br>V                  |

|                    | Regulator Pin Short-Circuit Limit            |                                                                                                                                                                                                                               |   | 8                              |                                |                                   | mA                      |

| I <sub>B</sub>     | Input Bias Current                           | In/Out of Pins C1 Through C12<br>When Measuring Cell<br>When Not Measuring Cell                                                                                                                                               |   | -10                            | 1                              | 10                                | μA<br>nA                |

| I <sub>S</sub>     | Supply Current, Measure Mode<br>(Note 7)     | Current Into the V <sup>+</sup> Pin When Measuring<br>Continuous Measuring (CDC = 2)<br>Continuous Measuring (CDC = 2)<br>Measure Every 130ms (CDC = 5)<br>Measure Every 500ms (CDC = 6)<br>Measure Every 2 Seconds (CDC = 7) | • | 620<br>600<br>190<br>140<br>55 | 780<br>780<br>250<br>175<br>70 | 1000<br>1150<br>360<br>250<br>105 | Αμ<br>Α<br>Α<br>Αμ<br>Α |

| I <sub>QS</sub>    | Supply Current, Standby                      | Current Into V <sup>+</sup> Pin When In Standby, All Serial<br>Port Pin at Logic "1"<br>LTC6803IG<br>LTC6803HG                                                                                                                | • | 8<br>6<br>6                    | 12<br>12<br>12                 | 16.5<br>18<br>19                  | μΑ<br>μΑ<br>μΑ          |

| I <sub>SD</sub>    | Supply Current, Hardware Shutdown            | Current Out of V <sup>-</sup> , V <sub>C12</sub> = 43.2V, V <sup>+</sup> Floating<br>(Note 8)                                                                                                                                 | • |                                | 0.001                          | 1                                 | μA                      |

|                    | Discharge Switch-On Resistance               | V <sub>CELL</sub> > 3V (Note 3)                                                                                                                                                                                               | ٠ | 10                             |                                | 20                                | Ω                       |

| I <sub>OW</sub>    | Current Used for Open-Wire Detection         |                                                                                                                                                                                                                               | • | 70                             | 110                            | 140                               | μA                      |

|                    | Thermal Shutdown Temperature                 |                                                                                                                                                                                                                               |   |                                | 145                            |                                   | °C                      |

|                    | Thermal Shutdown Hysteresis                  |                                                                                                                                                                                                                               |   |                                | 5                              |                                   | °C                      |

| Voltage M          | ode Timing Specifications                    | ·                                                                                                                                                                                                                             |   |                                |                                |                                   |                         |

| t <sub>cycle</sub> | Measurement Cycling                          | Time Required to Measure 12 Cells<br>Time Required to Measure 10 Cells<br>Time Required to Measure 3 Temperatures<br>Time Required to Measure 1 Cell or Temperature                                                           | • | 11<br>9<br>2.8<br>1.0          | 13<br>11<br>3.4<br>1.2         | 15<br>13<br>4.1<br>1.4            | ms<br>ms<br>ms<br>ms    |

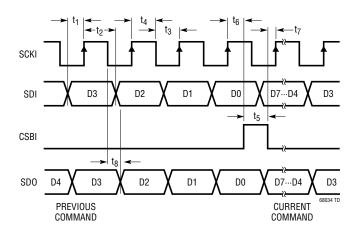

| t <sub>1</sub>     | SDI Valid to SCKI Rising Setup               |                                                                                                                                                                                                                               |   | 10                             |                                |                                   | ns                      |

| t <sub>2</sub>     | SDI Valid to SCKI Rising Hold                |                                                                                                                                                                                                                               |   | 250                            |                                |                                   | ns                      |

| t <sub>3</sub>     | SCKI Low                                     |                                                                                                                                                                                                                               |   | 400                            |                                |                                   | ns                      |

| t <sub>4</sub>     | SCKI High                                    |                                                                                                                                                                                                                               | ٠ | 400                            |                                |                                   | ns                      |

| t <sub>5</sub>     | CSBI Pulse Width                             |                                                                                                                                                                                                                               |   | 400                            |                                |                                   | ns                      |

| t <sub>6</sub>     | CSBI Falling to SCKI Rising                  |                                                                                                                                                                                                                               | ٠ | 100                            |                                |                                   | ns                      |

| t <sub>7</sub>     | CSBI Falling to SDO Valid                    |                                                                                                                                                                                                                               |   | 100                            |                                |                                   | ns                      |

| t <sub>8</sub>     | SCKI Falling to SDO Valid                    |                                                                                                                                                                                                                               |   |                                |                                | 250                               | ns                      |

|                    | Clock Frequency                              |                                                                                                                                                                                                                               |   |                                |                                | 1                                 | MHz                     |

|                    | Watchdog Timer Timeout Period                |                                                                                                                                                                                                                               |   | 1                              |                                | 2.5                               | Seconds                 |

## **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sup>+</sup> = 43.2V, V<sup>-</sup> = 0V, unless otherwise noted.

| SYMBOL          | PARAMETER                  | CONDITIONS                               | CONDITIONS |   |  | MAX | UNITS |

|-----------------|----------------------------|------------------------------------------|------------|---|--|-----|-------|

| Voltage Mo      | de Digital I/O             |                                          |            |   |  |     |       |

| V <sub>IH</sub> | Digital Input Voltage High | Pins SCKI, SDI and CSBI                  | •          | 2 |  |     | V     |

| VIL             | Digital Input Voltage Low  | Pins SCKI, SDI and CSBI                  | •          |   |  | 0.8 | V     |

| V <sub>OL</sub> | Digital Output Voltage Low | Pin SDO, Sinking 500µA                   | •          |   |  | 0.3 | V     |

| l <sub>IN</sub> | Digital Input Current      | V <sub>MODE</sub> , TOS, SCKI, SDI, CSBI | •          |   |  | 10  | μA    |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: The ADC specifications are guaranteed by the Total Measurement Error (V<sub>ERR</sub>) specification.

Note 3: Due to the contact resistance of the production tester, this specification is tested to relaxed limits. The  $20\Omega$  limit is guaranteed by design.

**Note 4:**  $V_{CELL}$  refers to the voltage applied across Cn to Cn - 1 for n = 1 to 12. V<sub>TEMP</sub> refers to the voltage applied from V<sub>TEMP1</sub> or V<sub>TEMP2</sub> to V<sup>-</sup>.

**Note 5:** These absolute maximum ratings apply provided that the voltage between inputs do not exceed the absolute maximum ratings.

**Note 6:** Supply current is tested during continuous measuring. The supply current during periodic measuring (130ms, 500ms, 2s) is guaranteed by design.

Note 7: The CDC = 5, 6 and 7 supply currents are not measured. They are guaranteed by the CDC = 2 supply current measurement.

Note 8: Limit is determined by high speed automated test capability.

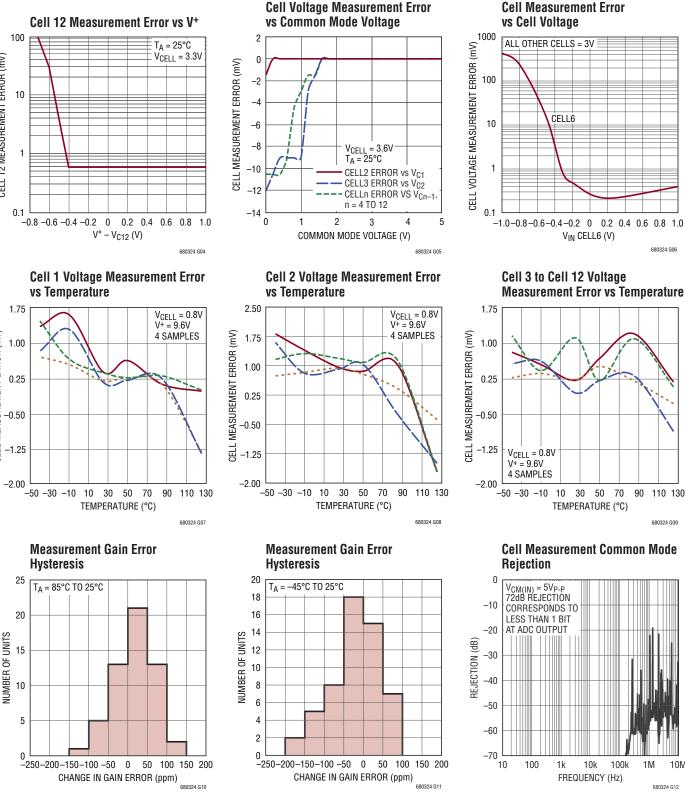

### TYPICAL PERFORMANCE CHARACTERISTICS

Cell Measurement Error

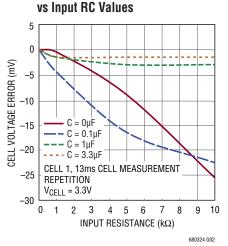

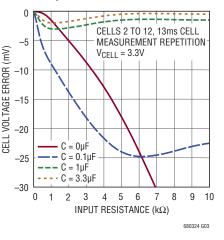

#### **Cell Measurement Error** vs Input RC Values

CELL 12 MEASUREMENT ERROR (mV)

CELL MEASUREMENT ERROR (mV)

### TYPICAL PERFORMANCE CHARACTERISTICS

70 30 50 90 110 130 TEMPERATURE (°C)

680324 G09

680324 G06

### **Cell Measurement Common Mode**

680324fa

Downloaded from Arrow.com.

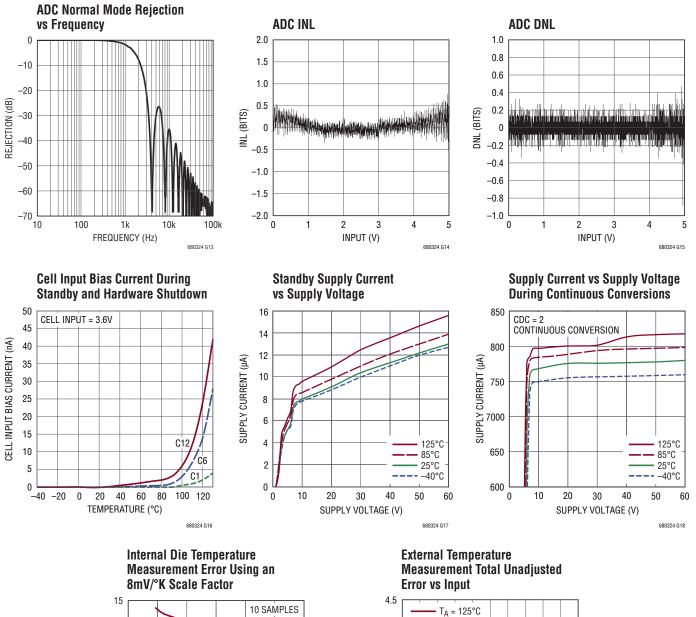

### **TYPICAL PERFORMANCE CHARACTERISTICS**

### **TYPICAL PERFORMANCE CHARACTERISTICS**

### PIN FUNCTIONS

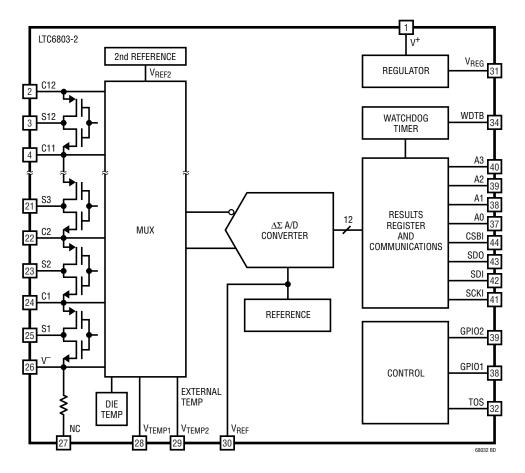

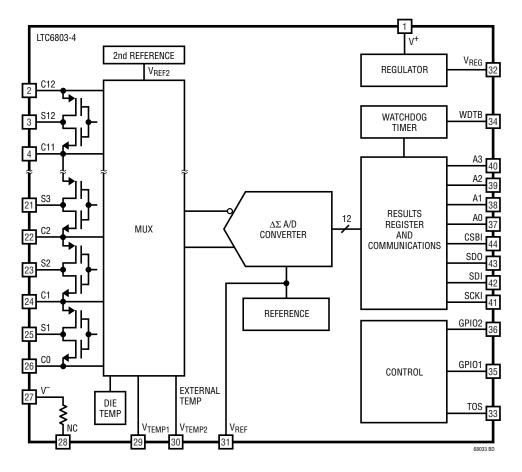

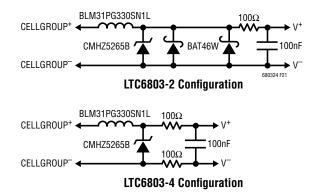

To ensure pin compatibility with LTC6802-2, the LTC6803-2 is configured such that the bottom cell input (C0) is connected internally to the negative supply voltage (V<sup>-</sup>). The LTC6803-4 offers a unique pinout with an input for the bottom cell (C0). This simple functional difference offers the possibility for enhanced cell 1 measurement accuracy, enhanced SPI noise tolerance and simplified wiring. More information is provided in the Applications Information section entitled Advantages of Kelvin Connection for C0.

**V<sup>+</sup> (Pin 1):** Positive Power Supply. Pin 1 can be tied to the most positive potential in the battery stack or an isolated power supply. V<sup>+</sup> must be greater than the most positive potential in the battery stack under normal operation. With an isolated power supply, LTC6803 can be turned off by simply shutting down V<sup>+</sup>.

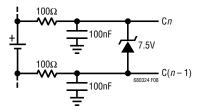

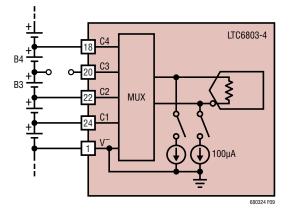

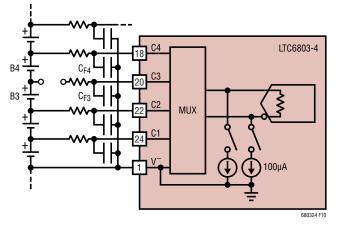

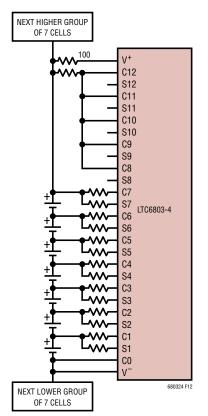

**C12, C11, C10, C9, C8, C7, C6, C5, C4, C3, C2, C1** (**Pins 2, 4, 6, 8, 10, 12, 14, 16, 18, 20, 22, 24**): C1 through C12 are the inputs for monitoring battery cell voltages. The negative terminal of the bottom cell should be tied to the V<sup>-</sup> pin for the LTC6803-2, and the C0 pin for the LTC6803-4. The next lowest potential is tied to C1 and so forth. See the figures in the Applications Information section for more details on connecting batteries to the LTC6803-2 and LTC6803-4. The LTC6803 can monitor a series connection of up to 12 cells. Each cell in a series connection must have a common mode voltage that is greater than or equal to the cells below it. 100mV negative voltages are permitted.

**C0 (Pin 26 on LTC6803-4):** Negative Terminal of the Bottom Battery Cell. C0 and V<sup>-</sup> form a Kelvin connection to eliminate effect of voltage drop at the V<sup>-</sup> trace.

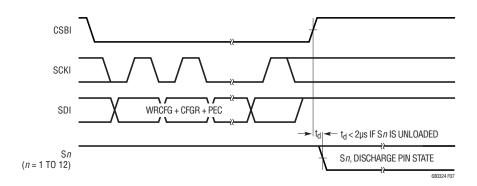

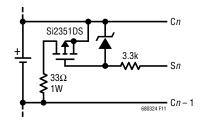

**S12, S11, S10, S9, S8, S7, S6, S5, S4, S3, S2, S1 (Pins 3, 5, 7, 9, 11, 13, 15, 17, 19, 21, 23, 25):** S1 though S12 pins are used to balance battery cells. If one cell in a series becomes overcharged, an S output can be used to discharge the cell. Each S output has an internal N-channel MOSFET for discharging. See the Block Diagram. The NMOS has a maximum on-resistance of  $20\Omega$ . An external resistor

should be connected in series with the NMOS to dissipate heat outside of the LTC6803 package. When using the internal MOSFETs to discharge cells, the die temperature should be monitored. See Power Dissipation and Thermal Shutdown in the Applications Information section. The S pins also feature an internal pull-up PMOS. This allows the S pins to be used to drive the gates of external MOSFETs for higher discharge capability.

V<sup>-</sup> (Pin 26 on LTC6803-2/Pin 27 on LTC6803-4): Connect V<sup>-</sup> to the most negative potential in the series of cells.

**NC (Pin 27 on LTC6803-2/Pin 28 on LTC6803-4):** This pin is not used and is internally connected to V<sup>-</sup> through  $10\Omega$ . It can be left unconnected or connected to V<sup>-</sup> on the PCB.

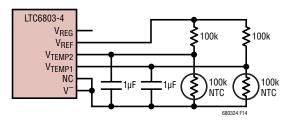

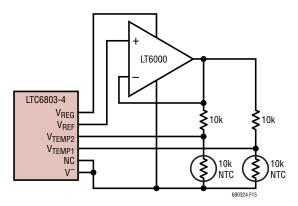

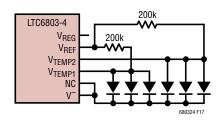

**V<sub>TEMP1</sub>, V<sub>TEMP2</sub> (Pins 28, 29 on LTC6803-2/Pins 29, 30, on LTC6803-4)**: Temperature Sensor Inputs. The ADC will measure the voltage on  $V_{TEMPn}$  with respect to V<sup>-</sup> and store the result in the TMP register. The ADC measurements are relative to the V<sub>REF</sub> pin voltage. Therefore a simple thermistor and resistor combination connected to the V<sub>REF</sub> pin can be used to monitor temperature. The V<sub>TEMP</sub> inputs can also be general purpose ADC inputs.

**V**<sub>REF</sub> (Pin 30 on LTC6803-2/Pin 31 on LTC6803-4): 3.065V Voltage Reference Output. This pin should be bypassed with a 1µF capacitor. The V<sub>REF</sub> pin can drive a 100k resistive load connected to V<sup>-</sup>. Larger loads should be buffered with an LT6003 op amp, or a similar device.

$V_{REG}$  (Pin 31 on LTC6803-2/Pin 32 on LTC6803-4): Linear Voltage Regulator Output. This pin should be bypassed with a 1µF capacitor. The  $V_{REG}$  is capable of sourcing up to 4mA to an external load. The  $V_{REG}$  pin does not sink current.

**TOS (Pin 32 on LTC6803-2/Pin 33 on LTC6803-4):** Top of Stack Input. The TOS pin can be tied to  $V_{REG}$  or  $V^-$  for the LTC6803. The state of the TOS pin alters the operation of the SDO pin in the toggle polling mode. See the Serial Port description.

NC (Pin 33 on LTC6803-2): No Connection.

### PIN FUNCTIONS

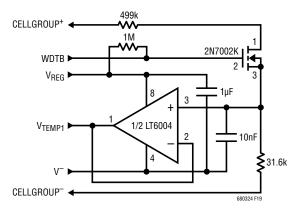

**WDTB (Pin 34):** Watchdog Timer Output (Active Low). If there is no valid command received in 1 to 2.5 seconds, the WDTB output is asserted. The WDTB pin is an open-drain NMOS output. When asserted it pulls the output down to  $V^-$  and resets the configuration register to its default state.

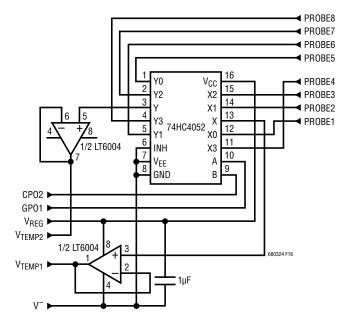

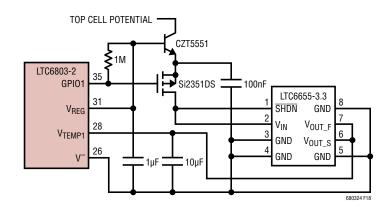

GPI01, GPI02 (Pins 35, 36): General Purpose Input/ Output. By writing a "0" to a GPIO configuration register bit, the open-drain output is activated and the pin is pulled to V<sup>-</sup>. By writing a logic "1" to the configuration register bit, the corresponding GPIO pin is high impedance. An external resistor is required to pull the pin up to V<sub>RFG</sub>. By reading the configuration register locations GPI01 and GPIO2, the state of the pins can be determined. For example, if a "0" is written to register bit GPI01, a "0" is always read back because the output N-channel MOSFET pulls Pin 35 to  $V^-$ . If a "1" is written to register bit GPIO1, the pin becomes high impedance. Either a "1" or a "0" is read back, depending on the voltage present at Pin 35. The GPIOs makes it possible to turn-on/off circuitry around the LTC6803-4, or read logic values from a circuit around the LTC6803-4. The GPIO pins should be connected to V<sup>-</sup> if not used.

**A0, A1, A2, A3 (Pins 37, 38, 39, 40):** Address Inputs. These pins are tied to  $V_{REG}$  or  $V^-$ . The state of the address pins ( $V_{REG} = 1$ ,  $V^- = 0$ ) determines the LTC6803 address. See Address Commands in the Serial Port subsection of the Applications Information section.

**SCKI (Pin 41):** Serial Clock Input. The SCKI pin interfaces to any logic gate (TTL levels). See Serial Port in the Applications Information section.

**SDI (Pin 42):** Serial Data Input. The SDI pin interfaces to any logic gate (TTL levels). See Serial Port in the Applications Information section.

**SDO (Pin 43):** Serial Data Output. The SDO pin is an NMOS open-drain output. A pull-up resistor is needed on SDO. See Serial Port in the Applications Information section.

**CSBI (Pin 44):** Chip Select (Active Low) Input. The CSBI pin interfaces to any logic gate (TTL levels). See Serial Port in the Applications Information section.

### **BLOCK DIAGRAMS**

### **BLOCK DIAGRAMS**

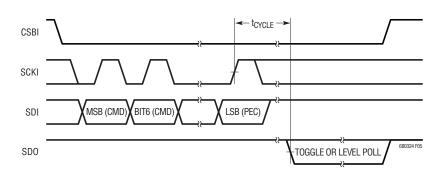

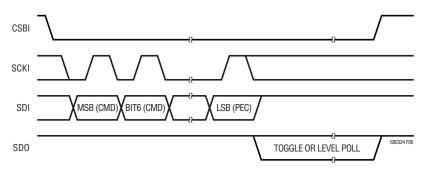

### TIMING DIAGRAM

#### Timing Diagram of the Serial Interface

#### THEORY OF OPERATION

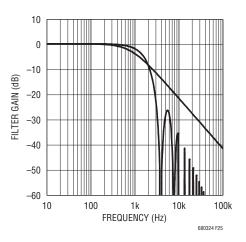

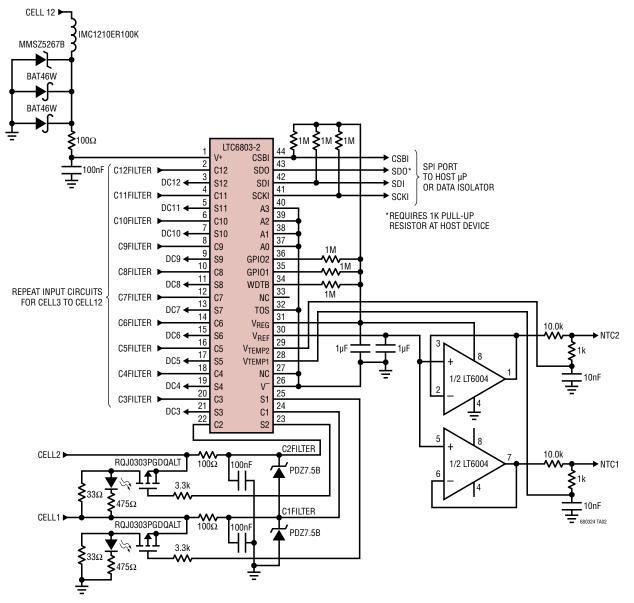

The LTC6803 is a data acquisition IC capable of measuring the voltage of 12 series connected battery cells. An input multiplexer connects the batteries to a 12-bit delta-sigma analog-to-digital converter (ADC). An internal 8ppm/°C voltage reference combined with the ADC give the LTC6803 its outstanding measurement accuracy. The inherent benefits of the delta-sigma ADC versus other types of ADCs (e.g., successive approximation) are explained in Advantages of Delta-Sigma ADCs in the Applications Information section.

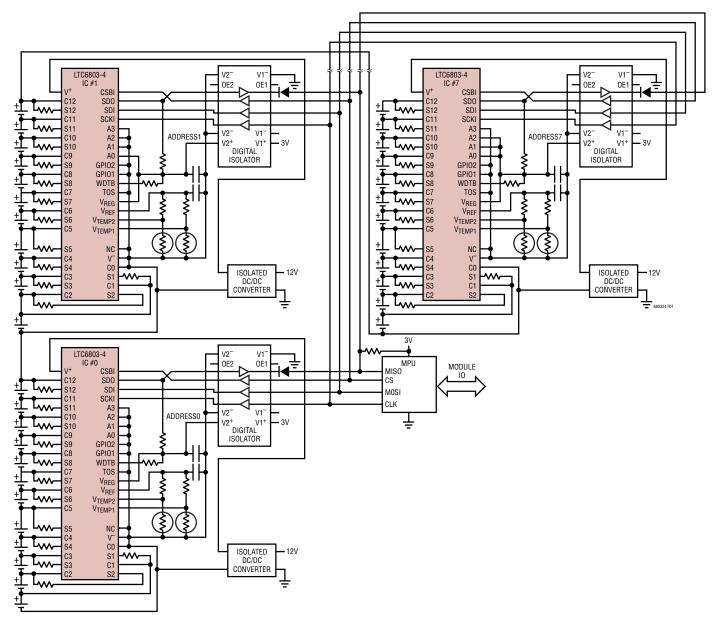

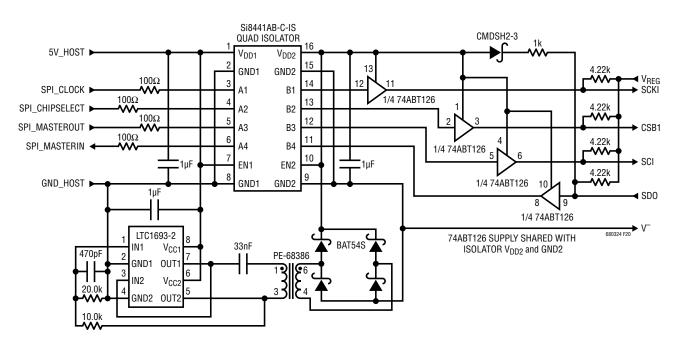

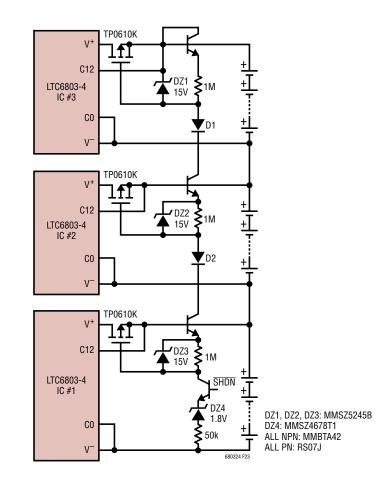

Communication between the LTC6803 and a host processor is handled by a SPI compatible serial interface. Multiple LTC6803s can be connected to a single serial interface. As shown in Figure 1, the LTC6803-2s or LTC6803-4s are isolated from one another using digital isolators. A unique addressing scheme allows all the LTC6803-2s or LTC6803-4s to connect to the same serial port of the host processor. Further explanation of the LTC6803-2/LTC6803-4 can be found in the Serial Port section of the data sheet.

The LTC6803 also contains circuitry to balance cell voltages. Internal MOSFETs can be used to discharge cells. These internal MOSFETs can also be used to control external balancing circuits. Figure 1 illustrates cell balancing by internal discharge. Figure 3 shows the S pin controlling an external balancing circuit. It is important to note that the LTC6803 makes no decisions about turning on/off the internal MOSFETs. This is completely controlled by the host processor. The host processor writes values to a configuration register inside the LTC6803 to control the switches. The watchdog timer on the LTC6803 can be used to turn off the discharge switches if communication with the host processor is interrupted.

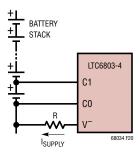

Since the LTC6803-4 separates C0 and V<sup>-</sup>, C0 can have higher potential than V<sup>-</sup>. This feature is very useful for super capacitors and fuel cells whose voltages can go to zero or slightly negative. In such a case, the stacked cells can't power the LTC6803-4. In Figure 1, an isolated 36V and -3.6V provides power to each LTC6803-4. This allows the C1 to C12 pins to go up to 3.6V below C0. The LTC6803 has three modes of operation: hardware shutdown, standby and measure. Hardware shutdown is a true zero power mode. Standby mode is a power saving state where all circuits except the serial interface are turned off. In measure mode, the LTC6803 is used to measure cell voltages and store the results in memory. Measure mode will also monitor each cell voltage for overvoltage (OV) and undervoltage (UV) conditions.

#### HARDWARE SHUTDOWN MODE

The V<sup>+</sup> pin can be disconnected from the C pins and the battery pack. If the V<sup>+</sup> supply pin is 0V, the LTC6803 will typically draw less than 1nA from the battery cells. All circuits inside the IC are off. It is not possible to communicate with the IC when V<sup>+</sup> = 0V. See the Applications Information section for hardware shutdown circuits.

#### **STANDBY MODE**

The LTC6803 defaults (powers up) to standby mode. Standby mode is the lowest supply current state with a supply connected. Standby current is typically 12µA when  $V^+ = 44V$ . All circuits are turned off except the serial interface and the voltage regulator. For the lowest possible standby current consumption, all SPI logic inputs should be set to logic 1 level. The LTC6803 can be programmed for standby mode by setting the comparator duty cycle configuration bits, CDC[2:0], to 0. If the part is put into standby mode while ADC measurements are in progress, the measurements will be interrupted and the cell voltage registers will be in an indeterminate state. To exit standby mode, the CDC bits must be written to a value other than 0.

#### **MEASURE MODE**

The LTC6803 is in measure mode when the CDC bits are programmed with a value from 1 to 7. When CDC = 1 the LTC6803 is on and waiting for a start ADC conversion command. When CDC is 2 through 7 the IC monitors each cell voltage and produces an interrupt signal on the SDO pin indicating all cell voltages are within the UV and OV limits. The value of the CDC bits determines how often the cells are monitored, and, how much average supply current is consumed.

### LTC6803-2/LTC6803-4

### OPERATION

Figure 1. Simplified 96-Cell Battery or Supercapacitor, Isolated Interface. In this Diagram the Battery Negative is Isolated from the Module Ground. Isolated Power Supplies Each LTC6803-4. Opto-Couplers or Digital Isolators Allow Each IC to Be Addressed Individually

There are two methods for indicating the UV/OV interrupt status: toggle polling (using a 1kHz output signal) and level polling (using a high or low output signal). The polling methods are described in the Serial Port section. The UV/OV limits are set by the V<sub>UV</sub> and V<sub>OV</sub> values in the configuration registers. When a cell voltage exceeds the UV/OV limits a bit is set in the flag register. The UV and OV flag status for each cell can be determined using the *Read Flag Register Group*.

An ADC measurement can be requested at any time when the IC is in measure mode. To initiate cell voltage measurements while in measure mode, a Start A/D Conversion command is sent. After the command has been sent, the LTC6803 will indicate the A/D converter status via toggle polling or level polling (as described in the Serial Port section). During cell voltage measurement commands, the UV and OV flags (within the flag register group) are also updated. When the measurements are complete, the part will continue monitoring UV and OV conditions at the rate designated by the CDC bits. Note that there is a 5µs window during each UV/OV comparison cycle where an ADC measurement request may be missed. This is an unlikely event. For example, the comparison cycle is 2 seconds when CDC = 7. Use the CLEAR command to detect missing ADC commands.

#### **Operating with Less than 12 Cells**

If fewer than 12 cells are connected to the LTC6803, the unused input channels must be masked. The MCxI bits in the configuration registers are used to mask channels. In addition, the LTC6803 can be configured to automatically bypass the measurements of the top 2 cells, reducing power consumption and measurement time. If the CELL10 bit is high, the inputs for cell 11 and cell 12 are masked and only the bottom 10-cell voltages will be measurement of all 12-cell voltages. Additional information regarding operation with less than 12 cells is provided in the applications section.

#### ADC RANGE AND OUTPUT FORMAT

The ADC outputs a 12-bit code with an offset of 0x200 (512 decimal). The input voltage can be calculated as:

$V_{IN} = (DOUT - 512) \bullet V_{LSB}; V_{LSB} = 1.5mV$

where DOUT is a decimal integer.

For example, a OV input will have an output reading of 0x200. An ADC reading of 0x000 means the input was -0.768V. The absolute ADC measurement range is -0.768V to 5.376V. The resolution is V<sub>LSB</sub> = 1.5mV =  $(5.376 + 0.768)/2^{12}$ . The useful range is -0.3V to 5V. This range allows monitoring supercapacitors which could have small negative voltage. Inputs below -0.3V exceed the absolute maximum rating of the C pins. If all inputs are negative, the ADC range is reduced to -0.1V. Inputs above 5V will have noisy ADC readings (see Typical Performance Characteristics).

#### ADC MEASUREMENTS DURING CELL BALANCING

The primary cell voltage ADC measurement commands (STCVAD and STOWAD) automatically turn off a cell's discharge switch while its voltage is being measured. The discharge switches for the cell above and the cell below will also be turned off during the measurement. For example, discharge switches S4, S5 and S6 will be off while cell 5 is being measured. The UV/OV comparison conversions in CDC modes 2 through 7 also cause a momentary turn-off of the discharge switch. For example, switches S4, S5 and S6 will be off while cell 5 is checked for a UV/OV condition.

In some systems it may be desirable to allow discharging to continue during cell voltage measurements. The cell voltage ADC conversion commands STCVDC and STOWDC allow the discharge switches to remain on during cell voltage measurements. This feature allows the system to perform a self test to verify the discharge functionality.

#### ADC REGISTER CLEAR COMMAND

The clear command can be used to clear the cell voltage registers and temperature registers. The clear command will set all registers to 0xFFF. This command is used to make sure conversions are being made. When cell voltages are stable, ADC results could stay the same. If a start ADC conversion command is sent to the LTC6803 but the PEC fails to match then the command is ignored and the voltage register contents also will not change. Sending a *clear* command then reading back register contents is a way to make sure LTC6803 is accepting command takes 1ms to execute.

#### ADC CONVERTER SELF TEST

Two self-test commands can be used to verify the functionality of the digital portions of the ADC. The self tests also verify the cell voltage registers and temperature monitoring registers. During these self tests a test signal is applied to the ADC. If the circuitry is working properly all cell voltage and temperature registers will contain 0x555 or 0xAAA. The time required for the self-test function is the same as required to measure all cell voltages or all temperature sensors.

#### **MULTIPLEXER AND REFERENCE SELF TEST**

The LTC6803 uses a multiplexer to measure the 12 battery cell inputs as well as the temperature signals. A diagnostic command is used to validate the function of the multiplexer, the temperature sensor, and the precision reference circuit. Diagnostic registers will be updated after each diagnostic test. The *muxfail* bit of the registers will be 1 if the multiplexer self test fails.

A constant voltage generated by the 2nd reference circuit will be measured by the ADC and the results written to the diagnostic register. The voltage reading should be 2.5V  $\pm 16\%$ . Readings outside this range indicate a failure of the temperature sensor circuit, the precision reference circuit, or the analog portion of the ADC. The DAGN command executes in 16.4ms, which is the sum of the 12-cell t<sub>CYCLE</sub> and the 3 temperature t<sub>CYCLE</sub>. The diagnostic read command can be used to read the registers.

## USING THE GENERAL PURPOSE INPUTS/OUTPUTS (GPI01, GPI02)

The LTC6803 has two general purpose digital input/output pins. By writing a GPIO configuration register bit to a logic low, the open-drain output can be activated. The GPIOs give the user the ability to turn on/off circuitry around the LTC6803. One example might be a circuit to verify the operation of the system.

When a GPIO configuration bit is written to a logic high, the corresponding GPIO pin may be used as an input. The read back value of that bit will be the logic level that appears at the GPIO pins.

#### WATCHDOG TIMER CIRCUIT

The LTC6803 includes a watchdog timer circuit. The watchdog timer is on for all modes except CDC = 0. The watchdog timer times out if no valid command is received for 1 to 2.5 seconds. When the watchdog timer circuit times out, the WDTB open-drain output is asserted low and the configuration register bits are reset to their default (power-up) state. In the power-up state, CDC is 0, the S outputs are off and the IC is in the low power standby mode. The WDTB pin remains low until a valid command is received. The watchdog timer provides a means to turn off cell discharging should communications to the MPU be interrupted. There is no need for the watchdog timer at CDC = 0 since discharging is off. The open-drain WDTB output can be wire ORd with other external open-drain signals. Pulling the WDTB signal low will not initiate a watchdog event, but the CNFGO bit 7 will reflect the state of this signal. Therefore, the WDTB pin can be used to monitor external digital events if desired.

#### SERIAL PORT

#### Overview

The LTC6803-2/LTC6803-4 has an SPI bus compatible serial port. Devices can be connected in parallel, using digital isolators. Multiple devices are uniquely identified by a part address determined by the A0 to A3 pins. Physical Layer on the LTC6803-2/LTC6803-4, four pins comprise the serial interface: CSBI, SCKI, SDI and SDO. The SDO

and SDI may be tied together, if desired, to form a single, bi-directional port. Four address pins (A0 to A3) set the part address for address commands. The TOS pin designates the top device (logic high) for polling commands. All interface pins are voltage mode, with voltage levels sensed with respect to the V<sup>-</sup> supply. See Figure 1.

#### Data Link Layer

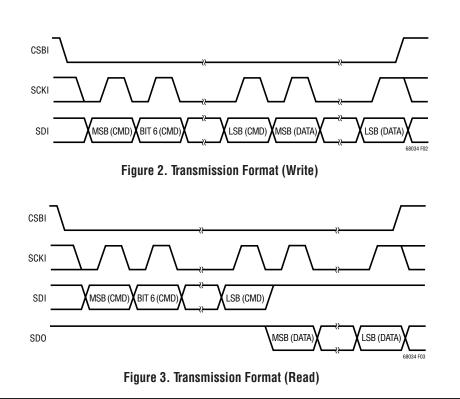

*Clock Phase And Polarity:* The LTC6803 SPI compatible interface is configured to operate in a system using CPHA = 1 and CPOL = 1. Consequently, data on SDI must be stable during the rising edge of SCKI.

*Data Transfers:* Every byte consists of 8 bits. Bytes are transferred with the most significant bit (MSB) first. On a write, the data value on SDI is latched into the device on the rising edge of SCKI (Figure 2). Similarly, on a read, the data value output on SDO is valid during the rising edge of SCKI and transitions on the falling edge of SCKI (Figure 3).

CSBI must remain low for the entire duration of a command sequence, including between a command byte and subsequent data. On a write command, data is latched in on the rising edge of CSBI.

#### **Network Layer**

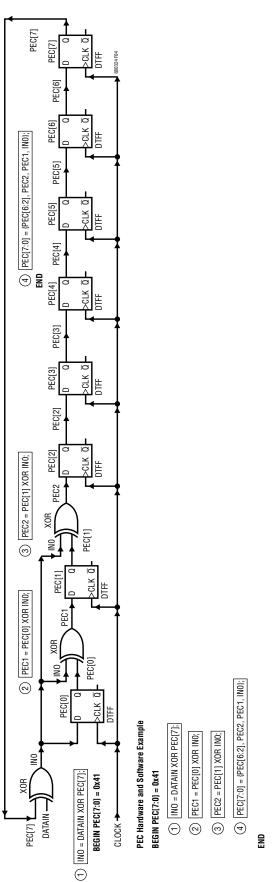

*PEC Byte:* The packet error code (PEC) byte is a cyclic redundancy check (CRC) value calculated for all of the bits in a register group in the order they are passed, using the initial PEC value of 01000001 and the following characteristic polynomial:

$x^8 + x^2 + x + 1$

To calculate the 8-bit PEC value, a simple procedure can be established:

- 1. Initialize the PEC to 0100 0001.

- 2. For each bit DIN coming into the register group, set IN0 = DIN XOR PEC[7], then IN1 = PEC[0] XOR IN0, IN2 = PEC[1] XOR IN0.

- 3. Update the 8-bit PEC as PEC[7] = PEC[6], PEC[6] = PEC[5],.....PEC[3] = PEC[2], PEC[2] = IN2, PEC[1] = IN1, PEC[0] = IN0.

- 4. Go back to step 2 until all data are shifted. The 8-bit result is the final PEC byte.

680324fz

An example to calculate the PEC is listed in Table 1 and Figure 4. The PEC of the 1 byte data 0x01 is computed as 0xC7 after the last bit of the byte streamed in. For multiple byte data, PEC is valid at the end (LSB) of the last byte.

LTC6803 calculates PEC byte for any command or data received and compares it with the PEC byte following the command or data. The command or data is regarded as valid only if the PEC bytes match. LTC6803 also attaches the calculated PEC byte at the end of the data it shifts out.

*Broadcast Commands:* A broadcast command is one to which all devices on the bus will respond, regardless of device address. See the Bus Protocols and Commands sections. With broadcast commands all devices can be sent commands simultaneously. This is useful for ADC conversion and polling commands. It can also be used with write commands when all parts are being written with the same data. Broadcast read commands should not be used in the parallel configuration.

*Address Commands:* An address command is one in which only the addressed device on the bus responds. The first byte of an address command consists of 4 bits with a value of 1000 and 4 address bits. Following the address command is its PEC byte. The third and fourth bytes are the command byte and its PEC byte respectively. See the Bus Protocols and Commands section.