# **Selection Guides**

|                             |                                | 7C265-15 | 7C265-25 | 7C265-40 | 7C265-50 | Unit |

|-----------------------------|--------------------------------|----------|----------|----------|----------|------|

| Minimum Address Set-Up Time |                                | 15       | 25       | 40       | 50       | ns   |

| Maximum Clock to Output     |                                | 12       | 15       | 20       | 25       | ns   |

| Maximum Operating Current   | Aximum Operating Current Com'l |          | 120      | 100      |          | mA   |

|                             | Mil                            |          |          |          | 120      | mA   |

# **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.) Storage Temperature .....-65°C to +150°C Ambient Temperature with Power Applied.....-55°C to +125°C Supply Voltage to Ground Potential.....-0.5V to +7.0V DC Voltage Applied to Outputs in High Z State .....-0.5V to +7.0V DC Input Voltage....-3.0V to +7.0V

| DC Program Voltage                                         |                           |

|------------------------------------------------------------|---------------------------|

| UV Exposure                                                | 7258 Wsec/cm <sup>2</sup> |

| Static Discharge Voltage<br>(per MIL-STD-883, Method 3015) | >2001V                    |

| Latch-Up Current                                           | >200 mA                   |

## **Operating Range**

| Range                   | Ambient<br>Temperature | v <sub>cc</sub> |

|-------------------------|------------------------|-----------------|

| Commercial              | 0°C to +70°C           | 5V ±10%         |

| Military <sup>[1]</sup> | –55°C to +125°C        | 5V ±10%         |

Note 1.  $T_A$  is the "instant on" case temperature.

|                                |                                   |                                                     |       | 7C265 | 7C265-15, 25 |      | 7C265-40 |      | 7C265-50 |      |

|--------------------------------|-----------------------------------|-----------------------------------------------------|-------|-------|--------------|------|----------|------|----------|------|

| Parameter                      | Description                       | Test Conditions                                     |       | Min.  | Max.         | Min. | Max.     | Min. | Max.     | Unit |

| V <sub>OH</sub>                | Output HIGH Voltage               | $V_{CC}$ = Min., $I_{OH}$ = -2.0 mA                 |       |       |              |      |          |      |          | V    |

|                                |                                   | $V_{CC} = Min., I_{OH} = -4.0 mA$                   | ١     |       |              | 2.4  |          | 2.4  |          |      |

| V <sub>OL</sub>                | Output LOW Voltage                | $V_{CC}$ = Min., $I_{OL}$ = 8.0 mA                  | Com'l |       | 0.4          |      |          |      |          | V    |

|                                |                                   | V <sub>CC</sub> = Min., I <sub>OL</sub> = 12.0 mA   |       |       |              |      | 0.4      |      | 0.4      |      |

|                                |                                   | $V_{CC}$ = Min., $I_{OL}$ = 6.0 mA                  | Mil   |       | 0.4          |      |          |      |          |      |

|                                |                                   | $V_{CC}$ = Min., $I_{OL}$ = 8.0 mA                  |       |       |              |      |          |      | 0.4      |      |

| V <sub>IH</sub>                | Input HIGH Voltage                |                                                     |       | 2.0   |              | 2.0  |          | 2.0  |          | V    |

| V <sub>IL</sub>                | Input LOW Voltage                 |                                                     |       |       | 0.8          |      | 0.8      |      | 0.8      | V    |

| I <sub>IX</sub>                | Input Load Current                | $GND \leq V_{IN} \leq V_{CC}$                       |       | -10   | +10          | -10  | +10      | -10  | +10      | μΑ   |

| I <sub>OZ</sub>                | Output Leakage Current            | $GND \leq V_{OUT} \leq V_{CC}$ ,<br>Output Disabled |       | -40   | +40          | -40  | +40      | -40  | +40      | μΑ   |

| I <sub>OS</sub> <sup>[3]</sup> | Output Short Circuit Current      | V <sub>CC</sub> = Max., V <sub>OUT</sub> = GND      |       |       | 90           |      | 90       |      | 90       | mA   |

| I <sub>CC</sub>                | V <sub>CC</sub> Operating Supply  | V <sub>CC</sub> = Max., I <sub>OUT</sub> = 0 mA     | Com'l |       | 120          |      | 100      |      |          | mA   |

|                                | Current                           |                                                     | Mil   |       |              |      |          |      | 120      |      |

| V <sub>PP</sub>                | Programming Supply Voltage        |                                                     |       | 12    | 13           | 12   | 13       | 12   | 13       | V    |

| I <sub>PP</sub>                | Programming Supply Current        |                                                     |       |       | 50           |      | 50       |      | 50       | mA   |

| V <sub>IHP</sub>               | Input HIGH Programming<br>Voltage |                                                     |       | 3.0   |              | 3.0  |          | 3.0  |          | V    |

| V <sub>ILP</sub>               | Input LOW Programming<br>Voltage  |                                                     |       |       | 0.4          |      | 0.4      |      | 0.4      | V    |

# Electrical Characteristics Over the Operating Range<sup>[2]</sup>

# Capacitance<sup>[4]</sup>

| Parameter        | Description        | Test Conditions                           | Max. | Unit |

|------------------|--------------------|-------------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | $T_{A} = 25^{\circ}C, f = 1 \text{ MHz},$ | 10   | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>CC</sub> = 5.0V                    | 10   | pF   |

Notes

- Notes

See the last page of this specification for Group A subgroup testing information.

For test purposes, not more than one output at a time should be shorted. Short circuit test duration should not exceed 30 seconds.

See Introduction to CMOS PROMs in this Data Book for general information on testing.

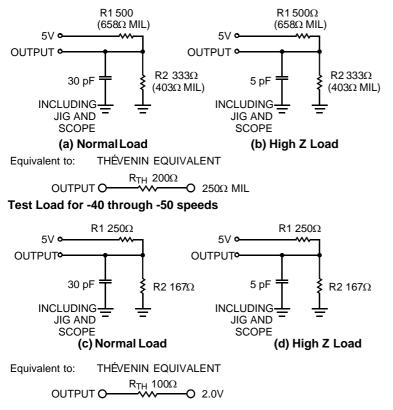

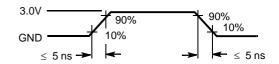

# AC Test Loads and Waveforms

## Test Load for -15 through -25 speeds

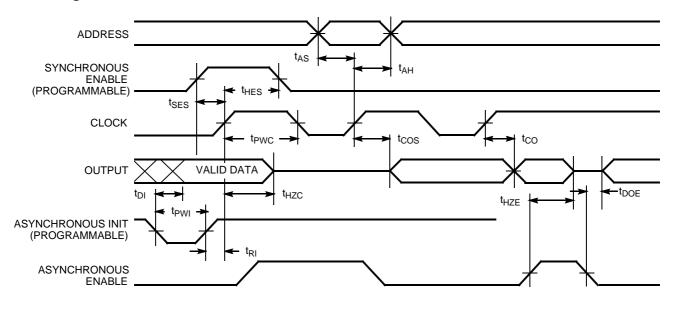

# Switching Characteristics Over the Operating Range<sup>[2, 4]</sup>

|                  |                                                       | 7C2  | 65-15 | 7C20 | 65-25 | 7C20 | 65-40 | 7C2  | 7C265-50 |      |

|------------------|-------------------------------------------------------|------|-------|------|-------|------|-------|------|----------|------|

| Parameter        | Description                                           | Min. | Max.  | Min. | Max.  | Min. | Max.  | Min. | Max.     | Unit |

| t <sub>AS</sub>  | Address Set-Up to Clock                               | 15   |       | 25   |       | 40   |       | 50   |          | ns   |

| t <sub>HA</sub>  | Address Hold from Clock                               | 0    |       | 0    |       | 0    |       | 0    |          | ns   |

| t <sub>CO</sub>  | Clock to Output Valid                                 |      | 12    |      | 15    |      | 20    |      | 25       | ns   |

| t <sub>PWC</sub> | Clock Pulse Width                                     | 12   |       | 15   |       | 15   |       | 20   |          | ns   |

| t <sub>SES</sub> | E <sub>S</sub> Set-Up to Clock<br>(Sync. Enable Only) | 12   |       | 15   |       | 15   |       | 15   |          | ns   |

| t <sub>HES</sub> | E <sub>S</sub> Hold from Clock                        | 5    |       | 5    |       | 5    |       | 5    |          | ns   |

| t <sub>DI</sub>  | INIT to Output Valid                                  |      | 15    |      | 18    |      | 25    |      | 35       | ns   |

| t <sub>RI</sub>  | INIT Recovery to Clock                                | 12   |       | 15   |       | 20   |       | 25   |          | ns   |

| t <sub>PWI</sub> | INIT Pulse Width                                      | 12   |       | 15   |       | 25   |       | 35   |          | ns   |

| t <sub>COS</sub> | Output Valid from Clock<br>(Sync. Mode)               |      | 12    |      | 15    |      | 20    |      | 25       | ns   |

| t <sub>HZC</sub> | Output Inactive from Clock<br>(Sync. Mode)            |      | 12    |      | 15    |      | 20    |      | 25       | ns   |

| t <sub>DOE</sub> | Output Valid from E LOW<br>(Async. Mode)              |      | 12    |      | 15    |      | 20    |      | 25       | ns   |

# **Switching Characteristics** Over the Operating Range<sup>[2, 4]</sup> (continued)

|                  |                                                        | 7C265-15 |      | 7C26 | 7C265-25 7C265-40 |      | 65-40 | 7C265-50 |      |      |

|------------------|--------------------------------------------------------|----------|------|------|-------------------|------|-------|----------|------|------|

| Parameter        | Description                                            | Min.     | Max. | Min. | Max.              | Min. | Max.  | Min.     | Max. | Unit |

| t <sub>HZE</sub> | Output Inactive from $\overline{E}$ HIGH (Async. Mode) |          | 12   |      | 15                |      | 20    |          | 25   | ns   |

## Switching Waveform

## **Erasure Characteristics**

Wavelengths of light less than 4000 angstroms begin to erase the 7C265 in the windowed package. For this reason, an opaque label should be placed over the window if the PROM is exposed to sunlight or fluorescent lighting for extended periods of time.

The recommended dose of ultraviolet light for erasure is a wavelength of 2537 angstroms for a minimum dose (UV intensity • exposure time) of 25 Wsec/cm<sup>2</sup>. For an ultraviolet lamp with a 12 mW/cm<sup>2</sup> power rating the exposure time would be approximately 45 minutes. The 7C265 needs to be within one inch of the lamp during erasure. Permanent damage may result if the PROM is exposed to high-intensity UV light for an extended period of time. 7258 Wsec/cm<sup>2</sup> is the recommended maximum dosage.

## **Bit Map Data**

| Programmer A | Programmer Address (Hex.) |          |  |  |  |  |

|--------------|---------------------------|----------|--|--|--|--|

| Decimal      | Hex                       | Contents |  |  |  |  |

# **Bit Map Data**

| 0                    | 0                    | Data                              |

|----------------------|----------------------|-----------------------------------|

|                      | •                    | •                                 |

| 8191<br>8192<br>8193 | 1FFF<br>2000<br>2001 | Data<br>INIT Byte<br>Control Byte |

Control Byte

- 00 Asynchronous output enable (default condition)

- 01 Synchronous output enable

- 02 Asynchronous initialize

#### **Programming Modes**

The 7C265 offers a limited selection of programmed architectures. Programming these features should be done with a single 10-ms-wide pulse in place of the intelligent algorithm, mainly because these features are verified operationally, not with the VFY pin. Architecture programming is implemented by applying the supervoltage to two additional pins during programming. In programming the 7C265 architecture, VPP is applied to pins 3, 9, and 22. The choice of a particular mode depends on the states of the other pins during programming, so it is important that the condition of the other pins be met as set forth in the mode table. The considerations that apply with

respect to power-up and power-down during intelligent programming also apply during architecture programming. Once the supervoltages have been established and the correct logic states exist on the other device pins,

programming may begin. Programming is accomplished by pulling PGM from HIGH to LOW and then back to HIGH with a pulse width equal to 10 ms.

#### Table 1. Mode Selection

|                         |                        | Pin Function     |                                 |                                 |                  |                                |                                |                  |  |  |  |

|-------------------------|------------------------|------------------|---------------------------------|---------------------------------|------------------|--------------------------------|--------------------------------|------------------|--|--|--|

|                         | Read or Output Disable | A <sub>12</sub>  | A <sub>11</sub>                 | A <sub>10</sub> –A <sub>7</sub> | A <sub>6</sub>   | A <sub>5</sub>                 | $A_4 - A_3$                    | A <sub>2</sub>   |  |  |  |

| Mode                    | Other                  | A <sub>12</sub>  | A <sub>11</sub>                 | A <sub>10</sub> –A <sub>7</sub> | A <sub>6</sub>   | A <sub>5</sub>                 | A <sub>4</sub> –A <sub>3</sub> | A <sub>2</sub>   |  |  |  |

| Asynchron               | A <sub>12</sub>        | A <sub>11</sub>  | A <sub>10</sub> –A <sub>7</sub> | A <sub>6</sub>                  | A <sub>5</sub>   | A <sub>4</sub> -A <sub>3</sub> | A <sub>2</sub>                 |                  |  |  |  |

| Synchronous Enable Read |                        |                  | A <sub>11</sub>                 | A <sub>10</sub> –A <sub>7</sub> | A <sub>6</sub>   | A <sub>5</sub>                 | A <sub>4</sub> -A <sub>3</sub> | A <sub>2</sub>   |  |  |  |

| Asynchron               | A <sub>12</sub>        | A <sub>11</sub>  | A <sub>10</sub> –A <sub>7</sub> | A <sub>6</sub>                  | A <sub>5</sub>   | A <sub>4</sub> -A <sub>3</sub> | A <sub>2</sub>                 |                  |  |  |  |

| Program M               | lemory                 | A <sub>12</sub>  | A <sub>11</sub>                 | A <sub>10</sub> –A <sub>7</sub> | A <sub>6</sub>   | A <sub>5</sub>                 | A <sub>4</sub> -A <sub>3</sub> | A <sub>2</sub>   |  |  |  |

| Program V               | 'erify                 | A <sub>12</sub>  | A <sub>11</sub>                 | A <sub>10</sub> –A <sub>7</sub> | A <sub>6</sub>   | A <sub>5</sub>                 | A <sub>4</sub> -A <sub>3</sub> | A <sub>2</sub>   |  |  |  |

| Program Ir              | nhibit                 | A <sub>12</sub>  | A <sub>11</sub>                 | A <sub>10</sub> –A <sub>7</sub> | A <sub>6</sub>   | A <sub>5</sub>                 | A <sub>4</sub> -A <sub>3</sub> | A <sub>2</sub>   |  |  |  |

| Program S               | synchronous Enable     | V <sub>IHP</sub> | V <sub>IHP</sub>                | A <sub>10</sub> –A <sub>7</sub> | V <sub>IHP</sub> | V <sub>PP</sub>                | A <sub>4</sub> -A <sub>3</sub> | V <sub>IHP</sub> |  |  |  |

| Program Initialize      |                        | V <sub>ILP</sub> | V <sub>IHP</sub>                | A <sub>10</sub> –A <sub>7</sub> | V <sub>IHP</sub> | V <sub>PP</sub>                | $A_4 - A_3$                    | V <sub>ILP</sub> |  |  |  |

| Program Initial Byte    |                        | A <sub>12</sub>  | V <sub>ILP</sub>                | $A_{10} - A_7$                  | V <sub>IHP</sub> | V <sub>PP</sub>                | $A_4 - A_3$                    | V <sub>ILP</sub> |  |  |  |

|            |                         |                 |                  |                  | Pin Fu                           | Inction          |                 |                                |

|------------|-------------------------|-----------------|------------------|------------------|----------------------------------|------------------|-----------------|--------------------------------|

|            | Read or Output Disable  | A <sub>1</sub>  | A <sub>0</sub>   | GND              | CLK                              | GND              | Ē, Ī            | 0 <sub>7</sub> –0 <sub>0</sub> |

| Mode       | Other                   | A <sub>1</sub>  | A <sub>0</sub>   | PGM              | CLK                              | VFY              | V <sub>PP</sub> | D <sub>7</sub> D <sub>0</sub>  |

| Asynchron  | ous Enable Read         | A <sub>1</sub>  | A <sub>0</sub>   | GND              | V <sub>IL</sub>                  | GND              | V <sub>IL</sub> | O <sub>7</sub> –O <sub>0</sub> |

| Synchrono  | us Enable Read          | A <sub>1</sub>  | A <sub>0</sub>   | GND              | V <sub>IL</sub> /V <sub>IH</sub> | GND              | V <sub>IL</sub> | O <sub>7</sub> –O <sub>0</sub> |

| Asynchron  | ous Initialization Read | A <sub>1</sub>  | A <sub>0</sub>   | GND              | V <sub>IL</sub>                  | GND              | V <sub>IL</sub> | O <sub>7</sub> –O <sub>0</sub> |

| Program M  | lemory                  | A <sub>1</sub>  | A <sub>0</sub>   | V <sub>ILP</sub> | V <sub>ILP</sub>                 | V <sub>IHP</sub> | V <sub>PP</sub> | D <sub>7</sub> –D <sub>0</sub> |

| Program V  | erify                   | A <sub>1</sub>  | A <sub>0</sub>   | V <sub>IHP</sub> | V <sub>ILP</sub>                 | V <sub>ILP</sub> | V <sub>PP</sub> | O <sub>7</sub> –O <sub>0</sub> |

| Program Ir | hibit                   | A <sub>1</sub>  | A <sub>0</sub>   | V <sub>IHP</sub> | V <sub>ILP</sub>                 | V <sub>IHP</sub> | V <sub>PP</sub> | High Z                         |

| Program S  | ynchronous Enable       | V <sub>PP</sub> | V <sub>ILP</sub> | V <sub>ILP</sub> | V <sub>ILP</sub>                 | V <sub>IHP</sub> | V <sub>PP</sub> | D <sub>7</sub> D <sub>0</sub>  |

| Program Ir | nitialize               | V <sub>PP</sub> | V <sub>ILP</sub> | V <sub>ILP</sub> | V <sub>ILP</sub>                 | V <sub>IHP</sub> | V <sub>PP</sub> | D <sub>7</sub> D <sub>0</sub>  |

| Program Ir | nitial Byte             | V <sub>PP</sub> | V <sub>IHP</sub> | V <sub>ILP</sub> | V <sub>ILP</sub>                 | V <sub>IHP</sub> | V <sub>PP</sub> | D <sub>7</sub> D <sub>0</sub>  |

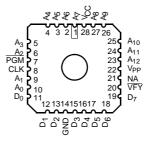

#### Figure 1. Programming Pinout

LCC/PLCC (Opaque Only)

# **Programming Information**

Programming support is available from Cypress as well as from a number of third-party software vendors. For detailed

programming information, including a listing of software packages, please see the PROM Programming Information located at the end of this section. Programming algorithms can be obtained from any Cypress representative.

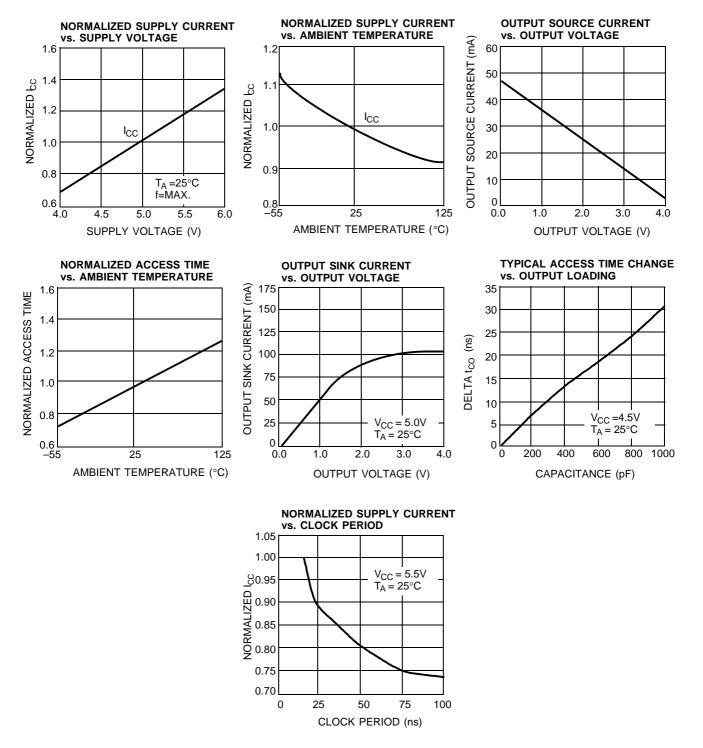

# **Typical DC and AC Characteristics**

# **Ordering Information**

| Speed<br>(ns) | I <sub>CC</sub><br>(mA) | Ordering Code | Package<br>Name | Package Type                        | Operating<br>Range |

|---------------|-------------------------|---------------|-----------------|-------------------------------------|--------------------|

| 15            | 120                     | CY7C265-15JC  | J64             | 28-Lead Plastic Leaded Chip Carrier | Commercial         |

|               |                         | CY7C265-15WC  | W22             | 28-Lead (300-Mil) Windowed CerDIP   |                    |

| 25            | 120                     | CY7C265-25WC  | W22             | 28-Lead (300-Mil) Windowed CerDIP   | Commercial         |

| 40            | 100                     | CY7C265-40PC  | P21             | 28-Lead (300-Mil) Molded DIP        | Commercial         |

# MILITARY SPECIFICATIONS Group A Subgroup Testing

## **DC Characteristics**

| Parameter       | Subgroups |

|-----------------|-----------|

| V <sub>OH</sub> | 1, 2, 3   |

| V <sub>OL</sub> | 1, 2, 3   |

| V <sub>IH</sub> | 1, 2, 3   |

| V <sub>IL</sub> | 1, 2, 3   |

| I <sub>IX</sub> | 1, 2, 3   |

| I <sub>OZ</sub> | 1, 2, 3   |

| I <sub>CC</sub> | 1, 2, 3   |

# **Switching Characteristics**

| Parameter        | Subgroups       |

|------------------|-----------------|

| t <sub>AS</sub>  | 7, 8, 9, 10, 11 |

| t <sub>HA</sub>  | 7, 8, 9, 10, 11 |

| t <sub>CO</sub>  | 7, 8, 9, 10, 11 |

| t <sub>PW</sub>  | 7, 8, 9, 10, 11 |

| t <sub>SES</sub> | 7, 8, 9, 10, 11 |

| t <sub>HES</sub> | 7, 8, 9, 10, 11 |

| t <sub>COS</sub> | 7, 8, 9, 10, 11 |

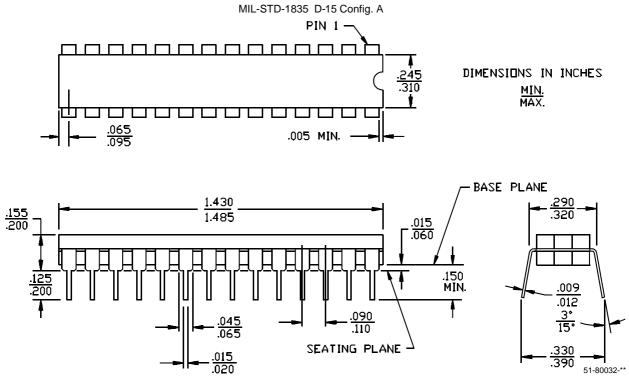

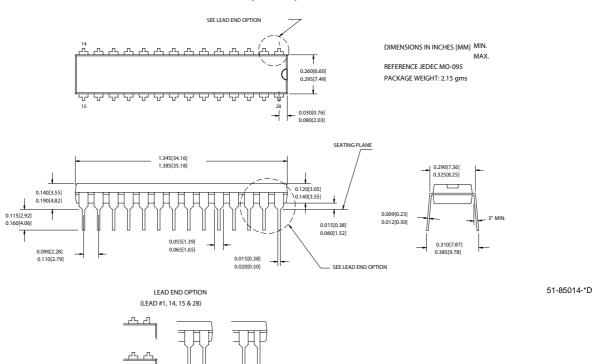

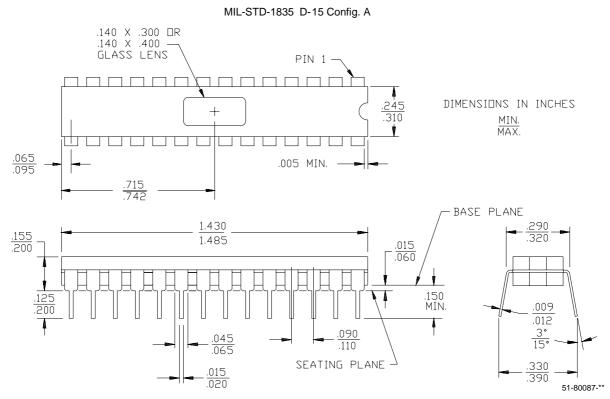

# **Package Diagrams**

Figure 2. 28-Lead (300-Mil) CerDIP D22

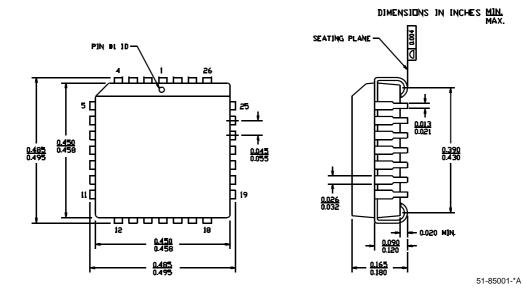

Figure 3. 28-Lead Plastic Leaded Chip Carrier J64

# Package Diagrams (continued) Figure 4. 28-Lead (300-Mil) Molded DIP P21

#### 28-Lead (300-Mil) PDIP P21

## Package Diagrams (continued)

#### Figure 5. 28-Lead (300-Mil) Windowed CerDIP W22

All product and company names mentioned in this document may be the trademarks of their respective holders.

#### Document #: 38-04012 Rev. \*B

© Cypress Semiconductor Corporation, 2006. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

# **Document History Page**

| Document Title: CY7C265 8K x 8 Registered PROM<br>Document Number: 38-04012 |         |               |                    |                                                |

|-----------------------------------------------------------------------------|---------|---------------|--------------------|------------------------------------------------|

| REV.                                                                        | ECN NO. | Issue<br>Date | Orig. of<br>Change | Description of Change                          |

| **                                                                          | 114139  | 03/18/02      | DSG                | Changed from Spec number: 38-00084 to 38-04012 |

| *A                                                                          | 118896  | 10/09/02      | GBI                | Updated ordering information                   |

| *В                                                                          | 499562  | See ECN       | PCI                | Updated ordering information                   |