## Ultra37000 CPLD Family

### **Contents**

| Logic Block Diagrams                       | 3  |

|--------------------------------------------|----|

| Selection Guide                            | 6  |

| 5 V Selection Guide                        | 6  |

| 3.3 V Selection Guide                      | 7  |

| Pin Configurations                         | 8  |

| Architecture Overview of Ultra37000 Family |    |

| Programmable Interconnect Matrix           | 13 |

| Logic Block                                | 13 |

| Product Term Allocator                     | 14 |

| Ultra37000 Macrocell                       | 14 |

| Clocking                                   | 16 |

| Timing Model                               | 16 |

| JTAG and PCI Standards                     | 17 |

| PCI Compliance                             | 17 |

| IEEE 1149.1-compliant JTAG                 | 17 |

| Development Software Support               | 17 |

| Warp                                       |    |

| Warp Professional™                         |    |

| Warp Enterprise™                           | 17 |

| Third-Party Software                       |    |

| Programming                                | 17 |

| Third-Party Programmers                    | 18 |

| 5 V Device Maximum Ratings                 | 19 |

| Operating Range                            |    |

| 5 V Device Electrical Characteristics      |    |

| Inductance                                 | 20 |

| Capacitance                                | 20 |

| Endurance Characteristics               | 20 |

|-----------------------------------------|----|

| 3.3 V Device Maximum Ratings            | 21 |

| Operating Range                         |    |

| 3.3 V Device Electrical Characteristics | 21 |

| Inductance                              | 22 |

| Capacitance                             | 22 |

| Endurance Characteristics               | 22 |

| AC Test Loads and Waveforms             | 23 |

| Switching Characteristics               | 25 |

| Switching Characteristics               | 27 |

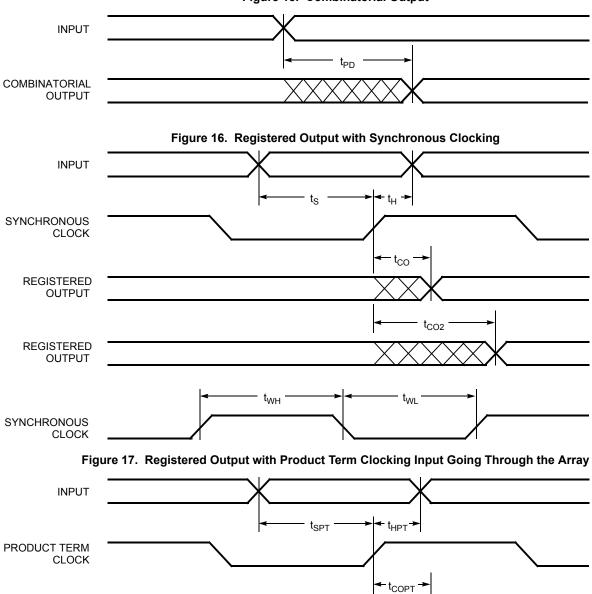

| Switching Waveforms                     | 30 |

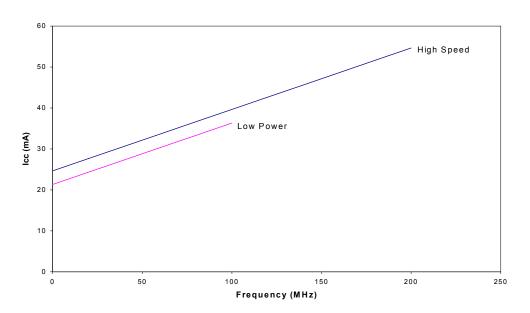

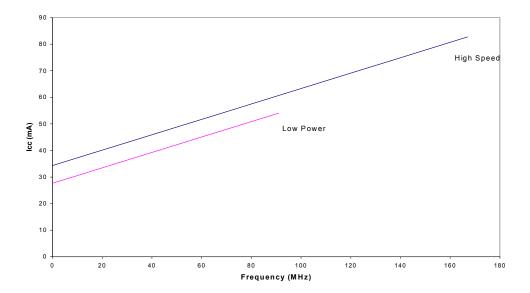

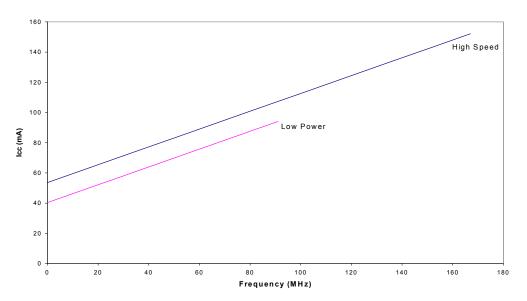

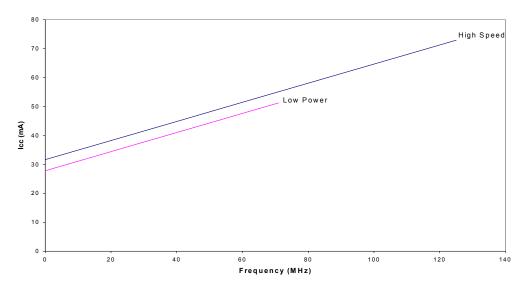

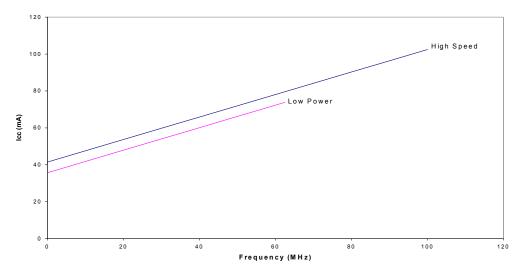

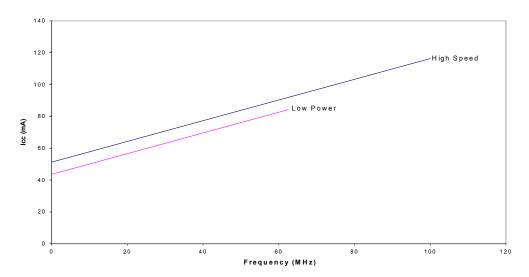

| Power Consumption                       | 34 |

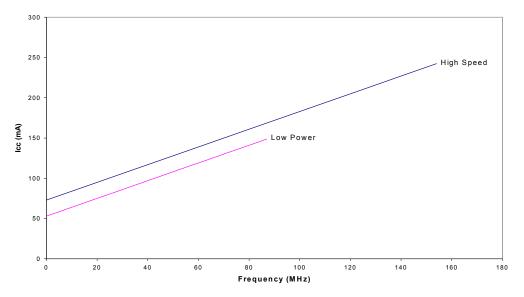

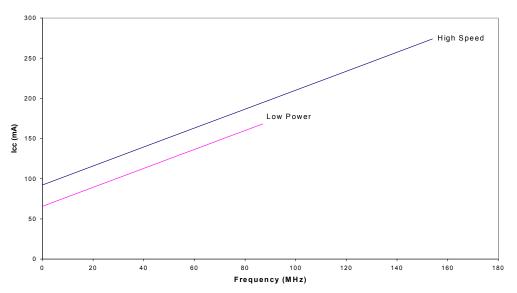

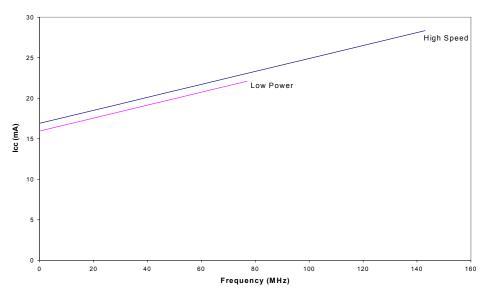

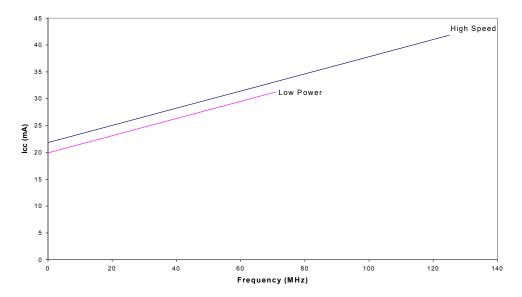

| Typical 5 V Power Consumption           |    |

| Typical 3.3 V Power Consumption         | 37 |

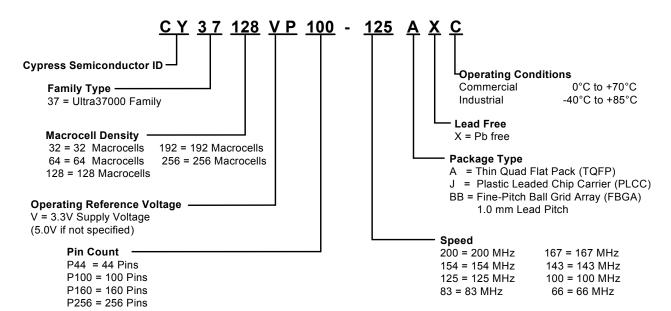

| Ordering Information                    | 40 |

| 5 V Ordering Information                | 40 |

| 3.3 V Ordering Information              | 40 |

| Ordering Code Definitions               | 41 |

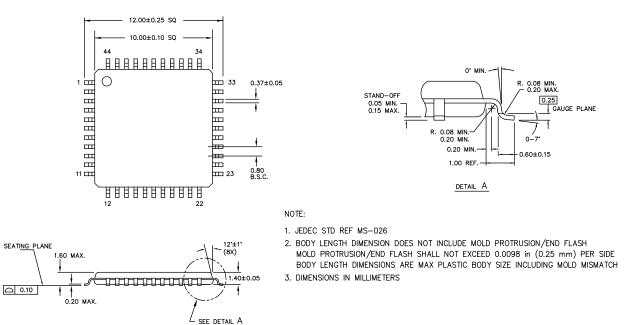

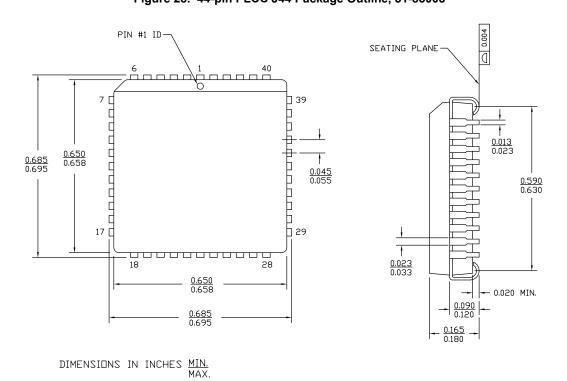

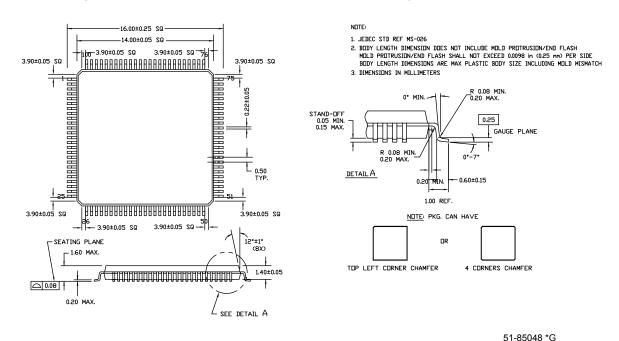

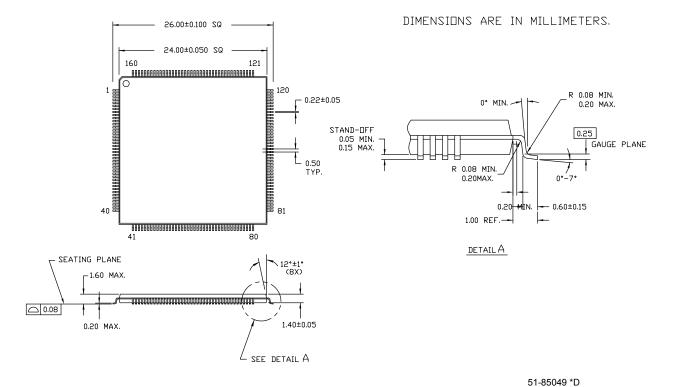

| Package Diagrams                        |    |

| Acronyms                                |    |

| Document Conventions                    | 45 |

| Units of Measure                        | 45 |

| Document History Page                   | 46 |

| Sales, Solutions, and Legal Information | 50 |

| Worldwide Sales and Design Support      | 50 |

| Products                                | 50 |

| PSoC Solutions                          | 50 |

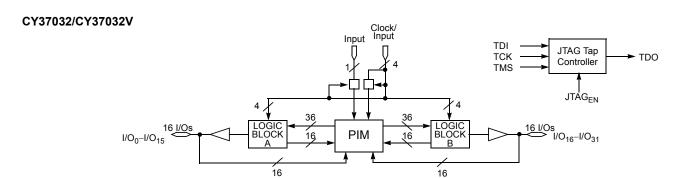

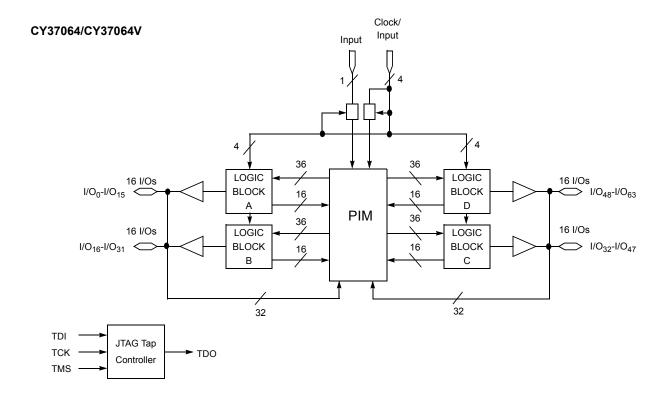

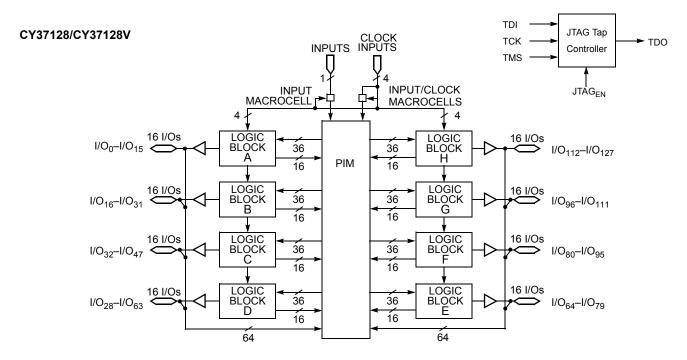

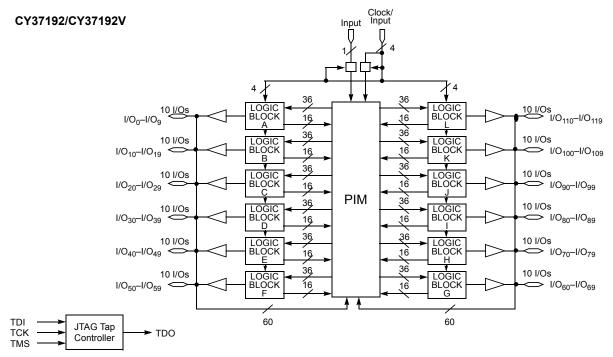

### **Logic Block Diagrams**

### Logic Block Diagrams (continued)

### **Logic Block Diagrams** (continued)

### **Selection Guide**

### **5 V Selection Guide**

**Table 1. General Information**

| Device  | Macrocells | Dedicated<br>Inputs | I/O Pins    | Speed (t <sub>PD</sub> ) | Speed (f <sub>MAX</sub> ) |

|---------|------------|---------------------|-------------|--------------------------|---------------------------|

| CY37032 | 32         | 5                   | 32          | 6                        | 200                       |

| CY37064 | 64         | 5                   | 32/64       | 6                        | 200                       |

| CY37128 | 128        | 5                   | 64/128      | 6.5                      | 167                       |

| CY37192 | 192        | 5                   | 120         | 7.5                      | 154                       |

| CY37256 | 256        | 5                   | 128/160/192 | 7.5                      | 154                       |

Table 2. Speed Bins

| Device  | 200 | 167 | 154 | 125 | 100 | 83 |

|---------|-----|-----|-----|-----|-----|----|

| CY37032 |     |     | X   | Х   |     |    |

| CY37064 | Х   |     | Х   | Х   |     |    |

| CY37128 |     | Х   |     | Х   | Х   |    |

| CY37192 |     |     |     | Х   |     | Х  |

| CY37256 |     |     |     | Х   |     | Х  |

Table 3. Device-Package Offering and I/O Count

| Device  | 44-pin TQFP | 44-pin PLCC | 100-pin TQFP | 160-pin TQFP |

|---------|-------------|-------------|--------------|--------------|

| CY37032 | 37          | 37          |              |              |

| CY37064 | 37          | 37          | 69           |              |

| CY37128 |             |             | 69           | 133          |

| CY37192 |             |             |              | 125          |

| CY37256 |             |             |              | 133          |

### 3.3 V Selection Guide

### **Table 4. General Information**

| Device   | Macrocells | Dedicated<br>Inputs | I/O Pins    | Speed (t <sub>PD</sub> ) | Speed (f <sub>MAX</sub> ) |

|----------|------------|---------------------|-------------|--------------------------|---------------------------|

| CY37032V | 32         | 5                   | 32          | 8.5                      | 143                       |

| CY37064V | 64         | 5                   | 32/64       | 8.5                      | 143                       |

| CY37128V | 128        | 5                   | 64/80/128   | 10                       | 125                       |

| CY37192V | 192        | 5                   | 120         | 12                       | 100                       |

| CY37256V | 256        | 5                   | 128/160/192 | 12                       | 100                       |

### Table 5. Speed Bins

| Device   | 143 | 125 | 100 | 83 | 66 |

|----------|-----|-----|-----|----|----|

| CY37032V | Х   |     | X   |    |    |

| CY37064V | X   |     | X   |    |    |

| CY37128V |     | Х   |     | Х  |    |

| CY37192V |     |     | X   |    | Х  |

| CY37256V |     |     | X   |    | X  |

### Table 6. Device-Package Offering and I/O Count

| Device   | 44-pin TQFP | 100-pin TQFP | 160-pin TQFP | 256-ball FBGA |

|----------|-------------|--------------|--------------|---------------|

| CY37032V | 37          |              |              |               |

| CY37064V | 37          | 69           |              |               |

| CY37128V |             | 69           | 133          |               |

| CY37192V |             |              | 125          |               |

| CY37256V |             |              | 133          | 197           |

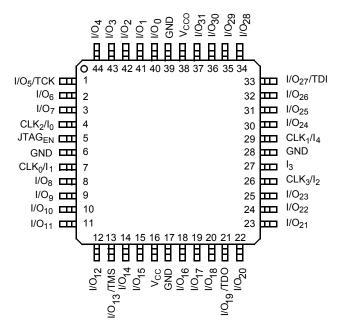

### **Pin Configurations**

The Pin Configurations are as follows. [2]

Figure 1. 44-pin TQFP pinout (Top View)

Figure 2. 44-pin PLCC pinout (Top View)

Note

2. For 3.3 V versions (Ultra37000V),  $V_{CCO} = V_{CC}$ .

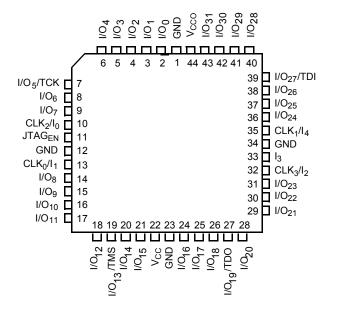

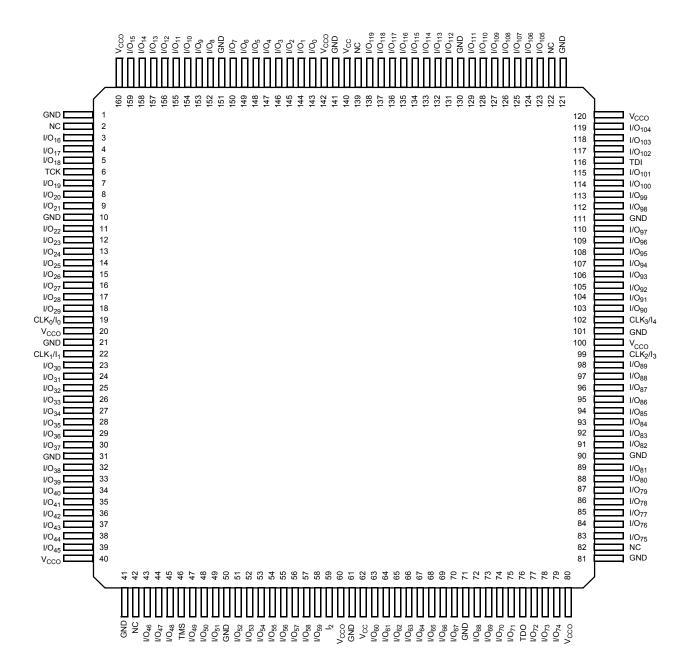

The Pin Configurations are as follows. [2]

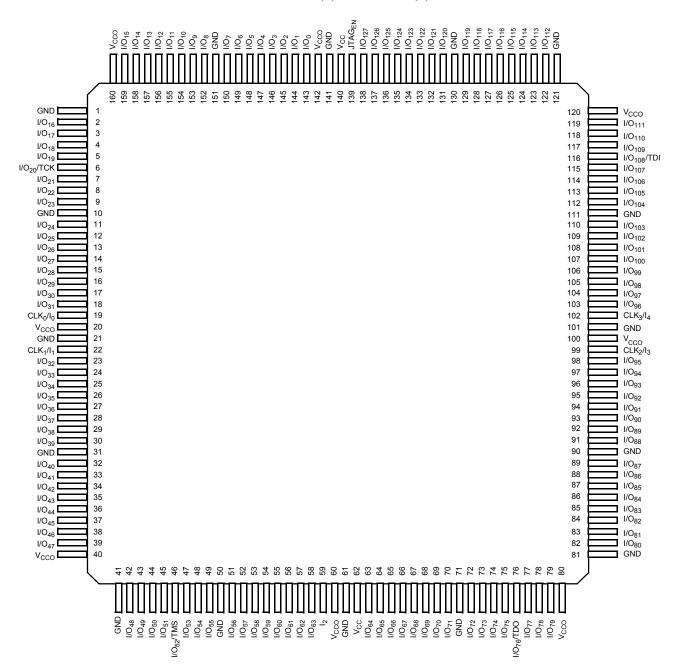

Figure 3. 100-pin TQFP pinout (Top View)

### Note

3. This pin is a N/C, but Cypress recommends that you connect it to  $V_{CC}$  to ensure future compatibility.

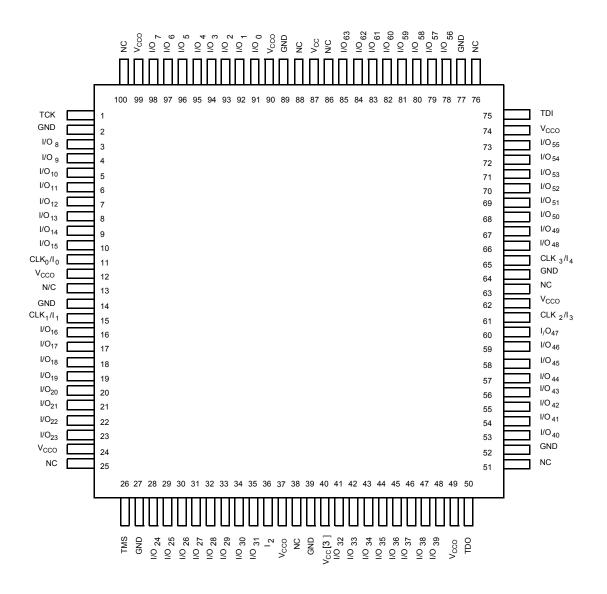

The Pin Configurations are as follows. [2]

Figure 4. 160-pin TQFP pinout (Top View)

For CY37128(V) and CY37256(V)

The Pin Configurations are as follows. [2]

Figure 5. 160-pin TQFP pinout (Top View)

For CY37192(V)

The Pin Configurations are as follows. [2]

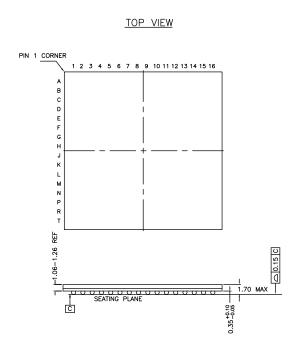

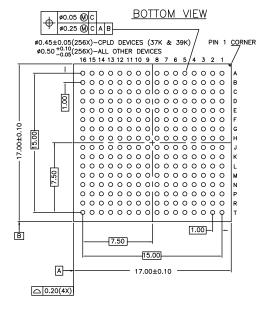

Figure 6. 256-ball FBGA pinout (Top View)

|   | 1                 | 2                 | 3                 | 4                 | 5                                    | 6                 | 7                 | 8                 | 9                  | 10                 | 11                 | 12                                   | 13                 | 14                 | 15                 | 16                 |

|---|-------------------|-------------------|-------------------|-------------------|--------------------------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--------------------|--------------------------------------|--------------------|--------------------|--------------------|--------------------|

| Α | GND               | GND               | I/O <sub>26</sub> | I/O <sub>24</sub> | I/O <sub>20</sub>                    | V <sub>CC</sub>   | I/O <sub>11</sub> | GND               | GND                | I/O <sub>186</sub> | V <sub>CC</sub>    | I/O <sub>177</sub>                   | I/O <sub>172</sub> | I/O <sub>167</sub> | GND                | GND                |

| В | GND               | I/O <sub>27</sub> | I/O <sub>25</sub> | I/O <sub>23</sub> | I/O <sub>19</sub>                    | I/O <sub>15</sub> | I/O <sub>10</sub> | GND               | GND                | I/O <sub>185</sub> | I/O <sub>181</sub> | I/O <sub>176</sub>                   | I/O <sub>171</sub> | I/O <sub>166</sub> | I/O <sub>165</sub> | GND                |

| С | I/O <sub>29</sub> | I/O <sub>28</sub> | NC                | I/O <sub>22</sub> | I/O <sub>18</sub>                    | I/O <sub>14</sub> | I/O <sub>9</sub>  | I/O <sub>4</sub>  | I/O <sub>191</sub> | I/O <sub>184</sub> | I/O <sub>180</sub> | I/O <sub>175</sub>                   | I/O <sub>170</sub> | NC                 | I/O <sub>163</sub> | I/O <sub>164</sub> |

| D | I/O <sub>32</sub> | I/O <sub>31</sub> | I/O <sub>30</sub> | NC                | I/O <sub>17</sub>                    | I/O <sub>13</sub> | I/O <sub>8</sub>  | I/O <sub>3</sub>  | I/O <sub>190</sub> | I/O <sub>183</sub> | I/O <sub>179</sub> | I/O <sub>174</sub>                   | I/O <sub>169</sub> | I/O <sub>160</sub> | I/O <sub>161</sub> | I/O <sub>162</sub> |

| E | I/O <sub>35</sub> | I/O <sub>34</sub> | I/O <sub>33</sub> | I/O <sub>21</sub> | I/O <sub>16</sub>                    | I/O <sub>12</sub> | I/O <sub>7</sub>  | I/O <sub>2</sub>  | I/O <sub>189</sub> | V <sub>CC</sub>    | I/O <sub>178</sub> | I/O <sub>173</sub>                   | I/O <sub>168</sub> | I/O <sub>157</sub> | I/O <sub>158</sub> | I/O <sub>159</sub> |

| F | V <sub>CC</sub>   | I/O <sub>38</sub> | I/O <sub>37</sub> | I/O <sub>36</sub> | TCK                                  | V <sub>CC</sub>   | I/O <sub>6</sub>  | I/O <sub>1</sub>  | I/O <sub>188</sub> | I/O <sub>182</sub> | V <sub>CC</sub>    | TDI                                  | I/O <sub>154</sub> | I/O <sub>155</sub> | I/O <sub>156</sub> | V <sub>CC</sub>    |

| G | I/O <sub>43</sub> | I/O <sub>42</sub> | I/O <sub>41</sub> | I/O <sub>40</sub> | V <sub>CC</sub>                      | I/O <sub>39</sub> | I/O <sub>5</sub>  | I/O <sub>0</sub>  | I/O <sub>187</sub> | I/O <sub>148</sub> | I/O <sub>149</sub> | CLK <sub>3</sub><br>/ I <sub>4</sub> | I/O <sub>150</sub> | I/O <sub>151</sub> | I/O <sub>152</sub> | I/O <sub>153</sub> |

| Н | GND               | GND               | I/O <sub>47</sub> | I/O <sub>46</sub> | CLK <sub>0</sub><br>/ I <sub>0</sub> | I/O <sub>45</sub> | I/O <sub>44</sub> | GND               | GND                | I/O <sub>144</sub> | I/O <sub>145</sub> | CLK <sub>2</sub><br>/ I <sub>3</sub> | I/O <sub>146</sub> | I/O <sub>147</sub> | GND                | GND                |

| J | GND               | GND               | I/O <sub>51</sub> | I/O <sub>50</sub> | NC                                   | I/O <sub>49</sub> | I/O <sub>48</sub> | GND               | GND                | I/O <sub>140</sub> | I/O <sub>141</sub> | l <sub>2</sub>                       | I/O <sub>142</sub> | I/O <sub>143</sub> | GND                | GND                |

| K | I/O <sub>57</sub> | I/O <sub>56</sub> | I/O <sub>55</sub> | I/O <sub>54</sub> | CLK <sub>1</sub><br>/ I <sub>1</sub> | I/O <sub>53</sub> | I/O <sub>52</sub> | I/O <sub>91</sub> | I/O <sub>96</sub>  | I/O <sub>101</sub> | I/O <sub>135</sub> | V <sub>CC</sub>                      | I/O <sub>136</sub> | I/O <sub>137</sub> | I/O <sub>138</sub> | I/O <sub>139</sub> |

| L | V <sub>CC</sub>   | I/O <sub>60</sub> | I/O <sub>59</sub> | I/O <sub>58</sub> | TMS                                  | V <sub>CC</sub>   | I/O <sub>86</sub> | I/O <sub>92</sub> | I/O <sub>97</sub>  | I/O <sub>102</sub> | V <sub>CC</sub>    | TDO                                  | I/O <sub>132</sub> | I/O <sub>133</sub> | I/O <sub>134</sub> | V <sub>CC</sub>    |

| М | I/O <sub>63</sub> | I/O <sub>62</sub> | I/O <sub>61</sub> | I/O <sub>72</sub> | I/O <sub>77</sub>                    | I/O <sub>82</sub> | V <sub>CC</sub>   | I/O <sub>93</sub> | I/O <sub>98</sub>  | I/O <sub>103</sub> | I/O <sub>108</sub> | I/O <sub>112</sub>                   | I/O <sub>117</sub> | I/O <sub>129</sub> | I/O <sub>130</sub> | I/O <sub>131</sub> |

| N | I/O <sub>66</sub> | I/O <sub>65</sub> | I/O <sub>64</sub> | I/O <sub>73</sub> | I/O <sub>78</sub>                    | I/O <sub>83</sub> | I/O <sub>87</sub> | I/O <sub>94</sub> | I/O <sub>99</sub>  | I/O <sub>104</sub> | I/O <sub>109</sub> | I/O <sub>113</sub>                   | NC                 | I/O <sub>126</sub> | I/O <sub>127</sub> | I/O <sub>128</sub> |

| Р | I/O <sub>68</sub> | I/O <sub>67</sub> | NC                | I/O <sub>74</sub> | I/O79                                | I/O <sub>84</sub> | I/O <sub>88</sub> | I/O <sub>95</sub> | I/O <sub>100</sub> | I/O <sub>105</sub> | I/O <sub>110</sub> | I/O <sub>114</sub>                   | I/O <sub>118</sub> | NC                 | I/O <sub>124</sub> | I/O <sub>125</sub> |

| R | GND               | I/O <sub>69</sub> | I/O <sub>70</sub> | I/O <sub>75</sub> | I/O <sub>80</sub>                    | I/O <sub>85</sub> | I/O <sub>89</sub> | GND               | GND                | I/O <sub>106</sub> | I/O <sub>111</sub> | I/O <sub>115</sub>                   | I/O <sub>119</sub> | I/O <sub>121</sub> | I/O <sub>123</sub> | GND                |

| Т | GND               | GND               | I/O <sub>71</sub> | I/O <sub>76</sub> | I/O <sub>81</sub>                    | V <sub>CC</sub>   | I/O <sub>90</sub> | GND               | GND                | I/O <sub>107</sub> | V <sub>CC</sub>    | I/O <sub>116</sub>                   | I/O <sub>120</sub> | I/O <sub>122</sub> | GND                | GND                |

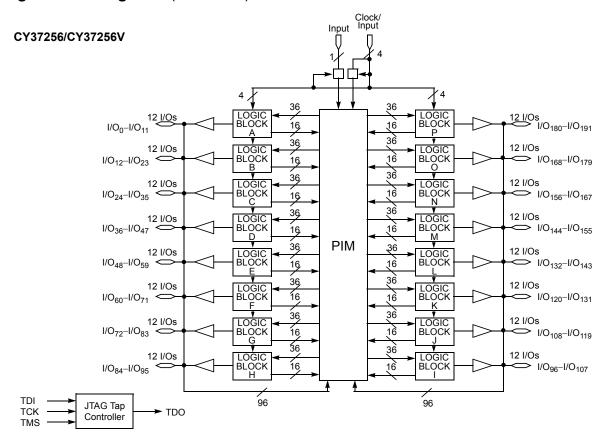

### **Architecture Overview of Ultra37000 Family**

### **Programmable Interconnect Matrix**

The PIM consists of a completely global routing matrix for signals from I/O pins and feedbacks from the logic blocks. The PIM provides extremely robust interconnection to avoid fitting and density limitations.

The inputs to the PIM consist of all I/O and dedicated input pins and all macrocell feedbacks from within the logic blocks. The number of PIM inputs increases with pin count and the number of logic blocks. The outputs from the PIM are signals routed to the appropriate logic blocks. Each logic block receives 36 inputs from the PIM and their complements, allowing for 32-bit operations to be implemented in a single pass through the device. The wide number of inputs to the logic block also improves the routing capacity of the Ultra37000 family.

An important feature of the PIM is its simple timing. The propagation delay through the PIM is accounted for in the timing specifications for each device. There is no additional delay for traveling through the PIM. In fact, all inputs travel through the PIM. As a result, there are no route-dependent timing parameters on the Ultra37000 devices. The worst-case PIM delays are incorporated in all appropriate Ultra37000 specifications.

Routing signals through the PIM is completely invisible to the user. All routing is accomplished by software — no hand routing is necessary. Warp<sup>®</sup> and third-party development packages automatically route designs for the Ultra37000 family in a matter of minutes. Finally, the rich routing resources of the Ultra37000 family accommodate last minute logic changes while maintaining fixed pin assignments.

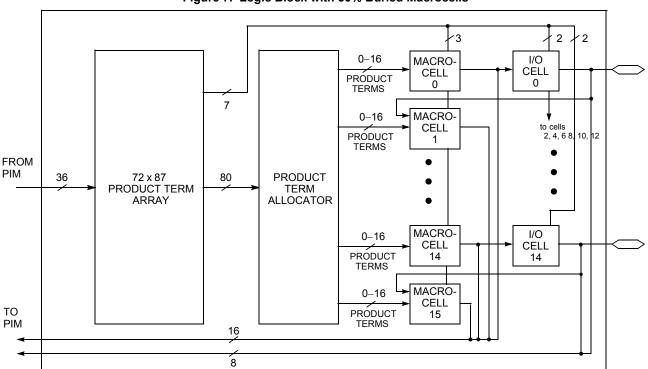

### Logic Block

The logic block is the basic building block of the Ultra37000 architecture. It consists of a product term array, an intelligent product-term allocator, 16 macrocells, and a number of I/O cells. The number of I/O cells varies depending on the device used. Refer to Figure 7 for the block diagram.

### Product Term Array

Each logic block features a 72  $\times$  87 programmable product term array. This array accepts 36 inputs from the PIM, which originate from macrocell feedbacks and device pins. Active LOW and active HIGH versions of each of these inputs are generated to create the full 72-input field. The 87 product terms in the array can be created from any of the 72 inputs.

Of the 87 product terms, 80 are for general-purpose use for the 16 macrocells in the logic block. Four of the remaining seven product terms in the logic block are output enable (OE) product terms. Each of the OE product terms controls up to eight of the 16 macrocells and is selectable on an individual macrocell basis. In other words, each I/O cell can select between one of two OE product terms to control the output buffer. The first two of these four OE product terms are available to the upper half of the I/O macrocells in a logic block. The other two OE product terms are available to the lower half of the I/O macrocells in a logic block.

The next two product terms in each logic block are dedicated asynchronous set and asynchronous reset product terms. The final product term is the product term clock. The set, reset, OE and product term clock have polarity control to realize OR functions in a single pass through the array.

Figure 7. Logic Block with 50% Buried Macrocells

### Low Power Option

Each logic block can operate in high speed mode for critical path performance, or in low power mode for power conservation. The logic block mode is set by the user on a logic block by logic block basis.

### **Product Term Allocator**

Through the product term allocator, software automatically distributes product terms among the 16 macrocells in the logic block as needed. A total of 80 product terms are available from the local product term array. The product term allocator provides two important capabilities without affecting performance: product term steering and product term sharing.

### Product Term Steering

Product term steering is the process of assigning product terms to macrocells as needed. For example, if one macrocell requires ten product terms while another needs just three, the product term allocator will "steer" ten product terms to one macrocell and three to the other. On Ultra37000 devices, product terms are steered on an individual basis. Any number between 0 and 16 product terms can be steered to any macrocell. Note that 0 product terms is useful in cases where a particular macrocell is unused or used as an input register.

### Product Term Sharing

Product term sharing is the process of using the same product term among multiple macrocells. For example, if more than one output has one or more product terms in its equation that are common to other outputs, those product terms are only programmed once. The Ultra37000 product term allocator allows sharing across groups of four output macrocells in a variable fashion. The software automatically takes advantage of this capability—the user does not have to intervene.

Note that neither product term sharing nor product term steering have any effect on the speed of the product. All worst-case steering and sharing configurations are incorporated in the timing specifications for the Ultra37000 devices.

### Ultra37000 Macrocell

Within each logic block there are 16 macrocells. Macrocells can either be I/O Macrocells, which include an I/O Cell which is associated with an I/O pin, or buried Macrocells, which do not connect to an I/O. The combination of I/O Macrocells and buried Macrocells varies from device to device.

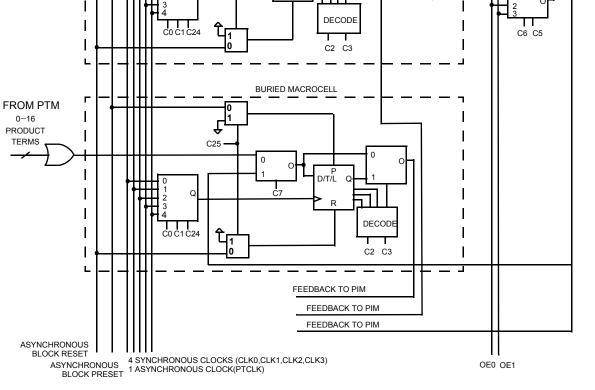

### Buried Macrocell

Figure 8 displays the architecture of buried macrocells. The buried macrocell features a register that can be configured as combinatorial, a D flip-flop, a T flip-flop, or a level-triggered latch.

The register can be asynchronously set or asynchronously reset at the logic block level with the separate set and reset product terms. Each of these product terms features programmable polarity. This allows the registers to be set or reset based on an AND expression or an OR expression.

Clocking of the register is very flexible. Four global synchronous clocks and a product term clock are available to clock the register. Furthermore, each clock features programmable polarity so that registers can be triggered on falling and rising edges (see Clocking on page 16). Clock polarity is chosen at the logic block level.

The buried macrocell also supports input register capability. The buried macrocell can be configured to act as an input register (D-type or latch) whose input comes from the I/O pin associated with the neighboring macrocell. The output of all buried macrocells is sent directly to the PIM regardless of its configuration.

### I/O Macrocell

Figure 8 on page 15 illustrates the architecture of the I/O macrocell. The I/O macrocell supports the same functions as the buried macrocell with the addition of I/O capability. At the output of the macrocell, a polarity control mux is available to select active LOW or active HIGH signals. This has the added advantage of allowing significant logic reduction to occur in many applications.

The Ultra37000 macrocell features a feedback path to the PIM separate from the I/O pin input path. This means that if the macrocell is buried (fed back internally only), the associated I/O pin can still be used as an input.

### Bus Hold Capabilities on all I/Os

Bus-hold, which is an improved version of the popular internal pull-up resistor, is a weak latch connected to the pin that does not degrade the device's performance. As a latch, bus-hold maintains the last state of a pin when the pin is placed in a high impedance state, thus reducing system noise in bus-interface applications. Bus-hold additionally allows unused device pins to remain unconnected on the board, which is particularly useful during prototyping as designers can route new signals to the device without cutting trace connections to  $V_{\rm CC}$  or GND. For more information, see the application note  $\it Understanding Bus-Hold - A Feature of Cypress CPLDs.$

### Programmable Slew Rate Control

Each output has a programmable configuration bit, which sets the output slew rate to fast or slow. For designs concerned with meeting FCC emissions standards the slow edge provides for lower system noise. For designs requiring very high performance the fast edge rate provides maximum system performance.

1 C26

I/O CELL

I/O MACROCELL FAST. FROM PTM SLEV 0-16 PRODUCT C25 TERMS D/T/L DECODE C2 C3

Figure 8. I/O and Buried Macrocells

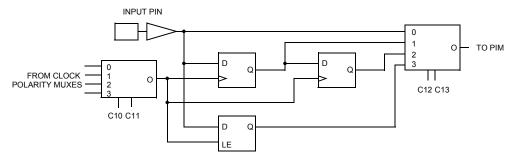

Figure 9. Input Macrocell

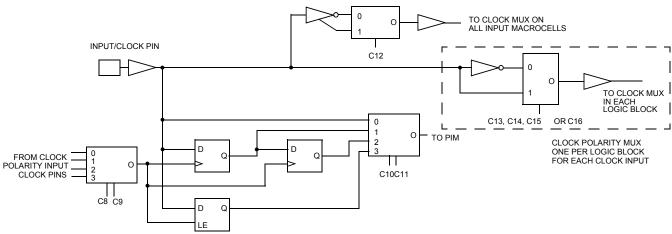

Figure 10. Input/Clock Macrocell

### Clocking

Each I/O and buried macrocell has access to four synchronous clocks (CLK0, CLK1, CLK2 and CLK3) and an asynchronous product term clock PTCLK. Each input macrocell has access to all four synchronous clocks.

### Dedicated Inputs/Clocks

Five pins on each member of the Ultra37000 family are designated as input-only. There are two types of dedicated inputs on Ultra37000 devices: input pins and input/clock pins. Figure 9 on page 15 illustrates the architecture for input pins. Four input options are available for the user: combinatorial, registered, double-registered, or latched. If a registered or latched option is selected, any one of the input clocks can be selected for control.

Figure 10 illustrates the architecture for the input/clock pins. Similar to the input pins, input/clock pins can be combinatorial, registered, double-registered, or latched. In addition, these pins feed the clocking structures throughout the device. The clock path at the input has user-configurable polarity.

### Product Term Clocking

In addition to the four synchronous clocks, the Ultra37000 family also has a product term clock for asynchronous clocking. Each logic block has an independent product term clock which is available to all 16 macrocells. Each product term clock also supports user configurable polarity selection.

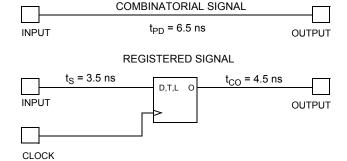

### **Timing Model**

One of the most important features of the Ultra37000 family is the simplicity of its timing. All delays are worst case and system performance is unaffected by the features used. Figure 11 illustrates the true timing model for the 167-MHz devices in high speed mode. For combinatorial paths, any input to any output incurs a 6.5 ns worst-case delay regardless of the amount of logic used. For synchronous systems, the input setup time to the output macrocells for any input is 3.5 ns and the clock to output

time is also 4.0 ns. These measurements are for any output and synchronous clock, regardless of the logic used.

The Ultra37000 features:

- No fanout delays

- No expander delays

- No dedicated vs. I/O pin delays

- No additional delay through PIM

- No penalty for using 0–16 product terms

- No added delay for steering product terms

- No added delay for sharing product terms

- No routing delays

- No output bypass delays

The simple timing model of the Ultra37000 family eliminates unexpected performance penalties.

Figure 11. Timing Model for CY37128

### JTAG and PCI Standards

### **PCI Compliance**

5V operation of the Ultra37000 is fully compliant with the PCI Local Bus Specification published by the PCI Special Interest Group. The 3.3V products meet all PCI requirements except for the output 3.3V clamp, which is in direct conflict with 5V tolerance. The Ultra37000 family's simple and predictable timing model ensures compliance with the PCI AC specifications independent of the design.

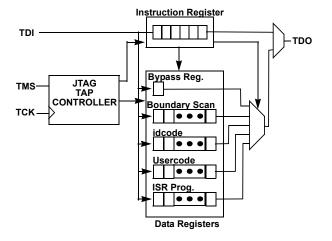

### IEEE 1149.1-compliant JTAG

The Ultra37000 family has an IEEE 1149.1 JTAG interface for both Boundary Scan and ISR.

### Boundary Scan

The Ultra37000 family supports Bypass, Sample/Preload, Extest, Idcode, and Usercode boundary scan instructions. The JTAG interface is shown in Figure 12.

Figure 12. JTAG Interface

### In-System Reprogramming (ISR)

In-System Reprogramming is the combination of the capability to program or reprogram a device on-board, and the ability to support design changes without changing the system timing or device pinout. This combination means design changes during debug or field upgrades do not cause board respins. The Ultra37000 family implements ISR by providing a JTAG compliant interface for on-board programming, robust routing resources for pinout flexibility, and a simple timing model for consistent system performance.

### **Development Software Support**

### Warp

Warp is a state-of-the-art compiler and complete CPLD design tool. For design entry, Warp provides an IEEE-STD-1076/1164 VHDL text editor, an IEEE-STD-1364 Verilog text editor, and a graphical finite state machine editor. It provides optimized synthesis and fitting by replacing basic circuits with ones pre-optimized for the target device, by implementing logic in unused memory and by perfect communication between fitting and synthesis. To facilitate design and debugging, Warp provides graphical timing simulation and analysis.

### Warp Professional™

Warp Professional contains several additional features. It provides an extra method of design entry with its graphical block diagram editor. It allows up to 5 ms timing simulation instead of only 2 ms. It allows comparison of waveforms before and after design changes.

### *Warp* Enterprise™

Warp Enterprise provides even more features. It provides unlimited timing simulation and source-level behavioral simulation as well as a debugger. It has the ability to generate graphical HDL blocks from HDL text. It can even generate testbenches.

Warp is available for PC and UNIX platforms. Some features are not available in the UNIX version. For further information see the Warp for PC, Warp for UNIX, Warp Professional and Warp Enterprise data sheets on Cypress's web site.

### **Third-Party Software**

Although *Warp* is a complete CPLD development tool on its own, it interfaces with nearly every third party EDA tool. All major third-party software vendors provide support for the Ultra37000 family of devices. Refer to the third-party software data sheet or contact your local sales office for a list of currently supported third-party vendors.

### **Programming**

There are four programming options available for Ultra37000 devices. The first method is to use a PC with the 37000 UltraISR programming cable and software. With this method, the ISR pins of the Ultra37000 devices are routed to a connector at the edge of the printed circuit board. The 37000 UltraISR programming cable is then connected between the parallel port of the PC and this connector. A simple configuration file instructs the ISR software of the programming operations to be performed on each of the Ultra37000 devices in the system. The ISR software then automatically completes all of the necessary data manipulations required to accomplish the programming, reading, verifying, and other ISR functions. For more information on the Cypress ISR Interface, see the CYUSBISRPC Programming Cable User's Guide.

The second method for programming Ultra37000 devices is on automatic test equipment (ATE). This is accomplished through a file created by the ISR software. Check the Cypress website for the latest ISR software download information.

The third programming option for Ultra37000 devices is to utilize the embedded controller or processor that already exists in the system. The Ultra37000 ISR software assists in this method by converting the device JEDEC maps into the ISR serial stream that contains the ISR instruction information and the addresses and data of locations to be programmed. The embedded controller then simply directs this ISR stream to the chain of Ultra37000 devices to complete the desired reconfiguring or diagnostic operations. Contact your local sales office for information on availability of this option.

The fourth method for programming Ultra37000 devices is to use the same programmer that is currently being used to program FLASH370i devices.

For all pinout, electrical, and timing requirements, refer to device data sheets. For ISR cable and software specifications, refer to the UltraISR kit data sheet (CY3700i).

### **Third-Party Programmers**

As with development software, Cypress support is available on a wide variety of third-party programmers. All major third-party programmers (including BP Micro, Data I/O, and SMS) support the Ultra37000 family.

Document Number: 38-03007 Rev. \*I Page 18 of 50

### 5 V Device Maximum Ratings

Exceeding maximum ratings may shorten the useful life of the device. These user guidelines are not tested.

Storage Temperature ......-65 °C to +150 °C Ambient Temperature with Power Applied ......55 °C to +125 °C Supply Voltage to Ground Potential .....-0.5 V to +7.0 V

| DC Voltage Applied to Outputs in High-Z State           | 0.5 V to +7.0 V |

|---------------------------------------------------------|-----------------|

| DC Input Voltage                                        | 0.5 V to +7.0 V |

| DC Program Voltage                                      | 4.5 to 5.5 V    |

| Current into Outputs                                    | 16 mA           |

| Static Discharge Voltage (per MIL-STD-883, Method 3015) | > 2001 V        |

| Latch-up Current                                        | > 200 mA        |

### **Operating Range**

The Operating Range is described as follows. [4]

| Range      | Ambient Temperature [4] | Junction Temperature | Output Condition | V <sub>CC</sub>  | V <sub>cco</sub> |

|------------|-------------------------|----------------------|------------------|------------------|------------------|

| Commercial | 0 °C to +70 °C          | 0 °C to +90 °C       | 5 V              | 5 V $\pm$ 0.25 V | 5 V ± 0.25 V     |

|            |                         |                      | 3.3 V            | 5 V ± 0.25 V     | $3.3~V\pm0.3~V$  |

| Industrial | –40 °C to +85 °C        | –40 °C to +105 °C    | 5 V              | 5 V ± 0.5 V      | 5 V ± 0.5 V      |

|            |                         |                      | 3.3 V            | 5 V ± 0.5 V      | 3.3 V ± 0.3 V    |

### 5 V Device Electrical Characteristics

Over the Operating Range

| Parameter       | Description                          |                                    | Test Conditions                                                       | Min         | Тур | Max                | Unit |

|-----------------|--------------------------------------|------------------------------------|-----------------------------------------------------------------------|-------------|-----|--------------------|------|

| V <sub>OH</sub> | Output HIGH Voltage                  | V <sub>CC</sub> = Min              | I <sub>OH</sub> = -3.2 mA<br>(Commercial / Industrial) <sup>[6]</sup> | 2.4         | _   | _                  | V    |

|                 |                                      |                                    | I <sub>OH</sub> = –2.0 mA (Military) <sup>[6]</sup>                   | 2.4         | -   | _                  | V    |

| $V_{OHZ}$       | Output HIGH Voltage with Output      | V <sub>CC</sub> = Max              | I <sub>OH</sub> = 0 μA (Commercial) <sup>[8]</sup>                    | _           | _   | 4.2                | V    |

|                 | Disabled [7]                         |                                    | I <sub>OH</sub> = 0 μA (Industrial / Military) <sup>[8]</sup>         | _           | _   | 4.5                | V    |

|                 |                                      |                                    | $I_{OH} = -100 \mu\text{A} (\text{Commercial})^{[8]}$                 | _           | _   | 3.6                | V    |

|                 |                                      |                                    | $I_{OH} = -150 \mu A$<br>(Industrial / Military) [8]                  | -           | _   | 3.6                | V    |

| V <sub>OL</sub> | Output LOW Voltage                   | V <sub>CC</sub> = Min              | I <sub>OL</sub> = 16 mA<br>(Commercial / Industrial) <sup>[6]</sup>   | _           | -   | 0.5                | V    |

|                 |                                      |                                    | I <sub>OL</sub> = 12 mA (Military) <sup>[6]</sup>                     | _           | _   | 0.5                | V    |

| V <sub>IH</sub> | Input HIGH Voltage                   | Guaranteed<br>Inputs [9]           | Input Logical HIGH Voltage for all                                    | 2.0         | -   | V <sub>CCmax</sub> | V    |

| V <sub>IL</sub> | Input LOW Voltage                    | Guaranteed<br>Inputs [9]           | Input Logical LOW Voltage for all                                     | -0.5        | -   | 0.8                | V    |

| I <sub>IX</sub> | Input Load Current                   | V <sub>I</sub> = GND o             | r V <sub>CC</sub> , Bus-Hold Disabled                                 | -10         | -   | 10                 | μΑ   |

| l <sub>oz</sub> | Output Leakage Current               | V <sub>O</sub> = GND o<br>Disabled | or V <sub>CC</sub> , Output Disabled, Bus-Hold                        | <b>–</b> 50 | _   | 50                 | μА   |

| I <sub>OS</sub> | Output Short Circuit Current [7, 10] | V <sub>CC</sub> = Max,             | V <sub>OUT</sub> = 0.5 V                                              | -30         | _   | -160               | mA   |

### Notes

- Normal Programming Conditions apply across Ambient Temperature Range for specified programming methods. For more information on programming the Ultra37000 Family devices, refer to the Application Note titled An Introduction to In System Reprogramming with the Ultra37000.

- 5. T<sub>A</sub> is the "Instant On" case temperature.

- I<sub>OH</sub> = 2 mA, I<sub>OL</sub> = 2 mA for TDO.

Tested initially and after any design or process changes that may affect these parameters.

When the I/O is output disabled, the bus-hold circuit can weakly pull the I/O to above 3.6V if no leakage current is allowed. Note that all I/Os are output disabled during ISR programming. Refer to the application note "Understanding Bus-Hold" for additional information.

These are absolute values with respect to device ground. All overshoots due to system or tester noise are included.

- 10. Not more than one output should be tested at a time. Duration of the short circuit should not exceed 1 second. V<sub>OUT</sub> = 0.5 V is chosen to avoid test problems caused

### **5 V Device Electrical Characteristics (continued)**

Over the Operating Range

| Parameter         | Description                            | Test Conditions                                | Min        | Тур | Max  | Unit |

|-------------------|----------------------------------------|------------------------------------------------|------------|-----|------|------|

| I <sub>BHL</sub>  | Input Bus-Hold LOW Sustaining Current  | V <sub>CC</sub> = Min, V <sub>IL</sub> = 0.8 V | +75        | -   | _    | μА   |

| Івнн              | Input Bus-Hold HIGH Sustaining Current | V <sub>CC</sub> = Min, V <sub>IH</sub> = 2.0 V | <b>–75</b> | _   | _    | μА   |

| I <sub>BHLO</sub> | Input Bus-Hold LOW Overdrive Current   | V <sub>CC</sub> = Max                          | _          | _   | +500 | μА   |

| Івнно             | Input Bus-Hold HIGH Overdrive Current  | V <sub>CC</sub> = Max                          | _          | _   | -500 | μА   |

### Inductance

| Parameter [11] | Description            | Test<br>Conditions                 | 44-pin TQFP | 44-pin PLCC | 100-pin TQFP | 160-pin TQFP | Unit |

|----------------|------------------------|------------------------------------|-------------|-------------|--------------|--------------|------|

| L              | Maximum Pin Inductance | V <sub>IN</sub> = 5 V at f = 1 MHz | 2           | 5           | 8            | 9            | nΗ   |

### Capacitance

| Parameter [11]   | Description              | Test Conditions                              | Max | Unit |

|------------------|--------------------------|----------------------------------------------|-----|------|

| C <sub>I/O</sub> | Input/Output Capacitance | $V_{IN}$ = 5 V at f = 1 MHz at $T_A$ = 25 °C | 10  | pF   |

| C <sub>CLK</sub> | Clock Signal Capacitance | $V_{IN}$ = 5 V at f = 1 MHz at $T_A$ = 25 °C | 12  | pF   |

| $C_{DP}$         | Dual-Function Pins [12]  | $V_{IN}$ = 5 V at f = 1 MHz at $T_A$ = 25 °C | 16  | pF   |

### **Endurance Characteristics**

| Parameter [11] | Description                  | Test Conditions                    | Min   | Тур    | Unit   |

|----------------|------------------------------|------------------------------------|-------|--------|--------|

| N              | Minimum Reprogramming Cycles | Normal Programming Conditions [13] | 1,000 | 10,000 | Cycles |

11. Tested initially and after any design or process changes that may affect these parameters.

Document Number: 38-03007 Rev. \*I Page 20 of 50

Dual pins are I/O with JTAG pins.

Normal Programming Conditions apply across Ambient Temperature Range for specified programming methods. For more information on programming the Ultra37000 Family devices, refer to the Application Note titled An Introduction to In System Reprogramming with the Ultra37000.

### 3.3 V Device Maximum Ratings

Exceeding maximum ratings may shorten the useful life of the device. These user guidelines are not tested.

| DC Voltage Applied to Outputs in High-Z State           | 0.5 V to +7.0 V |

|---------------------------------------------------------|-----------------|

| DC Input Voltage                                        | 0.5 V to +7.0 V |

| DC Program Voltage                                      | 3.0 to 3.6 V    |

| Current into Outputs                                    | 8 mA            |

| Static Discharge Voltage (per MIL-STD-883, Method 3015) | > 2001 V        |

| Latch-up Current                                        | > 200 mA        |

### **Operating Range**

The Operating Range is described as follows. [14]

| Range      | Ambient Temperature [14] | Junction Temperature | V <sub>CC</sub> [15] |

|------------|--------------------------|----------------------|----------------------|

| Commercial | 0 °C to +70 °C           | 0 °C to +90 °C       | 3.3 V ± 0.3 V        |

| Industrial | –40 °C to +85 °C         | –40 °C to +105 °C    | 3.3 V ± 0.3 V        |

### 3.3 V Device Electrical Characteristics

Over the Operating Range

| Parameter         | Description                              | Test Conditions                                                | Min         | Max  | Unit |

|-------------------|------------------------------------------|----------------------------------------------------------------|-------------|------|------|

| V <sub>OH</sub>   | Output HIGH Voltage                      | $V_{CC}$ = Min $I_{OH}$ = -4 mA (Commercial) [16]              | 2.4         | _    | V    |

|                   |                                          | I <sub>OH</sub> = –3 mA (Military) <sup>[16]</sup>             |             |      |      |

| V <sub>OL</sub>   | Output LOW Voltage                       | V <sub>CC</sub> = Min I <sub>OL</sub> = 8 mA (Commercial) [16] | _           | 0.5  | V    |

|                   |                                          | I <sub>OL</sub> = 6 mA (Military) <sup>[16]</sup>              |             |      |      |

| V <sub>IH</sub>   | Input HIGH Voltage                       | Guaranteed Input Logical HIGH Voltage for all Inputs [17]      | 2.0         | 5.5  | V    |

| V <sub>IL</sub>   | Input LOW Voltage                        | Guaranteed Input Logical LOW Voltage for all Inputs [17]       | -0.5        | 0.8  | V    |

| I <sub>IX</sub>   | Input Load Current                       | V <sub>I</sub> = GND or V <sub>CC</sub> , Bus-Hold Disabled    | -10         | 10   | μА   |

| I <sub>OZ</sub>   | Output Leakage Current                   | $V_{O}$ = GND or $V_{CC}$ , Output Disabled, Bus-Hold Disabled | <b>–</b> 50 | 50   | μА   |

| I <sub>OS</sub>   | Output Short Circuit<br>Current [18, 19] | $V_{CC}$ = Max, $V_{OUT}$ = 0.5 V                              | -30         | -160 | mA   |

| I <sub>BHL</sub>  | Input Bus-Hold LOW Sustaining Current    | V <sub>CC</sub> = Min, V <sub>IL</sub> = 0.8 V                 | +75         | _    | μА   |

| I <sub>BHH</sub>  | Input Bus-Hold HIGH Sustaining Current   | V <sub>CC</sub> = Min, V <sub>IH</sub> = 2.0 V                 | <b>–</b> 75 | _    | μА   |

| I <sub>BHLO</sub> | Input Bus-Hold LOW Overdrive Current     | V <sub>CC</sub> = Max                                          | _           | +500 | μА   |

| Івнно             | Input Bus-Hold HIGH Overdrive Current    | V <sub>CC</sub> = Max                                          | _           | -500 | μА   |

### Notes

- 14. Normal Programming Conditions apply across Ambient Temperature Range for specified programming methods. For more information on programming the Ultra37000 Family devices, refer to the Application Note titled *An Introduction to In System Reprogramming with the Ultra37000*.

- 15. For CY37064VP100-143AXC, CY37064VP44-143AXC; Operating Range:  $V_{CC}$  is 3.3 V  $\pm$  0.16 V.

- 16.  $I_{OH}$  = -2 mA,  $I_{OL}$  = 2 mA for TDO.

- 17. These are absolute values with respect to device ground. All overshoots due to system or tester noise are included.

- 18. Tested initially and after any design or process changes that may affect these parameters.

- 19. Not more than one output should be tested at a time. Duration of the short circuit should not exceed 1 second. V<sub>OUT</sub> = 0.5 V is chosen to avoid test problems caused

### Inductance

| Parameter [20] | Description            | Test<br>Conditions                      | 44- pin TQFP | 44-pin PLCC | 100-pin TQFP | 160-pin TQFP | Unit |

|----------------|------------------------|-----------------------------------------|--------------|-------------|--------------|--------------|------|

| L              | Maximum Pin Inductance | V <sub>IN</sub> = 3.3 V at<br>f = 1 MHz | 2            | 5           | 8            | 9            | nΗ   |

### Capacitance

| Parameter [20]   | Description               | Test Conditions                                                | Max | Unit |

|------------------|---------------------------|----------------------------------------------------------------|-----|------|

| C <sub>I/O</sub> | Input/Output Capacitance  | $V_{IN}$ = 3.3 V at f = 1 MHz at $T_A$ = 25 °C                 | 8   | pF   |

| C <sub>CLK</sub> | Clock Signal Capacitance  | $V_{IN}$ = 3.3 V at f = 1 MHz at $T_A$ = 25 °C                 | 12  | pF   |

| C <sub>DP</sub>  | Dual Functional Pins [21] | V <sub>IN</sub> = 3.3 V at f = 1 MHz at T <sub>A</sub> = 25 °C | 16  | pF   |

### **Endurance Characteristics**

| Parameter [20] | Description                  | Test Conditions                    | Min   | Тур    | Unit   |

|----------------|------------------------------|------------------------------------|-------|--------|--------|

| N              | Minimum Reprogramming Cycles | Normal Programming Conditions [22] | 1,000 | 10,000 | Cycles |

<sup>20.</sup> Tested initially and after any design or process changes that may affect these parameters.

21. Dual pins are I/O with JTAG pins.

22. Normal Programming Conditions apply across Ambient Temperature Range for specified programming methods. For more information on programming the Ultra37000 Family devices, refer to the Application Note titled An Introduction to In System Reprogramming with the Ultra37000.

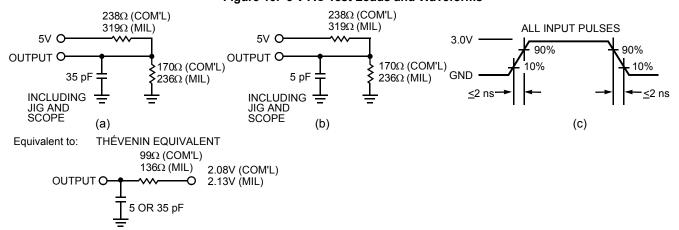

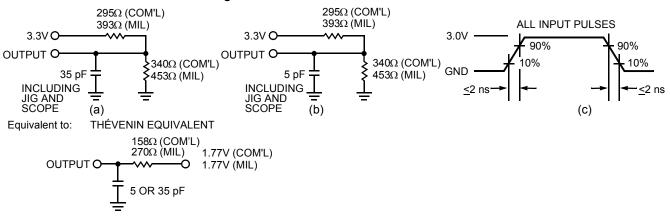

### **AC Test Loads and Waveforms**

Figure 13. 5 V AC Test Loads and Waveforms

Figure 14. 3.3 V AC Test Loads and Waveforms

| Parameter [23]     | $V_{X}$       | Output Waveform — Measurement Level |

|--------------------|---------------|-------------------------------------|

| t <sub>ER(-)</sub> | 1.5 V         | V <sub>OH</sub>                     |

| t <sub>ER(+)</sub> | 2.6 V         | V <sub>OL</sub> 0.5V                |

| t <sub>EA(+)</sub> | 1.5 V         | V <sub>X</sub> 0.5V V <sub>OH</sub> |

| t <sub>EA(-)</sub> | $V_{\sf the}$ | V <sub>X</sub> 0.5V V <sub>OL</sub> |

(d) Test Waveforms

Note  $$23.\,t_{\text{ER}}$$  measured with 5 pF AC Test Load and  $t_{\text{EA}}$  measured with 35 pF AC Test Load.

### **Switching Characteristics**

Over the Operating Range

| Parameter [24]                            | Description                                                                                                                                                                                          | Unit |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Combinatorial M                           | ode Parameters                                                                                                                                                                                       |      |

| t <sub>PD</sub> <sup>[25, 26, 27]</sup>   | Input to Combinatorial Output                                                                                                                                                                        | ns   |

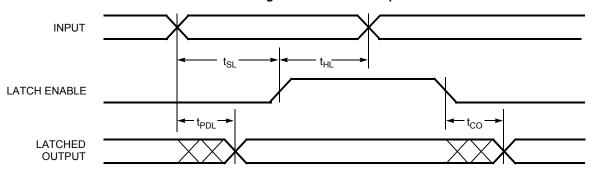

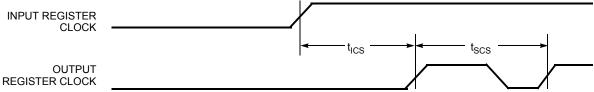

| t <sub>PDL</sub> <sup>[25, 26, 27]</sup>  | Input to Output Through Transparent Input or Output Latch                                                                                                                                            | ns   |

| t <sub>PDLL</sub> [25, 26, 27]            | Input to Output Through Transparent Input and Output Latches                                                                                                                                         | ns   |

| t <sub>EA</sub> <sup>[25, 26, 27]</sup>   | Input to Output Enable                                                                                                                                                                               | ns   |

| t <sub>ER</sub> <sup>[25, 28]</sup>       | Input to Output Disable                                                                                                                                                                              | ns   |

| Input Register Pa                         | arameters                                                                                                                                                                                            |      |

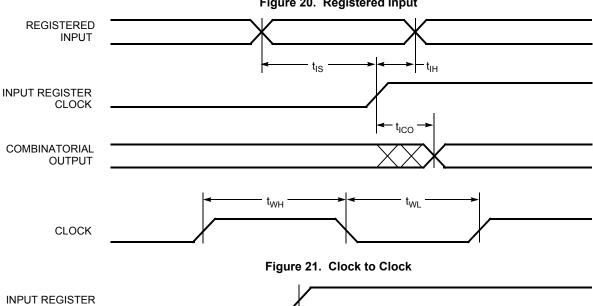

| $t_{WL}$                                  | Clock or Latch Enable Input LOW Time <sup>[10]</sup>                                                                                                                                                 | ns   |

| t <sub>WH</sub>                           | Clock or Latch Enable Input HIGH Time <sup>[10]</sup>                                                                                                                                                | ns   |

| t <sub>IS</sub>                           | Input Register or Latch Set-up Time                                                                                                                                                                  | ns   |

| t <sub>IH</sub>                           | Input Register or Latch Hold Time                                                                                                                                                                    | ns   |

| t <sub>ICO</sub> <sup>[25, 26, 27]</sup>  | Input Register Clock or Latch Enable to Combinatorial Output                                                                                                                                         | ns   |

| t <sub>ICOL</sub> <sup>[25, 26, 27]</sup> | Input Register Clock or Latch Enable to Output Through Transparent Output Latch                                                                                                                      | ns   |

|                                           | ocking Parameters                                                                                                                                                                                    | •    |

| t <sub>CO</sub> <sup>[26, 27]</sup>       | Synchronous Clock (CLK <sub>0</sub> , CLK <sub>1</sub> , CLK <sub>2</sub> , or CLK <sub>3</sub> ) or Latch Enable to Output                                                                          | ns   |

| t <sub>S</sub> <sup>[25]</sup>            | Set-Up Time from Input to Sync. Clk (CLK <sub>0</sub> , CLK <sub>1</sub> , CLK <sub>2</sub> , or CLK <sub>3</sub> ) or Latch Enable                                                                  | ns   |

| t <sub>H</sub>                            | Register or Latch Data Hold Time                                                                                                                                                                     | ns   |

| t <sub>CO2</sub> <sup>[25, 26, 27]</sup>  | Output Synchronous Clock (CLK <sub>0</sub> , CLK <sub>1</sub> , CLK <sub>2</sub> , or CLK <sub>3</sub> ) or Latch Enable to Combinatorial Output Delay (Through Logic Array)                         | ns   |

| t <sub>SCS</sub> <sup>[25]</sup>          | Output Synchronous Clock ( $CLK_0$ , $CLK_1$ , $CLK_2$ , or $CLK_3$ ) or Latch Enable to Output Synchronous Clock ( $CLK_0$ , $CLK_1$ , $CLK_2$ , or $CLK_3$ ) or Latch Enable (Through Logic Array) | ns   |

| t <sub>SL</sub> <sup>[25]</sup>           | Set-Up Time from Input Through Transparent Latch to Output Register Synchronous Clock ( $CLK_0$ $CLK_1$ , $CLK_2$ , or $CLK_3$ ) or Latch Enable                                                     | ns   |

| t <sub>HL</sub>                           | Hold Time for Input Through Transparent Latch from Output Register Synchronous Clock ( $CLK_0$ , $CLK_1$ , $CLK_2$ , or $CLK_3$ ) or Latch Enable                                                    | ns   |

$\begin{tabular}{ll} \textbf{Notes} \\ 24. & All AC parameters are measured with two outputs switching and 35 pF AC Test Load. \\ 25. & Logic blocks operating in low power mode, add $t_{LP}$ to this specification. \\ 26. & Outputs using Slow Output Slew Rate, add $t_{SLEW}$ to this specification. \\ 27. & When $V_{CCO} = 3.3V$, add $t_{3.3|O}$ to this specification. \\ 28. & t_{ER}$ measured with 5 pF AC Test Load and $t_{EA}$ measured with 35 pF AC Test Load. \\ \end{tabular}$

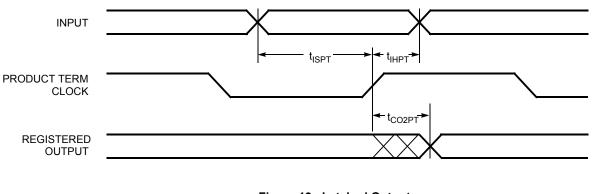

### **Switching Characteristics (continued)**

Over the Operating Range

| Parameter [24]                          | Description                                                                                                                                                     | Unit |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Product Term Cl                         | ocking Parameters                                                                                                                                               |      |

| t <sub>COPT</sub> [30, 31, 32]          | Product Term Clock or Latch Enable (PTCLK) to Output                                                                                                            | ns   |

| t <sub>SPT</sub>                        | Set-Up Time from Input to Product Term Clock or Latch Enable (PTCLK)                                                                                            | ns   |

| t <sub>HPT</sub>                        | Register or Latch Data Hold Time                                                                                                                                | ns   |

| t <sub>ISPT</sub> <sup>[30]</sup>       | Set-Up Time for Buried Register used as an Input Register from Input to Product Term Clock or Latch Enable (PTCLK)                                              | ns   |

| t <sub>IHPT</sub>                       | Buried Register Used as an Input Register or Latch Data Hold Time                                                                                               | ns   |

| t <sub>CO2PT</sub> [30, 31, 32]         | Product Term Clock or Latch Enable (PTCLK) to Output Delay (Through Logic Array)                                                                                | ns   |

| Pipelined Mode I                        | Parameters Parameters                                                                                                                                           | •    |

| t <sub>ICS</sub> <sup>[30]</sup>        | Input Register Synchronous Clock ( $CLK_0$ , $CLK_1$ , $CLK_2$ , or $CLK_3$ ) to Output Register Synchronous Clock ( $CLK_0$ , $CLK_1$ , $CLK_2$ , or $CLK_3$ ) | ns   |

| Operating Frequ                         | ency Parameters                                                                                                                                                 |      |

| f <sub>MAX1</sub>                       | Maximum Frequency with Internal Feedback (Lesser of 1/t <sub>SCS</sub> , 1/(t <sub>S</sub> + t <sub>H</sub> ), or 1/t <sub>CO</sub> ) [33]                      | MHz  |

| f <sub>MAX2</sub>                       | Maximum Frequency Data Path in Output Registered/Latched Mode (Lesser of $1/(t_{WL} + t_{WH})$ , $1/(t_S + t_H)$ , or $1/t_{CO}$ ) [33]                         | MHz  |

| f <sub>MAX3</sub>                       | Maximum Frequency with External Feedback (Lesser of 1/(t <sub>CO</sub> + t <sub>S</sub> ) or 1/(t <sub>WL</sub> + t <sub>WH</sub> ) [33]                        | MHz  |

| f <sub>MAX4</sub>                       | Maximum Frequency in Pipelined Mode (Lesser of $1/(t_{CO}+t_{IS})$ , $1/t_{ICS}$ , $1/(t_{WL}+t_{WH})$ , $1/(t_{IS}+t_{IH})$ , or $1/t_{SCS})^{[33]}$           | MHz  |

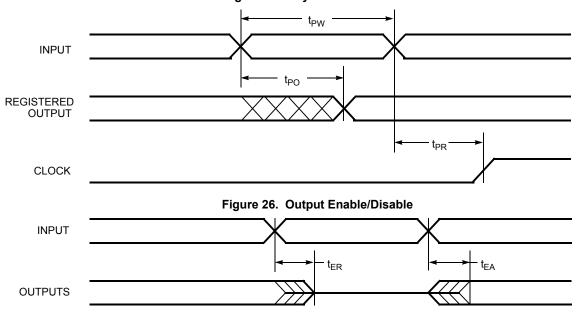

| Reset/Preset Par                        |                                                                                                                                                                 |      |

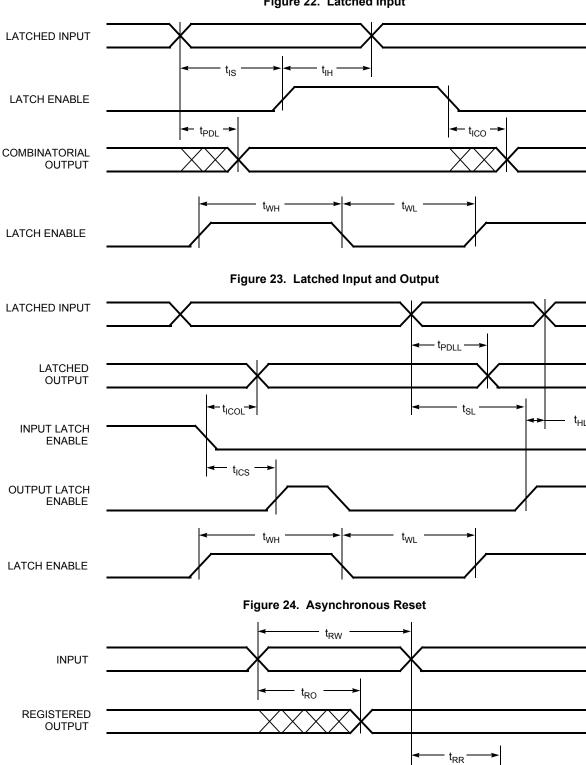

| t <sub>RW</sub>                         | Asynchronous Reset Width [33]                                                                                                                                   | ns   |

| t <sub>RR</sub> <sup>[30]</sup>         | Asynchronous Reset Recovery Time [33]                                                                                                                           | ns   |

| t <sub>RO</sub> <sup>[30, 31, 32]</sup> | Asynchronous Reset to Output                                                                                                                                    | ns   |

| t <sub>PW</sub>                         | Asynchronous Preset Width [33]                                                                                                                                  | ns   |

| t <sub>PR</sub> <sup>[30]</sup>         | Asynchronous Preset Recovery Time [33]                                                                                                                          | ns   |

| t <sub>PO</sub> <sup>[30, 31, 32]</sup> | Asynchronous Preset to Output                                                                                                                                   | ns   |

| User Option Para                        | ameters                                                                                                                                                         |      |

| t <sub>LP</sub>                         | Low Power Adder                                                                                                                                                 | ns   |

| t <sub>SLEW</sub>                       | Slow Output Slew Rate Adder                                                                                                                                     | ns   |

| t <sub>3.3IO</sub>                      | 3.3 V I/O Mode Timing Adder [33]                                                                                                                                | ns   |

| JTAG Timing Pa                          |                                                                                                                                                                 |      |

| t <sub>S JTAG</sub>                     | Set-up Time from TDI and TMS to TCK [33]                                                                                                                        | ns   |

| t <sub>H JTAG</sub>                     | Hold Time on TDI and TMS [33]                                                                                                                                   | ns   |

| t <sub>CO JTAG</sub>                    | Falling Edge of TCK to TDO [33]                                                                                                                                 | ns   |

| $f_{JTAG}$                              | Maximum JTAG Tap Controller Frequency [33]                                                                                                                      | ns   |

- **Notes**29. All AC parameters are measured with two outputs switching and 35 pF AC Test Load. 30. Logic blocks operating in low power mode, add  $t_{LP}$  to this specification. 31. Outputs using Slow Output Slew Rate, add  $t_{SLEW}$  to this specification. 32. When  $V_{CCO}$  = 3.3V, add  $t_{3.3IO}$  to this specification. 33. Tested initially and after any design or process changes that may affect these parameters.

11

# **Switching Characteristics**

Over the Operating Range

| ं रहा साट अप्रवासमाध्य । स्वाचित    | 26.12.1   |          |         |      |         |      |         |      |         |            |         |              |        |        |        | u                |      |

|-------------------------------------|-----------|----------|---------|------|---------|------|---------|------|---------|------------|---------|--------------|--------|--------|--------|------------------|------|

|                                     | 200       | 200 MHz  | 167 MHz | MHz  | 154 MHz | MHz  | 143 MHz | /IHz | 125 MHz | MHz        | 100 MHz | MHz          | 83 MHz | IHz    | 99 WHz | ĵis              |      |

| Parameter [34]                      | niM       | Max      | niM     | Max  | niM     | Max  | niM     | Мах  | niM     | Мах        | niM     | Мах          | niM    | Мах    | niM    | XeM<br>⊖Ü ∖\     | Unit |

| Combinatorial Mode Parameters       | Mode Pai  | ameters  |         |      |         |      |         |      |         |            |         |              |        |        |        | .ən              |      |

| t <sub>PD</sub> [35, 36, 37]        | ı         | 9        | 1       | 6.5  | 1       | 7.5  | ı       | 8.5  | I       | 10         | I       | 12           | 1      | 15     | 1      | 2 <sub>0</sub>   | ns   |

| <sup>t</sup> PDL [35, 36, 37]       | I         | 7        | ı       | 12.5 | 1       | 14.5 | ı       | 16   | ı       | 16.5       | I       | 17           | ı      | 19     | ı      | 125              | ns   |

| t <sub>PDLL</sub> [35, 36, 37]      | I         | 12       | ı       | 13.5 | I       | 15.5 | ı       | 17   | I       | 17.5       | I       | 18           | ı      | 20     | ı      | 2<br>9₽p         | ns   |

| t <sub>EA</sub> [35, 36, 37]        | ı         | 8        | ı       | 8.5  | ı       | 1    | ı       | 13   | I       | 41         | I       | 16           | ı      | 19     | ı      | 2 <del>1</del> 0 | ns   |

| t <sub>ER</sub> [35, 38]            | ı         | 8        | ı       | 8.5  | ı       | 7    | ı       | 13   | I       | 41         | I       | 16           | ı      | 19     | ı      | 2 <b>4</b> ⊞     | ns   |

| Input Register Parameters           | aramete   | irs      |         |      |         |      |         |      |         |            |         |              |        |        |        | ШO               |      |

| twL                                 | 2.5       | I        | 2.5     | ı    | 2.5     | ı    | 2.5     | ı    | 3       | I          | 3       | ı            | 4      | ı      | 2      | ၁ခု              | ns   |

| twн                                 | 2.5       | I        | 2.5     | I    | 2.5     | I    | 2.5     | I    | 3       | I          | 3       | I            | 4      | ı      | 2      | 님                | ns   |

| tls                                 | 2         | I        | 2       | I    | 2       | ı    | 2       | I    | 2       | I          | 2.5     | I            | က      | ı      | 4      | οŅ               | ns   |

| tн                                  | 2         | I        | 2       | ı    | 2       | ı    | 2       | ı    | 2       | ı          | 2.5     | ı            | က      | ı      | 4      | ··1              | ns   |

| t <sub>ICO</sub> [35, 36, 37]       | ı         | 7        | ı       | 7    | ı       | 7    | ı       | 12.5 | I       | 12.5       | I       | 16           | ı      | 19     | ı      | 24               | ns   |

| t <sub>ICOL</sub> [35, 36, 37]      | ı         | 12       | ı       | 12   | 1       | 12   | ı       | 4    | ı       | 16         | ı       | 18           | ı      | 21     | ı      | 26               | ns   |

| Synchronous Clocking Parameters     | locking l | Paramete | ırs     |      |         |      |         |      |         |            |         |              |        |        |        |                  |      |

| t <sub>CO</sub> <sup>[36, 37]</sup> | ı         | 4        | ı       | 4    | -       | 4.5  | ı       | 9    |         | [6.2 [38]] |         | $6.5^{[40]}$ | ı      | 8 [41] | ı      | 10               | ns   |

| t <sub>S</sub> [35]                 | 4         | -        | 4       | _    | 2       | I    | 2       | -    | [88]    | _          | [40]    | _            | 8 [41] | -      | 10     | Ι                | ns   |

| tн                                  | 0         | I        | 0       | ı    | 0       | ı    | 0       | I    | 0       | I          | 0       | I            | 0      | I      | 0      | I                | ns   |

| t <sub>CO2</sub> [35, 36, 37]       | -         | 9.6      | 1       | 10   | _       | 11   | -       | 12   | _       | 14         | _       | 16           | 1      | 19     | 1      | 24               | ns   |

| t <sub>SCS</sub> <sup>[35]</sup>    | 5         | I        | 9       | I    | 6.5     | I    | 7       | ı    | 8 [39]  | I          | 10      | _            | 12     | Ι      | 15     | I                | ns   |

| t <sub>SL</sub> [35]                | 7.5       | I        | 7.5     | Ι    | 8.5     | Ι    | 6       | 1    | 10      | -          | 12      | _            | 15     | _      | 15     | Ι                | ns   |

| tHL                                 | 0         | I        | 0       | I    | 0       | ı    | 0       | ı    | 0       | I          | 0       | I            | 0      | ı      | 0      | I                | ns   |

# Notes

Page 27 of 50

A All AC parameters are measured with two outputs switching and 35 pF AC Test Load.

35. Logic blocks operating in low power mode, add t<sub>LP</sub> to this specification.

36. Outputs using Slow Output Slew Rate, add t<sub>SLEW</sub> to this specification.

37. When V<sub>CCO</sub> = 3.3V, add t<sub>SJS</sub> to this specification.

38. Experience only, the following values correspond to the obsolete CY37512 devices: t<sub>CO</sub> = 5 ns, t<sub>SCS</sub> = 8.5 ns, t<sub>CCS</sub> = 8.5 ns, t<sub>MAX1</sub> = 118 MHz.

39. For reference only, the following values correspond to the obsolete CY37512 devices: t<sub>CO</sub> = 6 ns, t<sub>S</sub> = 7 ns, t<sub>MAX2</sub> = 143 MHz, t<sub>MAX3</sub> = 77 MHz, and t<sub>MAX4</sub> = 100 MHz; and for the CY37512 devices: t<sub>S</sub> = 7 ns.

40. The following values correspond to the obsolete CY37512V devices: t<sub>CO</sub> = 6.5 ns, t<sub>S</sub> = 9.5 ns, and t<sub>MAX2</sub> = 105 MHz.

# Switching Characteristics (continued)

Over the Operating Range

| -                                 | )         |          |         |     |         |     |         |     |                     |     |              |      |         |     |          |                 |      |

|-----------------------------------|-----------|----------|---------|-----|---------|-----|---------|-----|---------------------|-----|--------------|------|---------|-----|----------|-----------------|------|

| :                                 | 200       | 200 MHz  | 167 MHz | MHz | 154 MHz | MHz | 143 MHz | MHz | 125 MHz             | MHz | 100 MHz      | /IHz | 83 MHz  | 1Hz | ੁ 2HM 99 | Hz=             |      |

| Parameter [34]                    | niM       | Мах      | niM     | Мах | niM     | Max | niM     | Мах | niM                 | Мах | niM          | Мах  | niM     | Мах | niM      | Max<br>Gigi     | Unit |

| Product Term Clocking Parameters  | locking l | Paramet  | ers     |     |         |     | 1       |     |                     |     |              |      |         |     |          | <b>a</b> ^      |      |

| t <sub>COPT</sub> [42, 43, 44]    | ı         | 7        | ı       | 10  | ı       | 10  | ı       | 13  | I                   | 13  | ı            | 13   | ı       | 15  | ı        | 200             | ns   |

| tspT                              | 2.5       | ı        | 2.5     | ı   | 2.5     | 1   | က       | ı   | 2                   | ı   | 5.5          | ı    | 9       | ı   | 7        | Λ¹ <sub>1</sub> | ns   |

| tHPT                              | 2.5       | ı        | 2.5     | ı   | 2.5     | ı   | က       | 1   | 2                   | I   | 5.5          | ı    | 9       | I   | 7        | οî              | ns   |

| t <sub>ISPT</sub> <sup>[42]</sup> | 0         | ı        | 0       | ı   | 0       | ı   | 0       | 1   | 0                   | I   | 0            | ı    | 0       | I   | 0        | pə              | ns   |

| t <sub>IHPT</sub>                 | 9         | ı        | 6.5     | ı   | 6.5     | ı   | 7.5     | 1   | 6                   | ı   | 7            | ı    | 4       | ı   | 19       | ρμŧ             | ns   |

| t <sub>CO2PT</sub> [42, 43, 44]   | ı         | 12       | ı       | 14  |         | 15  |         | 19  |                     | 19  |              | 21   |         | 24  | ı        | e<br>Wi         | ns   |

| Pipelined Mode Parameters         | Parame    | ters     |         |     |         |     |         |     |                     |     |              |      |         |     |          | шс              |      |

| t <sub>ICS</sub> <sup>[42]</sup>  | 2         | ı        | 9       | ı   | 9       | ı   | 7       | ı   | 8 [45]              | ı   | 10           | ı    | 12      | ı   | 15       | ာခုခ            | ns   |

| Operating Frequency Parameters    | ency Pa   | arameter | .s      |     |         |     |         |     |                     |     |              |      |         |     |          | В               |      |

| f <sub>MAX1</sub>                 | 200       | ı        | 167     | ı   | 154     | ı   | 143     | ı   | 125 <sup>[45]</sup> | I   | 100          | 1    | 83      | ı   | 99       | 191             | MHz  |

| f <sub>M</sub> AX2                | 200       | I        | 200     | ı   | 200     | ı   | 167     | I   | 154                 | I   | $153^{[46]}$ | ı    | 125[47] | I   | 100      | ۱.,             | MHz  |

| f <sub>MAX3</sub>                 | 125       | ı        | 125     | ı   | 105     | ı   | 91      | 1   | 83                  | I   | 80 [46]      | ı    | 62.5    | I   | 20       | ı               | MHz  |

| f <sub>MAX4</sub>                 | 191       | I        | 167     | ı   | 154     | ı   | 125     | I   | 118                 | I   | 100          | I    | 83      | I   | 99       | I               | MHz  |

| Reset/Preset Parameters           | ameters   |          |         |     |         |     |         |     |                     |     |              |      |         |     |          |                 |      |

| t <sub>RW</sub>                   | 8         | ı        | 8       | ı   | 8       | ı   | ω       | ı   | 10                  | I   | 12           | I    | 15      | I   | 20       | ı               | ns   |

| t <sub>RR</sub> [42]              | 10        | I        | 10      | 1   | 10      | ı   | 10      | _   | 12                  | I   | 14           | I    | 17      | -   | 22       | I               | ns   |

Page 28 of 50

<sup>42.</sup> Logic blocks operating in low power mode, add  $t_{\rm LP}$  to this specification.

43. Outputs using Slow Output Slew Rate, add  $t_{\rm SLEW}$  to this specification.

44. When V<sub>CCO</sub>= 3.3V, add  $t_{\rm 3.3IO}$  to this specification.

45. For reference only, the following values correspond to the obsolete CY37512 devices:  $t_{\rm CO}$  = 5 ns,  $t_{\rm MAX2}$  = 143 MHz, and  $t_{\rm MAX3}$  = 710 MHz, and  $t_{\rm MAX4}$  = 100 MHz; and for the CY37512 devices:  $t_{\rm CO}$  = 6 ns,  $t_{\rm S}$  = 7 ns,  $t_{\rm MAX2}$  = 143 MHz,  $t_{\rm MAX3}$  = 770 MHz, and  $t_{\rm MAX4}$  = 100 MHz; and for the CY37512 devices:  $t_{\rm CO}$  = 6.5 ns,  $t_{\rm S}$  = 9.5 ns, and  $t_{\rm MAX2}$  = 105 MHz.

# Switching Characteristics (continued)

Over the Operating Range

|          | Chrit          | SU                           | SU  | SU                   | SU                           |                               | SU         | SU     | SU                      |                        | SU      | SU             | su        | MHz   |

|----------|----------------|------------------------------|-----|----------------------|------------------------------|-------------------------------|------------|--------|-------------------------|------------------------|---------|----------------|-----------|-------|

| 66 MHz = | Max            | 26-J                         | ۱ڄ۸ | Λ¹η                  | 262                          | pə                            | 2.<br>JPI€ | e<br>E | o<br>M                  | ၁၃                     | 占       | 191            | <u>20</u> | 20    |

| 199      | niM            | ı                            | 20  | 22                   | I                            |                               | ı          | ı      | ı                       |                        | 0       | 20             | I         | I     |

| 83 MHz   | Мах            | 21                           | I   | I                    | 21                           |                               | 2.5        | က      | 0.3                     |                        | ı       | I              | 20        | 20    |

| 831      | niM            | I                            | 15  | 17                   | I                            |                               | I          | I      | I                       |                        | 0       | 20             | I         | I     |

| 100 MHz  | Мах            | 18                           | I   | I                    | 18                           |                               | 2.5        |        | 0.3                     |                        | I       | I              | 20        | 20    |

| 100      | niM            | I                            | 12  | 14                   | I                            |                               | I          | I      | I                       |                        | 0       | 20             | I         | I     |

| 125 MHz  | Мах            | 15                           | I   | I                    | 15                           |                               | 2.5        | က      | 0.3                     |                        | ı       | I              | 20        | 20    |

| 125      | niM            | I                            | 10  | 12                   | I                            |                               | ı          | I      | I                       |                        | 0       | 20             | I         | ı     |

| 143 MHz  | Мах            | 14                           | I   | I                    | 41                           |                               | 2.5        | က      | 0.3                     |                        | ı       | I              | 20        | 20    |

| 143      | niM            | I                            | 8   | 10                   | I                            |                               | I          | I      | I                       |                        | 0       | 20             | I         | I     |

| 154 MHz  | Мах            | 13                           | I   | I                    | 13                           |                               | 2.5        | က      | 0.3                     |                        | ı       | I              | 20        | 20    |

| 154      | niM            | ı                            | ∞   | 10                   | I                            |                               | ı          | I      | ı                       |                        | 0       | 20             | I         | ı     |

| 167 MHz  | Мах            | 13                           | I   | I                    | 13                           |                               | 2.5        | င      | 0.3                     |                        | I       | I              | 20        | 20    |

| 167      | niM            | I                            | 8   | 10                   | I                            |                               | I          | I      | I                       |                        | 0       | 20             | I         | I     |

| 200 MHz  | Мах            | 12                           | I   | I                    | 12                           |                               | 2.5        | 3      | 0.3                     | <i>(</i> 6             | ı       | I              | 20        | 20    |

| 200      | niM            | ı                            | 8   | 10                   | ı                            | ameters                       | I          | ı      | ı                       | rameters               | 0       | 20             | I         | ı     |

| :        | Parameter [34] | t <sub>RO</sub> [48, 49, 50] | tpw | t <sub>PR</sub> [48] | t <sub>PO</sub> [48, 49, 50] | <b>User Option Parameters</b> | trp        | tsLEW  | t <sub>3.310</sub> [51] | JTAG Timing Parameters | ts JTAG | <sup>t</sup> н | tco JTAG  | fjtag |