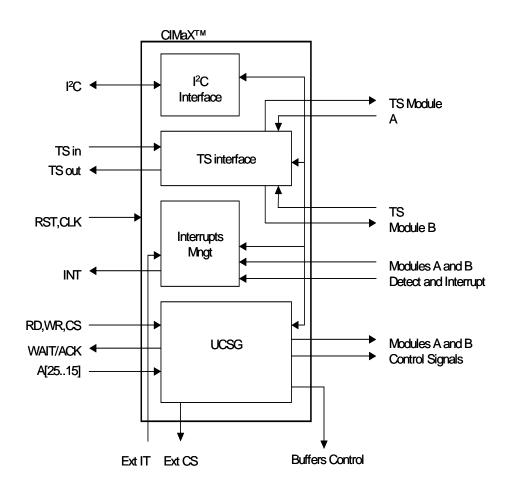

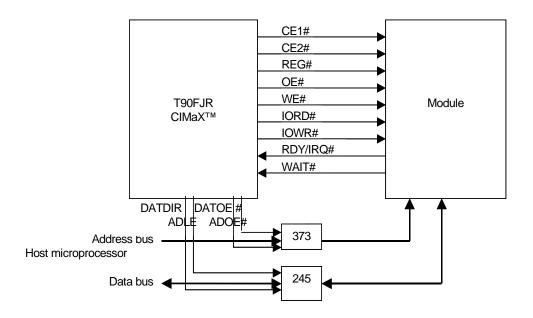

Generator (UCSG)maps CPU control bus into Command Interface control signals. To minimize pin count, host address and data buses transit through external buffers that are driven by  $CIMaX^{TM}$ .

CIMaX<sup>™</sup> includes a memory mode that allows to use any of the two Common interface slots to read/write a 8-bit PC Card Memory card. This feature gives the receiver memory extension capability for software upgrade or better performance.

In case of modules order is significant, CIMaX<sup>™</sup> may virtually swap them (SCM' Patent Pending) after identifying which module must be in front of the transport stream.

CI Pack+™ includes hardware, software and qualification tools and is suitable for Set Top box, Digital TV set or PC board.

# 3. Block Diagram

Figure 3-1. Block Diagram

# 4. Pin description

| Name     | I/O | Туре      | RST | Function                                |

|----------|-----|-----------|-----|-----------------------------------------|

| RESET    | I   | TTL       |     | CIMaX™ reset                            |

| CLK      | I   | TTL       |     | 27MHz clock input                       |

| SA1      | I   | CMOS      |     | I <sup>2</sup> C address bit 2          |

| SA0      | I   | CMOS      |     | I <sup>2</sup> C address bit 1          |

| SCL      | I   | trig      |     | I <sup>2</sup> C clock                  |

| SDA      | I/O | trig      | Z   | I <sup>2</sup> C data                   |

| A25      | I   | TTL       |     | Host microprocessor address bit 25      |

| A24      | I   | TTL       |     | Host microprocessor address bit 24      |

| A23      | I   | TTL       |     | Host microprocessor address bit 23      |

| A22      | I   | TTL       |     | Host microprocessor address bit 22      |

| A21      | I   | TTL       |     | Host microprocessor address bit 21      |

| A20      | I   | TTL       |     | Host microprocessor address bit 20      |

| A19      | I   | TTL       |     | Host microprocessor address bit 19      |

| A18      | I   | TTL       |     | Host microprocessor address bit 18      |

| A17      | I   | TTL       |     | Host microprocessor address bit 17      |

| A16      | I   | TTL       |     | Host microprocessor address bit 16      |

| A15      | I   | TTL       |     | Host microprocessor address bit 15      |

| CS       | I   | TTL       |     | CIMaX™ chip select input                |

| RD/DIR   | I   | TTL       |     | Read strobe / transfer direction input  |

| WR/STR   | I   | TTL       |     | Write strobe / transfer strobe          |

| WAIT/ACK | 0   | CMOS / TS | Z   | WAIT / transfer acknowledge             |

| INT      | 0   | CMOS / TS | Z   | Interrupt output to host microprocessor |

| EXTCS    | 0   | CMOS / TS | Z   | External device chip select             |

| EXTINT   | I   | TTL       |     | External device interrupt input         |

| Name   | 1/0 | Туре | RST | Function                        |

|--------|-----|------|-----|---------------------------------|

| MICLK  | I   | TTL  |     | MPEG clock input from front-end |

| MISTRT | I   | TTL  |     | MPEG packet start input         |

| MIVAL  | I   | TTL  |     | MPEG valid data input           |

| MDI7   | I   | TTL  |     | MPEG data input bit 7           |

| MDI6   | I   | TTL  |     | MPEG data input bit 6           |

| MDI5   | I   | TTL  |     | MPEG data input bit 5           |

| MDI4   | I   | TTL  |     | MPEG data input bit 4           |

| Name                                                                        | I/O                                  | Туре                                                                                                | RST               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MDI3                                                                        | I                                    | TTL                                                                                                 |                   | MPEG data input bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MDI2                                                                        | I                                    | TTL                                                                                                 |                   | MPEG data input bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MDI1                                                                        | I                                    | TTL                                                                                                 |                   | MPEG data input bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MDI0                                                                        | I                                    | TTL                                                                                                 |                   | MPEG data input bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MOCLK                                                                       | 0                                    | CMOS                                                                                                | 0                 | MPEG clock output to MPEG decoder                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MOSTRT                                                                      | 0                                    | CMOS                                                                                                | 0                 | MPEG packet start output                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MOVAL                                                                       | 0                                    | CMOS                                                                                                | 0                 | MPEG valid data output                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MDO7                                                                        | 0                                    | CMOS                                                                                                | 0                 | MPEG data output bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MDO6                                                                        | 0                                    | CMOS                                                                                                | 0                 | MPEG data output bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MDO5                                                                        | 0                                    | CMOS                                                                                                | 0                 | MPEG data output bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MDO4                                                                        | 0                                    | CMOS                                                                                                | 0                 | MPEG data output bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MDO3                                                                        | 0                                    | CMOS                                                                                                | 0                 | MPEG data output bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MDO2                                                                        | 0                                    | CMOS                                                                                                | 0                 | MPEG data output bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MDO1                                                                        | 0                                    | CMOS                                                                                                | 0                 | MPEG data output bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MDO0                                                                        | 0                                    | CMOS                                                                                                | 0                 | MPEG data output bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Name                                                                        | I/O                                  | Туре                                                                                                | RST               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MICLKA                                                                      | 0                                    | CMOS / TS                                                                                           | Z                 | Module A MPEG clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MISTRTA                                                                     | 0                                    | CMOS / TS                                                                                           | Z                 | Module A MPEG packet start input                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1                                                                           | J                                    |                                                                                                     |                   | ' '                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MIVALA                                                                      | 0                                    | CMOS / TS                                                                                           | Z                 | Module A MPEG valid data input                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MIVALA<br>MDIA7                                                             |                                      | CMOS/TS CMOS/TS                                                                                     | Z<br>Z            | i i                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                             | 0                                    |                                                                                                     |                   | Module A MPEG valid data input                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MDIA7                                                                       | 0                                    | CMOS / TS                                                                                           | Z                 | Module A MPEG valid data input  Module A MPEG data input bit 7                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MDIA7<br>MDIA6                                                              | 0 0                                  | CMOS / TS                                                                                           | Z<br>Z            | Module A MPEG valid data input  Module A MPEG data input bit 7  Module A MPEG data input bit 6                                                                                                                                                                                                                                                                                                                                                                                  |

| MDIA7 MDIA6 MDIA5                                                           | 0 0 0                                | CMOS / TS  CMOS / TS  CMOS / TS                                                                     | z<br>z<br>z       | Module A MPEG valid data input  Module A MPEG data input bit 7  Module A MPEG data input bit 6  Module A MPEG data input bit 5                                                                                                                                                                                                                                                                                                                                                  |

| MDIA7 MDIA6 MDIA5 MDIA4                                                     | 0 0 0 0 0                            | CMOS/TS CMOS/TS CMOS/TS CMOS/TS                                                                     | Z Z Z Z Z         | Module A MPEG valid data input  Module A MPEG data input bit 7  Module A MPEG data input bit 6  Module A MPEG data input bit 5  Module A MPEG data input bit 4                                                                                                                                                                                                                                                                                                                  |

| MDIA7 MDIA6 MDIA5 MDIA4 MDIA3                                               | 0<br>0<br>0<br>0                     | CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS                                                             | Z Z Z Z Z Z       | Module A MPEG valid data input  Module A MPEG data input bit 7  Module A MPEG data input bit 6  Module A MPEG data input bit 5  Module A MPEG data input bit 4  Module A MPEG data input bit 3                                                                                                                                                                                                                                                                                  |

| MDIA7 MDIA6 MDIA5 MDIA4 MDIA3 MDIA2                                         | 0<br>0<br>0<br>0<br>0                | CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS                                                     | Z Z Z Z Z Z Z     | Module A MPEG valid data input  Module A MPEG data input bit 7  Module A MPEG data input bit 6  Module A MPEG data input bit 5  Module A MPEG data input bit 4  Module A MPEG data input bit 3  Module A MPEG data input bit 2                                                                                                                                                                                                                                                  |

| MDIA7 MDIA6 MDIA5 MDIA4 MDIA3 MDIA2 MDIA1                                   | 0<br>0<br>0<br>0<br>0<br>0           | CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS                                     | Z Z Z Z Z Z Z Z Z | Module A MPEG valid data input  Module A MPEG data input bit 7  Module A MPEG data input bit 6  Module A MPEG data input bit 5  Module A MPEG data input bit 4  Module A MPEG data input bit 3  Module A MPEG data input bit 2  Module A MPEG data input bit 1                                                                                                                                                                                                                  |

| MDIA7 MDIA6 MDIA5 MDIA4 MDIA3 MDIA2 MDIA1 MDIA0                             | 0<br>0<br>0<br>0<br>0<br>0           | CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS                             | Z Z Z Z Z Z Z Z Z | Module A MPEG valid data input  Module A MPEG data input bit 7  Module A MPEG data input bit 6  Module A MPEG data input bit 5  Module A MPEG data input bit 4  Module A MPEG data input bit 3  Module A MPEG data input bit 2  Module A MPEG data input bit 1  Module A MPEG data input bit 1                                                                                                                                                                                  |

| MDIA7 MDIA6 MDIA5 MDIA4 MDIA3 MDIA2 MDIA1 MDIA0 MOCLKA                      | 0<br>0<br>0<br>0<br>0<br>0<br>0      | CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS TTL down                    | Z Z Z Z Z Z Z Z Z | Module A MPEG valid data input  Module A MPEG data input bit 7  Module A MPEG data input bit 6  Module A MPEG data input bit 5  Module A MPEG data input bit 4  Module A MPEG data input bit 3  Module A MPEG data input bit 2  Module A MPEG data input bit 1  Module A MPEG data input bit 0  Module A MPEG clock output to MPEG decoder                                                                                                                                      |

| MDIA7 MDIA6 MDIA5 MDIA4 MDIA3 MDIA2 MDIA1 MDIA0 MOCLKA MOSTRTA              | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS TTL down TTL down                   | Z Z Z Z Z Z Z Z Z | Module A MPEG valid data input  Module A MPEG data input bit 7  Module A MPEG data input bit 6  Module A MPEG data input bit 5  Module A MPEG data input bit 4  Module A MPEG data input bit 3  Module A MPEG data input bit 2  Module A MPEG data input bit 1  Module A MPEG data input bit 0  Module A MPEG clock output to MPEG decoder  Module A MPEG packet start output                                                                                                   |

| MDIA7 MDIA6 MDIA5 MDIA4 MDIA3 MDIA2 MDIA1 MDIA0 MOCLKA MOSTRTA MOVALA       | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS TTL down TTL down TTL down          | Z Z Z Z Z Z Z Z Z | Module A MPEG valid data input  Module A MPEG data input bit 7  Module A MPEG data input bit 6  Module A MPEG data input bit 5  Module A MPEG data input bit 4  Module A MPEG data input bit 3  Module A MPEG data input bit 2  Module A MPEG data input bit 1  Module A MPEG data input bit 0  Module A MPEG clock output to MPEG decoder  Module A MPEG packet start output  Module A MPEG valid data output                                                                  |

| MDIA7 MDIA6 MDIA5 MDIA4 MDIA3 MDIA2 MDIA1 MDIA0 MOCLKA MOSTRTA MOVALA MDOA7 |                                      | CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS CMOS/TS TTL down TTL down TTL down TTL down | Z Z Z Z Z Z Z Z Z | Module A MPEG valid data input  Module A MPEG data input bit 7  Module A MPEG data input bit 6  Module A MPEG data input bit 5  Module A MPEG data input bit 4  Module A MPEG data input bit 3  Module A MPEG data input bit 2  Module A MPEG data input bit 1  Module A MPEG data input bit 0  Module A MPEG data input bit 0  Module A MPEG clock output to MPEG decoder  Module A MPEG packet start output  Module A MPEG valid data output  Module A MPEG data output bit 7 |

| Name    | I/O | Туре      | RST                             | Function                                   |

|---------|-----|-----------|---------------------------------|--------------------------------------------|

| MDOA3   | I   | TTL down  |                                 | Module A MPEG data output bit 3            |

| MDOA2   | I   | TTL down  | Module A MPEG data output bit 2 |                                            |

| MDOA1   | I   | TTL down  |                                 | Module A MPEG data output bit 1            |

| MDOA0   | I   | TTL down  |                                 | Module A MPEG data output bit 0            |

| MICLKB  | 0   | CMOS / TS | Z                               | Module B MPEG clock input                  |

| MISTRTB | 0   | CMOS / TS | Z                               | Module B MPEG packet start input           |

| MIVALB  | 0   | CMOS / TS | Z                               | Module B MPEG valid data input             |

| MDIB7   | 0   | CMOS / TS | Z                               | Module B MPEG data input bit 7             |

| MDIB6   | 0   | CMOS / TS | Z                               | Module B MPEG data input bit 6             |

| MDIB5   | 0   | CMOS / TS | Z                               | Module B MPEG data input bit 5             |

| MDIB4   | 0   | CMOS / TS | Z                               | Module B MPEG data input bit 4             |

| MDIB3   | 0   | CMOS / TS | Z                               | Module B MPEG data input bit 3             |

| MDIB2   | 0   | CMOS / TS | Z                               | Module B MPEG data input bit 2             |

| MDIB1   | 0   | CMOS / TS | Z                               | Module B MPEG data input bit 1             |

| MDIB0   | 0   | CMOS / TS | Z                               | Module B MPEG data input bit 0             |

| MOCLKB  | I   | TTL down  |                                 | Module B MPEG clock output to MPEG decoder |

| MOSTRTB | I   | TTL down  |                                 | Module B MPEG packet start output          |

| MOVALB  | I   | TTL down  |                                 | Module B MPEG valid data output            |

| MDOB7   | I   | TTL down  |                                 | Module B MPEG data output bit 7            |

| MDOB6   | I   | TTL down  |                                 | Module B MPEG data output bit 6            |

| MDOB5   | I   | TTL down  |                                 | Module B MPEG data output bit 5            |

| MDOB4   | I   | TTL down  | Module B MPEG data output bit 4 |                                            |

| MDOB3   | I   | TTL down  | Module B MPEG data output bit 3 |                                            |

| MDOB2   | I   | TTL down  | Module B MPEG data output bit 2 |                                            |

| MDOB1   | I   | TTL down  | Module B MPEG data output bit 1 |                                            |

| MDOB0   | 1   | TTL down  |                                 | Module B MPEG data output bit 0            |

| Name      | 1/0 | Туре         | RST | Function                    |

|-----------|-----|--------------|-----|-----------------------------|

| RSTA      | 0   | CMOS/TS      | Z   | Module A reset              |

| CD1A#     | I   | CMOS trig up |     | Module A card detect 1      |

| CD2A#     | 1   | CMOS trig up |     | Module A card detect 2      |

| CE1A#     | 0   | CMOS/TS      | Z   | Module A card enable 1      |

| CE2A#     | 0   | CMOS / TS    | Z   | Module A card enable 2      |

| RDY/IRQA# | 1   | TTL          |     | Module A Ready / IRQ signal |

| Name      | I/O | Туре         | RST | Function                              |

|-----------|-----|--------------|-----|---------------------------------------|

| WAITA#    | ļ   | TTL          |     | Module A WAIT# signal                 |

| RSTB      | 0   | CMOS / TS    | Z   | Module B reset                        |

| CD1B#     | I   | CMOS trig up |     | Module B card detect 1                |

| CD2B#     | I   | CMOS trig up |     | Module B card detect 2                |

| CE1B#     | 0   | CMOS / TS    | Z   | Module B card enable 1                |

| CE2B#     | 0   | CMOS / TS    | Z   | Module B card enable 2                |

| RDY/IRQB# | I   | TTL          |     | Module B Ready / IRQ signal           |

| WAITB#    | I   | TTL          |     | Module B WAIT# signal                 |

| REG#      | 0   | CMOS / TS    | Z   | Modules REG# signal                   |

| OE#       | 0   | CMOS / TS    | Z   | Modules output enable                 |

| WE#       | 0   | CMOS / TS    | Z   | Modules write enable                  |

| IORD#     | 0   | CMOS / TS    | Z   | Modules I/O read                      |

| IOWR#     | 0   | CMOS/TS      | Z   | Modules I/O write                     |

| VCCEN     | 0   | CMOS         | Z   | Modules VCC switch control            |

| DATOE#    | 0   | CMOS         | 1   | External data buffers output enable   |

| DATDIR    | 0   | CMOS         | 0   | External data buffer direction        |

| ADOE#     | 0   | CMOS         | 1   | External address buffer output enable |

| ADLE      | 0   | CMOS         | 1   | External address buffer latch enable  |

| Name     | I/O | Туре  | Function                                           |

|----------|-----|-------|----------------------------------------------------|

| VCC_DVB1 |     | Power | DVB CI modules buffers power                       |

| VCC_DVB2 |     | Power | DVB CI modules buffers power                       |

| VCC_CORE |     | Power | Core power                                         |

| VCC_TSI  |     | Power | MPEG input buffers power                           |

| VCC_TSO  |     | Power | MPEG output buffers power                          |

| VCC_PROC |     | Power | Host microprocessor control signals buffers power  |

| GND_DVB1 |     | Power | DVB CI modules buffers ground                      |

| GND_DVB2 |     | Power | DVB CI modules buffers ground                      |

| GND_CORE |     | Power | Core ground                                        |

| GND_TSI  |     | Power | MPEG input buffers ground                          |

| GND_TSO  |     | Power | MPEG output buffers ground                         |

| GND_PROC |     | Power | Host microprocessor control signals buffers ground |

Note: RST column indicates the output pin status after a reset issued by asserting RESET pin or RST bit in the CIMaX™ Control Register.

### **Notations:**

TTL: TTL level CMOS:CMOS level

TS: Tristate

trig: Schmitt Trigger internal pull-up up: down:internal pull-down

#### **Host Microprocessor Interface** 5.

#### 5.1 **Configuration interface**

The CIMaX™ needs a clock source at 27MHz frequency with a duty cycle comprised between 33% and 67%. This frequency is commonly available in any digital video system.

A RESET input pin (active high) is available to reset the CIMaX™ at any time when power is on (e.g. : power monitor, watchdog...). The clock must be activated before the end of the reset. The reset signal must be active during at least 16 clock cycles (600ns @ 27MHz), before CIMaX™ reset. The CIMaX™ is operational 8 cycles after reset deactivation.

CIMaX™ includes an input high order address bus A[25:15] to achieve address decoding for automatic destination select or to be rerouted to the modules when using a memory PC Card with HAD=1 and TSIEN=0 and TSOEN=0, in the Module Control Register.

The CIMaX™ configuration is achieved by accessing the various registers through a standard I<sup>2</sup>C interface. The I<sup>2</sup>C device address can be chosen among four values by connecting SA1 and SA0 to VCC or GND. The binary address is 1 0 0 0 0 SA1 SA0 R/W. Though, the base address can be chosen between 80h, 82h, 84h or 86h allowing the connection of up to four CIMaX™ on the same bus.

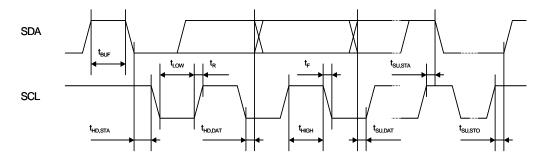

Figure 5-1. Chronograms

| Parameter                            | Symbol              | Min | Max | Unit |

|--------------------------------------|---------------------|-----|-----|------|

| SCL frequency                        | f <sub>SCL</sub>    |     | 400 | KHz  |

| Bus free time between stop and start | t <sub>BUF</sub>    | 1.3 |     | μs   |

| Hold time start condition            | t <sub>HD,STA</sub> | 0.6 |     | μs   |

| SCL low period                       | t <sub>LOW</sub>    | 1.3 |     | μs   |

| SCL high period                      | t <sub>HIGH</sub>   | 0.6 |     | μs   |

| Parameter                              | Symbol              | Min | Max | Unit |

|----------------------------------------|---------------------|-----|-----|------|

| Setup time before a repeated start     | t <sub>SU,STA</sub> | 0.6 |     | μs   |

| Data hold time                         | t <sub>HD,DAT</sub> | 0   | 0.9 | μs   |

| Data setup time                        | t <sub>SU,DAT</sub> | 100 |     | ns   |

| Rise time for both SDA and SCL signals | t <sub>R</sub>      | 20  | 300 | ns   |

| Fall time for both SDA and SCL signals | t <sub>F</sub>      | 20  | 300 | ns   |

| Setup time before a stop condition     | t <sub>SU,STO</sub> | 0.6 |     | μs   |

| Capacitive load for each bus line      | C <sub>b</sub>      |     | 400 | pF   |

# 5.2 Universal Control Signal Generator (UCSG)

CIMaX<sup>™</sup> can be connected to various CPUs, each of them having a different external bus control structure with different signals and timings. To interface with a large number of different microprocessors, the host microprocessor interface includes a fully configurable UCSG block that generates the right PCMCIA control signals.

At reset, the host microprocessor interface is disabled; CS, RD/DIR and WR/STR inputs are inactive and WAIT/ACK and INT are in high impedance state. The only available access is the configuration interface (I2C) which permits to set up the CIMaX<sup>TM</sup>. Once the proper parameters have been entered in the CIMaX<sup>TM</sup>, the interface is enabled by setting the LOCK bit in the CIMaX<sup>TM</sup> Control Register (@1Fh). The access to the modules is then possible and some parameters related to the host microprocessor interface are impossible to modify.

Host microprocessor input control signals are CS, RD/DIR, WR/STR and output signals are WAIT/ACK and INT. Input and output active levels can be individually set up by configuration bits. In addition, the output buffer structure is also configurable to be either open-drain (allowing wired-or) or push-pull, in the UCSG1 and UCSG2 registers.

- CS: Chip select signal indicates to the CIMaX<sup>™</sup> that the current bus cycle is addressed to one of the modules (or external device)

- RD/DIR: Read strobe or direction signal. This signal function can be chosen with the RDIR bit. Read strobe indicates a valid read bus cycle or direction signal indicates the bus transfer direction when a valid bus transfer is indicated by the transfer strobe signal

- WR/STR: Write strobe or transfer strobe. This signal function can be adjusted with the WSTR bit. Write strobe indicates a valid write bus cycle or transfer strobe indicates a valid bus transfer in direction indicated by RD/DIR state.

- WAIT/ACK: Wait or Acknowledge transfer. In WAIT mode, this signal inserts wait cycles in the bus read or write operation in process. In ACK mode, this signal indicates the completion of the bus cycle.

- INT: Interrupt output to the host microprocessor.

The UCSG (universal control signals generator) inputs the RD / DIR, WR / STR and CS signals from host microprocessor, WAITA# and WAITB# from the modules and generates all the control signals to modules, host microprocessor, buffers and external device: CE1A#, CE2A#, CE1B#, CE2B#, REG#, OE#, WE#, IORD#, IOWR#, WAIT, ACK, ADLE, ADOE#, DATDIR, DATOE#.

The input signals from the host microprocessor are combined, depending on the host microprocessor configuration, to form a read and write signal RD' and WR'. These signals indicate an active read or write cycle in process.

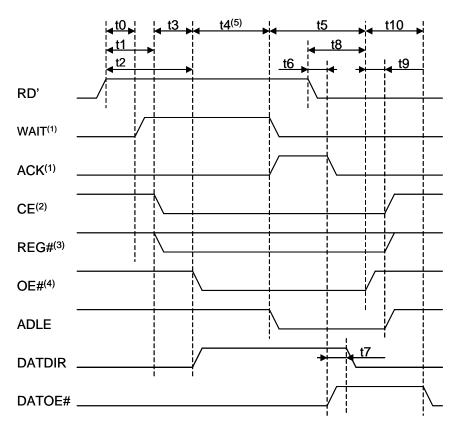

Figure 5-2. Read access

Notes:

- 1. The WAIT/ACK output is either WAIT or ACK formatted according to the WAIT/ACK pin settings (active level, driving structure).

- 2. Depending on the read access type, CE can be either CE1A# or CE1B# for access to memory or IO to module A or B, CE2A# or CE2B# for access in EC (Extended Channel) mode, or even EXTCS for access to external device in regenerate mode.

- 3. REG# signal is not asserted during a common memory or external access.

- 4. OE# signal is asserted during a memory access (attribute or common). It is replaced by IORD# during an IO read cycle, an EC (Extended Channel) read cycle (using CE2A# or CE2B#) or an external access in regenerate mode.

- 5. t4 can be lengthened by the insertion of wait cycles. When the destination module asserts WAIT# signal, the t4 cycles counter stops until WAIT# becomes inactive anew.

Memory read timings are given for various cycle duration. In attribute memory mode, only 600ns and 300ns cycles are available. In common memory mode, 300ns doesn't exist. IO and external device in regenerate mode share the same timing specifications as they all use IORD# and IOWR# signals. Timings are given in CIMaX™ clock cycles. They are calculated to comply with PCMCIA specifications when 27MHz clock is used.

|                       |       | Memory read       |       |                                  |           |           |                |  |

|-----------------------|-------|-------------------|-------|----------------------------------|-----------|-----------|----------------|--|

|                       | 600ns | 300 ns            | 250ns | 200ns                            | 150n<br>s | 100n<br>s | IO, EC,<br>Ext |  |

| t0 max <sub>(1)</sub> |       |                   |       | 26 ns                            |           |           |                |  |

| t1 max                |       |                   |       | 1.5 cycle + 26 ns <sub>(2)</sub> |           |           |                |  |

| t2 min                | 3     | 1                 | 1     | 1                                | 1         | 1         | 2              |  |

| t3                    | 3     | 1                 | 1     | 1                                | 1         | 1         | 2              |  |

| t4                    | 14    | 8                 | 7     | 5                                | 4         | 3         | 3              |  |

| t5 min                |       |                   |       | 0                                |           |           | 2              |  |

| t6 max <sub>(1)</sub> |       |                   |       | 26 ns                            |           |           |                |  |

| t7 min                |       |                   |       | 0 ns                             |           |           |                |  |

| t7 max                |       |                   |       | 70 ns                            |           |           |                |  |

| t8 max                |       | 1.5 cycle + 26 ns |       |                                  |           |           |                |  |

| t9                    | 1     | 1                 | 1     | 1                                | 1         | 1         | 1              |  |

| t10 min               | 5     | 3                 | 3     | 3                                | 3         | 2         | 2              |  |

- (1) these timings are given for a load of 50 pF on WAIT/ACK pin.

- (1) 1.5 cycle corresponds to the start cycle detection time. t1 depends actually on the previous cycle completion which depends on t8 and t10 read timings. So t1 ranges from 3.5 to 6.5 cycles.

Note: t0: delay between start of a read cycle and activation of WAIT

- t1: delay between start of a read cycle and falling edge of CE and REG# (if required for the current cycle)

- t2: delay between start of a read cycle and falling edge of OE# (and switching of the data buffer direction control)

- t3: delay between falling edge of CE and falling edge of OE# (and switching of the data buffer direction control)

- t4: read cycle length. This time is the necessary delay for the module to present the read data on the data output bus. After t4 delay is expired, WAIT is deasserted and ACK asserted thus enabling the processor to read the data on the bus. At the same time, ADLE is reset to latch the address presented to the module so that the data is not changed while the processor is reading. t4 can be lengthened by the module if the module requires extra wait cycles by asserting its WAIT# pin low.

- t5: delay to deassertion of module read signal (OE# or IORD#) after minimum delay after t4.

- t6: delay between end of read cycle indicated by the processor and data bus isolation (DATOE# asserted)

- t7: delay between data bus isolation and switching back of the data bus direction

- t8: delay to deassertion of module read signal (OE# or IORD#) after end of a read cycle by the processor.

- t9: delay between deassertion of the module read signal and deassertion of CE, REG# and ADLE (releasing the address bus)

- t10: delay between deassertion of the module read signal and re-enabling of the data bus (see t7 on write cycle)

The corresponding timings are given below for a 27 MHz clock:

|         | Memory read |        |             |                                                  |           |           |                |

|---------|-------------|--------|-------------|--------------------------------------------------|-----------|-----------|----------------|

|         | 600ns       | 300 ns | 250ns       | 200ns                                            | 150n<br>s | 100n<br>s | IO, EC,<br>Ext |

| t0 max  |             |        |             | 26 ns                                            |           |           |                |

| t1 max  |             | 8      | 30 ns (from | start cycle detection – see note in table above) |           |           |                |

| t2 min  | 111 ns      | 37 ns  | 37 ns       | 37 ns                                            | 37 ns     | 37 ns     | 75 ns          |

| t3      | 111 ns      | 37 ns  | 37 ns       | 37 ns                                            | 37 ns     | 37 ns     | 75 ns          |

| t4      | 530 ns      | 297 ns | 260 ns      | 185 ns                                           | 150<br>ns | 111<br>ns | 111 ns         |

| t5 min  |             |        |             | 0 ns                                             |           |           | 75 ns          |

| t6 max  |             |        |             | 26 ns                                            |           |           |                |

| t7 min  |             |        |             | 0 ns                                             |           |           |                |

| t7 max  |             |        |             | 70 ns                                            |           |           |                |

| t8 max  |             |        |             | 80 ns                                            |           |           |                |

| t9      | 37 ns       | 37 ns  | 37 ns       | 37 ns                                            | 37 ns     | 37 ns     | 37 ns          |

| t10 min | 185 ns      | 111 ns | 111 ns      | 111 ns                                           | 111<br>ns | 75 ns     | 75 ns          |

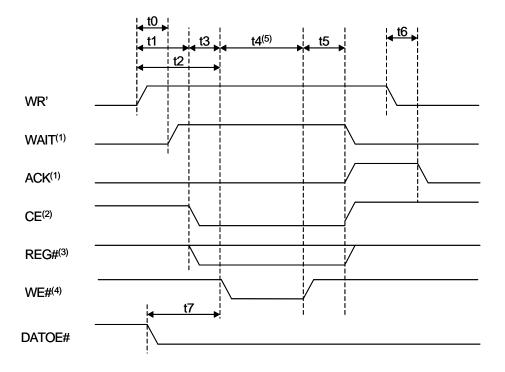

## 5.2.1 Write Access

Note:

- (1): The WAIT / ACK output is either WAIT or ACK formatted according to the WAIT / ACK pin settings (active level, driving structure).

- (2): Depending on the write access type, CE can be either CE1A# or CE1B# for access to memory or IO to module A or B, CE2A# or CE2B# for access in EC (Extended Channel) mode or even EXTCS for access to external device in regenerate mode

- (3): REG# signal is not asserted during a common memory or external access.

- (4): WE# signal is asserted during a memory access (attribute or common). It is replaced by IOWR# during an IO write cycle, an EC (Extended Channel) write cycle (using CE2A# or CE2B#) or an external access in regenerate mode.

- (5): t4 can be lengthened by the insertion of wait cycles. When the destination module asserts WAIT# signal, the t4 cycles counter stops until WAIT# becomes inactive anew.

Memory write is valid for both attribute and common memory access. Timings are given in CIMaX<sup>™</sup> clock cycles. They are calculated to comply with PCMCIA specifications when 27MHz clock is used.

|                       | Memory write |       |       |                   |       |                   |

|-----------------------|--------------|-------|-------|-------------------|-------|-------------------|

|                       | 600ns        | 250ns | 200ns | 150ns             | 100ns | IO,<br>EC,<br>Ext |

| t0 max <sub>(1)</sub> |              |       |       | 26 ns             |       |                   |

| t1 max                |              |       | 1.5   | cycle + 26 ns (2) |       |                   |

| t2 min                | 2            | 1     | 1     | 1                 | 1     | 2                 |

| t3                    | 2            | 1     | 1     | 1                 | 1     | 2                 |

| t4                    | 9            | 5     | 4     | 3                 | 2     | 5                 |

| t5                    | 2            | 1     | 1     | 1                 | 1     | 1                 |

| t6 max <sub>(1)</sub> | 26 ns        |       |       |                   |       |                   |

| t7 min                | 1            | 1     | 1     | 1                 | 1     | 2                 |

Note:

- 1. these timings are given for a load of 50 pF on WAIT/ACK pin.

- 2. 1.5 cycle corresponds to the start cycle detection time. t1 depends actually on the previous cycle completion which depends on t8 and t10 read timings. So t1 ranges from 3.5 to 6.5 cycles.

Note:

- t0: delay between start of a write cycle and activation of WAIT

- t1: delay between start of a write cycle and assertion of CE and REG# (if necessary for the current cycle)

- t2: delay to assertion of the write signal (WE# or IOWR#) after the start of the write cycle

- t3: delay to assertion of the write signal (WE# or IOWR#) after the assertion of CE

- t4: write cycle duration. This delay can be lengthened by the assertion of the module WAIT# pin

- t5: delay between deassertion of the write signal and deassertion of CE, REG# and WAIT and assertion of ACK indicating to the processor the end of its write cycle

- t6: delay between end of the write cycle and deassertion of ACK

- t7: delay between enabling of the data bus and write signal assertion. This delay is necessary when a write cycle is immediately following a read cycle (see t10 in read cycle)

The corresponding timings are given below for a 27 MHz clock:

|        |       |       | Mem            | ory write                                |  | IO,<br>EC, |  |  |  |  |  |

|--------|-------|-------|----------------|------------------------------------------|--|------------|--|--|--|--|--|

|        | 600ns |       |                |                                          |  |            |  |  |  |  |  |

| t0 max |       | 24 ns |                |                                          |  |            |  |  |  |  |  |

| t1 max |       | 80 ns | (from start cy | cle detection – see note in table above) |  |            |  |  |  |  |  |

|        |        | Memory write |        |        |       |            |  |  |  |

|--------|--------|--------------|--------|--------|-------|------------|--|--|--|

|        | 600ns  | 250ns        | 200ns  | 150ns  | 100ns | EC,<br>Ext |  |  |  |

| t2 min | 75 ns  | 37 ns        | 37 ns  | 37 ns  | 37 ns | 75 ns      |  |  |  |

| t3     | 75 ns  | 37 ns        | 37 ns  | 37 ns  | 37 ns | 75 ns      |  |  |  |

| t4     | 334 ns | 185 ns       | 150 ns | 111 ns | 75 ns | 185<br>ns  |  |  |  |

| t5     | 75 ns  | 37 ns        | 37 ns  | 37 ns  | 37 ns | 37 ns      |  |  |  |

| t6 max |        |              |        | 26 ns  |       |            |  |  |  |

| t7 min | 37 ns  | 37 ns        | 37 ns  | 37 ns  | 37 ns | 75 ns      |  |  |  |

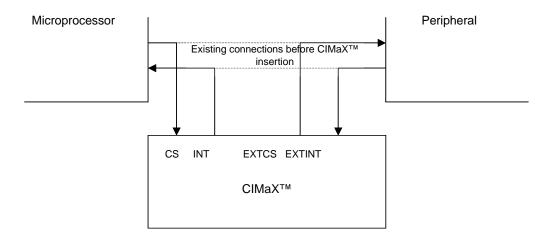

## 5.3 External Peripheral Control Signals

CIMaX<sup>™</sup> outputs a chip select EXTCS. This output is fully configurable through the Destination Select register to be open-drain or push-pull output driver and active high or low.

The activation of this output can be programmed to be automatically the default selection when none of the modules is selected (bit DEF = 1 in the external access auto select mask low register) and CS input is asserted or when address match the external access auto select mask and pattern registers on the same basis as for the modules auto selection when DEF = 0.

The EXTCS output can also be manually chosen to be the destination when AUTOSEL bit is 0 in the Destination Select Register and when SEL = 11.

In addition, the EXTCS output can work in two ways :transmit mode or regenerate mode selected by the XCSMOD in the Destination Select Register.

The EXTCS output reproduces the CS input whenever the external device selection conditions are met in the CIMaX<sup>TM</sup>, regardless of the selection mode (automatic / manual, default / pattern match). This mode permits to insert the CIMaX<sup>TM</sup> in an existing hardware architecture by replacing an existing peripheral by the CIMaX<sup>TM</sup> on the address decoder and connecting this peripheral to the CIMaX<sup>TM</sup>. The address decoding must then be set up properly on the address decoder and in the CIMaX<sup>TM</sup> to match the new hardware architecture but no extra CS is needed on the address decoder; the CIMaX<sup>TM</sup> provides a new one in replacement of the one it needs. The following table gives the maximum propagation delay according to different conditions (70 °C):

| Co    | nditions   |                          |

|-------|------------|--------------------------|

| Vcc   | EXTCS Load | CS to EXTCS maximum time |

| 4.5 V | 10 pF      | 9 ns                     |

| 4.5 V | 50 pF      | 13 ns                    |

| 3.0 V | 10 pF      | 13 ns                    |

| 3.0 V | 50 pF      | 16 ns                    |

In regenerate mode, the EXTCS output acts as CEx# outputs to the modules as it is generated by the internal CIMaX<sup>TM</sup> state machine in conjunction with assertion of IORD# or IOWR#. This mode permits to access to any 8-bit peripheral accessed with a RD, a WR and a CS input such

as a static RAM or an UART for example with programmable access time provided by the  $CIMaX^{TM}$ .

The CIMaX<sup>™</sup> also provides an interrupt input. This input is rerouted to the INT output connected to the host microprocessor through the interrupt manager of the CIMaX<sup>™</sup>. EXTINT pin is programmable to be either active-high or active-low with the EXTLVL bit in the Interrupt Config Register and is maskable with the EXTM bit in the Interrupt Mask Register. The EXTINT input status can be monitored by reading the EXT bit in the Interrupt Status Register. This feature can be used to insert the CIMaX<sup>™</sup> in an existing environment by using an interrupt input of the host microprocessor already used by a peripheral for the CIMaX<sup>™</sup> interrupt and connecting this peripheral's interrupt to the CIMaX<sup>™</sup>.

Using EXTCS and EXTINT enables to insert the CIMaX $^{\text{TM}}$  in an existing design where all the chip selects and interrupts are already affected as it virtually does not use any chip select nor interrupt.

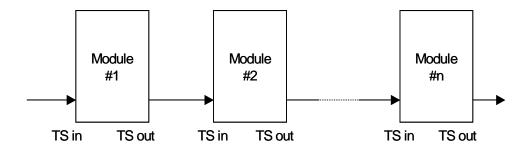

# 6. TS Daisy Chain

In the DVB Common Interface, each module has an MPEG input port constituted by MPEG clock, MPEG packet start, MPEG valid data and MPEG data bus and an MPEG output port composed of the same signals. The MPEG transport stream transits through the modules on a daisy chain basis.

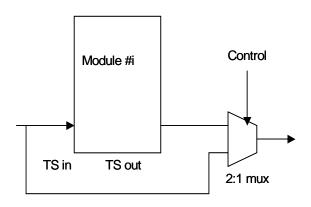

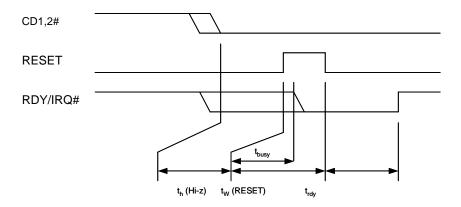

## 6.1 Hot Plug and Bypass

As a module can be inserted or removed at any time, in order not to break the daisy chain, the CIMaX<sup>™</sup> handles one MPEG transport stream bypass for each module. This bypass is enabled as long as a valid DVB CI module is not recognized to be inserted and activated in the corresponding slot or automatically as soon as the module is removed from a slot. The disabling of the bypass is controlled by the TSOEN bit in each Module Control Register. The bypass can be switched at any time, regardless of the MPEG stream synchronization.

### 6.1.1 TS swap (SCM Patent Pending)

With standard conditional access modules, the order in which the transport stream passes through has no influence. However, in some particular cases, it can be useful to choose which module is first in the TS daisy chain. The TSWAP bit in the Destination Select Register when set, virtually swaps the two modules so that the MPEG stream passes first in the B module and then in the A module.

### 6.1.2 TS / Addresses input signals

The MPEG input stream pins on the module are shared with the high order addresses specified by the PC Card standard. When a module is inserted, before initialization, all these pins are forced to logical 0 state. If a memory module is recognized, the high order addresses A[25..15] can be applied to the module by setting the HAD bit in the Module Control Register. If a DVB module is recognized, the MPEG stream is applied to the module by setting the TSIEN bit in the Module Control Register. Those two bits cannot be set at the same time and are reset when the module is extracted

When HAD is set, the maximum propagation delay between A[25..15] inputs and TS outputs to the modules is 25 ns with a load of 50 pF on the outputs.

The TSOEN bit (TS bypass control bit) can only be set when TSIEN has previously been set.

Resetting TSIEN also resets TSOEN.

### 6.1.3 Invert mask

Some modules can output an MPEG stream with inverted bits in the MPEG data bus. The CIMaX<sup>™</sup> is able to re-invert those bits to restore the correct data on the bus. This is achieved by setting the appropriate bits in the Invert Mask Register.

### 6.1.4 IO characteristics

The CIMaX<sup>™</sup> ensures that the MPEG stream output signals applied to the modules and to the MPEG decoder (or chained CIMaX<sup>™</sup>) meets the AC and DC electrical characteristics defined in the PC Card standard [1], the DVB CI standard [2] and Guidelines for implementation [3]. Moreover, the CIMaX<sup>™</sup> MPEG inputs from MPEG source (e.g. front-end receiver) and from the modules comply with the same requirements. In order to fulfil the timing requirements, the MPEG stream is re-synchronized at each step in the daisy chain, thus introducing a few MPEG clock cycles delay (1 to 3) on the data stream between the input and output depending on the number of active modules.

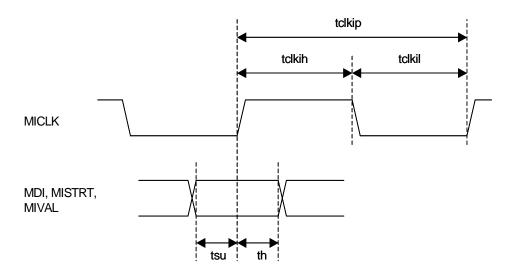

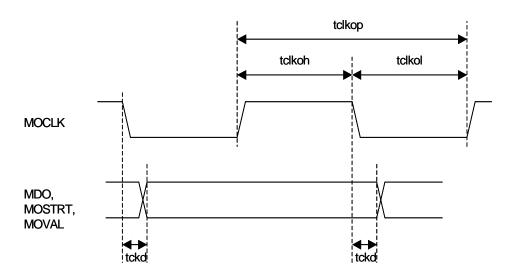

### 6.1.4.1 TS signals chronograms

Note: According to Errata in EN 50221 and the Cenelec report Guidelines for implementation and use of the common interface for DVB decoder applications—CIT057 – rev6., delays for MICLK, MDI, MIVAL, MISTRT are also applicable to MOCLKA, MOCLKB, MDOA, MDOB, MOVALA, MOVALB,

MOSTRTA, MOSTRB except for clock high and low times. Delays for MOCLK, MDO, MOSTRT, MOVAL are also applicable to MICLKA, MICLKB, MDIA, MDIB, MIVALA, MIVALB, MISTRTA, MISTRTB.

### 6.1.4.2 AC Electrical characteristics

VCC = 5V, T = 25°C

|        | Parameter                                                     | Min      | Max                     | Unit |

|--------|---------------------------------------------------------------|----------|-------------------------|------|

| tclkip | MPEG input clock period                                       | 111      |                         | ns   |

| tclkih | MICLK input clock high time<br>MOCLKA/B input clock high time | 24<br>44 | 97 <sub>(1)</sub><br>67 | ns   |

| tclkil | MICLK input clock low time<br>MOCLKA/B input clock low time   | 24<br>44 | 97 <sub>(1)</sub><br>67 | ns   |

| tclkop | MPEG output clock period                                      | 111      |                         | ns   |

| tclkoh | output clock high time                                        | 24       | 91 <sub>(1)</sub>       | ns   |

| tclkol | output clock low time                                         | 24       | 91 <sub>(1)</sub>       | ns   |

| tsu    | input data setup                                              | 10       |                         | ns   |

| th     | input data hold                                               | 10       |                         | ns   |

| tckd   | clock to data delay                                           | 0        | 15                      | ns   |

Note: (1) for a clock period of 111 ns

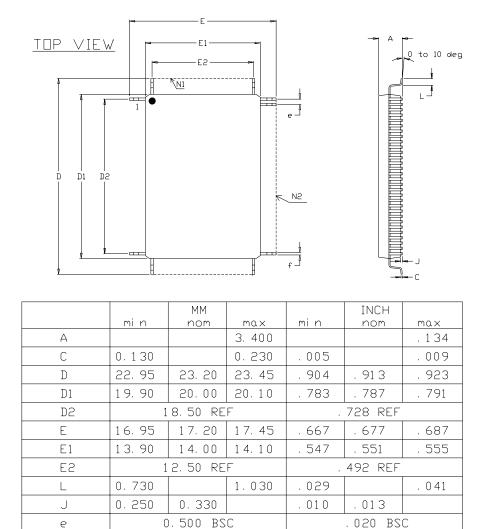

## 7. Command interface

The command interface is directly issued from PC Card standard [1] restricted to 8 bits access and 15 bits addressing. The command interface of a CI module is described in detail in the PC Card standard [1] and the restrictions applied to this standard for the command interface are described in the DVB CI standard [2].

## 7.1 Command interface signals

The 15 address bits and 8 data bits of the CI module are connected to the host microprocessor bus through buffers (type 373 and 245) which are controlled by the CIMaX<sup>™</sup>. The CIMaX<sup>™</sup> provides the buffers control signals:

- DATOE#Data Output enable (active low)

- ADOE# Address Output enable (active low)

- DATDIR Data direction according to the read/write current cycle

- ADLE Address Latch enable to latch the address bus until the end of the read/write cycle.

(see application note for connection of the buffers)

The buffers should be powered by the same source (voltage) as the modules.

The CI control signals are the same as the PC Card control signals : CE1#, CE2#, REG#, OE#, WE#, IORD#, IOWR#, RDY/IRQ#, WAIT#. The CIMaX<sup>™</sup> generates those signals so that they fit

the PC Card standard whenever the host microprocessor accesses one of the modules. The control signals activated depend on the access type chosen in the Module Control Register with ACS[1..0]. The read and write signals active level duration is configured in the memory access cycle time registers. The CIMaX<sup>™</sup> receives RDY/IRQ# from the module and retransmits the interruption to the host microprocessor. The module can also send a WAIT# request that is also transmitted to the host microprocessor in addition to the wait states already generated due to the read and write duration.

# 8. Registers Description

CIMaX<sup>™</sup> includes several internal registers as depicted below, and described into the following sections.

| Address | Description                                |

|---------|--------------------------------------------|

| 00      | Module A Control Register                  |

| 01      | Module A auto select mask high Register    |

| 02      | Module A auto select mask low Register     |

| 03      | Module A auto select pattern high Register |

| 04      | Module A auto select pattern low Register  |

| 05      | Memory access A cycle time Register        |

| 06      | Invert Input Mask A Register               |

| 07      | RFU                                        |

| 08      | RFU                                        |

| 09      | Module B Control Register                  |

| 0A      | Module B auto select mask high Register    |

| Address | Description                                       |  |  |  |

|---------|---------------------------------------------------|--|--|--|

| 0B      | Module B auto select mask low Register            |  |  |  |

| 0C      | Module B auto select pattern high Register        |  |  |  |

| 0D      | Module B auto select pattern low Register         |  |  |  |

| 0E      | Memory access B cycle time Register               |  |  |  |

| 0F      | Invert Input Mask B Register                      |  |  |  |

| 10      | RFU                                               |  |  |  |

| 11      | RFU                                               |  |  |  |

| 12      | External access auto select mask high Register    |  |  |  |

| 13      | External access auto select mask low Register     |  |  |  |

| 14      | External access auto select pattern high Register |  |  |  |

| 15      | External access auto select pattern low Register  |  |  |  |

| 16      | RFU                                               |  |  |  |

| 17      | Destination select Register                       |  |  |  |

| 18      | Power control Register                            |  |  |  |

| 19      | RFU                                               |  |  |  |

| 1A      | Interrupt Status Register                         |  |  |  |

| 1B      | Interrupt Mask Register                           |  |  |  |

| 1C      | Interrupt Config Register                         |  |  |  |

| 1D      | UCSG1 : Microprocessor interface config Register  |  |  |  |

| 1E      | UCSG2 : Microprocessor wait/ack config Register   |  |  |  |

| 1F      | CIMaX <sup>™</sup> control Register               |  |  |  |

Note: All registers are reset to 00h. Register bits marked **X** should not be set. They are read as 0. RFU = Reserved for Future Use

# 8.1 CIMaX™ Control Register

This register is used to control the basic functions of  $CIMaX^{TM}$ .

## 8.1.1 CIMaX™ control: (@1Fh)

| KOI A A EOOK | RST X X X | X X | LOCK |

|--------------|-----------|-----|------|

|--------------|-----------|-----|------|

8.1.1.1 LOCK

validates and locks the chip setup

0 chip is not configured. Microprocessor inputs and outputs are inactive

1 chip is configured. Configuration bits are locked and CIMaX™ IOs are active

8.1.1.2 RST

reset chip

equivalent to asserting the RESET pin. CIMaX<sup>™</sup> is reset to its initial state this bit is automatically reset; no need to write 0 in italways reads as 0

1 reset

## 8.2 Modules Control Registers

This register is available for each module A and B to control the initialization and access to them.

## 8.2.1 Module control : (@00h mod A, @09h mod B)

| RST | TSOEN | TSIEN | HAD | ACS1 | ACS0 | AUTO | DET |

|-----|-------|-------|-----|------|------|------|-----|

|     |       |       |     |      |      |      |     |

8.2.1.1 DET

module detection

read only, write has no effect

0 no module present

1 module inserted

8.2.1.2 AUTO

module auto activation on detection

0 no auto activation procedure

Interrupt is generated immediately when DET = 1

1 start module auto activation when DET = 1 if VCC = 1

Interrupt is generated at the end of auto activation

8.2.1.3 ACS[1:0]

module access type

automatically forced to 00 when DET = 0

writing those bits is only allowed when DET = 1

00 access to attribute memory

01 access to I/O space

10 access to common memory

11 access to Extended Channel using CE2# signal

8.2.1.4 HAD

source selection applied to the module

automatically forced to 0 when DET = 0

setting this bit is only allowed when DET = 1 and TSIEN = 0 and TSOEN = 0

0 apply MPEG stream

1 apply A[25:15] for memory access

8.2.1.5 TSIEN

MPEG transport stream input control

20 A/T90FJR I

automatically forced to 0 when DET = 0

setting this bit is only allowed when DET = 1 and HAD = 0

0 no MPEG stream (all signals forced to 0)

1 MPEG stream enabled

#### 8.2.1.6 TSOEN

MPEG transport stream bypass control

automatically forced to 0 when DET = 0 or TSIEN = 0

setting this bit is only allowed when DET = 1 and HAD = 0 and TSIEN = 1

0 bypass enabled

1 bypass disabled (TS through module enabled)

### 8.2.1.7 RST

module RST pin control

automatically forced to 0 when DET = 0

setting this bit is only allowed when DET = 1

The state of this bit is reproduced on the RST (A or B) pin of the module.

# 8.3 Invert Input Mask Register

The Invert Input Mask Register is used to complement selected bits on the incoming MPEG data stream from modules.

## 8.3.1 Invert input mask: (@06h mod A, @0Fh mod B)

| INV7 | INV6 | INV5 | INV4 | INV3 | INV2 | INV1 | INV0 |  |

|------|------|------|------|------|------|------|------|--|

|      |      |      |      |      |      |      |      |  |

### 8.3.1.1 INV[7:0]

Invert mask

0 corresponding bit is not complemented

1 corresponding bit is complemented

### 8.4 Destination Select Register

The Destination Select Register is used to choose which peripheral will be accessed by the microprocessor when selecting the CIMaX<sup>™</sup>. The three available destinations are the two modules and the external device selected by the EXTCS output signal from the CIMaX<sup>™</sup>. For each module, the access mode (memory / IO) is chosen in the Module Control Register.

The destination select can be achieved either manually when AUTOSEL bit is 0 using SEL bits or automatically by configuring the select masks and patterns registers.

### 8.4.1 Destination select: (@17h)

|         |          | Х             | TSWAP                          | XCSDRV           | XCSLVL       | XCSMOD        | SEL1    | SEL0 | AUTOSEL    |

|---------|----------|---------------|--------------------------------|------------------|--------------|---------------|---------|------|------------|

| 8.4.1.1 | AUTOSEL  |               |                                |                  |              |               |         |      |            |

| 0.4.1.1 | HOTOGEE  | automatic mo  | odule selection                |                  |              |               |         |      |            |

|         |          | uses high ord | der addresses t                | o choose modu    | le or extern | al device (us | ing EXT | CS)  |            |

|         |          | 0             | manu                           | al selection     |              |               |         |      |            |

|         |          | 1             | autom                          | natic selection  |              |               |         |      |            |

| 8.4.1.2 | SEL[1:0] |               |                                |                  |              |               |         |      |            |

|         | . ,      | module selec  | et                             |                  |              |               |         |      |            |

|         |          | relevant only | when AUTOSE                    | EL = 0           |              |               |         |      |            |

|         |          | 00            | no destination                 | selected         |              |               |         |      |            |

|         |          | 01            | select module                  | Α                |              |               |         |      |            |

|         |          | 10            | select module                  | В                |              |               |         |      |            |

|         |          | 11            | select externa                 | I device using E | EXTCS        |               |         |      |            |

| 8.4.1.3 | XCSMOD   |               |                                |                  |              |               |         |      |            |

|         |          | EXTCS signa   | al mode                        |                  |              |               |         |      |            |

|         |          |               | bit is only allow              |                  |              |               |         |      |            |

|         |          |               | S signal input one for CE# sig | •                |              |               |         |      | regenerate |

|         |          | 0             | transmit mode                  | )                |              |               |         |      |            |

|         |          | 1             | regenerate mo                  | ode              |              |               |         |      |            |

| 8.4.1.4 | XCSLVL   |               |                                |                  |              |               |         |      |            |

|         |          | EXTCS outpo   | ut pin active lev              | el               |              |               |         |      |            |

|         |          | changing this | bit is only allow              | wed when LOC     | K = 0        |               |         |      |            |

|         |          | 0             | EXTCS pin is                   | active-low       |              |               |         |      |            |

|         |          | 1             | EXTCS pin is                   | active-high      |              |               |         |      |            |

| 8.4.1.5 | XCSDRV   |               |                                |                  |              |               |         |      |            |

|         |          | EXTCS outpo   | ut pin structure               |                  |              |               |         |      |            |

|         |          | changing this | bit is only allow              | wed when LOC     | K = 0        |               |         |      |            |

|         |          | 0             | EXTCS buffer                   | -                |              |               |         |      |            |

|         |          | 1             | EXTCS buffer                   | is push-pull     |              |               |         |      |            |

| 8.4.1.6 | TSWAP    |               |                                |                  |              |               |         |      |            |

|         |          | -             | in order swap (                |                  | ending)      |               |         |      |            |

|         |          | 0             | module A befo                  | ore module B     |              |               |         |      |            |

22 A/T90FJR \_\_\_\_

1 module B before module A

## 8.5 Power Control Register

This register is used to control the power of the modules if the power switch is implemented (optional, see application note). When the VCC bit is 0, no VCC is supposed to be applied to the modules so all the outputs to the modules are in high impedance state. When VCC = 0, ADOE# and DATOE# are also high to put the address and data buffers outputs in high impedance. This implies that when no VCC switch is used, the VCC bit should anyway be set to enable the control signals to be applied to the modules.

## 8.5.1 Power control : (@18h)

| VCDRV | VCLVL | x | X | Х | Х | Х | vcc |

|-------|-------|---|---|---|---|---|-----|

|-------|-------|---|---|---|---|---|-----|

8.5.1.1 VCC

module power supply switch control

changing this bit is only allowed when LOCK = 1

0 power off

1 power on

8.5.1.2 VCLVL

module VCC output pin active level

changing this bit is only allowed when LOCK = 0

0 VCC pin is active-low

1 VCC pin is active-high

8.5.1.3 VCDRV

module VCC output pin structure

changing this bit is only allowed when LOCK = 0

0 VCC buffer is open drain

1 VCC buffer is push-pull

## 8.6 Module Auto Select Registers

When automatic destination selection is used, the module auto select mask indicates the high order address bits used for decoding the address windows for each module and the module auto select pattern register determines the address at which the module is addressed.

### 8.6.1 Auto select mask high: (@01h mod A, @0Ah mod B)

| Х | Х | х | Х | х | MA25 | MA24 | MA23 |

|---|---|---|---|---|------|------|------|

|---|---|---|---|---|------|------|------|

### 8.6.2 Auto select mask low: (@02h mod A, @0Bh mod B)

| MA22 | MA21 | MA20 | MA19 | MA18 | MA17 | MA16 | MA15 |

|------|------|------|------|------|------|------|------|

|------|------|------|------|------|------|------|------|

### 8.6.2.1 MA[25:15]

address mask for decoding

- 0 address bit doesn't care

- 1 address bit should match programmed address bit in module auto select pattern register

## 8.6.3 Auto select mask high external : (@12h)

| DEF | Х | Х | х | x | MA25 | MA24 | MA23 |

|-----|---|---|---|---|------|------|------|

|-----|---|---|---|---|------|------|------|

### 8.6.4 Auto select mask low external : (@13h)