## **TABLE OF CONTENTS**

| Features                                                | 1  |

|---------------------------------------------------------|----|

| Applications                                            | 1  |

| General Description                                     | 1  |

| Revision History                                        | 3  |

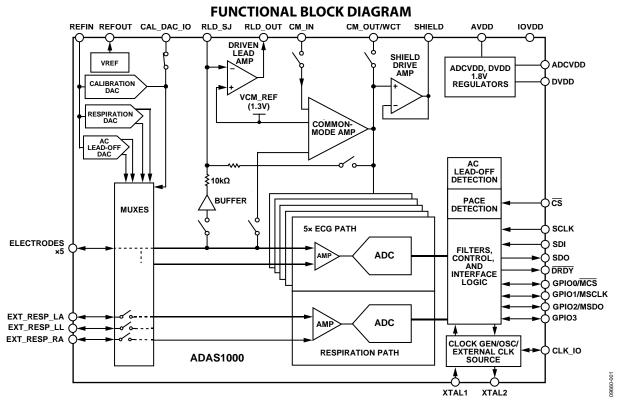

| Functional Block Diagram                                | 4  |

| Specifications                                          | 5  |

| Noise Performance                                       | 10 |

| Timing Characteristics                                  | 11 |

| Absolute Maximum Ratings                                | 14 |

| Thermal Resistance                                      | 14 |

| ESD Caution                                             | 14 |

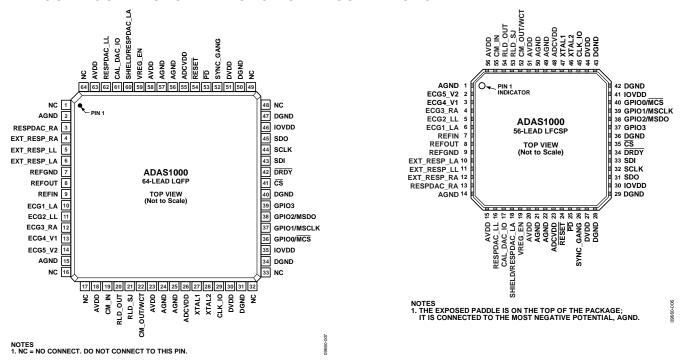

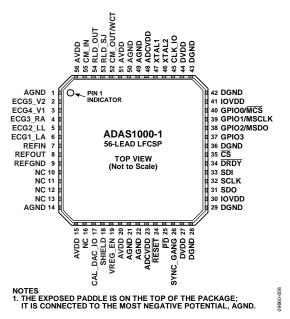

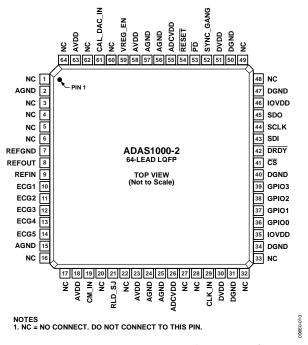

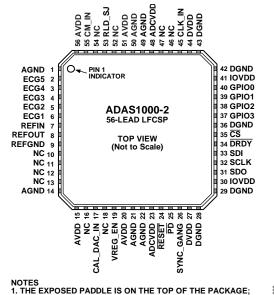

| Pin Configurations and Function Descriptions            | 15 |

| Typical Performance Characteristics                     | 19 |

| Applications Information                                | 26 |

| Overview                                                | 26 |

| ECG Inputs—Electrodes/Leads                             | 29 |

| ECG Channel                                             | 30 |

| Electrode/Lead Formation and Input Stage Configuration. | 31 |

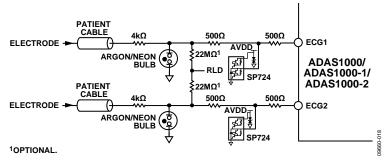

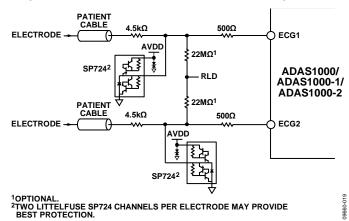

| Defibrillator Protection                                | 35 |

| ESIS Filtering                                          | 35 |

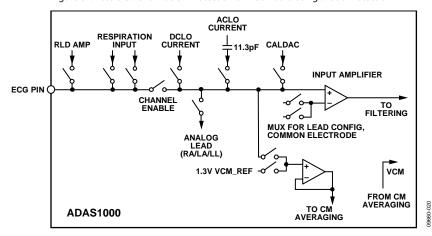

| ECG Path Input Multiplexing                             | 35 |

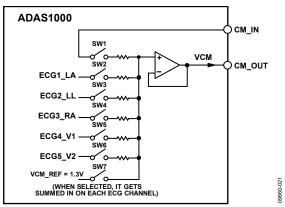

| Common-Mode Selection and Averaging                     | 36 |

| Wilson Central Terminal (WCT)                           | 37 |

| Right Leg Drive/Reference Drive                         | 37 |

| Calibration DAC                                         | 38 |

| Gain Calibration                                        | 38 |

| Lead-Off Detection                                      | 38 |

| AC Lead-Off Detection                                   | 39 |

| Shield Driver                                           | 40 |

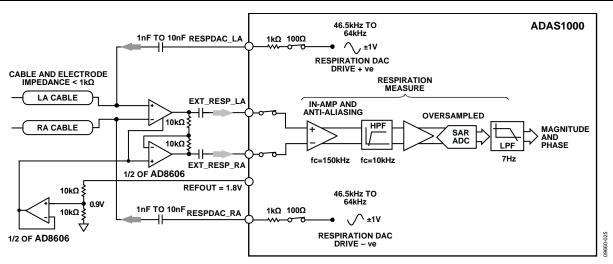

| Respiration (ADAS1000 Model Only)                       | 40 |

| Evaluating Respiration Performance                      | 43 |

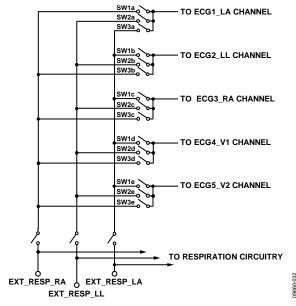

| Extend Switch On Respiration Paths                      | 44 |

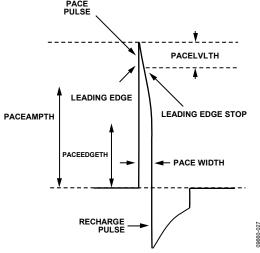

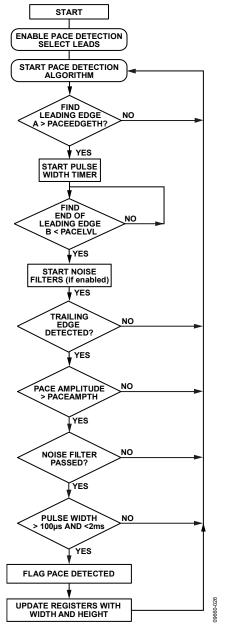

| Pacing Artifact Detection Function (ADAS1000 Only) 45                          |

|--------------------------------------------------------------------------------|

| Biventricular Pacers                                                           |

| Pace Detection Measurements                                                    |

| Evaluating Pace Detection Performance                                          |

| Pace Width                                                                     |

| Pace Latency                                                                   |

| Pace Detection via Secondary Serial Interface (ADAS1000 and ADAS1000-1 Only)48 |

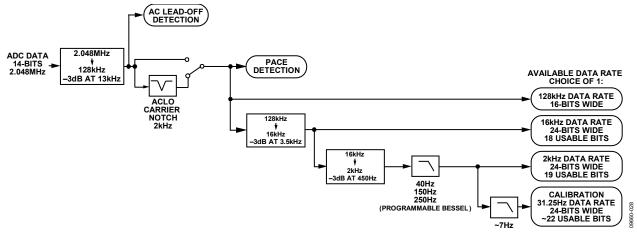

| Filtering                                                                      |

| Voltage Reference50                                                            |

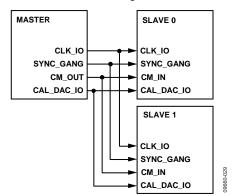

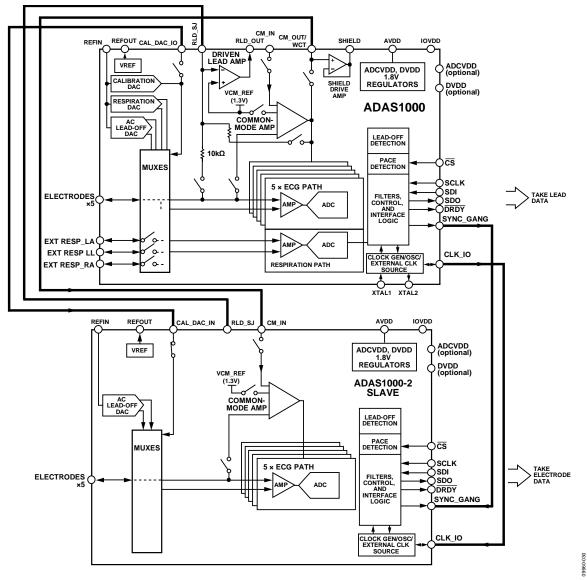

| Gang Mode Operation50                                                          |

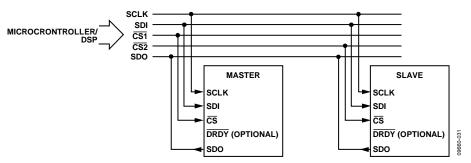

| Interfacing in Gang Mode52                                                     |

| Serial Interfaces                                                              |

| Standard Serial Interface                                                      |

| SPI Interface Resync56                                                         |

| Secondary Serial Interface                                                     |

| RESET58                                                                        |

| PD Function                                                                    |

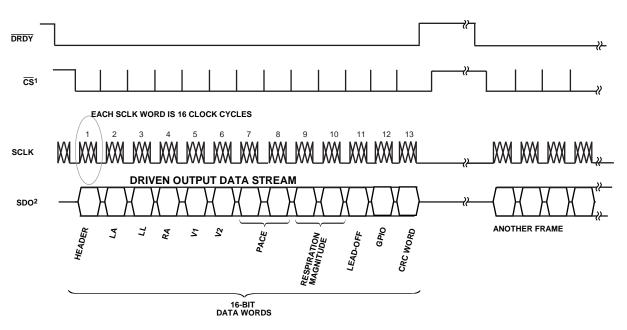

| SPI Output Frame Structure (ECG and Status Data) 59                            |

| SPI Register Definitions and Memory Map 60                                     |

| Control Registers Details                                                      |

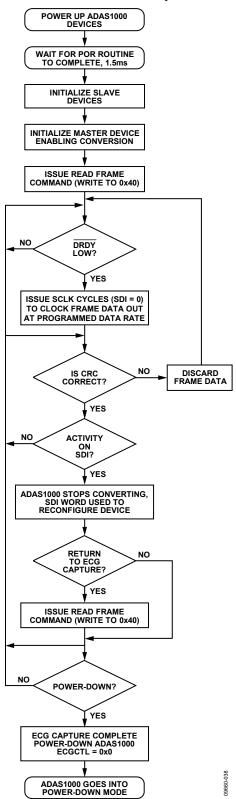

| Examples of Interfacing to the ADAS1000                                        |

| Software Flowchart                                                             |

| Power Supply, Grounding, and Decoupling Strategy 83                            |

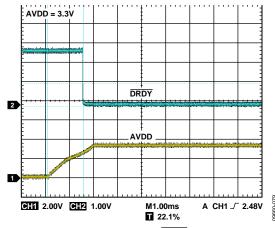

| AVDD83                                                                         |

| ADCVDD and DVDD Supplies83                                                     |

| Unused Pins/Paths83                                                            |

| Layout Recommendations83                                                       |

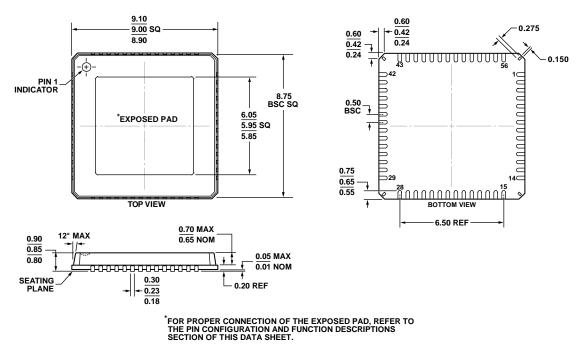

| Outline Dimensions                                                             |

| Ordering Guide85                                                               |

## **Data Sheet**

# ADAS1000/ADAS1000-1/ADAS1000-2

### **REVISION HISTORY**

| 11/2018—Rev. B to Rev. C                                     |     |

|--------------------------------------------------------------|-----|

| Changes to Table 2                                           | 5   |

| Changes to Table 9                                           |     |

| Changes to Figure 35                                         | 22  |

| Changes to Figure 36 Through Figure 41                       | 23  |

| Change to Figure 53                                          |     |

| Change to Figure 54                                          | 27  |

| Changes to DC Lead-Off and High Gains Section                | 38  |

| Added DC Lead-Off Debounce Timer Section                     | 39  |

| Changes to AC Lead-Off Detection Section                     | 39  |

| Added ACLO and Common-Mode Configuration Section             | 40  |

| Changes to Figure 69                                         | 41  |

| Changes to Figure 71, Table 13, and Table 14                 | 43  |

| Changes to Pace Amplitude Threshold Section                  | 47  |

| Changes to Synchronizing Devices Section and Figure 76       | 50  |

| Changes to Sequencing Devices into Gang Mode Section         | 51  |

| Added Number of Devices in Gang Mode Section                 | 51  |

| Added SPI Interface Resync Section                           | 56  |

| Changes to CRC Word Section, Clocks Section, and             |     |

| Figure 80                                                    | 57  |

| Changes to Table 28                                          | 61  |

| Change to Table 32                                           | 66  |

| Changes to Table 43                                          | 72  |

| Changes to Table 44                                          | 73  |

| Changes to Table 47                                          | 74  |

| Changes to Table 48                                          | 75  |

| Changes to Table 52                                          | 77  |

| Changes to Example 6: Writing to Master and Slave Devices    | and |

| Streaming Conversion Data Section, and Table 61              | 81  |

| Changes to Power Supply, Grounding, and Decoupling Strategy  | 7   |

| Section                                                      | 83  |

|                                                              |     |

| 6/2014—Rev. A to Rev. B                                      |     |

| Moved Revision History                                       |     |

| Change to AC Lead-Off, Frequency Range Parameter, Table      |     |

| Changes to Figure 17                                         |     |

| Changes to Figure 40 and Figure 41                           |     |

| Changes to ECG Channel Section                               |     |

| Replaced Figure 57                                           |     |

| Added Figure 58, Figure 59, Figure 60, Figure 61, and Figure |     |

| Renumbered Sequentially                                      | 31  |

| Deleted Figure 63, Figure 64, and Figure 65; Renumbered    |    |

|------------------------------------------------------------|----|

| Sequentially                                               | 35 |

| Change to Figure 65, Figure 66, and Figure 67              | 3! |

| Changes to Lead-Off Detection Section, Added Figure 68;    |    |

| Renumbered Sequentially                                    | 37 |

| Changes to Respiration (ADAS1000 Model Only) Section and   |    |

| Figure 69, Figure 70, and Figure 71; Added Table 13 and    |    |

| Table 14; Renumbered Sequentially                          | 39 |

| Changes to Pacing Artifact Detection Function (ADAS1000    |    |

| Only) Section                                              | 42 |

| Changes to Evaluating Pace Detection Performance Section   | 4  |

| Added Pace Width Section                                   | 4  |

| Changes to Standard Serial Interface Section               | 50 |

| Changes to Data Ready (DRDY) Section                       | 52 |

| Changes to Secondary Serial Interface Section and Table 25 | 54 |

| Change to Bit 3, Table 28                                  | 57 |

| Changes to Table 43                                        | 67 |

| Change to Table 45                                         | 68 |

| Changes to Table 50                                        | 70 |

| Changes to Table 52                                        | 7  |

| Changes to Table 53                                        | 72 |

| 1/2013—Rev. 0 to Rev. A                                    |    |

| Changes to Features Section                                |    |

| Changes to Table 1                                         |    |

| Changes to Excitation Current, Test Conditions/Comments,   |    |

| Table 2                                                    |    |

| Added Table 3; Renumbered Sequentially                     |    |

| Changes to Respiration (ADAS1000 Model Only) Section,      |    |

| Figure 66, and Internal Respiration Capacitors Section     | 37 |

| Changes to Figure 67                                       | 38 |

| Changes to Figure 68                                       |    |

| Added Evaluating Pace Detection Performance Section        |    |

| Added Table 15                                             |    |

| Changes to Clocks Section                                  | 5  |

| Changes to RESPAMP Name, Function, Table 28                |    |

| Changes to Bits[14:9], Function, Table 30                  |    |

| Changes to Ordering Guide                                  |    |

8/2012—Revision 0: Initial Version

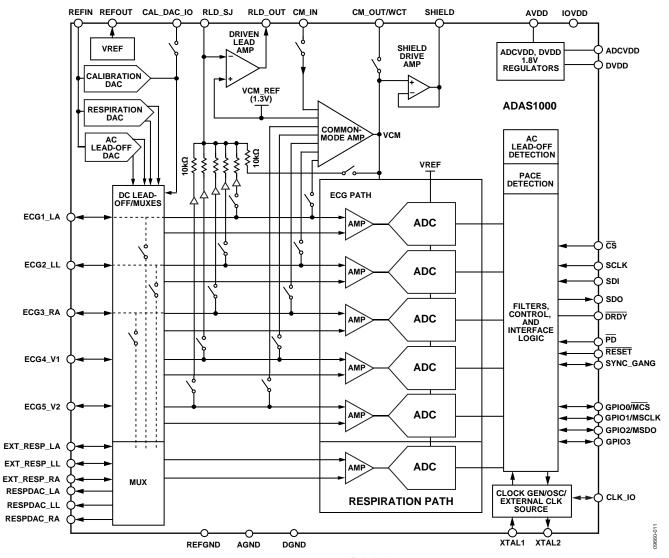

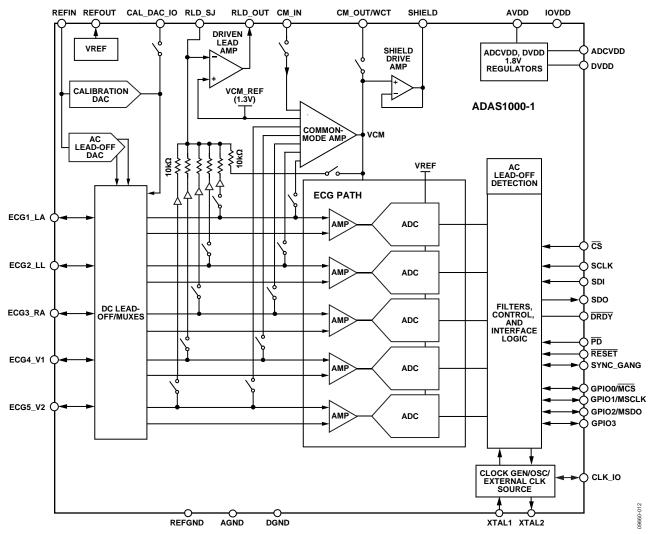

Figure 1. ADAS 1000 Full Featured Model

Table 1. Overview of Features Available from ADAS1000 Generics

|                      |                |              |                 |             | Pace      | Shield | Master                 | Package     |

|----------------------|----------------|--------------|-----------------|-------------|-----------|--------|------------------------|-------------|

| Generic <sup>1</sup> | ECG            | Operation    | Right Leg Drive | Respiration | Detection | Driver | Interface <sup>2</sup> | Option      |

| ADAS1000             | 5 ECG channels | Master/slave | Yes             | Yes         | Yes       | Yes    | Yes                    | LFCSP, LQFP |

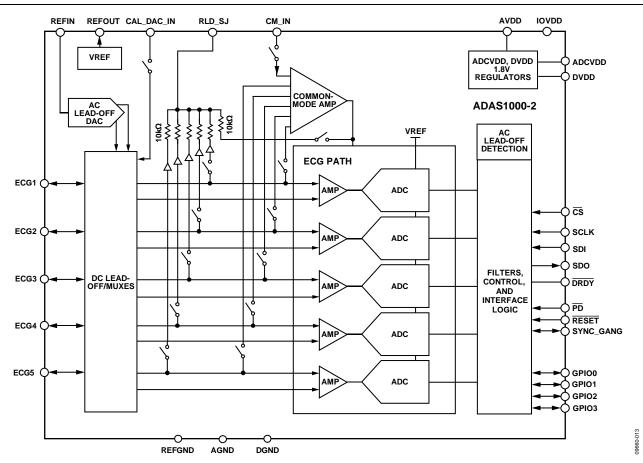

| ADAS1000-1           | 5 ECG channels | Master/slave | Yes             |             |           | Yes    | Yes                    | LFCSP       |

| ADAS1000-2           | 5 ECG channels | Slave        |                 |             |           |        |                        | LFCSP, LQFP |

| ADAS1000-3           | 3 ECG channels | Master/slave | Yes             |             |           | Yes    | Yes                    | LFCSP, LQFP |

| ADAS1000-4           | 3 ECG channels | Master/slave | Yes             | Yes         | Yes       | Yes    | Yes                    | LFCSP, LQFP |

<sup>&</sup>lt;sup>1</sup> The ADAS1000-2 is a companion device for increased channel count purposes. It has a subset of features and is not intended for standalone use. It can be used in conjunction with any master device.

<sup>&</sup>lt;sup>2</sup> Master interface is provided for users wishing to utilize their own digital pace algorithm; see the Secondary Serial Interface section.

### **SPECIFICATIONS**

AVDD = 3.3 V  $\pm$  5%, IOVDD = 1.65 V to 3.6 V, AGND = DGND = 0 V, REFIN tied to REFOUT, externally supplied crystal/clock = 8.192 MHz. Decoupling for reference and supplies as noted in the Power Supply, Grounding, and Decoupling Strategy section.  $T_A = -40^{\circ}\text{C}$  to +85°C, unless otherwise noted. Typical specifications are mean values at  $T_A = 25^{\circ}\text{C}$ .

For specified performance, internal ADCVDD and DVDD linear regulators have been used. They may be supplied from external regulators. ADCVDD =  $1.8 \text{ V} \pm 5\%$ , DVDD =  $1.8 \text{ V} \pm 5\%$ .

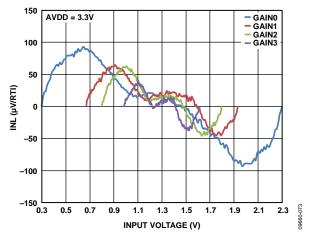

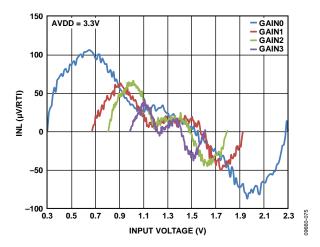

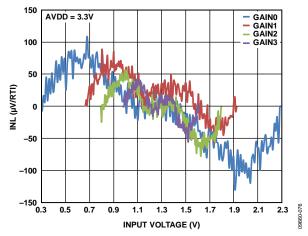

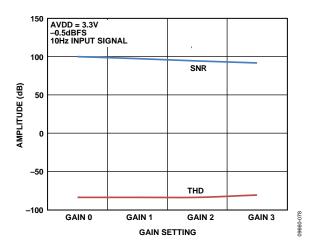

Front-end gain settings: GAIN  $0 = \times 1.4$ , GAIN  $1 = \times 2.1$ , GAIN  $2 = \times 2.8$ , GAIN  $3 = \times 4.2$ .

Table 2.

| Parameter                                            | Min  | Тур   | Max  | Unit   | Test Conditions/Comments                                                                                                                                                  |

|------------------------------------------------------|------|-------|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

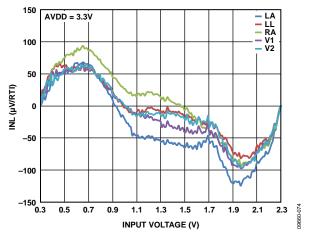

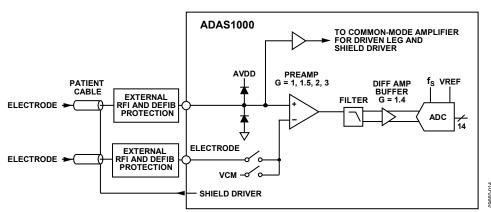

| ECG CHANNEL                                          |      |       |      |        | These specifications apply to the following pins:<br>ECG1_LA, ECG2_LL, ECG3_RA, ECG4_V1, ECG5_V2,<br>CM_IN (CE mode), EXT_RESP_xx pins when used in<br>extend switch mode |

| Electrode Input Range                                |      |       |      |        | Independent of supply                                                                                                                                                     |

|                                                      | 0.3  | 1.3   | 2.3  | V      | GAIN 0 (gain setting ×1.4)                                                                                                                                                |

|                                                      | 0.63 | 1.3   | 1.97 | V      | GAIN 1 (gain setting ×2.1)                                                                                                                                                |

|                                                      | 0.8  | 1.3   | 1.8  | V      | GAIN 2 (gain setting ×2.8)                                                                                                                                                |

|                                                      | 0.97 | 1.3   | 1.63 | V      | GAIN 3 (gain setting ×4.2)                                                                                                                                                |

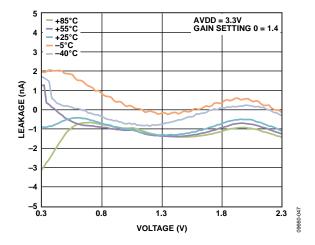

| Input Bias Current                                   | -10  | ±1    | +10  | nA     | Relates to each electrode input; over specified electrode input range; dc and ac lead-off are disabled, applies at ambient temperature, $T_A = 25^{\circ}C$               |

|                                                      | -20  | ±1    | +20  | nA     | Relates to each electrode input; over specified electrode input range; dc and ac lead-off are disabled, applies across full temperature range, $T_A = -40$ °C to $+85$ °C |

|                                                      | -200 |       | +200 | nA     | Over full AGND to AVDD input range                                                                                                                                        |

| Input Offset                                         | 200  | -7    | 1200 | mV     | Electrode/vector mode with VCM = VCM REF GAIN 3                                                                                                                           |

| input onset                                          |      | -7    |      | mV     | GAIN 2                                                                                                                                                                    |

|                                                      |      | -15   |      | mV     | GAIN 1                                                                                                                                                                    |

|                                                      |      | -22   |      | mV     | GAIN 0                                                                                                                                                                    |

| Input Offset Tempco <sup>1</sup>                     |      | ±2    |      | μV/°C  | G/IIIV 0                                                                                                                                                                  |

| Input Amplifier Input Impedance <sup>2</sup>         |      | 1  10 |      | GΩ  pF | At 10 Hz                                                                                                                                                                  |

| CMRR <sup>2</sup>                                    | 105  | 110   |      | dB     | 51 k $\Omega$ imbalance, 60 Hz with $\pm 300$ mV differential dc offset; per AAMI/IEC standards; with driven leg loop close                                               |

| Crosstalk <sup>1</sup>                               |      | 80    |      | dB     | Between channels                                                                                                                                                          |

| Resolution <sup>2</sup>                              |      | 19    |      | Bits   | Electrode/vector mode, 2 kHz data rate, 24-bit data-word                                                                                                                  |

|                                                      |      | 18    |      | Bits   | Electrode/vector mode, 16 kHz data rate, 24-bit data-wor                                                                                                                  |

|                                                      |      | 16    |      | Bits   | Electrode/analog lead mode, 128 kHz data rate, 16-bit data-word                                                                                                           |

| Integral Nonlinearity Error                          |      | 30    |      | ppm    | GAIN 0; all data rates                                                                                                                                                    |

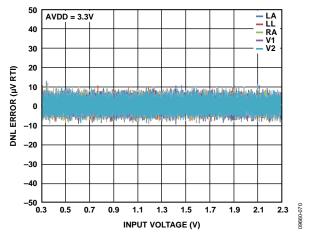

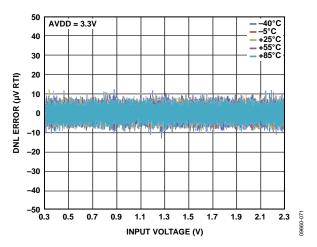

| Differential Nonlinearity Error<br>Gain <sup>2</sup> |      | 5     |      | ppm    | GAIN 0 Referred to input. $(2 \times VREF)/Gain/(2^N - 1)$ ; applies after factory calibration; user calibration adjusts this number                                      |

| GAIN 0 (×1.4)                                        |      | 4.9   |      | μV/LSB | At 19-bit level in 2 kHz data rate                                                                                                                                        |

|                                                      |      | 9.81  |      | μV/LSB | At 18-bit level in 16 kHz data rate                                                                                                                                       |

|                                                      |      | 39.24 |      | μV/LSB | At 16-bit level in 128 kHz data rate                                                                                                                                      |

| GAIN 1 (×2.1)                                        |      | 3.27  |      | μV/LSB | At 19-bit level in 2 kHz data rate                                                                                                                                        |

|                                                      |      | 6.54  |      | μV/LSB | At 18-bit level in 16 kHz data rate                                                                                                                                       |

|                                                      |      | 26.15 |      | μV/LSB | At 16-bit level in 128 kHz data rate                                                                                                                                      |

| GAIN 2 (×2.8)                                        |      | 2.45  |      | μV/LSB | At 19-bit level in 2 kHz data rate                                                                                                                                        |

|                                                      |      | 4.9   |      | μV/LSB | At 18-bit level in 16 kHz data rate                                                                                                                                       |

|                                                      |      | 19.62 |      | μV/LSB | At 16-bit level in 128 kHz data rate                                                                                                                                      |

| GAIN 3 (×4.2)                                        |      | 1.63  |      | μV/LSB | No factory calibration for this gain setting<br>At 19-bit level in 2 kHz data rate                                                                                        |

|                                                      |      | 3.27  |      | μV/LSB | At 18-bit level in 16 kHz data rate                                                                                                                                       |

|                                                      |      | 13.08 |      | μV/LSB | At 16-bit level in 128 kHz data rate                                                                                                                                      |

| Parameter                               | Min  | Тур         | Max  | Unit   | Test Conditions/Comments                                                                                                                                                                             |

|-----------------------------------------|------|-------------|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

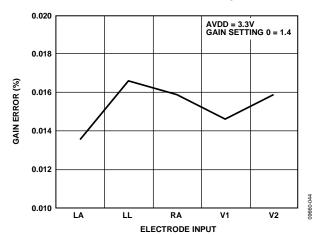

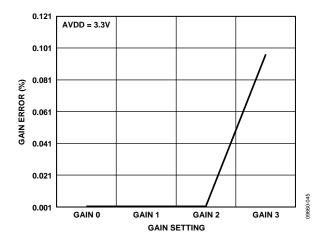

| Gain Error                              | -1   | +0.01       | +1   | %      | GAIN 0 to GAIN 2, factory calibrated; programmable user or factory calibration option enables; factory gair                                                                                          |

|                                         |      |             |      |        | calibration applies only to standard ECG interface                                                                                                                                                   |

|                                         | -2   | +0.1        | +2   | %      | GAIN 3 setting, no factory calibration for this gain                                                                                                                                                 |

| Gain Matching                           | -0.1 | +0.02       | +0.1 | %      | GAIN 0 to GAIN 2                                                                                                                                                                                     |

|                                         | -0.5 | +0.1        | +0.5 | %      | GAIN 3                                                                                                                                                                                               |

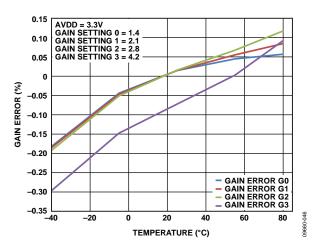

| Gain Tempco <sup>1</sup>                |      | 25          |      | ppm/°C |                                                                                                                                                                                                      |

| Input Referred Noise1                   |      |             |      |        | GAIN 2, 2 kHz data rate, see Table 4                                                                                                                                                                 |

| Analog Lead Mode                        |      | 6           |      | μV p-p | 0.5 Hz to 40 Hz; high performance mode                                                                                                                                                               |

|                                         |      | 10          |      | μV p-p | 0.05 Hz to 150 Hz; high performance mode                                                                                                                                                             |

|                                         |      | 12          |      | μV p-p | 0.05 Hz to 150 Hz; low power mode                                                                                                                                                                    |

| Electrode Mode                          |      | 11          |      | μV p-p | 0.05 Hz to 150 Hz; high performance mode                                                                                                                                                             |

|                                         |      | 12          |      | μV p-p | 0.05 Hz to 150 Hz; low power mode                                                                                                                                                                    |

| Digital Lead Mode                       |      | 14          |      | μV p-p | 0.05 Hz to 150 Hz; high performance mode                                                                                                                                                             |

|                                         |      | 16          |      | μV p-p | 0.05 Hz to 150 Hz; low power mode                                                                                                                                                                    |

| Power Supply Sensitivity <sup>2</sup>   |      | 100         |      | dB     | At 120 Hz                                                                                                                                                                                            |

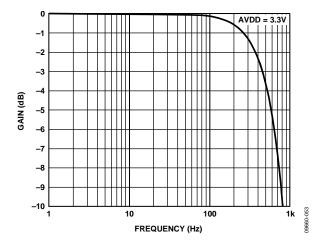

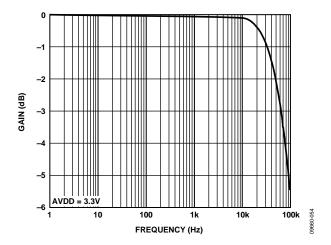

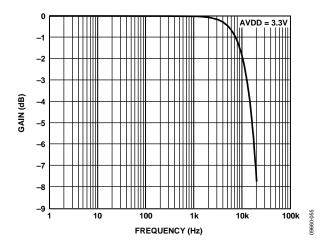

| Analog Channel Bandwidth <sup>1</sup>   |      | 65          |      | kHz    |                                                                                                                                                                                                      |

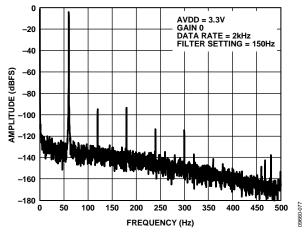

| Dynamic Range <sup>1</sup>              |      | 104         |      | dB     | GAIN 0, 2 kHz data rate, –0.5 dBFS input signal, 10 Hz                                                                                                                                               |

| Signal-to-Noise Ratio <sup>1</sup>      |      | 100         |      | dB     | –0.5 dB FS input signal                                                                                                                                                                              |

| COMMON-MODE INPUT                       |      |             |      |        | CM_IN pin                                                                                                                                                                                            |

| Input Voltage Range                     | 0.3  |             | 2.3  | V      |                                                                                                                                                                                                      |

| Input Impedance <sup>2</sup>            |      | 1  10       |      | GΩ  pF |                                                                                                                                                                                                      |

| Input Bias Current                      | -40  | ±1          | +40  | nA     | Over operating range; dc and ac lead-off disabled                                                                                                                                                    |

| ·                                       | -200 |             | +200 | nA     | AGND to AVDD                                                                                                                                                                                         |

| COMMON-MODE OUTPUT                      |      |             |      |        | CM_OUT pin                                                                                                                                                                                           |

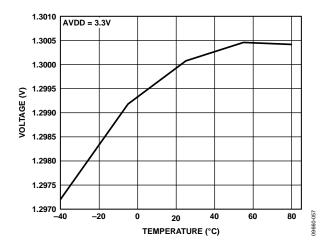

| VCM_REF                                 | 1.28 | 1.3         | 1.32 | V      | Internal voltage; independent of supply                                                                                                                                                              |

| Output Voltage, VCM                     | 0.3  | 1.3         | 2.3  | v      | No dc load                                                                                                                                                                                           |

| Output Impedance <sup>1</sup>           |      | 0.75        | 2.0  | kΩ     | Not intended to drive current                                                                                                                                                                        |

| Short Circuit Current <sup>1</sup>      |      | 4           |      | mA     | Not interfaced to drive edifferit                                                                                                                                                                    |

| Electrode Summation                     |      | 1           |      | %      | Resistor matching error                                                                                                                                                                              |

| Weighting Error <sup>2</sup>            |      |             |      | 70     |                                                                                                                                                                                                      |

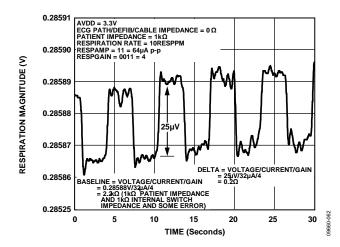

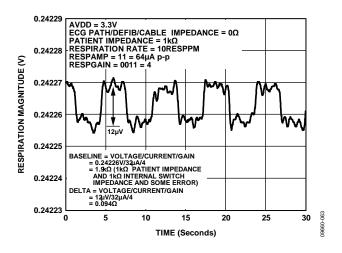

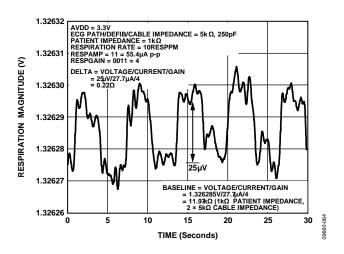

| RESPIRATION FUNCTION<br>(ADAS1000 ONLY) |      |             |      |        | These specifications apply to the following pins:<br>EXT_RESP_LA, EXT_RESP_LL, EXT_RESP_RA and selected<br>internal respiration paths (Lead I, Lead II, Lead III)                                    |

| Input Voltage Range                     | 0.3  |             | 2.3  | V      | AC-coupled, independent of supply                                                                                                                                                                    |

| Input Voltage Range (Linear             | 0.5  | 1.8/gain    | 2.3  | V p-p  | Programmable gain (10 states)                                                                                                                                                                        |

| Operation)                              |      | 1.0/ gaii i |      | VPP    | rrogrammable gam (10 states)                                                                                                                                                                         |

| Input Bias Current                      | -10  | ±1          | +10  | nA     | Applies to EXT_RESP_xx pins over AGND to AVDD                                                                                                                                                        |

| Input Referred Noise <sup>1</sup>       |      | 0.85        |      | μV rms |                                                                                                                                                                                                      |

| Frequency <sup>2</sup>                  |      | 46.5 to 64  |      | kHz    | Programmable frequency, see Table 30                                                                                                                                                                 |

| Excitation Current                      |      |             |      |        | Respiration drive current corresponding to differential voltage programmed by RESPAMP bits in RESPCTL register. Internal respiration mode, cable 5 k $\Omega$ /200 pF 1.2 k $\Omega$ chest impedance |

|                                         |      | 64          |      | μА р-р | Drive Range A                                                                                                                                                                                        |

|                                         |      | 32          |      | μΑ р-р | Drive Range B <sup>2</sup>                                                                                                                                                                           |

|                                         |      | 16          |      | μА р-р | Drive Range C <sup>2</sup>                                                                                                                                                                           |

|                                         |      | 8           |      | μΑ р-р | Drive Range D <sup>2</sup>                                                                                                                                                                           |

| Resolution <sup>2</sup>                 |      | 24          |      | bits   | Update rate 125 Hz                                                                                                                                                                                   |

| Measurement Resolution <sup>1</sup>     |      | 0.2         |      | Ω      | Cable $<$ 5 k $\Omega$ /200 pF per electrode, body resistance modeled as 1.2 k $\Omega$                                                                                                              |

|                                         |      | 0.02        |      | Ω      | No cable impedance, body resistance modeled as 1.2 kg                                                                                                                                                |

| In-Amp Gain <sup>1</sup>                |      | 1 to 10     |      |        | Digitally programmable in steps of 1                                                                                                                                                                 |

| Gain Error                              |      | . 10 10     | 1    | %      | LSB weight for GAIN 0 setting                                                                                                                                                                        |

| Gain Tempco <sup>1</sup>                |      | 25          | •    | ppm/C  | 200 Weight for Grant o Setting                                                                                                                                                                       |

| Parameter                                                 | Min   | Тур   | Max        | Unit     | Test Conditions/Comments                                                                                                         |

|-----------------------------------------------------------|-------|-------|------------|----------|----------------------------------------------------------------------------------------------------------------------------------|

| RIGHT LEG DRIVE/DRIVEN LEAD<br>(ADAS1000/ADAS1000-1 ONLY) |       |       |            |          |                                                                                                                                  |

| Output Voltage Range                                      | 0.2   |       | AVDD - 0.2 | V        |                                                                                                                                  |

| RLD_OUT Short Circuit Current                             | -5    | ±2    | +5         | mA       | External protection resistor required to meet regulatory patient current limits; output shorted to AVDD/AGND                     |

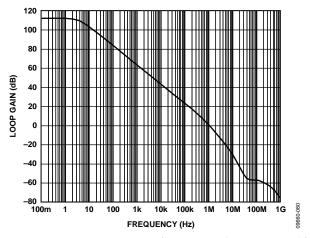

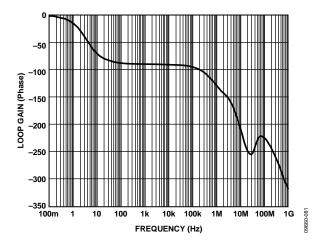

| Closed-Loop Gain Range <sup>2</sup>                       | 25    |       |            | V/V      |                                                                                                                                  |

| Slew Rate <sup>2</sup>                                    |       | 200   |            | mV/ms    |                                                                                                                                  |

| Input Referred Noise <sup>1</sup>                         |       | 8     |            | μV p-p   | 0.05 Hz to 150 Hz                                                                                                                |

| Amplifier GBP <sup>2</sup>                                |       | 1.5   |            | MHz      |                                                                                                                                  |

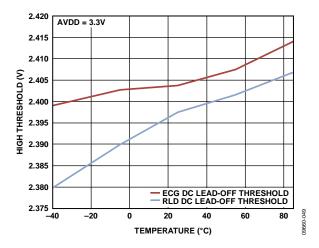

| DC LEAD-OFF                                               |       |       |            |          | Internal current source, pulls up open ECG pins;<br>programmable in 10 nA steps: 10 nA to 70 nA                                  |

| Lead-Off Current Accuracy                                 |       | ±10   |            | %        | Of programmed value                                                                                                              |

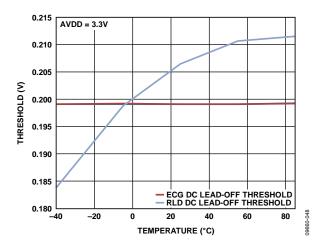

| High Threshold Level <sup>1</sup>                         |       | 2.4   |            | V        | Inputs are compared to threshold levels; if inputs exceed levels, lead-off flag is raised                                        |

| Low Threshold Level <sup>1</sup>                          |       | 0.2   |            | V        |                                                                                                                                  |

| Threshold Accuracy                                        |       | 25    |            | mV       |                                                                                                                                  |

| AC LEAD-OFF                                               |       |       |            |          | Programmable in 4 steps: 12.5 nA rms, 25 nA rms, 50 nA rms, 100 nA rms                                                           |

| Frequency Range                                           |       | 2.039 |            | kHz      | Fixed frequency                                                                                                                  |

| Lead-Off Current Accuracy                                 |       | ±10   |            | %        | Of programmed value, measured into low impedance                                                                                 |

| REFIN                                                     |       |       |            |          |                                                                                                                                  |

| Input Range <sup>2</sup>                                  | 1.76  | 1.8   | 1.84       | V        | Channel gain scales directly with REFIN                                                                                          |

| Input Current                                             |       | 113   |            | μA       | Per active ADC                                                                                                                   |

|                                                           | 450   | 675   | 950        | μΑ       | 5 ECG channels and respiration enabled                                                                                           |

| REFOUT                                                    |       |       |            |          | On-chip reference voltage for ADC; not intended to drive other components reference inputs directly, must be buffered externally |

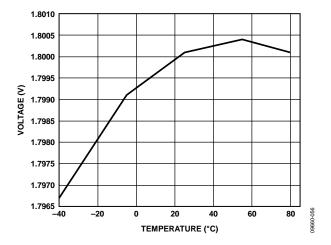

| Output Voltage, VREF                                      | 1.785 | 1.8   | 1.815      | V        | ast we sumered externally                                                                                                        |

| Reference Tempco <sup>1</sup>                             | 05    | ±10   |            | ppm/°C   |                                                                                                                                  |

| Output Impedance <sup>2</sup>                             |       | 0.1   |            | Ω        |                                                                                                                                  |

| Short Circuit Current <sup>1</sup>                        |       | 4.5   |            | mA       | Short circuit to ground                                                                                                          |

| Voltage Noise <sup>1</sup>                                |       | 33    |            | μV p-p   | 0.05 Hz to 150 Hz (ECG band)                                                                                                     |

| -                                                         |       | 17    |            | μV p-p   | 0.05 Hz to 5 Hz (respiration)                                                                                                    |

| CALIBRATION DAC                                           |       |       |            |          | Available on CAL_DAC_IO (output for master, input for slave)                                                                     |

| DAC Resolution                                            |       | 10    |            | Bits     | ,                                                                                                                                |

| Full-Scale Output Voltage                                 | 2.64  | 2.7   | 2.76       | V        | No load, nominal FS output is 1.5 × REFOUT                                                                                       |

| Zero-Scale Output Voltage                                 | 0.24  | 0.3   | 0.36       | V        | No load                                                                                                                          |

| DNL                                                       | -1    |       | +1         | LSB      |                                                                                                                                  |

| Output Series Resistance <sup>2</sup>                     |       | 10    |            | kΩ       | Not intended to drive low impedance load, used for slave CAL_DAC_IO configured as an input                                       |

| Input Current                                             |       | ±5    |            | nA       | When used as input                                                                                                               |

| CALIBRATION DAC TEST TONE                                 |       |       |            |          |                                                                                                                                  |

| Output Voltage                                            | 0.9   | 1     | 1.1        | mV p-p   | Rides on common-mode voltage, VCM_REF = 1.3 V                                                                                    |

| Square Wave                                               |       | 1     |            | Hz       |                                                                                                                                  |

| Low Frequency Sine Wave                                   |       | 10    |            | Hz       |                                                                                                                                  |

| High Frequency Sine Wave                                  |       | 150   |            | Hz       |                                                                                                                                  |

| SHIELD DRIVER (ADAS1000/<br>ADAS1000-1 ONLY)              |       |       |            |          |                                                                                                                                  |

| Output Voltage Range<br>Gain                              | 0.3   | 1     | 2.3        | V<br>V/V | Rides on common-mode voltage, VCM                                                                                                |

| Gain<br>Offset Voltage                                    | 20    | 1     | 120        |          |                                                                                                                                  |

| Short Circuit Current                                     | -20   | 15    | +20<br>25  | mV<br>μA | Output current limited by internal series resistance                                                                             |

| Stable Capacitive Load <sup>2</sup>                       |       | IJ    | 25<br>10   | μA<br>nF | Output current innited by internal series resistance                                                                             |

| CRYSTAL OSCILLATOR                                        |       |       | 10         | 111      | Applied to XTAL1 and XTAL2                                                                                                       |

| Frequency <sup>2</sup>                                    |       | 8.192 |            | MHz      | Applied to ATALT dilu ATALZ                                                                                                      |

| Start-Up Time <sup>2</sup>                                |       | 15    |            | ms       | Internal startup                                                                                                                 |

| Parameter                                        | Min         | Тур      | Max                | Unit  | Test Conditions/Comments                                                                        |

|--------------------------------------------------|-------------|----------|--------------------|-------|-------------------------------------------------------------------------------------------------|

| CLOCK_IO                                         |             |          |                    |       | External clock source supplied to CLK_IO; this pin is configured as an input when the device is |

| Operating Frequency?                             |             | 0.102    |                    | NALL- | programmed as a slave                                                                           |

| Operating Frequency <sup>2</sup>                 | 20          | 8.192    | 00                 | MHz   |                                                                                                 |

| Input Duty Cycle <sup>2</sup>                    | 20          |          | 80                 | %     |                                                                                                 |

| Output Duty Cycle <sup>2</sup>                   |             | 50       |                    | %     |                                                                                                 |

| DIGITAL INPUTS                                   |             |          |                    |       | Applies to all digital inputs                                                                   |

| Input Low Voltage, V <sub>IL</sub>               |             |          | $0.3 \times IOVDD$ | V     |                                                                                                 |

| Input High Voltage, V <sub>IH</sub>              | 0.7 × IOVDD |          |                    | V     |                                                                                                 |

| Input Current, I <sub>IH</sub> , I <sub>IL</sub> | -1          |          | +1                 | μΑ    |                                                                                                 |

|                                                  | -20         |          | +20                | μΑ    | RESET has an internal pull-up                                                                   |

| Pin Capacitance <sup>2</sup>                     |             | 3        |                    | pF    |                                                                                                 |

| DIGITAL OUTPUTS                                  |             |          |                    |       |                                                                                                 |

| Output Low Voltage, Vol                          |             |          | 0.4                | V     | $I_{SINK} = 1 \text{ mA}$                                                                       |

| Output High Voltage, V <sub>OH</sub>             | IOVDD – 0.4 |          |                    | V     | $I_{SOURCE} = -1 \text{ mA}$                                                                    |

| Output Rise/Fall Time                            |             | 4        |                    | ns    | Capacitive load = 15 pF, 20% to 80%                                                             |

| OVDD REGULATOR                                   |             |          |                    |       | Internal 1.8 V regulator for DVDD                                                               |

| Output Voltage                                   | 1.75        | 1.8      | 1.85               | V     |                                                                                                 |

| Available Current <sup>1</sup>                   |             | 1        |                    | mA    | Droop < 10 mV; for external device loading purposes                                             |

| Short Circuit Current limit                      |             | 40       |                    | mA    |                                                                                                 |

| ADCVDD REGULATOR                                 |             |          |                    |       | Internal 1.8 V regulator for ADCVDD; not                                                        |

|                                                  |             |          |                    |       | recommended as a supply for other circuitry                                                     |

| Output Voltage                                   | 1.75        | 1.8      | 1.85               | V     |                                                                                                 |

| Short Circuit Current Limit                      |             | 40       |                    | mA    |                                                                                                 |

| POWER SUPPLY RANGES <sup>2</sup>                 |             |          |                    |       |                                                                                                 |

| AVDD                                             | 3.15        | 3.3      | 5.5                | V     |                                                                                                 |

| IOVDD                                            | 1.65        |          | 3.6                | V     |                                                                                                 |

| ADCVDD                                           | 1.71        | 1.8      | 1.89               | V     | If applied by external 1.8 V regulator                                                          |

| DVDD                                             | 1.71        | 1.8      | 1.89               | V     | If applied by external 1.8 V regulator                                                          |

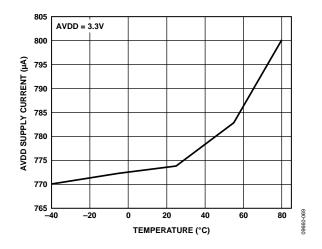

| POWER SUPPLY CURRENTS                            |             |          |                    |       | перристи у силения из и годината                                                                |

| AVDD Standby Current                             |             | 785      | 975                | μΑ    |                                                                                                 |

| IOVDD Standby Current                            |             | 1        | 60                 | μΑ    |                                                                                                 |

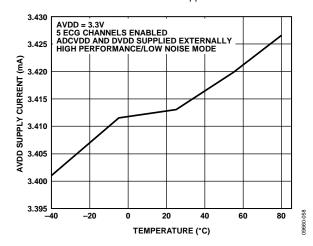

| EXTERNALLY SUPPLIED ADCVDD AND DVDD              |             | <u>.</u> |                    | pr'   | All 5 channels enabled, RLD enabled, pace enabled                                               |

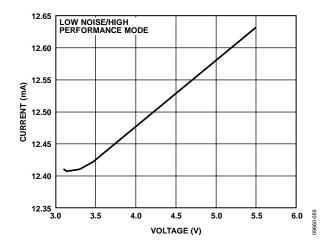

| AVDD Current                                     |             | 3.4      | 6.25               | mA    | High performance mode                                                                           |

| AVDD Current                                     |             | 3.1      | 5.3                | mA    | Low performance mode                                                                            |

|                                                  |             | 4.25     | 6.3                | mA    | High performance mode, respiration enabled                                                      |

| ADCVDD Current                                   |             | 6.2      | 9                  | mA    | High performance mode                                                                           |

| ADCVDD Cullent                                   |             | 4.7      | 6.5                | mA    | Low performance mode                                                                            |

|                                                  |             | 4.7<br>7 | 9                  | mA    | High performance mode, respiration enabled                                                      |

| DVDD Command                                     |             |          |                    |       | ,                                                                                               |

| DVDD Current                                     |             | 2.7      | 5                  | mA    | High performance mode                                                                           |

|                                                  |             | 1.4      | 3.5                | mA    | Low performance mode                                                                            |

| NTERNALLY SUPPLIED ADCVDD                        |             | 3.4      | 5.5                | mA    | High performance mode, respiration enabled  All 5 channels enabled, RLD enabled, pace enabled   |

| AND DVDD                                         |             |          |                    |       | 7.11.3 chamicis chabled, fieb chabled, pace chabled                                             |

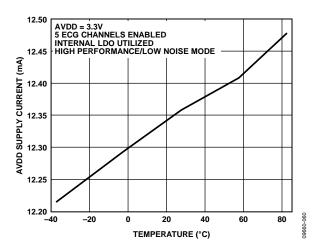

| AVDD Current                                     |             | 12.5     | 15.3               | mA    | High performance mode                                                                           |

|                                                  | 1           | 9.4      | 12.4               | mA    | Low performance mode                                                                            |

|                                                  |             | 14.8     | 17.3               | mA    | High performance mode, respiration enabled                                                      |

| POWER DISSIPATION                                |             |          |                    |       | All 5 channels enabled, RLD enabled, pace enabled                                               |

| Externally Supplied ADCVDD and DVDD <sup>3</sup> |             |          |                    |       |                                                                                                 |

| All 5 Input Channels and RLD                     | 1           | 27       |                    | mW    | High performance (low noise)                                                                    |

| ,                                                | 1           | 21       |                    | mW    | Low power mode                                                                                  |

| Internally Supplied ADCVDD and DVDD              |             |          |                    |       | All 5 channels enabled, RLD enabled, pace enabled                                               |

| All 5 Input Channels and RLD                     |             | 41       |                    | mW    | High performance (low noise)                                                                    |

|                                                  |             | 31       |                    | mW    | Low power mode                                                                                  |

# **Data Sheet**

| Parameter                    | Min | Тур | Max | Unit | Test Conditions/Comments |

|------------------------------|-----|-----|-----|------|--------------------------|

| OTHER FUNCTIONS <sup>4</sup> |     |     |     |      |                          |

| Power Dissipation            |     |     |     |      |                          |

| Respiration                  |     | 7.6 |     | mW   |                          |

| Shield Driver                |     | 150 |     | μW   |                          |

Guaranteed by characterization, not production tested.

Guaranteed by design, not production tested.

ADCVDD and DVDD can be powered from an internal LDO or, alternatively, can be powered from external 1.8 V rail, which may result in a lower power solution.

Pace is a digital function and incurs no power penalty.

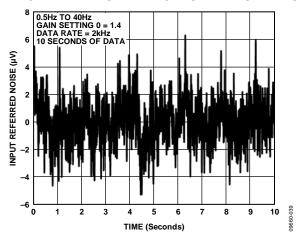

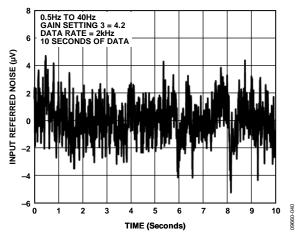

### **NOISE PERFORMANCE**

Table 3. Typical Input Referred Noise over 0.5 Second Window (μV p-p)<sup>1</sup>

| Mode                          | Data Rate <sup>2</sup>    | GAIN 0 (×1.4)<br>±1 VCM | GAIN 1 (×2.1)<br>±0.67 VCM | GAIN 2 (×2.8)<br>±0.5 VCM | GAIN 3 (×4.2)<br>±0.3 VCM |

|-------------------------------|---------------------------|-------------------------|----------------------------|---------------------------|---------------------------|

| Analog Lead Mode <sup>3</sup> |                           |                         |                            |                           |                           |

| High Performance Mode         | 2 kHz (0.5 Hz to 40 Hz)   | 8                       | 6                          | 5                         | 4                         |

|                               | 2 kHz (0.05 Hz to 150 Hz) | 14                      | 11                         | 9                         | 7.5                       |

<sup>&</sup>lt;sup>1</sup> Typical values measured at 25°C, not subject to production test.

Table 4. Typical Input Referred Noise (μV p-p)<sup>1</sup>

|                                   |                           | GAIN 0 (×1.4)<br>±1 VCM | GAIN 1 (×2.1)<br>±0.67 VCM | GAIN 2 (×2.8)<br>±0.5 VCM | GAIN 3 (×4.2)<br>±0.3 VCM |

|-----------------------------------|---------------------------|-------------------------|----------------------------|---------------------------|---------------------------|

| Analog Lead Mode <sup>3</sup>     |                           |                         | _0.07 0 0                  |                           |                           |

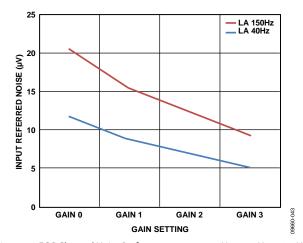

| High Performance Mode             | 2 kHz (0.5 Hz to 40 Hz)   | 12                      | 8.5                        | 6                         | 5                         |

| <b>3</b>                          | 2 kHz (0.05 Hz to 150 Hz) | 20                      | 14.5                       | 10                        | 8.5                       |

|                                   | 2 kHz (0.05 Hz to 250 Hz) | 27                      | 18                         | 14.5                      | 10.5                      |

|                                   | 2 kHz (0.05 Hz to 450 Hz) | 33.5                    | 24                         | 19                        | 13.5                      |

|                                   | 16 kHz                    | 95                      | 65                         | 50                        | 39                        |

|                                   | 128 kHz                   | 180                     | 130                        | 105                       | 80                        |

| Low Power Mode                    | 2 kHz (0.5 Hz to 40 Hz)   | 13                      | 9.5                        | 7.5                       | 5.5                       |

|                                   | 2 kHz (0.05 Hz to 150 Hz) | 22                      | 15.5                       | 12                        | 9                         |

|                                   | 16 kHz                    | 110                     | 75                         | 59                        | 45                        |

|                                   | 128 kHz                   | 215                     | 145                        | 116                       | 85                        |

| Electrode Mode <sup>4</sup>       |                           |                         |                            |                           |                           |

| High Performance Mode             | 2 kHz (0.5 Hz to 40 Hz)   | 13                      | 9.5                        | 8                         | 5.5                       |

| -                                 | 2 kHz (0.05 Hz to 150 Hz) | 21                      | 15                         | 11                        | 9                         |

|                                   | 2 kHz (0.05 Hz to 250 Hz) | 26                      | 19                         | 15.5                      | 11.5                      |

|                                   | 2 kHz (0.05 Hz to 450 Hz) | 34.5                    | 25                         | 20.5                      | 14.5                      |

|                                   | 16 kHz                    | 100                     | 70                         | 57                        | 41                        |

|                                   | 128 kHz                   | 190                     | 139                        | 110                       | 85                        |

| Low Power Mode                    | 2 kHz (0.5 Hz to 40 Hz)   | 14                      | 9.5                        | 7.5                       | 5.5                       |

|                                   | 2 kHz (0.05 Hz to 150 Hz) | 22                      | 15.5                       | 12                        | 9.5                       |

|                                   | 16 kHz                    | 110                     | 75                         | 60                        | 45                        |

|                                   | 128 kHz                   | 218                     | 145                        | 120                       | 88                        |

| Digital Lead Mode <sup>5, 6</sup> |                           |                         |                            |                           |                           |

| High Performance Mode             | 2 kHz (0.5 Hz to 40 Hz)   | 16                      | 11                         | 9                         | 6.5                       |

|                                   | 2 kHz (0.05 Hz to 150 Hz) | 25                      | 19                         | 15                        | 10                        |

|                                   | 2 kHz (0.05 Hz to 250 Hz) | 34                      | 23                         | 18                        | 13                        |

|                                   | 2 kHz (0.05 Hz to 450 Hz) | 46                      | 31                         | 24                        | 17.5                      |

|                                   | 16 kHz                    | 130                     | 90                         | 70                        | 50                        |

| Low Power Mode                    | 2 kHz (0.5 Hz to 40 Hz)   | 18                      | 12.5                       | 10                        | 7                         |

|                                   | 2 kHz (0.05 Hz to 150 Hz) | 30                      | 21                         | 16                        | 11                        |

|                                   | 16 kHz                    | 145                     | 100                        | 80                        | 58                        |

<sup>&</sup>lt;sup>1</sup> Typical values measured at 25°C, not subject to production test.

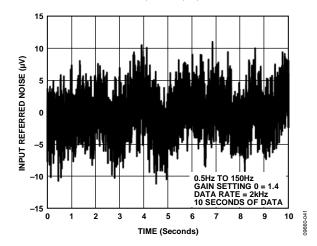

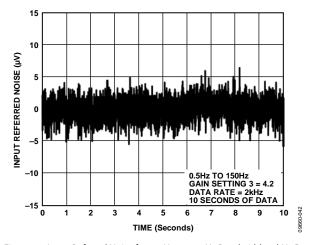

<sup>&</sup>lt;sup>2</sup> Data gathered using the 2 kHz packet/frame rate is measured over 0.5 seconds. The ADAS1000 internal programmable low-pass filter is configured for either 40 Hz or 150 Hz bandwidth. The data is gathered and post processed using a digital filter of either 0.05 Hz or 0.5 Hz to provide data over noted frequency bands.

<sup>&</sup>lt;sup>3</sup> Analog lead mode as shown in Figure 58.

<sup>&</sup>lt;sup>2</sup> Data gathered using the 2 kHz packet/frame rate is measured over 20 seconds. The ADAS1000 internal programmable low-pass filter is configured for either 40 Hz or 150 Hz bandwidth. The data is gathered and post processed using a digital filter of either 0.05 Hz or 0.5 Hz to provide data over noted frequency bands.

<sup>&</sup>lt;sup>3</sup> Analog lead mode as shown in Figure 58.

<sup>&</sup>lt;sup>4</sup> Single-ended input electrode mode as shown in Figure 61. Electrode mode refers to common electrode A, common electrode B, and single-ended input electrode configurations. See Electrode/Lead Formation and Input Stage Configuration section.

<sup>&</sup>lt;sup>5</sup> Digital lead mode as shown in Figure 59.

<sup>&</sup>lt;sup>6</sup> Digital lead mode is available in 2 kHz and 16 kHz data rates.

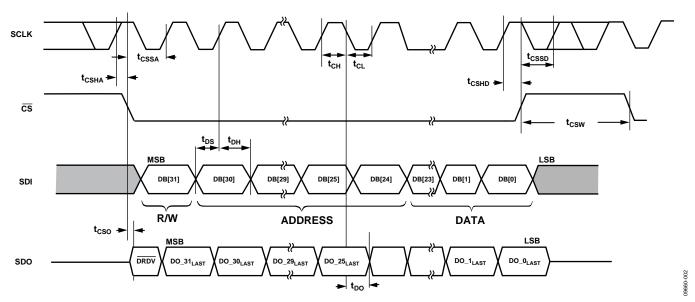

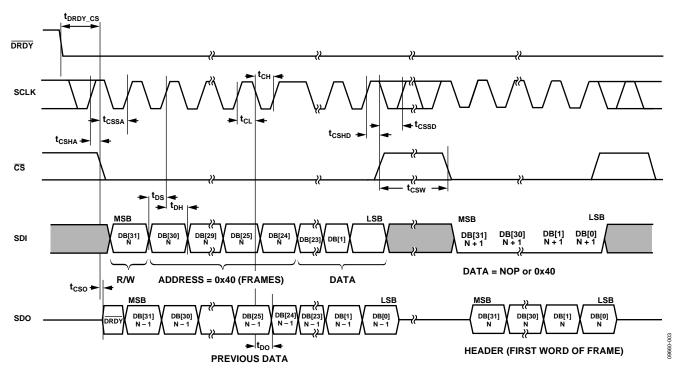

### **TIMING CHARACTERISTICS**

### Standard Serial Interface

AVDD = 3.3 V  $\pm$  5%, IOVDD = 1.65 V to 3.6 V, AGND = DGND = 0 V, REFIN tied to REFOUT, externally supplied crystal/clock = 8.192 MHz.  $T_A = -40^{\circ}$ C to +85°C, unless otherwise noted. Typical specifications are mean values at  $T_A = 25^{\circ}$ C.

Table 5.

|                                   |       | IOVDD |       |        |                                                                                                                                                                                            |

|-----------------------------------|-------|-------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter <sup>1</sup>            | 3.3 V | 2.5 V | 1.8 V | Unit   | Description                                                                                                                                                                                |

| Output Rate <sup>2</sup>          | 2     |       | 128   | kHz    | Across specified IOVDD supply range; three programmable output data rates available as configured in FRMCTL register (see Table 37) 2 kHz, 16 kHz, 128 kHz; use skip mode for slower rates |

| SCLK Cycle Time                   | 25    | 40    | 50    | ns min | See Table 21 for details on SCLK vs. packet data rates                                                                                                                                     |

| tcssa                             | 8.5   | 9.5   | 12    | ns min | CS valid setup time to rising SCLK                                                                                                                                                         |

| t <sub>CSHA</sub>                 | 3     | 3     | 3     | ns min | CS valid hold time to rising SCLK                                                                                                                                                          |

| $t_{CH}$                          | 8     | 8     | 8     | ns min | SCLK high time                                                                                                                                                                             |

| t <sub>CL</sub>                   | 8     | 8     | 8     | ns min | SCLK low time                                                                                                                                                                              |

| $t_{DO}$                          | 8.5   | 11.5  | 20    | ns typ | SCLK falling edge to SDO valid delay; SDO capacitance of 15 pF                                                                                                                             |

|                                   | 11    | 19    | 24    | ns max |                                                                                                                                                                                            |

| $t_{\text{DS}}$                   | 2     | 2     | 2     | ns min | SDI valid setup time from SCLK rising edge                                                                                                                                                 |

| $t_{DH}$                          | 2     | 2     | 2     | ns min | SDI valid hold time from SCLK rising edge                                                                                                                                                  |

| t <sub>CSSD</sub>                 | 2     | 2     | 2     | ns min | CS valid setup time from SCLK rising edge                                                                                                                                                  |

| $t_{\text{CSHD}}$                 | 2     | 2     | 2     | ns min | CS valid hold time from SCLK rising edge                                                                                                                                                   |

| t <sub>csw</sub>                  | 25    | 40    | 50    | ns min | CS high time between writes (if used). Note that CS is an optional input, it may be tied permanently low. See a full description in the Serial Interfaces section.                         |

| t <sub>DRDY_CS</sub> <sup>2</sup> | 0     | 0     | 0     | ns min | DRDY to CS setup time                                                                                                                                                                      |

| tcso                              | 6     | 7     | 9     | ns typ | Delay from CS assert to SDO active                                                                                                                                                         |

| RESET Low Time <sup>2</sup>       | 20    | 20    | 20    | ns min | Minimum pulse width; RESET is edge triggered                                                                                                                                               |

$<sup>^{\</sup>rm 1}$  Guaranteed by characterization, not production tested.

<sup>&</sup>lt;sup>2</sup> Guaranteed by design, not production tested.

Figure 2. Data Read and Write Timing Diagram (CPHA = 1, CPOL = 1)

Figure 3. Starting Read Frame Data (CPHA = 1, CPOL = 1)

Figure 4. Data Read and Write Timing Diagram (CPHA = 0, CPOL = 0)

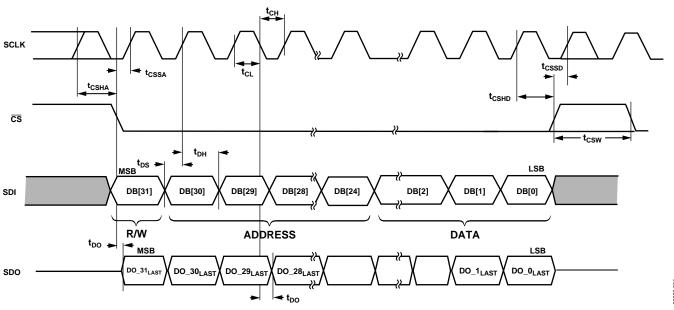

### Secondary Serial Interface (Master Interface for Customer-Based Digital Pace Algorithm) ADAS1000/ADAS1000-1 Only

AVDD = 3.3 V  $\pm$  5%, IOVDD = 1.65 V to 3.6 V, AGND = DGND = 0 V, REFIN tied to REFOUT, externally supplied crystal/clock = 8.192 MHz.  $T_A = -40$ °C to +85°C, unless otherwise noted. Typical specifications are mean values at  $T_A = 25$ °C. The following timing specifications apply for the master interface when ECGCTL register is configured for high performance mode (ECGCTL[3] = 1), see Table 28.

Table 6.

| Parameter <sup>1</sup>         | Min Typ                 | Max | Unit | Description                                                                                         |

|--------------------------------|-------------------------|-----|------|-----------------------------------------------------------------------------------------------------|

| Output Frame Rate <sup>2</sup> | 128                     |     | kHz  | All five 16-bit ECG data-words are available at frame rate of 128 kHz only                          |

| f <sub>SCLK</sub> <sup>2</sup> | 2.5 × crystal frequency |     | MHz  | Crystal frequency = 8.192 MHz                                                                       |

| t <sub>MCSSA</sub>             | 24.4                    |     | ns   | MCS valid setup time                                                                                |

| $t_{MDO}$                      | 0                       |     | ns   | MSCLK rising edge to MSDO valid delay                                                               |

| <b>t</b> <sub>MCSHD</sub>      | 48.8                    |     | ns   | MCS valid hold time from MSCLK falling edge                                                         |

| t <sub>MCSW</sub>              | 2173                    |     | ns   | $\overline{MCS}$ high time, SPIFW = 0, $\overline{MCS}$ asserted for entire frame as shown in       |

|                                |                         |     |      | Figure 5, and configured in Table 33                                                                |

|                                | 2026                    |     | ns   | $\overline{MCS}$ high time, SPIFW = 1, $\overline{MCS}$ asserted for each word in frame as shown in |

|                                |                         |     |      | Figure 6 and configured in Table 33                                                                 |

<sup>&</sup>lt;sup>1</sup> Guaranteed by characterization, not production tested.

<sup>&</sup>lt;sup>2</sup> Guaranteed by design, not production tested.

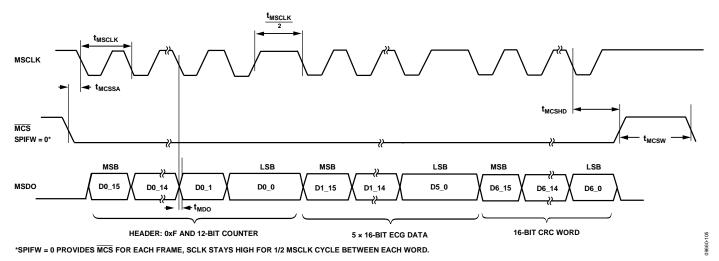

Figure 5. Data Read and Write Timing Diagram for SPIFW = 0, Showing Entire Packet of Data (Header, 5 ECG Words, and CRC Word)

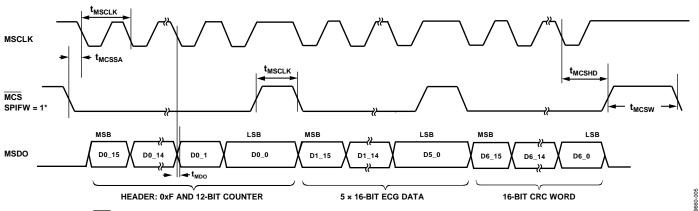

\*SPIFW = 1 PROVIDES  $\overline{MCS}$  FOR EACH FRAME, SCLK STAYS HIGH FOR 1 MSCLK CYCLE BETWEEN EACH WORD.

Figure 6. Data Read and Write Timing Diagram for SPIFW = 1, Showing Entire Packet of Data (Header, 5 ECG Words, and CRC Word)

### **ABSOLUTE MAXIMUM RATINGS**

Table 7.

| Tubic /:                             |                         |

|--------------------------------------|-------------------------|

| Parameter                            | Rating                  |

| AVDD to AGND                         | -0.3 V to +6 V          |

| IOVDD to DGND                        | −0.3 V to +6 V          |

| ADCVDD to AGND                       | -0.3 V to +2.5 V        |

| DVDD to DGND                         | -0.3 V to +2.5 V        |

| REFIN/REFOUT to REFGND               | -0.3 V to +2.1 V        |

| ECG and Analog Inputs to AGND        | -0.3 V to AVDD + 0.3 V  |

| Digital Inputs to DGND               | -0.3 V to IOVDD + 0.3 V |

| REFIN to ADCVDD                      | ADCVDD + 0.3 V          |

| AGND to DGND                         | -0.3 V to + 0.3 V       |

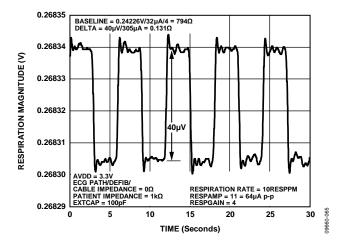

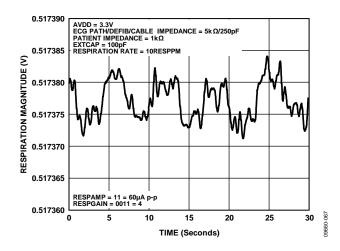

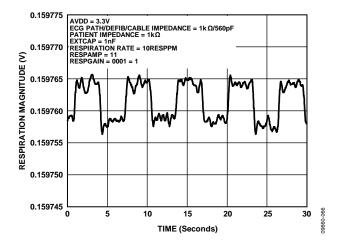

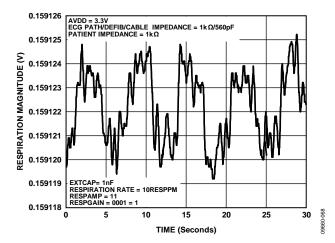

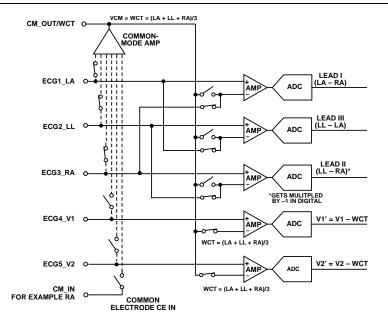

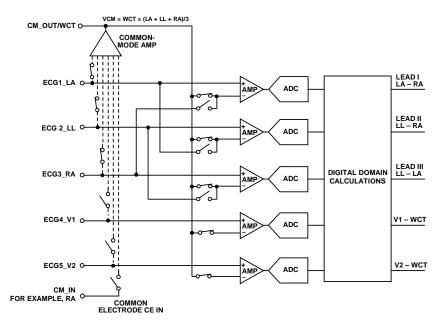

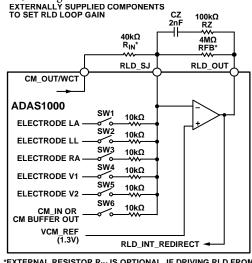

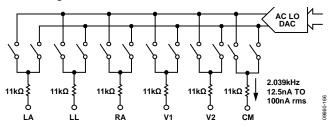

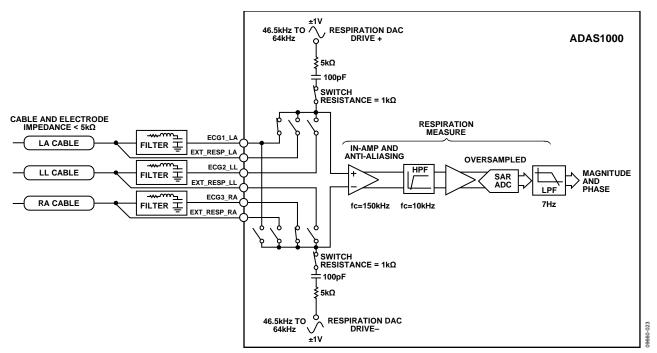

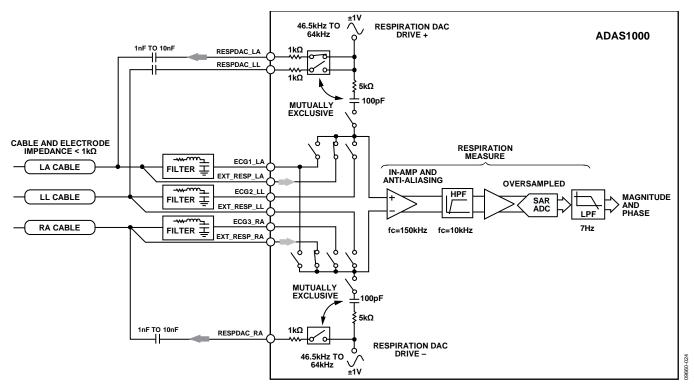

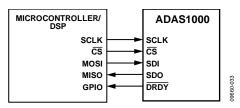

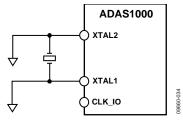

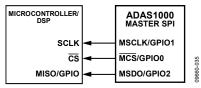

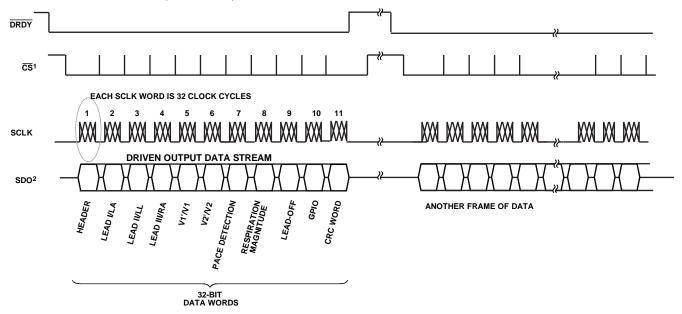

| REFGND to AGND                       | -0.3 V to + 0.3 V       |