Data Sheet

# **AD835**

# **TABLE OF CONTENTS**

| Features                                                 |

|----------------------------------------------------------|

| Applications1                                            |

| General Description1                                     |

| Functional Block Diagram1                                |

| Product Highlights1                                      |

| Revision History                                         |

| Specifications                                           |

| Absolute Maximum Ratings                                 |

| Thermal Resistance                                       |

| ESD Caution5                                             |

| Pin Configuration and Function Descriptions6             |

| REVISION HISTORY                                         |

| 12/14—Rev. D to Rev. E                                   |

| Changes to Figure 1                                      |

| Changes to Figure 20                                     |

| Changes to Wideband Voltage-Controlled Amplifier Section |

| and Figure 2111                                          |

| Changes to Ordering Guide                                |

| 12/10—Rev. C to Rev. D                                   |

| Changes to Figure 11                                     |

| Changes to Absolute Maximum Ratings and Table 25         |

| Added Figure 19, Renumbered Subsequent Tables10          |

| Added Figure 2311                                        |

| 10/09—Rev. B to Rev. C                                   |

| Updated FormatUniversal                                  |

| Changes to Figure 2211                                   |

| Updated Outline Dimensions                               |

| Changes to Ordering Guide14                              |

| 6/03—Rev. A to Rev. B                                    |

| Undated Formet Universal                                 |

| Typical Performance Characteristics   |    |

|---------------------------------------|----|

| Theory of Operation                   | 10 |

| Basic Theory                          | 10 |

| Scaling Adjustment                    | 10 |

| Applications Information              | 11 |

| Multiplier Connections                | 11 |

| Wideband Voltage-Controlled Amplifier | 11 |

| Amplitude Modulator                   | 11 |

| Squaring and Frequency Doubling       | 12 |

| Outline Dimensions                    | 13 |

| Ordering Guide                        | 14 |

# **SPECIFICATIONS**

$T_{\text{A}}$  = 25°C,  $V_{\text{S}}$  = ±5 V,  $R_{\text{L}}$  = 150  $\Omega,\,C_{\text{L}}$   $\leq$  5 pF, unless otherwise noted.

Table 1.

| Parameter                       | Conditions                                        | Min                          | Тур           | Max              | Unit    |

|---------------------------------|---------------------------------------------------|------------------------------|---------------|------------------|---------|

| TRANSFER FUNCTION               |                                                   | $W = \frac{(\Sigma X)^2}{2}$ | (X1 - X2)(Y1) | (-Y2)            |         |

|                                 |                                                   |                              | U             |                  |         |

| INPUT CHARACTERISTICS (X, Y)    | ., .,                                             |                              |               |                  | ,,      |

| Differential Voltage Range      | $V_{CM} = 0 V$                                    | 1                            | ±1            |                  | V       |

| Differential Clipping Level     |                                                   | ±1.21                        | ±1.4          | a =1             | V       |

| Low Frequency Nonlinearity      | $X = \pm 1 \text{ V}, Y = 1 \text{ V}$            |                              | 0.3           | 0.5 <sup>1</sup> | % FS    |

|                                 | $Y = \pm 1 V, X = 1 V$                            |                              | 0.1           | 0.3 <sup>1</sup> | % FS    |

| vs. Temperature                 | T <sub>MIN</sub> to T <sub>MAX</sub> <sup>2</sup> |                              |               |                  |         |

|                                 | $X = \pm 1 \text{ V}, Y = 1 \text{ V}$            |                              |               | 0.7              | % FS    |

|                                 | $Y = \pm 1 \text{ V}, X = 1 \text{ V}$            |                              |               | 0.5              | % FS    |

| Common-Mode Voltage Range       |                                                   | -2.5                         |               | +3               | V       |

| Offset Voltage                  |                                                   |                              | ±3            | ±20 <sup>1</sup> | mV      |

| vs. Temperature                 | $T_{MIN}$ to $T_{MAX}^2$                          |                              |               | ±25              | mV      |

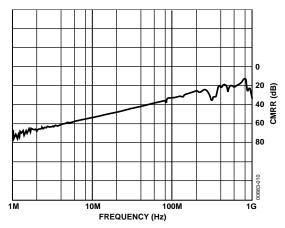

| CMRR                            | $f \le 100 \text{ kHz; } \pm 1 \text{ V p-p}$     | 70 <sup>1</sup>              |               |                  | dB      |

| Bias Current                    |                                                   |                              | 10            | 20 <sup>1</sup>  | μΑ      |

| vs. Temperature                 | T <sub>MIN</sub> to T <sub>MAX</sub> <sup>2</sup> |                              |               | 27               | μΑ      |

| Offset Bias Current             |                                                   |                              | 2             |                  | μΑ      |

| Differential Resistance         |                                                   |                              | 100           |                  | kΩ      |

| Single-Sided Capacitance        |                                                   |                              | 2             |                  | pF      |

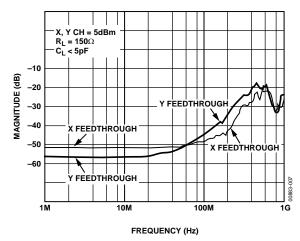

| Feedthrough, X                  | $X = \pm 1 \text{ V}, Y = 0 \text{ V}$            |                              |               | $-46^{1}$        | dB      |

| Feedthrough, Y                  | $Y = \pm 1 \text{ V}, X = 0 \text{ V}$            |                              |               | $-60^{1}$        | dB      |

| DYNAMIC CHARACTERISTICS         |                                                   |                              |               |                  |         |

| –3 dB Small Signal Bandwidth    |                                                   | 150                          | 250           |                  | MHz     |

| –0.1 dB Gain Flatness Frequency |                                                   |                              | 15            |                  | MHz     |

| Slew Rate                       | W = -2.5 V  to  +2.5 V                            |                              | 1000          |                  | V/µs    |

| Differential Gain Error, X      | f = 3.58 MHz                                      |                              | 0.3           |                  | %       |

| Differential Phase Error, X     | f = 3.58 MHz                                      |                              | 0.2           |                  | Degrees |

| Differential Gain Error, Y      | f = 3.58 MHz                                      |                              | 0.1           |                  | %       |

| Differential Phase Error, Y     | f = 3.58 MHz                                      |                              | 0.1           |                  | Degrees |

| Harmonic Distortion             | X or $Y = 10$ dBm, second and third harmonic      |                              |               |                  |         |

|                                 | Fund = 10 MHz                                     |                              | -70           |                  | dB      |

|                                 | Fund = 50 MHz                                     |                              | -40           |                  | dB      |

| Settling Time, X or Y           | To 0.1%, W = 2 V p-p                              |                              | 20            |                  | ns      |

| SUMMING INPUT (Z)               | · ·                                               |                              |               |                  |         |

| Gain                            | From Z to W, f ≤ 10 MHz                           | 0.990                        | 0.995         |                  |         |

| –3 dB Small Signal Bandwidth    | ·                                                 |                              | 250           |                  | MHz     |

| Differential Input Resistance   |                                                   |                              | 60            |                  | kΩ      |

| Single-Sided Capacitance        |                                                   |                              | 2             |                  | pF      |

| Maximum Gain                    | X, Y  to  W, Z  shorted to  W, f = 1  kHz         |                              | 50            |                  | dB      |

| Bias Current                    | ., ,                                              |                              | 50            |                  | μA      |

| Parameter                      | Conditions                                        | Min  | Тур  | Max              | Unit   |

|--------------------------------|---------------------------------------------------|------|------|------------------|--------|

| OUTPUT CHARACTERISTICS         |                                                   |      |      |                  |        |

| Voltage Swing                  |                                                   | ±2.2 | ±2.5 |                  | V      |

| vs. Temperature                | T <sub>MIN</sub> to T <sub>MAX</sub> <sup>2</sup> | ±2.0 |      |                  | V      |

| Voltage Noise Spectral Density | X = Y = 0 V, f < 10 MHz                           |      | 50   |                  | nV/√H: |

| Offset Voltage                 |                                                   |      | ±25  | ±75 <sup>1</sup> | mV     |

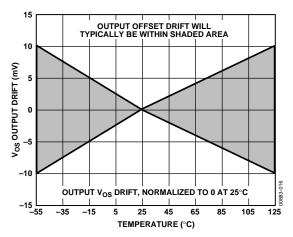

| vs. Temperature <sup>3</sup>   | T <sub>MIN</sub> to T <sub>MAX</sub> <sup>2</sup> |      |      | ±10              | mV     |

| Short-Circuit Current          |                                                   |      | 75   |                  | mA     |

| Scale Factor Error             |                                                   |      | ±5   | ±81              | % FS   |

| vs. Temperature                | T <sub>MIN</sub> to T <sub>MAX</sub> <sup>2</sup> |      |      | ±9               | % FS   |

| Linearity (Relative Error)⁴    |                                                   |      | ±0.5 | ±1.01            | % FS   |

| vs. Temperature                | T <sub>MIN</sub> to T <sub>MAX</sub> <sup>2</sup> |      |      | ±1.25            | % FS   |

| POWER SUPPLIES                 |                                                   |      |      |                  |        |

| Supply Voltage                 |                                                   |      |      |                  |        |

| For Specified Performance      |                                                   | ±4.5 | ±5   | ±5.5             | V      |

| Quiescent Supply Current       |                                                   |      | 16   | 25 <sup>1</sup>  | mA     |

| vs. Temperature                | T <sub>MIN</sub> to T <sub>MAX</sub> <sup>2</sup> |      |      | 26               | mA     |

| PSRR at Output vs. VP          | +4.5 V to +5.5 V                                  |      |      | 0.5 <sup>1</sup> | %/V    |

| PSRR at Output vs. VN          | −4.5 V to −5.5 V                                  |      |      | 0.5              | %/V    |

<sup>&</sup>lt;sup>1</sup> All minimum and maximum specifications are guaranteed. These specifications are tested on all production units at final electrical test.

<sup>&</sup>lt;sup>2</sup> T<sub>MIN</sub> = -40°C, T<sub>MAX</sub> = 85°C.

<sup>3</sup> Normalized to zero at 25°C.

<sup>4</sup> Linearity is defined as residual error after compensating for input offset, output voltage offset, and scale factor errors.

## **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                          | Rating          |

|------------------------------------|-----------------|

| Supply Voltage                     | ±6 V            |

| Internal Power Dissipation         | 300 mW          |

| Operating Temperature Range        | −40°C to +85°C  |

| Storage Temperature Range          | −65°C to +150°C |

| Lead Temperature, Soldering 60 sec | 300°C           |

| ESD Rating                         |                 |

| НВМ                                | 1500 V          |

| CDM                                | 250 V           |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

For more information, see the Analog Devices, Inc., Tutorial MT-092, *Electrostatic Discharge*.

### THERMAL RESISTANCE

Table 3.

| Package Type    | θ <sub>JA</sub> | θις | Unit |

|-----------------|-----------------|-----|------|

| 8-Lead PDIP (N) | 90              | 35  | °C/W |

| 8-Lead SOIC (R) | 115             | 45  | °C/W |

### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                       |

|---------|----------|-----------------------------------|

| 1       | Y1       | Noninverting Y Multiplicand Input |

| 2       | Y2       | Inverting Y Multiplicand Input    |

| 3       | VN       | Negative Supply Voltage           |

| 4       | Z        | Summing Input                     |

| 5       | W        | Product                           |

| 6       | VP       | Positive Supply Voltage           |

| 7       | X2       | Inverting X Multiplicand Input    |

| 8       | X1       | Noninverting X Multiplicand Input |

## TYPICAL PERFORMANCE CHARACTERISTICS

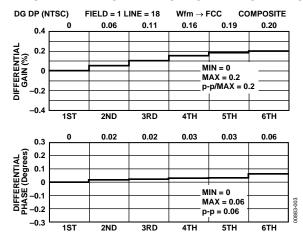

Figure 3. Typical Composite Output Differential Gain and Phase, NTSC for X Channel; f = 3.58 MHz,  $R_L = 150$   $\Omega$

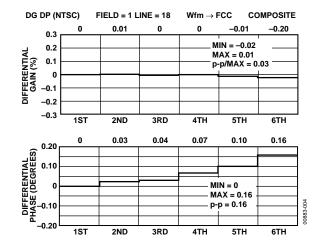

Figure 4. Typical Composite Output Differential Gain and Phase, NTSC for Y Channel; f = 3.58 MHz,  $R_L = 150 \Omega$

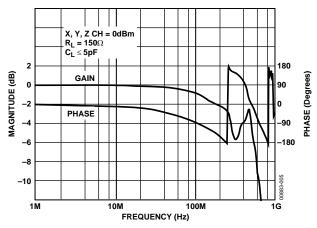

Figure 5. Gain and Phase vs. Frequency of X, Y, Z Inputs

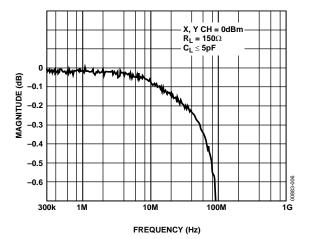

Figure 6. Gain Flatness to 0.1 dB

Figure 7. X and Y Feedthrough vs. Frequency

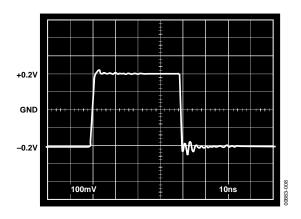

Figure 8. Small Signal Pulse Response at W Output,  $R_L = 150 \Omega$ ,  $C_L \le 5 pF$ , X Channel =  $\pm 0.2 V$ , Y Channel =  $\pm 1.0 V$

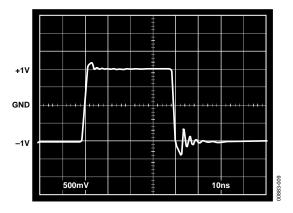

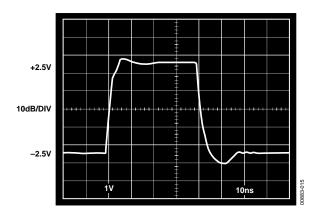

Figure 9. Large Signal Pulse Response at W Output,  $R_L = 150 \Omega$ ,  $C_L \le 5$  pF, X Channel =  $\pm 1.0$  V, Y Channel =  $\pm 1.0$  V

Figure 10. CMRR vs. Frequency for X or Y Channel,  $R_L = 150 \Omega$ ,  $C_L \le 5 pF$

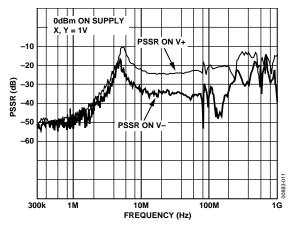

Figure 11. PSRR vs. Frequency for V+ and V- Supply

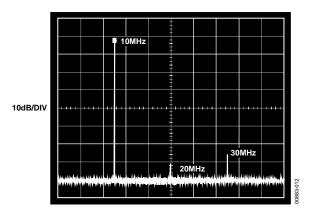

Figure 12. Harmonic Distortion at 10 MHz; 10 dBm Input to X or Y Channels,  $R_L=150~\Omega,~C_L\leq 5~pF$

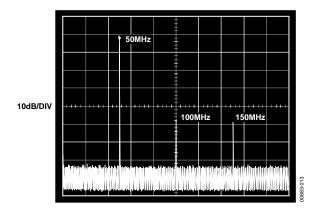

Figure 13. Harmonic Distortion at 50 MHz, 10 dBm Input to X or Y Channel,  $R_L=150~\Omega,~C_L\leq 5~pF$

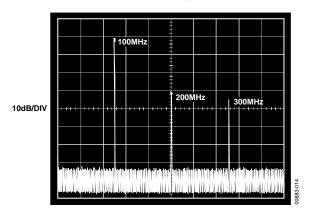

Figure 14. Harmonic Distortion at 100 MHz, 10 dBm Input to X or Y Channel,  $R_L=150~\Omega,~C_L\leq 5~pF$

Figure 15. Maximum Output Voltage Swing,  $R_L = 50 \Omega$ ,  $C_L \le 5 pF$

Figure 16. Vos Output Drift vs. Temperature

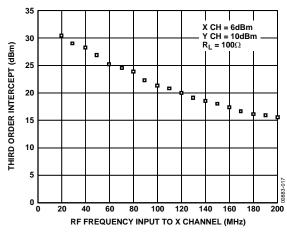

Figure 17. Fixed LO on Y Channel vs. RF Frequency Input to X Channel

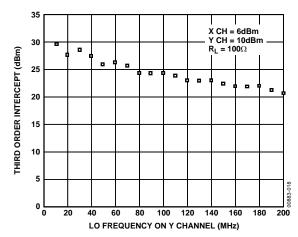

Figure 18. Fixed IF vs. LO Frequency on Y Channel

## THEORY OF OPERATION

The AD835 is a four-quadrant, voltage output analog multiplier, fabricated on an advanced dielectrically isolated complementary bipolar process. In its basic mode, it provides the linear product of its X and Y voltage inputs. In this mode, the -3 dB output voltage bandwidth is 250 MHz (with small signal rise time of 1 ns). Full-scale (-1 V to +1 V) rise to fall times are 2.5 ns (with a standard  $R_{\rm L}$  of 150  $\Omega$ ), and the settling time to 0.1% under the same conditions is typically 20 ns.

As in earlier multipliers from Analog Devices a unique summing feature is provided at the Z input. As well as providing independent ground references for the input and the output and enhanced versatility, this feature allows the AD835 to operate with voltage gain. Its X-, Y-, and Z-input voltages are all nominally  $\pm 1$  V FS, with an overrange of at least 20%. The inputs are fully differential at high impedance (100 k $\Omega$ ||2 pF) and provide a 70 dB CMRR (f  $\leq 1$  MHz).

The low impedance output is capable of driving loads as small as 25  $\Omega$ . The peak output can be as large as  $\pm 2.2$  V minimum for  $R_L = 150~\Omega$ , or  $\pm 2.0$  V minimum into  $R_L = 50~\Omega$ . The AD835 has much lower noise than the AD534 or AD734, making it attractive in low level, signal processing applications, for example, as a wideband gain control element or modulator.

#### **BASIC THEORY**

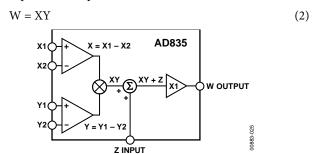

The multiplier is based on a classic form, having a translinear core, supported by three (X, Y, and Z) linearized voltage-to-current converters, and the load driving output amplifier. The scaling voltage (the denominator U in the equations) is provided by a band gap reference of novel design, optimized for ultralow noise. Figure 19 shows the functional block diagram.

In general terms, the AD835 provides the function

$$W = \frac{(X1 - X2)(Y1 - Y2)}{U} + Z \tag{1}$$

where the variables W, U, X, Y, and Z are all voltages. Connected as a simple multiplier, with X = X1 - X2, Y = Y1 - Y2, and Z = 0 and with a scale factor adjustment (see Figure 19) that sets U = 1 V, the output can be expressed as

Figure 19. Functional Block Diagram

Simplified representations of this sort, where all signals are presumed expressed in V, are used throughout this data sheet to

avoid the needless use of less intuitive subscripted variables (such as,  $V_{x_1}$ ). All variables as being normalized to 1 V.

For example, the input X can either be stated as being in the -1 V to +1 V range or simply -1 to +1. The latter representation is found to facilitate the development of new functions using the AD835. The explicit inclusion of the denominator, U, is also less helpful, as in the case of the AD835, if it is not an electrical input variable.

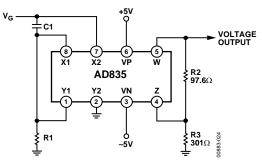

#### **SCALING ADJUSTMENT**

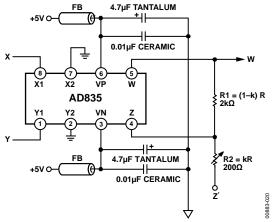

The basic value of U in Equation 1 is nominally 1.05 V. Figure 20, which shows the basic multiplier connections, also shows how the effective value of U can be adjusted to have any lower voltage (usually 1 V) through the use of a resistive divider between W (Pin 5) and Z (Pin 4). Using the general resistor values shown, Equation 1can be rewritten as

$$W = \frac{XY}{U} + kW + (1 - k)Z' \tag{3}$$

where Z is distinguished from the signal Z at Pin 4. It follows that

$$W = \frac{XY}{(1-k)U} + Z' \tag{4}$$

In this way, the effective value of U can be modified to

$$U' = (1 - k)U \tag{5}$$

without altering the scaling of the Z' input, which is expected because the only ground reference for the output is through the Z' input.

Therefore, to set U' to 1 V, remembering that the basic value of U is 1.05 V, R1 must have a nominal value of  $20 \times R2$ . The values shown allow U to be adjusted through the nominal range of 0.95 V to 1.05 V. That is, R2 provides a 5% gain adjustment.

In many applications, the exact gain of the multiplier may not be very important; in which case, this network may be omitted entirely, or R2 fixed at 100  $\Omega$ .

Figure 20. Multiplier Connections

## APPLICATIONS INFORMATION

The AD835 is easy to use and versatile. The capability for adding another signal to the output at the Z input is frequently valuable. Three applications of this feature are presented here: a wideband voltage-controlled amplifier, an amplitude modulator, and a frequency doubler. Of course, the AD835 may also be used as a square law detector (with its X inputs and Y inputs connected in parallel). In this mode, it is useful at input frequencies to well over 250 MHz because that is the bandwidth limitation of the output amplifier only.

#### **MULTIPLIER CONNECTIONS**

Figure 20 shows the basic connections for multiplication. The inputs are often single sided, in which case the X2 and Y2 inputs are normally grounded. Note that by assigning Pin 7 (X2) and Pin 2 (Y2), respectively, to these (inverting) inputs, an extra measure of isolation between inputs and output is provided. The X and Y inputs may be reversed to achieve some desired overall sign with inputs of a particular polarity, or they may be driven fully differentially.

Power supply decoupling and careful board layout are always important in applying wideband circuits. The decoupling recommendations shown in Figure 20 should be followed closely. In Figure 21, Figure 23, and Figure 24, these power supply decoupling components are omitted for clarity but should be used wherever optimal performance with high speed inputs is required. However, if the full, high frequency capabilities of the AD835 are not being exploited, these components can be omitted.

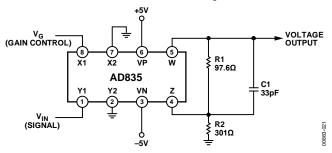

#### WIDEBAND VOLTAGE-CONTROLLED AMPLIFIER

Figure 21 shows the AD835 configured to provide a gain of nominally 0 dB to 12 dB. (In fact, the control range extends from well under -12 dB to about +14 dB.) R1 and R2 set the gain to be nominally  $\times 4$ . The attendant bandwidth reduction that comes with this increased gain is partially offset by the addition of the peaking capacitor C1. Although this circuit shows the use of dual supplies, the AD835 can operate from a single 9 V supply (such as a 9 V battery) with a slight revision. For G = 0 dB, omit R1 and R2, and connect Pin Z directly to ground. Pin Z must be connected to a reference; otherwise, the output W floats to a rail.

Figure 21. Voltage-Controlled 50 MHz Amplifier Using the AD835

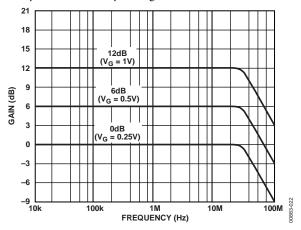

The ac response of this amplifier for gains of 0 dB ( $V_G = 0.25 \text{ V}$ ), 6 dB ( $V_G = 0.5 \text{ V}$ ), and 12 dB ( $V_G = 1 \text{ V}$ ) is shown in Figure 22. In this application, the resistor values have been slightly adjusted to reflect the nominal value of U = 1.05 V. The overall sign of the gain may be controlled by the sign of  $V_G$ .

Figure 22. AC Response of VCA

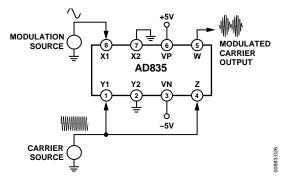

#### **AMPLITUDE MODULATOR**

Figure 23 shows a simple modulator. The carrier is applied to the Y input and the Z input, while the modulating signal is applied to the X input. For zero modulation, there is no product term so the carrier input is simply replicated at unity gain by the voltage follower action from the Z input. At X=1 V, the RF output is doubled, while for X=-1 V, it is fully suppressed. That is, an X input of approximately  $\pm 1$  V (actually  $\pm U$  or about 1.05 V) corresponds to a modulation index of 100%. Carrier and modulation frequencies can be up to 300 MHz, somewhat beyond the nominal -3 dB bandwidth.

Of course, a suppressed carrier modulator can be implemented by omitting the feedforward to the Z input, grounding that pin instead.

Figure 23. Simple Amplitude Modulator Using the AD835

#### **SQUARING AND FREQUENCY DOUBLING**

Amplitude domain squaring of an input signal, E, is achieved simply by connecting the X and Y inputs in parallel to produce an output of  $\rm E^2/U$ . The input can have either polarity, but the output in this case is always positive. The output polarity can be reversed by interchanging either the X or Y inputs.

When the input is a sine wave  $E \sin \omega t$ , a signal squarer behaves as a frequency doubler because

$$\frac{(E\sin\omega t)^2}{U} = \frac{E^2}{2U}(1-\cos 2\omega t) \tag{6}$$

While useful, Equation 6 shows a dc term at the output, which varies strongly with the amplitude of the input, *E*.

Figure 24 shows a frequency doubler that overcomes this limitation and provides a relatively constant output over a moderately wide frequency range, determined by the time constant R1C1. The voltage applied to the X and Y inputs is exactly in quadrature at a frequency  $f = \frac{1}{2}\pi C1R1$ , and their amplitudes are equal. At higher frequencies, the X input becomes smaller while the Y input increases in amplitude; the opposite happens at lower frequencies. The result is a double frequency output centered on ground whose amplitude of 1 V for a 1 V input varies by only 0.5% over a frequency range of  $\pm 10\%$ . Because there is no squared dc component at the output, sudden changes in the input amplitude do not cause a bounce in the dc level.

Figure 24. Broadband Zero-Bounce Frequency Doubler

This circuit is based on the identity

$$\cos\theta\sin\theta = \frac{1}{2}\sin 2\theta\tag{7}$$

At  $\omega_0 = 1/C1R1$ , the X input leads the input signal by 45° (and is attenuated by  $\sqrt{2}$ , while the Y input lags the input signal by 45° and is also attenuated by  $\sqrt{2}$ . Because the X and Y inputs are 90° out of phase, the response of the circuit is

$$W = \frac{1}{U} \frac{E}{\sqrt{2}} (\sin \omega t - 45^{\circ}) \frac{E}{\sqrt{2}} (\sin \omega t + 45^{\circ}) = \frac{E^{2}}{2U} (\sin 2\omega t)$$

(8)

which has no dc component, R2 and R3 are included to restore the output to 1 V for an input amplitude of 1 V (the same gain adjustment as previously mentioned). Because the voltage across the capacitor (C1) decreases with frequency, while that across the resistor (R1) increases, the amplitude of the output varies only slightly with frequency. In fact, it is only 0.5% below its full value (at its center frequency  $\omega_0 = 1/C1R1$ ) at 90% and 110% of this frequency.

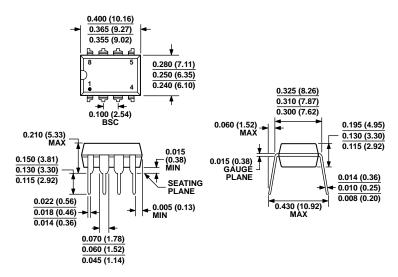

## **OUTLINE DIMENSIONS**

#### **COMPLIANT TO JEDEC STANDARDS MS-001**

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN. CORNER LEADS MAY BE CONFIGURED AS WHOLE OR HALF LEADS.

Figure 25. 8-Lead Plastic Dual In-Line Package [PDIP] Narrow Body (N-8)

Dimensions shown in inches and (millimeters)

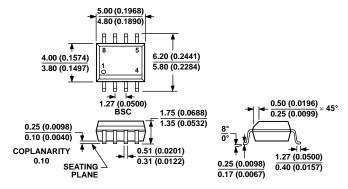

#### COMPLIANT TO JEDEC STANDARDS MS-012-AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 26. 8-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-8)

Dimensions shown in millimeters and (inches)

Rev. E | Page 13 of 14

### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                            | Package Option |

|--------------------|-------------------|------------------------------------------------|----------------|

| AD835ANZ           | -40°C to +85°C    | 8-Lead Plastic Dual In-Line Package [PDIP]     | N-8            |

| AD835AR            | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N] | R-8            |

| AD835AR-REEL7      | −40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N] | R-8            |

| AD835ARZ           | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N] | R-8            |

| AD835ARZ-REEL      | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N] | R-8            |

| AD835ARZ-REEL7     | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N] | R-8            |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part.