Contents STA311B

# **Contents**

| 6        |

|----------|

| 6        |

| 7        |

| 11       |

|          |

|          |

|          |

| 12       |

| 13       |

| 13       |

| 14       |

| 15       |

| 16       |

|          |

| ation 17 |

| ation    |

|          |

| 17       |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

STA311B Contents

|             | 7.4  | Read c  | pperation                                               | 20 |

|-------------|------|---------|---------------------------------------------------------|----|

|             |      | 7.4.1   | Current address byte read                               | 20 |

|             |      | 7.4.2   | Current address multi-byte read                         | 20 |

|             |      | 7.4.3   | Random address byte read                                |    |

|             |      | 7.4.4   | Random address multi-byte read                          | 21 |

| 8           | Regi | sters . |                                                         | 22 |

|             | 8.1  |         | er summary                                              |    |

|             | 8.2  | Registe | er description                                          | 27 |

|             |      | 8.2.1   | Configuration register A (0x00)                         |    |

|             |      | 8.2.2   | Configuration register B (0x01) - serial input formats  |    |

|             |      | 8.2.3   | Configuration register C (0x02) - serial output formats |    |

|             |      | 8.2.4   | Configuration register D (0x03)                         |    |

|             |      | 8.2.5   | Configuration register E (0x04)                         |    |

|             |      | 8.2.6   | Configuration register F (0x05)                         |    |

|             |      | 8.2.7   | Configuration register G (0x06)                         |    |

|             |      | 8.2.8   | Configuration register H (0x07)                         |    |

|             |      | 8.2.9   | Configuration register I (0x08)                         |    |

|             |      | 8.2.10  | Master mute register (0x09)                             |    |

|             |      | 8.2.11  | Master volume register (0x0A)                           |    |

|             |      | 8.2.12  | Channel 1 volume (0x0B)                                 |    |

|             |      | 8.2.13  | Channel 2 volume (0x0C)                                 |    |

|             |      | 8.2.14  | Channel 3 volume (0x0D)                                 | 41 |

|             |      | 8.2.15  | Channel 4 volume (0x0E)                                 | 41 |

|             |      | 8.2.16  | Channel 5 volume (0x0F)                                 | 41 |

|             |      | 8.2.17  | Channel 6 volume (0x10)                                 | 41 |

|             |      | 8.2.18  | Channel 7 volume (0x11)                                 |    |

|             |      | 8.2.19  | Channel 8 volume (0x12)                                 | 41 |

|             |      | 8.2.20  | Channel 1 volume trim, mute, bypass (0x13)              | 41 |

|             |      | 8.2.21  | Channel 2 volume trim, mute, bypass (0x14)              | 42 |

|             |      | 8.2.22  | Channel 3 volume trim, mute, bypass (0x15)              | 42 |

|             |      | 8.2.23  | Channel 4 volume trim, mute, bypass (0x16)              | 42 |

|             |      | 8.2.24  | Channel 5 volume trim, mute, bypass (0x17)              | 42 |

|             |      | 8.2.25  | Channel 6 volume trim, mute, bypass (0x18)              | 42 |

|             |      | 8.2.26  | Channel 7 volume trim, mute, bypass (0x19)              |    |

|             |      | 8.2.27  | Channel 8 volume trim, mute, bypass (0x1A)              | 42 |

|             |      | 8.2.28  | Channel input mapping channels 1 and 2 (0x1B)           | 44 |

| <del></del> |      |         |                                                         |    |

Contents STA311B

| 8.2.2 | Channel input mapping channels 3 and 4 (0x1C)                   | 14 |

|-------|-----------------------------------------------------------------|----|

| 8.2.3 | Channel input mapping channels 5 and 6 (0x1D)                   | 44 |

| 8.2.3 | Channel input mapping channels 7 and 8 (0x1E)                   | 14 |

| 8.2.3 | AUTO1 - AutoModes EQ, volume, GC (0x1F)                         | 45 |

| 8.2.3 | AUTO2 - AutoModes bass management2 (0x20)                       | 46 |

| 8.2.3 | AUTO3 - AutoMode AM/pre-scale/bass management scale (0x21)      | 48 |

| 8.2.3 | PREEQ - Preset EQ settings (0x22)                               | 48 |

| 8.2.3 | 36 AGEQ - graphic EQ 80-Hz band (0x23)                          | 50 |

| 8.2.3 | BGEQ - graphic EQ 300-Hz band (0x24)                            | 50 |

| 8.2.3 | 38 CGEQ - graphic EQ 1-kHz band (0x25)                          | 5C |

| 8.2.3 | 39 DGEQ - graphic EQ 3-kHz band (0x26)                          | 5C |

| 8.2.4 | 10 EGEQ - graphic EQ 8-kHz band (0x27)                          | 5C |

| 8.2.4 | Biquad internal channel loop-through (0x28)                     | 52 |

| 8.2.4 | Mix internal channel loop-through (0x29)                        | 52 |

| 8.2.4 | 3 EQ bypass (0x2A)                                              | 52 |

| 8.2.4 | Tone control bypass (0x2B)                                      | 53 |

| 8.2.4 | Tone control (0x2C)                                             | 53 |

| 8.2.4 | Channel limiter select channels 1, 2, 3, 4 (0x2D)               | 54 |

| 8.2.4 | Channel limiter select channels 5, 6, 7, 8 (0x2E)               | 54 |

| 8.2.4 | Limiter 1 attack/release rate (0x2F)                            | 54 |

| 8.2.4 | Limiter 1 attack/release threshold (0x30)                       | 54 |

| 8.2.5 | Limiter 2 attack/release rate (0x31)                            | 54 |

| 8.2.5 | ,                                                               |    |

| 8.2.5 | Bit description                                                 | 54 |

| 8.2.5 | Channel 1 and 2 output timing (0x33)                            | 59 |

| 8.2.5 | Channel 3 and 4 output timing (0x34)                            | 59 |

| 8.2.5 | Channel 5 and 6 output timing (0x35)                            | 59 |

| 8.2.5 | Channel 7 and 8 output timing (0x36)                            | 59 |

| 8.2.5 | Channel I <sup>2</sup> S output mapping channels 1 and 2 (0x37) | 3C |

| 8.2.5 | Channel I <sup>2</sup> S output mapping channels 3 and 4 (0x38) | 3C |

| 8.2.5 | Channel I <sup>2</sup> S output mapping channels 5 and 6 (0x39) | 30 |

| 8.2.6 | Channel I <sup>2</sup> S output mapping channels 7 and 8 (0x3A) | 3C |

| 8.2.6 | Coefficient address register 1 (0x3B)                           | 31 |

| 8.2.6 | Coefficient address register 2 (0x3C)                           | 31 |

| 8.2.6 | Coefficient b1 data register, bits 23:16 (0x3D)                 | 31 |

| 8.2.6 | Coefficient b1 data register, bits 15:8 (0x3E)                  | 31 |

| 8.2.6 | Coefficient b1 data register, bits 7:0 (0x3F)                   | 31 |

4/102 DocID024340 Rev 1

STA311B Contents

|   |      | 8.2.66         | Coefficient b2 data register, bits 23:16 (0x40) 6                                                                               | 1        |

|---|------|----------------|---------------------------------------------------------------------------------------------------------------------------------|----------|

|   |      | 8.2.67         | Coefficient b2 data register, bits 15:8 (0x41)                                                                                  | 2        |

|   |      | 8.2.68         | Coefficient b2 data register, bits 7:0 (0x42)                                                                                   | 2        |

|   |      | 8.2.69         | Coefficient a1 data register, bits 23:16 (0x43) 6                                                                               | 2        |

|   |      | 8.2.70         | Coefficient a1 data register, bits 15:8 (0x44)                                                                                  | 2        |

|   |      | 8.2.71         | Coefficient a1 data register, bits 7:0 (0x45)                                                                                   | 2        |

|   |      | 8.2.72         | Coefficient a2 data register, bits 23:16 (0x46) 6                                                                               | 2        |

|   |      | 8.2.73         | Coefficient a2 data register, bits 15:8 (0x47)                                                                                  | 3        |

|   |      | 8.2.74         | Coefficient a2 data register, bits 7:0 (0x48)                                                                                   | 3        |

|   |      | 8.2.75         | Coefficient b0 data register, bits 23:16 (0x49) 6                                                                               | 3        |

|   |      | 8.2.76         | Coefficient b0 data register, bits 15:8 (0x4A) 6                                                                                | 3        |

|   |      | 8.2.77         | Coefficient b0 data register, bits 7:0 (0x4B) 6                                                                                 | 3        |

|   |      | 8.2.78         | Coefficient write control register (0x4C)                                                                                       | 3        |

|   | 8.3  | Readin         | ng a coefficient from RAM 6                                                                                                     | 4        |

|   | 8.4  | Readin         | ng a set of coefficients from RAM 6                                                                                             | 4        |

|   | 8.5  | Writing        | a single coefficient to RAM 6                                                                                                   | 4        |

|   | 8.6  | Writing        | a set of coefficients to RAM 6                                                                                                  | 5        |

|   |      | _              |                                                                                                                                 |          |

| 9 | Conf | figuratio      | on registers (0x77; 0x78; 0x79) 6                                                                                               | 6        |

|   | 9.1  | Post-so        | cale                                                                                                                            | 7        |

|   | 9.2  | Variabl        | e max power correction                                                                                                          | 0        |

|   |      | 9.2.1          | MPCC1-2 (0x4D, 0x4E)                                                                                                            | '0       |

|   | 9.3  | Variabl        | e distortion compensation                                                                                                       | 0        |

|   |      | 9.3.1          | DCC1-2 (0x4F, 0x50)                                                                                                             | '0       |

|   | 9.4  | PSCor          | rect registers                                                                                                                  | 1        |

|   |      | 9.4.1          |                                                                                                                                 |          |

|   |      | 9.4.2          | PSC3: correction normalization value (CNV) (0x53)                                                                               |          |

|   | 9.5  | Extend         | led DRC configuration registers                                                                                                 | ·1       |

|   |      | 9.5.1          | Extended limiter/dynamic range control LUT (NLENAR)(0x5A)7                                                                      |          |

|   |      | 9.5.2          | Extended limiter/dynamic range LUT registers (nLxAT/RT) (0x6B, 0x6C, 0x6D, 0x6E)                                                |          |

|   |      | 9.5.3          | Recombination control register 1 (0x5D)                                                                                         |          |

|   |      |                | · , , , ,                                                                                                                       |          |

|   |      | 9.5.4          | Recombination control register 5, 6 and 7 (0x62: 0x63: 0x64)                                                                    | S        |

|   |      | 9.5.4<br>9.5.5 | Recombination control register 5, 6 and 7 (0x62; 0x63; 0x64) 8  Recombination control register 8, 9 and 10 (0x65; 0x66; 0x67) 8 |          |

|   |      | 9.5.5          | Recombination control register 8, 9 and 10 (0x65; 0x66; 0x67)8                                                                  | 35       |

|   |      |                | •                                                                                                                               | 35<br>36 |

Contents STA311B

| 12 | Revis | sion his | tory                                                      | 101  |

|----|-------|----------|-----------------------------------------------------------|------|

| 11 | Pack  | age info | ormation                                                  | 98   |

|    | 10.3  | User-de  | efined delay time (0x82) and (0x83)                       | 96   |

|    | 10.2  | Configu  | uration register (0x81)                                   | 95   |

|    | 10.1  | DPT: P   | WM and tristate delay (0x80)                              | 95   |

| 10 | Start | up/shut  | down pop noise removal                                    | 95   |

|    |       | 9.5.10   | RMS level registers (0x7A, 0x7B, 0x7C, 0x7D)              | . 92 |

|    |       | 9.5.9    | Clock manager configuration                               | . 90 |

|    |       | 9.5.8    | RMS post-processing selectors and Fs autodetection (0x70) | . 89 |

|    |       |          |                                                           |      |

STA311B List of tables

# List of tables

| Table 1.  | Device summary                                         | 1   |

|-----------|--------------------------------------------------------|-----|

| Table 2.  | Pin description                                        | 12  |

| Table 3.  | Absolute maximum ratings                               | 15  |

| Table 4.  | Thermal data                                           | 15  |

| Table 5.  | Recommended operating conditions                       | 15  |

| Table 6.  | General interface electrical specifications            | 16  |

| Table 7.  | DC electrical characteristics: 3.3-V buffers           | 16  |

| Table 8.  | Timing parameters for slave mode                       | 17  |

| Table 9.  | Serial data bit first                                  | 18  |

| Table 10. | Serial audio input formats according to sampling rate  | 18  |

| Table 11. | Register summary                                       | 26  |

| Table 12. | Serial audio input formats according to sampling rate  | 34  |

| Table 13. | Serial audio output formats according to sampling rate | 36  |

| Table 14. | RAM block for biquads, mixing, and bass management     | 70  |

| Table 15. | Extended release thresholds (AC mode)                  | 74  |

| Table 16. | Extended attack thresholds (AC mode)                   | 76  |

| Table 17. | Extended attack thresholds (DRC mode)                  | 79  |

| Table 18. | Extended release thresholds (DRC mode)                 | 81  |

| Table 19. | Gain adjustment (sensitivity)                          | 84  |

| Table 20. | Normal channel attenuation                             | 86  |

| Table 21. | Threshold configuration                                | 88  |

| Table 22. | RMS channel select                                     | 90  |

| Table 23. | Zero-detect threshold                                  | 90  |

| Table 24. | Zero-detect hysteresis                                 | 90  |

| Table 25. | RMS post-processing channel select                     | 91  |

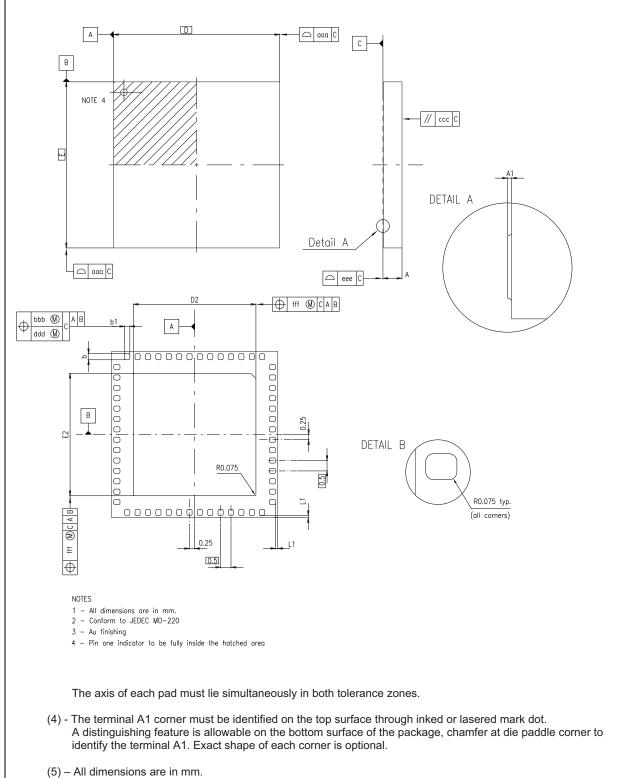

| Table 26. | VFQFPN-56 (8 x 8 mm) package dimensions                | 99  |

| Table 27. | Exposed pad variations                                 |     |

| Table 28. | Document revision history                              | 101 |

List of figures STA311B

# **List of figures**

| Figure 1.  | Block diagram                                                    |

|------------|------------------------------------------------------------------|

| Figure 2.  | Pin connections VFQFPN-56 (top view)                             |

| Figure 3.  | Timing diagram for SAI interface                                 |

| Figure 4.  | Processing data path                                             |

| Figure 5.  | I <sup>2</sup> S recombination block diagram                     |

| Figure 6.  | Power-on sequence for pop-free startup                           |

| Figure 7.  | Write mode sequence                                              |

| Figure 8.  | Read mode sequence                                               |

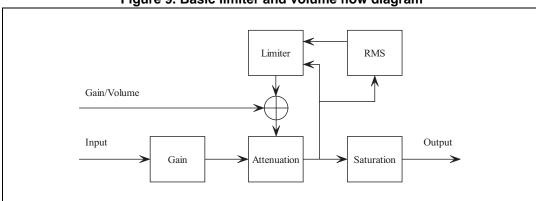

| Figure 9.  | Basic limiter and volume flow diagram                            |

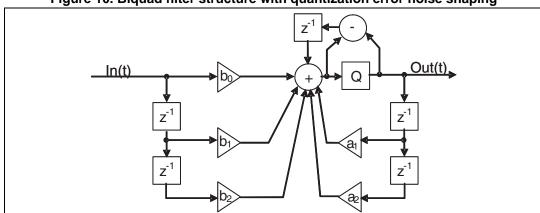

| Figure 10. | Biquad filter structure with quantization error noise shaping 69 |

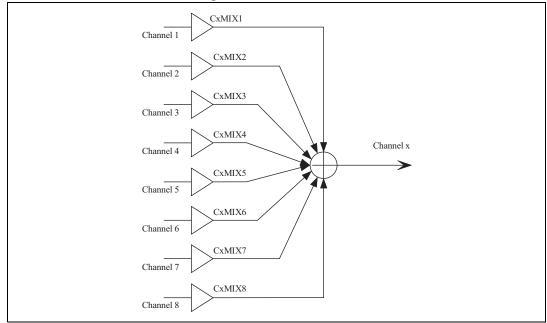

| Figure 11. | Channel mixer                                                    |

| Figure 12. | VFQFPN-56 (8 x 8 mm) package outline                             |

8/102 DocID024340 Rev 1

STA311B Description

# 1 Description

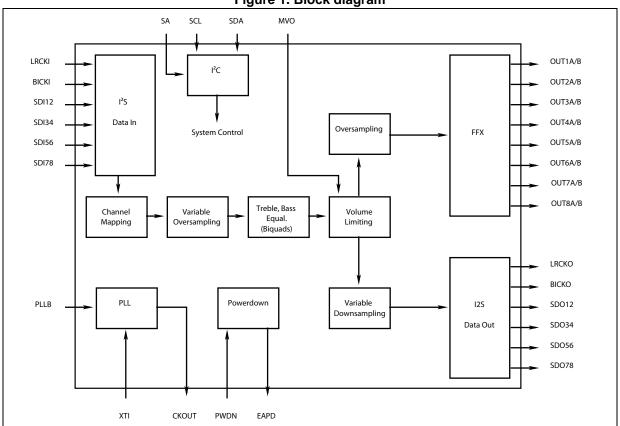

The STA311B is a single-chip solution for digital audio processing and control in multichannel applications and provides output capabilities for FFX<sup>™</sup> (full flexible amplification). In conjunction with an FFX<sup>™</sup> power device, it provides high-quality, high-efficiency, all digital amplification. The device is extremely versatile, allowing for input of most digital formats including 6.1/7.1-channel and 192 kHz, 24-bit DVD-audio, DSD/SACD. In the 5.1 application the additional 2 channels can be used for audio line-out or headphone drive.

Device overview STA311B

### 2 Device overview

### 2.1 Block diagram

Figure 1. Block diagram

57/

STA311B Device overview

### 2.2 Pin description

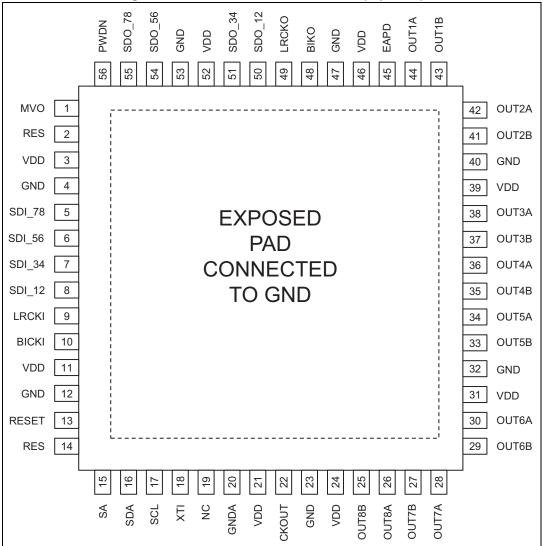

Figure 2. Pin connections VFQFPN-56 (top view)

Device overview STA311B

Table 2. Pin description

| Pin | Type                                                                                                          | Name         | Description                                              |

|-----|---------------------------------------------------------------------------------------------------------------|--------------|----------------------------------------------------------|

| 1   | 5-V tolerant TTL input buffer                                                                                 | MVO/DSD_CLK  | Master volume override/<br>DSD input clock               |

| 2   | Reserved                                                                                                      | RES          | Connect to GND                                           |

| 5   | 5-V tolerant TTL input buffer                                                                                 | SDI_78/DSD_6 | Input serial data channels 7 & 8/<br>DSD input channel 6 |

| 6   | 5-V tolerant TTL input buffer                                                                                 | SDI_56/DSD_5 | Input serial data channels 5 & 6/<br>DSD input channel 5 |

| 7   | 5-V tolerant TTL input buffer                                                                                 | SDI_34/DSD_4 | Input serial data channels 3 & 4/<br>DSD input channel 4 |

| 8   | 5-V tolerant TTL input buffer                                                                                 | SDI_12/DSD_3 | Input serial data channels 1 & 2/<br>DSD input channel 3 |

| 9   | 5-V tolerant TTL input buffer                                                                                 | LRCKI/DSD_2  | Input left/right clock/<br>DSD input channel 2           |

| 10  | 5-V tolerant TTL input buffer                                                                                 | BICKI/DSD_1  | Input serial clock/<br>DSD input channel 1               |

| 18  | 5-V tolerant TTL Schmitt trigger input buffer                                                                 | RESETN       | Global reset                                             |

| 14  | Reserved                                                                                                      | RES          | Connect to GND                                           |

| 15  | 1.8V CMOS input buffer with pull-down                                                                         | SA           | Select address (I <sup>2</sup> C)                        |

| 16  | Bidirectional buffer: 5-V tolerant TTL Schmitt trigger input; 3.3-V capable 2 mA slew-rate controlled output. | SDA          | Serial data (I <sup>2</sup> C)                           |

| 17  | 5-V tolerant TTL Schmitt trigger input buffer                                                                 | SCL          | Serial clock (I <sup>2</sup> C)                          |

| 18  | 5-V tolerant TTL Schmitt trigger input buffer                                                                 | ХТІ          | Crystal oscillator input (clock input)                   |

| 19  | Not connected                                                                                                 | NC           | Reserved                                                 |

| 20  | Analog ground                                                                                                 | GNDA         | PLL ground                                               |

| 22  | 3.3-V capable TTL tristate 4 mA output buffer                                                                 | СКОИТ        | Clock output                                             |

| 25  | 3.3-V capable TTL 2 mA output buffer                                                                          | OUT8B        | PWM channel 8 output B                                   |

| 26  | 3.3-V capable TTL 2 mA output buffer                                                                          | OUT8A        | PWM channel 8 output A                                   |

| 27  | 3.3-V capable TTL 2 mA output buffer                                                                          | OUT7B        | PWM channel 7 output B                                   |

| 28  | 3.3-V capable TTL 2 mA output buffer                                                                          | OUT7A        | PWM channel 7 output A                                   |

| 29  | 3.3-V capable TTL 2 mA output buffer                                                                          | OUT6B        | PWM channel 6 output B                                   |

| 30  | 3.3-V capable TTL 2 mA output buffer                                                                          | OUT6A        | PWM channel 6 output A                                   |

| 33  | 3.3-V capable TTL 2 mA output buffer                                                                          | OUT5B        | PWM channel 5 output B                                   |

| 34  | 3.3-V capable TTL 2 mA output buffer                                                                          | OUT5A        | PWM channel 5 output A                                   |

| 35  | 3.3-V capable TTL 2 mA output buffer                                                                          | OUT4B        | PWM channel 4 output B                                   |

12/102 DocID024340 Rev 1

STA311B Device overview

Table 2. Pin description (continued)

| Pin                            | Туре                                          | Name Description |                                                                                        |  |  |

|--------------------------------|-----------------------------------------------|------------------|----------------------------------------------------------------------------------------|--|--|

| 36                             | 3.3-V capable TTL 2 mA output buffer          | OUT4A            | PWM channel 4 output A                                                                 |  |  |

| 37                             | 3.3-V capable TTL 2 mA output buffer          | OUT3B            | PWM channel 3 output B                                                                 |  |  |

| 38                             | 3.3-V capable TTL 2 mA output buffer          | OUT3A            | PWM channel 3 output A                                                                 |  |  |

| 41                             | 3.3-V capable TTL 2 mA output buffer          | OUT2B            | PWM channel 2 output B                                                                 |  |  |

| 42                             | 3.3-V capable TTL 2 mA output buffer          | OUT2A            | PWM channel 2 output A                                                                 |  |  |

| 43                             | 3.3-V capable TTL 2 mA output buffer          | OUT1B            | PWM channel 1 output B                                                                 |  |  |

| 44                             | 3.3-V capable TTL 2 mA output buffer          | OUT1A            | PWM channel 1 output A                                                                 |  |  |

| 45                             | 3.3-V capable TTL 4 mA output buffer          | EAPD             | External amp power-down                                                                |  |  |

| 48                             | 3.3-V capable TTL 2 mA output buffer          | BICKO            | Output serial clock                                                                    |  |  |

| 49                             | 3.3-V capable TTL 2 mA output buffer          | LRCKO            | Output left/right clock                                                                |  |  |

| 50                             | 3.3-V capable TTL 2 mA output buffer          | SDO_12           | Output serial data channels 1&2                                                        |  |  |

| 51                             | 3.3-V capable TTL 2 mA output buffer          | SDO_34           | Output serial data channels 3&4                                                        |  |  |

| 54                             | 3.3-V capable TTL 2 mA bidirectional buffer   | SDO_56           | Output serial data channels 5&6<br>External power bridge fault input                   |  |  |

| 55                             | 3.3-V capable TTL 2mA output buffer           | SDO_78           | Output serial data channels 7&8 External power bridge tristate signal ('0' = tristate) |  |  |

| 56                             | 5-V tolerant TTL Schmitt trigger input buffer | PWDN             | Device power-down                                                                      |  |  |

| 3, 11,21,24,<br>31, 39, 46, 52 | 3.3-V digital supply voltage                  | VDD              | 3.3-V supply                                                                           |  |  |

| 4, 12, 23, 32,<br>40, 47, 53   | Digital ground                                | GND              | Ground                                                                                 |  |  |

### Master volume override (MVO)

This pin enables the user to bypass the volume control on all channels. When MVO is pulled high, the master volume register is set to 0x00, which corresponds to its full-scale setting. The master volume register setting offsets the individual channel volume settings, which default to 0 dB.

#### Serial data in (SDI\_12, SDI\_34, SDI\_56, SDI\_78)

Audio information enters the device here. Six format choices are available including I<sup>2</sup>S, left-justified or right-justified, LSB or MSB first, with word widths of 16, 18, 20 and 24 bits.

#### **RESET**

Driving this pin low turns off the outputs and returns all settings to their defaults.

#### I2C bus

The SA, SDA and SCL pins operate per the Phillips I<sup>2</sup>C specification. See Section 7: I<sup>2</sup>C bus operation on page 23.

DocID024340 Rev 1

13/102

Device overview STA311B

### Phase-locked loop (PLL)

The phase-locked loop section provides the system timing signals and CKOUT.

#### Clock output (CKOUT)

System synchronization and master clocks are provided by CKOUT.

### **PWM outputs (OUT1 through OUT8)**

The PWM outputs provide the input signal for the power devices.

#### External amplifier power-down (EAPD)

This signal can be used to control the power-down of the FFX power devices.

### Serial data out (SDO\_12, SDO\_34, SDO\_56, SDO\_78)

When the pop-noise removal feature is disabled, these are the outputs for the audio information. Six different formats are available including I2S, left-or right-justified, LSB or MSB first, with word widths of 16, 18, 20 and 24 bits.

However, when the pop-noise removal feature is enabled, SDO\_12 and SDO\_34 output the audio information, whereas SDO\_56 is used as the external power bridge fault input and SDO\_78 as the external power bridge tristate signal.

#### **Device power-down (PWDN)**

Pulling PWDN low begins the power-down sequence which puts the STA311B into a low-power state. EAPD goes low approximately 30 ms later.

### Frequency sampling autodetection

The system clock is generated by PLL using XTI or BICKI input, and the ratio (IR) between the frequency sampling (Fs) of the audio serial and the PLL clock has to be set in the appropriate registers via the I<sup>2</sup>C interface. If the Fs autodetection function has been enabled, the IR parameter will be set automatically based on the Fs input (see Fs autodetection on page 32).

# 3 Electrical characteristics

### 3.1 Absolute maximum ratings

Table 3. Absolute maximum ratings

| Symbol           | Parameter                     | Min  | Тур | Max       | Unit |

|------------------|-------------------------------|------|-----|-----------|------|

| $V_{DD}$         | 3.3-V I/O power supply        | -0.5 |     | 4         | ٧    |

| Vi               | Voltage on input pins         | -0.5 |     | VDD + 0.5 | ٧    |

| V <sub>o</sub>   | Voltage on output pins        | -0.5 |     | VDD + 0.3 | ٧    |

| VSA              | Voltage on SA pin 15          | -0.5 |     | 2.0       | ٧    |

| T <sub>stg</sub> | Storage temperature           | -40  |     | 150       | °C   |

| T <sub>amb</sub> | Ambient operating temperature | -40  |     | 90        | °C   |

### 3.2 Thermal data

Table 4. Thermal data

| Symbol               | Parameter                               | Min | Тур | Max | Unit |

|----------------------|-----------------------------------------|-----|-----|-----|------|

| R <sub>thj-amb</sub> | Thermal resistance, junction to ambient |     | 85  |     | °C/W |

### 3.3 Recommended operating conditions

Table 5. Recommended operating conditions

| Symbol         | Parameter                      | Min | Тур | Max  | Unit |

|----------------|--------------------------------|-----|-----|------|------|

| $V_{DD}$       | I/O power supply               | 3.0 | 3.3 | 3.6  | V    |

| VSA            | Voltage on SA pin 15           | 0.0 | 1.8 | 1.95 | V    |

| T <sub>j</sub> | Operating junction temperature | -40 | 25  | 125  | °C   |

Electrical characteristics STA311B

# 3.4 Electrical specifications

The following specifications are valid for  $V_{DD}$  =3.3 V ± 0.3 V, VSA=0V and  $T_{amb}$  = 25 °C, unless otherwise stated.

Table 6. General interface electrical specifications

| Symbol           | Parameter                                    | Conditions           | Min  | Тур | Max | Unit |

|------------------|----------------------------------------------|----------------------|------|-----|-----|------|

| I <sub>il</sub>  | Low-level input, no pull-up                  | V <sub>i</sub> = 0 V |      |     | 1   | μΑ   |

| I <sub>ih</sub>  | High-level input, no pull-down               | $V_i = V_{DD}$       |      |     | 2   | μΑ   |

| I <sub>OZ</sub>  | Tristate output leakage without pull-up/down | $V_i = V_{DD}$       |      |     | 2   | μΑ   |

| V <sub>esd</sub> | Electrostatic protection (human body model)  | Leakage < 1 μA       | 2000 |     |     | V    |

Table 7. DC electrical characteristics: 3.3-V buffers

| Symbol              | Parameter                  | Conditions                   | Min         | Тур  | Max  | Unit |

|---------------------|----------------------------|------------------------------|-------------|------|------|------|

| V <sub>IL</sub>     | Low-level input voltage    |                              |             |      | 8.0  | V    |

| V <sub>IH</sub>     | High-level input voltage   |                              | 2.0         |      |      | V    |

| V <sub>ILhyst</sub> | Low-level threshold        | Input falling                | 0.8         |      | 1.35 | V    |

| V <sub>IHhyst</sub> | High-level threshold       | Input rising                 | 1.3         |      | 2.0  | V    |

| V <sub>hyst</sub>   | Schmitt trigger hysteresis |                              | 0.3         |      | 0.8  | V    |

| V <sub>ol</sub>     | Low-level output           | I <sub>OI</sub> = 100 μA     |             |      | 0.2  | V    |

| V <sub>oh</sub>     | High-level output          | I <sub>oh</sub> = -100 μA    | VDD-<br>0.2 |      |      | >    |

|                     |                            | I <sub>oh</sub> = -2 mA      | 2.4         |      |      | V    |

| ldd                 | Quiescent current          | Reset conditions             |             | 15   |      | mA   |

| luu                 | Quiescent current          | Normal conditions with CKOUT |             | 60   |      | mA   |

| fckout              |                            | Reset=1<br>PWDN=1            |             | 2.85 |      | MHz  |

STA311B Serial audio interface

### 4 Serial audio interface

The STA311B audio serial input interfaces with standard digital audio components and accepts a number of serial data formats. The STA311B always acts as a slave when receiving audio input from standard digital audio components. Serial data for eight channels is provided using 6 input pins: left/right clock LRCKI, serial clock BICKI, serial data 1 and 2 SDI\_12, serial data 3 and 4 SDI\_34, serial data 5 and 6 SDI\_56, and serial data 7 and 8 SDI\_78. The SAI/SAIFB register (configuration register B, address 0x01) is used to specify the serial data format. The default serial data format is I²S, MSB-first.

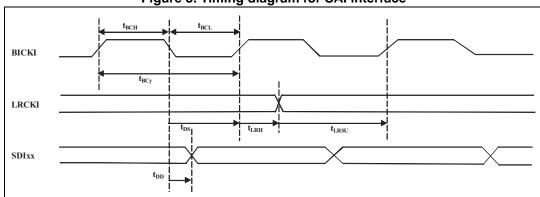

### 4.1 Timings

In the STA311B, the BICKI and LRCKI pins are configured as inputs and they must be supplied by the external peripheral.

Figure 3. Timing diagram for SAI interface

Table 8. Timing parameters for slave mode

| Symbol            | Parameter                                    | Min | Тур | Max | Unit |

|-------------------|----------------------------------------------|-----|-----|-----|------|

| t <sub>BCy</sub>  | BICK cycle time                              | 50  | -   | -   | ns   |

| t <sub>BCH</sub>  | BICK pulse width high                        | 20  | -   | -   | ns   |

| t <sub>BCL</sub>  | BICK pulse width low                         | 20  | -   | -   | ns   |

| t <sub>LRSU</sub> | LRCKI setup time to BICKI strobing edge      | 10  | -   | -   | ns   |

| t <sub>LRH</sub>  | LRCKI hold time to BICKI strobing edge       | 10  | -   | -   | ns   |

| t <sub>DD</sub>   | SDI propagation delay from BICKI active edge | 0   | -   | 10  | ns   |

Serial audio interface STA311B

### 4.2 Serial data formats

Available formats are shown in the following tables.

Table 9. Serial data bit first

| Bit | RW | RST | Name | Description                                                                |

|-----|----|-----|------|----------------------------------------------------------------------------|

| 4   | RW | 0   |      | Determines MSB or LSB first for all SAO formats: 0: MSB first 1: LSB first |

Note: Serial input and output formats are specified separately

For example, SAI = 1110 and SAIFB = 1 would specify right-justified 16-bit data, LSB-first.

The table below lists the serial audio input formats supported by the STA311B as related to BICKI = 32 \* fs, 48 \* fs, 64 \* fs, where the sampling rate, fs = 32, 44.1, 48, 88.2, 96, 176.4, 192 kHz.

Table 10. Serial audio input formats according to sampling rate

| віскі   | SAI [3:0] | SAIFB | Interface format                 |

|---------|-----------|-------|----------------------------------|

| 32 * fs | 1100      | Х     | I²SI²S 15-bit data               |

| 32 15   | 1110      | Х     | Left/right-justified 16-bit data |

|         | 0100      | Х     | I <sup>2</sup> S 23-bit data     |

|         | 0100      | Х     | I <sup>2</sup> S 20-bit data     |

|         | 1000      | Х     | I <sup>2</sup> S 18-bit data     |

|         | 0100      | 0     | MSB-first I2S 16-bit data        |

|         | 1100      | 1     | LSB-first I2S 16-bit data        |

|         | 0001      | Х     | Left-justified 24-bit data       |

| 48 * fs | 0101      | Х     | Left-justified 20-bit data       |

|         | 1001      | Х     | Left-justified 18-bit data       |

|         | 1101      | Х     | Left-justified 16-bit data       |

|         | 0010      | Х     | Right-justified 24-bit data      |

|         | 0110      | Х     | Right-justified 20-bit data      |

|         | 1010      | Х     | Right-justified 18-bit data      |

|         | 1110      | Х     | Right-justified 16-bit data      |

STA311B Serial audio interface

Table 10. Serial audio input formats according to sampling rate (continued)

| BICKI   | SAI [3:0] | SAIFB | Interface format                       |

|---------|-----------|-------|----------------------------------------|

|         | 0000      | X     | I <sup>2</sup> S 24-bit data           |

|         | 0100      | Х     | I <sup>2</sup> S 20-bit data           |

|         | 1000      | Х     | I <sup>2</sup> S 18-bit data           |

|         | 0000      | 0     | MSB-first I <sup>2</sup> S 16-bit data |

|         | 1100      | 1     | LSB-first I2S 16-bit data              |

|         | 0001      | Х     | Left-justified 24-bit data             |

| 64 * fs | 0101      | Х     | Left-justified 20-bit data             |

|         | 1001      | X     | Left-justified 18-bit data             |

|         | 1101      | Х     | Left-justified 16-bit data             |

|         | 0010      | Х     | Right-justified 24-bit data            |

|         | 0110      | Х     | Right-justified 20-bit data            |

|         | 1010      | Х     | Right-justified 18-bit data            |

|         | 1110      | Х     | Right-justified 16-bit data            |

### 4.3 Processing data paths

The whole STA311B processing chain is depicted in *Figure 4*. A programmable rate conversion algorithm is applied to the incoming digital audio data (x3,x2,x1,/2) resampling it to the processing rate. A dual-channel plus line out processing is then implemented, with mixing, EQ capability followed by a Volume/DRC block and final DC cut filter. The final oversampling stage and post scaler will provide the output data stream to the PWM modulators. Three different DRC configurations can be used, single-band, dual-band or enhanced dual-band DRC, as shown below.

6 Inputs From DSD DSD Conversion Interp\_Rate 8 Inputs 1x,2x,4x Mapping/ Biquads Volume Mix #2 Interp Mix #1 B/T Limiter Interp FFX Distortion Output C Con PWM

Figure 4. Processing data path

DocID024340 Rev 1

19/102

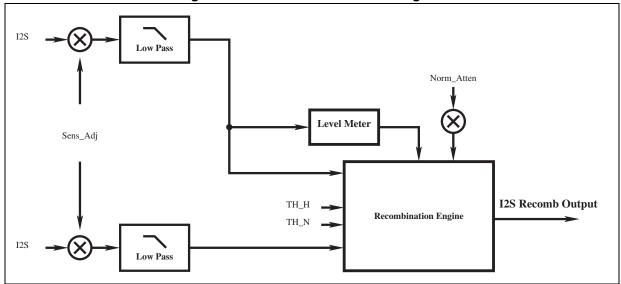

# 5 I<sup>2</sup>S recombination interface

The I<sup>2</sup>S recombination interface shares the same controls for thresholds and gains. However, the low-pass filter is not present and thus the I<sup>2</sup>S signals coming from the outside should be correctly filtered and conditioned for a correct recombination.

Figure 5. I2S recombination block diagram

# 6 Startup/shutdown pop noise removal in SE application

Click and pop can generally be defined as undesired audible transients generated by the amplifier system not coming from the system input signal. Such transients can be generated when the amplifier system changes its operating mode: system power-up/power-down, mute/unmute. Every time the PWM starts or stops, if no soft charge method is applied, the result is an audible pop noise.

The STA311B integrates a "pop-elimination" circuitry that removes undesired audible pop noise at the PWM switching start and stop either in single-ended or single-ended virtual ground configurations.

In particular the pop elimination circuit receives as inputs the PWMs generated by the modulator (PWMs\_in) and it generates both a delayed version of the PWMs (PWMs\_out) and a tristate signal that are sent to the Power stages to attenuate the audible pop at the power up/down.

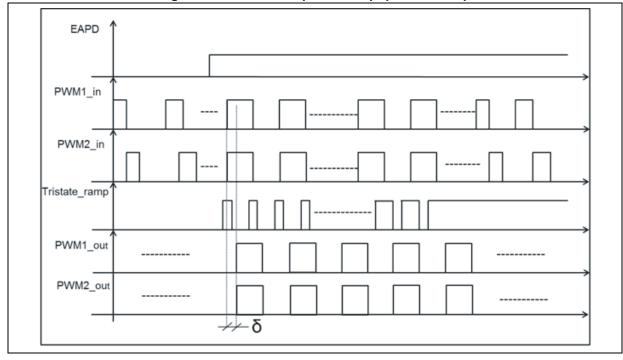

### 6.1 PWM start

At power-up as soon as the external amplifier power-down (EAPD) is set to one, if at least one channel at the output of the modulator is in binary mode, the pop elimination circuit selects the related PWM input which exhibits the lower PWM timing delay (set using the I<sup>2</sup>C registers 0x33, 0x34,0x35, 0x36), and it uses it as a PWM reference to synchronize the remaining PWMs\_in whose channels are set in binary mode (synchronization phase).

Moreover, during the synchronization phase the modulator is internally muted by setting the audio input signal to

zero. At the end of this phase, all the PWMs\_in are synchronous with the PWM reference and they have a duty cycle of 50%.

At each rising edge of the PWM reference, twoTristate\_ramp pulses with increasing duty cycle are generated. As depicted in *Figure 10*, where for the sake of simplicity, only two PWMs\_in (PWM1\_in and PWM2\_in) are shown, each pulse is centered with respect to both the rising and falling edges of the PWM reference, and their duty cycle initially set to 21.87% increases gradually and becomes equal to 100% at the end of theTristate\_ramp.

Figure 6. Power-on sequence for pop-free startup

Moreover in order to compensate an internal delay between the tristate signal and the PWM present in the Power stage devices, the pop noise removal circuit generates a delayed version of the PWM\_in with respect to the Tristate\_ramp signal named PWM1\_out and PWM2\_out in *Figure 6*. The delay value delta between the Tristate\_ramp and the PWM\_in is programmable using the I<sup>2</sup>C register 0x80 and the default value is 290 ns.

Finally when the Tristate\_ramp duty cycle is equal to 100%, during the de-synchronization phase the PWM time slots, equal for all the PWMs outputs, are changed so that the final channel shift will be the one configured by registers 0x33, 0x34, 0x35 and 0x36. At this point the PWM modulator is automatically un-muted so that the processing outputs can be played.

### 6.2 PWM stop

When the EAPD signal is set to zero, the modulator is stopped internally, forcing the input audio signal, used to feed the modulator, to zero. After that, the PWM which exhibits the lower PWM timing delay is internally selected and used as a reference. Using the PWM reference, all the PWMs are re-synchronized, and as soon as all PWMs are aligned, at each rising edge of a PWM reference, a reverse tristate\_ramp signal is generated. As during startup, the reverse tristate\_ramp pulses are centered with respect to the rising and falling edge of the PWM reference, but in this case the starting duty cycle is equal to 100% and gradually becomes equal to zero when the reverse tristate\_ramp finishes.

In the STA311B the pop-elimination circuit is activated only when at least one channel is set in binary mode, and the PWMs out speed is set to 384 kHz. In all the other cases the no pop-free PWM switching start/stop procedure is adopted.

57

22/102 DocID024340 Rev 1

STA311B I<sup>2</sup>C bus operation

### 7 I<sup>2</sup>C bus operation

The STA311B supports the I<sup>2</sup>C protocol via the input ports SCL and SDA\_IN (master to slave) and the output port SDA\_OUT (slave to master).

This protocol defines any device that sends data on to the bus as a transmitter and any device that reads the data as a receiver.

The device that controls the data transfer is known as the master and the other as the slave. The master always starts the transfer and provides the serial clock for synchronization. The STA311B is always a slave device in all of its communications.

### 7.1 Communication protocol

### 7.1.1 Data transition or change

Data changes on the SDA line must only occur when the SCL clock is low. An SDA transition while the clock is high is used to identify a START or STOP condition.

### 7.1.2 Start condition

START is identified by a high-to-low transition of the data bus SDA signal while the clock signal SCL is stable in the high state. A START condition must precede any command for data transfer.

### 7.1.3 Stop condition

STOP is identified by a low-to-high transition of the data bus SDA signal while the clock signal SCL is stable in the high state. A STOP condition terminates communication between the STA311B and the bus master.

#### 7.1.4 Data input

During the data input the STA311B samples the SDA signal on the rising edge of clock SCL.

For correct device operation the SDA signal must be stable during the rising edge of the clock and the data can change only when the SCL line is low.

### 7.2 Device addressing

To start communication between the master and the Omega FFX core, the master must initiate with a start condition. Following this, the master sends 8 bits onto the SDA line (MSB first) corresponding to the device select address and read or write mode.

The 7 most significant bits are the device address identifiers, corresponding to the  $I^2C$  bus definition. In the STA311B the  $I^2C$  interface has two device addresses depending on the SA port configuration, 0x40 or 0100000x when SA = 0, and 0x42 or 0100001x when SA = 1.

The 8<sup>th</sup> bit (LSB) identifies read or write operation RW, this bit is set to 1 in read mode and 0 for write mode. After a START condition the STA311B identifies on the bus the device address and if a match is found, it acknowledges the identification on SDA bus during the 9<sup>th</sup>-bit time. The byte following the device identification byte is the internal space address.

DocID024340 Rev 1 23/102

I<sup>2</sup>C bus operation STA311B

### 7.3 Write operation

Following the START condition the master sends a device select code with the RW bit set to 0. The STA311B acknowledges this and the writes for the byte of internal address.

After receiving the internal byte address the STA311B again responds with an acknowledgement.

### 7.3.1 Byte write

In the byte write mode the master sends one data byte, this is acknowledged by the Omega FFX core. The master then terminates the transfer by generating a STOP condition.

### 7.3.2 Multi-byte write

The multi-byte write modes can start from any internal address. The master generating a STOP condition terminates the transfer.

Figure 7. Write mode sequence

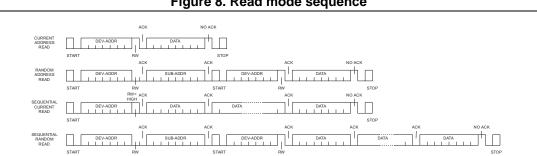

### 7.4 Read operation

### 7.4.1 Current address byte read

Following the START condition, the master sends a device select code with the RW bit set to 1. The STA311B acknowledges this and then responds by sending one byte of data. The master then terminates the transfer by generating a STOP condition.

### 7.4.2 Current address multi-byte read

The multi-byte read modes can start from any internal address. Sequential data bytes are read from sequential addresses within the STA311B. The master acknowledges each data byte read and then generates a STOP condition, terminating the transfer.

#### 7.4.3 Random address byte read

Following the START condition, the master sends a device select code with the RW bit set to 0. The STA311B acknowledges this and then the master writes the internal address byte. After receiving the internal byte address, the STA311B again responds with an acknowledgement. The master then initiates another START condition and sends the device select code with the RW bit set to 1. The STA311B acknowledges this and then responds by sending one byte of data. The master then terminates the transfer by generating a STOP condition.

**STA311B** I<sup>2</sup>C bus operation

#### 7.4.4 Random address multi-byte read

The multi-byte read mode can start from any internal address. Sequential data bytes are read from sequential addresses within the STA311B. The master acknowledges each data byte read and then generates a STOP condition, terminating the transfer.

Figure 8. Read mode sequence

Registers STA311B

# 8 Registers

# 8.1 Register summary

Table 11. Register summary

| Addr   | Name       | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

|--------|------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Config | uration    |       |       |       |       |       |       |       |       |

| 0x00   | CONFA      | COS1  | COS0  | DSPB  | IR1   | IR0   | MCS2  | MCS1  | MCS0  |

| 0x01   | ConfB      |       |       |       | SAIFB | SAI3  | SAI2  | SAI1  | SAI0  |

| 0x02   | ConfC      |       |       | SAOD4 | SAOFB | SAO3  | SAO2  | SAO1  | SAO0  |

| 0x03   | ConfD      | MPC   | CSZ4  | CSZ3  | CSZ2  | CSZ1  | CSZ0  | OM1   | ОМО   |

| 0x04   | ConfE      | C8BO  | С7ВО  | C6BO  | C5BO  | C4BO  | СЗВО  | C2BO  | C1BO  |

| 0x05   | ConfF      | PWMS2 | PWMS1 | PWMS0 | BQL   | PSL   | DEMP  | DRC   | HPB   |

| 0x06   | ConfG      | MPCV  | DCCV  | HPE   | AM2E  | AME   | COD   | SID   | PWMD  |

| 0x07   | ConfH      | ECLE  | LDTE  | BCLE  | IDE   | ZDE   | SVE   | ZCE   | NSBW  |

| 0x08   | Confl      | EAPD  |       |       |       |       |       |       | PSCE  |

| Volume | e control  | •     | •     | •     | •     | •     |       | •     | •     |

| 0x09   | MMUTE      |       |       |       |       |       |       |       | MMUTE |

| 0x0A   | Mvol       | MV7   | MV6   | MV5   | MV4   | MV3   | MV2   | MV1   | MV0   |

| 0x0B   | C1Vol      | C1V7  | C1V6  | C1V5  | C1V4  | C1V3  | C1V2  | C1V1  | C1V0  |

| 0x0C   | C2Vol      | C2V7  | C2V6  | C2V5  | C2V4  | C2V3  | C2V2  | C2V1  | C2V0  |

| 0x0D   | C3Vol      | C3V7  | C3V6  | C3V5  | C3V4  | C3V3  | C3V2  | C3V1  | C3V0  |

| 0x0E   | C4Vol      | C4V7  | C4V6  | C4V5  | C4V4  | C4V3  | C4V2  | C4V1  | C4V0  |

| 0x0F   | C5Vol      | C5V7  | C5V6  | C5V5  | C5V4  | C5V3  | C5V2  | C5V1  | C5V0  |

| 0x10   | C6Vol      | C6V7  | C6V6  | C6V5  | C6V4  | C6V3  | C6V2  | C6V1  | C6V0  |

| 0x11   | C7Vol      | C7V7  | C7V6  | C7V5  | C7V4  | C7V3  | C7V2  | C7V1  | C7V0  |

| 0x12   | C8Vol      | C8V7  | C8V6  | C8V5  | C8V4  | C8V3  | C8V2  | C8V1  | C8V0  |

| 0x13   | C1VTM<br>B | C1M   | C1VBP |       | C1VT4 | C1VT3 | C1VT2 | C1VT1 | C1VT0 |

| 0x14   | C2VTM<br>B | C2M   | C2VBP |       | C2VT4 | C2VT3 | C2VT2 | C2VT1 | C2VT0 |

| 0x15   | C3VTM<br>B | СЗМ   | C3VBP |       | C3VT4 | C3VT3 | C3VT2 | C3VT1 | C3VT0 |

| 0x16   | C4VTM<br>B | C4M   | C4VBP |       | C4VT4 | C4VT3 | C4VT2 | C4VT1 | C4VT0 |

| 0x17   | C5VTM<br>B | C5M   | C5VBP |       | C5VT4 | C5VT3 | C5VT2 | C5VT1 | C5VT0 |

| 0x18   | C6VTM<br>B | С6М   | C6VBP |       | C6VT4 | C6VT3 | C6VT2 | C6VT1 | C6VT0 |

26/102 DocID024340 Rev 1

STA311B Registers

Table 11. Register summary (continued)

|         | Table 11. Register summary (continued) |            |            |            |        |            |            |            |            |  |  |  |

|---------|----------------------------------------|------------|------------|------------|--------|------------|------------|------------|------------|--|--|--|

| Addr    | Name                                   | D7         | D6         | D5         | D4     | D3         | D2         | D1         | D0         |  |  |  |

| 0x19    | C7VTM<br>B                             | С7М        | C7VBP      |            | C7VT4  | C7VT3      | C7VT2      | C7VT1      | C7VT0      |  |  |  |

| 0x1A    | C8VTM<br>B                             | C8M        | C8VBP      |            | C8VT4  | C8VT3      | C8VT2      | C8VT1      | C8VT0      |  |  |  |

| Input r | napping                                |            |            |            |        |            |            |            |            |  |  |  |

| 0x1B    | C12im                                  |            | C2IM2      | C2IM1      | C2IM0  |            | C1IM2      | C1IM1      | C1IM0      |  |  |  |

| 0x1C    | C34im                                  |            | C4IM2      | C4IM1      | C4IM0  |            | C3IM2      | C3IM1      | C3IM0      |  |  |  |

| 0x1D    | C56im                                  |            | C6IM2      | C6IM1      | C6IM0  |            | C5IM2      | C5IM1      | C5IM0      |  |  |  |

| 0x1E    | C78im                                  |            | C8IM2      | C8IM1      | C8IM0  |            | C7IM2      | C7IM1      | C7IM0      |  |  |  |

| AutoM   | ode                                    | •          | •          | •          | •      | •          | •          | •          | •          |  |  |  |

| 0x1F    | Auto1                                  | AMDM       | AMGC2      | AMGC1      | AMGC0  | AMV1       | AMV0       | AMEQ1      | AMEQ0      |  |  |  |

| 0x20    | Auto2                                  | SUB        | RSS1       | RSS0       | CSS1   | CSS0       | FSS        | AMBMX<br>E | AMBMM<br>E |  |  |  |

| 0x21    | Auto3                                  | AMAM2      | AMAM1      | AMAM0      | AMAME  |            |            | MSA        | AMPS       |  |  |  |

| 0x22    | PreEQ                                  | XO2        | XO1        | XO0        | PEQ4   | PEQ3       | PEQ2       | PEQ1       | PEQ0       |  |  |  |

| 0x23    | Ageq                                   |            |            |            | AGEQ4  | AGEQ3      | AGEQ2      | AGEQ1      | AGEQ0      |  |  |  |

| 0x24    | Bgeq                                   |            |            |            | BGEQ4  | BGEQ3      | BGEQ2      | BGEQ1      | BGEQ0      |  |  |  |

| 0x25    | Cgeq                                   |            |            |            | CGEQ4  | CGEQ3      | CGEQ2      | CGEQ1      | CGEQ0      |  |  |  |

| 0x26    | Dgeq                                   |            |            |            | DGEQ4  | DGEQ3      | DGEQ2      | DGEQ1      | DGEQ0      |  |  |  |

| 0x27    | Egeq                                   |            |            |            | EGEQ4  | EGEQ3      | EGEQ2      | EGEQ1      | EGEQ0      |  |  |  |

| Proces  | ssing loop                             | )          |            |            |        |            |            |            |            |  |  |  |

| 0x28    | BQlp                                   | C8BLP      | C7BLP      | C6BLP      | C5BLP  | C4BLP      | C3BLP      | C2BLP      | C1BLP      |  |  |  |

| 0x29    | MXIp                                   | C8MXL<br>P | C7MXL<br>P | C6MXL<br>P | C5MXLP | C4MXL<br>P | C3MXL<br>P | C2MXL<br>P | C1MXLP     |  |  |  |

| Proces  | sing bypa                              | ass        | •          | •          |        | •          | •          | •          |            |  |  |  |

| 0x2A    | EQbp                                   | C8EQB<br>P | C7EQB<br>P | C6EQB<br>P | C5EQB  | C4EQB<br>P | C3EQB<br>P | C2EQB<br>P | C1EQBP     |  |  |  |

| 0x2B    | ToneBP                                 | С8ТСВ      | С7ТСВ      | С6ТСВ      | C5TCB  | C4TCB      | СЗТСВ      | C2TCB      | C1TCB      |  |  |  |

| Tone c  | ontrol                                 | •          | •          | •          | •      | •          | •          | •          | •          |  |  |  |

| 0x2C    | Tone                                   | TTC3       | TTC2       | TTC1       | TTC0   | BTC3       | BTC2       | BTC1       | BTC0       |  |  |  |

| Dynam   | nics contro                            | ol         | 1          | 1          | I      | ı          | ı          | 1          | l          |  |  |  |

| 0x2D    | C1234ls                                | C4LS1      | C4LS0      | C3LS1      | C3LS0  | C2LS1      | C2LS0      | C1LS1      | C1LS0      |  |  |  |

| 0x2E    | C5678ls                                | C8LS1      | C8LS0      | C7LS1      | C7LS0  | C6LS1      | C6LS0      | C5LS1      | C5LS0      |  |  |  |

| 0x2F    | L1ar                                   | L1A3       | L1A2       | L1A1       | L1A0   | L1R3       | L1R2       | L1R1       | L1R0       |  |  |  |

| 0x30    | L1atrt                                 | L1AT3      | L1AT2      | L1AT1      | L1AT0  | L1RT3      | L1RT2      | L1RT1      | L1RT0      |  |  |  |

| 0x31    | L2ar                                   | L2A3       | L2A2       | L2A1       | L2A0   | L2R3       | L2R2       | L2R1       | L2R0       |  |  |  |

DocID024340 Rev 1

27/102

Registers STA311B

Table 11. Register summary (continued)

| Addr                                    | Name      | D7          | D6         | D5         | D4     | D3         | D2         | D1    | D0    |  |

|-----------------------------------------|-----------|-------------|------------|------------|--------|------------|------------|-------|-------|--|

| 0x32                                    | L2atrt    | L2AT3       | L2AT2      | L2AT1      | L2AT0  | L2RT3      | L2RT2      | L2RT1 | L2RT0 |  |

| PWM c                                   | utput tim | ing         |            |            |        |            |            |       | •     |  |

| 0x33                                    | C12ot     |             | C2OT2      | C2OT1      | C2OT0  |            | C1OT2      | C1OT1 | C1OT0 |  |

| 0x34                                    | C34ot     |             | C4OT2      | C4OT1      | C4OT0  |            | C3OT2      | C3OT1 | C3OT0 |  |

| 0x35                                    | C56ot     |             | C6OT2      | C6OT1      | C6OT0  |            | C5OT2      | C5OT1 | C5OT0 |  |

| 0x36                                    | C78ot     |             | C8OT2      | C8OT1      | C8OT0  |            | C7OT2      | C7OT1 | C7OT0 |  |

| I <sup>2</sup> S output channel mapping |           |             |            |            |        |            |            |       |       |  |

| 0x37                                    | C12om     |             | C2OM2      | C2OM1      | C2OM0  |            | C1OM2      | C1OM1 | C1OM0 |  |

| 0x38                                    | C34om     |             | C4OM2      | C4OM1      | C4OM0  |            | C3OM2      | C3OM1 | СЗОМО |  |

| 0x39                                    | C56om     |             | C6OM2      | C6OM1      | C6OM0  |            | C5OM2      | C5OM1 | C5OM0 |  |

| 0x3A                                    | C78om     |             | C8OM2      | C8OM1      | C8OM0  |            | C7OM2      | C7OM1 | С7ОМ0 |  |

| User-d                                  | efined co | efficient F | RAM        | •          |        | •          | •          | •     | 1     |  |

| 0x3B                                    | Cfaddr1   |             |            |            |        |            |            | CFA9  | CFA8  |  |

| 0x3C                                    | Cfaddr2   | CFA7        | CFA6       | CFA5       | CFA4   | CFA3       | CFA2       | CFA1  | CFA0  |  |

| 0x3D                                    | B1cf1     | C1B23       | C1B22      | C1B21      | C1B20  | C1B19      | C1B18      | C1B17 | C1B16 |  |

| 0x3E                                    | B1cf2     | C1B15       | C1B14      | C1B13      | C1B12  | C1B11      | C1B10      | C1B9  | C1B8  |  |

| 0x3F                                    | B1cf3     | C1B7        | C1B6       | C1B5       | C1B4   | C1B3       | C1B2       | C1B1  | C1B0  |  |

| 0x40                                    | B2cf1     | C2B23       | C2B22      | C2B21      | C2B20  | C2B19      | C2B18      | C2B17 | C2B16 |  |

| 0x41                                    | B2cf2     | C2B15       | C2B14      | C2B13      | C2B12  | C2B11      | C2B10      | C2B9  | C2B8  |  |

| 0x42                                    | B2cf3     | C2B7        | C2B6       | C2B5       | C2B4   | C2B3       | C2B2       | C2B1  | C2B0  |  |

| 0x43                                    | A1cf1     | C3B23       | C3B22      | C3B21      | C3B20  | C3B19      | C3B18      | C3B17 | C3B16 |  |

| 0x44                                    | A1cf2     | C3B15       | C3B14      | C3B13      | C3B12  | C3B11      | C3B10      | C3B9  | C3B8  |  |

| 0x45                                    | A1cf3     | C3B7        | C3B6       | C3B5       | C3B4   | C3B3       | C3B2       | C3B1  | C3B0  |  |

| 0x46                                    | A2cf1     | C4B23       | C4B22      | C4B21      | C4B20  | C4B19      | C4B18      | C4B17 | C4B16 |  |

| 0x47                                    | A2cf2     | C4B15       | C4B14      | C4B13      | C4B12  | C4B11      | C4B10      | C4B9  | C4B8  |  |

| 0x48                                    | A2cf3     | C4B7        | C4B6       | C4B5       | C4B4   | C4B3       | C4B2       | C4B1  | C4B0  |  |

| 0x49                                    | B0cf1     | C5B23       | C5B22      | C5B21      | C5B20  | C5B19      | C5B18      | C5B17 | C5B16 |  |

| 0x4A                                    | B0cf2     | C5B15       | C5B14      | C5B13      | C5B12  | C5B11      | C5B10      | C5B9  | C5B8  |  |

| 0x4B                                    | B0cf3     | C5B7        | C5B6       | C5B5       | C5B4   | C5B3       | C5B2       | C5B1  | C5B0  |  |

| 0x4C                                    | Cfud      |             |            |            |        |            |            | WA    | W1    |  |

| 0x4D                                    | MPCC1     | MPCC1<br>5  | MPCC1<br>4 | MPCC1<br>3 | MPCC12 | MPCC1<br>1 | MPCC1<br>0 | MPCC9 | MPCC8 |  |

| 0x4E                                    | MPCC2     | MPCC7       | MPCC6      | MPCC5      | MPCC4  | MPCC3      | MPCC2      | MPCC1 | MPCC0 |  |

| 0x4F                                    | DCC1      | DCC15       | DCC14      | DCC13      | DCC12  | DCC11      | DCC10      | DCC9  | DCC8  |  |

| 0x50                                    | DCC2      | DCC7        | DCC6       | DCC5       | DCC4   | DCC3       | DCC2       | DCC1  | DCC0  |  |

28/102 DocID024340 Rev 1

STA311B Registers

Table 11. Register summary (continued)

|         | Table 11. Register summary (continued) |              |            |              |                      |                     |            |            |        |  |  |  |  |

|---------|----------------------------------------|--------------|------------|--------------|----------------------|---------------------|------------|------------|--------|--|--|--|--|

| Addr    | Name                                   | D7           | D6         | D5           | D4                   | D3                  | D2         | D1         | D0     |  |  |  |  |

| 0x51    | PSC1                                   | RCV11        | RCV10      | RCV9         | RCV8                 | RCV7                | RCV6       | RCV5       | RCV4   |  |  |  |  |

| 0x52    | PSC2                                   | RCV3         | RCV2       | RCV1         | RCV0                 | CNV11               | CNV10      | CNV9       | CNV8   |  |  |  |  |

| 0x53    | PSC3                                   | CNV7         | CNV6       | CNV5         | CNV4                 | CNV3                | CNV2       | CNV1       | CNV0   |  |  |  |  |

| I2S rec | ombinatio                              | n interfac   | e          |              |                      | •                   | •          | •          |        |  |  |  |  |

| 0x5D    | RCTR1                                  | Boost6d<br>b |            |              | I <sup>2</sup> S_byp | l <sup>2</sup> S_en |            |            |        |  |  |  |  |

| 0x5E    | PDMCT                                  | AdvM6        | AdvM5      | AdvM4        | AdvM3                | AdvM2               | AdvM1      |            | •      |  |  |  |  |

| 0x5F    | RCTR2                                  |              | bypRM1     | CH1GG[5      | 5:0]                 |                     |            |            |        |  |  |  |  |

| 0x60    | RCTR3                                  |              | bypRM2     | 2 CH2GG[5:0] |                      |                     |            |            |        |  |  |  |  |

| 0x61    | RCTR4                                  |              | bypRM3     | CH3GG[5:0]   |                      |                     |            |            |        |  |  |  |  |

| 0x62    | RCTR5                                  |              | LP1en      | CH1NCA       | [5:0]                |                     |            |            |        |  |  |  |  |

| 0x63    | RCTR6                                  |              | LP2en      | CH2NCA       | [5:0]                |                     |            |            |        |  |  |  |  |

| 0x64    | RCTR7                                  |              | LP3en      | CH3NCA       | [5:0]                |                     |            |            |        |  |  |  |  |

| 0x65    | RCTR8                                  |              |            | CH1TH_I      | N[5:0]               |                     |            |            |        |  |  |  |  |

| 0x66    | RCTR9                                  |              |            | CH2TH_I      | N[5:0]               |                     |            |            |        |  |  |  |  |

| 0x67    | RCTR1<br>0                             |              |            | CH3TH_I      | N[5:0]               |                     |            |            |        |  |  |  |  |

| 0x68    | RCTR11                                 |              |            | CH1TH_I      | H[5:0]               |                     |            |            |        |  |  |  |  |

| 0x69    | RCTR1<br>2                             |              |            | CH2TH_I      | H[5:0]               |                     |            |            |        |  |  |  |  |

| 0x6A    | RCTR1<br>3                             |              |            | CH3TH_I      | H[5:0]               |                     |            |            |        |  |  |  |  |

| Extend  | led DRC c                              | onfigurat    | ion regist | ers          |                      |                     |            |            |        |  |  |  |  |

| 0x6B    | nL1at                                  |              | L1AT6      | L1AT5        | L1AT4                | L1AT3               | L1AT2      | L1AT1      | L1AT0  |  |  |  |  |

| 0x6C    | nL2at                                  |              | L2AT6      | L2AT5        | L2AT4                | L2AT3               | L2AT2      | L2AT1      | L2AT0  |  |  |  |  |

| 0x6D    | nL1rt                                  |              |            | L1RT5        | L1RT4                | L1RT3               | L1RT2      | L1RT1      | L1RT0  |  |  |  |  |

| 0x6E    | nL2rt                                  |              |            | L2RT5        | L2RT4                | L2RT3               | L2RT2      | L2RT1      | L2RT0  |  |  |  |  |

| 0x6F    | 0Mute                                  | RMSZS<br>2   | RMSZS<br>1 | RMSZS<br>0   | ZMTHS2               | ZMTHS<br>1          | ZMTHS<br>0 | ZMHYS<br>1 | ZMHYS0 |  |  |  |  |

| 0x70    |                                        | RMS2         | RMS1       | RMS0         |                      |                     |            |            | FXLRC0 |  |  |  |  |

| Clock   | manager o                              | configurat   | ion/status | registers    | 5                    |                     | •          | •          |        |  |  |  |  |

| 0x71    | pllfrac1                               | PLFI15       | PLFI14     | PLFI13       | PLFI12               | PLFI11              | PLFI10     | PLFI9      | PLFI8  |  |  |  |  |

| 0x72    | pllfrac0                               | PLFI7        | PLFI6      | PLFI5        | PLFI4                | PLFI3               | PLFI2      | PLFI1      | PLFI0  |  |  |  |  |

| 0x73    | pll div                                | PLLDD1       | PLLDD0     | PLLND5       | PLLND4               | PLLND3              | PLLND2     | PLLND1     | PLLND0 |  |  |  |  |

| 0x74    | pll conf0                              | PDPDC        | PLLFC      | PLSTR<br>B   | PLSTBB               | PLIFD3              | PLIFD2     | PLIFD1     | PLIFD0 |  |  |  |  |

DocID024340 Rev 1

29/102

Registers STA311B

Table 11. Register summary (continued)

| Addr                 | Name        | D7         | D6         | D5         | D4     | D3     | D2         | D1     | D0         |  |  |

|----------------------|-------------|------------|------------|------------|--------|--------|------------|--------|------------|--|--|

| 0x75                 | pll conf1   |            |            |            |        | PLLBYP | PLLDP<br>R | LOWEN  | BST32K     |  |  |

| 0x76                 | pll stat    |            |            |            |        | PLLBYS | PLLPDS     | оѕсок  | LOWCK<br>S |  |  |

| Biquad configuration |             |            |            |            |        |        |            |        |            |  |  |

| 0x77                 | CBQ1        | EBQ3_1     | EBQ3_0     | EBQ2_1     | EBQ2_0 | EBQ1_1 | EBQ1_0     | EBQ0_0 | EBQ0_0     |  |  |

| 0x78                 | CBQ2        | EBQ7_1     | EBQ7_0     | EBQ6_1     | EBQ6_0 | EBQ5_1 | EBQ5_0     | EBQ4_0 | EBQ4_0     |  |  |

| 0x79                 | CBQ3        |            |            |            | nshen  | EBQ9_1 | EBQ9_0     | EBQ8_0 | EBQ8_0     |  |  |

| RMS s                | tatus regi: | sters      |            |            |        |        |            |        |            |  |  |

| 0x7A                 | rmsZMH      | RZM15      | RZM14      | RZM13      | RZM12  | RZM11  | RZM10      | RZM9   | RZM8       |  |  |

| 0X7B                 | rmsZML      | RZM7       | RZM6       | RZM5       | RZM4   | RZM3   | RZM2       | RZM1   | RZM0       |  |  |

| 0X7C                 | rmsPOH      | RPO15      | RPO14      | RPO13      | RPO12  | RPO11  | RPO10      | RPO9   | RPO8       |  |  |

| 0X7D                 | rmsPOL      | RPO7       | RPO6       | RPO5       | RPO4   | RPO3   | RPO2       | RPO1   | RPO0       |  |  |

| Tristate             | e startup/s | shutdown   | pop remo   | val signa  | ls     |        |            |        |            |  |  |

| 0x80                 | DPT         |            |            |            | DPT4   | DPT3   | DPT2       | DPT1   | DPT0       |  |  |

| 0x81                 | CFR129      | RL3        | RL2        | RL1        | RL0    | RD     | SID1       | FBYP   | RTP        |  |  |

| 0x82                 | TSDLY1      | UDDT1<br>5 | UDDT1<br>4 | UDDT1<br>3 | UDDT12 | UDDT11 | UDDT1<br>0 | UDDT9  | UDDT8      |  |  |

| 0x83                 | TSDLY2      | UDDT7      | UDDT6      | UDDT5      | UDDT4  | UDDT3  | UDDT2      | UDDT1  | UDDT0      |  |  |

30/102 DocID024340 Rev 1

Downloaded from Arrow.com.

STA311B Registers

### 8.2 Register description

### 8.2.1 Configuration register A (0x00)

| D7   | D6   | D5   | D4  | D3  | D2   | D1   | D0   |

|------|------|------|-----|-----|------|------|------|

| COS1 | COS0 | DSPB | IR1 | IR0 | MCS2 | MCS1 | MCS0 |

| 1    | 0    | 0    | 0   | 0   | 0    | 1    | 1    |

| Bit | RW | RST | Name | Description                                                                                          |

|-----|----|-----|------|------------------------------------------------------------------------------------------------------|

| 0   | RW | 1   | MCS0 |                                                                                                      |

| 1   | RW | 1   | MCS1 | Master clock select: selects the ratio between the input I2S sampling frequency and the input clock. |

| 2   | RW | 0   | MCS2 | 3 3 1 2 3 4 2 3 4 3 4 3 4 3 4 3 4 3 4 3 4 3 4                                                        |

The STA311B supports sample rates of 32 kHz, 44.1 kHz, 48 kHz, 88.2 kHz, 96 kHz, 176.4 kHz, 192 kHz, 2.8224 MHz DSD. Therefore the internal clocks are:

- 65.536 MHz for 32 kHz

- 90.3168 MHz for 44.1 kHz, 88.2 kHz, 176.4 kHz, and DSD

- 98.304 MHz for 48 kHz, 96 kHz, 192 kHz

The external clock frequency provided to the XTI or BICKI pin (depending on the MCS settings) must be a multiple of the input sampling frequency (fs). The relationship between the input clock (either XTI or BICKI) and the input sampling rate is determined by both the MCS[2:0] and the IR[1:0] (input rate) register bits in normal mode, if the Fs autodetect mode has been set, the IR[1:0] parameter and the BST32K bit will be set automatically (see Fs autodetection on page 32). The MCS[2:0] bits determine the PLL factor generating the internal clock and the IR[1:0] bits determine the oversampling ratio used internally.

If XTI input is not used, related pin must be tied to GND.

To get 98.304 MHz of system clock frequency when fs = 32 kHz, an extra oversampling factor is available by setting the BST32K bit in the 0x75 register (see *Clock manager configuration register (0x75) on page 93*).

|                              |    | MCS[2:0] |       |        |        |        |        |        |  |

|------------------------------|----|----------|-------|--------|--------|--------|--------|--------|--|

| Input sampling rate fs (kHz) |    | віскі    |       | хті    |        |        |        |        |  |

|                              |    | 111      | 110   | 10-    | 011    | 010    | 001    | 000    |  |

| 32, 44.1, 48                 | 00 | 64*fs    | na    | 128*fs | 256*fs | 384*fs | 512*fs | 768*fs |  |

| 88.2, 96                     | 01 | 64*fs    | 32*fs | 64*fs  | 128*fs | 192*fs | 256*fs | 384*fs |  |

| 176.4, 192                   | 10 | 64*fs    | 32*fs | 64*fs  | 128*fs | 192*fs | 256*fs | na     |  |

| DSD/PDM                      | 11 | 2*fs     | 2*fs  | 2*fs   | 4*fs   | 6*fs   | 8*fs   | 12*fs  |  |

Registers STA311B

#### Fs autodetection

When FXLRC0 = '0' (see 0x70 register), the autodetection function is disabled, IR[1:0] and BST32K must be set via I<sup>2</sup>C. When FXLRC0 = '1' the autodetection function is enabled, then IR and BST32K will be set automatically based on Fs. Before and after enabling the function m, LRCKI must be stable for at least 3 cycles with a fixed Fs as reference. After 3 fixed Fs cycles when the function has been enabled, the real Fs can be fed to LRCKI.

### Interpolation ratio select

| Bit | RW | RST | Name | Description                                                          |  |  |  |

|-----|----|-----|------|----------------------------------------------------------------------|--|--|--|

| 3   | RW | 0   | IR0  | Interpolation ratio select: selects internal                         |  |  |  |

| 4   | RW | 0   | IR1  | interpolation ratio based on input I <sup>2</sup> S sample frequency |  |  |  |

The STA311B has variable interpolation (oversampling) settings such that internal processing and FFX output rates remain consistent. The first processing block interpolates by either 4 times, 2 times, or 1 time (pass-through).