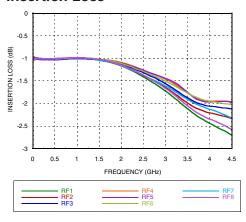

#### **Insertion Loss**

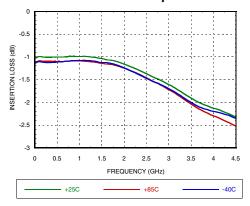

### Insertion Loss vs. Temperature

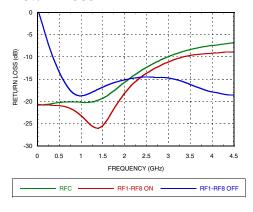

#### **Return Loss**

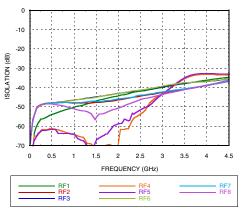

### Isolation

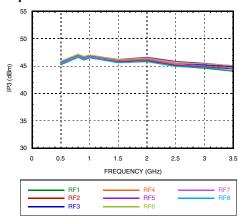

### Input IP3

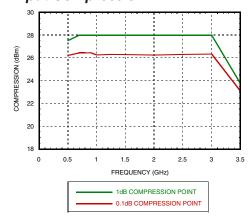

### Input Compression

## Bias Voltage & Current

| Vdd Range = +5 Vdc ± 10% |                 |                 |  |

|--------------------------|-----------------|-----------------|--|

| Vdd (Vdc)                | Idd (Typ.) (mA) | Idd (Max.) (mA) |  |

| +5                       | 4.5             | 7.5             |  |

## **TTL/CMOS Control Voltages**

| State | Bias Condition              |

|-------|-----------------------------|

| Low   | 0 to +0.8 Vdc @ <1 μA Typ.  |

| High  | +2.0 to +5 Vdc @ 60 μA Typ. |

#### **Truth Table**

| Control Input |      | Signal Path State |           |

|---------------|------|-------------------|-----------|

| А             | В    | С                 | RFCOM to: |

| Low           | Low  | Low               | RF1       |

| High          | Low  | Low               | RF2       |

| Low           | High | Low               | RF3       |

| High          | High | Low               | RF4       |

| Low           | Low  | High              | RF5       |

| High          | Low  | High              | RF6       |

| Low           | High | High              | RF7       |

| High          | High | High              | RF8       |

NOTE.

DC Blocking capacitors are required at ports RFC and RF1, 2, 3, 4, 5, 6, 7, 8.

## **Absolute Maximum Ratings**

| Bias Voltage Range (Port Vdd)                         | +7.0 Vdc                    |

|-------------------------------------------------------|-----------------------------|

| Control Voltage Range (A, B, C)                       | -0.5V to Vdd +1Vdc          |

| Channel Temperature                                   | 150 °C                      |

| Thermal Resistance (channel to package ground paddle) |                             |

| Through Path                                          | 183 °C/W                    |

| Termination Path                                      | 274 °C/W                    |

| Tommaton Fath                                         | 20,                         |

| Storage Temperature                                   | -65 to +150 °C              |

| Operating Temperature                                 | -40 to +85 °C               |

| Maximum Input Power (Vdd = +5V)                       |                             |

| Through Path                                          | +20 dBm (0.05 - 0.5 GHz)    |

| Throught aut                                          | , , ,                       |

|                                                       | +25 dBm (0.5 - 3.5 GHz)     |

| Terminated Path                                       | +20 dBm (0.05 - 0.5 GHz)    |

|                                                       | +23.5 dBm (0.5 - 3.5 GHz)   |

|                                                       | 120.0 dBiii (0.0 0.0 di i2) |

| ESD Sensitivity (HBM)                                 | Class 1A                    |

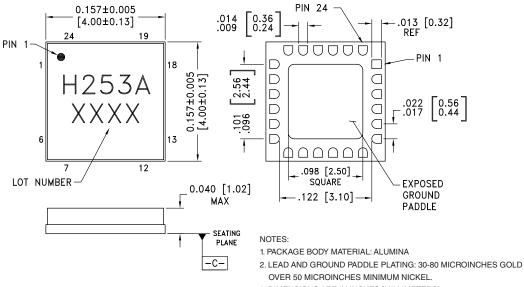

## **Outline Drawing**

#### **BOTTOM VIEW**

- 3. DIMENSIONS ARE IN INCHES [MILLIMETERS].

- 4. LEAD SPACING TOLERANCE IS NON-CUMULATIVE.

- 5. PACKAGE WARP SHALL NOT EXCEED 0.05mm DATUM -C-  $\,$

- ${\it 6.}\,{\it ALL}$  GROUND LEADS AND GROUND PADDLE MUST BE SOLDERED TO PCB RF GROUND.

# **Pin Descriptions**

| Pin Number                                | Function           | Description                                                                       | Interface Schematic |

|-------------------------------------------|--------------------|-----------------------------------------------------------------------------------|---------------------|

| 1, 3, 5, 7, 12, 14, 16,<br>18, 20, 21, 23 | GND                | Package bottom has exposed metal paddle that must also be connected to RF ground. | O CND               |

| 2, 4, 6, 13, 15,<br>17, 19, 22, 24        | RF1 - RF8<br>& RFC | This pin is DC coupled and matched to 50 Ohms.  Blocking capacitors are required. |                     |

| 8                                         | Vdd                | Supply Voltage +5 Vdc ±10%                                                        | Vdd 0               |

| 9                                         | CTLC               |                                                                                   | Vdd                 |

| 10                                        | CTLB               | See truth table and control voltage table.                                        | <u> </u>            |

| 11                                        | CTLA               |                                                                                   | <u> </u>            |

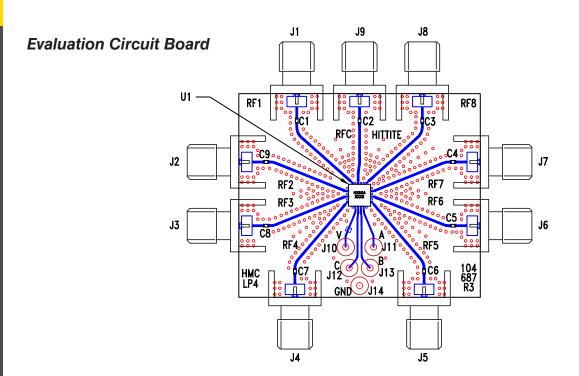

### List of Materials for Evaluation PCB EV1HMC253ALC4 [1]

| Item      | Description                 |

|-----------|-----------------------------|

| J1 - J9   | PCB Mount SMA Connector     |

| J10 - J14 | DC Pin                      |

| C1 - C9   | 100 pF Capacitor, 0402 Pkg. |

| U1        | HMC253ALC4 SP8T Switch      |

| PCB [2]   | 104687 Eval Board           |

[1] Reference this number when ordering complete evaluation PCB

[2] Circuit Board Material: Rogers 4350

The circuit board used in the application should be generated with proper RF circuit design techniques. Signal lines at the RF ports should have 50 ohm impedance while the package ground leads should be connected directly to the ground plane similar to that shown above. A sufficient number of via holes should be used to connect the top and bottom ground planes. The evaluation circuit board shown above is available from Hittite Microwave Corporation upon request.