# **Contents**

| Pinc | out                               | . 3 |

|------|-----------------------------------|-----|

| Турі | ical Circuits                     | . 4 |

| Con  | figuring the CY8CMBR2016          | . 8 |

| Devi | ice Features                      | . 8 |

|      | CapSense Buttons                  | . 8 |

|      | SmartSense Auto-Tuning            | . 8 |

|      | Flanking Sensor Suppression (FSS) | . 8 |

|      | Key Scan Interface                | . 8 |

|      | Truth Table Output                | 10  |

|      | Encoded 4-bit Output              |     |

|      | Buzzer Signal Output              | 10  |

|      | Interrupt Line                    | 10  |

|      | Button Auto Reset                 | 10  |

|      | Output Select                     | 11  |

|      | Scan Rate                         | 11  |

|      | Sensitivity                       | 11  |

|      | System Diagnostics                | 11  |

|      | Serial Debug Data Out             | 13  |

|      | Power Consumption                 |     |

| and  | Device Operating Modes            | 15  |

|      | Response Time                     | 16  |

|      | Deep Sleep Mode                   | 16  |

| Layout Guidelines and Best Practices    | 17 |

|-----------------------------------------|----|

| Sample Layout                           |    |

| Electrical Specifications               | 21 |

| DC Electrical Characteristics           | 21 |

| AC Electrical Specifications            | 23 |

| CapSense Specification                  |    |

| Package Information                     |    |

| Ordering Information                    |    |

| Ordering Code Definitions               | 25 |

| Appendix                                |    |

| Acronyms                                | 27 |

| Document Conventions                    |    |

| Units of Measure                        | 27 |

| Document History Page                   | 28 |

| Sales, Solutions, and Legal Information |    |

| Worldwide Sales and Design Support      | 29 |

| Products                                |    |

| PSoC® Solutions                         | 29 |

| Cypress Developer Community             | 29 |

| Technical Support                       |    |

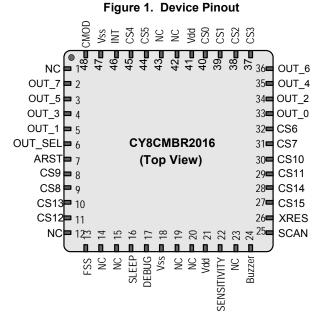

# **Pinout**

Table 1. Pinout for the Device

| Pin | Pin Name        | Type | Description                                                             |

|-----|-----------------|------|-------------------------------------------------------------------------|

| 1   | NC              | _    | No connection                                                           |

| 2   | OUT_7           | DO   | READ_3/TT_ROW_3/EO_3/<br>FMEA_CLK line - Output port<br>interface pin 7 |

| 3   | OUT_5           | DO   | READ_1/TT_ROW_1/EO_1 -<br>Output port interface pin 5                   |

| 4   | OUT_3           | DIO  | SCAN_3/TT_COL_3 - Output port interface pin 3                           |

| 5   | OUT_1           | DIO  | SCAN_1/TT_COL_1 - Output port interface pin 1                           |

| 6   | OUT_SEL         | Al   | Selects the output interface                                            |

| 7   | ARST            | Al   | Controls button auto reset period                                       |

| 8   | CS9             | Al   | CapSense button 9                                                       |

| 9   | CS8             | Al   | CapSense button 8                                                       |

| 10  | CS13            | Al   | CapSense button 13                                                      |

| 11  | CS12            | Al   | CapSense button 12                                                      |

| 12  | NC              | _    | Reserved pin                                                            |

| 13  | FSS             | DI   | Controls FSS feature                                                    |

| 14  | NC              | _    | No connection                                                           |

| 15  | NC              | _    | No connection                                                           |

| 16  | SLEEP           | DI   | Controls entry/exit to Deep Sleep                                       |

| 17  | DEBUG           | DO   | Serial Debug Data out from the device (UART TX8 line)                   |

| 18  | $V_{SS}$        | _    | GND                                                                     |

| 19  | NC              | _    | No connection                                                           |

| 20  | NC              | -    | No connection                                                           |

| 21  | V <sub>DD</sub> | -    | Power supply                                                            |

| 22  | SENSITIVITY     | Al   | Selects the sensitivity of the CS system                                |

| 23  | NC              | _    | Reserved for shield out                                                 |

| 24  | BUZZER          | DO   | Connects to DC Buzzer for audio feedback                                |

| 25  | SCAN            | Al   | Controls the sleep rate of the system                                   |

| 26  | XRES            | DI   | System reset pin                                                        |

| 27  | CS15            | Al   | CapSense button 15                                                      |

| 28  | CS14            | Al   | CapSense button 14                                                      |

| 29  | CS11            | Al   | CapSense button 11                                                      |

| 30  | CS10            | Al   | CapSense button 10                                                      |

| 31  | CS7             | Al   | CapSense button 7                                                       |

| 32  | CS6             | Al   | CapSense button 6                                                       |

| 33  | OUT_0           | DIO  | SCAN_0/TT_COL_0 - Output port interface pin 0                           |

| 34 | OUT_2            | DIO | SCAN_2/TT_COL_2 - Output port interface pin 2                    |

|----|------------------|-----|------------------------------------------------------------------|

| 35 | OUT_4            | DO  | READ_0/TT_ROW_0/EO_0 - Output port interface pin 4               |

| 36 | OUT_6            | DO  | READ_2/TT_ROW_2/EO_2/FMEA_D<br>ATA - Output port interface pin 6 |

| 37 | CS3              | AI  | CapSense button 3                                                |

| 38 | CS2              | Al  | CapSense button 2                                                |

| 39 | CS1              | Al  | CapSense button 1                                                |

| 40 | CS0              | Al  | CapSense button 0                                                |

| 41 | Vdd              | _   | Power supply                                                     |

| 42 | NC               | -   | No connection                                                    |

| 43 | NC               | -   | No connection                                                    |

| 44 | CS5              | Al  | CapSense button 5                                                |

| 45 | CS4              | Al  | CapSense button 4                                                |

| 46 | INT              | DO  | Interrupt line to Host                                           |

| 47 | Vss              | _   | GND                                                              |

| 48 | C <sub>MOD</sub> | AI  | Modulator capacitor, 2.2 nF                                      |

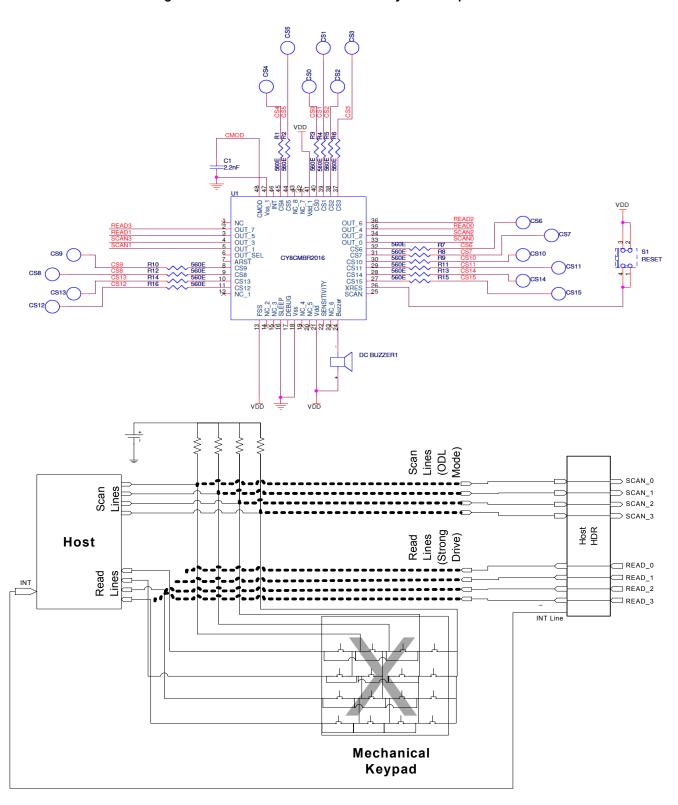

# **Typical Circuits**

Figure 2. Schematic 1: 16 Buttons with Key Scan Output Mode

In Schematic 1, CY8CMBR2016 is configured as follows:

- 16 CapSense buttons

- Key Scan Interface

- Continuous scan mode

- High sensitivity for all buttons

- FSS enabled

- Button Auto Reset disabled

- Serial Debug Data Out disabled

- DC buzzer output

- Reset button

- Interrupt line output

Document Number: 001-67921 Rev. \*G Page 5 of 29

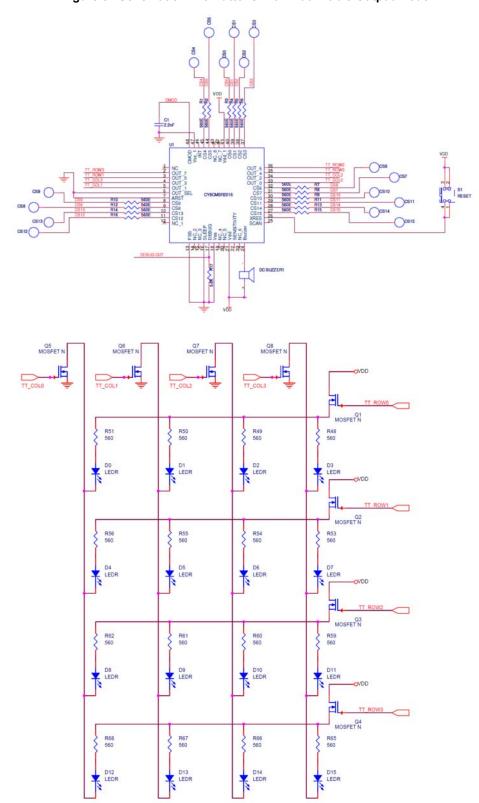

Figure 3. Schematic 2: 16 Buttons with Truth Table Output Mode

In Schematic 2, CY8CMBR2016 is configured as follows:

- 16 CapSense buttons

- Truth Table Output configured to drive LEDs

- Continuous Scan mode

- High sensitivity for all buttons

- FSS disabled

- Button Auto Reset enable, with a period of 5 seconds

- Serial Debug Data Out enabled

- DC buzzer output

- Reset button

- Interrupt line output

Document Number: 001-67921 Rev. \*G Page 7 of 29

# Configuring the CY8CMBR2016

The CY8CMBR2016 device features are configured using external resistors. The resistors on the hardware configurable pins are determined by the device upon power-on. The Appendix on page 26 gives the matrix of features enabled using different external resistor configurations.

#### **Device Features**

Table 2. Device Feature List

| Feature                              | Description/Use                                                                       |

|--------------------------------------|---------------------------------------------------------------------------------------|

| 16 CapSense Buttons                  | Mechanical button/keypad replacement                                                  |

| Flanking Sensor<br>Suppression (FSS) | Helps in distinguishing closely spaced buttons                                        |

| Key Scan Interface                   | Mechanical matrix replacement                                                         |

| Truth Table Output                   | Easy to decode truth table based output mode                                          |

| 4-bit Encoded Output                 | Fewer pins needed to output button status                                             |

| Button Auto Reset                    | Prevents buttons from getting stuck during run time                                   |

| Scan/Sleep Rate                      | Configures the device based on power needs                                            |

| Configurable Sensitivity             | Selects the sensitivity for the system – minimum change in capacitance to be detected |

| Deep Sleep                           | Reduce power consumption by hibernating the device                                    |

| System Diagnostics                   | Supports for production testing and debugging                                         |

### CapSense Buttons

- Device supports up to 16 CapSense Buttons.

- Ground the CSx Pin to disable CapSense input.

- 2.2 nF (± 10%) capacitor should be connected on C<sub>MOD</sub> pin for proper CapSense operation.

- The parasitic capacitance (C<sub>P</sub>) of each button must be less than 40 pF for proper CapSense operation.

#### **SmartSense Auto-Tuning**

- Device supports auto-tuning of CapSense button parameters.

- No manual tuning required; all parameters are automatically tuned by the device.

- Compensates printed circuit board (PCB) variations, device process variations, and PCB vendor changes.

- Ensures portability of the user interface design.

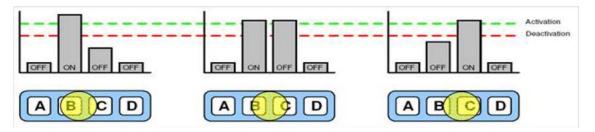

### Flanking Sensor Suppression (FSS)

- Helps to distinguish closely spaced buttons.

- Also used in situations when a button can produce opposite effects. For example, an interface with two buttons for brightness control (UP or DOWN).

- FSS action can be explained for the following different scenarios:

- When only one button is touched, it is reported as ON.

- □ When more than one button is detected as ON and previously one of those buttons was touched, then the previously touched button is reported as ON. (Refer to Figure 4.)

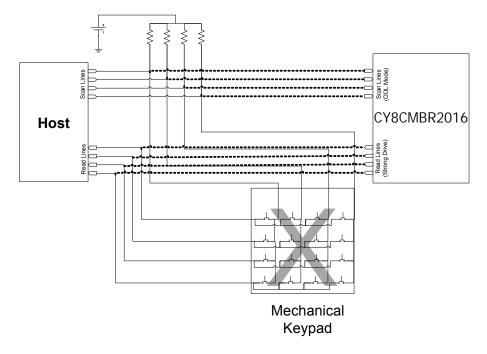

#### **Key Scan Interface**

- Mimics legacy mechanical keypads Four SCAN lines (I/P) and four READ lines (O/P)

- Reads the SCAN lines and updates the READ lines based on the button status (Refer to Figure 5).

- 'Plug' n 'Play' replacement for mechanical keypads.

- When buttons are disabled or found to be invalid, Table 3 helps identifying the scan and read lines.

- The unused SCAN lines should be connected to  $V_{DD}$ , typically with a 5.6-k $\Omega$  resistor

- OUT0 to OUT3 in the pin out form the SCAN lines and OUT4 to OUT7 form the READ lines

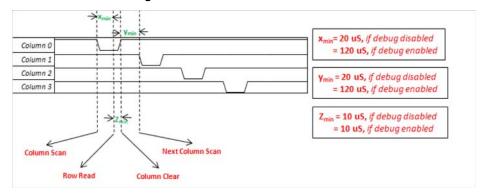

- Refer to Figure 6 for SCAN line waveform details.

Table 3. Key Scan interface Selection based on # of Buttons

| No. of Buttons | SCAN × READ Lines | Scan Lines   |

|----------------|-------------------|--------------|

| (>12)          | 4 × 4             | OUT0 to OUT3 |

| (<=12) && (>8) | 3 × 4             | OUT0 to OUT2 |

| (<=8) && (>4)  | 2 × 4             | OUT0 to OUT1 |

| (<=4)          | 1 × 4             | OUT0         |

Document Number: 001-67921 Rev. \*G Page 8 of 29

Figure 4. Button Status with Respect to Finger Touch when FSS is Enabled  $^{\rm [3]}$

Figure 5. Key Scan interface Retrofit

Figure 6. SCAN Line Waveform Details

#### Note

3. When finger moves from one button to other (FSS enabled).

#### **Truth Table Output**

- Another output interface providing matrix outputs.

- All pins are output pins divided into ROW/COLUMN.

- Only one button can be reported at a time cannot be used in conjunction with FSS disabled.

- Button status is reported in an encoded ROW/COLUMN fashion as shown in Table 4.

- Each button has its own ROW-COLUMN code.

- Easy to integrate into a system requiring a simple interface with single key press requirement.

- OUT4 to OUT7 in the pin out form the ROW lines and OUT0 to OUT3 form the COLUMN lines.

Table 4. Truth Table Output

| 4x4     |    | Matrix Code |    |    |   |         |   |   |   |

|---------|----|-------------|----|----|---|---------|---|---|---|

|         | 0  |             |    |    | • |         |   |   | • |

|         | 1  |             |    |    | • |         |   | • |   |

|         | 2  |             |    |    | • |         | • |   |   |

|         | 3  |             |    |    | • | •       |   |   |   |

|         | 4  |             |    | •  |   |         |   |   | • |

|         | 5  |             |    | •  |   |         |   | • |   |

|         | 6  |             |    | •  |   |         | • |   |   |

|         | 7  |             |    | •  |   | •       |   |   |   |

| Buttons | 8  |             | •  |    |   |         |   |   | • |

|         | 9  |             | •  |    |   |         |   | • |   |

|         | 10 |             | •  |    |   |         | • |   |   |

|         | 11 |             | •  |    |   | •       |   |   |   |

|         | 12 | •           |    |    |   |         |   |   | • |

|         | 13 | •           |    |    |   |         |   | • |   |

|         | 14 | •           |    |    |   |         | • |   |   |

|         | 15 | •           |    |    |   | •       |   |   |   |

|         |    | 3           | 2  | 1  | 0 | 3       | 2 | 1 | 0 |

|         |    |             | Ro | ws |   | Columns |   |   |   |

#### **Encoded 4-bit Output**

- Only 4 pins to report a button press out of 16 buttons.

- Each button has its own code.

- Only one button can be reported at a time using this interface.

- Table 5 defines the decode table.

Table 5. Encoded Output

| Keypress Detected By<br>CapSense | EO[3:0] | Interrupt<br>Time |

|----------------------------------|---------|-------------------|

| Key #1                           | 0000    | 1                 |

| Key #2                           | 0001    | 1                 |

| Key #3                           | 0010    | 1                 |

| Key #4                           | 0011    | 1                 |

|                                  |         | 1                 |

| Key #16                          | 1111    | 1                 |

| No keys pressed                  | XXXX    | 0                 |

#### **Buzzer Signal Output**

- A dedicated pin for buzzer output is provided in the device.

- Buzzer output can be used to drive an p-type transistor driving a buzzer or directly a DC buzzer up to 10 mA sink current.

#### **Interrupt Line**

- An interrupt line to the host controller.

- On a button touch, the device pulls the INT line HIGH to indicate an interrupt to the host. The INT line remains HIGH as long as a button is touched.

- Can be used as a latch input at the host side to read the OUT lines.

- Can also be used as an interrupt line for the host controller to read the OUT lines.

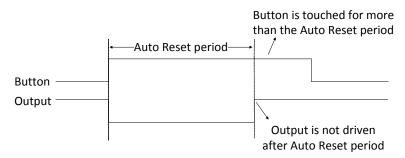

#### **Button Auto Reset**

- Prevents button stuck, due to any conducting object placed close to a button.

- Useful when output to be kept ON only for a specific time.

- The Button Auto Reset period is controlled by the hardware configuration on the ARST pin. Refer Table 19 in Appendix on page 26 for pin configuration details.

- When touched, a button is treated active for a maximum of Button Auto Reset period (refer to Figure 7).

- After the button is released the CSx will be hold for 440 ms.

Figure 7. Button Auto Reset

#### **Output Select**

- One among the three output interfaces defined earlier in the section can be selected by the hardware configuration on the OUT\_SEL pin. Refer Table 19 in Appendix on page 26 for pin configuration details.

- Only one of three output interfaces can be used at a given time.

#### Scan Rate

- This defines the rate at which the device scans all the buttons and then sleeps, in the Low Power Sleep mode. For more details about Low Power Sleep mode, refer to Power Consumption and Device Operating Modes on page 15.

- The device scan rate is defined by the hardware configuration on the SCAN pin. Refer Table 19 in Appendix on page 26 for details.

- Device power consumption is dependent on Scan Rate. For a higher scan rate, the power consumption is less, and vice versa. Refer to the CY8CMBR2016 Design Guide, section 5 for power calculations.

#### Sensitivity

- Sensitivity is defined as the minimum change in capacitance which can be detected as a finger touch.

- Use higher sensitivity setting when the overlay thickness is higher, or the button diameter is small.

- Use a lower sensitivity setting when power consumption needs to be low.

- Possible sensitivity settings are "High", "Medium", and "Low".

Sensitivity can be controlled by the hardware configuration on the SENSITIVITY pin. For details, refer to Table 19 in Appendix on page 26.

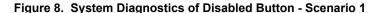

#### **System Diagnostics**

A built-in power on self test (POST) mechanism detects the following at power on reset (POR), which can be useful in production testing. Any failure is reported on the OUT\_6 and OUT 7 pins, as detailed below.

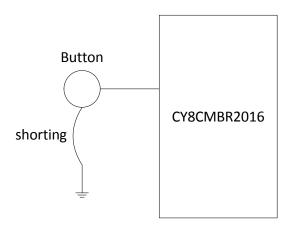

#### Button Shorted to Ground

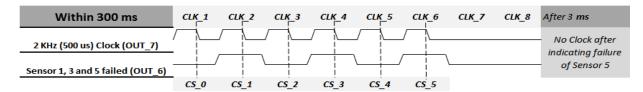

If a button is disabled/found shorted to Ground (as shown in Figure 10), then the corresponding bit in the button mask is set, and the same is sent out serially through the OUT\_6 pin, synchronised with a 2 kHz clock on OUT 7 pin.

If no clock is sensed on OUT\_7 till 300 ms after power-on, then all the buttons have passed the System Diagnostics. If a clock is sensed, then starting from the first falling edge of the clock, each button takes up one clock slot. A high output on OUT\_6 during a falling edge on OUT\_7 indicates a failure of the button in that clock slot.

The clock output stops after indicating the last failed button. For instance, if Button 1, 3 and 5 are disabled, then the System Diagnostics data is transmitted as shown in Figure 8. CS1 failure is marked by a HIGH on OUT\_6 in the 0.5 ms to 1 ms slot. CS3 failure is marked by a HIGH on OUT\_6 in the 1.5 ms to 2 ms slot. CS5 failure is marked by a HIGH on OUT\_6 in the 2.5 ms to 3 ms slot. After indicating the failure of CS5, clock output is ceased.

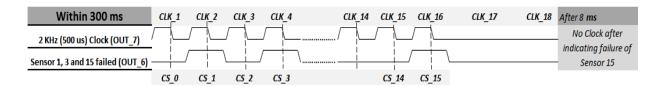

As an example, Figure 9 shows the System Diagnostics output when CS1, CS3 and CS15 fail the POST.

Document Number: 001-67921 Rev. \*G Page 11 of 29

Figure 9. System Diagnostics of Disabled Button - Scenario 2

Figure 10. Button Shorted to GND

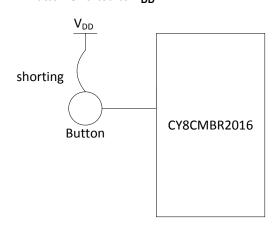

# Button Shorted to V<sub>DD</sub>

If any button is shorted to  $V_{DD}$  that button is disabled and the corresponding bit field is set and System Diagnostics data is sent as defined in button to GND short section.

Figure 11. Button Shorted to V<sub>DD</sub>

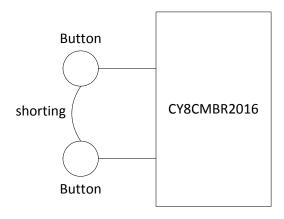

#### Button to Button Short

Any button that are shorted together are disabled and the corresponding bit field is set and System Diagnostics data is sent as defined in button to GND short section.

Figure 12. Button to Button Short

#### Improper Value of C<sub>MOD</sub>

- $\blacksquare$  Recommended value of  $C_{\mbox{\scriptsize MOD}}$  is 2 nF to 2.4 nF.

- If C<sub>MOD</sub> of < 1 nF or > 4 nF is connected, all buttons are disabled and the status output will be logic high on all slots.

## Button $C_P > 40 pF$

If the parasitic capacitance ( $C_P$ ) of any button exceeds 40 pF that button is disabled and the corresponding bit field is set and System Diagnostics data is sent as defined in button to GND short section.

Document Number: 001-67921 Rev. \*G Page 12 of 29

#### **Serial Debug Data Out**

- Used to see CapSense data through the Debug pin.

- To enable this feature, the DEBUG pin is pulled down with a 5.6 K resistor.

- The Cypress MultiChart tool can be used to view the debug data for each button

- Serial data is sent out at ~115,200 baud rate

- Firmware revision, CapSense status, baseline, raw counts, difference counts and parasitic capacitances of all sensors are sent out

For more information on Raw Count, Baseline, Difference Count, and Parasitic Capacitance, refer Getting Started with CapSense, section 2.

For more information on MultiChart tool, refer AN2397 - CapSense Data Viewing Tools, method 2.

- The MultiChart tool arranges the data in the format as shown in Table 6 on page 13.

- The Serial Debug Data is sent by the device in the order shown in Table 7 on page 14.

Table 6. Serial Debug Data Arranged in MultiChart

| SI. No. | Raw Count Array |         | Baselii   | ne Array | Difference Count array |         |

|---------|-----------------|---------|-----------|----------|------------------------|---------|

| MSB LSB |                 | MSB     | LSB       | MSB      | LSB                    |         |

| 0       | CS0_RC          |         | CS0_BL    | CS0_BL ( |                        |         |

| 1       | CS1_RC          |         | CS1_BL    |          | CS1_DIFF               |         |

| 2       | CS2_RC          |         | CS2_BL    |          | CS2_DIFF               |         |

| 3       | CS3_RC          |         | CS3_BL    |          | CS3_DIFF               |         |

| 4       | CS4_RC          |         | CS4_BL    |          | CS4_DIFF               |         |

| 5       | CS5_RC          |         | CS5_BL    |          | CS5_DIFF               |         |

| 6       | CS6_RC          |         | CS6_BL    |          | CS6_DIFF               |         |

| 7       | CS7_RC          |         | CS7_BL    |          | CS7_DIFF               |         |

| 8       | CS8_RC          |         | CS8_BL    |          | CS8_DIFF               |         |

| 9       | CS9_RC          |         | CS9_BL    |          | CS9_DIFF               |         |

| 10      | CS10_RC         |         | CS10_BL   |          | CS10_DIFF              |         |

| 11      | CS11_RC         |         | CS11_BL   |          | CS11_DIFF              |         |

| 12      | CS12_RC         |         | CS12_BL   |          | CS12_DIFF              |         |

| 13      | CS13_RC         |         | CS13_BL   |          | CS13_DIFF              |         |

| 14      | CS14_RC         |         | CS14_BL   |          | CS14_DIFF              |         |

| 15      | CS15_RC         |         | CS15_BL   |          | CS15_DIFF              |         |

| 16      | 0x00            | F/W Rev | CS_Status |          | 0x00                   | CS10_CP |

| 17      | 0x00            | CS0_CP  | 0x00      | CS5_CP   | 0x00                   | CS11_CP |

| 18      | 0x00            | CS1_CP  | 0x00      | CS6_CP   | 0x00                   | CS12_CP |

| 19      | 0x00            | CS2_CP  | 0x00      | CS7_CP   | 0x00                   | CS13_CP |

| 20      | 0x00            | CS3_CP  | 0x00      | CS8_CP   | 0x00                   | CS14_CP |

| 21      | 0x00            | CS4_CP  | 0x00      | CS9_CP   | 0x00                   | CS15_CP |

Document Number: 001-67921 Rev. \*G Page 13 of 29

Table 7. Serial Data Output sent by CY8CMBR2016

| BYTE     | DATA      | Notes                                      |  |  |  |  |

|----------|-----------|--------------------------------------------|--|--|--|--|

| 0        | 0x0D      | Dummy variables for multi chart tool       |  |  |  |  |

| 1        | 0x0A      |                                            |  |  |  |  |

| 2        | CS0_RC    | CS0 Raw counts, unsigned 16-bit integer    |  |  |  |  |

| 3        |           |                                            |  |  |  |  |

| 4        | CS1_RC    | CS1 Raw counts, unsigned 16-bit integer    |  |  |  |  |

| 5        |           |                                            |  |  |  |  |

| 6        | CS2_RC    | CS2 Raw counts, unsigned 16-bit integer    |  |  |  |  |

| 7        |           |                                            |  |  |  |  |

|          |           |                                            |  |  |  |  |

| 32       | CS15_RC   | CS15 Raw counts, unsigned 16-bit integer   |  |  |  |  |

| 33       |           |                                            |  |  |  |  |

| 34       | 0x00      | -                                          |  |  |  |  |

| 35       | FW_REV    | Firmware revision                          |  |  |  |  |

| 36       | 0x00      | -                                          |  |  |  |  |

| 37       | CS0_CP    | Parasitic capacitance of CS0               |  |  |  |  |

| 38       | 0x00      | -                                          |  |  |  |  |

| 39       | CS1_CP    | Parasitic capacitance of CS1               |  |  |  |  |

| 40       | 0x00      | -                                          |  |  |  |  |

| 41       | CS2_CP    | Parasitic capacitance of CS2               |  |  |  |  |

| 42       | 0x00      | -                                          |  |  |  |  |

| 43       | CS3_CP    | Parasitic capacitance of CS3               |  |  |  |  |

| 44       | 0x00      | -                                          |  |  |  |  |

| 45       | CS4_CP    | Parasitic capacitance of CS4               |  |  |  |  |

| 46       | CS0_BL    | CS0 Baseline, unsigned 16-bit integer      |  |  |  |  |

| 47       |           |                                            |  |  |  |  |

| 48       | CS1_BL    | CS1 Baseline, unsigned 16-bit integer      |  |  |  |  |

| 49       |           |                                            |  |  |  |  |

| 50       | CS2_BL    | CS2 Baseline, unsigned 16-bit integer      |  |  |  |  |

| 51       |           |                                            |  |  |  |  |

|          |           |                                            |  |  |  |  |

| 76       | CS15_BL   | CS15 Baseline, unsigned 16-bit integer     |  |  |  |  |

| 77       |           |                                            |  |  |  |  |

| 78<br>79 | CS_Status | CapSense Status, unsigned 16 bit integer – |  |  |  |  |

| 80       | 0x00      | -                                          |  |  |  |  |

| 81       | CS5_CP    | Parasitic capacitance of CS5               |  |  |  |  |

| 82       | 0x00      | -                                          |  |  |  |  |

| 83       | CS6_CP    | Parasitic capacitance of CS6               |  |  |  |  |

| 84       | 0x00      | -                                          |  |  |  |  |

Table 7. Serial Data Output sent by CY8CMBR2016 (continued)

| BYTE     | DATA       | Notes                                           |  |  |  |

|----------|------------|-------------------------------------------------|--|--|--|

| 85       | CS7_CP     | Parasitic capacitance of CS7                    |  |  |  |

| 86       | 0x00       | -                                               |  |  |  |

| 87       | CS8_CP     | Parasitic capacitance of CS8                    |  |  |  |

| 88       | 0x00       | -                                               |  |  |  |

| 89       | CS9_CP     | Parasitic capacitance of CS9                    |  |  |  |

| 90       | CS0_DIFF   | CS0 difference counts, unsigned 16-bit integer  |  |  |  |

| 91<br>92 | CS1_DIFF   | CS1 difference counts, unsigned 16-bit integer  |  |  |  |

| 93<br>94 | CS2_DIFF   | CS2 difference counts, unsigned 16-bit integer  |  |  |  |

|          |            |                                                 |  |  |  |

| 121      | CS15_ DIFF | CS15 difference counts, unsigned 16-bit integer |  |  |  |

| 122      |            |                                                 |  |  |  |

| 123      | 0x00       | -                                               |  |  |  |

| 124      | CS10_CP    | Parasitic capacitance of CS10                   |  |  |  |

| 125      | 0x00       | -                                               |  |  |  |

| 126      | CS11_CP    | Parasitic capacitance of CS11                   |  |  |  |

| 127      | 0x00       | -                                               |  |  |  |

| 128      | CS12_CP    | Parasitic capacitance of CS12                   |  |  |  |

| 129      | 0x00       | -                                               |  |  |  |

| 130      | CS13_CP    | Parasitic capacitance of CS13                   |  |  |  |

| 131      | 0x00       | -                                               |  |  |  |

| 132      | CS14_CP    | Parasitic capacitance of CS14                   |  |  |  |

| 133      | 0x00       | -                                               |  |  |  |

| 134      | CS15_CP    | Parasitic capacitance of CS15                   |  |  |  |

| 135      | 0x00       | Dummy variable for multi chart tool             |  |  |  |

| 136      | 0xFF       |                                                 |  |  |  |

| 137      | 0xFF       |                                                 |  |  |  |

#### **Power Consumption and Device Operating Modes**

The CY8CMBR2016 is designed to meet the low power requirements of battery powered applications. To design for the lowest operating current -

- Ground all unused CapSense inputs

- Minimize Cp using the design guidelines in Getting Started with CapSense, section 3.7.1.

- Lower the supply voltage.

- Use a higher Button Scan Rate or Deep Sleep operating mode. To know more about the steps to reduce power consumption, refer to CY8CMBR2016 Design Guide, section 5.

There are two device operating modes:

- Low power sleep mode

- Deep sleep mode

Document Number: 001-67921 Rev. \*G Page 15 of 29

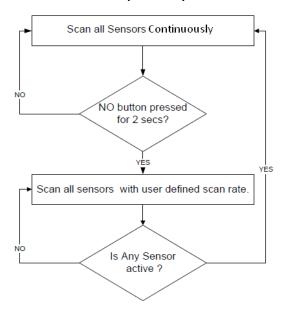

Low Power Sleep Mode

The following flow chart describes the low power sleep mode operation.

Figure 13. Low Power Sleep Mode Operation

For details on Low power sleep look at the Scan Rate on page 11 section.

#### **Response Time**

Response Time is the minimum amount of time the button should be touched for the device to detect as valid button touch.

It is given by the following equations -

RT<sub>FRT</sub> =User defined Button Scan Rate + 40 ms

$RT_{CBT} = 40 \text{ ms}$

Where,

RT<sub>FBT</sub> is Response time for first button touch

${\sf RT}_{\sf CBT}$  is Response time for consecutive button touch after first button touch

Refer to Scan Rate on page 11 section for more details on the User defined Button Scan Rate.

For example, consider a nine button design with the User defined Button Scan Rate set to Low (250 ms). The response time for such a design is given as:

RT<sub>FBT</sub> =250+40=290 ms

$RT_{CBT} = 40 \text{ ms}$

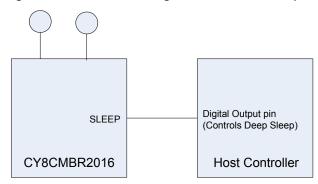

#### **Deep Sleep Mode**

Figure 14. SLEEP Pin Configuration to Enable Deep Sleep

- To enable the deep sleep mode, the hardware configuration pin Sleep should be connected to the master device.

- Master should pull the pin to V<sub>DD</sub> for the device to go into deep sleep.

- The master output pin should be in strong drive mode, so that the Sleep pin is not left floating.

- In deep sleep mode, all blocks are turned off and the device power consumption is 0.1 μA.

- There is no CapSense scanning in deep sleep mode.

- Sleep pin should be pulled low for the device to wake up from deep sleep.

- When device comes out of deep sleep mode, the CapSense system is reinitialized. Typical time for re-initialization is 8 ms.Any button press within this time is not reported.

- After the device comes out of deep sleep, the device operates in low power sleep mode.

- If the Sleep pin is pulled high at power on, then the device does not go to deep sleep immediately. The device goes to deep sleep after initializing all internal blocks and scanning all sensors once.

- If the Sleep pin is pulled high at power on, then the scan rate is calculated when the device is taken out of Deep Sleep by the master.

# **Layout Guidelines and Best Practices**

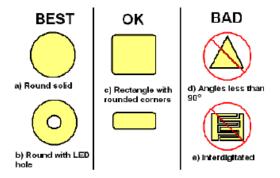

Table 8. Layout Guidelines

| SI. No. | Category                                            | Min                                    | Max     | Recommendations/Remarks                                                                                                                                                                       |

|---------|-----------------------------------------------------|----------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.      | Button shape                                        | _                                      | _       | Solid round pattern, Round with LED hole, rectangle with round corners                                                                                                                        |

| 2.      | Button size                                         | 5 mm                                   | 15 mm   | Given in layout estimator sheet                                                                                                                                                               |

| 3.      | Button-Button spacing                               | equal to<br>button ground<br>clearance |         | 8 mm                                                                                                                                                                                          |

| 4.      | Button ground clearance                             | 0.5 mm                                 | 2 mm    | Given in layout estimator sheet                                                                                                                                                               |

| 5.      | Ground flood - Top layer                            | _                                      | _       | Hatched ground 7 mil trace and 45 mil grid (15% filling)                                                                                                                                      |

| 6.      | Ground flood -<br>bottom layer                      | -                                      | _       | Hatched ground 7 mil trace and 70 mil grid (10% filling)                                                                                                                                      |

| 7.      | Trace length from sensor to device pin              | -                                      | 450     | Given in layout estimator sheet                                                                                                                                                               |

| 8.      | Trace width                                         | 0.17 mm                                | 0.20 mm | 0.17 mm (7 mil)                                                                                                                                                                               |

| 9.      | Trace routing                                       | -                                      | _       | Traces should be routed on the non sensor side. If any non CapSense trace crosses CapSense trace, ensure that intersection is orthogonal.                                                     |

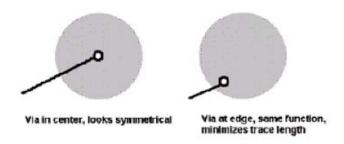

| 10.     | Via position for the sensors                        | -                                      | _       | Via should be placed near the edge of the button to reduce trace length thereby increasing sensitivity.                                                                                       |

| 11.     | Via hole size for sensor traces                     | -                                      | _       | 10 mil                                                                                                                                                                                        |

| 12.     | No. of via on sensor trace                          | 1                                      | 2       | 1                                                                                                                                                                                             |

| 13.     | CapSense series resistor placement                  | -                                      | 10 mm   | Place CapSense series resistors close to the device for noise suppression.CapSense resistors have highest priority compared to other resistors, so place them first.                          |

| 14.     | Distance between any CapSense trace to ground flood | 10 mil                                 | 20 mil  | 20 mil                                                                                                                                                                                        |

| 15.     | Device placement                                    | -                                      | _       | Mount the device on the layer opposite to sensor. The CapSense trace length between the device and sensors should be minimum (see trace length above)                                         |

| 16.     | Placement of components in two layer PCB            | -                                      | _       | Top layer-Sensors and bottom layer-device, other components and traces.                                                                                                                       |

| 17.     | Placement of components in four layer PCB           | _                                      | _       | Top layer-Sensors, second layer – CapSense traces & Vdd and avoid the Vdd traces below the sensors, third layer-hatched ground, Bottom layer- device other components and non CapSense traces |

| 18.     | Overlay thickness                                   | 0 mm                                   | 5 mm    | Use layout estimator sheet to decide on overlay, given maximum limit is for plastic overlay.                                                                                                  |

| 19.     | Overlay material                                    | _                                      | _       | Should to be non-conductive material. Glass, ABS Plastic, Formica, wood etc. No air gap should be there between PCB and overlay. Use adhesive to stick the PCB and overlay.                   |

| 20.     | Overlay adhesives                                   | _                                      | _       | Adhesive should be non conductive and dielectrically homogenous. 467 MP and 468 MP adhesives made by 3 M are recommended.                                                                     |

| 21.     | Board thickness                                     | _                                      | _       | Standard board thickness for CapSense FR4 based designs is 1.6 mm.                                                                                                                            |

|         | •                                                   | •                                      |         |                                                                                                                                                                                               |

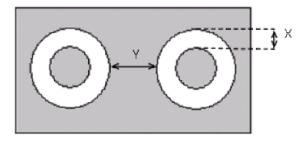

Figure 15. CapSense Button Shapes

Figure 16. Button Layout Design

- X: Button to ground clearance (Refer to Layout Guidelines and Best Practices on page 17)

- Y: Button to button clearance (Refer to Layout Guidelines and Best Practices on page 17)

Figure 17. Recommended via Hole Placement

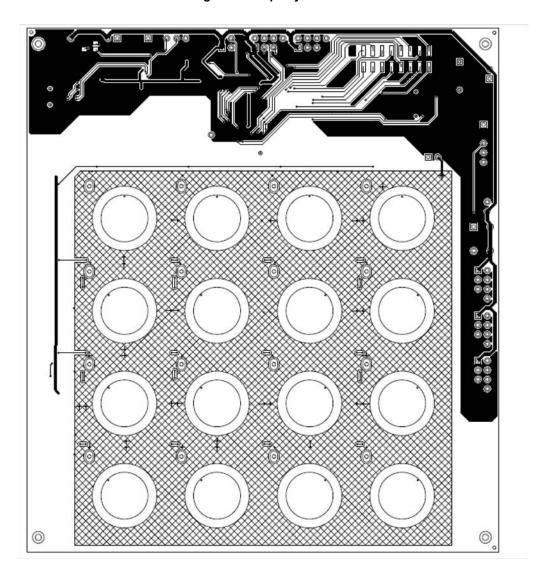

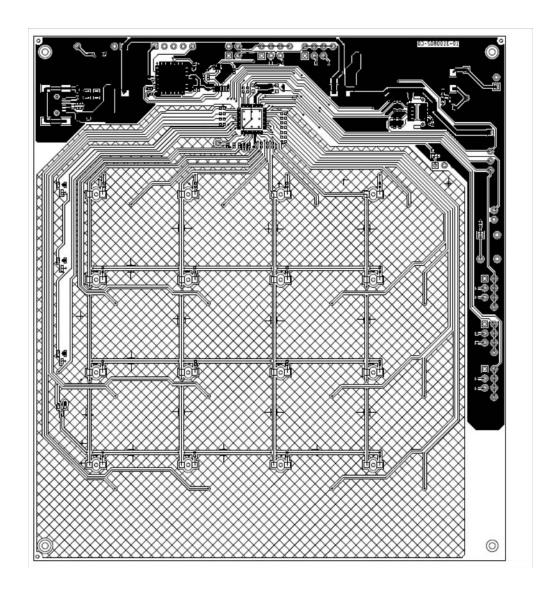

# Sample Layout

Figure 18. Top Layer

Figure 19. Bottom Layer

# **Electrical Specifications**

This section presents the DC and AC electrical specifications of the CY8CMBR2044 device.

#### Table 9. Absolute Maximum Ratings

| Parameter        | Description                                           | Min                   | Тур | Max                   | Unit | Notes                                                                                                                                                                              |

|------------------|-------------------------------------------------------|-----------------------|-----|-----------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>STG</sub> | Storage temperature                                   | <b>-</b> 55           | 25  | +125                  | °C   | Higher storage temperatures reduce data retention time. Recommended storage temperature is +25 °C ± 25 °C. Extended duration storage temperatures above 85 °C degrade reliability. |

| $V_{DD}$         | Supply voltage relative to V <sub>SS</sub>            | -0.5                  | _   | +6.0                  | V    | -                                                                                                                                                                                  |

| V <sub>IO</sub>  | DC voltage on CapSense inputs and digital output pins | V <sub>SS</sub> – 0.5 | ı   | V <sub>DD</sub> + 0.5 | V    | -                                                                                                                                                                                  |

| I <sub>MIG</sub> | Maximum current into any GPO output pin               | -25                   | ı   | +50                   | mA   | -                                                                                                                                                                                  |

| ESD              | Electrostatic discharge voltage                       | 2000                  | -   | _                     | V    | Human body model ESD                                                                                                                                                               |

| LU               | Latch up current                                      | _                     | -   | 200                   | mA   | In accordance with JESD78 standard                                                                                                                                                 |

#### **Table 10. Operating Temperature**

| Parameter      | Description                 | Min | Тур | Max  | Unit | Notes |

|----------------|-----------------------------|-----|-----|------|------|-------|

| T <sub>A</sub> | Ambient temperature         | -40 | -   | +85  | °C   | _     |

| $T_{C}$        | Commercial temperature      | 0   | -   | +70  | °C   | _     |

| $T_J$          | Operational die temperature | -40 | _   | +100 | °C   | _     |

#### **DC Electrical Characteristics**

The following table lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

Table 11. DC Chip Level Specifications

| Parameter                            | Description        | Min  | Тур  | Max | Unit | Notes                                                                                                                                                                          |

|--------------------------------------|--------------------|------|------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> <sup>[4, 5, 6]</sup> | Supply voltage     | 1.71 | _    | 5.5 | V    | _                                                                                                                                                                              |

| I <sub>DD</sub>                      | Supply current     | _    | 3.3  | 4.0 | mA   | Conditions are V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C                                                                                                                 |

| I <sub>DA</sub>                      | Active current     | _    | 3.3  | 4.0 | mA   | Conditions are V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C, continuous sensor scan                                                                                         |

| I <sub>DS</sub>                      | Deep sleep current | _    | 0.1  | 0.5 | μΑ   | Conditions are V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C                                                                                                                 |

| I <sub>AV1</sub>                     | Average current    | -    | 0.25 | -   | mA   | Conditions are $V_{DD}$ = 3.0 V, $T_{A}$ = 25 °C and 16 buttons used, with 0% touch time, $C_{P}$ of all sensors < 19 pFand scan rate = 250 ms                                 |

| I <sub>AV2</sub>                     | Average current    | -    | 2.13 | -   | mA   | Conditions are $V_{DD}$ = 3.0 V, $T_A$ = 25 °C and 16 buttons used, with 50% touch time, $C_P$ of all sensors < 19 pFand scan rate = 250 ms, Key Scan mode enabled             |

| I <sub>AV3</sub>                     | Average current    | -    | 0.42 | _   | mA   | Conditions are $V_{DD}$ = 3.0 V, $T_A$ = 25 °C and 16 buttons used, with 0% touch time, $C_P$ of all sensors >19 pF and < 40 pF and scan rate = 250 ms                         |

| I <sub>AV4</sub>                     | Average current    | -    | 2.2  | -   | mA   | Conditions are $V_{DD}$ = 3.0 V, $T_A$ = 25 °C and 16 buttons used, with 50% touch time, $C_P$ of all sensors >19 pF and < 40 pF and scan rate = 250 ms, Key Scan mode enabled |

#### Notes

Document Number: 001-67921 Rev. \*G Page 21 of 29

When V<sub>DD</sub> remains in the range from 1.75 V to 1.9 V for more than 50 µs, the slew rate when moving from the 1.75 V to 1.9 V range to greater than 2 V must be slower than 1 V/500 µs. This helps to avoid triggering POR. The only other restriction on slew rates for any other voltage range or transition is the SR<sub>POWER\_UP</sub>

After power down, ensure that V<sub>DD</sub> falls below 100 mV before powering backup.

For proper CapSense block functionality, if the drop in V<sub>DD</sub> exceeds 5% of the base V<sub>DD</sub>, the rate at which V<sub>DD</sub> drops should not exceed 200 mV/s. Base V<sub>DD</sub> can be between 1.8 V and 5.5 V

# DC General Purpose I/O Specifications

These tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 3.0 V to 5.5 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , 2.4 V to 3.0 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , or 1.71 V to 2.4 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25  $^{\circ}\text{C}$  and are for design guidance only.

Table 12. 3.0 V to 5.5 V DC General Purpose I/O Specification

| Parameter        | Description                              | Min                   | Тур | Max  | Unit | Notes                                                                       |  |

|------------------|------------------------------------------|-----------------------|-----|------|------|-----------------------------------------------------------------------------|--|

| V <sub>OH1</sub> | High output voltage on all output pins   | V <sub>DD</sub> – 0.2 | _   | -    |      | $I_{OH}$ < 10 μA, Maximum of 40 μA source in all I/Os                       |  |

| V <sub>OH2</sub> | High output voltage on OUT pins          | V <sub>DD</sub> – 0.9 | _   | _    | V    | I <sub>OH</sub> = 1 mA, Maximum of 2 mA source in all I/Os                  |  |

| V <sub>OH3</sub> | High output voltage on INT and BUZZ pins | V <sub>DD</sub> – 0.9 | _   | -    | V    | I <sub>OH</sub> = 5 mA, Maximum of 10 mA source in all I/Os                 |  |

| V <sub>OL</sub>  | Low output voltage                       | _                     | _   | 0.75 | V    | $I_{OL}$ = 25 mA/pin, $V_{DD}$ > 3.3 V, Maximum of 60 mA source in all I/Os |  |

| $V_{IL}$         | Input low voltage                        | -                     | -   | 0.80 | V    | -                                                                           |  |

| V <sub>IH</sub>  | Input high voltage                       | 2.00                  | _   | -    | V    | _                                                                           |  |

Table 13. 2.4 V to 3.0 V DC General Purpose I/O Specifications

| Parameter        | Description                         | Min                   | Тур | Max  | Unit | Notes                                                                       |  |

|------------------|-------------------------------------|-----------------------|-----|------|------|-----------------------------------------------------------------------------|--|

| V <sub>OH1</sub> | High output voltage on all outputs  | V <sub>DD</sub> – 0.2 | _   | _    |      | $I_{OH}$ < 10 μA, Maximum of 40 μA Source in all I/Os                       |  |

| V <sub>OH2</sub> | High output voltage on OUT pins     | V <sub>DD</sub> – 0.4 | _   | _    |      | I <sub>OH</sub> = 0.2 mA, Maximum of 0.4 mA source in all I/Os              |  |

| V <sub>OH3</sub> | High output voltage on INT and BUZZ | V <sub>DD</sub> – 0.5 | _   | -    | V    | I <sub>OH</sub> = 2 mA, Maximum of 4 mA source in all I/Os                  |  |

| V <sub>OL</sub>  | Low output voltage                  | _                     | _   | 0.75 | V    | $I_{OL}$ = 10 mA/pin, $V_{DD}$ > 3.3 V, Maximum of 30 mA source in all I/Os |  |

| $V_{IL}$         | Input low voltage                   | _                     | -   | 0.72 | V    | _                                                                           |  |

| V <sub>IH</sub>  | Input high voltage                  | 1.40                  | -   | _    | V    | _                                                                           |  |

Table 14. 1.71 V to 2.4 V DC General Purpose I/O Specifications

| Parameter        | Description                         | Min                    | Тур | Max                  | Unit | Notes                                                                      |

|------------------|-------------------------------------|------------------------|-----|----------------------|------|----------------------------------------------------------------------------|

| V <sub>OH1</sub> | High output voltage on OUT pins     | V <sub>DD</sub> – 0.2  | -   | _                    | V    | I <sub>OH</sub> =10 μA, maximum of 20 μA<br>source in all I/Os             |

| V <sub>OH2</sub> | High output voltage on OUT pins     | V <sub>DD</sub> – 0.5  | -   | _                    | V    | I <sub>OH</sub> = 0.5 mA, maximum of 1 mA source in all I/Os               |

| V <sub>OH3</sub> | High output voltage on INT and BUZZ | V <sub>DD</sub> – 0.2  | _   | _                    | V    | I <sub>OH</sub> =100 μA, maximum of 200 μA source in all I/Os              |

| V <sub>OH4</sub> | High output voltage on INT and BUZZ | V <sub>DD</sub> – 0.5  | _   | _                    | V    | I <sub>OH</sub> = 2 mA, maximum of 4 mA source in all I/Os                 |

| V <sub>OL</sub>  | Low output voltage                  | _                      | _   | 0.4                  | V    | $I_{OL}$ = 5 mA/pin, $V_{DD}$ > 3.3 V, maximum of 20 mA source in all I/Os |

| V <sub>IL</sub>  | Input low voltage                   | _                      | -   | $0.30 \times V_{DD}$ | V    | _                                                                          |

| V <sub>IH</sub>  | Input high voltage                  | 0.65 × V <sub>DD</sub> | _   | _                    | ٧    | _                                                                          |

Document Number: 001-67921 Rev. \*G Page 22 of 29

# **AC Electrical Specifications**

The following table lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

# Table 15. AC Chip-Level Specifications

| Parameter              | Description                               | Min | Max | Unit | Notes                                                             |

|------------------------|-------------------------------------------|-----|-----|------|-------------------------------------------------------------------|

| SR <sub>POWER_UP</sub> | Power supply slew rate                    | -   | 250 | V/ms | V <sub>DD</sub> slew rate during power-up                         |

| T <sub>XRST</sub>      | External reset pulse width at power-up    | 1   | -   | ms   | Applicable after device power supply is active                    |

| T <sub>XRST2</sub>     | External reset pulse width after power-up | 10  | _   | ms   | Applicable after device V <sub>DD</sub> has reached maximum value |

# Table 16. AC General Purpose I/O Specifications

| Parameter          | Description                                   | Min | Тур | Max | Unit | Notes                        |

|--------------------|-----------------------------------------------|-----|-----|-----|------|------------------------------|

| T <sub>Rise1</sub> | Rise time on OUT pins, Cload = 50 pF          | 15  | _   | 80  | ns   | VDD = 3.0 to 3.6 V, 10%–90%  |

| T <sub>Rise2</sub> | Rise time on INT and BUZZ pins, Cload = 50 pF | 10  | -   | 50  | ns   | VDD = 3.0 to 3.6 V, 10%–90%  |

| T <sub>Rise3</sub> | Rise time on OUT pins, Cload = 50 pF          | 15  | _   | 80  | ns   | VDD = 1.71 to 3.0 V, 10%–90% |

| T <sub>Rise4</sub> | Rise time on INT and BUZZ pins, Cload = 50 pF | 10  | -   | 80  | ns   | VDD = 1.71 to 3.0 V, 10%–90% |

| T <sub>Fall1</sub> | Fall time, Cload = 50 pF all outputs          | 10  | _   | 50  | ns   | VDD = 3.0 to 3.6 V, 90%–10%  |

| T <sub>Fall2</sub> | Fall time, Cload = 50 pF all outputs          | 10  | _   | 70  | ns   | VDD = 1.71 to 3.0 V, 90%–10% |

# **CapSense Specification**

| Parameter        | Description                                | Min  | Тур | Max                                  | Unit | Notes                                                                                                                                                                              |

|------------------|--------------------------------------------|------|-----|--------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C <sub>P</sub>   | Parasitic capacitance                      | 5.0  | _   | (C <sub>P</sub> +C <sub>F</sub> )<40 | pF   | $C_{P}$ is the total capacitance seen<br>by the pin when no finger is<br>present. $C_{P}$ is sum of $C_{S}$ sensor,<br>$C_{S}$ trace, and Capacitance of the<br>vias and $C_{PIN}$ |

| C <sub>F</sub>   | Finger capacitance                         | 0.25 | _   | (C <sub>P</sub> +C <sub>F</sub> )<40 | pF   | C <sub>F</sub> is the capacitance added by the finger touch                                                                                                                        |

| C <sub>PIN</sub> | Capacitive load on pins as input           | 0.5  | 1.7 | 7                                    | pF   | Mandatory for CapSense to work                                                                                                                                                     |

| C <sub>MOD</sub> | External modulator capacitor               | 2    | 2.2 | 2.4                                  | nF   | Mandatory for CapSense to work                                                                                                                                                     |

| R <sub>S</sub>   | Series resistor between pin and the button | -    | 560 | 616                                  | Ω    | Reduces the RF noise                                                                                                                                                               |

Document Number: 001-67921 Rev. \*G Page 23 of 29

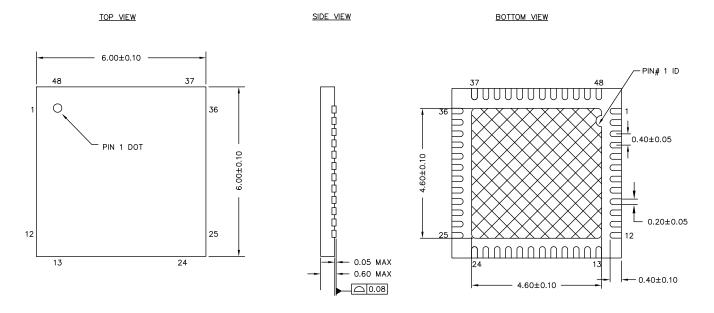

# **Package Information**

# Table 17. Thermal Impedances by Package

| Package                   | Typical θ <sub>JA</sub> <sup>[7]</sup> |

|---------------------------|----------------------------------------|

| 48-pin QFN <sup>[8]</sup> | 19 °C/W                                |

#### Table 18. Solder Reflow Peak Temperature

| Package    | Minimum Peak Temperature [9] | Maximum Peak Temperature | Time at Max Temperature |

|------------|------------------------------|--------------------------|-------------------------|

| 48-pin QFN | 240 °C                       | 260 °C                   | 30 s                    |

Figure 20. 48-pin QFN (6 × 6 × 0.6 mm) Package Outline

#### NOTES:

- 1. HATCH AREA IS SOLDERABLE EXPOSED PAD

- 2. REFERENCE JEDEC # MO-248

- 3. PACKAGE WEIGHT: 68 ±7

- 4. ALL DIMENSIONS ARE IN MILLIMETERS

001-57280 \*E

#### Notes

- 7. T<sub>J</sub> = T<sub>A</sub> + Power x θ<sub>JA</sub>

8. To achieve the thermal impedance specified for the QFN package, the center thermal pad must be soldered to the PCB ground plane

- 9. Higher temperatures may be required based on the solder melting point. Typical temperatures for solder are 220 ± 5 °C with Sn-Pb or 245 ± 5 °C with Sn-Ag-Cu paste. Refer to the solder manufacturer specifications.

Page 25 of 29

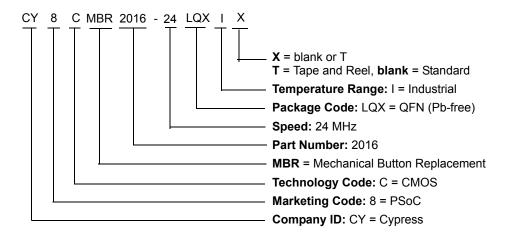

# **Ordering Information**

| Ordering Code       | Package Type                                | Operating<br>Temperature | CapSense<br>Inputs | Other<br>I/Os      | XRES<br>pin |

|---------------------|---------------------------------------------|--------------------------|--------------------|--------------------|-------------|

| CY8CMBR2016-24LQXI  | 48-pin (6 × 6 × 0.6 mm) QFN                 | Industrial               | 17 <sup>[10]</sup> | 17 <sup>[11]</sup> | Yes         |

| CY8CMBR2016-24LQXIT | 48-pin (6 × 6 × 0.6 mm) QFN (Tape and Reel) | Industrial               | 17 <sup>[10]</sup> | 17 <sup>[11]</sup> | Yes         |

# **Ordering Code Definitions**

Notes

10. 16 CapSense input + 1 C<sub>MOD</sub> pin

11. 8 Configurable GPIOs + 1 buzzer output + 1 Sleep line + 1 Interrupt line + 1 Debug line + 5 configuration pins

# **Appendix**

Table 19. Device Features versus Resistor Configuration Matrix

| Features                          | Comments                                 | Pin configuration      | Device Pin Name |  |

|-----------------------------------|------------------------------------------|------------------------|-----------------|--|

| Flanking Sensor Suppression (FSS) | Disabled                                 | Ground                 | FSS             |  |

|                                   | Enabled                                  | VDD / Floating         |                 |  |

| Button Auto Reset                 | Enabled, Auto Reset period = 5 ms Ground |                        | ARST            |  |

|                                   | Enabled, Auto Reset period = 20 ms       | 1.5 kΩ (±5%) to ground |                 |  |

|                                   | Enabled, Auto Reset period = 40 ms       | 5 kΩ (±5%) to ground   |                 |  |

|                                   | Disabled                                 | VDD / Floating         |                 |  |

| Output Select                     | Truth Table I/F                          | Ground                 | OUT_SEL         |  |

|                                   | Encoded 4 bit output                     | 1.5 kΩ (±5%) to ground |                 |  |

|                                   | Keypad scanning interface output         | VDD / Floating         |                 |  |

| Scan Rate                         | Low, 250 ms                              | Ground                 | SCAN            |  |

|                                   | Medium, 150 ms                           | 1.5 kΩ (±5%) to ground |                 |  |

|                                   | High, 40 ms                              | 5 kΩ (±5%) to ground   |                 |  |

|                                   | Continuous scan                          | VDD / Floating         |                 |  |

| Sensitivity                       | Low                                      | Ground                 | SENSITIVITY     |  |

|                                   | Medium                                   | 1.5 kΩ (±5%) to ground |                 |  |

|                                   | High                                     | VDD / Floating         |                 |  |

| Deep Sleep Mode                   | Device out of Deep Sleep                 | Ground                 | SLEEP           |  |

|                                   | Device in Deep Sleep                     | VDD                    |                 |  |

Document Number: 001-67921 Rev. \*G Page 26 of 29

# **Acronyms**

| Acronym          | Description                                 |  |  |

|------------------|---------------------------------------------|--|--|

| AC               | alternating current                         |  |  |

| C <sub>F</sub>   | finger capacitance                          |  |  |

| C <sub>MOD</sub> | modulator capacitor                         |  |  |

| C <sub>P</sub>   | parasitic capacitance                       |  |  |

| EO_x             | Encoded Output - Bit 'x'                    |  |  |

| FMEA             | failure mode effect analysis                |  |  |

| FSS              | flanking sensor suppression                 |  |  |

| ODL              | Open Drain Low                              |  |  |

| POR              | power-on reset                              |  |  |

| POST             | power on self test                          |  |  |

| QFN              | quad flat no leads                          |  |  |

| RF               | radio frequency                             |  |  |

| READ_x           | D_x KeyScan Interface - 'x'th Read line     |  |  |

| SCAN_x           | x KeyScan Interface - 'x'th Scan line       |  |  |

| SNR              | signal-to-noise ratio                       |  |  |

| TT_COL_x         | _x Truth Table Column output - 'x'th Column |  |  |

| TT_ROW_x         | ROW_x Truth Table Row output - 'x'th Row    |  |  |

# **Document Conventions**

# **Units of Measure**

| Symbol | Unit of Measure   |  |  |

|--------|-------------------|--|--|

| °C     | degree Celsius    |  |  |

| kHz    | kilohertz         |  |  |

| kΩ     | kilohm            |  |  |

| MHz    | megahertz         |  |  |

| ΜΩ     | megaohm           |  |  |

| μΑ     | microampere       |  |  |

| μF     | microfarad        |  |  |

| μs     | microsecond       |  |  |

| mA     | milliampere       |  |  |

| ms     | millisecond       |  |  |

| mV     | millivolt         |  |  |

| nA     | nanoampere        |  |  |

| nF     | nanofarad         |  |  |

| ns     | nanosecond        |  |  |

| Ω      | ohm               |  |  |

| pF     | picofarad         |  |  |

| ppm    | parts per million |  |  |

| s      | second            |  |  |

| V      | volt              |  |  |

| W      | watt              |  |  |

Document Number: 001-67921 Rev. \*G Page 27 of 29

# **Document History Page**

|          | Document Title: CY8CMBR2016, CapSense <sup>®</sup> Express™ 16 Button Matrix Controller Document Number: 001-67921 |                    |                    |                                                                                                                                                                                                                                                                                       |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Revision | ECN                                                                                                                | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                 |  |  |

| **       | 3202566                                                                                                            | MSUR               | 03/22/2011         | New data sheet.                                                                                                                                                                                                                                                                       |  |  |

| *A       | 3387102                                                                                                            | MSUR               | 10/10/2011         | Changed status from Preliminary to Final. Added Char data into the table. Minor edits across the document.                                                                                                                                                                            |  |  |

| *B       | 3473096                                                                                                            | MSUR               | 12/22/2011         | No technical updates.                                                                                                                                                                                                                                                                 |  |  |

| *C       | 3633927                                                                                                            | UDYG               | 10/31/2012         | Updated title. Updated Features, Scan Rate, Sensitivity, and Button Shorted to Ground section. Added parameters $V_{IL}$ and $V_{IH}$ in Table 12, Table 13, and Table 14, and parameter $T_{C}$ in Table 10. Added Figure 14 and section Response Time. Updated Package Information. |  |  |

| *D       | 4387211                                                                                                            | SSHH               | 05/22/2014         | Updated pin 36 description in Table 1. Updated Figure 3 for better clarity. Modified statement on unused SCAN lines in Key Scan Interface.                                                                                                                                            |  |  |

| *E       | 4422219                                                                                                            | SSHH               | 06/26/2014         | Updated Truth Table Output (Table 4)                                                                                                                                                                                                                                                  |  |  |

| *F       | 5705905                                                                                                            | AESATMP7           | 04/12/2017         | Updated Logo and Copyright.                                                                                                                                                                                                                                                           |  |  |

| *G       | 5744947                                                                                                            | SSHH               | 05/22/2017         | Updated to new template. Completing Sunset Review.                                                                                                                                                                                                                                    |  |  |

Document Number: 001-67921 Rev. \*G Page 28 of 29

# Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

cypress.com/usb

cypress.com/wireless

#### **Products**

**USB Controllers**

Wireless Connectivity

ARM® Cortex® Microcontrollers cypress.com/arm Automotive cypress.com/automotive Clocks & Buffers cypress.com/clocks Interface cypress.com/interface Internet of Things cypress.com/iot Memory cypress.com/memory Microcontrollers cypress.com/mcu **PSoC** cypress.com/psoc Power Management ICs cypress.com/pmic Touch Sensing cypress.com/touch

#### PSoC® Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

#### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

## **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2011–2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 001-67921 Rev. \*G Revised May 22, 2017 Page 29 of 29