## **Contents**

| 1 | Intro | duction                                                 | 9  |

|---|-------|---------------------------------------------------------|----|

| 2 | Desc  | eription                                                | 9  |

|   | 2.1   | STM8L ultra-low-power 8-bit family benefits             | 10 |

|   | 2.2   | Device overview                                         | 11 |

|   | 2.3   | Ultra-low-power continuum                               | 12 |

| 3 | Func  | tional overview1                                        | 13 |

|   | 3.1   | Low-power modes                                         | 14 |

|   | 3.2   | Central processing unit STM8                            | 15 |

|   |       | 3.2.1 Advanced STM8 Core                                | 15 |

|   |       | 3.2.2 Interrupt controller                              | 15 |

|   | 3.3   | Reset and supply management                             | 16 |

|   |       | 3.3.1 Power supply scheme                               | 16 |

|   |       | 3.3.2 Power supply supervisor                           | 16 |

|   |       | 3.3.3 Voltage regulator                                 | 17 |

|   | 3.4   | Clock management                                        | 17 |

|   | 3.5   | Low-power real-time clock                               | 18 |

|   | 3.6   | LCD (Liquid crystal display)                            | 19 |

|   | 3.7   | Memories                                                | 19 |

|   | 3.8   | DMA                                                     | 19 |

|   | 3.9   | Analog-to-digital converter                             | 20 |

|   | 3.10  | Digital-to-analog converter                             | 20 |

|   | 3.11  | Ultra-low-power comparators                             | 20 |

|   | 3.12  | System configuration controller and routing interface   |    |

|   | 3.13  | Touch sensing                                           |    |

|   | 3.14  | Timers                                                  |    |

|   |       | 3.14.1 16-bit advanced control timer (TIM1)             |    |

|   |       | 3.14.2 16-bit general purpose timers (TIM2, TIM3, TIM5) |    |

|   |       | 3.14.3 8-bit basic timer (TIM4)                         |    |

|   | 3.15  | Watchdog timers                                         | 22 |

|   |       | 3.15.1 Window watchdog timer                            |    |

|   |       |                                                         |    |

|             |       | 3.15.2    | Independent watchdog timer                               | 22    |

|-------------|-------|-----------|----------------------------------------------------------|-------|

|             | 3.16  | Веере     | r                                                        | 23    |

|             | 3.17  | Comm      | unication interfaces                                     | 23    |

|             |       | 3.17.1    | SPI                                                      | 23    |

|             |       | 3.17.2    | I <sup>2</sup> C                                         | 23    |

|             |       | 3.17.3    | USART                                                    | 24    |

|             | 3.18  | Infrare   | d (IR) interface                                         | 24    |

|             | 3.19  | Develo    | ppment support                                           | 24    |

| 4           | Pin o | descrip   | tion                                                     | 25    |

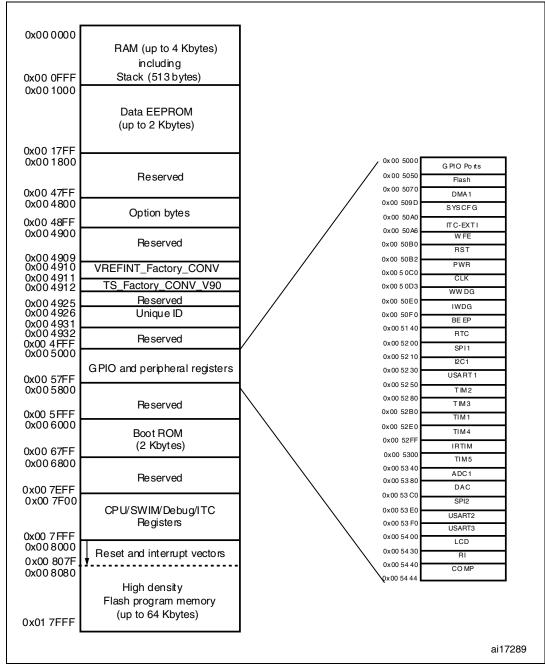

| 5           | Mem   | ory and   | d register map                                           | 40    |

|             | 5.1   | Memo      | ry mapping                                               | 40    |

|             | 5.2   | Regist    | er map                                                   | 41    |

| 6           | Inter | rupt ve   | ctor mapping                                             | 61    |

| 7           | Opti  | on byte   | s                                                        | 63    |

|             |       |           |                                                          |       |

| 8           | Uniq  | ue ID .   |                                                          | 66    |

| 9           | Elec  | trical pa | arameters                                                | 67    |

|             | 9.1   | Param     | eter conditions                                          | 67    |

|             |       | 9.1.1     | Minimum and maximum values                               | 67    |

|             |       | 9.1.2     | Typical values                                           | 67    |

|             |       | 9.1.3     | Typical curves                                           | 67    |

|             |       | 9.1.4     | Loading capacitor                                        | 67    |

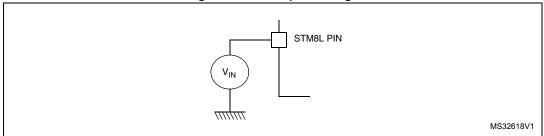

|             |       | 9.1.5     | Pin input voltage                                        | 68    |

|             | 9.2   | Absolu    | ite maximum ratings                                      | 68    |

|             | 9.3   | Opera     | ting conditions                                          | 70    |

|             |       | 9.3.1     | General operating conditions                             | 70    |

|             |       | 9.3.2     | Embedded reset and power control block characteristics . | 71    |

|             |       | 9.3.3     | Supply current characteristics                           | 74    |

|             |       | 9.3.4     | Clock and timing characteristics                         | 89    |

|             |       | 9.3.5     | Memory characteristics                                   | 94    |

|             |       | 9.3.6     | I/O current injection characteristics                    | 96    |

|             |       | 9.3.7     | I/O port pin characteristics                             | 96    |

| <b>\7</b> / |       |           | DocID17943 Rev 10                                        | 3/146 |

| 12 | Revis | sion his | tory                               |

|----|-------|----------|------------------------------------|

| 11 | Orde  | ring inf | ormation scheme141                 |

|    | 10.5  | WLCSI    | P32 package information            |

|    | 10.4  | UFQFF    | N48 package information            |

|    | 10.3  | LQFP4    | 8 package information              |

|    | 10.2  | LQFP6    | 4 package information              |

|    | 10.1  | LQFP8    | 0 package information              |

| 10 | Pack  | age info | ormation                           |

|    | 9.4   | Therma   | al characteristics                 |

|    |       | 9.3.15   | EMC characteristics                |

|    |       | 9.3.14   | 12-bit ADC1 characteristics        |

|    |       | 9.3.13   | 12-bit DAC characteristics         |

|    |       | 9.3.12   | Comparator characteristics         |

|    |       | 9.3.11   | Temperature sensor                 |

|    |       | 9.3.10   | Embedded reference voltage         |

|    |       | 9.3.9    | LCD controller (STM8L152x6/8 only) |

|    |       | 9.3.8    | Communication interfaces           |

# List of tables

| Table 1.             | Device summary                                                                       | . 1 |

|----------------------|--------------------------------------------------------------------------------------|-----|

| Table 2.             | High-density and medium+ density STM8L15xx6/8 low power device features and          |     |

| Table 3.             | peripheral counts                                                                    |     |

| Table 3.             | Legend/abbreviation                                                                  |     |

| Table 4.             | High-density and medium+ density STM8L15x pin description                            |     |

| Table 5.             | Flash and RAM boundary addresses                                                     |     |

| Table 7.             | Factory conversion registers                                                         |     |

|                      |                                                                                      |     |

| Table 8.<br>Table 9. | I/O port hardware register map                                                       |     |

| Table 9.             | CPU/SWIM/debug module/interrupt controller registers                                 |     |

| Table 10.            |                                                                                      |     |

| Table 11.            | Interrupt mapping                                                                    |     |

| Table 12.            | ·                                                                                    |     |

| Table 13.            | Option byte description                                                              |     |

| Table 14.            | Voltage characteristics                                                              |     |

| Table 15.            | Current characteristics                                                              |     |

| Table 10.            | Thermal characteristics                                                              |     |

| Table 17.            | General operating conditions                                                         |     |

| Table 16.            | Embedded reset and power control block characteristics                               |     |

| Table 19.            | Total current consumption in Run mode                                                |     |

| Table 20.            | Total current consumption in Wait mode                                               |     |

| Table 21.            | Total current consumption and timing in Low-power run mode at VDD = 1.65 V to 3.6 V. |     |

| Table 22.            | Total current consumption in Low-power wait mode at VDD = 1.65 V to 3.6 V            |     |

| Table 23.            | Total current consumption and timing in Active-halt mode                             | 02  |

| 1 able 24.           | at VDD = 1.65 V to 3.6 V                                                             | 84  |

| Table 25.            | Typical current consumption in Active-halt mode, RTC clocked by LSE external crystal | 86  |

| Table 26.            | Total current consumption and timing in Halt mode at VDD = 1.65 to 3.6 V             | 87  |

| Table 27.            | Peripheral current consumption                                                       | 88  |

| Table 28.            | Current consumption under external reset                                             | 89  |

| Table 29.            | HSE external clock characteristics                                                   | 89  |

| Table 30.            | LSE external clock characteristics                                                   | 90  |

| Table 31.            | HSE oscillator characteristics                                                       | 90  |

| Table 32.            | LSE oscillator characteristics                                                       | 91  |

| Table 33.            | HSI oscillator characteristics                                                       | 92  |

| Table 34.            | LSI oscillator characteristics                                                       | 93  |

| Table 35.            | RAM and hardware registers                                                           | 94  |

| Table 36.            | Flash program and data EEPROM memory                                                 | 95  |

| Table 37.            | I/O current injection susceptibility                                                 | 96  |

| Table 38.            | I/O static characteristics                                                           | 97  |

| Table 39.            | Output driving current (high sink ports)                                             | 100 |

| Table 40.            | Output driving current (true open drain ports)                                       | 100 |

| Table 41.            | Output driving current (PA0 with high sink LED driver capability)                    | 100 |

| Table 42.            | NRST pin characteristics                                                             |     |

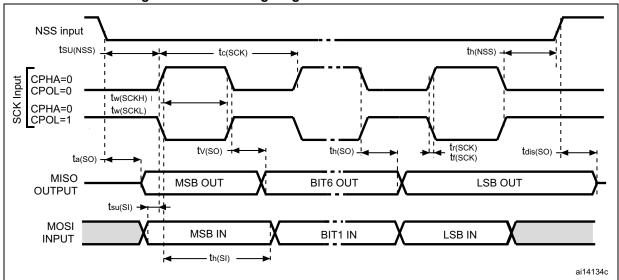

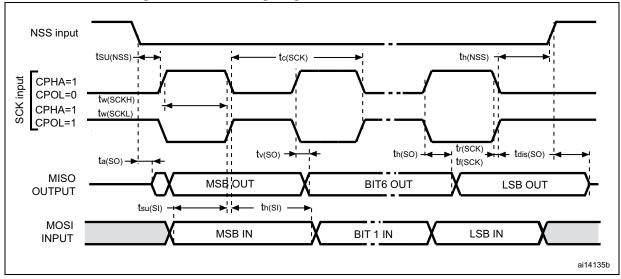

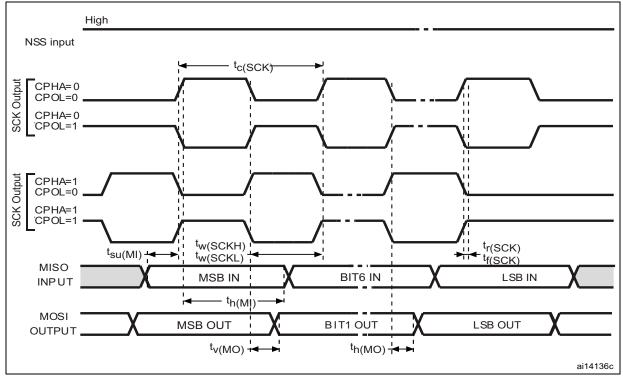

| Table 43.            | SPI1 characteristics                                                                 | 104 |

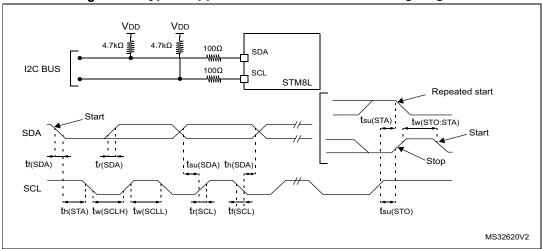

| Table 44.            | I2C characteristics                                                                  | 107 |

| Table 45.            | LCD characteristics                                                                  | 109 |

| Table 46.            | Reference voltage characteristics                                                    | 110 |

DocID17943 Rev 10

5/146

#### List of tables

#### STM8L151x6/8 STM8L152x6/8

| Table 47. | TS characteristics                                                        | 111 |

|-----------|---------------------------------------------------------------------------|-----|

| Table 48. | Comparator 1 characteristics                                              | 111 |

| Table 49. | Comparator 2 characteristics                                              | 112 |

| Table 50. | DAC characteristics                                                       | 113 |

| Table 51. | DAC accuracy                                                              | 114 |

| Table 52. | DAC output on PB4-PB5-PB6                                                 | 114 |

| Table 53. | ADC1 characteristics                                                      |     |

| Table 54. | ADC1 accuracy with VDDA = 3.3 V to 2.5 V                                  | 117 |

| Table 55. | ADC1 accuracy with VDDA = 2.4 V to 3.6 V                                  | 117 |

| Table 56. | ADC1 accuracy with VDDA = VREF+ = 1.8 V to 2.4 V                          | 117 |

| Table 57. | R <sub>AIN</sub> max for f <sub>ADC</sub> = 16 MHz                        | 119 |

| Table 58. | EMS data                                                                  | 121 |

| Table 59. | EMI data                                                                  | 122 |

| Table 60. | ESD absolute maximum ratings                                              | 122 |

| Table 61. | Electrical sensitivities                                                  | 123 |

| Table 62. | Thermal characteristics                                                   | 123 |

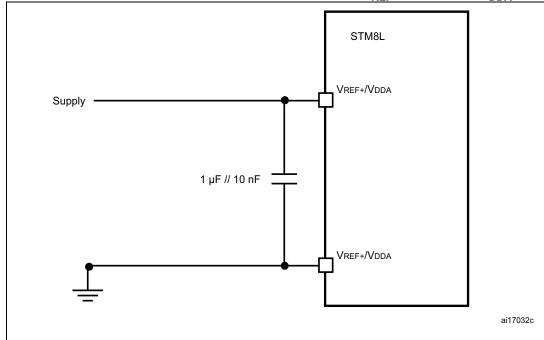

| Table 63. | LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package                 |     |

|           | mechanical data                                                           | 125 |

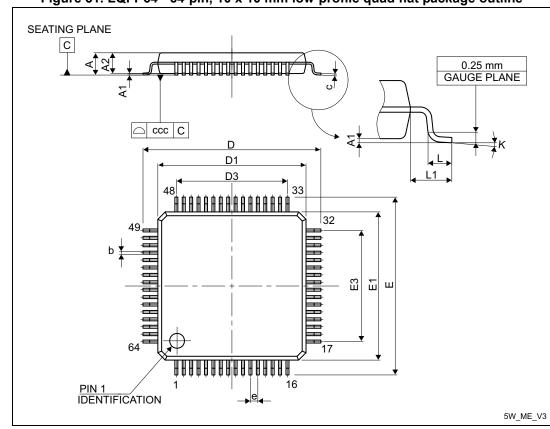

| Table 64. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat                         |     |

|           | package mechanical data                                                   | 128 |

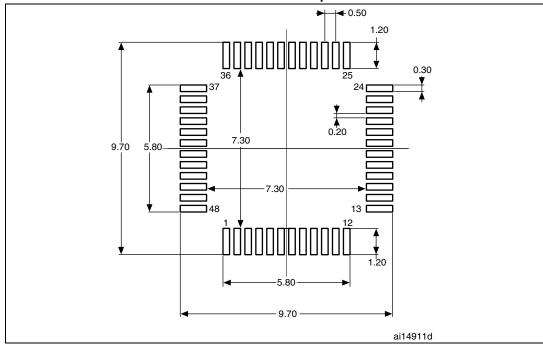

| Table 65. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                   |     |

|           | mechanical data                                                           | 132 |

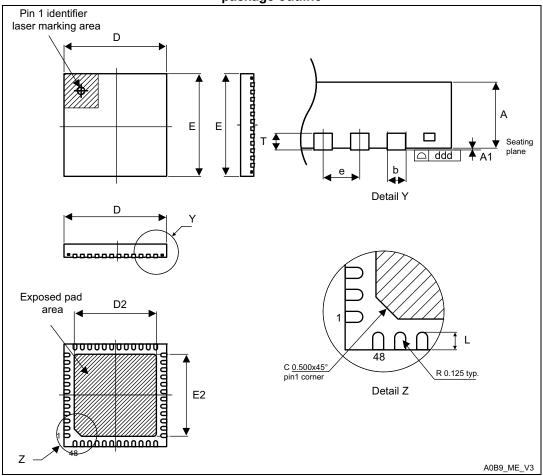

| Table 66. | UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |     |

|           | package mechanical data                                                   | 136 |

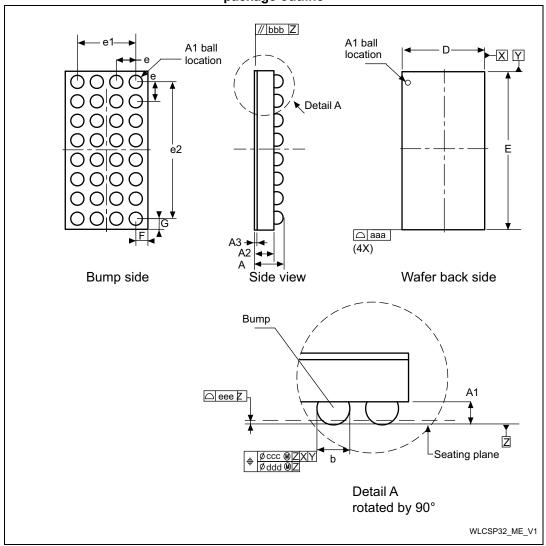

| Table 67. | WLCSP32 - 32-ball, 1.913 x 3.329 mm, 0.4 mm pitch wafer level chip scale  |     |

|           | package mechanical data                                                   | 139 |

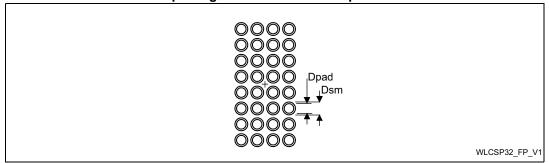

| Table 68. | WLCSP32 recommended PCB design rules                                      |     |

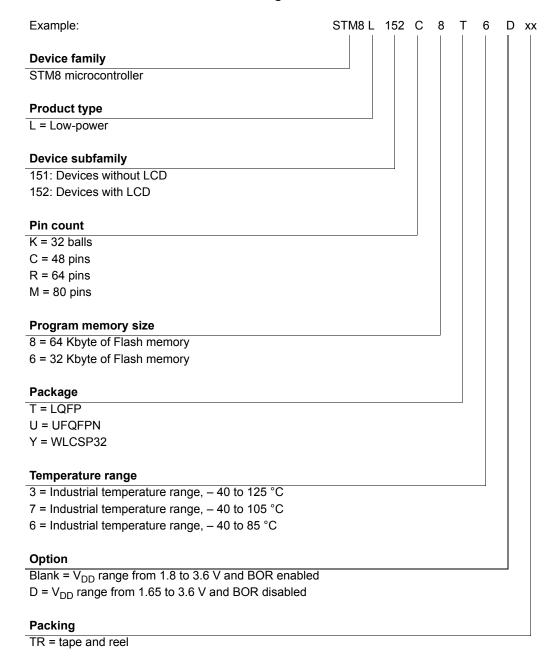

| Table 69. | Ordering information scheme                                               | 141 |

| Table 70. | Document revision history                                                 | 142 |

|           |                                                                           |     |

# List of figures

| Figure 1.  | High-density and medium+ density STM8L15xx6/8 device block diagram                                     | 13  |

|------------|--------------------------------------------------------------------------------------------------------|-----|

| Figure 1.  | Clock tree diagram                                                                                     |     |

| Figure 3.  | STM8L151M8 80-pin package pinout (without LCD)                                                         |     |

| Figure 3.  | ,                                                                                                      |     |

| -          | STM8L152M8 80-pin package pinout (with LCD)                                                            |     |

| Figure 5.  | STM8L151R8 and STM8L151R6 64-pin pinout (without LCD)                                                  |     |

| Figure 6.  | STM8L152R8 and STM8L152R6 64-pin pinout (with LCD)                                                     |     |

| Figure 7.  | STM8L151C8 48-pin pinout (without LCD)                                                                 |     |

| Figure 8.  | STM8L152C8 48-pin pinout (with LCD)                                                                    |     |

| Figure 9.  | STM8L152K8 32-ball ballout                                                                             |     |

| Figure 10. | Memory map                                                                                             |     |

| Figure 11. | Pin loading conditions                                                                                 |     |

| Figure 12. | Pin input voltage                                                                                      |     |

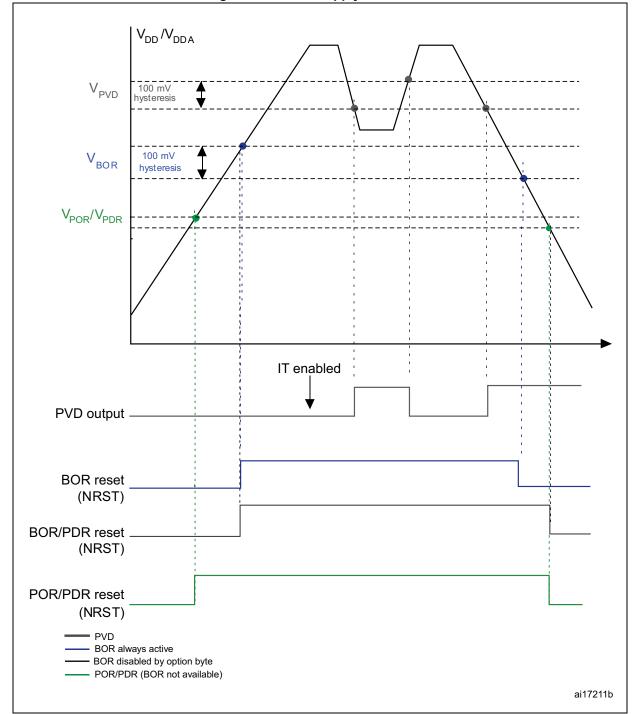

| Figure 13. | Power supply thresholds                                                                                |     |

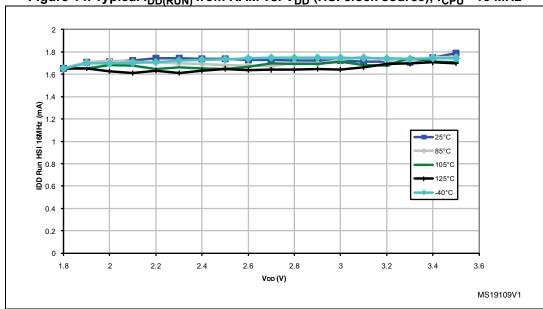

| Figure 14. | Typical I <sub>DD(RUN)</sub> from RAM vs. V <sub>DD</sub> (HSI clock source), f <sub>CPU</sub> =16 MHz | 76  |

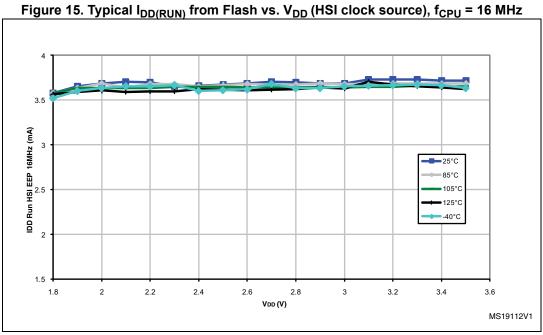

| Figure 15. | Typical $I_{DD(RUN)}$ from Flash vs. $V_{DD}$ (HSI clock source), $f_{CPU} = 16 \text{ MHz} \dots$     | 76  |

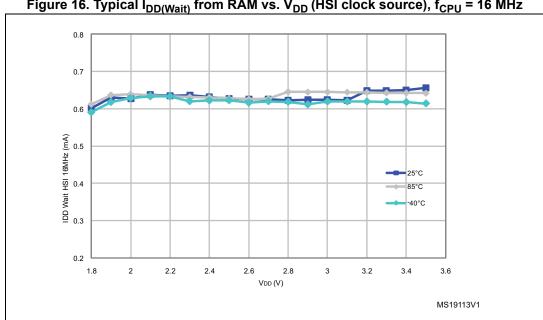

| Figure 16. | Typical $I_{DD(Wait)}$ from RAM vs. $V_{DD}$ (HSI clock source), $f_{CPU} = 16$ MHz                    | 79  |

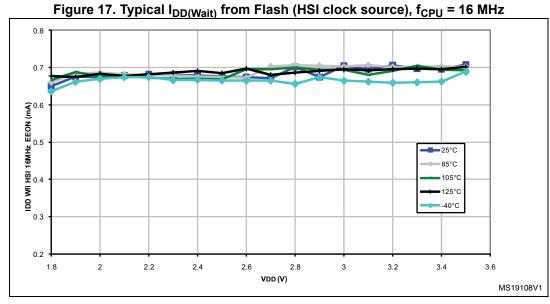

| Figure 17. | Typical I <sub>DD(Wait)</sub> from Flash (HSI clock source), f <sub>CPU</sub> = 16 MHz                 |     |

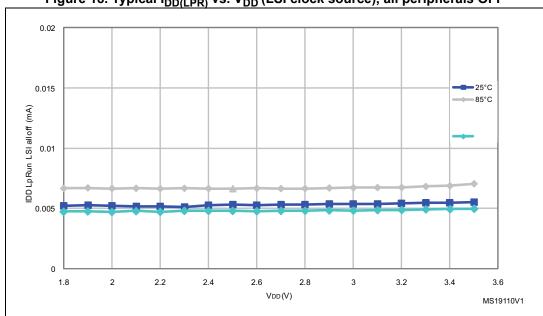

| Figure 18. | Typical I <sub>DD(LPR)</sub> vs. V <sub>DD</sub> (LSI clock source), all peripherals OFF               |     |

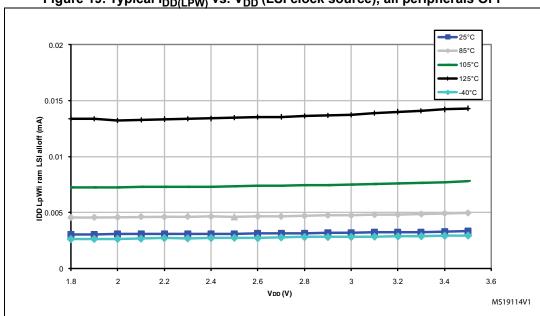

| Figure 19. | Typical I <sub>DD(LPW)</sub> vs. V <sub>DD</sub> (LSI clock source), all peripherals OFF               | 83  |

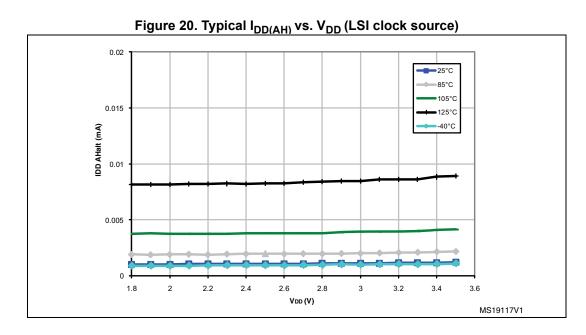

| Figure 20. | Typical IDD(AH) vs. V <sub>DD</sub> (LSI clock source)                                                 |     |

| Figure 21. | Typical IDD(Halt) vs. V <sub>DD</sub> (internal reference voltage OFF)                                 |     |

| Figure 22. | HSE oscillator circuit diagram                                                                         |     |

| Figure 23. | LSE oscillator circuit diagram                                                                         |     |

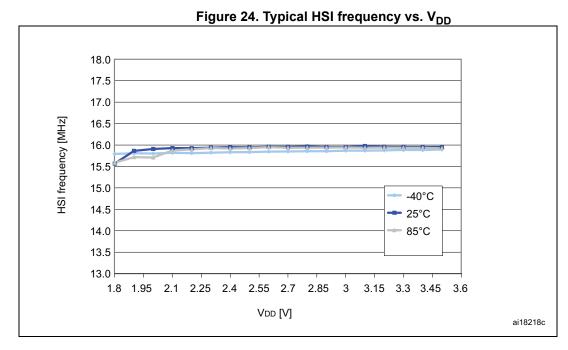

| Figure 24. | Typical HSI frequency vs. V <sub>DD</sub>                                                              |     |

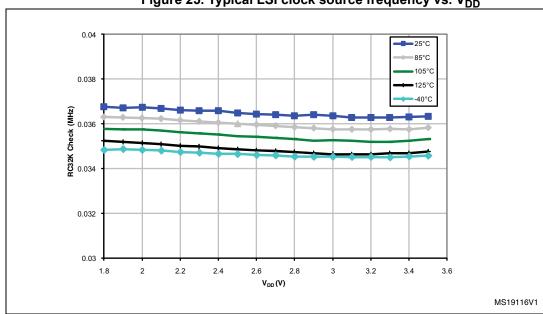

| Figure 25. | Typical LSI clock source frequency vs. VDD                                                             |     |

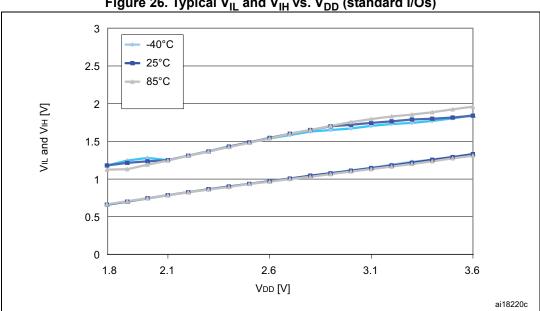

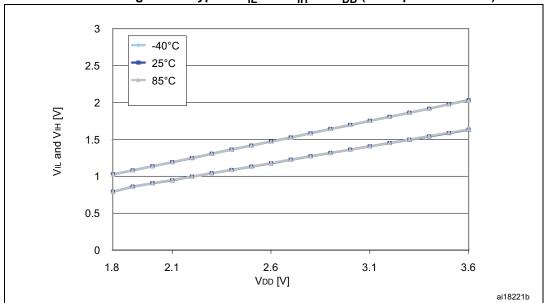

| Figure 26. | Typical VIL and VIH vs. VDD (standard I/Os)                                                            |     |

| Figure 27. | Typical VIL and VIH vs. VDD (standard 1/03)                                                            |     |

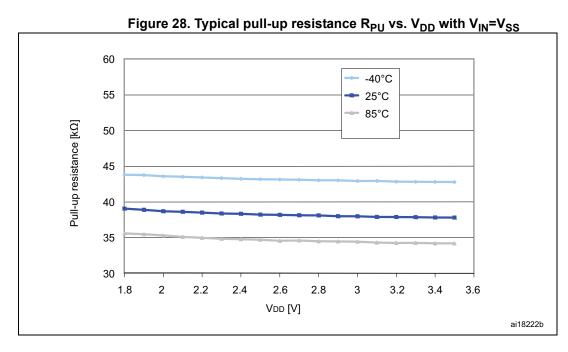

| Figure 28. | Typical vill and viri vs. vbb (tide open diam vos)                                                     |     |

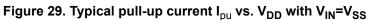

| Figure 29. | Typical pull-up current I <sub>pu</sub> vs. V <sub>DD</sub> with VIN=VSS                               |     |

| -          |                                                                                                        |     |

| Figure 30. | Typical VOL @ VDD = 3.0 V (high sink ports)                                                            |     |

| Figure 31. | Typical VOL @ VDD = 1.8 V (high sink ports)                                                            |     |

| Figure 32. | Typical VOL @ VDD = 3.0 V (true open drain ports)                                                      |     |

| Figure 33. | Typical VOL @ VDD = 1.8 V (true open drain ports)                                                      |     |

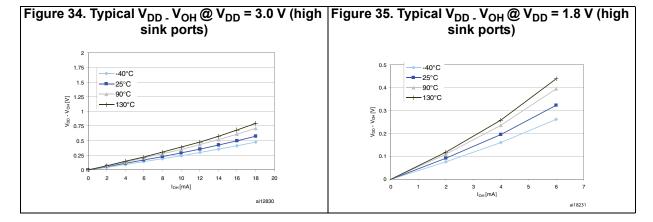

| Figure 34. | Typical VDD - VOH @ VDD = 3.0 V (high sink ports)                                                      |     |

| Figure 35. | Typical VDD - VOH @ VDD = 1.8 V (high sink ports)                                                      |     |

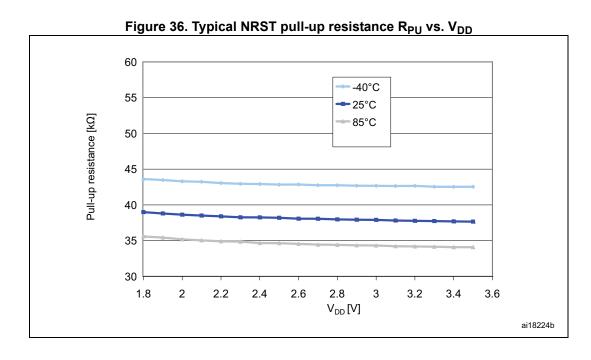

| Figure 36. | Typical NRST pull-up resistance R <sub>PU</sub> vs. V <sub>DD</sub>                                    |     |

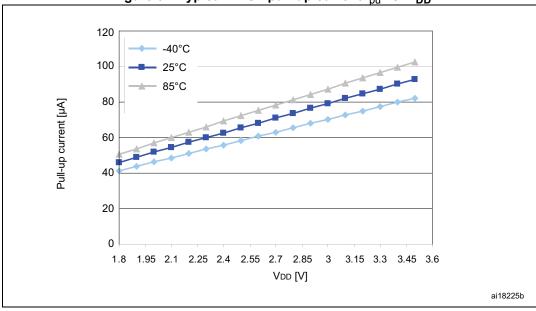

| Figure 37. | Typical NRST pull-up current I <sub>pu</sub> vs. V <sub>DD</sub>                                       |     |

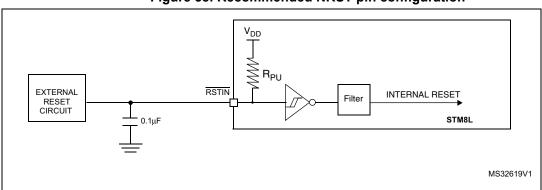

| Figure 38. | Recommended NRST pin configuration                                                                     |     |

| Figure 39. | SPI1 timing diagram - slave mode and CPHA=0                                                            | 105 |

| Figure 40. | SPI1 timing diagram - slave mode and CPHA=1                                                            | 105 |

| Figure 41. | SPI1 timing diagram - master mode                                                                      |     |

| Figure 42. | Typical application with I2C bus and timing diagram                                                    | 108 |

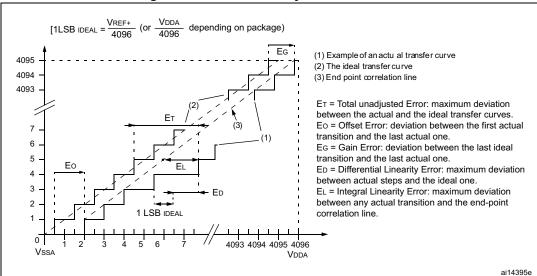

| Figure 43. | ADC1 accuracy characteristics                                                                          | 118 |

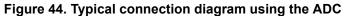

| Figure 44. | Typical connection diagram using the ADC                                                               | 118 |

| Figure 45. | Maximum dynamic current consumption on V <sub>REF+</sub> supply pin during ADC                         |     |

| -          | conversion                                                                                             | 119 |

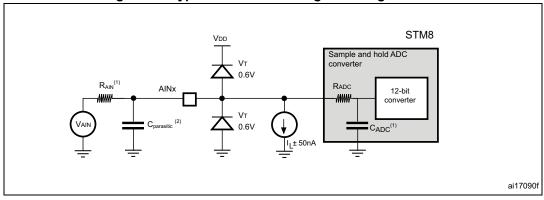

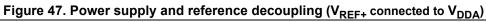

| Figure 46. | Power supply and reference decoupling (V <sub>REF+</sub> not connected to V <sub>DDA</sub> )           |     |

| Figure 47. | Power supply and reference decoupling (VREF+ connected to VDDA)                                        |     |

|            |                                                                                                        |     |

| Figure 48. | LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package outline         | 124 |

|------------|---------------------------------------------------------------------------|-----|

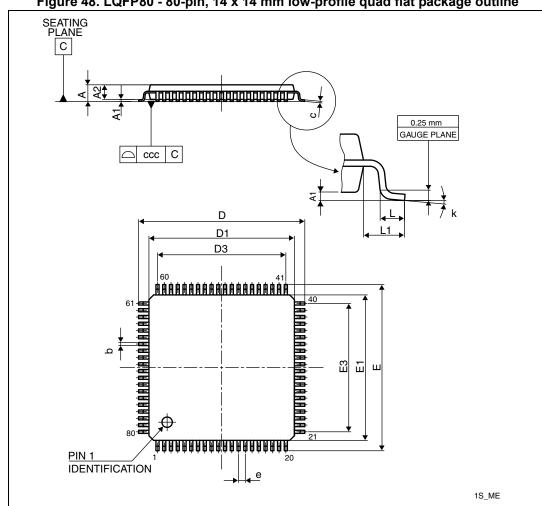

| Figure 49. | LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package                 |     |

| •          | recommended footprint                                                     | 126 |

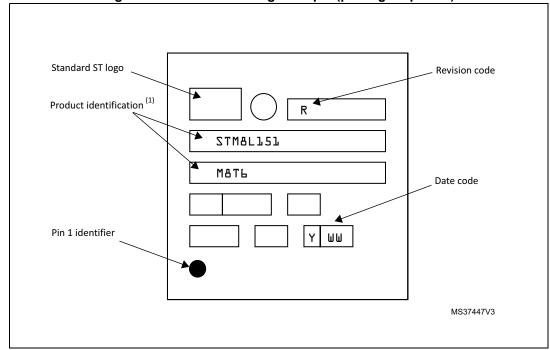

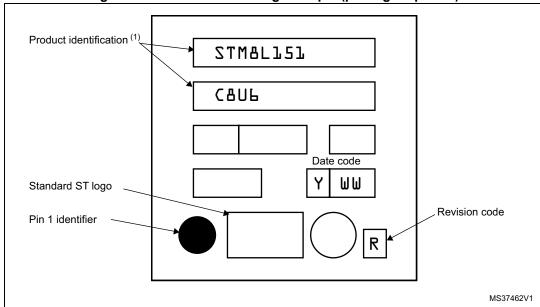

| Figure 50. | LQFP80 marking example (package top view)                                 |     |

| Figure 51. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline         |     |

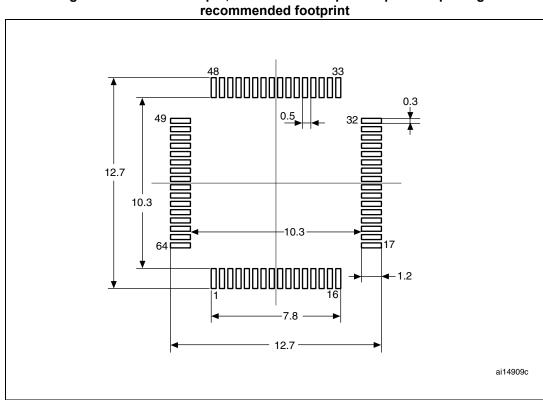

| Figure 52. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package                 |     |

| •          | recommended footprint                                                     | 129 |

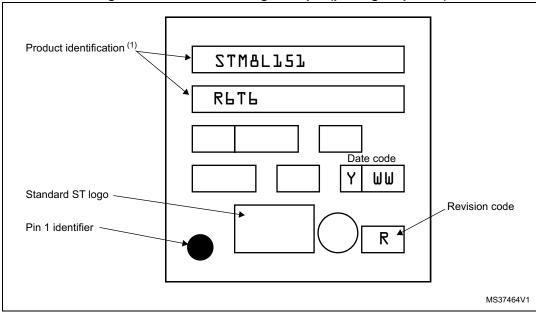

| Figure 53. | LQFP64 marking example (package top view)                                 |     |

| Figure 54. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline           |     |

| Figure 55. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                   |     |

| •          | recommended footprint                                                     | 133 |

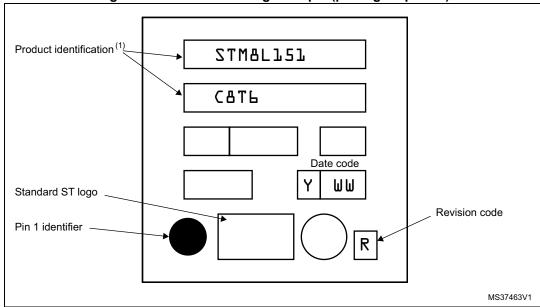

| Figure 56. | LQFP48 marking example (package top view)                                 |     |

| Figure 57. | UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |     |

| J          | package outline                                                           | 135 |

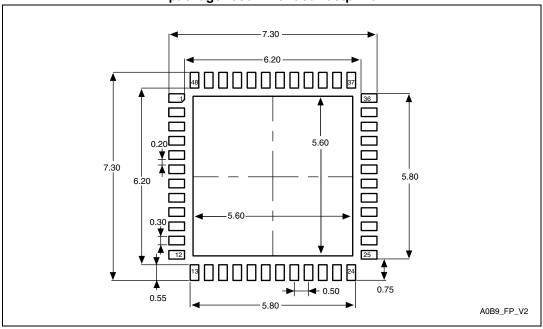

| Figure 58. | UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |     |

| J          | package recommended footprint                                             | 136 |

| Figure 59. | UFQFPN48 marking example (package top view)                               |     |

| Figure 60. | WLCSP32 - 32-ball, 1.913 x 3.329 mm, 0.4 mm pitch wafer level chip scale  |     |

| J          | package outline                                                           | 138 |

| Figure 61. | WLCSP32 - 32-ball, 1.913 x 3.329 mm, 0.4 mm pitch wafer level chip scale  |     |

| ŭ          | package recommended footprint                                             | 139 |

### 1 Introduction

This document describes the features, pinout, mechanical data and ordering information for: devices.

- High-density STM8L15xxx devices: STM8L151x8 and STM8L152x8 microcontrollers with a Flash memory density of 64 Kbyte.

- Medium+ density STM8L15xxx devices: STM8L151R6 and STM8L152R6 microcontrollers with Flash memory density of 32 Kbyte.

For further details on the STMicroelectronics ultra-low-power family please refer to Section 2.3: Ultra-low-power continuum on page 12.

For detailed information on device operation and registers, refer to the reference manual (RM0031).

For information on to the Flash program memory and data EEPROM, refer to the programming manual (PM0054).

For information on the debug module and SWIM (single wire interface module), refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).

For information on the STM8 core, refer to the STM8 CPU programming manual (PM0044).

### 2 Description

The high-density and medium+ density STM8L15xx6/8 ultra-low-power devices feature an enhanced STM8 CPU core providing increased processing power (up to 16 MIPS at 16 MHz) while maintaining the advantages of a CISC architecture with improved code density, a 24-bit linear addressing space and an optimized architecture for low-power operations.

The family includes an integrated debug module with a hardware interface (SWIM) which allows non-intrusive in-application debugging and ultrafast Flash programming.

All high-density and medium+ density STM8L15xx6/8 microcontrollers feature embedded data EEPROM and low-power low-voltage single-supply program Flash memory.

The devices incorporate an extensive range of enhanced I/Os and peripherals, a 12-bit ADC, two DACs, two comparators, a real-time clock, four 16-bit timers, one 8-bit timer, as well as standard communication interfaces such as two SPIs, an I<sup>2</sup>C interface, and three USARTs. A 8x40 or 4x44-segment LCD is available on the STM8L152x8 devices. The modular design of the peripheral set allows the same peripherals to be found in different ST microcontroller families including 32-bit families. This makes any transition to a different family very easy, and simplified even more by the use of a common set of development tools.

### 2.1 STM8L ultra-low-power 8-bit family benefits

High-density and medium+ density STM8L15xx6/8 devices are part of the STM8L ultra-low-power family providing the following benefits:

- Integrated system

- Up to 64 Kbyte of high-density embedded Flash program memory

- Up to 2 Kbyte of data EEPROM

- Up to 4 Kbyte of RAM

- Internal high-speed and low-power low speed RC.

- Embedded reset

- ultra-low-power consumption

- 1 µA in Active-halt mode

- Clock gated system and optimized power management

- Capability to execute from RAM for Low-power wait mode and Low-power run mode

- Advanced features

- Up to 16 MIPS at 16 MHz CPU clock frequency

- Direct memory access (DMA) for memory-to-memory or peripheral-to-memory access.

- Short development cycles

- Application scalability across a common family product architecture with compatible pinout, memory map and modular peripherals.

- Wide choice of development tools

STM8L ultra-low-power microcontrollers can operate either from 1.8 to 3.6 V (down to 1.65 V at power-down) or from 1.65 to 3.6 V. They are available in the -40 to +85  $^{\circ}$ C and -40 to +125  $^{\circ}$ C temperature ranges.

These features make the STM8L ultra-low-power microcontroller families suitable for a wide range of applications:

- Medical and handheld equipment

- Application control and user interface

- PC peripherals, gaming, GPS and sport equipment

- Alarm systems, wired and wireless sensors

- Metering

The devices are offered in five different packages from 32 to 80 pins. Different sets of peripherals are included depending on the device. Refer to Section 3 for an overview of the complete range of peripherals proposed in this family.

All STM8L ultra-low-power products are based on the same architecture with the same memory mapping and a coherent pinout.

*Figure 1* shows the block diagram of the High-density and medium+ density STM8L15xx6/8 families.

### 2.2 Device overview

Table 2. High-density and medium+ density STM8L15xx6/8 low power device features and peripheral counts

| Fea                                  | atures                                                               | STM8L15xC8                                                                                                             | STM8L15xK8                            | STM8L15xR8                           | STM8L15xM8                                              | STM8L15xR6        |  |  |  |  |

|--------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------|---------------------------------------------------------|-------------------|--|--|--|--|

| Flash (Kbyte)                        |                                                                      | 64                                                                                                                     | 64                                    | 64                                   | 64                                                      | 32                |  |  |  |  |

| Data EEPROM (                        | (Kbyte)                                                              | 2                                                                                                                      | 2                                     | 2                                    | 2                                                       | 1                 |  |  |  |  |

| RAM (Kbyte)                          |                                                                      | 4                                                                                                                      | 4                                     | 4                                    | 4                                                       | 2                 |  |  |  |  |

| LCD                                  |                                                                      | 8x24 or<br>4x28 <sup>(1)</sup>                                                                                         | 4x15 <sup>(1)</sup>                   | 8x36 or<br>4x40 <sup>(1)</sup>       | 8x40 or 8x36 or 4x44 <sup>(1)</sup> 4x40 <sup>(1)</sup> |                   |  |  |  |  |

|                                      | Basic                                                                | 1<br>(8-bit)                                                                                                           | 1<br>(8-bit)                          | 1<br>(8-bit)                         | 1<br>(8-bit)                                            | 1<br>(8-bit)      |  |  |  |  |

| Timers                               | General purpose                                                      | 3<br>(16-bit)                                                                                                          | 3<br>(16-bit)                         | 3<br>(16-bit)                        | 3<br>(16-bit)                                           | 3<br>(16-bit)     |  |  |  |  |

|                                      | Advanced control                                                     | 1<br>(16-bit)                                                                                                          | 1<br>(16-bit)                         | 1<br>(16-bit)                        | 1<br>(16-bit)                                           | 1<br>(16-bit)     |  |  |  |  |

|                                      | SPI                                                                  | 2                                                                                                                      | 1                                     | 2                                    | 2                                                       | 2                 |  |  |  |  |

| Communication interfaces             | I2C                                                                  | 1                                                                                                                      | 1                                     | 1                                    | 1                                                       | 1                 |  |  |  |  |

| e.r.aeee                             | USART                                                                | 3                                                                                                                      | 2                                     | 3                                    | 3                                                       | 3                 |  |  |  |  |

| GPIOs                                |                                                                      | 41 <sup>(2)</sup>                                                                                                      | 28 <sup>(2)</sup>                     | 54 <sup>(2)</sup>                    | 68 <sup>(2)</sup>                                       | 54 <sup>(2)</sup> |  |  |  |  |

| 12-bit synchroniz<br>(number of chan |                                                                      | 1<br>(25)                                                                                                              | 1<br>(18)                             | 1<br>(28)                            | 1<br>(28)                                               | 1<br>(28)         |  |  |  |  |

| 12-Bit DAC                           |                                                                      | 2                                                                                                                      | 1                                     | 2                                    | 2                                                       | 2                 |  |  |  |  |

| Number of chan                       | nels                                                                 | 2                                                                                                                      | 1                                     | 2                                    | 2                                                       | 2                 |  |  |  |  |

| Comparators (C                       | OMP1/COMP2)                                                          | 2                                                                                                                      | 2                                     | 2                                    | 2                                                       | 2                 |  |  |  |  |

| Others                               |                                                                      | RTC, window watchdog, independent watchdog, 16-MHz and 38-kHz internal RC, 1- to 16-MHz and 32-kHz external oscillator |                                       |                                      |                                                         |                   |  |  |  |  |

| CPU frequency                        |                                                                      |                                                                                                                        |                                       | 16 MHz                               |                                                         |                   |  |  |  |  |

| Operating voltage                    | e                                                                    | 1.8                                                                                                                    | · · · · · · · · · · · · · · · · · · · | to 1.65 V at pow<br>to 3.6 V without | ver-down) with B<br>BOR                                 | OR                |  |  |  |  |

| Operating temper                     | perating temperature —40 to +85 °C / -40 to +105 °C / -40 to +125 °C |                                                                                                                        |                                       |                                      |                                                         |                   |  |  |  |  |

| Packages                             |                                                                      | UFQFPN48<br>LQFP48                                                                                                     | WLCSP32                               | LQFP64                               | LQFP80 LQFP64                                           |                   |  |  |  |  |

<sup>1.</sup> STM8L152x6/8 versions only.

<sup>2.</sup> The number of GPIOs given in this table includes the NRST/PA1 pin but the application can use the NRST/PA1 pin as general purpose output only (PA1).

### 2.3 Ultra-low-power continuum

The ultra-low-power STM8L151x6/8, STM8L152x6/8 and STM8L162x8 are fully pin-to-pin, software and feature compatible. Besides the full compatibility within the family, the devices are part of STMicroelectronics microcontrollers ultra-low-power strategy which also includes STM8L101 line, STM8L151/152 lines, and STM8L162 line. The STM8L and STM32L families allow a continuum of performance, peripherals, system architecture, and features.

They are all based on STMicroelectronics 0.13 µm ultra low-leakage process.

Note: 1 The STM8L151xx and STM8L152xx are pin-to-pin compatible with STM8L101xx devices.

The STM32L family is pin-to-pin compatible with the general purpose STM32F family. Please refer to STM32Lxxxxx documentation for more information on these devices.

#### **Performance**

All families incorporate highly energy-efficient cores with both Harvard architecture and pipelined execution: advanced STM8 core for STM8L families and ARM® Cortex®-M3 core for STM32L family. In addition specific care for the design architecture has been taken to optimize the mA/DMIPS and mA/MHz ratios.

This allows the ultra-low-power performance to range from 5 up to 33.3 DMIPs.

#### Shared peripherals

STM8L15xx6/8 and STM32Lxxxxx share identical peripherals which ensure a very easy migration from one family to another:

- Analog peripherals: ADC1, DAC1/DAC2, and comparators COMP1/COMP2

- Digital peripherals: RTC and some communication interfaces

#### **Common system strategy**

To offer flexibility and optimize performance, the STM8L15xx6/8 and STM32Lxxxxx devices use a common architecture:

- Same power supply range from 1.65 to 3.6 V. For STM8L101xx and medium-density STM8L15xxx, the power supply must be above 1.8 V at power-on, and go below 1.65 V at power-down.

- Architecture optimized to reach ultra low consumption both in low-power modes and Run mode

- Fast startup strategy from low-power modes

- Flexible system clock

- Ultra safe reset: same reset strategy for both STM8L15xx6/8 and STM32Lxxxxx including power-on reset, power-down reset, brownout reset and programmable voltage detector.

#### **Features**

STMicroelectronics ultra-low-power continuum also lies in feature compatibility:

- More than 10 packages with pin counts from 20 to 100 pins and size down to 3 x 3 mm

- Memory density ranging from 4 to 128 Kbyte

57

#### 3 **Functional overview**

OSC\_IN, OSC\_OUT  $@V_{DD}$ 1-16 MHz oscillator V<sub>DD</sub>=1.65 V to 3.6 V V<sub>DD18</sub>◆ Power Clock 16 MHz internal RC controller  $v_{SS}$ VOLT. REG OSC32 IN and CSS 32 kHz oscillator Clocks OSC32\_OUT to core and 38 kHz internal RC peripherals NRST RESET Interrupt controller POR/PDR STM8 Core Debug module BOR SWIM (SWIM) PVD\_IN PVD 3 channels 16-bit Timer 1 2 channels 16-bit Timer 2 up to 16-bit Timer 3 64-Kbyte 2 channels Program memory 8-bit Timer 4 databuses up to 2-Kbyte Data EEPROM 2 channels 16-bit Timer 5 IR\_TIM ב Infrared interface up to 4-Kbyte RAM and DMA1 (4 channels) PA[7:0]

PBI7:01 SCL, SDA, SMB Port A control I<sup>2</sup>C1 SPI1\_MOSI, SPI1\_MISO, Port B SPI1 SPI1\_SCK, SPI1\_NSS PC[7:0] SPI2\_MOSI, SPI2\_MISO, Port C SPI2 SPI2\_SCK, SPI2\_NSS PD[7:0] Port D USART1\_RX, USART1\_TX, USART1\_CK USART1 PE[7:0] Port E USART2\_RX, USART2\_TX, USART2 USART2\_CK PF[7:0] USART3\_RX, USART3\_TX, USART3\_CK Port F USART3 PG[7:0] Port G V<sub>DDA</sub>, V<sub>SSA</sub> PH[7:0] Port H ADC1\_INx 12-bit ADC1 PI[3:0] V<sub>REF+</sub> Port I V<sub>REF-</sub> BEEP Temp sensor Beeper ALARM, CALIB, TAMP1/2/3 RTC Internal reference VREFINT out IWDG voltage (38 kHz clock) COMP1\_INP COMP2\_INP COMP2\_INM COMP 1 WWDG COMP 2 DAC1\_OUT 🞝 12-bit DAC1 LCD driver SEGx, COMx DAC2\_OUT 12-bit DAC2  $V_{LCD} = 2.5 \text{ to } 3.6 \text{ V}$ LCD booster ai17288b

Figure 1. High-density and medium+ density STM8L15xx6/8 device block diagram

#### Legend:

AF: alternate function ADC: Analog-to-digital converter BOR: Brownout reset

DMA: Direct memory access

DAC: Digital-to-analog converter

I2C: Inter-integrated circuit multimaster interface

IWDG: Independent watchdog

DocID17943 Rev 10

13/146

LCD: Liquid crystal display POR/PDR: Power on reset / power-down reset

RTC: Real-time clock

SPI: Serial peripheral interface SWIM: Single wire interface module

USART: Universal synchronous asynchronous receiver transmitter

WWDG: Window watchdog

#### 3.1 Low-power modes

The high-density and medium+ density STM8L15xx6/8 devices support five low-power modes to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

- Wait mode: CPU clock is stopped, but selected peripherals keep running. An internal or external interrupt or a Reset can be used to exit the microcontroller from Wait mode (WFE or WFI mode).

- Low-power run mode: The CPU and the selected peripherals are running. Execution is done from RAM with a low speed oscillator (LSI or LSE). Flash memory and data EEPROM are stopped and the voltage regulator is configured in ultra-low-power mode. The microcontroller enters Low-power run mode by software and can exit from this mode by software or by a reset.

- All interrupts must be masked. They cannot be used to exit the microcontroller from this mode.

- Low-power wait mode: This mode is entered when executing a Wait for event in Lowpower run mode. It is similar to Low-power run mode except that the CPU clock is stopped. The wakeup from this mode is triggered by a Reset or by an internal or external event (peripheral event generated by the timers, serial interfaces, DMA controller (DMA1), comparators and I/O ports). When the wakeup is triggered by an event, the system goes back to Low-power run mode. All interrupts must be masked. They cannot be used to exit the microcontroller from this mode.

- Active-halt mode: CPU and peripheral clocks are stopped, except RTC. The wakeup can be triggered by RTC interrupts, external interrupts or reset.

- Halt mode: CPU and peripheral clocks are stopped, the device remains powered on. The RAM content is preserved. The wakeup is triggered by an external interrupt or reset. A few peripherals have also a wakeup from Halt capability. Switching off the internal reference voltage reduces power consumption. Through software configuration it is also possible to wake up the device without waiting for the internal reference voltage wakeup time to have a fast wakeup time of 5 µs.

### 3.2 Central processing unit STM8

#### 3.2.1 Advanced STM8 Core

The 8-bit STM8 core is designed for code efficiency and performance with an Harvard architecture and a 3-stage pipeline.

It contains 6 internal registers which are directly addressable in each execution context, 20 addressing modes including indexed indirect and relative addressing, and 80 instructions.

#### Architecture and registers

- Harvard architecture

- 3-stage pipeline

- 32-bit wide program memory bus single cycle fetching most instructions

- X and Y 16-bit index registers enabling indexed addressing modes with or without offset and read-modify-write type data manipulations

- 8-bit accumulator

- 24-bit program counter 16 Mbyte linear memory space

- 16-bit stack pointer access to a 64 Kbyte level stack

- 8-bit condition code register 7 condition flags for the result of the last instruction

#### Addressing

- 20 addressing modes

- Indexed indirect addressing mode for lookup tables located anywhere in the address space

- Stack pointer relative addressing mode for local variables and parameter passing

#### Instruction set

- 80 instructions with 2-byte average instruction size

- Standard data movement and logic/arithmetic functions

- 8-bit by 8-bit multiplication

- 16-bit by 8-bit and 16-bit by 16-bit division

- Bit manipulation

- Data transfer between stack and accumulator (push/pop) with direct stack access

- Data transfer using the X and Y registers or direct memory-to-memory transfers

#### 3.2.2 Interrupt controller

The high-density and medium+ density STM8L15xx6/8x devices feature a nested vectored interrupt controller:

- Nested interrupts with 3 software priority levels

- 32 interrupt vectors with hardware priority

- Up to 40 external interrupt sources on 11 vectors

- Trap and reset interrupts

DocID17943 Rev 10

15/146

### 3.3 Reset and supply management

### 3.3.1 Power supply scheme

The device requires a 1.65 V to 3.6 V operating supply voltage ( $V_{DD}$ ). The external power supply pins must be connected as follows:

- V<sub>SS1</sub>, V<sub>DD1</sub>, V<sub>SS2</sub>, V<sub>DD2</sub>, V<sub>SS3</sub>, V<sub>DD3</sub>, V<sub>SS4</sub>, V<sub>DD4</sub>= 1.65 to 3.6 V: external power supply for I/Os and for the internal regulator. Provided externally through V<sub>DD</sub> pins, the corresponding ground pin is V<sub>SS</sub>. V<sub>SS1</sub>/V<sub>SS2</sub>/V<sub>SS3</sub>/V<sub>SS4</sub> and V<sub>DD1</sub>/V<sub>DD2</sub>/V<sub>DD3</sub>/V<sub>DD4</sub> must not be left unconnected.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.65 to 3.6 V: external power supplies for analog peripherals (minimum voltage to be applied to V<sub>DDA</sub> is 1.8 V when the ADC1 is used). V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>REF+</sub>, V<sub>REF-</sub> (for ADC1): external reference voltage for ADC1. Must be provided externally through V<sub>REF+</sub> and V<sub>REF-</sub> pin.

- V<sub>REF+</sub> (for DAC1/2): external voltage reference for DAC1 and DAC2 must be provided externally through V<sub>REF+</sub>.

### 3.3.2 Power supply supervisor

The device has an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR). For the device sales types without the "D" option (see *Section 11: Ordering information scheme*), it is coupled with a brownout reset (BOR) circuitry. It that case the device operates between 1.8 and 3.6 V, BOR is always active and ensures proper operation starting from 1.8 V. After the 1.8 V BOR threshold is reached, the option byte loading process starts, either to confirm or modify default thresholds, or to disable BOR permanently (in which case, the V<sub>DD</sub> min. value at power-down is 1.65 V).

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Halt mode, it is possible to automatically switch off the internal reference voltage (and consequently the BOR) in Halt mode. The device remains in reset state when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

Note:

For device sales types with the "D" option (see Section 11: Ordering information scheme) BOR is permanently disabled and the device operates between 1.65 and 3.6 V. In this case it is not possible to enable BOR through the option bytes.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

57/

#### 3.3.3 Voltage regulator

The high-density and medium+ density STM8L15xx6/8 devices embed an internal voltage regulator for generating the 1.8 V power supply for the core and peripherals.

This regulator has two different modes:

- Main voltage regulator mode (MVR) for Run, Wait for interrupt (WFI) and Wait for event (WFE) modes.

- Low-power voltage regulator mode (LPVR) for Halt, Active-halt, Low-power run and Low-power wait modes.

When entering Halt or Active-halt modes, the system automatically switches from the MVR to the LPVR in order to reduce current consumption.

### 3.4 Clock management

The clock controller distributes the system clock (SYSCLK) coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness.

#### **Features**

- Clock prescaler: to get the best compromise between speed and current consumption the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler

- **Safe clock switching:** Clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management:** To reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- System clock sources: 4 different clock sources can be used to drive the system clock:

- 1-16 MHz High speed external crystal (HSE)

- 16 MHz High speed internal RC oscillator (HSI)

- 32.768 Low speed external crystal (LSE) available on STM8L151xx and STM8L152xx devices

- 38 kHz Low speed internal RC (LSI)

- RTC and LCD clock sources: the above four sources can be chosen to clock the RTC and the LCD, whatever the system clock.

- **Startup clock:** After reset, the microcontroller restarts by default with an internal 2 MHz clock (HSI/8). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): This feature can be enabled by software. If a HSE clock failure occurs, the system clock is automatically switched to HSI.

- Configurable main clock output (CCO): This outputs an external clock for use by the application.

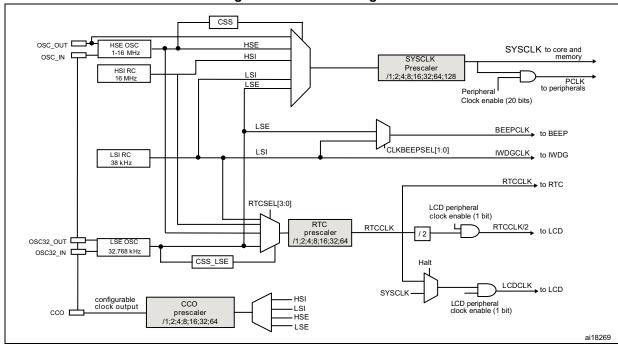

Figure 2. Clock tree diagram

### 3.5 Low-power real-time clock

The real-time clock (RTC) is only available on STM8L151xx and STM8L152xx devices.

The real-time clock (RTC) is an independent binary coded decimal (BCD) timer/counter.

Six byte locations contain the second, minute, hour (12/24 hour), week day, date, month, year, in BCD (binary coded decimal) format. Correction for 28, 29 (leap year), 30, and 31 day months are made automatically. The subsecond field can also be read in binary format.

The calendar can be corrected from 1 to 32767 RTC clock pulses. This allows to make a synchronization to a master clock.

The RTC offers a digital calibration which allows an accuracy of +/-0.5 ppm.

It provides a programmable alarm and programmable periodic interrupts with wakeup from Halt capability.

- Periodic wakeup time using the 32.768 kHz LSE with the lowest resolution (of 61  $\mu$ s) is from min. 122  $\mu$ s to max. 3.9 s. With a different resolution, the wakeup time can reach 36 hours

- Periodic alarms based on the calendar can also be generated from LSE period to every year

A clock security system detects a failure on LSE, and can provide an interrupt with wakeup capability. The RTC clock can automatically switch to LSI in case of LSE failure.

The RTC also provides 3 anti-tamper detection pins. This detection embeds a programmable filter and can wakeup the MCU.

577

## 3.6 LCD (Liquid crystal display)

The LCD is only available on STM8L152x6/8 devices.

The liquid crystal display drives up to 8 common terminals and up to 40 segment terminals to drive up to 320 pixels. It can also be configured to drive up to 4 common and 44 segments (up to 176 pixels).

- Internal step-up converter to guarantee contrast control whatever V<sub>DD</sub>.

- Static 1/2, 1/3, 1/4, 1/8 duty supported.

- Static 1/2, 1/3, 1/4 bias supported.

- Phase inversion to reduce power consumption and EMI.

- Up to 8 pixels which can programmed to blink.

- The LCD controller can operate in Halt mode.

Note: Unnecessary segments and common pins can be used as general I/O pins.

#### 3.7 Memories

The high-density and medium+ density STM8L15xx6/8 devices have the following main features:

- Up to 4 Kbyte of RAM

- The non-volatile memory is divided into three arrays:

- Up to 64 Kbyte of medium-density embedded Flash program memory

- Up to 2 Kbyte of Data EEPROM

- Option bytes.

The EEPROM embeds the error correction code (ECC) feature. It supports the read-while-write (RWW): it is possible to execute the code from the program matrix while programming/erasing the data matrix.

The option byte protects part of the Flash program memory from write and readout piracy.

#### 3.8 DMA

A 4-channel direct memory access controller (DMA1) offers a memory-to-memory and peripherals-from/to-memory transfer capability. The 4 channels are shared between the following IPs with DMA capability: ADC1, DAC1, DAC2, I2C1, SPI1, SPI2, USART1, USART2, USART3, and the 5 Timers.

### 3.9 Analog-to-digital converter

- 12-bit analog-to-digital converter (ADC1) with 28 channels (including 4 fast channel), temperature sensor and internal reference voltage

- Conversion time down to 1 µs with f<sub>SYSCLK</sub>= 16 MHz

- Programmable resolution

- Programmable sampling time

- Single and continuous mode of conversion

- Scan capability: automatic conversion performed on a selected group of analog inputs

- Analog watchdog: interrupt generation when the converted voltage is outside the programmed threshold

- Triggered by timer

Note: ADC1 can be served by DMA1.

### 3.10 Digital-to-analog converter

- 12-bit DAC with 2 buffered outputs (two digital signals can be converted into two analog voltage signal outputs)

- Synchronized update capability using timers

- DMA capability for each channel

- External triggers for conversion

- Noise-wave generation

- Triangular-wave generation

- Dual DAC channels with independent or simultaneous conversions

- Input reference voltage V<sub>REF+</sub> for better resolution

Note: DAC can be served by DMA1.

### 3.11 Ultra-low-power comparators

The high-density and medium+ density STM8L15xx6/8 devices embed two comparators (COMP1 and COMP2) sharing the same current bias and voltage reference. The voltage reference can be internal or external (coming from an I/O).

- One comparator with fixed threshold (COMP1).

- One comparator rail to rail with fast or slow mode (COMP2). The threshold can be one

of the following:

- DAC output

- External I/O

- Internal reference voltage or internal reference voltage submultiple (1/4, 1/2, 3/4)

The two comparators can be used together to offer a window function. They can wake up from Halt mode.

### 3.12 System configuration controller and routing interface

The system configuration controller provides the capability to remap some alternate functions on different I/O ports. TIM4 and ADC1 DMA channels can also be remapped.

The highly flexible routing interface allows application software to control the routing of different I/Os to the TIM1 timer input captures. It also controls the routing of internal analog signals to ADC1, COMP1, COMP2, DAC1 and the internal reference voltage V<sub>REFINT</sub>. It also provides a set of registers for efficiently managing the charge transfer acquisition sequence (see *Section 3.13: Touch sensing*).

### 3.13 Touch sensing

The high-density and medium+ density STM8L15xx6/8 devices provide a simple solution for adding capacitive sensing functionality to any application. Capacitive sensing technology is able to detect finger presence near an electrode which is protected from direct touch by a dielectric (for example glass or plastic). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists of charging the electrode capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. In the high-density and medium+ density STM8L15xx6/8 devices, the acquisition sequence is managed by software and it involves analog I/O groups and the routing interface.

Reliable touch sensing solution can be quickly and easily implemented using the free STM8 touch sensing firmware library.

#### 3.14 Timers

The high-density and medium+ density STM8L15xx6/8 devices contain one advanced control timer (TIM1), three 16-bit general purpose timers (TIM2,TIM3 and TIM5) and one 8-bit basic timer (TIM4).

All the timers can be served by DMA1.

Table 3 compares the features of the advanced control, general-purpose and basic timers.

DMA1 Counter Capture/compare Complementary Counter Timer Prescaler factor request resolution channels outputs type generation Any integer TIM1 3 + 13 from 1 to 65536 TIM2 16-bit up/down Any power of 2 TIM3 2 Yes from 1 to 128 None TIM5 Any power of 2 TIM4 8-bit 0 up from 1 to 32768

Table 3. Timer feature comparison

57/

DocID17943 Rev 10

21/146

#### 3.14.1 16-bit advanced control timer (TIM1)

This is a high-end timer designed for a wide range of control applications. With its complementary outputs, dead-time control and center-aligned PWM capability, the field of applications is extended to motor control, lighting and half-bridge driver.

- 16-bit up, down and up/down autoreload counter with 16-bit prescaler

- 3 independent capture/compare channels (CAPCOM) configurable as input capture, output compare, PWM generation (edge and center aligned mode) and single pulse mode output

- 1 additional capture/compare channel which is not connected to an external I/O

- Synchronization module to control the timer with external signals

- Break input to force timer outputs into a defined state

- 3 complementary outputs with adjustable dead time

- Encoder mode

- Interrupt capability on various events (capture, compare, overflow, break, trigger)

### 3.14.2 16-bit general purpose timers (TIM2, TIM3, TIM5)

- 16-bit autoreload (AR) up/down-counter

- 7-bit prescaler adjustable to fixed power of 2 ratios (1...128)

- 2 individually configurable capture/compare channels

- PWM mode

- Interrupt capability on various events (capture, compare, overflow, break, trigger)

- Synchronization with other timers or external signals (external clock, reset, trigger and enable)

#### 3.14.3 8-bit basic timer (TIM4)

The 8-bit timer consists of an 8-bit up auto-reload counter driven by a programmable prescaler. It can be used for timebase generation with interrupt generation on timer overflow or for DAC trigger generation.

### 3.15 Watchdog timers

The watchdog system is based on two independent timers providing maximum security to the applications.

#### 3.15.1 Window watchdog timer

The window watchdog (WWDG) is used to detect the occurrence of a software fault, usually generated by external interferences or by unexpected logical conditions, which cause the application program to abandon its normal sequence.

#### 3.15.2 Independent watchdog timer

The independent watchdog peripheral (IWDG) can be used to resolve processor malfunctions due to hardware or software failures.

It is clocked by the internal LSI RC clock source, and thus stays active even in case of a CPU clock failure.

### 3.16 Beeper

The beeper function outputs a signal on the BEEP pin for sound generation. The signal is in the range of 1, 2 or 4 kHz.

### 3.17 Communication interfaces

#### 3.17.1 SPI

The serial peripheral interfaces (SPI1 and SPI2) provide half/ full duplex synchronous serial communication with external devices.

- Maximum speed: 8 Mbit/s (f<sub>SYSCLK</sub>/2) both for master and slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on 2 lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- Hardware CRC calculation

- Slave/master selection input pin

Note: SPI1 and SPI2 can be served by the DMA1 Controller.

### 3.17.2 I<sup>2</sup>C

The I<sup>2</sup>C bus interface (I2C1) provides multi-master capability, and controls all I<sup>2</sup>C bus-specific sequencing, protocol, arbitration and timing.

- · Master, slave and multi-master capability

- Standard mode up to 100 kHz and fast speed modes up to 400 kHz.

- 7-bit and 10-bit addressing modes.

- SMBus 2.0 and PMBus support

- Hardware CRC calculation

Note:  $I^2C1$  can be served by the DMA1 Controller.

#### 3.17.3 USART

The USART interfaces (USART1, USART2 and USART3) allow full duplex, asynchronous communications with external devices requiring an industry standard NRZ asynchronous serial data format. It offers a very wide range of baud rates.

- 1 Mbit/s full duplex SCI

- SPI1 emulation

- High precision baud rate generator

- Smartcard emulation

- IrDA SIR encoder decoder

- Single wire half duplex mode

Note: USART1, USART2 and USART3 can be served by the DMA1 Controller.

### 3.18 Infrared (IR) interface

The high-density and medium+ density STM8L15xx6/8 devices contain an infrared interface which can be used with an IR LED for remote control functions. Two timer output compare channels are used to generate the infrared remote control signals.

### 3.19 Development support

#### **Development tools**

Development tools for the STM8 microcontrollers include:

- The STice emulation system offering tracing and code profiling

- The STVD high-level language debugger including C compiler, assembler and integrated development environment

- The STVP Flash programming software

The STM8 also comes with starter kits, evaluation boards and low-cost in-circuit debugging/programming tools.

#### Single wire data interface (SWIM) and debug module

The debug module with its single wire data interface (SWIM) permits non-intrusive real-time in-circuit debugging and fast memory programming.

The Single wire interface is used for direct access to the debugging module and memory programming. The interface can be activated in all device operation modes.

The non-intrusive debugging module features a performance close to a full-featured emulator. Beside memory and peripherals, CPU operation can also be monitored in real-time by means of shadow registers.

#### **Bootloader**

A bootloader is available to reprogram the Flash memory using the USART1, USART2, USART3 (USARTs in asynchronous mode), SPI1 or SPI2 interfaces. The reference document for the bootloader is *UM0560: STM8 bootloader user manual*.

## 4 Pin description

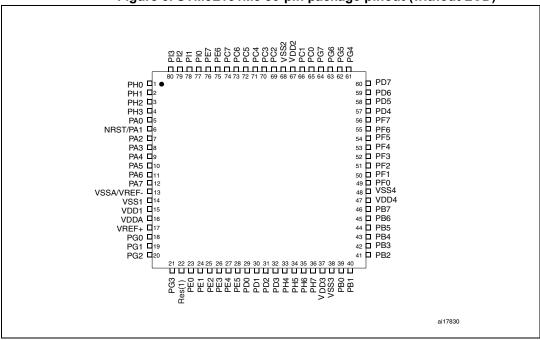

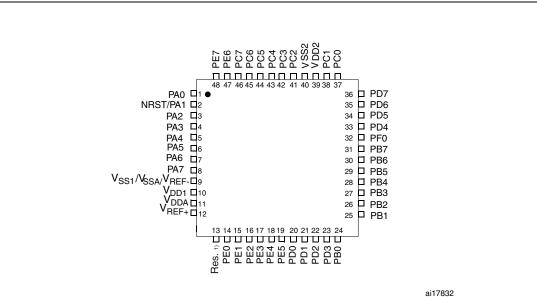

Figure 3. STM8L151M8 80-pin package pinout (without LCD)

- Pin 22 is reserved and must be tied to V<sub>DD</sub>.

- 2. The above figure shows the package top view.

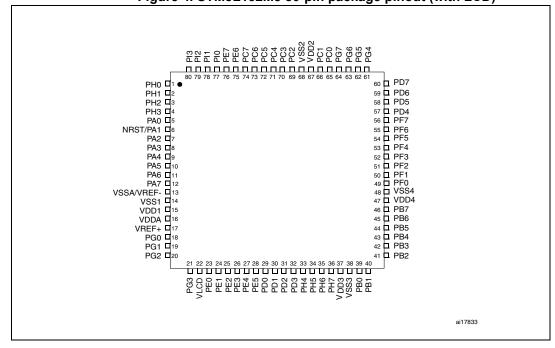

Figure 4. STM8L152M8 80-pin package pinout (with LCD)

1. The above figure shows the package top view.

DocID17943 Rev 10

Figure 5. STM8L151R8 and STM8L151R6 64-pin pinout (without LCD)

- Pin 18 is reserved and must be tied to V<sub>DD</sub>.

- 2. The above figure shows the package top view.

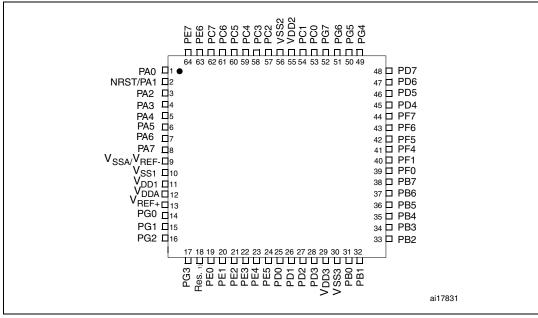

4 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 🗖 PD7 PA0 □1 ● 47 PD6 46 PD5 NRST/PA1 □2 PA2 45 PD4 44 PF7 PA3 PA4 □5 PA5 □6 43 PF6 PA6 🗖 42 PF5 41 PF4 40 PF1 39 PF0 PA7 🗖8 V<sub>SSA/</sub>V<sub>REF-□9</sub> V<sub>SS1</sub> □10 V<sub>DD1</sub> □11 V<sub>DD5</sub> □12 38 🗖 PB7 □ PB6 V<sub>REF+□13</sub> 36 ☐ PB5 35 ☐ PB4 PG0 ☐14 PG1 □15 PG2 □16 34 🏻 PB3 33 🗆 PB2 ai17835

Figure 6. STM8L152R8 and STM8L152R6 64-pin pinout (with LCD)

1. The above figure shows the package top view.

57

Figure 7. STM8L151C8 48-pin pinout (without LCD)

- Pin 13 is reserved and must be tied to V<sub>DD</sub>.

- 2. The above figure shows the package top view.

□ PD7 PA0 NRST/PA1 □ PD6 PA2 □ PD5 PA3 □ PD4 PA4 D5 PA5 D6 □ PF0 □ PB7 PA6 = 7 □ PB6 PA7 =8 □ PB5 V<sub>SS1</sub>/V<sub>SSA</sub>/V<sub>REF-U9</sub> V<sub>DD1</sub> U10 V<sub>DDA</sub> U11 □ PB4 27 🏻 PB3 26 PB2 25 PB1 VREF+ 13 14 15 16 17 18 19 20 21 22 23 24 ai17834

Figure 8. STM8L152C8 48-pin pinout (with LCD)

1. The above figure shows the package top view.

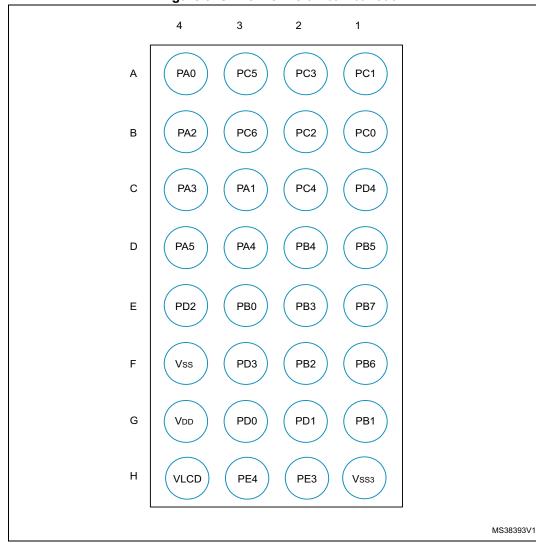

Figure 9. STM8L152K8 32-ball ballout

Warning:

For the 32-pin STM8L152K8 devices, some active I/O pins are not bonded out of the package. Effectively, all ports available on 48-pin devices must be considered as active ports also for 32-pin devices - see *Table 5: High-density and medium+density STM8L15x pin description* for more details. To avoid spurious effects, users have to configure active ports as input pull-up. A small increase in consumption (typ. < 300  $\mu$ A) may occur during the power up and reset phase until these ports are properly configured.

**577**

### Table 4. Legend/abbreviation

| Туре             | I= input, O = output, S = power supply                                                                                                                                                            |                                                      |  |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|--|--|--|--|--|--|

| Level            | FT: Five-volt tolerant                                                                                                                                                                            |                                                      |  |  |  |  |  |  |  |  |

| Levei            | Output                                                                                                                                                                                            | HS = high sink/source (20 mA)                        |  |  |  |  |  |  |  |  |

| Port and control | Input                                                                                                                                                                                             | float = floating, wpu = weak pull-up                 |  |  |  |  |  |  |  |  |

| configuration    | Output                                                                                                                                                                                            | T = true open drain, OD = open drain, PP = push pull |  |  |  |  |  |  |  |  |

| Reset state      | Bold X (pin state after reset release). Unless otherwise specified, the pin state is the same during the reset phase (i.e. "under reset") and after internal reset release (i.e. at reset state). |                                                      |  |  |  |  |  |  |  |  |

Table 5. High-density and medium+ density STM8L15x pin description

| Pi     | in nu  | ımb                        | er      |                                                                                                    |      |                   | I        | npu | t              | 0                | utpı | ıt | -                              |                                                                                                        |

|--------|--------|----------------------------|---------|----------------------------------------------------------------------------------------------------|------|-------------------|----------|-----|----------------|------------------|------|----|--------------------------------|--------------------------------------------------------------------------------------------------------|

| LQFP80 | LQFP64 | <b>UFQFPN48</b> and LQFP48 | WLCSP32 | Pin name                                                                                           | Туре | I/O level         | floating | ndw | Ext. interrupt | High sink/source | ОD   | dd | Main function<br>(after reset) | Default alternate<br>function                                                                          |

| 1      | -      | 1                          |         | PH0/LCD SEG 36 (3)                                                                                 |      | FT <sup>(6)</sup> | X        | Χ   | Χ              | HS               | Χ    | Χ  | Port H0                        | LCD segment 36                                                                                         |

| 2      | -      | -                          | -       | PH1/LCD SEG 37 (3)                                                                                 |      | FT <sup>(6)</sup> | X        | Χ   | Χ              | HS               | Χ    | Χ  | Port H1                        | LCD segment 37                                                                                         |

| 3      | -      | 1                          | -       | PH2/LCD SEG 38 (3)                                                                                 |      | FT <sup>(6)</sup> | X        | Χ   | X              | HS               | Χ    | Χ  | Port H2                        | LCD segment 38                                                                                         |

| 4      | -      | 1                          |         | PH3/LCD SEG 39 (3)                                                                                 | I/O  | FT <sup>(6)</sup> | X        | Χ   | X              | HS               | Χ    | Χ  | Port H3                        | LCD segment 39                                                                                         |

| 6      | 2      | 2                          | СЗ      | NRST/PA1 <sup>(1)</sup>                                                                            | I/O  | -                 | -        | X   |                | HS               |      | Χ  | Reset                          | PA1                                                                                                    |

| 7      | 3      | 3                          | B4      | PA2/OSC_IN/<br>[USART1_TXJ <sup>(2)</sup> /<br>[SPI1_MISO] <sup>(2)</sup>                          | I/O  | -                 | x        | х   | х              | HS               | Х    | х  | Port A2                        | HSE oscillator input / [USART1 transmit] / [SPI1 master in- slave out] /                               |

| 8      | 4      | 4                          | C4      | PA3/OSC_OUT/<br>[USART1_RX] <sup>(2)</sup> /[<br>SPI1_MOSI] <sup>(2)</sup>                         | I/O  | -                 | х        | Х   | Х              | HS               | Х    | Х  | Port A3                        | HSE oscillator output /<br>[USART1 receive]/ [SPI1<br>master out/slave in]/                            |

| 9      | 5      | 5                          | D3      | PA4/TIM2_BKIN/<br>[TIM2_ETR] <sup>(2)</sup><br>LCD_COM0 <sup>(3)</sup> /ADC1_IN2<br>[COMP1_INP]    | I/O  | FT <sup>(6)</sup> | x        | x   | х              | HS               | х    | x  | Port A4                        | Timer 2 - break input / /[Timer 2 - trigger] / LCD COM 0 / ADC1 input 2/ [Comparator 1 positive input] |

| 10     | 6      | 6                          | D4      | PA5/TIM3_BKIN/<br>[TIM3_ETR] <sup>(2)</sup> /<br>LCD_COM1 <sup>(3)</sup> /ADC1_IN1/<br>[COMP1_INP] | I/O  | FT <sup>(6)</sup> | x        | x   | x              | HS               | X    | x  |                                | Timer 3 - break input / [Timer 3 - trigger] / LCD_COM 1 / ADC1 input 1/ [Comparator 1 positive input]  |

Table 5. High-density and medium+ density STM8L15x pin description (continued)

| Pi     | n nu   | ımb                 | er      |                                                                                                   |      |                   | ı        | npu | t              | 0                | utpu | ıt | -                              |                                                                                                                            |

|--------|--------|---------------------|---------|---------------------------------------------------------------------------------------------------|------|-------------------|----------|-----|----------------|------------------|------|----|--------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| LQFP80 | LQFP64 | UFQFPN48 and LQFP48 | WLCSP32 | Pin name                                                                                          | Туре | I/O level         | floating | wpn | Ext. interrupt | High sink/source | ОО   | ЬР | Main function<br>(after reset) | Default alternate<br>function                                                                                              |

| 11     | 7      | 7                   | _(4)    | PA6/ADC1_TRIG/<br>LCD_COM2 <sup>(3)</sup> /ADC1_IN0/<br>[COMP1_INP]                               | I/O  | FT <sup>(6)</sup> | X        | X   | X              | HS               | X    | X  | Port A6                        | ADC1 - trigger /<br>LCD_COM2 / ADC1<br>input 0/<br>[Comparator 1 positive<br>input]                                        |

| 12     | 8      | 8                   | _(4)    | PA7/LCD_SEG0 <sup>(3)</sup> /<br>TIM5_CH1                                                         | I/O  | FT <sup>(6)</sup> | X        | X   | X              | HS               | Χ    | Χ  | Port A7                        | LCD segment 0 /<br>TIM5 channel 1                                                                                          |

| 39     | 31     | 24                  | E3      | PB0 <sup>(5)</sup> /TIM2_CH1/<br>LCD_SEG10 <sup>(3)</sup> /ADC1_IN18<br>/ [COMP1_INP]             | I/O  | FT <sup>(6)</sup> | X        | X   | X              | HS               | X    | X  | Port B0                        | Timer 2 - channel 1 /LCD segment 10/ ADC1_IN18/ [Comparator 1 positive input]                                              |

| 40     | 32     | 25                  | G1      | PB1/TIM3_CH1/<br>LCD_SEG11 <sup>(3)</sup> /ADC1_IN17<br>/ [COMP1_INP]                             | I/O  | FT <sup>(6)</sup> | X        | X   | X              | HS               | X    | X  | Port B1                        | Timer 3 - channel 1 / LCD segment 11 / ADC1_IN17/ [Comparator 1 positive input]                                            |

| 41     | 33     | 26                  | F2      | PB2/<br>TIM2_CH2/LCD_SEG12 <sup>(3)</sup> /<br>ADC1_IN16/[COMP1_INP]                              | I/O  | FT <sup>(6)</sup> | x        | X   | X              | HS               | х    | x  | Port B2                        | Timer 2 - channel 2<br>/ LCD segment 12 /<br>ADC1_IN16/<br>[Comparator 1 positive<br>input]                                |