## SSM2141\* PRODUCT PAGE QUICK LINKS

Last Content Update: 12/18/2017

## COMPARABLE PARTS -

View a parametric search of comparable parts.

### **DOCUMENTATION**

#### **Application Notes**

AN-938: Digital and Analog Measurement Units for Digital CMOS Microphone Preamplifier ASICs

#### **Data Sheet**

SSM2141: High Common-Mode Rejection Differential Line Receiver Data Sheet

### REFERENCE MATERIALS •

#### **Informational**

Advantiv<sup>™</sup> Advanced TV Solutions

## **DESIGN RESOURCES**

- SSM2141 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- Symbols and Footprints

### **DISCUSSIONS**

View all SSM2141 EngineerZone Discussions.

### SAMPLE AND BUY 🖵

Visit the product page to see pricing options.

### TECHNICAL SUPPORT 🖳

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

This page is dynamically generated by Analog Devices, Inc., and inserted into this data sheet. A dynamic change to the content on this page will not trigger a change to either the revision number or the content of the product data sheet. This dynamic page may be frequently modified.

## SSM2141-SPECIFICATIONS

# **ELECTRICAL CHARACTERISTICS** (@ $V_S = \pm 18 \text{ V}$ , $T_A = +25 ^{\circ}\text{C}$ , unless otherwise noted)

|                                  |                 |                                                         | SSM2141 |               |      |       |

|----------------------------------|-----------------|---------------------------------------------------------|---------|---------------|------|-------|

| Parameter                        | Symbol          | Conditions                                              | Min     | Тур           | Max  | Units |

| OFFSET VOLTAGE                   | V <sub>OS</sub> | $V_{CM} = 0 V$                                          | -1000   | 25            | 1000 | μV    |

| GAIN ERROR                       |                 | No Load, $V_{IN} = \pm 10 \text{ V}$ , $R_S = 0 \Omega$ |         | 0.001         | 0.01 | %     |

| INPUT VOLTAGE RANGE              | IVR             | (Note 1)                                                | ±10     |               |      | V     |

| COMMON-MODE REJECTION            | CMR             | $V_{CM} = \pm 10 \text{ V}$                             | 80      | 100           |      | dB    |

| POWER SUPPLY REJECTION RATIO     | PSRR            | $V_S = \pm 6 \text{ V to } \pm 18 \text{ V}$            |         | 0.7           | 15   | μV/V  |

| OUTPUT SWING                     | $V_{O}$         | $R_L = 2 k\Omega$                                       | ±13     | ±14.7         |      | V     |

| SHORT-CIRCUIT CURRENT LIMIT      | $I_{SC}$        | Output Shorted to Ground                                | +45/-15 |               |      | mA    |

| SMALL-SIGNAL BANDWIDTH (-3 dB)   | BW              | $R_L = 2 k\Omega$                                       |         | 3             |      | MHz   |

| SLEW RATE                        | SR              | $R_L = 2 k\Omega$                                       | 6       | 9.5           |      | V/µs  |

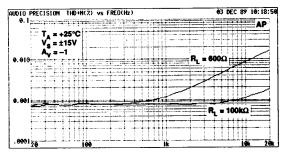

| TOTAL HARMONIC DISTORTION        | THD             | $R_L = 100 \ k\Omega$ $R_L = 600 \ \Omega$              |         | 0.001<br>0.01 |      | %     |

| CAPACITIVE LOAD DRIVE CAPABILITY | $C_{L}$         | No Oscillation                                          |         | 300           |      | pF    |

| SUPPLY CURRENT                   | $I_{SY}$        | No Load                                                 |         | 2.5           | 3.5  | mA    |

NOTES

Specifications subject to change without notice

## ELECTRICAL CHARACTERISTICS (@ $V_S = \pm 18~V, -40^{\circ}C \le T_A \le +85^{\circ}C$ )

| Parameter                    | Symbol          | Conditions                                              | Min   | Тур   | Max  | Units |

|------------------------------|-----------------|---------------------------------------------------------|-------|-------|------|-------|

| OFFSET VOLTAGE               | V <sub>OS</sub> | $V_{CM} = 0 \text{ V}$                                  | -2500 | 200   | 2500 | μV    |

| GAIN ERROR                   |                 | No Load, $V_{IN} = \pm 10 \text{ V}$ , $R_S = 0 \Omega$ |       | 0.002 | 0.02 | %     |

| INPUT VOLTAGE RANGE          | IVR             | (Note 1)                                                | ±10   |       |      | V     |

| COMMON-MODE REJECTION        | CMR             | $V_{CM} = \pm 10 \text{ V}$                             | 75    | 90    |      | dB    |

| POWER SUPPLY REJECTION RATIO | PSRR            | $V_S = \pm 6 \text{ V to } \pm 18 \text{ V}$            |       | 1.0   | 20   | μV/V  |

| OUTPUT SWING                 | Vo              | $R_L = 2 k\Omega$                                       | ±13   | ±14.7 |      | V     |

| SLEW RATE                    | SR              | $R_L = 2 k\Omega$                                       |       | 9.5   |      | V/µs  |

| SUPPLY CURRENT               | I <sub>SY</sub> | No Load                                                 |       | 2.6   | 4.0  | mA    |

NOTES

-2- REV. **C**

<sup>&</sup>lt;sup>1</sup>Input Voltage Range Guaranteed by CMR test.

<sup>&</sup>lt;sup>1</sup>Input Voltage Range Guaranteed by CMR test.

Specifications subject to change without notice

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Supply Voltage                              |

|---------------------------------------------|

| Input Voltage <sup>1</sup> Supply Voltage   |

| Output Short-Circuit Duration Continuous    |

| Storage Temperature Range                   |

| P Package65°C to +150°C                     |

| Lead Temperature (Soldering, 60 sec) +300°C |

| Junction Temperature +150°C                 |

| Operating Temperature Range = 40°C to ±85°C |

| Package Type          | $\theta_{JA}^2$ $\theta_{JC}$ |    | Units |  |

|-----------------------|-------------------------------|----|-------|--|

| 8-Pin Plastic DIP (P) | 103                           | 43 | °C/W  |  |

#### NOTES

## **Typical Performance Characteristics**

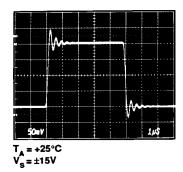

Small Signal Transient Response

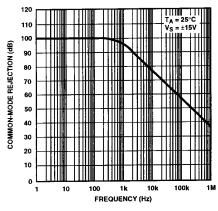

Common-Mode Rejection vs. Frequency

Total Harmonic Distortion vs. Frequency

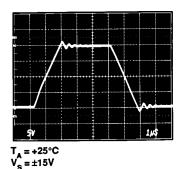

Large Signal Transient Response

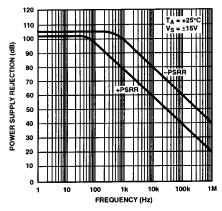

Power Supply Rejection vs. Frequency

Dynamic Intermodulation Distortion vs. Frequency

$<sup>^1</sup>For$  supply voltages less than  $\pm\,18$  V, the absolute maximum input voltage is equal to the supply voltage.

$<sup>^2\</sup>theta_{JA}$  is specified for worst case mounting conditions, i.e.,  $\theta_{JA}$  is specified for device in socket for P-DIP package.

## SSM2141-Typical Performance Characteristics

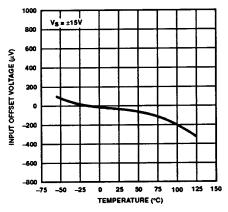

Input Offset Voltage vs. Temperature

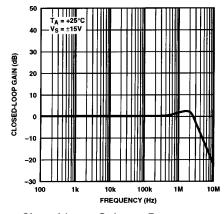

Closed-Loop Gain vs. Frequency

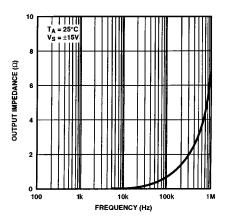

Closed-Loop Output Impedance vs. Frequency

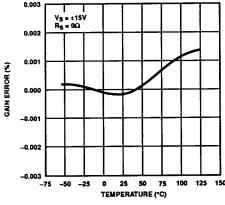

Gain Error vs. Temperature

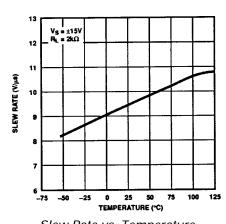

Slew Rate vs. Temperature

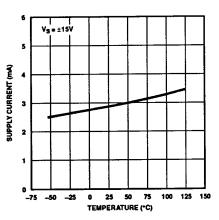

Supply Current vs. Temperature

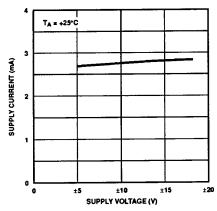

Supply Current vs. Supply Voltage

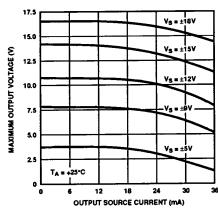

Maximum Output Voltage vs. Output Current (Source)

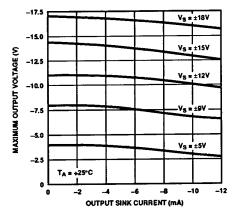

Maximum Output Voltage vs. Output Current (Sink)

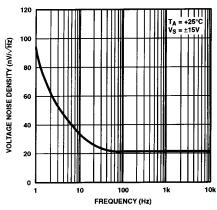

Voltage Noise Density vs. Frequency

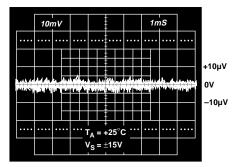

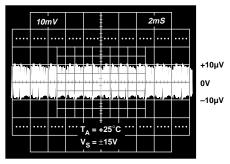

NOTE: EXTERNAL AMPLIFIER GAIN = 1000; THEREFORE, VERTICAL SCALE =  $10\mu V/DIV$ .

Voltage Noise from 0 kHz to 1 kHz

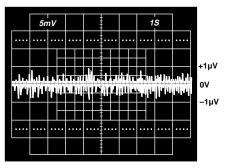

0.1 TO 10Hz PEAK-TO-PEAK NOISE

Low Frequency Voltage Noise

NOTE: EXTERNAL AMPLIFIER GAIN = 1000; THEREFORE, VERTICAL SCALE =  $10\mu V/DIV$ .

Voltage Noise from 0 kHz to 10 kHz

#### APPLICATIONS INFORMATION

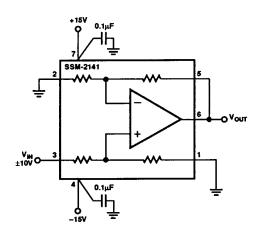

The SSM2141 represents a versatile analog building block. In order to capitalize on fast settling time, high slew rate, and high CMR, proper decoupling and grounding techniques must be employed. For decoupling, place 0.1  $\mu F$  capacitor located within close proximity from each supply pin to ground.

Slew Rate Test Circuit

### SSM2141

#### MAINTAINING COMMON-MODE REJECTION

In order to achieve the full common-mode rejection capability of the SSM2141, the source impedance must be carefully controlled. Slight imbalances of the source resistance will result in a degradation of DC CMR—even a 5  $\Omega$  imbalance will degrade CMR by 20 dB. Also, the matching of the reactive source impedance must be matched in order to preserve the CMRR over frequency.

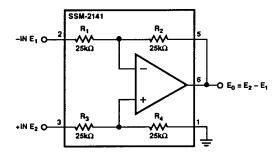

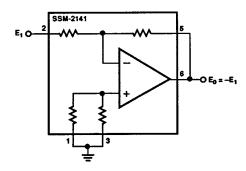

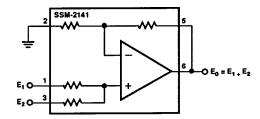

Figure 1. Precision Difference Amplifier. Rejects

Common-Mode Signal =  $\frac{[E_1+E_2]}{2}$  by 100 dB

Figure 2. Precision Unity Gain Inverting Amplifier

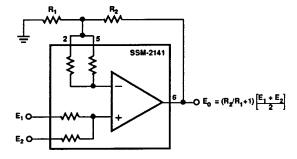

Figure 3. Precision Summing Amplifier

Figure 4. Precision Summing Amplifier with Gain

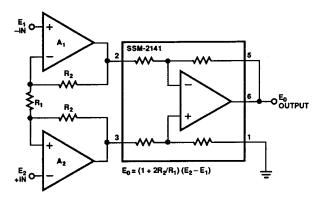

Figure 5. Suitable Instrumentation Amplifier Requirements can be Addressed by Using an Input Stage Consisting of  $A_1$ ,  $A_2$ ,  $R_1$  and  $R_2$

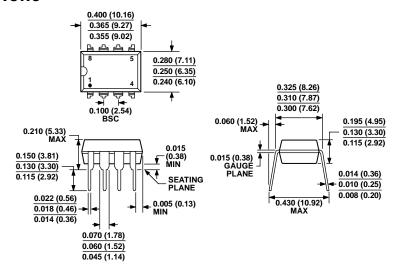

## **OUTLINE DIMENSIONS**

#### COMPLIANT TO JEDEC STANDARDS MS-001

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN. CORNER LEADS MAY BE CONFIGURED AS WHOLE OR HALF LEADS.

Figure 6. 8-Lead Plastic Dual In-Line Package [PDIP] Narrow Body (N-8)

Dimensions shown in inches and (millimeters)

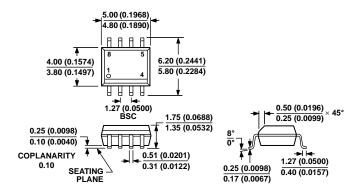

#### COMPLIANT TO JEDEC STANDARDS MS-012-AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 7.8-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-8)

Dimensions shown in millimeters and (inches)

REV. C -7-

## SSM2141

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range                                                     | Package Description | Package Option |

|--------------------|-----------------------------------------------------------------------|---------------------|----------------|

| SSM2141PZ          | $-40$ °C $\leq$ T <sub>A</sub> $\leq$ $+85$ °C                        | 8-Lead PDIP         | N-8            |

| SSM2141SZ          | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$ | 8-Lead SOIC_N       | R-8            |

| SSM2141SZ-REEL     | $-40$ °C $\leq$ T <sub>A</sub> $\leq$ $+85$ °C                        | 8-Lead SOIC_N       | R-8            |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

#### **REVISION HISTORY**

6/11—Rev. B to Rev. C

5/91—Rev. A to Rev. B

www.analog.com

©2007 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

D10008-0-6/11(C)

REV. C