# **Contents**

| 1. | Ord  | ering Information                            | 3    |

|----|------|----------------------------------------------|------|

| 2. |      | Description                                  |      |

| 3. |      | Specifications                               |      |

|    | 3.1. | Absolute Maximum Ratings                     |      |

|    | 3.2. | Continuous Ratings                           |      |

|    | 3.3. | Receiver                                     | 5    |

|    | 3.4. | Transmitter                                  | 7    |

|    | 3.5. | 2-Wire Serial Interface                      | . 10 |

| 4. | Fun  | ctional Description                          | . 12 |

|    | 4.1. | Overview                                     | . 12 |

|    | 4.2. | Receiver Features                            | . 12 |

|    | 4.3. | Transmitter features                         | . 15 |

|    | 4.4. | Laser Safety Features                        | . 20 |

|    | 4.5. | Temperature Measurement                      | . 23 |

| 5. | Con  | itrol Interface                              | . 24 |

|    | 5.1. | Boot Sequence                                | . 25 |

|    | 5.2. | Main Control Loop                            | . 27 |

|    | 5.3. | 2-wire Serial Interface                      | . 28 |

| 6. |      | jister Map                                   | . 30 |

| 7. | Sim  | plified Interface Models                     | . 42 |

| 8. |      | lications Information                        | . 44 |

|    | 8.1. | PHY2078 in an ONU application                |      |

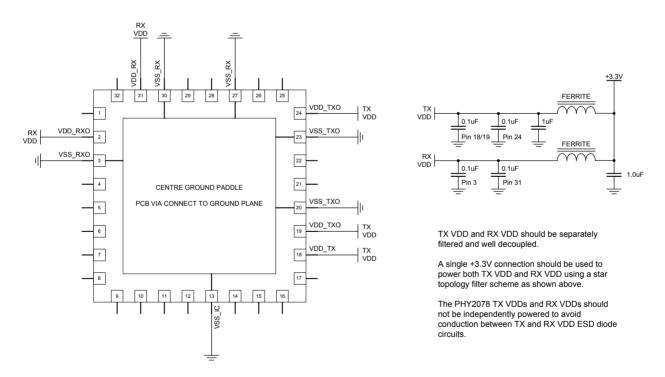

|    | 8.2. | Power Supply Connections                     |      |

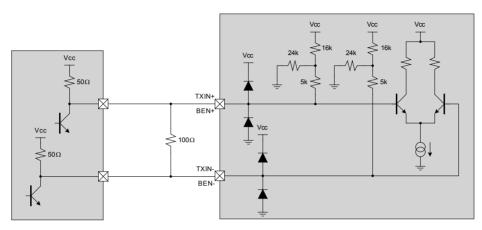

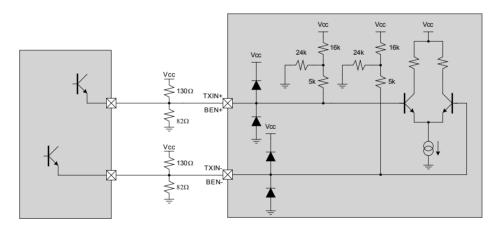

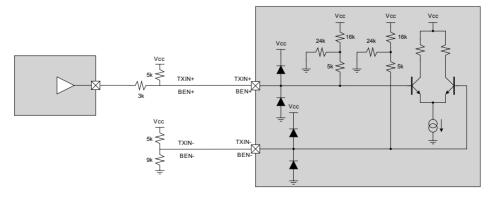

|    | 8.3. | Burst Enable and TX Input connection options | . 46 |

|    | 8.4. | Laser Connection – DC-Coupled                |      |

|    | 8.5. | Mean Power Control Loop Startup Algorithm    | . 48 |

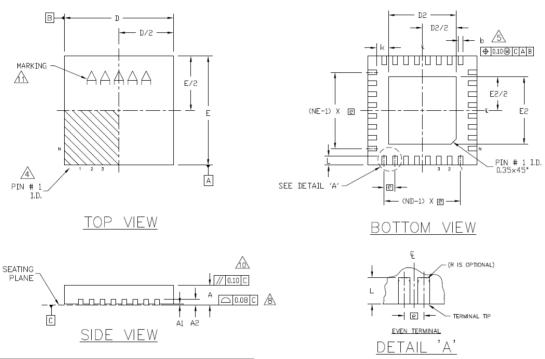

| 9. | Pac  | kaging                                       | . 51 |

| 10 | Con  | tact Information                             | 53   |

# 1. Ordering Information

| Part Number Description |                                | Package                          |  |  |

|-------------------------|--------------------------------|----------------------------------|--|--|

| PHY2078QT-RR            | FTTx LASER driver and Post Amp | TQFN32, 5mmx5mm in Tape and Reel |  |  |

# 2. Pin Description

| Pin No | Name       | Direction | Туре                         | Description                                                      |

|--------|------------|-----------|------------------------------|------------------------------------------------------------------|

| 1      | EEPROM_SDA | I/O       | LVTTL                        | EEPROM 2 wire serial interface data, internal 8kΩ pull up        |

| 2      | VDD_RXO    |           | Power                        | Receiver output power supply                                     |

| 3      | VSS_RXO    |           | Ground                       | Receiver output ground connection                                |

| 4      | RXOUT-     | O/P       | CML                          | Limiting amplifier serial data output                            |

| 5      | RXOUT+     | O/P       | CML                          | Limiting amplifier serial data output                            |

| 6      | SDA        | I/O       | LVTTL                        | 2-wire serial interface data                                     |

| 7      | SCL        | I/O       | LVTTL                        | 2-wire serial interface clock                                    |

| 8      | RREF       |           |                              | Internal connection, leave open circuit                          |

| 9      | TX_FAULT   | O/P       | LVTTL<br>(Open<br>Collector) | Laser fail alarm (requires external pull up)                     |

| 10     | TX_DISABLE | I/P       | LVTTL                        | Laser enable / disable                                           |

| 11     | TXIN+      | I/P       | High Speed<br>Input          | Laser driver serial input, see section 7 for interfacing details |

| 12     | TXIN-      | I/P       | High Speed<br>Input          | Laser driver serial input, see section 7 for interfacing details |

| 13     | VSS_IC     |           |                              | Internal connection, connect to ground                           |

| 14     | BEN+       | I/P       | High Speed<br>Input          | Burst enable positive, see section 7 for interfacing details     |

| 15     | BEN-       | I/P       | High Speed<br>Input          | Burst enable negative, see section 7 for interfacing details     |

| 16     | MPD        | I/P       | Analog                       | Monitor photodiode input                                         |

| 17     | BIAS       | O/P       | Analog                       | Laser bias current output                                        |

| 18     | VDD_TX     |           | Power                        | Driver power supply                                              |

| 19     | VDD_TXO    |           | Power                        | Driver output power supply                                       |

| 20     | VSS_TXO    |           | Ground                       | Driver output ground connection                                  |

| 21     | LASER-     | O/P       | High speed<br>Output         | Laser driver serial output                                       |

| 22     | LASER+     | O/P       | High speed<br>Output         | Laser driver serial output                                       |

| 23     | VSS_TXO    |           | Ground                       | Driver output ground connection                                  |

| 24     | VDD_TXO    |           | Power                        | Driver output power supply                                       |

| 25     | TSENSE     | I/P       | Analog                       | External temperature component connection                        |

| Pin No | Name       | Direction | Туре                         | Description                                                                                   |

|--------|------------|-----------|------------------------------|-----------------------------------------------------------------------------------------------|

| 26     | SD/LOS     | O/P       | LVTTL<br>(Open<br>Collector) | Signal Detect or Loss of signal output (requires external pull up). Polarity selected by user |

| 27     | VSS_RX     |           | Ground                       | Receiver ground connection                                                                    |

| 28     | RXIN-      | I/P       | CML                          | Limiting amplifier serial data input                                                          |

| 29     | RXIN+      | I/P       | CML                          | Limiting amplifier serial data input                                                          |

| 30     | VSS_RX     |           | Power                        | Receiver ground connection                                                                    |

| 31     | VDD_RX     |           | Power                        | Receiver power supply                                                                         |

| 32     | EEPROM_SCL | O/P       | LVTTL                        | EEPROM 2-wire serial interface clock, internal 8kΩ pull up                                    |

| EP     | VSS_EP     |           | Ground                       | Common ground / thermal pad                                                                   |

# 3. Key Specifications

3.1. Absolute Maximum Ratings

| Parameter                 | Conditions                      | Min  | Тур | Max       | Unit |

|---------------------------|---------------------------------|------|-----|-----------|------|

| Supply voltage            |                                 | -0.5 |     | 6.5       | V    |

|                           |                                 | _    |     | VDD       |      |

| Voltage on any signal pin |                                 | -0.5 |     | +<br>0.5V | V    |

| Storage temperature       |                                 |      |     | 150       | °C   |

| Max junction temperature  |                                 |      |     | 140       | °C   |

| Max soldering temperature | IPC/JEDEC J-STD-020C            |      |     | 260       | °C   |

| ESD                       | Human Body Model JESD-22-A114-B | 2    |     |           | kV   |

Device not guaranteed to meet specifications, permanent damage may be incurred by operating beyond these limits.

3.2. Continuous Ratings

| Parameter                           | Conditions                                                         | Min  | Тур | Max  | Unit |

|-------------------------------------|--------------------------------------------------------------------|------|-----|------|------|

| Operating supply voltage            | Continuous operation                                               | 2.97 | 3.3 | 3.63 | V    |

| Current consumption                 | Excluding bias & modulation current at 20mA bias & 20mA modulation |      | 120 | 145  | mA   |

| On a section of the second sections | Case Temperature                                                   |      |     | +110 | °C   |

| Operating temperature               | Ambient Still Air                                                  | -40  | 25  | +95  | °C   |

## 3.3. Receiver

### 3.3.1. Receive Limiting Amplifier

| Parameter                   | Conditions                                                                                                                             | Min  | Тур                | Max | Unit  |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|-----|-------|

| Input sensitivity           | 1.25Gbps, PRBS 2 <sup>7</sup> -1, BER=1x10 <sup>-12</sup>                                                                              |      | 6                  | 8   | mVp-p |

|                             | 2.5Gbps, PRBS 2 <sup>31</sup> -1, BER=1x10 <sup>-10</sup>                                                                              |      | 7                  | 10  | mVp-p |

|                             | 1.25Gbps, PRBS 2 <sup>7</sup> -1, BER=1x10 <sup>-12</sup> With PHY1095 TIA PD Responsivity = 0.8A/W, PD Capacitance = 0.5pF, Er = 10dB |      | -32                |     | dBm   |

| System sensitivity          | 2.5Gbps, PRBS 2 <sup>31</sup> -1, BER=1x10 <sup>-10</sup> With PHY1097 TIA PD Responsivity = 0.9A/W, PD Capacitance = 0.5pF, ER = 10dB |      | -29                |     | dBm   |

| Maximum differential input  | TJ within spec                                                                                                                         | 1200 |                    |     | mVp-p |

| Input termination impedance | Differential                                                                                                                           | 80   | 100                | 120 | Ω     |

| Input common mode voltage   |                                                                                                                                        |      | VDD_RX<br>-<br>1.5 |     | V     |

| Input low frequency cutoff  | High pass 3dB point for RX system                                                                                                      |      | 15                 |     | kHz   |

| Parameter                                           | Conditions                                                                | Min        | Тур                       | Max        | Unit   |

|-----------------------------------------------------|---------------------------------------------------------------------------|------------|---------------------------|------------|--------|

| Differential output rise and fall times (20% - 80%) | Fast slew rate setting,<br>1250Mbps - 2488Mbps filter setting             |            |                           | 100        | ps     |

| Differential output swing                           | CML_LEVEL = 0<br>CML_LEVEL = 1                                            | 700<br>370 |                           | 900<br>470 | mVp-p  |

| Total jitter                                        | Input voltage swing 30mVp-p, K28.5 pattern                                |            |                           | 200        | mUlp-p |

| Output resistance                                   | RXOUT+/- Single ended to VDD_RXO                                          | 40         | 50                        | 60         | Ω      |

| Output return loss                                  | Differential, f<2GHz, device powered on                                   | 10         |                           |            | dB     |

| Rx 3dB frequency                                    | 125/155 Mbps setting 622 Mbps setting 1250 Mbps setting 2488 Mbps setting |            | 120<br>470<br>940<br>1900 |            | MHz    |

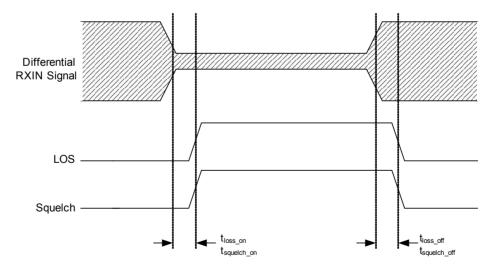

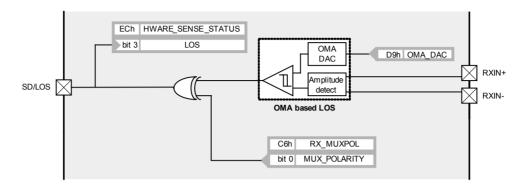

## 3.3.2. OMA LOS

| Parameter              | Symbol                   | Conditions                                                               | Min | Тур | Max | Unit |

|------------------------|--------------------------|--------------------------------------------------------------------------|-----|-----|-----|------|

| OMA LOS assert time    | t <sub>loss_on</sub>     |                                                                          |     |     | 100 | μS   |

| OMA LOS de-assert time | t <sub>loss_off</sub>    |                                                                          |     |     | 20  | μЅ   |

| Electrical hysteresis  |                          | 20log <sub>10</sub> (Vdeassert / Vassert)<br>High setting<br>Low setting |     | 4 3 |     | dB   |

| OMA LOS assert level   |                          | Set by OMA_DAC, Address D9h                                              | 10  |     | 50  | mV   |

| Squelch assert time    | t <sub>squelch_on</sub>  |                                                                          |     |     | 100 | μS   |

| Squelch de-assert time | t <sub>squelch_off</sub> |                                                                          |     |     | 20  | μS   |

Figure 3 - OMA LOS Detection

## 3.4. Transmitter

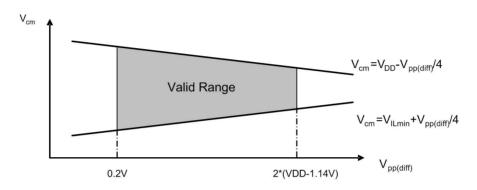

# 3.4.1. Transmitter Inputs: TXIN+/-, BEN+/-

| Parameter     | Conditions | Min  | Тур | Max    | Unit |

|---------------|------------|------|-----|--------|------|

| Input Voltage | VILmin     | 1.14 |     |        | V    |

|               | VIHmax     |      |     | VDD_TX | V    |

| Input Swing   | Vpp(diff)  | 0.2  |     |        | Vpp  |

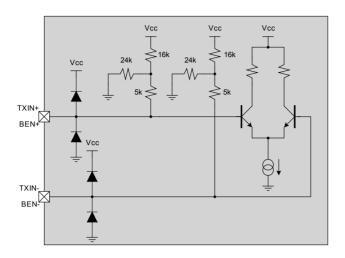

Figure 4 – Valid combinations of transmitter input voltages

### 3.4.2. Laser Driver

| Parameter                              | Conditions                                                                    | Min | Тур | Max    | Unit   |

|----------------------------------------|-------------------------------------------------------------------------------|-----|-----|--------|--------|

| Maximum bias current                   |                                                                               | 90  |     |        | mA     |

| Bias generator shutdown current        | TX_DISABLE active or BEN disabled                                             |     |     | 100    | μА     |

| Maximum modulation current             |                                                                               | 80  |     |        | mA     |

| Modulation generator shutdown current  | TX_DISABLE active or BEN disabled                                             |     |     | 100    | μА     |

| Electrical 20% to 80% rise / fall time | Measured using 15Ω⊡effective termination, Imod = 50mA, AC and DC applications |     | 95  |        | ps     |

| Electrical Pulse Width Distortion      | Measured using 15Ω⊟effective termination, Imod = 20 to 50mA                   |     |     | 50     | ps     |

| Total jitter contribution              | Measured over modulation current range                                        |     |     | 150    | mUlp-p |

| Laser output compliance range          | Allowed voltage for laser driver output pins in dynamic operation.            | 600 |     | VDD_TX | mV     |

| Bias current output compliance         | Minimum allowed voltage for pin BIAS, referenced to ground                    | 500 |     |        | mV     |

| MPD input sink current                 | For correct APC loop operation                                                |     |     | 2.6    | mA     |

| MPD capacitance                        | For correct APC loop operation                                                |     |     | 20     | pF     |

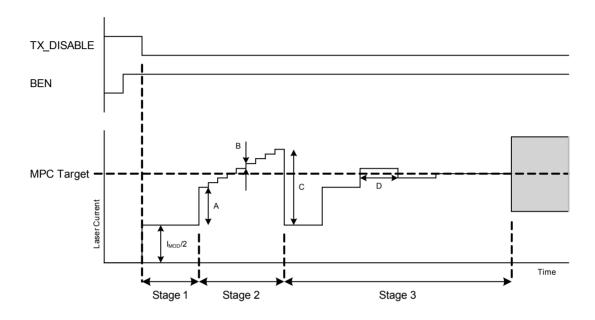

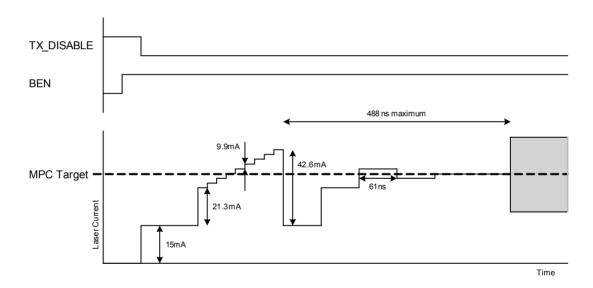

# 3.4.3. Burst Timings

| Parameter                                | Conditions                                                                                                                              | Min | Тур | Max  | Unit |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

|                                          | Assertion of BEN to 90% of desired bias + modulation current                                                                            |     |     |      |      |

| Burst enable/disable time (Electrical)   | De-assert of BEN to 10% of settled bias + modulation current  Target bias current > 3mA                                                 |     | 5   | 12.8 | ns   |

| Burst Length                             | During closed loop operation  MPD current must settle to 98% of final value within 60ns                                                 | 100 |     |      | ns   |

|                                          | During fast startup algorithm                                                                                                           | 400 |     |      | ns   |

| Initial mean power control settling time | From power up or negation of TX_DISABLE to 90% of desired optical power Fast settling algorithm enabled Overshoot < 10% See Section 7.5 |     | 1.2 |      | μS   |

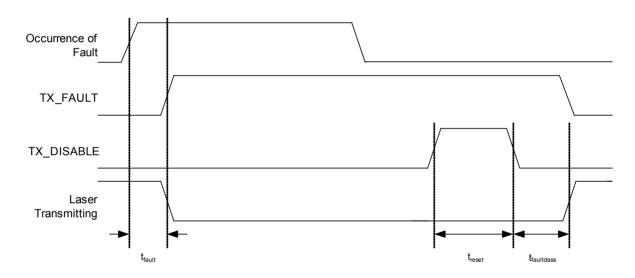

# 3.4.4. Fault Timing

| Parameter                   | Symbol                 | Condition                                                                                            | Min | Тур | Max       | Unit     |

|-----------------------------|------------------------|------------------------------------------------------------------------------------------------------|-----|-----|-----------|----------|

| Time to initialize          | t <sub>init</sub>      | From power on or application of VDD>2.97V during plug in                                             |     |     | 300       | ms       |

| Hard TX_DISABLE assert time | t <sub>off</sub>       | Time from rising edge of TX_DISABLE to when the optical output falls below 10% of nominal            |     | 5.5 |           | μ\$      |

| Hard TX_DISABLE negate time | t <sub>on</sub>        | Time from falling edge of TX_DISABLE to when the modulated optical output rises above 90% of nominal |     |     | 1         | ms       |

| Hard TX_FAULT assert time   | t <sub>fault</sub>     | Time from fault to TX_FAULT on Bias/Temperature ADC outside safe range All other fault conditions    |     |     | 10<br>100 | ms<br>μs |

| TX_DISABLE pulse width      | t <sub>reset</sub>     | Time TX_DISABLE must be held high to reset TX_FAULT                                                  | 5   |     |           | μS       |

| TX_FAULT deassert time      | t <sub>faultdass</sub> | Time to deassert TX_FAULT after TX_DISABLE                                                           |     |     | 300       | ms       |

Figure 5 - Device turn on

Figure 6 - Fault detection

### 3.4.5. Eye Safety Internal fixed limits

| Parameter                             | Symbol              | Comment               | Min   | Тур  | Max  | Unit |

|---------------------------------------|---------------------|-----------------------|-------|------|------|------|

| High supply voltage assert limit      | V <sub>eyeHa</sub>  |                       | 4.0   | 4.15 | 4.3  | V    |

| High supply voltage de-assert limit   | $V_{\text{eyeHd}}$  |                       | 3.7   | 3.85 | 4.0  | V    |

| Low supply voltage assert limit       | $V_{\text{eyeLa}}$  |                       | 2.45  | 2.6  | 2.75 | V    |

| Low supply voltage de-assert limit    | $V_{\text{eyeLd}}$  |                       | 2.7   | 2.8  | 2.95 | V    |

| High Supply Hysteresis                |                     | Applies to VDD TXO or | - 0.1 |      |      | V    |

| Low Supply Hysteresis                 |                     | VDD_TX                | 0.1   |      |      | V    |

| High RREF pin voltage assert limit    | $V_{rrefHa}$        |                       |       | 1.2  |      | V    |

| High RREF pin voltage de-assert limit | $V_{rrefHd}$        |                       |       | 1.1  |      | V    |

| Low RREF pin voltage assert limit     | V <sub>rrefLa</sub> |                       |       | 0.8  |      | V    |

| Low RREF pin voltage de-assert limit  | $V_{rrefLd}$        |                       |       | 0.9  |      | V    |

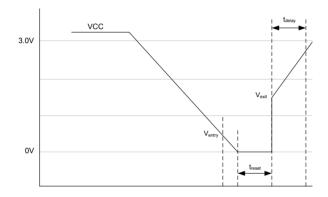

## 3.4.6. Power on Reset (PoR)

| Parameter                         | Symbol             | Comment                         | Min | Тур | Max | Unit |

|-----------------------------------|--------------------|---------------------------------|-----|-----|-----|------|

| Power on reset (PoR) voltage      |                    | Reset is low input voltage      |     |     | 0.5 | V    |

| PoR time to reset                 |                    |                                 | 1.0 |     |     | ms   |

| Power on reset (PoR) exit voltage | $V_{\text{exit}}$  |                                 | 1.2 |     |     | V    |

| PoR exit delay                    | t <sub>delay</sub> | Time before first EEPROM access | 8.0 |     |     | ms   |

Figure 7 – PoR Timing

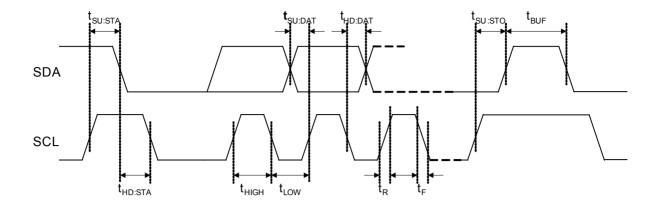

## 3.5. 2-Wire Serial Interface

### 3.5.1. AC Electrical Characteristics

| Parameter                                                      | Symbol              | Comment                                      | Min | Тур | Max  | Unit |

|----------------------------------------------------------------|---------------------|----------------------------------------------|-----|-----|------|------|

| SCL clock frequency                                            | f <sub>SCL</sub>    |                                              | 0   |     | 100  | kHz  |

| LOW period of the SCL clock                                    | t <sub>LOW</sub>    |                                              | 4.7 |     |      | μs   |

| HIGH period of the SCL clock                                   | t <sub>HIGH</sub>   |                                              | 4.0 |     |      | μs   |

| Set-up time for a repeated START condition                     | t <sub>su:sta</sub> |                                              | 4.7 |     |      | μS   |

| Hold time (repeated) START condition                           | t <sub>HD:STA</sub> |                                              | 4.0 |     |      | μs   |

| Data hold time                                                 | t <sub>HD:DAT</sub> |                                              | 0   |     | 3.45 | μs   |

| Data set-up time                                               | t <sub>su:DAT</sub> |                                              | 250 |     |      | ns   |

| Rise time of both SDA and SCL signals                          | t <sub>R</sub>      |                                              |     |     | 1000 | ns   |

| Fall time of both SDA and SCL signals                          | t <sub>F</sub>      |                                              |     |     | 300  | ns   |

| Set-up time for STOP condition                                 | t <sub>su:sto</sub> |                                              | 4.0 |     |      | μs   |

| Bus free time between a STOP and START condition               | t <sub>BUF</sub>    |                                              | 4.7 |     |      | μЅ   |

| Output fall time from $V_{\text{IHmin}}$ to $V_{\text{ILmax}}$ | t <sub>of</sub>     | 10pF < C <sub>b</sub> <sup>(1)</sup> < 400pF | 0   |     | 250  | ns   |

| Capacitance for each I/O pin                                   | Ci                  |                                              |     |     | 10   | pF   |

<sup>1:</sup> C<sub>b</sub> = capacitance of a single bus line in pF.

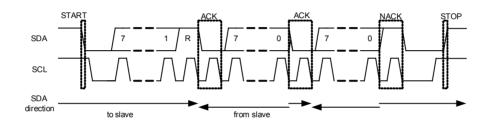

Figure 8 - SDA and SCL bus timing

#### 3.5.2. DC Electrical Characteristics

| Parameter                    | Symbol          | Comment                       | Min    | Тур | Max     | Unit |

|------------------------------|-----------------|-------------------------------|--------|-----|---------|------|

| Low level input voltage      | V <sub>IL</sub> |                               | -0.5   |     | 0.3VDD  | V    |

| High level input voltage     | V <sub>IH</sub> |                               | 0.7VDD |     | VDD+0.5 | V    |

| Low level O/P voltage        | V <sub>OL</sub> | 3 mA sink current             | 0      |     | 0.4     | V    |

| I/P current each I/O pin     | l <sub>i</sub>  | $0.1V_{DD} < V_i < 0.9V_{DD}$ | -10    |     | 10      | mA   |

| Power on reset (PoR) voltage |                 | Reset is low input voltage    |        |     | 0.5     | V    |

| PoR time to reset            |                 |                               | 1.0    |     |         | ms   |

### 3.5.3. LVTTL I/O Pins <sup>1</sup>

| Parameter                   | Comment                     | Min | Тур | Max          | Unit |

|-----------------------------|-----------------------------|-----|-----|--------------|------|

| LVTTL voltage out high      | External 4.7k to 10k pullup | 2.4 |     |              | V    |

| LVTTL voltage out low       | External 4.7k to 10k pullup |     |     | 0.4          | V    |

| LVTTL voltage in high       | Internal pullup             | 2.0 |     | VDD -<br>0.2 | V    |

| LVTTL voltage in low        | Internal pullup             | 0   |     | 0.8          | V    |

| Internal pull-up resistance | EEPROM_SDA, EEPROM_SCL      | 6   |     | 10           | kΩ   |

<sup>&</sup>lt;sup>1</sup> Applies to LVTTL Pins specified on pages 3-4

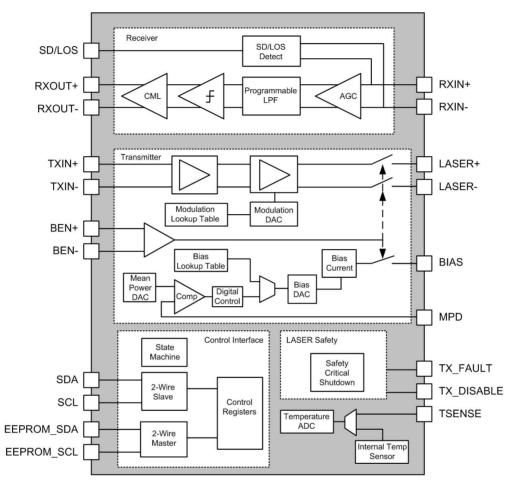

## 4. Functional Description

#### 4.1. Overview

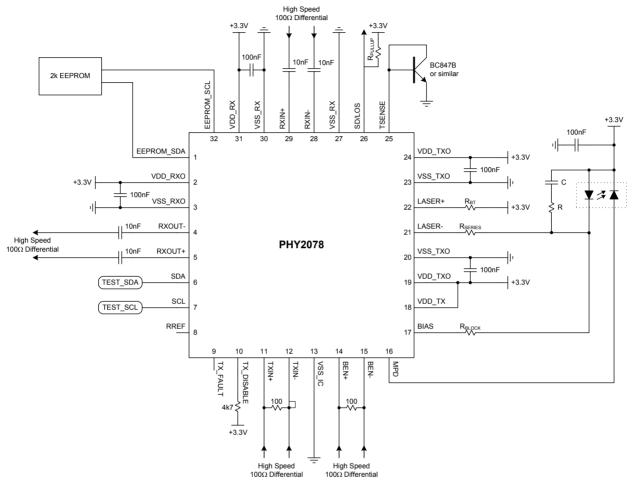

Figure 9 - PHY2078 Functional Overview

#### 4.2. Receiver Features

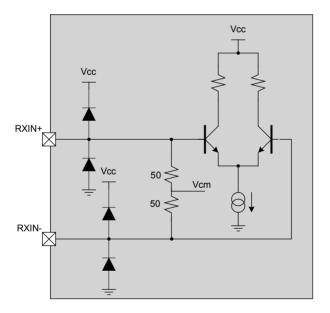

The PHY2078 receiver section consists of an Automatic Gain Control (AGC) input amplifier, which is followed by a programmable low pass filter. The filtered signal is passed to a limiting stage and the receiver output is a CML driver. Offset cancellation is provided by DC-feedback.

A Signal Detect (SD)/Loss Of Signal (LOS) alarm is provided to detect if the amplitude of the AC-signal at the receiver input is below a programmable threshold. For a transimpedance amplifier with a constant gain, the LOS threshold corresponds to a particular Optical Modulation Amplitude (OMA).

#### 4.2.1. Receiver Input Stage

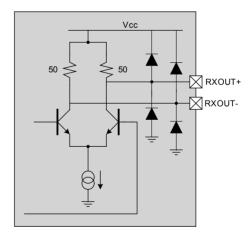

The receiver input stage includes internal  $50\Omega$  single-ended termination resistors and is designed to be AC-coupled to the transimpedance amplifier.

By default the receiver is non-inverting; however, to simplify the PCB layout of differential signals the polarity of the data can be inverted by setting RX POLARITY (C3h, RX LIMITER, bit 1) to '1'.

#### 4.2.2. Receiver Filter

The programmable low pass filter provides band limiting in the receive signal path and can be used to improve the system sensitivity when a higher bandwidth TIA is used. The bandwidth of the filter is set to 0.7 x signal data rate selected and is controlled by a 3-bit control word as follows:

|   | Bit |   | Data Data   |  |  |

|---|-----|---|-------------|--|--|

| 2 | 1   | 0 | Data Rate   |  |  |

| 0 | 0   | 0 | 125/155Mbps |  |  |

| 0 | 0   | 1 | 622Mbps     |  |  |

| 0 | 1   | 0 | Reserved    |  |  |

| 0 | 1   | 1 | 1.250Gbps   |  |  |

| 1 | 0   | 0 | 2.488Gbps   |  |  |

Table 1- Receive Filter Data Rates

The 3-bit control word is set in the RATE\_SELECT register (C4h, RX\_FILTER, bits 2:0).

#### 4.2.3. Receiver CML Output Stage

The CML output stage has two slew rate settings, selected by CML\_SLEW (C5h, RX\_DRIVER, bit 1). The switching speed can be reduced in order to minimise electromagnetic radiation by setting CML SLEW to a '1'. Setting CML SLEW to '0' maximises the slew rate of the output.

The signal swing can also be adjusted. Setting CML\_LEVEL to '0' (C5h, RX\_DRIVER, bit 0) results in a higher receiver differential output swing. Setting CML\_LEVEL to '1' results in a reduced output swing.

RXOUT+/- can also be disabled by setting RX SQUELCH to a '1' (C2h, RX AGC, bit 2).

The PHY2078 can automatically disable RXOUT+/- if a LOS condition is detected. To enable this function LOS\_TO\_SQUELCH should be set to '1' (C2h, RX\_AGC, bit 3).

In both cases the output termination remains as  $50\Omega$  but a logical '0' is output on RXOUT+/-.

#### 4.2.4. Loss of Signal

Figure 10 - LOS Detection

Signal Detect (SD) or Loss of Signal (LOS) is detected by measuring the optical modulation amplitude (OMA).

The signal amplitude measured at RXIN+/- is compared to an analog threshold level set by the OMA\_DAC register (D9h, OMA\_DAC). If the received signal amplitude does not exceed the threshold then the LOS pin is asserted and the LOS indicator bit is set (ECh, HWARE SENSE STATUS, bit 3).

The polarity of the LOS pin and register indicator bit are controlled by MUX\_POLARITY (C6h, RX\_MUXPOL, bit 0). If MUX\_POLARITY is set to '0' then the LOS pin is set high during a loss of signal condition. Conversely, if MUX\_POLARITY is set to '1' then the LOS pin is set high when a signal is detected.

LOS detection has hysteresis, the level of which can be selected by OMAHYSTSEL (C6h, RX\_MUXPOL, bit 1). If OMAHYSTSEL is set to '0' then 3dB of hysteresis is used. If OMAHYSTSEL is set to '1' then 4dB of hysteresis is used.

| Parameter | Comments             | Step Size      | DAC<br>Range | Operational<br>Range |

|-----------|----------------------|----------------|--------------|----------------------|

| OMA_DAC   | OMA LOS DAC (8 bits) | 250μV (±125μV) | 0 to 64mV    | 10mV to 50mV         |

Table 2 - LOS DAC Characteristics

#### 4.2.5. Voltage Reference

The PHY2078 includes a temperature stable 1V reference source which provides the bias for the internal analog circuitry. The reference voltage is set using an internal resistor RINTERNAL (CEh, DAC\_PWRD, bit 5) to 1. The accuracy of the reference voltage using the internal resistor is +/-10%.

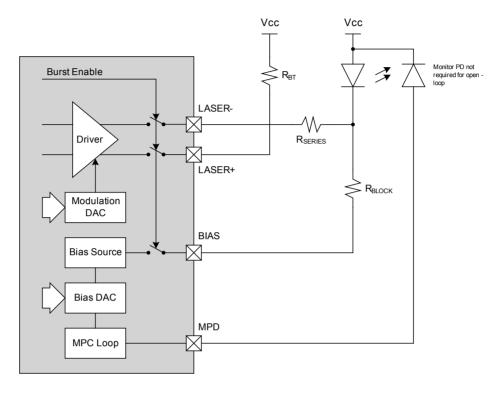

#### 4.3. Transmitter features

The transmitter input buffer provides the necessary drive to the laser driver output stage. It includes an internal high impedance bias network and is designed to be DC or AC-coupled. For high frequency applications an external termination network must be implemented. See section 7 for more interfacing details.

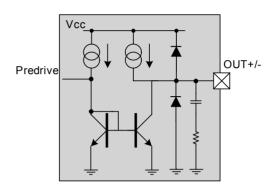

The laser driver output is designed to drive lasers in the common anode configuration using either AC- or DC-coupling. For burst mode operation DC-coupling must be used.

The laser driver circuit delivers a maximum peak to peak modulation current of 80mA measured at the device output pin LASER+.

By default the transmitter is non-inverting; however, to simplify the PCB layout of differential signals the polarity of the data can be inverted by setting TX POLARITY (CAh, TX DBUFF, bit 0) to '1'.

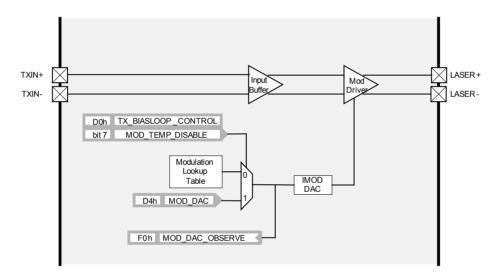

#### 4.3.1. Modulation Current Control

Figure 11 - Modulation Current Generation

The modulation current can be either set by a constant register value or controlled by a temperature indexed look-up table (LUT).

If MOD\_TEMP\_DISABLE is set to '1' (D0h, TX\_BIASLOOP\_CONTROL, bit 7) then the modulation DAC is set directly from a register (D4h, MOD\_DAC).

If MOD\_TEMP\_DISABLE is set to '0' then a 64 byte LUT is used to set the modulation DAC. The LUT is indexed by the temperature ADC (E1h, TEMP\_ADC\_VALUE), where the index is given by:

Index =  $(temperature ADC \times 64)/255$ .

The values of the LUT reside in the EEPROM, between addresses 80h (lowest temperature entry) and BFh (highest temperature entry), and are transferred at start up to on-chip registers.

The active setting for the modulation DAC can be observed by reading MOD DAC OBSERVE (F0h).

| Param  | eter Comm | nents                     | Step Size        | DAC<br>Range | Operational<br>Range |

|--------|-----------|---------------------------|------------------|--------------|----------------------|

| IMOD_D | AC Modula | tion current DAC (8 bits) | 0.375mA (±187μA) | 0 to 96mA    | 0mA to 80mA          |

Table 3 - Modulation DAC Characteristics

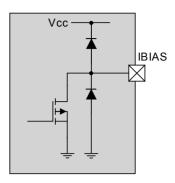

#### 4.3.2. Bias Current Control

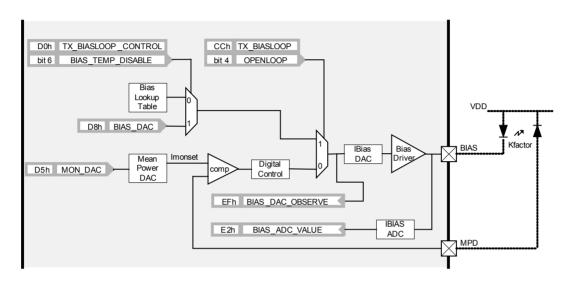

Figure 12 - Bias Current Generation

The PHY2078 can operate with open or closed loop bias control. In either mode the current setting for the bias DAC can be observed by reading BIAS\_DAC\_OBSERVE (EFh).

The bias current level is measured using an on-chip ADC and can be observed by reading BIAS\_ADC\_VALUE (E2h).

| Parameter | Comments                  | Step Size          | ADC<br>Range | Operational<br>Range |

|-----------|---------------------------|--------------------|--------------|----------------------|

| IBIAS_ADC | Bias current ADC (8 bits) | 0.588mA (±0.294mA) | 0 to 150mA   | 0mA to 90mA          |

Table 4 - Bias ADC Characteristics

| Parameter | Comments                  | Step Size          | DAC<br>Range | Operational<br>Range |

|-----------|---------------------------|--------------------|--------------|----------------------|

| IBIAS_DAC | Bias current DAC (8 bits) | 0.392mA (±0.196mA) | 0 to 100mA   | 0mA to 90mA          |

Table 5 - Bias DAC Characteristics

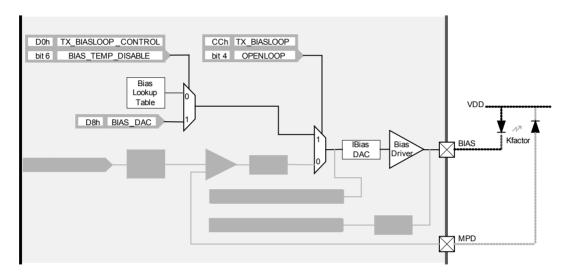

#### 4.3.3. Open Loop

If OPENLOOP is set to '1' (CCh, TX\_BIASLOOP, bit 4) the bias generator operates in open loop mode. The bias current can be either set by a constant register value or controlled by a temperature indexed lookup table (LUT).

If BIAS\_TEMP\_DISABLE is set to '1' (D0h, TX\_BIASLOOP\_CONTROL, bit 6) then the bias DAC is set directly from a register (D8h, BIAS\_DAC).

If BIAS\_TEMP\_DISABLE is set to '0' then a 128 byte LUT is used to set the bias DAC. The LUT is indexed by the temperature ADC (E1h), where the index is given by:

Index =  $(temperature ADC \times 128)/255$ .

The values for the LUT reside in the EEPROM, between addresses 00h (lowest temperature entry) and 7Fh (highest temperature entry), and are loaded into on-chip registers at start up.

In open loop mode the MPD device pin is not used and can be left unconnected.

Figure 13 - Bias Current Generation, Open Loop

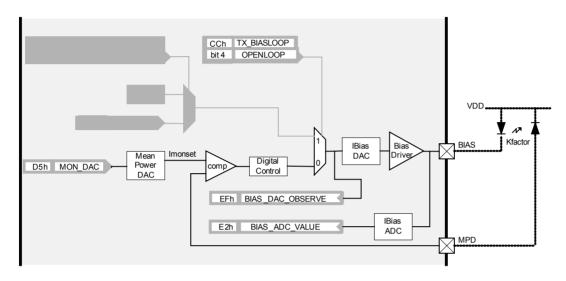

#### 4.3.4. Closed Loop

If OPENLOOP is set to '0' the bias generator operates in closed loop mode. The average output power of the laser is controlled by a digital mean power control loop. The feedback to the control loop is provided by a monitor photodiode connected to MPD. The current from the monitor photodiode is compared with a reference current (Imonset). This is output by the mean power DAC and controlled by MON\_DAC (D5h).

In order to provide the required resolution and range the mean power DAC has three step sizes as shown in the table below.

| Parameter | Comments                 | Step Size and Resolution                                                                                                                  | Range       |

|-----------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Imonset   | Mean power DAC (8 bits). | MON_DAC ≤ 31 = $1.042\mu$ A (±0.5 $\mu$ A)<br>32 ≤ MON_DAC ≤ 127 = $4.167\mu$ A (±2 $\mu$ A)<br>MON_DAC ≥ 128 = $16.67\mu$ A (±8 $\mu$ A) | 0 to 2.55mA |

Table 6 - Mean Power DAC Characteristics

The 3dB frequency of the digital mean power control loop is controlled by the size of a prescaling counter and can be determined (in Hertz) by:

$F_{3dB} = (Kfactor \times 692) / (M \times Imonset)$

where Kfactor = laser current to monitor photodiode current coupling coefficient Imonset = desired monitor photodiode current (A)  $M = 2^{(2 \times prescale\_size)}$

Prescale\_size is set by (D0h, TX\_BIASLOOP\_CONTROL, bits 2:0).

Figure 14 - Bias Current Generation, Closed Loop

#### 4.3.5. Initial Start-up

At power up or after TX\_DISABLE is de-asserted the PHY2078 can use a fast startup algorithm to quickly settle the mean power control loop to the desired bias level. The algorithm can only be invoked in closed loop, DC-coupled mode and after it has completed the low bandwidth digital mean power control loop takes over to maintain the optical output power. The details of the startup algorithm and its parameters are described in section 8.5.

#### 4.3.6. Burst Mode and Power Saving

In burst mode operation de-asserting the BEN+/- inputs causes the mean power control loop to pause and turning off the bias current. This mode of operation saves power compared with burst laser drivers that maintain a diverted bias current during burst off. The saving can be up to 95% of the bias and modulation current during burst off periods for a system with a split ratio of 16:1. Re-asserting the BEN+/- input re-enables the modulation current and releases the mean power control loop such that the bias current from the end of the preceding burst is used as the start point for the next burst. The burst on/off timings are detailed in the electrical timings section.

The polarity of the BEN+/- inputs can be inverted using BURST\_POLARITY (CAh, TX\_DBUFF, bit 2).

#### 4.3.7. Laser Driver Setup

There is a trimming network on the output driver which adjusts the time constant of the output damping on LASER+/-. It is controlled by the value in TX\_DRIVER\_CAP (C9h). Table 7 contains the valid register settings and the damping time constant they set, where RC = 16.8ps.

| TX_DRIVE_CAP value | Time Constant |

|--------------------|---------------|

| 00h                | 0             |

| 01h                | RC            |

| 02h                | 3RC           |

| 04h                | 5RC           |

| 08h                | 6RC           |

| 10h                | 7RC           |

| 20h                | 8RC           |

Table 7 - Time constant selection for the transmit output damping network

### 4.3.8. Performance Monitoring

As part of its main control loop the PHY2078 monitors temperature and transmit bias current via an onchip ADC. The ADC values are reported via registers TEMP\_ADC\_VALUE (E1h) and BIAS\_ADC\_VALUE (E2h).

The user has the option of using the measured values of temperature and bias current to set alarm bits. These are generated if the values measured are above or below programmable limits. The conditions are shown in Table 8 and 9 below.

| TEMP_MAX_ALARM_EN (DAh ALARM_EN bit 3) | TEMP_MIN_ALARM_EN (DAh ALARM_EN bit 2) | CONDITION                                             | TEMP_MAX_ERROR<br>(EAh bit7) | TEMP_MIN_ERROR<br>(EAh bit 6) |

|----------------------------------------|----------------------------------------|-------------------------------------------------------|------------------------------|-------------------------------|

| 1                                      | ×                                      | TEMP_ADC_VALUE > TEMP_MAX (DBh)                       | 1                            | 0                             |

| Х                                      | Х                                      | TEMP_MIN (DCh)<<br>TEMP_ADC_VALUE <<br>TEMP_MAX (DBh) | 0                            | 0                             |

| х                                      | 1                                      | TEMP_ADC_VALUE < TEMP_MIN (DCh)                       | 0                            | 1                             |

| 0                                      | 0                                      | Х                                                     | 0                            | 0                             |

Table 8 - Over and under temperature alarm generation

| BIAS_MAX_ALARM_EN<br>(DAh ALARM_EN bit 1) | BIAS_MIN_ALARM_EN<br>(DAh ALARM_EN bit 0) | CONDITION                                              | BIAS_MAX_ERROR<br>(EAh bit 5) | BIAS_MIN_ERROR<br>(EAh bit 4) |

|-------------------------------------------|-------------------------------------------|--------------------------------------------------------|-------------------------------|-------------------------------|

| 1                                         | ×                                         | BIAS_ADC_VALUE ><br>BIAS_MAX (DDh)                     | 1                             | 0                             |

| Х                                         | Х                                         | BIAS_MIN (DEh) <<br>BIAS_ADC_VALUE <<br>BIAS_MAX (DDh) | 0                             | 0                             |

| х                                         | 1                                         | BIAS_ADC_VALUE <<br>BIAS_MIN (DEh)                     | 0                             | 1                             |

| 0                                         | 0                                         | Х                                                      | 0                             | 0                             |

Table 9 - Bias current alarm generation

An out of range monitored temperature (TEMP\_MAX\_ERROR is set to '1' or TEMP\_MIN\_ERROR is set to '1') will cause a TX\_FAULT condition to be raised.

An out of range monitored bias current (BIAS\_MAX\_ERROR is set to '1' or BIAS\_MIN\_ERROR is set to '1') will cause a TX\_FAULT condition to be raised.

The response of the PHY2078 to an alarm condition is described in Section 4.4.

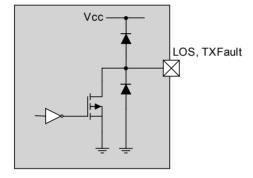

### 4.4. Laser Safety Features

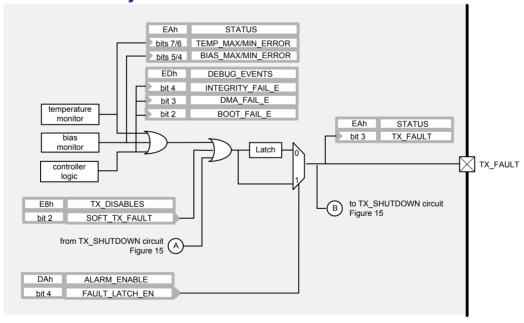

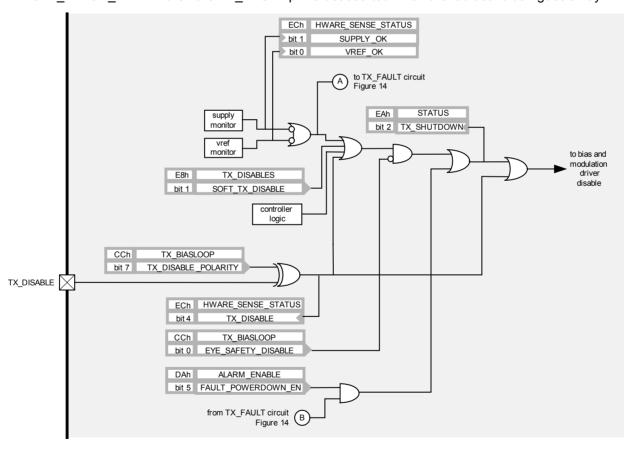

Figure 15 - Transmit Fault Generation

The laser safety circuit monitors the device for potential faults. If a fault is detected the pin TX\_FAULT is asserted.

The register bit TX\_FAULT (EAh, STATUS, bit 3) reflects the status of the pin TX\_FAULT.

Using bias alarm requires FAULT\_LATCH\_ENABLE to be set to 0.

A transmit fault can be raised by the following:

- 1. The temperature monitor detects that the measured temperature has gone out of range (see section 4.3.8).

- 2. The bias current monitor detects that the measured transmit bias current has gone out of range (see section 4.3.8).

- 3. The internal controller logic detects that a DMA from EEPROM has failed (see section 5.1)

- 4. The SOFT TX FAULT bit (E8h, TX DISABLES, bit 2) is set to '1'

- 5. The voltage reference monitoring circuit detects that the reference voltage is incorrect

- 6. The supply monitoring circuit detects that the power supply voltage is incorrect

If FAULT\_LATCH\_EN = '0' (DAh, ALARM\_ENABLE, bit 4) then a transmit fault condition will cause the TX\_FAULT pin to stay asserted even if the fault condition goes away. The pin will stay asserted until either the chip is power cycled or the pin TX\_DISABLE is set to '1' or the register SOFT\_TX\_DISABLE is set to '1' (E8h, TX\_DISABLES, bit 1) or FAULT\_LATCH\_EN is set to '1'.

If FAULT LATCH EN = '1' then the TX FAULT pin is deasserted when the fault condition goes away.

Figure 16 - Transmit Shutdown Generation

The PHY2078 contains circuitry to shutdown the transmitter bias and modulation current if a problem is detected. The conditions to cause a shutdown are:

- 1. The voltage reference monitoring circuit detects that the reference voltage is incorrect

- 2. The supply monitoring circuit detects that the power supply voltage is incorrect

- 3. The SOFT TX DISABLE bit (E8h, TX DISABLES, bit 1) is set to '1'

- 4. The internal controller logic has not successfully completed its initialisation (see section 5.1)

- 5. The pin TX\_DISABLE is asserted

- 6. TX FAULT is active and FAULT POWERDOWN EN = '1' (DAh ALARM EN bit 5)

If a shutdown condition occurs the modulation and bias currents are disabled. Conditions 1-4 can be disabled from contributing to shutdown by setting EYE\_SAFETY\_DISABLE = '1' (CCh, TX\_BIASLOOP, bit 0). This feature should be used with great caution.

The polarity of the TX\_DISABLE pin can be inverted by setting TX\_DISABLE\_POLARITY (CCh, TX\_BIASLOOP, bit 7).

The register bit TX\_SHUTDOWN (EAh, STATUS, bit 2) reflects the status of the shutdown circuit.

The register bit TX\_DISABLE (ECh, HWARE\_SENSE\_STATUS, bit 4) reflects the status of the pin TX\_DISABLE (after optional inversion using TX\_DISABLE\_POLARITY).

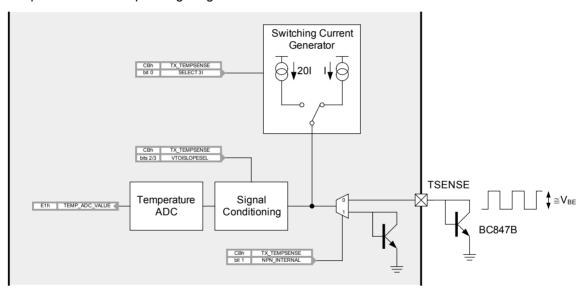

### 4.5. Temperature Measurement

The PHY2078 uses an on-chip 8 bit ADC to perform a temperature measurement once per iteration of its main control loop (approximately every 10ms). The measured ADC value can be read from register TEMP\_ADC\_VALUE (E1h). This measurement can be used to control the modulation and bias currents.

The temperature is determined by forcing two different currents through a diode connected transistor (base and collector shorted together) measuring the resulting voltage difference,  $\Delta V_{BE}$ . This voltage is directly proportional to the temperature. If NPN\_INTERNAL is set to '1' (CBh, TX\_TEMPSENSE, bit 1) then an on-chip transistor is used. In this case pin TSENSE should be left unconnected. If NPN\_INTERNAL is set to '0' then the ADC uses a suitable external device connected to pin TSENSE. The transistor can be any standard npn silicon transistor with a beta > 100, however Phyworks recommends using a BC847B or similar. Where accuracy improvement is needed calibration and averaging of the temperature sensor values are recommended or use of an external temperature sensor such as that in a microcontroller.

SELECT\_3I (CBh, TX\_TEMPSENSE, bit 0) and VTOISLOPESEL (CBh, TX\_TEMPSENSE, bits 2 - 3) can be adjusted, depending on the external device used, to ensure that the PHY2078 is capable of measuring the required range of temperatures.

The temperature sensor operating range is shown in Table 10.

Figure 17 – Temperature sensor functional block diagram

| Parameter                  | Comment           | Symbol          | Min | Typical | Max | Units  |

|----------------------------|-------------------|-----------------|-----|---------|-----|--------|

| Temperature                |                   | Т               | -45 |         | 90  | °C     |

| ADC slope                  | VTOISLOPESEL = 00 |                 |     | 0.67    |     | °C/bit |

|                            | VTOISLOPESEL = 01 |                 |     | 1.32    |     | °C/bit |

|                            | VTOISLOPESEL = 10 |                 |     | 1.63    |     | °C/bit |

|                            | VTOISLOPESEL = 11 |                 |     | 2.25    |     | °C/bit |

| TSENSE delta input voltage | VTOISLOPESEL = 00 | $\Delta V_{BE}$ | 50  |         | 100 | mV     |

Table 10 – Internal Temperature Measurement

### 5. Control Interface

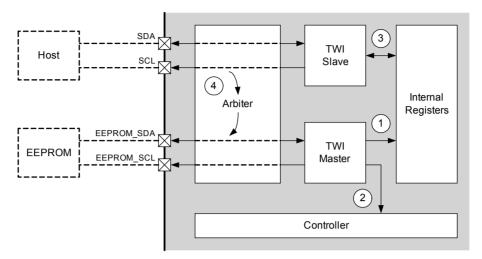

Figure 18 - Serial interfaces to internal registers

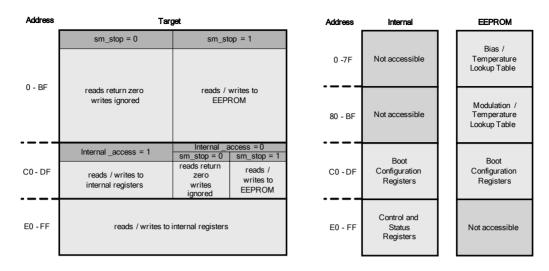

The host communicates with the PHY2078 and the EEPROM via the slave Two Wire Interface (TWI) pins of the PHY2078. Slave addresses A0h and A2h are supported, register settings for PHY2078 are stored in A2h. If a transaction arriving at the slave interface is addressed to A2h, then the PHY2078 examines the register address in order to decide how the transaction should be processed (see address map in figure 19).

- If the register is implemented in EEPROM only (addresses 00h to BFh) then the transaction is forwarded to the EEPROM via path 4 in figure 18. There is a direct combinational logic path between the slave and master interfaces which makes the PHY2078 transparent when transactions from the host are forwarded to the EEPROM.

- If the register is only implemented internally to the PHY2078 (addresses E0h to FFh) then the data is written to or read from the registers inside the PHY2078 (path 3).

- If the register is implemented both internally and EEPROM (addresses C0h to DFh) then the PHY2078 checks the INTERNAL\_ACCESS register bit (E7h INTERNAL bit 1) to determine whether the host wishes to access the EEPROM or internal registers. Set INTERNAL\_ACCESS is set to '1' to access the internal registers and '0' to access the EEPROM.

When the PHY2078 comes out of reset, the state machine uses the master two wire interface to read configuration bytes out of EEPROM. This data is used to configure the internal registers of the device (path 1).

Subsequently, during normal operation the state machine will use the master interface to periodically access look-up table and alarm threshold information stored in the EEPROM (path 2). In order to prevent collisions between state machine and host accesses to EEPROM, the host must always stop the state machine before attempting to access the EEPROM by setting an internal register bit, SM\_STOP, to '1' (E7h, INTERNAL, bit 0). When the host has completed its transactions with the EEPROM it must set SM\_STOP to '0' to allow normal operation of the state machine to resume. If the host attempts to access the EEPROM when SM STOP is set to '0' then writes are ignored and reads return a zero.

Figure 19 - PHY2078 TWI Slave Accesses

# 5.1. Boot Sequence

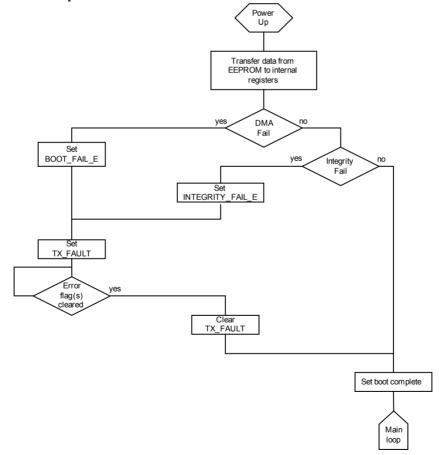

Figure 20 - PHY2078 Boot Sequence

At power up the PHY2078 attempts to read a number of bytes of configuration information from an external EEPROM into its internal registers.

If the read fails due to a problem on the TWI, such as a read not being correctly acknowledged, the state machine sets register bit BOOT\_FAIL\_E to '1' (EDh, DEBUG\_EVENTS, bit 2), raises a transmit fault condition and remains in an error state.

The first two bytes read from EEPROM, C0h and C1h, are compared against a data integrity number (C35Ah). If the compare fails, the state machine sets register bit INTEGRITY\_FAIL\_E to '1' (EDh, DEBUG EVENTS, bit 4), raises a transmit fault condition and remains in an error state.

In the error state the host is able to configure the internal registers of the PHY2078 using the slave TWI. When it has completed configuration the host must clear the active error(s) by writing a '1' to the corresponding bit(s). When the state machine sees that the error bit(s) are cleared it clears the transmit fault condition.

The state machine sets the register BOOT\_COMPLETE\_E (EDh, DEBUG\_EVENTS, bit 1) to indicate that the boot process is complete and then enters the main control loop.

# 5.2. Main Control Loop

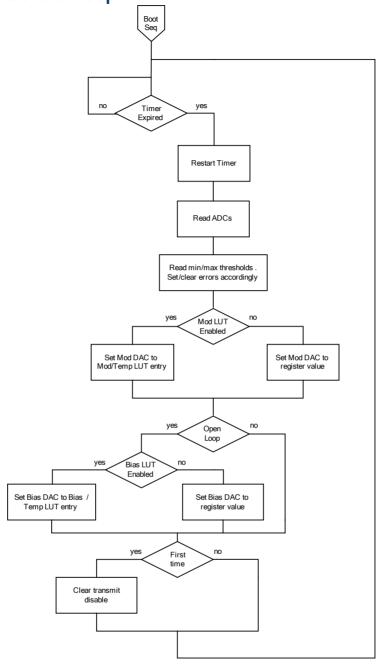

Figure 21 - PHY2078 Main Loop Function

A loop timer is implemented in the state machine to ensure that the start of each iteration of the loop is separated by 10ms.

When the timer has expired the state machine reads the on-chip ADC to obtain temperature and bias current levels, reads alarm levels out of EEPROM and sets/clears performance alarms accordingly.

The state machine then sets the modulation current and bias current.

At the end of the first iteration of the loop after boot-up the state machine clears transmit disable to enable the transmit data path.

#### 5.3. 2-wire Serial Interface

The PHY2078 has a pair of 2-wire serial interfaces: a slave for interfacing to a host for module setup and programming, and a master for interfacing to an external EEPROM and for device configuration after reset. Both interfaces communicate using the protocol described in this section.

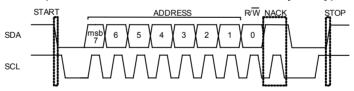

#### 5.3.1. Framing and Data Transfer

The two-wire interface comprises a clock line (SCL) and a data line (SDA). When the bus is idle both are pulled high within the PHY2078 by  $8k\Omega$  pull-ups.

An individual transaction is framed by a start condition and a stop condition. A start condition occurs when a bus master pulls SDA low while the clock is high. A stop condition occurs when the bus master allows SDA to transition low-to-high when the clock is high. Within the frame, the master has exclusive control of the bus. The PHY2078 supports REPEAT START conditions whereby the master may simultaneously end one frame and start another without releasing the bus by replacing the STOP condition with a START condition.

Within a frame, the state of SDA may only change when SCL is low. A data bit is transferred on a low-to-high transition of SCL. Data is arranged in packets of 9 bits. The first 8 bits represent data to be transferred (most significant bit first). The last bit is an acknowledge bit. The recipient of the data holds SDA low during the ninth clock cycle of a data packet to acknowledge (ACK) the byte. Leaving SDA to float high on the ninth bit signals a not-acknowledged (NACK) condition. The interpretation of the acknowledge bit by the sender will depend on the type of transaction and the nature of the byte being received.

#### 5.3.2. Device Addressing

The first byte to be sent after a START condition is an address byte. The first seven bits of the byte contain the target slave address (msb first). The eighth bit indicates the transaction type - '0' = write, '1' = read. Each slave interface on the bus is assigned a 7-bit slave address. If no slave matches the address broadcast by the master then SDA will be left to float high during the acknowledge bit and the master receives a NACK. The master must then assert a STOP condition. If a slave identifies the address then it acknowledges the master and proceeds with the transaction identified by the type bit.

Figure 22 - Address decoding example – slave not available

#### 5.3.3. Write Transaction

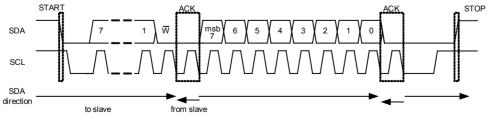

Figure 23 shows an example of a write transaction. The address byte is successfully acknowledged by the slave, and the type bit is set low to signify a write transaction. After the acknowledge the master sends a single data byte. All signalling is controlled by the master except for the SDA line during the acknowledge bits. During the acknowledge the direction of the SDA line is reversed and the slave pulls SDA low to return a '0' (ACK) to the master.

Figure 23 - Write transaction

If the slave is unable to receive data then it should return a NACK after the data byte. This will cause the master to issue a STOP and thus terminate the transaction.

The PHY2078 interprets the first data byte as a register address. This will be used to set an internal memory pointer. Subsequent data bytes within the same transaction will then be written to the memory location addressed by the pointer. The pointer is auto-incremented after each byte. There is no limit to the number of bytes which may be written in a single burst to the internal RAM of the PHY2078. If, however, the write access is destined for the EEPROM the requirements of page writes specified for the EEPROM apply.

If the slave is not ready to receive a byte then it may hold SCL low immediately after the acknowledge bit. When SCL is released the master starts to send the next byte. This is known as clock stretching. The PHY2078 slave interface will not clock stretch at up to 100 kHz SCL frequency.

#### 5.3.4. Read Transaction

Figure 24 - Read transaction

Figure 24 shows an example of a 2 byte read transaction. The address byte is successfully acknowledged by the slave, and the type bit is set high to signify a read. After the ACK the slave returns a byte from the location identified by the internal memory pointer. This pointer is then auto-incremented. The slave then releases SDA so that the master can ACK the byte. If the slave receives an ACK then it will send another byte. The master identifies the last byte by sending a NACK to the slave. The master then issues a STOP to terminate the transaction.

Thus, to implement a random access read transaction, a write must first be issued by the master containing a slave address byte and a single data byte (the register address) as shown in Figure 23. This sets up the memory pointer. A read is then sent to retrieve data from this address (see Figure 24).

# 6. Register Map

Where a single power-on reset (PoR) value is shown for a range of addresses, that value applies to all bytes in the range. Note that the power on reset values may be overwritten during initialisation from the EEPROM.

For registers containing a single 8-bit field, the most significant bit of the field is stored in bit 7 of the register byte.

Note that 'reserved' or 'internal use only' register bits are specified as read only. These registers should not changed from their PoR default settings.

- R Bit is read only. A write to this bit via the TWI will have no effect. The value may be changed by the device itself as part of its normal operation

- R/W Bit is readable and writable via the TWI. The value will not be changed by the device itself except under a device reset.

- Bit is readable via the TWI. The bit may be set by the device itself as part of its normal operation. Once set the bit may be cleared by writing a '1' via the TWI. Writing a '0' via the TWI has no effect.

| C0h  | DATA_INT | EGRITY | _LOWER | Integrity check for EEPROM contents. Must be set to C3h for a boot load from EEPROM to be successful.  Note, this register exists only in EEPROM and not in the |

|------|----------|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре | R/W      | PoR    | 00h    | internal registers of the device, therefore a write to this address when 'INTERNAL_ACCESS' is set high will be ignored and a read return zero.                  |

| C1h  | DATA_INT | EGRITY | _UPPER | Integrity check for EEPROM contents. Must be set to 5Ah for a boot load from EEPROM to be successful.  Note, this register exists only in EEPROM and not in the |

|------|----------|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре | R/W      | PoR    | 00h    | internal registers of the device, therefore a write to this address when 'INTERNAL_ACCESS' is set high will be ignored and a read return zero.                  |

| C2h | RX_AGC             |      |     | This register controls functions in the AGC in the receive path of the device                                                              |

|-----|--------------------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Field name         | Type | PoR |                                                                                                                                            |

| 7   | -                  | R    | 0   | reserved                                                                                                                                   |

| 6   | -                  | R    | 0   | reserved                                                                                                                                   |

| 5   | -                  | R    | 0   | reserved                                                                                                                                   |

| 4   | -                  | R    | 0   | reserved                                                                                                                                   |

| 3   | LOS_TO_<br>SQUELCH | R/W  | 0   | Setting this bit to a '1' connects the LOS function to the receiver squelch such that a LOS will automatically disable the receiver output |

| 2   | RX_SQUELCH         | R/W  | 0   | Setting this bit to a '1' causes the receiver output to be disabled                                                                        |

| 1   | -                  | R/W  | 0   | Internal use only. Must be set to '0'                                                                                                      |

| 0   | -                  | R/W  | 0   | Internal use only. Must be set to '0'                                                                                                      |

| C3h |             |      |     | This register controls functions in the limiter in the receive path of the device |

|-----|-------------|------|-----|-----------------------------------------------------------------------------------|

| Bit | Field name  | Type | PoR |                                                                                   |

| 7   | -           | R    | 0   | reserved                                                                          |

| 6   | -           | R    | 0   | reserved                                                                          |

| 5   | -           | R    | 0   | reserved                                                                          |

| 4   | -           | R    | 0   | reserved                                                                          |

| 3   | -           | R    | 0   | reserved                                                                          |

| 2   | -           | R/W  | 0   | Internal use only. Must be set to '0'                                             |

| 1   | RX_POLARITY | R/W  | 0   | Setting this bit to a '1' causes the receive output polarity to be inverted       |

| 0   | -           | R/W  | 0   | Internal use only. Must be set to '0'                                             |

| C4h | RX_FILTER      |      |     | This register controls functions in the filter in the receive path of the device |

|-----|----------------|------|-----|----------------------------------------------------------------------------------|

| Bit | Field name     | Type | PoR |                                                                                  |

| 7   | -              | R    | 0   | reserved                                                                         |

| 6   | -              | R    | 0   | reserved                                                                         |

| 5   | -              | R    | 0   | reserved                                                                         |

| 4   | -              | R    | 0   | reserved                                                                         |

| 3   | -              | R/W  | 0   | Internal use only. Must be set to '0'                                            |

| 2   | RATE_SELECT(2) | R/W  | 0   | Selects the filter rate in the receiver '000' = 155 Mbps                         |

| 1   | RATE_SELECT(1) | R/W  | 0   | '001' = 622 Mbps<br>'010' = Reserved                                             |

| 0   | RATE_SELECT(0) | R/W  | 0   | '011' = 1250 Mbps<br>'100' = 2488 Mbps                                           |

| C5h | RX_DRIVER  |      |     | This register controls functions in the output driver in the receive path of the device |

|-----|------------|------|-----|-----------------------------------------------------------------------------------------|

| Bit | Field name | Туре | PoR |                                                                                         |

| 7   | -          | R    | 0   | reserved                                                                                |

| 6   | -          | R    | 0   | reserved                                                                                |

| 5   | -          | R    | 0   | reserved                                                                                |

| 4   | -          | R    | 0   | reserved                                                                                |

| 3   | -          | R    | 0   | reserved                                                                                |

| 2   | -          | R    | 0   | reserved                                                                                |

| 1   | CML_SLEW   | R/W  | 0   | Sets the receiver output slew rate '1' = slow '0' = fast                                |

| 0   | CML_LEVEL  | R/W  | 0   | Sets the receiver output swing level '1' = low swing '0' = high swing                   |

| C6h | RX_MUXPOL    |      |     | This register controls the loss of signal detection circuit in the receive path of the device                  |

|-----|--------------|------|-----|----------------------------------------------------------------------------------------------------------------|

| Bit | Field name   | Type | PoR |                                                                                                                |

| 7   | -            | R    | 0   | reserved                                                                                                       |

| 6   | -            | R    | 0   | reserved                                                                                                       |

| 5   | -            | R    | 0   | reserved                                                                                                       |

| 4   | -            | R    | 0   | reserved                                                                                                       |

| 3   | -            | R    | 0   | reserved                                                                                                       |

| 2   | -            | R    | 0   | reserved                                                                                                       |

| 1   | OMAHYSTSEL   | R/W  | 0   | Sets the amount of hysteresis in the LOS detection circuit '1' = 4 dB of hysteresis '0' = 3 dB of hysteresis   |

| 0   | MUX_POLARITY | R/W  | 0   | Sets the polarity of LOS output pin '1' = Pin is high when signal detect '0' = Pin is high when loss of signal |

| C7h  | TEST0 |     |     | Internal use only, must be set to 00h |

|------|-------|-----|-----|---------------------------------------|

| Type | R/W   | PoR | 00h |                                       |

| C8h  | TEST1 |     |     | Internal use only, must be set to 00h |

|------|-------|-----|-----|---------------------------------------|

| Type | R/W   | PoR | 00h |                                       |

| C9h  | TX_DRIVER_CAI | Р   |     | This register allows selective snubbing capacitors to be applied to the transmit output stage. Setting the register |  |

|------|---------------|-----|-----|---------------------------------------------------------------------------------------------------------------------|--|

| Туре | R/W           | PoR | 00h | to 0h applies no damping.                                                                                           |  |

| CAh | TX_DBUFF           |      |     | This register controls functions in the data buffer in the transmit path of the device                                                                          |

|-----|--------------------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Field name         | Туре | PoR |                                                                                                                                                                 |

| 7   | -                  | R    | 0   | reserved                                                                                                                                                        |

| 6   | -                  | R    | 0   | reserved                                                                                                                                                        |

| 5   | -                  | R    | 0   | reserved                                                                                                                                                        |

| 4   | HIGH_EXT(1)        | R/W  | 0   | This register controls the pedestal current I <sub>ped</sub> to allow high extinction ratios to be set with consequently reduced rise time.                     |

| 3   | HIGH_EXT(0)        | R/W  | 0   | '00' : default, $I_{ped}$ = 0μA, low ER, higher speed<br>'01' : $I_{ped}$ = 130μA<br>'10' : $I_{ped}$ = 390μA<br>'11' : $I_{ped}$ = 520μA, high ER, lower speed |

| 2   | BURST_<br>POLARITY | R/W  | 0   | Setting this bit inverts the polarity of the burst enable input pins                                                                                            |

| 1   | -                  | R/W  | 0   | Internal use only. Must be set to '0'                                                                                                                           |

| 0   | TX_POLARITY        | R/W  | 0   | Setting this bit to a '1' causes the transmit output polarity to be inverted                                                                                    |

| CBh | TX_TEMPSENSE    | •    |     | This register controls functions associated with the device temperature measurement                                                                          |

|-----|-----------------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Field name      | Туре | PoR |                                                                                                                                                              |

| 7   | -               | R    | 0   | reserved                                                                                                                                                     |

| 6   | -               | R    | 0   | reserved                                                                                                                                                     |

| 5   | -               | R    | 0   | reserved                                                                                                                                                     |

| 4   | -               | R    | 0   | reserved                                                                                                                                                     |

| 3   | VTOISLOPESEL(1) | R/W  | 0   | This field modifies the expected slope from the temperature sensor into the ADC and should be set                                                            |

| 2   | VTOISLOPESEL(0) | R/W  | 0   | depending on the type of external temperature sensor                                                                                                         |

| 1   | NPN_INTERNAL    | R/W  | 0   | Setting this bit to '1' selects the internal sensor for temperature measurement. Setting to '0' selects an external sensor connected to the TSENSE input pin |

| 0   | SELECT_3I       | R/W  | 0   | Setting this bit to '1' causes the temperature sensor to operate at 3 times the default measurement current.                                                 |

| CCh | TX_BIASLOOP             |      |     | This register controls functions in the bias current generator in the transmit path of the device |

|-----|-------------------------|------|-----|---------------------------------------------------------------------------------------------------|

| Bit | Field name              | Type | PoR |                                                                                                   |

| 7   | TX_DISABLE_<br>POLARITY | R/W  | 0   | Setting this bit to a '1' inverts the polarity of the TX_DISABLE input pin                        |

| 6   | -                       | R/W  | 0   | Internal use only. Must be set to '0'                                                             |

| 5   | -                       | R/W  | 0   | Internal use only. Must be set to '0'                                                             |

| 4   | OPENLOOP                | R/W  | 0   | Sets the configuration of the transmit bias circuit '1' = open loop '0' = closed loop             |

| 3   | -                       | R/W  | 0   | Internal use only. Must be set to '0'                                                             |

| 2   | -                       | R/W  | 0   | Internal use only. Must be set to '0'                                                             |

| 1   | -                       | R/W  | 0   | Internal use only. Must be set to '0'                                                             |

| 0   | RESERVED                | R/W  | 0   | Set to '0' during operation of the device                                                         |

| CDh  | TEST2 |     |     | Internal use only, must be set to 00h |

|------|-------|-----|-----|---------------------------------------|

| Type | R/W   | PoR | 00h |                                       |

| CEh | DAC_PWRD   |      |     |                                                                                            |

|-----|------------|------|-----|--------------------------------------------------------------------------------------------|

| Bit | Field name | Туре | PoR |                                                                                            |

| 7   | -          | R    | 0   | reserved                                                                                   |

| 6   | -          | R    | 0   | reserved                                                                                   |

| 5   | RINTERNAL  | R/W  | 0   | Set to '1', an internal $10k\Omega$ resistor is used for generating the reference voltage. |

| 4   | -          | R/W  | 0   | Internal use only, must be set to 0                                                        |

| 3   | -          | R/W  | 0   | Internal use only, must be set to 0                                                        |

| 2   | -          | R/W  | 0   | Internal use only, must be set to 0                                                        |

| 1   | -          | R/W  | 0   | Internal use only, must be set to 0                                                        |

| 0   | -          | R/W  | 0   | Internal use only, must be set to 0                                                        |

| CFh  | TEST3 |     |     | Internal use only, must be set to 00h |

|------|-------|-----|-----|---------------------------------------|

| Туре | R/W   | PoR | 00h |                                       |

| D0h | TX_BIASLOOP_CONTROL       |      |     | This register controls generation of the transmit bias current                                                                       |

|-----|---------------------------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Field name                | Type | PoR |                                                                                                                                      |

| 7   | MOD_TEMP_<br>DISABLE      | R/W  | 0   | Setting this bit to '1' disables the modulation current / temperature lookup table                                                   |

| 6   | BIAS_TEMP_<br>DISABLE     | R/W  | 0   | In open loop mode setting this bit to '1' disables the bias current / temperature lookup table. In closed loop mode it has no effect |

| 5   | BURST_START_<br>FACTOR(1) | R/W  | 0   | These bits control the ramp rate used in the closed loop                                                                             |

| 4   | BURST_START_<br>FACTOR(0) | R/W  | 0   | bias current fast startup algorithm. See section 8.5 for further details                                                             |

| 3   | BIAS_STARTUP_<br>BYPASS   | R/W  | 0   | Setting this bit to '1' disables the fast startup algorithm used for closed loop bias current generation                             |

| 2   | PRESCALE_<br>SIZE(2)      | R/W  | 0   |                                                                                                                                      |

| 1   | PRESCALE_<br>SIZE(1)      | R/W  | 0   | These bits configure the loop bandwidth of the closed loop bias current. See the section 4.3.4 for further details                   |

| 0   | PRESCALE_<br>SIZE(0)      | R/W  | 0   |                                                                                                                                      |