### Liability disclaimer

Nordic Semiconductor ASA reserves the right to make changes without further notice to the product to improve reliability, function or design. Nordic Semiconductor ASA does not assume any liability arising out of the application or use of any product or circuits described herein.

All application information is advisory and does not form part of the specification.

#### Limiting values

Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the specifications are not implied. Exposure to limiting values for extended periods may affect device reliability.

#### Life support applications

Nordic Semiconductor's products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Nordic Semiconductor ASA customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Nordic Semiconductor ASA for any damages resulting from such improper use or sale.

| Data sheet status                 |                                                                          |

|-----------------------------------|--------------------------------------------------------------------------|

| Objective product specification   | This product specification contains target specifications for product    |

|                                   | development.                                                             |

| Preliminary product specification | This product specification contains preliminary data; supplementary      |

|                                   | data may be published from Nordic Semiconductor ASA later.               |

| Product specification             | This product specification contains final product specifications. Nordic |

|                                   | Semiconductor ASA reserves the right to make changes at any time         |

|                                   | without notice in order to improve design and supply the best possible   |

|                                   | product.                                                                 |

#### Contact details

For your nearest dealer, please see www.nordicsemi.com

#### Main office:

Otto Nielsens veg 12 7004 Trondheim Phone: +47 72 89 89 00 Fax: +47 72 89 89 89

www.nordicsemi.com

## **Revision History**

| Date           | Version | Description                                              |

|----------------|---------|----------------------------------------------------------|

| October 2009   | 1.0     | Product specification                                    |

| May 2010       | 1.1     | Updated section 2.1 on page 12, Table 14.                |

|                |         | on page 58, Table 15. on page 59, Figure                 |

|                |         | 34. on page 77, Table 34. on page 77, Table              |

|                |         | <u>57. on page 106, Table 113. on page 177,</u>          |

|                |         | chapter 12 on page 112, chapter 24 on                    |

|                |         | <u>page 171</u> .                                        |

| September 2010 | 1.2     | Updated sections 2.4 on page 16, 6.3.6.1                 |

|                |         | and <u>6.3.6.2 on page 75</u> , <u>Table 56. on page</u> |

|                |         | 104, Table 57. on page 106, Table 87. on                 |

|                |         | page 146, chapter 24 on page 171 and                     |

|                |         | chapter 28 on page 182.                                  |

#### **RoHS statement**

Nordic Semiconductor's products meet the requirements of Directive 2002/95/EC of the European Parliament and of the Council on the Restriction of Hazardous Substances (RoHS). Complete hazardous substance reports as well as material composition reports for all active Nordic products can be found on our web site <a href="https://www.nordicsemi.com">www.nordicsemi.com</a>.

## **Contents**

| 1      | Introduction                           | 11 |

|--------|----------------------------------------|----|

| 1.1    | Prerequisites                          | 11 |

| 1.2    | Writing conventions                    | 11 |

| 2      | Product overview                       | 12 |

| 2.1    | Features                               | 12 |

| 2.2    | Block diagram                          | 14 |

| 2.3    | Pin assignments                        |    |

| 2.3.1  | 24-pin 4×4 QFN-package variant         |    |

| 2.3.2  | 32-pin 5×5 QFN-package variant         |    |

| 2.3.3  | 48-pin 7×7 QFN-package variant         |    |

| 2.4    | Pin functions                          | 16 |

| 3      | RF transceiver                         |    |

| 3.1    | Features                               |    |

| 3.2    | Block diagram                          |    |

| 3.3    | Functional description                 |    |

| 3.3.1  | Operational Modes                      |    |

| 3.3.1. | - ·- · · · · · · · · · · · · · · · · · |    |

| 3.3.1. |                                        |    |

| 3.3.1. | · · · <b>,</b>                         |    |

| 3.3.1. |                                        |    |

| 3.3.1. |                                        |    |

| 3.3.1. | · · · · · · · · · · · · · · · · · · ·  |    |

| 3.3.1. | 9                                      |    |

| 3.3.2  | Air data rate                          |    |

| 3.3.3  | RF channel frequency                   |    |

| 3.3.4  | Received Power Detector measurements   |    |

| 3.3.5  | PA control                             |    |

| 3.3.6  | RX/TX control                          |    |

| 3.4    | Enhanced ShockBurst™                   |    |

| 3.4.1  | Features                               |    |

| 3.4.2  | Enhanced ShockBurst™ overview          |    |

| 3.4.3  | Enhanced Shockburst™ packet format     |    |

| 3.4.3. |                                        |    |

| 3.4.3. |                                        |    |

| 3.4.3. | <b>\</b>                               |    |

| 3.4.3. | <b>J</b>                               |    |

| 3.4.3. | ,                                      |    |

| 3.4.4  | Automatic packet assembly              |    |

| 3.4.5  | Automatic packet disassembly           |    |

| 3.4.6  | Automatic packet transaction handling  |    |

| 3.4.6. | <b>5</b>                               |    |

| 3.4.6. | \                                      |    |

| 3.4.7  | Enhanced ShockBurst™ flowcharts        | 31 |

| 3.4.7.1  | PTX operation                                              | 31  |

|----------|------------------------------------------------------------|-----|

| 3.4.7.2  | PRX operation                                              | 33  |

| 3.4.8    | MultiCeiver™                                               | 34  |

| 3.4.9    | Enhanced ShockBurst™ timing                                | 36  |

| 3.4.10   | Enhanced ShockBurst™ transaction diagram                   |     |

| 3.4.10.1 | Single transaction with ACK packet and interrupts          |     |

| 3.4.10.2 | Single transaction with a lost packet                      |     |

| 3.4.10.3 | Single transaction with a lost ACK packet                  |     |

| 3.4.10.4 | Single transaction with ACK payload packet                 |     |

| 3.4.10.5 | Single transaction with ACK payload packet and lost packet |     |

| 3.4.10.6 | Two transactions with ACK payload packet and the first ACK |     |

|          | packet lost                                                | .42 |

| 3.4.10.7 | Two transactions where max retransmissions is reached      |     |

| 3.4.11   | Compatibility with ShockBurst™                             |     |

| 3.4.11.1 | ShockBurst™ packet format                                  |     |

| 3.5      | Data and control interface                                 |     |

| 3.5.1    | SFR registers                                              |     |

| 3.5.2    | SPI operation                                              |     |

| 3.5.2.1  | SPI commands                                               |     |

| 3.5.3    | Data FIFO                                                  |     |

| 3.5.4    | Interrupt                                                  |     |

| 3.6      | Register map                                               |     |

| 3.6.1    | Register map table                                         |     |

|          | U                                                          |     |

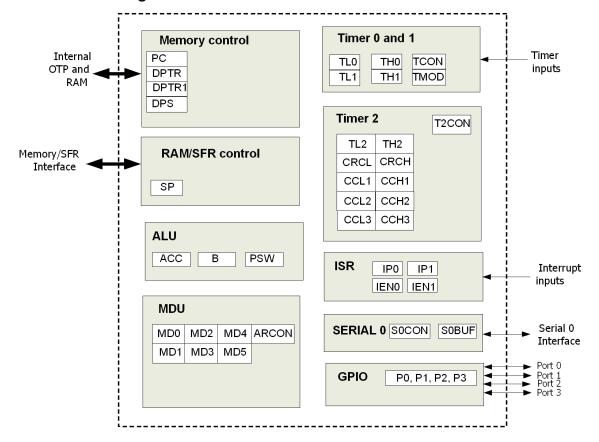

| 4.1      | Block diagram                                              |     |

| 4.2      | Features                                                   |     |

| 4.3      | Functional description                                     |     |

| 4.3.1    | Arithmetic Logic Unit (ALU)                                |     |

| 4.3.2    | Instruction set summary                                    |     |

| 4.3.3    | Opcode map                                                 |     |

|          | mory and I/O organization                                  |     |

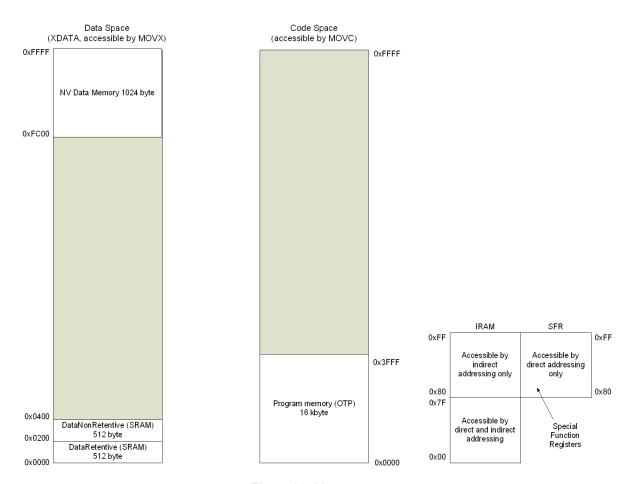

| 5.1      | PDATA memory addressing                                    |     |

| 5.2      | MCU Special Function Registers                             |     |

| 5.2.1    | Accumulator - ACC                                          |     |

| 5.2.2    | B Register – B                                             |     |

| 5.2.3    | Program Status Word Register - PSW                         |     |

| 5.2.4    | Stack Pointer – SP                                         |     |

| 5.2.5    | Data Pointer – DPH, DPL                                    | 65  |

| 5.2.6    | Data Pointer 1 – DPH1, DPL1                                |     |

| 5.2.7    | Data Pointer Select Register – DPS                         |     |

| 5.2.8    | PCON register                                              |     |

| 5.2.9    | Special Function Register Map                              |     |

| 5.2.10   | Special Function Registers reset values                    |     |

| 6 OT     | P memory                                                   |     |

| 6.1      | Features                                                   |     |

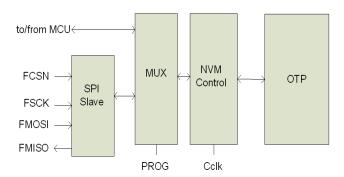

| 6.2      | Block diagram                                              | 71  |

| 6.3     | Functional description                       | 71 |

|---------|----------------------------------------------|----|

| 6.3.1   | Using the NV data memory                     | 72 |

| 6.3.2   | OTP memory configuration                     |    |

| 6.3.2.1 | InfoPage content                             |    |

| 6.3.2.2 | Memory configuration SFR                     |    |

| 6.3.3   | Brown-out                                    |    |

| 6.3.4   | Temperature restriction for OTP programming  | 74 |

| 6.3.5   | OTP programming from the MCU                 |    |

| 6.3.5.1 | MCU operations in the main block             |    |

| 6.3.6   | OTP programming through SPI                  |    |

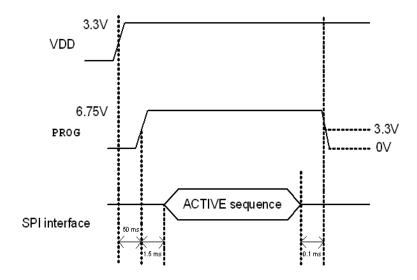

| 6.3.6.1 | PROG pin requirements                        |    |

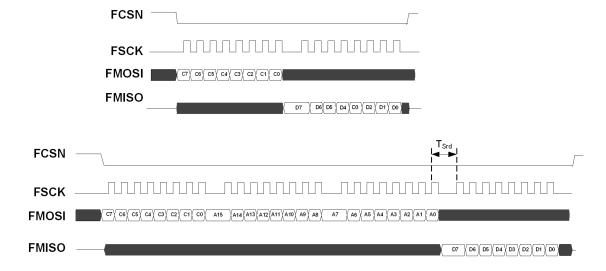

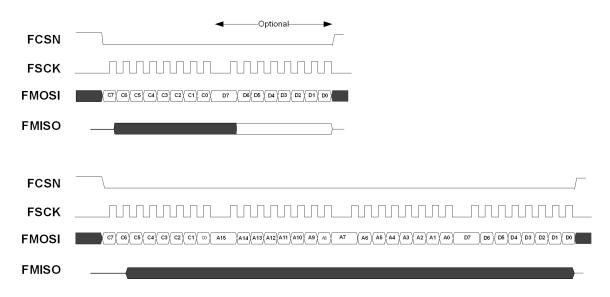

| 6.3.6.2 | SPI slave interface                          |    |

|         | ndom Access memory (RAM)                     |    |

| 7.1     | SRAM configuration                           |    |

|         | ers/counters                                 |    |

| 8.1     | Features                                     |    |

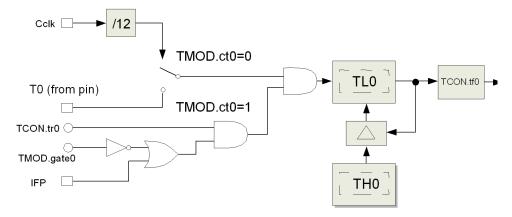

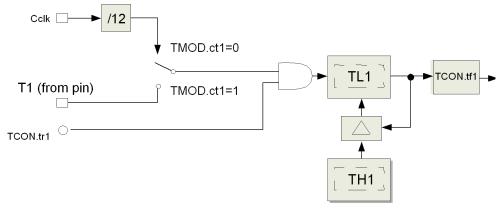

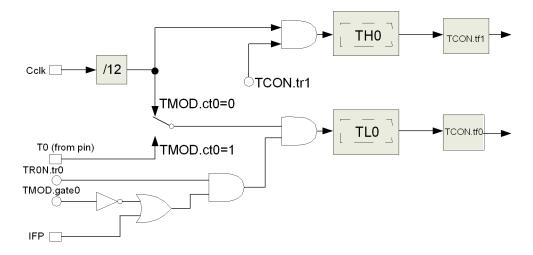

| 8.2     | Block diagram                                |    |

| 8.3     | Functional description                       |    |

| 8.3.1   | Timer 0 and Timer 1                          |    |

| 8.3.1.1 | Mode 0 and Mode 1                            |    |

| 8.3.1.2 | Mode 2                                       |    |

| 8.3.1.3 | Mode 3                                       |    |

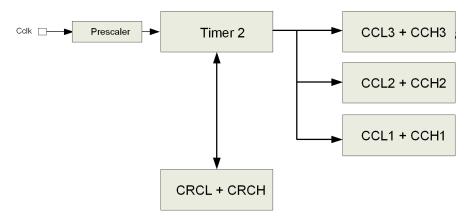

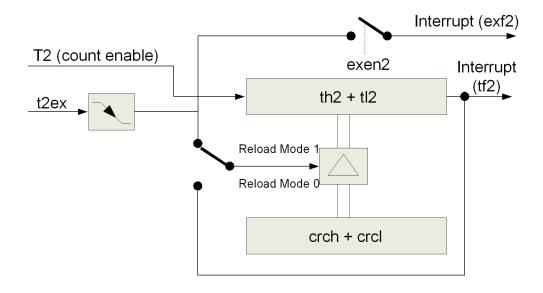

| 8.3.2   | Timer 2                                      |    |

| 8.3.2.1 | Timer 2 description                          |    |

| 8.3.2.2 | Timer mode                                   |    |

| 8.3.2.3 | Event counter mode                           |    |

| 8.3.2.4 | Gated timer mode                             |    |

| 8.3.2.5 | Timer 2 reload                               |    |

| 8.4     | SFR registers                                |    |

| 8.4.1   | Timer/Counter control register – TCON        |    |

| 8.4.2   | Timer mode register - TMOD                   |    |

| 8.4.3   | Timer 0 – TH0, TL0                           |    |

| 8.4.4   | Timer 1 – TH1, TL1                           |    |

| 8.4.5   | Timer 2 control register – T2CON             |    |

| 8.4.6   | Timer 2 – TH2, TL2                           |    |

| 8.4.7   | Compare/Capture enable register – CCEN       |    |

| 8.4.8   | Capture registers – CC1, CC2, CC3            |    |

| 8.4.9   | Compare/Reload/Capture register – CRCH, CRCL |    |

| 8.5     | Real Time Clock - RTC                        |    |

| 8.5.1   | Features                                     |    |

| 8.5.2   | Functional description of SFR registers      |    |

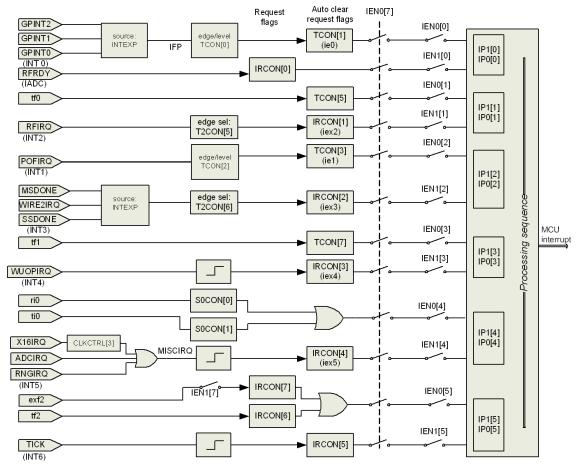

|         | rrupts                                       |    |

| 9.1     | Features                                     |    |

| 9.2     | Block diagram                                |    |

| 9.3     | Functional description                       |    |

| 9.4     | SFR registers                                |    |

|         |                                              |    |

| 9.4.1  | Interrupt Enable 0 Register – IEN0          | 96  |

|--------|---------------------------------------------|-----|

| 9.4.2  | Interrupt Enable 1 Register – IEN1          | 96  |

| 9.4.3  | Interrupt Priority Registers – IP0, IP1     | 96  |

| 9.4.4  | Interrupt Request Control Registers – IRCON |     |

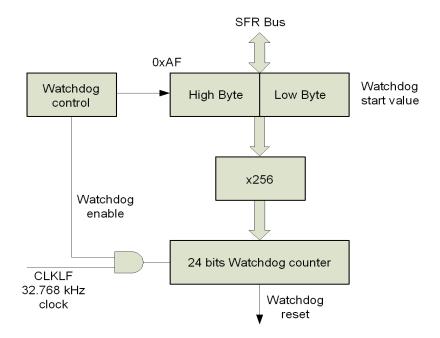

| 10 Wa  | tchdogtchdog                                |     |

| 10.1   | Features                                    |     |

| 10.2   | Block diagram                               | 98  |

| 10.3   | Functional description                      | 98  |

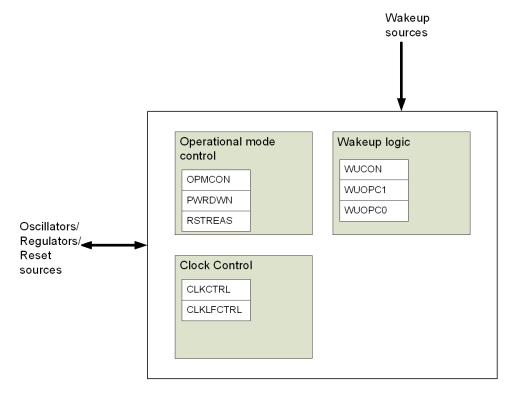

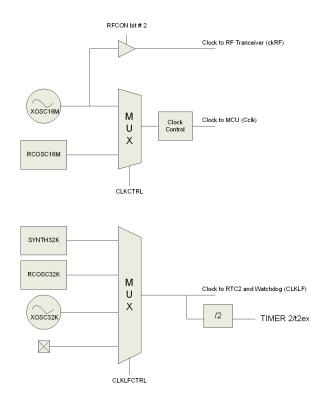

| 11 Pov | wer and clock management                    | 100 |

| 11.1   | Block diagram                               |     |

| 11.2   | Modes of operation                          | 100 |

| 11.3   | Functional description                      | 105 |

| 11.3.1 | Clock control                               | 105 |

| 11.3.2 | Power down control – PWRDWN                 |     |

| 11.3.3 | Operational mode control - OPMCON           | 109 |

| 11.3.4 | Reset result – RSTREAS                      | 109 |

| 11.3.5 | Wakeup configuration register – WUCON       | 110 |

| 11.3.6 | Pin wakeup configuration                    | 110 |

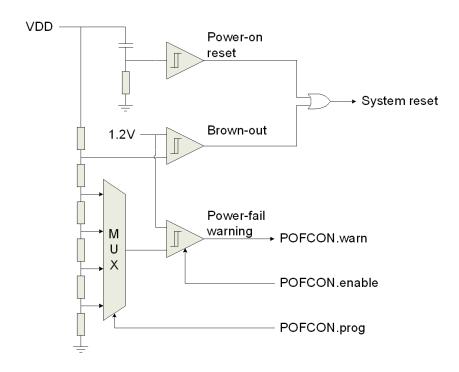

| 12 Pov | wer supply supervisor                       | 112 |

| 12.1   | Features                                    | 112 |

| 12.2   | Block diagram                               | 112 |

| 12.3   | Functional description                      | 112 |

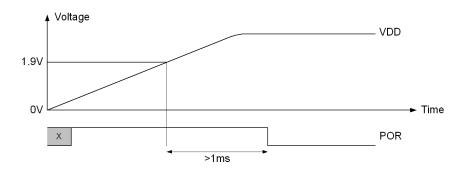

| 12.3.1 | Power-on reset                              | 112 |

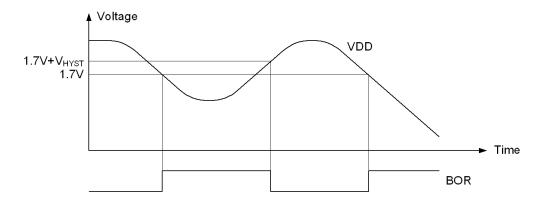

| 12.3.2 | Brown-out reset                             | 113 |

| 12.3.3 | Power-fail comparator                       |     |

| 12.4   | SFR registers                               |     |

|        | -chip oscillators                           |     |

| 13.1   | Features                                    |     |

| 13.2   | Block diagrams                              |     |

| 13.3   | Functional description                      |     |

| 13.3.1 | 16 MHz crystal oscillator                   |     |

| 13.3.2 | 16 MHz RC oscillator                        |     |

| 13.3.3 | External 16 MHz clock                       |     |

| 13.3.4 | 32.768 kHz crystal oscillator               |     |

| 13.3.5 | 32.768 kHz RC oscillator                    |     |

| 13.3.6 | Synthesized 32.768 kHz clock                |     |

| 13.3.7 | External 32.768 kHz clock                   |     |

|        | U Multiply Divide Unit                      |     |

| 14.1   | Features                                    |     |

| 14.2   | Block diagram                               |     |

| 14.3   | Functional description                      |     |

| 14.4   | SFR registers                               |     |

| 14.4.1 | Loading the MDx registers                   |     |

| 14.4.2 | Executing calculation                       |     |

| 14.4.3 | Reading the result from the MDx registers   |     |

| 14.4.4 | Normalizing                                 | 121 |

| 14.4.5   | Shifting                                        | 121 |

|----------|-------------------------------------------------|-----|

| 14.4.6   | The mdef flag                                   | 121 |

| 14.4.7   | The mdov flag                                   | 122 |

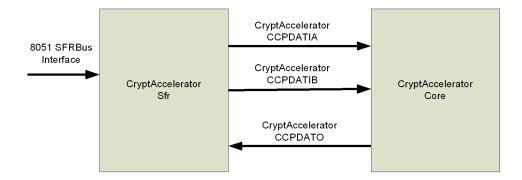

| 15 End   | cryption/decryption accelerator                 | 123 |

| 15.1     | Features                                        | 123 |

| 15.2     | Block diagram                                   | 123 |

| 15.3     | Functional description                          | 123 |

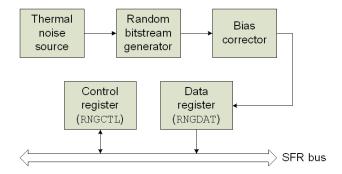

| 16 Rar   | ndom number generator                           | 125 |

| 16.1     | Features                                        | 125 |

| 16.2     | Block diagram                                   | 125 |

| 16.3     | Functional description                          | 125 |

| 16.4     | SFR registers                                   | 126 |

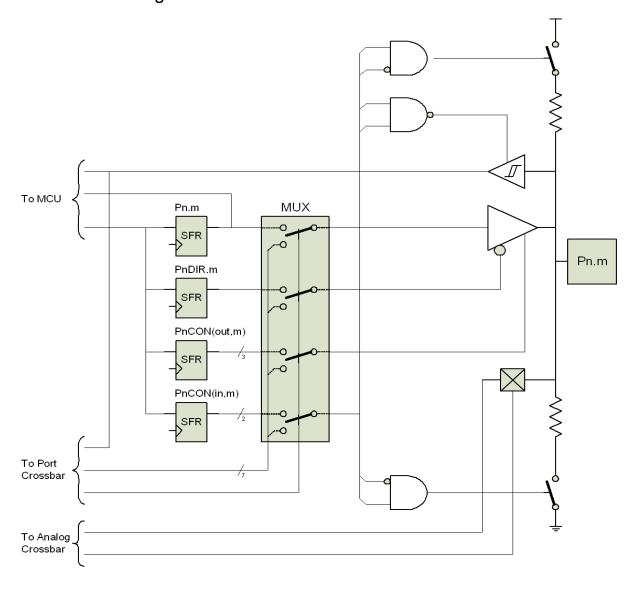

| 17 Ger   | neral purpose IO port and pin assignments       | 127 |

| 17.1     | Block diagram                                   | 127 |

| 17.2     | Functional description                          | 128 |

| 17.2.1   | General purpose IO pin functionality            | 128 |

| 17.2.2   | PortCrossbar functionality                      | 129 |

| 17.2.2.1 | Dynamic allocation of pins                      | 129 |

| 17.2.2.2 | Dynamic pin allocation for digital blocks       | 129 |

| 17.2.2.3 | Dynamic pin allocation for analog blocks        |     |

| 17.2.2.4 | Default pin allocation                          | 129 |

| 17.3     | IO pin maps                                     | 130 |

| 17.3.1   | Pin assignments in package 24 pin 4×4 mm        | 131 |

| 17.3.2   | Pin assignments in package 32 pin 5×5 mm        | 132 |

| 17.3.3   | Pin assignments in package 48 pin 7×7 mm        | 133 |

| 17.3.4   | Programmable registers                          | 135 |

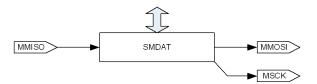

| 18 SPI   | -                                               | 143 |

| 18.1     | Features                                        | 143 |

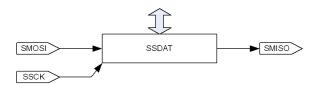

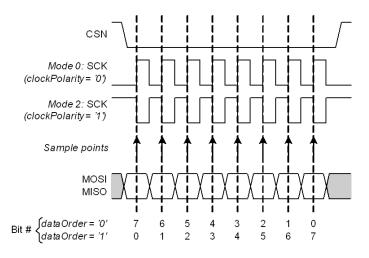

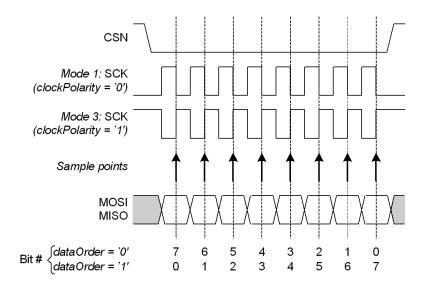

| 18.2     | Block diagram                                   | 143 |

| 18.3     | Functional description                          | 144 |

| 18.3.1   | SPI master                                      | 144 |

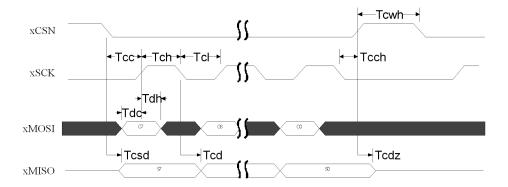

| 18.3.2   | SPI slave                                       | 146 |

| 18.3.3   | Slave SPI timing                                | 147 |

| 19 Ser   | ial port (UART)                                 | 150 |

| 19.1     | Features                                        | 150 |

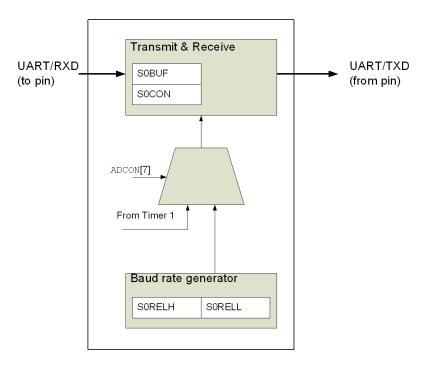

| 19.2     | Block diagram                                   | 150 |

| 19.3     | Functional description                          | 150 |

| 19.3.1   | Serial port 0 control register – S0CON          | 151 |

| 19.3.2   | Serial port 0 data buffer – S0BUF               |     |

| 19.3.3   | Serial port 0 reload register – S0RELH, S0RELL  | 152 |

| 19.3.4   | Serial port 0 baud rate select register - ADCON | 153 |

| 20 2-W   | /ire                                            |     |

| 20.1     | Features                                        | 154 |

| 20.2     | Functional description                          | 154 |

| 20.2.1   | Recommended use                                 | 154 |

| 20.2.2   | Master transmitter/receiver                     | 154 |

| 20.2.2.1 | TX mode                    | 154 |

|----------|----------------------------|-----|

| 20.2.2.2 | RX mode                    | 155 |

| 20.2.3   | Slave transmitter/receiver | 155 |

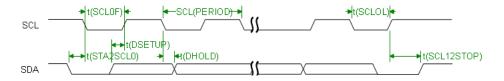

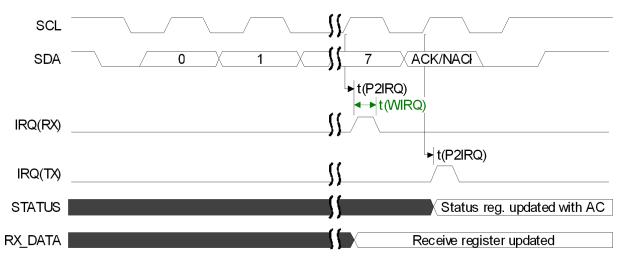

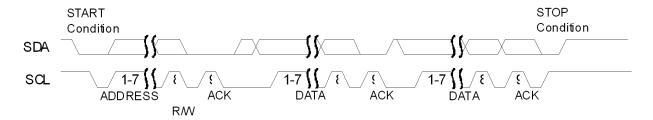

| 20.2.3.1 | 2-Wire timing              | 156 |

| 20.3     | SFR registers              | 157 |

| 21 AD    | )C                         | 160 |

| 21.1     | Features                   | 160 |

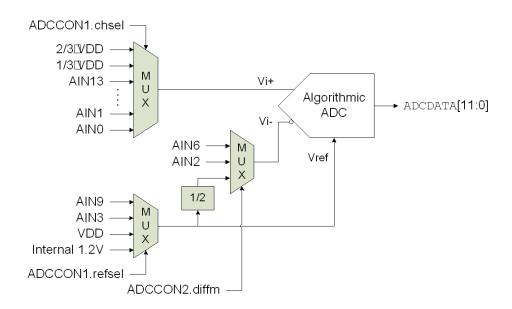

| 21.2     | Block diagram              | 160 |

| 21.3     | Functional description     | 160 |

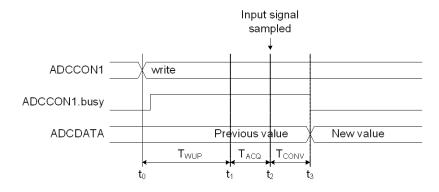

| 21.3.1   | Activation                 | 160 |

| 21.3.2   | Input selection            | 161 |

| 21.3.3   | Reference selection        | 161 |

| 21.3.4   | Resolution                 | 161 |

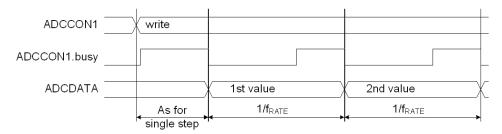

| 21.3.5   | Conversion modes           | 161 |

| 21.3.6   | Output data coding         | 162 |

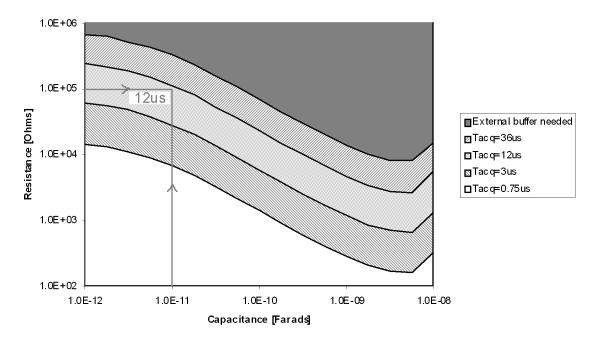

| 21.3.7   | Driving the analog input   | 163 |

| 21.3.8   | SFR registers              | 164 |

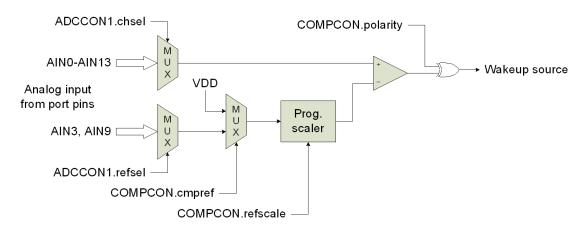

| 22 An    | alog comparator            | 166 |

| 22.1     | Features                   | 166 |

| 22.2     | Block diagram              | 166 |

| 22.3     | Functional description     |     |

| 22.3.1   | Activation                 | 166 |

| 22.3.2   | Input selection            |     |

| 22.3.3   | Reference selection        | 167 |

| 22.3.4   | Output polarity            | 167 |

| 22.3.5   | Input voltage range        |     |

| 22.3.6   | Configuration examples     |     |

| 22.3.7   | Driving the analog input   |     |

| 22.3.8   | SFR registers              | 168 |

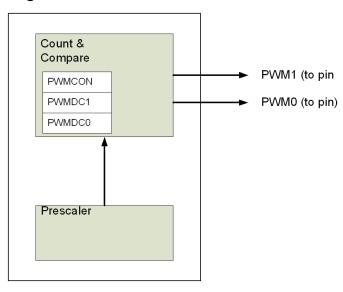

| 23 PV    | VM                         | 169 |

| 23.1     | Features                   | 169 |

| 23.2     | Block diagram              |     |

| 23.3     | Functional description     |     |

|          | solute maximum ratings     |     |

|          | perating condition         |     |

|          | ectrical specifications    |     |

| 26.1     | Power consumption          |     |

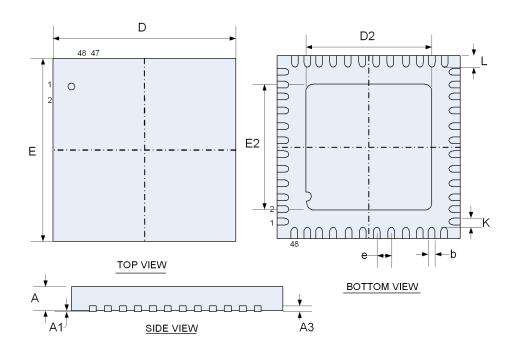

|          | chanical specifications    |     |

|          | ference circuits           |     |

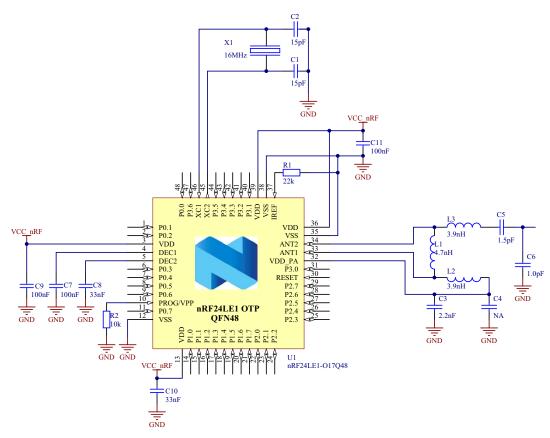

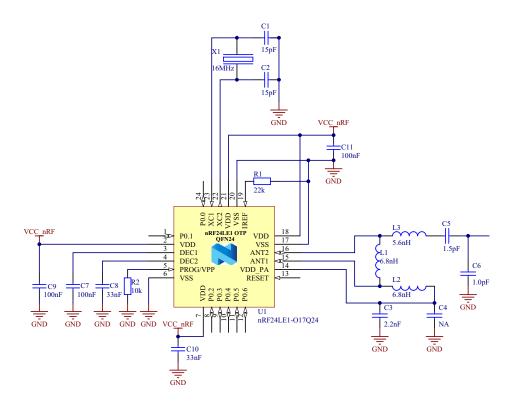

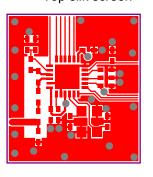

| 28.1     | nRF24LE1 OTP, 7×7 mm QFN48 |     |

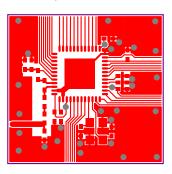

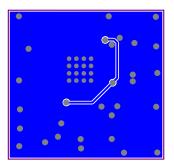

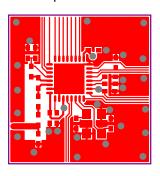

| 28.1.1   | Schematics                 |     |

| 28.1.2   | Layout                     | 183 |

| 28.1.3   | Bill of Materials (BOM)    | 183 |

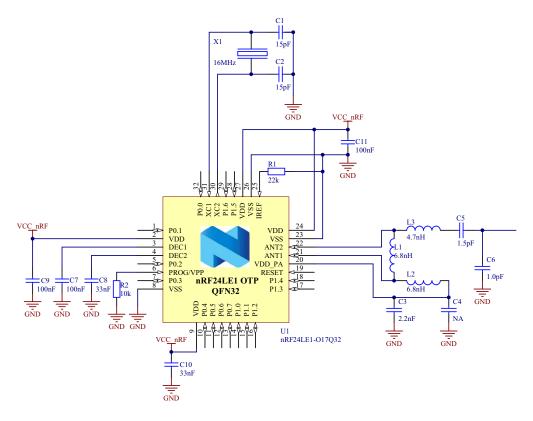

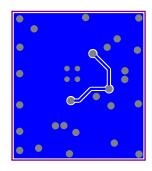

| 28.2     | nRF24LE1 OTP, 5×5 mm QFN32 |     |

| 28.2.1   | Schematics                 |     |

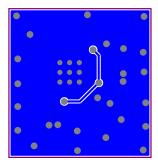

| 28.2.2   | Layout                     | 185 |

| 28.2.3 | Bill Of Materials (BOM)    | 185 |

|--------|----------------------------|-----|

| 28.3   | nRF24LE1 OTP, 4×4 mm QFN24 |     |

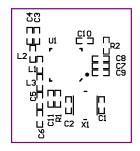

| 28.3.1 | Schematics                 |     |

| 28.3.2 | Layout                     | 187 |

| 28.3.3 | Bill Of Materials (BOM)    | 187 |

| 29 O   | rdering information        |     |

| 29.1   | Package marking            | 188 |

| 29.1.1 | Abbreviations              | 188 |

| 29.2   | Product options            | 188 |

| 29.2.1 | RF silicon                 | 188 |

| 29.2.2 | Development tools          | 189 |

| 30 G   | lossary                    | 190 |

#### 1 Introduction

The nRF24LE1 OTP is a member of the low-cost, high-performance family of intelligent 2.4 GHz RF transceivers with embedded microcontrollers. The nRF24LE1 OTP is optimized to provide a single chip solution for ULP wireless applications. The combination of processing power, memory, low power oscillators, real-time counter, AES encryption accelerator, random generator and a range of power saving modes provides an ideal platform for implementation of RF protocols. Benefits of using nRF24LE1 OTP include tighter protocol timing, security, lower power consumption and improved co-existence performance. For the application layer the nRF24LE1 OTP offers a rich set of peripherals including: SPI, 2-wire, UART, 6 to 12 bit ADC, PWM and an ultra low power analog comparator for voltage level system wake-up.

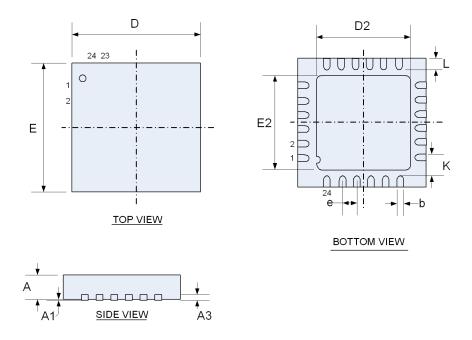

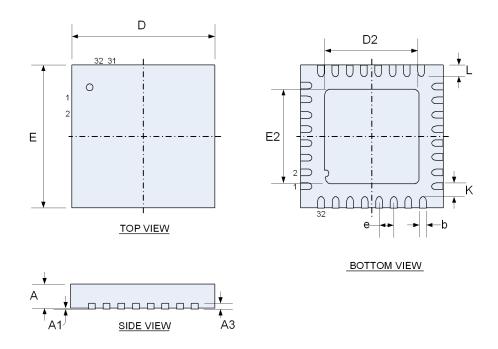

The nRF24LE1 OTP comes in different package variants:

- nRF24LE1: An ultra compact 4×4mm 24 pin QFN (7 generic I/O pins)

- nRF24LE1: A compact 5×5mm 32 pin QFN (15 generic I/O pins)

- nRF24LE1: A 7×7mm 48 pin QFN (31 generic I/O pins)

The 4×4mm 24 pin QFN is ideal for low I/O count applications where small size is key. Examples include wearable sports sensors and watches. The 5×5mm 32 pin QFN is ideal for medium I/O count applications such as wireless mouse, remote controls and toys. The 7×7mm 48 pin QFN is designed for high I/O count products like wireless keyboards.

## 1.1 Prerequisites

In order to fully understand the product specification, a good knowledge of electronic and software engineering is necessary.

## 1.2 Writing conventions

This product specification follows a set of typographic rules to make the document consistent and easy to read. The following writing conventions are used:

- Commands, bit state conditions, and register names are written in Courier New.

- Pin names and pin signal conditions are written in Courier New bold.

- Cross references are <u>underlined and highlighted in blue</u>.

## 2 Product overview

### 2.1 Features

#### Features of the nRF24LE1 OTP include:

- · Fast 8-bit microcontroller:

- ▶ Intel MCS 51 compliant instruction set

- ▶ Reduced instruction cycle time, up to 12 times compared to legacy 8051

- ▶ 32 bit multiplication division unit

- Memory:

- ▶ Program memory: 16 kB of OTP memory with security features

- ▶ Data memory: 1 kB of on-chip RAM memory

- ▶ Non-volatile data memory: 1 kB

- A number of on-chip hardware resources are available through programmable multi purpose input/ output pins (7–31 pins dependent on package variant):

- ▶ GPIO

- ▶ SPI master

- ▶ SPI slave

- ▶ 2-Wire master/ slave

- ▶ Full duplex serial port

- ▶ PWM

- ADC

- ▶ Analog comparator

- External interrupts

- ▶ Timer inputs

- ▶ 32.768 kHz crystal oscillator

- High performance 2.4 GHz RF transceiver

- ▶ True single chip GFSK transceiver

- ▶ Enhanced ShockBurst™ link layer support in HW:

- ▶ Packet assembly/disassembly

- ▶ Address and CRC computation

- ▶ Auto ACK and retransmit

- ▶ On the air data rate 250 kbps, 1 Mbps or 2 Mbps

- ▶ Digital interface (SPI) speed 0-8 Mbps

- ▶ 125 RF channels operation, with 79 (2.402 GHz –2.480 GHz) channels within 2.400–2.4835 GHz

- ▶ Short switching time enable frequency hopping

- ▶ Fully RF compatible with nRF24LXX

- ▶ RF compatible with nRF2401A, nRF2402, nRF24E1, nRF24E2 in 250 kbps and 1 Mbps mode

- A/D converter:

- ▶ 6, 8, 10 or 12 bit resolution

- ▶ 14 input channels

- ▶ Single ended or differential input

- ▶ Full-scale range set by internal reference, external reference or VDD

- ▶ Single step mode with conversion time down to 3 µs

- ▶ Continuous mode with 2, 4, 8 or 16 kbps sampling rate

- ▶ Low current consumption; only 0.1mA at 2 ksps

- Mode for measuring supply voltage

- Analog comparator:

- ▶ Used as wakeup source

- ▶ Low current consumption (0.75µA typical)

- ▶ Differential or single-ended input

- ► Single-ended threshold programmable to 25%, 50%, 75% or 100% of VDD or an arbitrary reference voltage from pin

- ▶ 14-channel input multiplexer

- ▶ Rail-to-rail input voltage range

- ► Programmable output polarity

- Encryption/decryption accelerator

- ▶ Utilize time and power effective AES firmware

- Random number generator:

- ▶ Non-deterministic architecture based on thermal noise

- ▶ No seed value required

- ▶ Non-repeating sequence

- ▶ Corrector algorithm ensures uniform statistical distribution

- ▶ Data rate up to 10 kB per second

- ▶ Operational while the processor is in standby

- System reset and power supply monitoring:

- ▶ On-chip power-on and brown-out reset

- ▶ Watchdog timer reset

- ▶ Reset from pin

- ▶ Power-fail comparator with programmable threshold and interrupt to MCU

- On-chip timers:

- ► Three16-bit timers/counters operating at the system clock (sources from the 16 MHz on-chip oscillators)

- ► One 16-bit timer/counter operating at the low frequency clock (32.768 kHz)

- On-chip oscillators:

- ▶ 16 MHz crystal oscillator XOSC16M

- ▶ 16 MHz RC-oscillator RCOSC16M

- ▶ 32.768 kHz crystal oscillator XOSC32K

- ▶ 32.768 kHz RC-oscillator RCOSC32K

- Power management function:

- ▶ Low power design supporting fully static stop/ standby

- ▶ Programmable MCU clock frequency from 125 kHz to 16 MHz

- ▶ On chip voltage regulators supporting low power mode

- ▶ Watchdog and wakeup functionality running in low power mode

- Complete firmware platform available:

- ▶ Hardware abstraction layer (HAL) Functions

- ▶ Library functions

- ► Gazell Wireless protocol

- ▶ Application examples

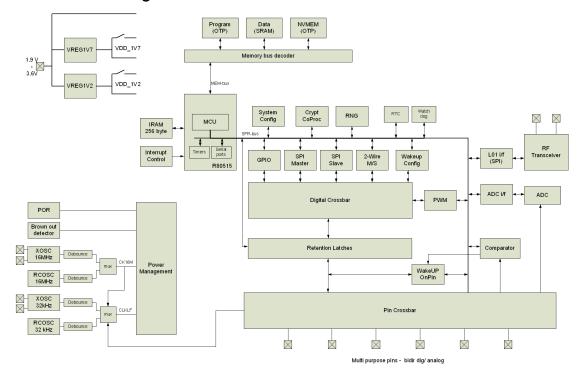

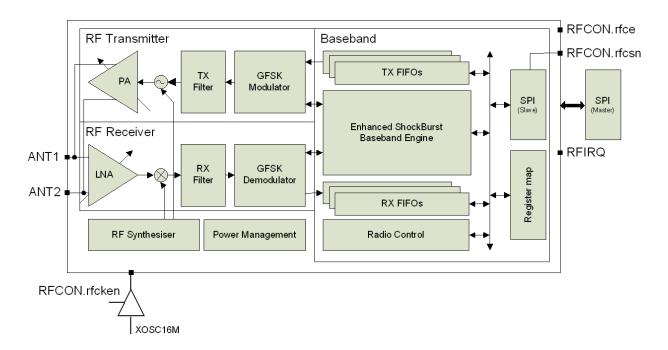

# 2.2 Block diagram

Figure 1. nRF24LE1 OTP block diagram

To find more information on the blocks shown in Figure 1, see <u>Table 1.</u> below:

| Name                          | Reference              |

|-------------------------------|------------------------|

| Memory (Program, Data, NVMEM) | Chapter 5 on page 63   |

| Power management              | Chapter 11 on page 100 |

| RF transceiver                | Chapter 3 on page 17   |

| 2-Wire                        | Chapter 20 on page 154 |

| SPI (Master and Slave)        | Chapter 18 on page 143 |

| GPIO                          | Chapter 17 on page 127 |

| PWM                           | Chapter 23 on page 169 |

| Watchdog                      | Chapter 10 on page 98  |

Table 1. Block diagram cross references

## 2.3 Pin assignments

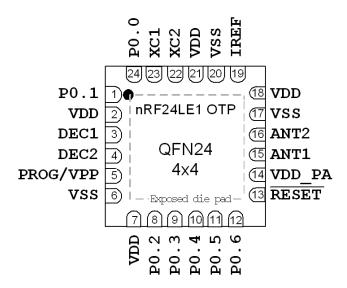

### 2.3.1 24-pin 4×4 QFN-package variant

Figure 2. nRF24LE1 OTP pin assignment (top view) for a QFN24 4×4 mm package

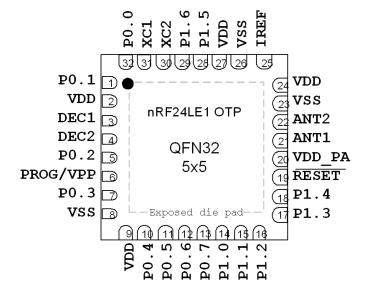

## 2.3.2 32-pin 5×5 QFN-package variant

Figure 3. nRF24LE1 OTP pin assignment (top view) for a QFN32 5×5 mm package

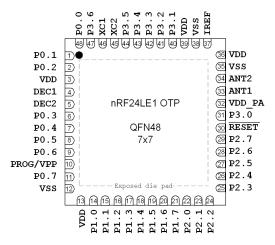

## 2.3.3 48-pin 7×7 QFN-package variant

Figure 4. nRF24LE1 OTP pin assignment (top view) for a QFN48 7×7 mm package

## 2.4 Pin functions

| Name Type Description |                           | Description                                         |  |

|-----------------------|---------------------------|-----------------------------------------------------|--|

| VDD                   | Power                     | Power supply (+1.9V to +3.6V DC)                    |  |

| VSS                   | Power                     | Ground (0V)                                         |  |

| DEC1                  | Power                     | Power supply outputs for de-coupling purposes       |  |

| DEC2                  |                           | (100nF for DEC1, 33nF for DEC2)                     |  |

| P0.0-P3.6             | Digital or analog I/O     | General purpose I/O pins. Number of I/O available   |  |

|                       |                           | depends on package type.                            |  |

| PROG/VPP              | Digital Input, High Volt- | Input to enable OTP programming. This pin           |  |

|                       | age                       | requires an external pull-down resistor, or must be |  |

|                       |                           | connected to ground if external programming is      |  |

|                       |                           | not needed.                                         |  |

| RESET                 | Digital Input             | Reset for microcontroller, active low               |  |

| IREF                  | Analog Input              | Device reference current output. To be connected    |  |

|                       |                           | to reference resistor on PCB.                       |  |

| VDD_PA                | Power Output              | Power supply output (+1.8V) for on-chip RF          |  |

|                       |                           | Power amplifier                                     |  |

| ANT1, ANT2            | RF                        | Differential antenna connection (TX and RX)         |  |

| XC1, XC2              | Analog Input              | Crystal connection for 16 MHz crystal               |  |

| Exposed die           | Power/heat relief         | For the nRF24LE1 OTP QFN48 7×7mm and                |  |

| pad                   |                           | QFN32 5×5mm connect the die pad to GND. For         |  |

|                       |                           | nRF24LE1 OTP QFN24 4×4mm do not connect             |  |

|                       |                           | the die pad to GND.                                 |  |

Table 2. nRF24LE1 OTP pin functions

#### 3 RF transceiver

The nRF24LE1 OTP uses the same 2.4 GHz GFSK RF transceiver with embedded protocol engine (Enhanced ShockBurst™) that is found in the nRF24L01+ single chip RF transceiver. The RF transceiver is designed for operation in the world wide ISM frequency band at 2.400–2.4835 GHz and is very well suited for ultra low power wireless applications.

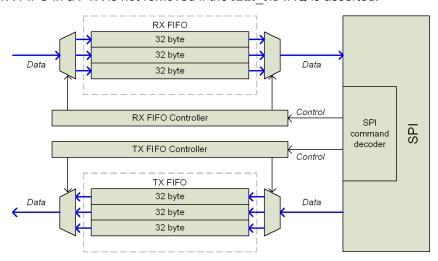

The RF transceiver module is configured and operated through the RF transceiver map. This register map is accessed by the MCU through a dedicated on-chip Serial Peripheral interface (SPI) and is available in all power modes of the RF transceiver module.

The embedded protocol engine (Enhanced ShockBurst™) enables data packet communication and supports various modes from manual operation to advanced autonomous protocol operation. Data FIFOs in the RF transceiver module ensure a smooth data flow between the RF transceiver module and the nRF24LE1 OTP MCU.

The rest of this chapter is written in the context of the RF transceiver module as the core and the rest of the nRF24LE1 OTP as external circuitry to this module.

#### 3.1 Features

Features of the RF transceiver include:

- General

- ▶ Worldwide 2.4 GHz ISM band operation

- ▶ Common antenna interface in transmit and receive

- ▶ GFSK modulation

- ▶ 250 kbps, 1 and 2 Mbps on air data rate

- Transmitter

- ▶ Programmable output power: 0, -6, -12 or -18dBm

- ▶ 11.1mA at 0dBm output power

- Receiver

- ▶ Integrated channel filters

- ▶ 13.3mA at 2 Mbps

- ▶ -82 dBm sensitivity at 2 Mbps

- ▶ -85 dBm sensitivity at 1 Mbps

- ▶ -94 dBm sensitivity at 250 kbps

- RF Synthesizer

- ▶ Fully integrated synthesizer

- ▶ 1 MHz frequency programming resolution

- ► Accepts low cost ±60ppm 16 MHz crystal

- ▶ 1 MHz non-overlapping channel spacing at 1 Mbps

- ▶ 2 MHz non-overlapping channel spacing at 2 Mbps

- Enhanced ShockBurst™

- ▶ 1 to 32 bytes dynamic payload length

- Automatic packet handling (assembly/disassembly)

- ▶ Automatic packet transaction handling (auto ACK, auto retransmit)

- 6 data pipe MultiCeiver™ for 6:1 star networks

## 3.2 Block diagram

Figure 5. RF transceiver block diagram

## 3.3 Functional description

This section describes the different operating modes of the RF transceiver and the parameters used to control it.

The RF transceiver module has a built-in state machine that controls the transitions between the different operating modes. The state machine is controlled by SFR register RFCON and RF transceiver register CONFIG, see section 3.5 for details.

## 3.3.1 Operational Modes

You can configure the RF transceiver to power down, standby, RX and TX mode. This section describes these modes in detail.

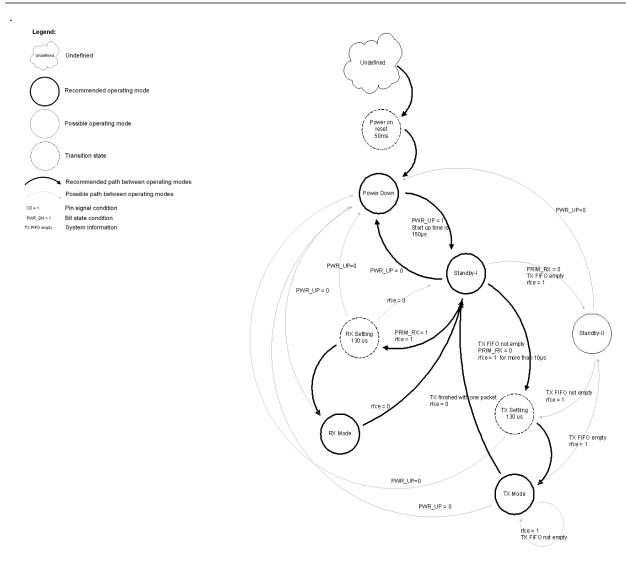

## 3.3.1.1 State diagram

The state diagram (<u>Figure 6.</u>) shows the operating modes of the RF transceiver and how they function. At the end of the reset sequence the RF transceiver enters Power Down mode. When the RF transceiver enters Power Down mode the MCU can still control the module through the SPI and the rfcsn bit in the RFCON register.

There are three types of distinct states highlighted in the state diagram:

- Recommended operating mode: is a recommended state used during normal operation.

- Possible operating mode: is a possible operating state, but is not used during normal operation.

- Transition state: is a time limited state used during start up of the oscillator and settling of the PLL.

Figure 6. Radio control state diagram

#### 3.3.1.2 Power down mode

In power down mode the RF transceiver is disabled with minimal current consumption. All the register values available from the SPI are maintained and the SPI can be activated. For start up times see <u>Table 5.</u> on page 23. Power down mode is entered by setting the PWR UP bit in the CONFIG register low.

#### 3.3.1.3 Standby modes

#### Standby-I mode

By setting the PWR\_UP bit in the CONFIG register to 1, the RF transceiver enters standby-I mode. Standby-I mode is used to minimize average current consumption while maintaining short start up times. Change to the active mode only happens if the rfce bit is enabled and when it is not enabled, the RF transceiver returns to standby-I mode from both the TX and RX modes.

#### Standby-II mode

In standby-II mode extra clock buffers are active and more current is used compared to standby-I mode. The RF transceiver enters standby-II mode if the rfce bit is held high on a PTX operation with an empty TX FIFO. If a new packet is downloaded to the TX FIFO, the PLL immediately starts and the packet is transmitted after the normal PLL settling delay (130  $\mu$ s).

The register values are maintained and the SPI can be activated during both standby modes. For start up times see Table 5. on page 23.

#### 3.3.1.4 RX mode

The RX mode is an active mode where the RF transceiver is used as a receiver. To enter this mode, the RF transceiver must have the PWR UP bit, PRIM RX bit and the rfce bit is set high.

In RX mode the receiver demodulates the signals from the RF channel, constantly presenting the demodulated data to the baseband protocol engine. The baseband protocol engine constantly searches for a valid packet. If a valid packet is found (by a matching address and a valid CRC) the payload of the packet is presented in a vacant slot in the RX FIFOs. If the RX FIFOs are full, the received packet is discarded.

The RF transceiver remains in RX mode until the MCU configures it to standby-I mode or power down mode. However, if the automatic protocol features (Enhanced ShockBurst™) in the baseband protocol engine are enabled, the RF transceiver can enter other modes in order to execute the protocol.

In RX mode a Received Power Detector (RPD) signal is available. The RPD is a signal that is set high when a RF signal higher than -64 dBm is detected inside the receiving frequency channel. The internal RPD signal is filtered before presented to the RPD register. The RF signal must be present for at least 40µs before the RPD is set high. How to use the RPD is described in Section 3.3.4 on page 22.

#### 3.3.1.5 TX mode

The TX mode is an active mode for transmitting packets. To enter this mode, the RF transceiver must have the PWR\_UP bit set high, PRIM\_RX bit set low, a payload in the TX FIFO and a high pulse on the rfce bit for more than 10  $\mu$ s.

The RF transceiver stays in TX mode until it finishes transmitting a packet. If rfce = 0, RF transceiver returns to standby-I mode. If rfce = 1, the status of the TX FIFO determines the next action. If the TX FIFO is not empty the RF transceiver remains in TX mode and transmits the next packet. If the TX FIFO is empty the RF transceiver goes into standby-II mode. The RF transceiver transmitter PLL operates in open loop when in TX mode. It is important never to keep the RF transceiver in TX mode for more than 4 ms at a time. If the Enhanced ShockBurst<sup>TM</sup> features are enabled, RF transceiver is never in TX mode longer than 4 ms.

## 3.3.1.6 Operational modes configuration

The following table (<u>Table 3</u>.) describes how to configure the operational modes.

| Mode       | PWR_UP<br>register | PRIM_RX register | rfce       | FIFO state                           |

|------------|--------------------|------------------|------------|--------------------------------------|

| RX mode    | 1                  | 1                | 1          | -                                    |

| TX mode    | 1                  | 0                | 1          | Data in TX FIFO. Will empty all lev- |

|            |                    |                  |            | els in TX FIFO <sup>a</sup> .        |

| TX mode    | 1                  | 0                |            | Data in TX FIFO.Will empty one       |

|            |                    |                  | high pulse | level in TX FIFO <sup>b</sup> .      |

| Standby-II | 1                  | 0                | 1          | TX FIFO empty                        |

| Standby-I  | 1                  | -                | 0          | No ongoing packet transmission       |

| Power Down | 0                  | -                | -          | -                                    |

- a. If the rfce bit is held high the TX FIFO is emptied and all necessary ACK and possible retransmits are carried out. The transmission continues as long as the TX FIFO is refilled. If the TX FIFO is empty when the rfce bit is still high, the RF transceiver enters standby-II mode. In this mode the transmission of a packet is started as soon as the rfcsn is set high after an upload (UL) of a packet to TX FIFO.

- b. This operating mode pulses the rfce bit high for at least 10 µs. This allows one packet to transmit. This is the normal operating mode. After the packet is transmitted, the RF transceiver enters standby-I mode.

Table 3. RF transceiver main modes

## 3.3.1.7 Timing information

The timing information in this section relates to the transitions between modes and the timing for the rfce bit. The transition from TX mode to RX mode or vice versa is the same as the transition from the standby modes to TX mode or RX mode (130  $\mu$ s), as described in Table 4.

| Name      | RF transceiver                    | Max.              | Min.  | Comments |

|-----------|-----------------------------------|-------------------|-------|----------|

| Tpd2stby  | Power Down → Standby mode         | 1 µs <sup>a</sup> |       |          |

| Tstby2a   | Standby modes → TX/RX mode        | 130 µs            |       |          |

| Thce      | Minimum rfce high                 |                   | 10 µs |          |

| Tpece2csn | Delay from rfce pos. edge to 4 µs |                   |       |          |

|           | rfcsn low                         |                   |       |          |

a. This presupposes that the XO is running. Please refer to CLKLFCTRL for bit 3 in <u>Table 58</u>. on page 107.

Table 4. Operational timing of RF transceiver

**Note:** If **VDD** is turned off, or if the nRF24LE1 OTP enters Deep Sleep or Memory Retention mode, the register values are lost and you must configure the RF transceiver before entering the TX or RX modes.

#### 3.3.2 Air data rate

The air data rate is the modulated signaling rate the RF transceiver uses when transmitting and receiving data. It can be 250 kbps, 1 Mbps or 2 Mbps. Using lower air data rate gives better receiver sensitivity than higher air data rate. But, high air data rate gives lower average current consumption and reduced probability of on-air collisions.

The air data rate is set by the RF\_DR bit in the RF\_SETUP register. A transmitter and a receiver must be programmed with the same air data rate to communicate with each other.

The RF transceiver is fully compatible with nRF24L01. For compatibility with nRF2401A, nRF2402, nRF24E1, and nRF24E2 the air data rate must be set to 250 kbps or 1 Mbps.

### 3.3.3 RF channel frequency

The RF channel frequency determines the center of the channel used by the RF transceiver. The channel occupies a bandwidth of less than 1 MHz at 250 kbps and 1 Mbps and a bandwidth of less than 2 MHz at 2 Mbps. The RF transceiver can operate on frequencies from 2.400 GHz to 2.525 GHz. The programming resolution of the RF channel frequency setting is 1 MHz.

At 2 Mbps the channel occupies a bandwidth wider than the resolution of the RF channel frequency setting. To ensure non-overlapping channels in 2 Mbps mode, the channel spacing must be 2 MHz or more. At 1 Mbps and 250 kbps the channel bandwidth is the same or lower than the resolution of the RF frequency.

The RF channel frequency is set by the RF CH register according to the following formula:

You must program a transmitter and a receiver with the same RF channel frequency to communicate with each other.

#### 3.3.4 Received Power Detector measurements

Received Power Detector (RPD), located in register 09, bit 0, triggers at received power levels above -64 dBm that are present in the RF channel you receive on. If the received power is less than -64 dBm, RDP = 0.

The RPD can be read out at any time while the RF transceiver is in receive mode. This offers a snapshot of the current received power level in the channel. The RPD is latched whenever a packet is received or when the MCU sets rfce low.

The status of RPD is correct when RX mode is enabled and after a wait time of Tstby2a +Tdelay\_AGC=  $130 \, \mu s + 40 \, \mu s$ . The RX gain varies over temperature which means that the RPD threshold also varies over temperature. The RPD threshold value is reduced by - 5dB at T = - $40^{\circ}$ C and increased by + 5dB at  $85^{\circ}$ C.

#### 3.3.5 PA control

The PA (Power Amplifier) control is used to set the output power from the RF transceiver power amplifier. In TX mode PA control has four programmable steps, see Table 5. on page 23

The PA control is set by the RF PWR bits in the RF SETUP register.

| SPI RF-SETUP<br>(RF_PWR) | RF output power | DC current consumption |

|--------------------------|-----------------|------------------------|

| 11                       | 0 dBm           | 11.1mA                 |

| 10                       | -6 dBm          | 8.8mA                  |

| 01                       | -12 dBm         | 7.3mA                  |

| 00                       | -18 dBm         | 6.8mA                  |

Conditions: VDD = 3.0V, VSS = 0V,  $T_A$  = 27°C, Load impedance = 15 $\Omega$ +j88 $\Omega$ .

Table 5. RF output power setting for the RF transceiver

#### 3.3.6 RX/TX control

The RX/TX control is set by PRIM\_RX bit in the CONFIG register and sets the RF transceiver in transmit/receive.

#### 3.4 Enhanced ShockBurst™

Enhanced ShockBurst™ is a packet based data link layer that features automatic packet assembly and timing, automatic acknowledgement and retransmissions of packets. Enhanced ShockBurst™ enables the implementation of ultra low power and high performance communication. The Enhanced ShockBurst™ features enable significant improvements of power efficiency for bi-directional and uni-directional systems, without adding complexity on the host controller side.

#### 3.4.1 Features

The main features of Enhanced ShockBurst™ are:

- 1 to 32 bytes dynamic payload length

- · Automatic packet handling

- Auto packet transaction handling

- ► Auto Acknowledgement

- ▶ Auto retransmit

- 6 data pipe MultiCeiver™ for 1:6 star networks

#### 3.4.2 Enhanced ShockBurst™ overview

Enhanced ShockBurst™ uses ShockBurst™ for automatic packet handling and timing. During transmit, ShockBurst™ assembles the packet and clocks the bits in the data packet for transmission. During receive, ShockBurst™ constantly searches for a valid address in the demodulated signal. When ShockBurst™ finds a valid address, it processes the rest of the packet and validates it by CRC. If the packet is valid the payload is moved into a vacant slot in the RX FIFOs. All high speed bit handling and timing is controlled by ShockBurst™.

Enhanced ShockBurst™ features automatic packet transaction handling for the easy implementation of a reliable bi-directional data link. An Enhanced ShockBurst™ packet transaction is a packet exchange between two transceivers, with one transceiver acting as the Primary Receiver (PRX) and the other transceiver acting as the Primary Transmitter (PTX). An Enhanced ShockBurst™ packet transaction is always initiated by a packet transmission from the PTX, the transaction is complete when the PTX has

received an acknowledgment packet (ACK packet) from the PRX. The PRX can attach user data to the ACK packet enabling a bi-directional data link.

The automatic packet transaction handling works as follows:

- 1. You begin the transaction by transmitting a data packet from the PTX to the PRX. Enhanced ShockBurst™ automatically sets the PTX in receive mode to wait for the ACK packet.

- 2. If the packet is received by the PRX, Enhanced ShockBurst™ automatically assembles and transmits an acknowledgment packet (ACK packet) to the PTX before returning to receive mode.

- 3. If the PTX does not receive the ACK packet immediately, Enhanced ShockBurst™ automatically retransmits the original data packet after a programmable delay and sets the PTX in receive mode to wait for the ACK packet.

In Enhanced ShockBurst™ it is possible to configure parameters such as the maximum number of retransmits and the delay from one transmission to the next retransmission. All automatic handling is done without the involvement of the MCU.

## 3.4.3 Enhanced Shockburst™ packet format

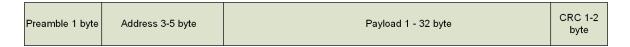

The format of the Enhanced ShockBurst™ packet is described in this section. The Enhanced ShockBurst™ packet contains a preamble field, address field, packet control field, payload field and a CRC field. Figure 7. shows the packet format with MSB to the left.

| Preamb | le 1 byte | Address 3-5 byte | Packet Control Field 9 bit | Payload 0 - 32 byte | CRC 1-2<br>byte |  |

|--------|-----------|------------------|----------------------------|---------------------|-----------------|--|

|--------|-----------|------------------|----------------------------|---------------------|-----------------|--|

Figure 7. An Enhanced ShockBurst™ packet with payload (0-32 bytes)

#### 3.4.3.1 Preamble

The preamble is a bit sequence used to synchronize the receivers demodulator to the incoming bit stream. The preamble is one byte long and is either 01010101 or 10101010. If the first bit in the address is 1 the preamble is automatically set to 10101010 and if the first bit is 0 the preamble is automatically set to 01010101. This is done to ensure there are enough transitions in the preamble to stabilize the receiver.

#### 3.4.3.2 Address

This is the address for the receiver. An address ensures that the correct packet is detected by the receiver. The address field can be configured to be 3, 4 or, 5 bytes long with the **AW** register.

**Note:** Addresses where the level shifts only one time (that is, 000FFFFFFF) can often be detected in noise and can give a false detection, which may give a raised Packet-Error-Rate.

Addresses as a continuation of the preamble (hi-low toggling) raises the Packet-Error-Rate.

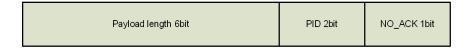

### 3.4.3.3 Packet Control Field (PCF)

<u>Figure 8.</u> shows the format of the 9 bit packet control field, MSB to the left.

Figure 8. Packet control field (PCF)

The packet control field contains a 6 bit payload length field, a 2 bit PID (Packet Identity) field and a 1 bit NO ACK flag.

#### Payload length

This 6 bit field specifies the length of the payload in bytes. The length of the payload can be from 0 to 32 bytes.

Coding: 000000 = 0 byte (only used in empty ACK packets.) 100000 = 32 byte, 100001 = Don't care.

This field is only used if the Dynamic Payload Length function is enabled.

#### PID (Packet identification)

The 2 bit PID field is used to detect if the received packet is new or retransmitted. PID prevents the PRX operation from presenting the same payload more than once to the MCU. The PID field is incremented at the TX side for each new packet received through the SPI. The PID and CRC fields (see <a href="section 3.4.3.5">section 3.4.3.5</a> on <a href="page 26">page 26</a>) are used by the PRX operation to determine if a packet is retransmitted or new. When several data packets are lost on the link, the PID fields may become equal to the last received PID. If a packet has the same PID as the previous packet, the RF transceiver compares the CRC sums from both packets. If the CRC sums are also equal, the last received packet is considered a copy of the previously received packet and discarded.

#### No Acknowledgment flag (NO ACK)

The Selective Auto Acknowledgement feature controls the NO ACK flag.

This flag is only used when the auto acknowledgement feature is used. Setting the flag high, tells the receiver that the packet is not to be auto acknowledged.

#### 3.4.3.4 Payload

The payload is the user defined content of the packet. It can be 0 to 32 bytes wide and is transmitted on-air when it is uploaded (unmodified) to the device.

Enhanced ShockBurst™ provides two alternatives for handling payload lengths; static and dynamic.

The default is static payload length. With static payload length all packets between a transmitter and a receiver have the same length. Static payload length is set by the RX\_PW\_Px registers on the receiver side. The payload length on the transmitter side is set by the number of bytes clocked into the TX\_FIFO and must equal the value in the RX\_PW\_Px register on the receiver side.

Dynamic Payload Length (DPL) is an alternative to static payload length. DPL enables the transmitter to send packets with variable payload length to the receiver. This means that for a system with different payload lengths it is not necessary to scale the packet length to the longest payload.

With the DPL feature the nRF24L01+ can decode the payload length of the received packet automatically instead of using the RX\_PW\_Px registers. The MCU can read the length of the received payload by using the R RX PL WID command.

Note: Always check if the packet width reported is 32 bytes or shorter when using the R\_RX\_PL\_WID command. If its width is longer than 32 bytes then the packet contains errors and must be discarded. Discard the packet by using the Flush RX command.

In order to enable DPL the <code>EN\_DPL</code> bit in the <code>FEATURE</code> register must be enabled. In RX mode the <code>DYNPD</code> register must be set. A PTX that transmits to a PRX with DPL enabled must have the <code>DPL PO bit in DYNPD set.</code>

#### 3.4.3.5 CRC (Cyclic Redundancy Check)

The CRC is the error detection mechanism in the packet. It may either be 1 or 2 bytes and is calculated over the address, Packet Control Field and Payload.

The polynomial for 1 byte CRC is  $X^8 + X^2 + X + 1$ . Initial value 0xFF.

The polynomial for 2 byte CRC is  $X^{16} + X^{12} + X^5 + 1$ . Initial value 0xFFFF.

No packet is accepted by Enhanced ShockBurst™ if the CRC fails.

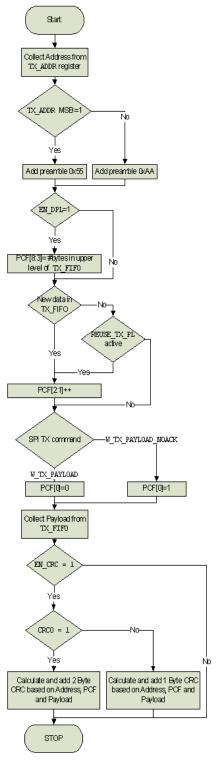

## 3.4.4 Automatic packet assembly

The automatic packet assembly assembles the preamble, address, packet control field, payload and CRC to make a complete packet before it is transmitted.

Figure 9. Automatic packet assembly

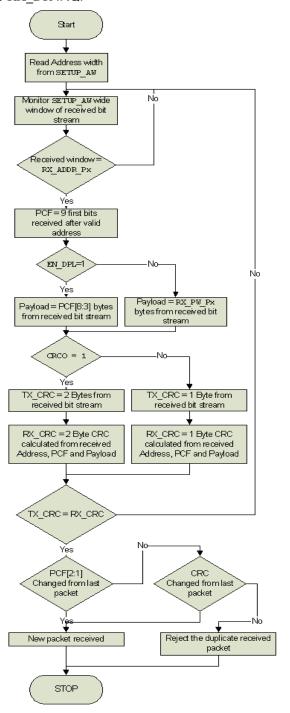

## 3.4.5 Automatic packet disassembly

After the packet is validated, Enhanced ShockBurst<sup>TM</sup> disassembles the packet and loads the payload into the RX FIFO, and asserts the  $\mathbf{RX}$   $\mathbf{DR}$  IRQ.

Figure 10. Automatic packet disassembly

### 3.4.6 Automatic packet transaction handling

Enhanced ShockBurst™ features two functions for automatic packet transaction handling; auto acknowledgement and auto re-transmit.

#### 3.4.6.1 Auto Acknowledgement

Auto Acknowledgment is a function that automatically transmits an ACK packet to the PTX after it has received and validated a packet. The Auto Acknowledgement function reduces the load of the system MCU and reduces average current consumption. The Auto Acknowledgement feature is enabled by setting the EN AA register.

Note: If the received packet has the NO ACK flag set, auto acknowledgement is not executed.

An ACK packet can contain an optional payload from PRX to PTX. In order to use this feature, the Dynamic Payload Length (DPL) feature must be enabled. The MCU on the PRX side has to upload the payload by clocking it into the TX FIFO by using the W\_ACK\_PAYLOAD command. The payload is pending in the TX FIFO (PRX) until a new packet is received from the PTX. The RF transceiver can have three ACK packet payloads pending in the TX FIFO (PRX) at the same time.

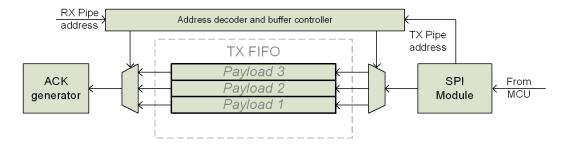

Figure 11. TX FIFO (PRX) with pending payloads

Figure 11. shows how the TX FIFO (PRX) is operated when handling pending ACK packet payloads. From the MCU the payload is clocked in with the  $\[mu]$ \_ACK\_PAYLOAD command. The address decoder and buffer controller ensure that the payload is stored in a vacant slot in the TX FIFO (PRX). When a packet is received, the address decoder and buffer controller are notified with the PTX address. This ensures that the right payload is presented to the ACK generator.

If the TX FIFO (PRX) contains more than one payload to a PTX, payloads are handled using the first in - first out principle. The TX FIFO (PRX) is blocked if all pending payloads are addressed to a PTX where the link is lost. In this case, the MCU can flush the TX FIFO (PRX) by using the FLUSH TX command.

In order to enable Auto Acknowledgement with payload the  ${\tt EN\_ACK\_PAY}$  bit in the FEATURE register must be set.

#### 3.4.6.2 Auto Retransmission (ART)

The Auto Retransmission is a function that retransmits a packet if an ACK packet is not received. It is used in an Auto Acknowledgement system on the PTX. When a packet is not acknowledged, you can set the number of times it is allowed to retransmit by setting the ARC bits in the SETUP\_RETR register. PTX enters RX mode and waits a time period for an ACK packet each time a packet is transmitted. The amount of time the PTX is in RX mode is based on the following conditions:

- Auto Retransmit Delay (ARD) elapsed.

- No address match within 250 µs.

- After received packet (CRC correct or not) if address match within 250 μs.

The RF transceiver asserts the TX DS IRQ when the ACK packet is received.

The RF transceiver enters standby-I mode if there is no more untransmitted data in the TX FIFO and the rfce bit in the RFCON register is low. If the ACK packet is not received, the RF transceiver goes back to TX mode after a delay defined by ARD and retransmits the data. This continues until acknowledgment is received, or the maximum number of retransmits is reached.

Two packet loss counters are incremented each time a packet is lost, ARC\_CNT and PLOS\_CNT in the <code>OBSERVE\_TX</code> register. The ARC\_CNT counts the number of retransmissions for the current transaction. You reset ARC\_CNT by initiating a new transaction. The PLOS\_CNT counts the total number of retransmissions since the last channel change. You reset <code>PLOS\_CNT</code> by writing to the <code>RF\_CH</code> register. It is possible to use the information in the <code>OBSERVE\_TX</code> register to make an overall assessment of the channel quality.

The ARD defines the time from the end of a transmitted packet to when a retransmit starts on the PTX. ARD is set in **SETUP\_RETR** register in steps of 250 µs. A retransmit is made if no ACK packet is received by the PTX.

There is a restriction on the length of ARD when using ACK packets with payload. The ARD time must never be shorter than the sum of the startup time and the time on-air for the ACK packet.

- For 2 Mbps data rate and 5-byte address; 15 byte is maximum ACK packet payload length for ARD=250 µs (reset value).

- For 1 Mbps data rate and 5-byte address; 5 byte is maximum ACK packet payload length for ARD=250 µs (reset value).

ARD=500 µs is long enough for any ACK payload length in 1 or 2 Mbps mode.

• For 250kbps data rate and 5-byte address the following values apply:

| ARD    | ACK packet size (in bytes) |

|--------|----------------------------|

| 1500µs | All ACK payload sizes      |

| 1250µs | <u>≤</u> 24                |

| 1000µs | <u>&lt; 16</u>             |

| 750µs  | <u>&lt;</u> 8              |

| 500µs  | Empty ACK with no payload  |

Table 6. Maximum ACK payload length for different retransmit delays at 250 kbps

As an alternative to Auto Retransmit it is possible to manually set the RF transceiver to retransmit a packet a number of times. This is done by the REUSE\_TX\_PL command. The MCU must initiate each transmission of the packet with a pulse on the CE pin when this command is used.

### 3.4.7 Enhanced ShockBurst™ flowcharts

This section contains flowcharts outlining PTX and PRX operation in Enhanced ShockBurst™.

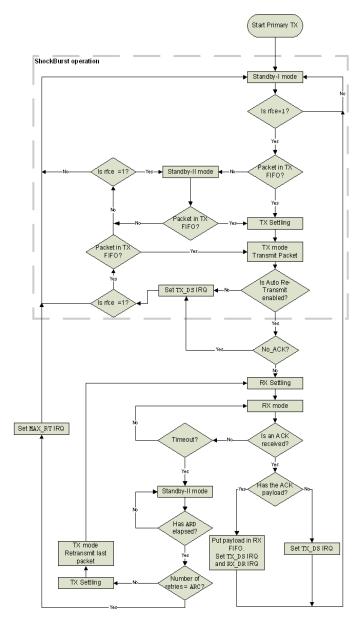

### 3.4.7.1 PTX operation

The flowchart in <u>Figure 12.</u> outlines how a RF transceiver configured as a PTX behaves after entering standby-I mode.

**Note:** ShockBurst<sup>™</sup> operation is outlined with a dashed square.

Figure 12. PTX operations in Enhanced ShockBurst™

Activate PTX mode by setting the rfce bit in the RFCON register high. If there is a packet present in the TX FIFO the RF transceiver enters TX mode and transmits the packet. If Auto Retransmit is enabled, the state machine checks if the NO\_ACK flag is set. If it is not set, the RF transceiver enters RX mode to receive an ACK packet. If the received ACK packet is empty, only the TX\_DS IRQ is asserted. If the ACK packet contains a payload, both TX\_DS IRQ and RX\_DR IRQ are asserted simultaneously before the RF transceiver returns to standby-I mode.

If the ACK packet is not received before timeout occurs, the RF transceiver returns to standby-II mode. It stays in standby-II mode until the ARD has elapsed. If the number of retransmits has not reached the ARC, the RF transceiver enters TX mode and transmits the last packet once more.

While executing the Auto Retransmit feature, the number of retransmits can reach the maximum number defined in ARC. If this happens, the RF transceiver asserts the MAX RT IRQ and returns to standby-I mode.

If the rfce bit in the RFCON register is high and the TX FIFO is empty, the RF transceiver enters Standby-II mode.

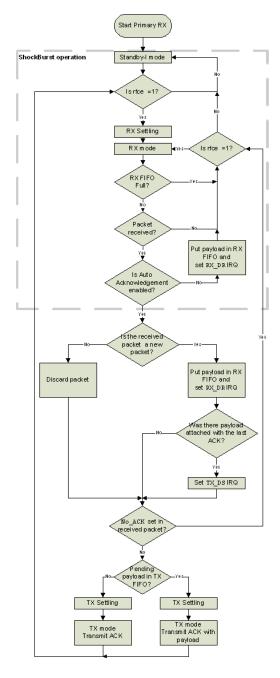

## 3.4.7.2 PRX operation

The flowchart in <u>Figure 13.</u> outlines how a RF transceiver configured as a PRX behaves after entering standby-I mode.

**Note:** ShockBurst™ operation is outlined with a dashed square.

Figure 13. PRX operations in Enhanced ShockBurst™

Activate PRX mode by setting the rfce bit in the RFCON register high. The RF transceiver enters RX mode and starts searching for packets. If a packet is received and Auto Acknowledgement is enabled, the RF transceiver decides if the packet is new or a copy of a previously received packet. If the packet is new the

payload is made available in the RX FIFO and the  $RX\_DR$  IRQ is asserted. If the last received packet from the transmitter is acknowledged with an ACK packet with payload, the  $TX\_DS$  IRQ indicates that the PTX received the ACK packet with payload. If the  $No\_ACK$  flag is not set in the received packet, the PRX enters TX mode. If there is a pending payload in the TX FIFO it is attached to the ACK packet. After the ACK packet is transmitted, the RF transceiver returns to RX mode.

A copy of a previously received packet might be received if the ACK packet is lost. In this case, the PRX discards the received packet and transmits an ACK packet before it returns to RX mode.

#### 3.4.8 MultiCeiver™

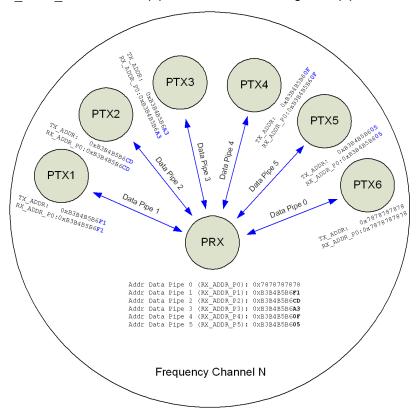

MultiCeiver™ is a feature used in RX mode that contains a set of six parallel data pipes with unique addresses. A data pipe is a logical channel in the physical RF channel. Each data pipe has its own physical address (data pipe address) decoding in the RF transceiver.

Figure 14. PRX using MultiCeiver™

The RF transceiver configured as PRX (primary receiver) can receive data addressed to six different data pipes in one frequency channel as shown in <u>Figure 14</u>. Each data pipe has its own unique address and can be configured for individual behavior.

Up to six RF transceivers configured as PTX can communicate with one RF transceiver configured as PRX. All data pipe addresses are searched for simultaneously. Only one data pipe can receive a packet at a time. All data pipes can perform Enhanced ShockBurst™ functionality.

The following settings are common to all data pipes:

- CRC enabled/disabled (CRC always enabled when Enhanced ShockBurst™ is enabled)

- CRC encoding scheme

- RX address width

- Frequency channel

- Air data rate

- LNA gain

The data pipes are enabled with the bits in the EN\_RXADDR register. By default only data pipe 0 and 1 are enabled. Each data pipe address is configured in the RX\_ADDR\_PX registers.

**Note:** Always ensure that none of the data pipes have the same address.

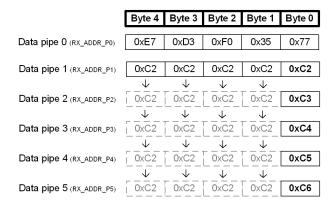

Each pipe can have up to a 5 byte configurable address. Data pipe 0 has a unique 5 byte address. Data pipes 1–5 share the four most significant address bytes. The LSByte must be unique for all six pipes. Figure 15. is an example of how data pipes 0-5 are addressed.

Figure 15. Addressing data pipes 0-5

The PRX, using MultiCeiver™ and Enhanced ShockBurst™, receives packets from more than one PTX. To ensure that the ACK packet from the PRX is transmitted to the correct PTX, the PRX takes the data pipe address where it received the packet and uses it as the TX address when transmitting the ACK packet. Figure 16. on page 36 is an example of an address configuration for the PRX and PTX. On the

PRX the RX\_ADDR\_Pn, defined as the pipe address, must be unique. On the PTX the TX\_ADDR must be the same as the RX\_ADDR\_PO and as the pipe address for the designated pipe.

Figure 16. Example of data pipe addressing in MultiCeiver™

Only when a data pipe receives a complete packet can other data pipes begin to receive data. When multiple PTXs are transmitting to a PRX, the ARD can be used to skew the auto retransmission so that they only block each other once.

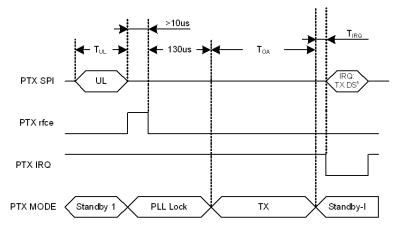

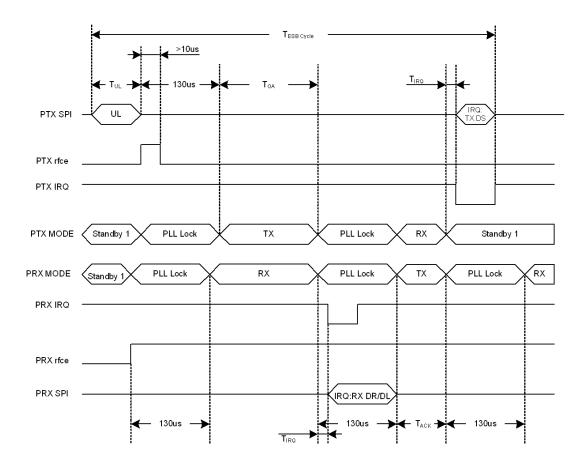

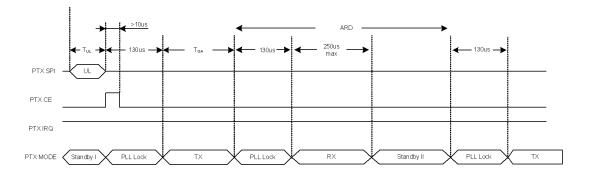

#### 3.4.9 Enhanced ShockBurst™ timing

This section describes the timing sequence of Enhanced ShockBurst™ and how all modes are initiated and operated. The Enhanced ShockBurst™ timing is controlled through the Data and Control interface. The RF transceiver can be set to static modes or autonomous modes where the internal state machine

controls the events. Each autonomous mode/sequence ends with a RFIRQ interrupt. All the interrupts are indicated as IRQ events in the timing diagrams.

1 IRQ if No Ack is on.

$T_{IRQ}$  = 8.2 $\mu$ s @ 1Mbps,  $T_{IRQ}$  = 6.0 $\mu$ s @ 2Mbps

Figure 17. Transmitting one packet with NO\_ACK on

The following equations calculate various timing measurements:

| Symbol           | Description                          | Equation                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>OA</sub>  | Time on-air                          |                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                  |                                      | $T_{OA} = \frac{packet  length}{air  data  rate} = \frac{8 \left[ \frac{bit}{byte} \right] \cdot \left( \frac{1[byte]}{preamble} + 3.4  or  5[bytes] + N[bytes] + N[bytes] + 1  or  2[bytes] \right) + 9[bit]}{air  data  rate} \left[ \frac{bit}{s} \right]}$                                                                                                                                                                        |

| T <sub>ACK</sub> | Time on-air Ack                      |                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                  |                                      | $T_{ACK} = \frac{packet  length}{air  data  rate} = \frac{8 \begin{bmatrix} bit/byte \end{bmatrix} \cdot \left(1 \begin{bmatrix} byte \end{bmatrix} + 3.4  or  5 \begin{bmatrix} bytes \end{bmatrix} + N \begin{bmatrix} bytes \end{bmatrix} + N \begin{bmatrix} bytes \end{bmatrix} + 1  or  2 \begin{bmatrix} bytes \end{bmatrix} + 9 \begin{bmatrix} bit \end{bmatrix}}{air  data  rate} + 9 \begin{bmatrix} bit/s \end{bmatrix}}$ |

| $T_{UL}$         | Time Upload                          |                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                  |                                      | $T_{UL} = \frac{payload\ length}{SPI\ data\ rate} = \frac{8 \left[\frac{bit}{byte}\right] \cdot N \left[\frac{bytes}{payload}\right]}{SPI\ data\ rate} \left[\frac{bit}{s}\right]$                                                                                                                                                                                                                                                    |

| T <sub>ESB</sub> | Time Enhanced Shock-<br>Burst™ cycle | $T_{ESB} = T_{UL} + 2 \cdot T_{stby2a} + T_{OA} + T_{ACK} + T_{IRQ}$                                                                                                                                                                                                                                                                                                                                                                  |

Table 7. Timing equations

Figure 18. Timing of Enhanced ShockBurst™ for one packet upload (2 Mbps)

In <u>Figure 18</u>. the transmission and acknowledgement of a packet is shown. The PRX operation activates RX mode (rfce=1), and the PTX operation is activated in TX mode (rfce=1 for minimum 10  $\mu$ s). After 130  $\mu$ s the transmission starts and finishes after the elapse of  $T_{OA}$ .

When the transmission ends the PTX operation automatically switches to RX mode to wait for the ACK packet from the PRX operation. When the PRX operation receives the packet it sets the interrupt for the host MCU and switches to TX mode to send an ACK. After the PTX operation receives the ACK packet it sets the interrupt to the MCU and clears the packet from the TX FIFO.

In <u>Figure 19</u>. the PTX timing of a packet transmission is shown when the first ACK packet is lost. To see the complete transmission when the ACK packet fails see <u>Figure 22</u>. on page 41.

Figure 19. Timing of Enhanced ShockBurst™ when the first ACK packet is lost (2 Mbps)

### 3.4.10 Enhanced ShockBurst™ transaction diagram

This section describes several scenarios for the Enhanced ShockBurst™ automatic transaction handling. The call outs in this section's figures indicate the IRQs and other events. For MCU activity the event may be placed at a different timeframe.

**Note:** The figures in this section indicate the earliest possible download (DL) of the packet to the MCU and the latest possible upload (UL) of payload to the transmitter.

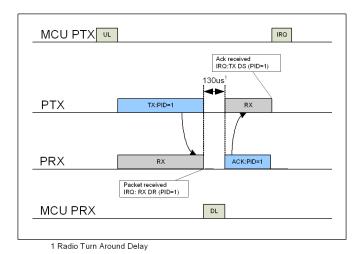

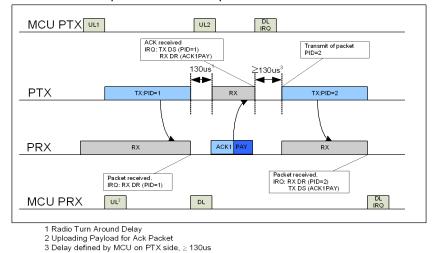

#### 3.4.10.1 Single transaction with ACK packet and interrupts

In <u>Figure 20.</u> the basic auto acknowledgement is shown. After the packet is transmitted by the PTX and received by the PRX the ACK packet is transmitted from the PRX to the PTX. The  $RX\_DR$  IRQ is asserted after the packet is received by the PRX, whereas the  $TX\_DS$  IRQ is asserted when the packet is acknowledged and the ACK packet is received by the PTX.

Figure 20. TX/RX cycles with ACK and the according interrupts

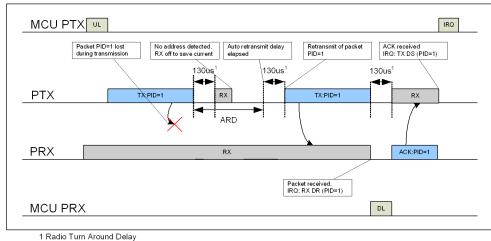

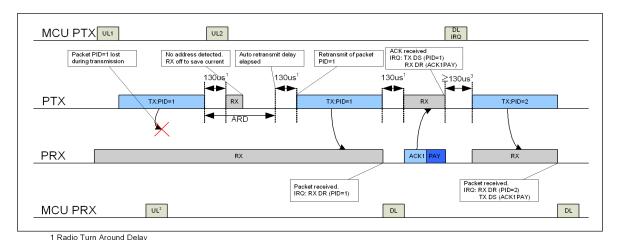

### 3.4.10.2 Single transaction with a lost packet

<u>Figure 21.</u> is a scenario where a retransmission is needed due to loss of the first packet transmit. After the packet is transmitted, the PTX enters RX mode to receive the ACK packet. After the first transmission, the PTX waits a specified time for the ACK packet, if it is not in the specific time slot the PTX retransmits the packet as shown in <u>Figure 21.</u>

Figure 21. TX/RX cycles with ACK and the according interrupts when the first packet transmit fails

When an address is detected the PTX stays in RX mode until the packet is received. When the retransmitted packet is received by the PRX (see <a href="Figure 21">Figure 21</a>.), the <a href="RX\_DR\_IRQ">RX\_DR\_IRQ</a> is asserted and an ACK is transmitted back to the PTX. When the ACK is received by the PTX, the <a href="TX\_DR\_IRQ">TX\_DR\_IRQ</a> is asserted.

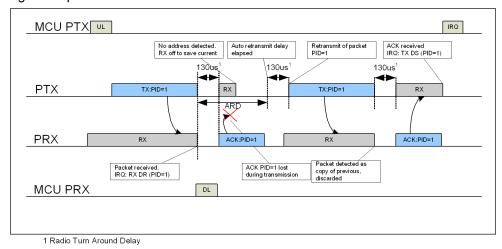

#### 3.4.10.3 Single transaction with a lost ACK packet

<u>Figure 22.</u> is a scenario where a retransmission is needed after a loss of the ACK packet. The corresponding interrupts are also indicated.

Figure 22. TX/RX cycles with ACK and the according interrupts when the ACK packet fails

### 3.4.10.4 Single transaction with ACK payload packet

Figure 23. is a scenario of the basic auto acknowledgement with payload. After the packet is transmitted by the PTX and received by the PRX the ACK packet with payload is transmitted from the PRX to the PTX. The RX\_DR IRQ is asserted after the packet is received by the PRX, whereas on the PTX side the  $TX_DS$  IRQ is asserted when the ACK packet is received by the PTX. On the PRX side, the  $TX_DS$  IRQ for the ACK packet payload is asserted after a new packet from PTX is received. The position of the IRQ in Figure 23. shows where the MCU can respond to the interrupt.

Figure 23. TX/RX cycles with ACK Payload and the according interrupts

#### 3.4.10.5 Single transaction with ACK payload packet and lost packet

<u>Figure 24.</u> is a scenario where the first packet is lost and a retransmission is needed before the RX\_DR IRQ on the PRX side is asserted. For the PTX both the  $TX_DS$  and  $RX_DR$  IRQ are asserted after the ACK packet is received. After the second packet (PID=2) is received on the PRX side both the  $RX_DR$  (PID=2) and  $TX_DS$  (ACK packet payload) IRQ are asserted.

- 2 Uploading Paylod for Ack Packet

- 3 Delay defined by MCU on PTX side, ≥ 130us

Figure 24. TX/RX cycles and the according interrupts when the packet transmission fails

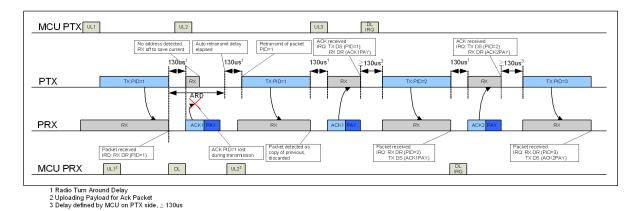

### 3.4.10.6 Two transactions with ACK payload packet and the first ACK packet lost

Figure 25. TX/RX cycles with ACK Payload and the according interrupts when the ACK packet fails

In Figure 25. the ACK packet is lost and a retransmission is needed before the  $TX_DS$  IRQ is asserted, but the  $RX_DR$  IRQ is asserted immediately. The retransmission of the packet (PID=1) results in a discarded packet. For the PTX both the  $TX_DS$  and  $RX_DR$  IRQ are asserted after the second transmission of ACK, which is received. After the second packet (PID=2) is received on the PRX both the  $RX_DR$  (PID=2) and  $TX_DS$  (ACK1PAY) IRQ is asserted. The callouts explains the different events and interrupts.

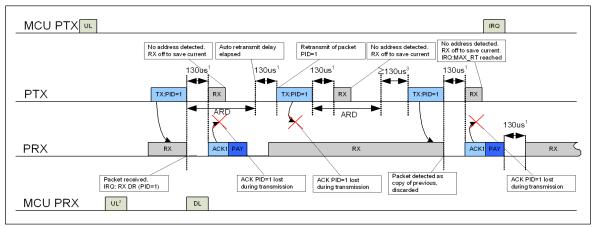

#### 3.4.10.7 Two transactions where max retransmissions is reached

- 1 Radio Turn Around Delay 2 Uploading Paylod for Ack Packet

- 3 Delay defined by MCU on PTX side, ≥ 130us

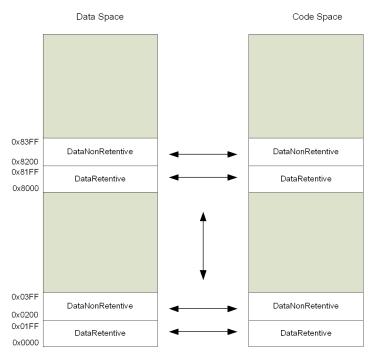

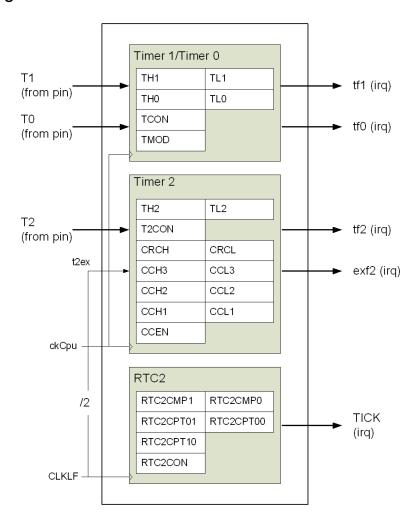

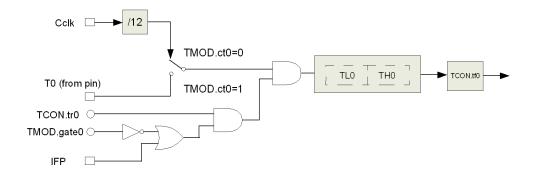

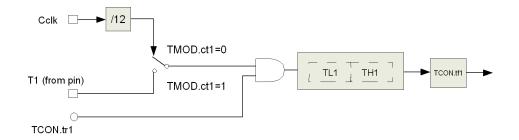

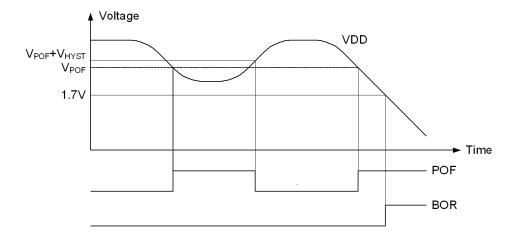

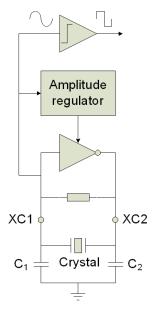

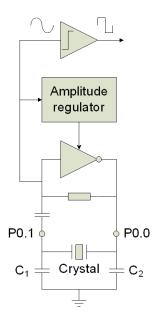

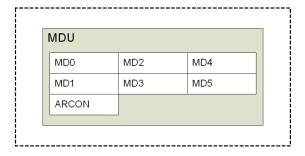

Figure 26. TX/RX cycles with ACK Payload and the according interrupts when the transmission fails. ARC is set to 2.