### CONTENTS

| 1 | FEATURES     |

|---|--------------|

| 2 | APPLICATIONS |

3 GENERAL DESCRIPTION

4 QUICK REFERENCE DATA

- 5 ORDERING INFORMATION

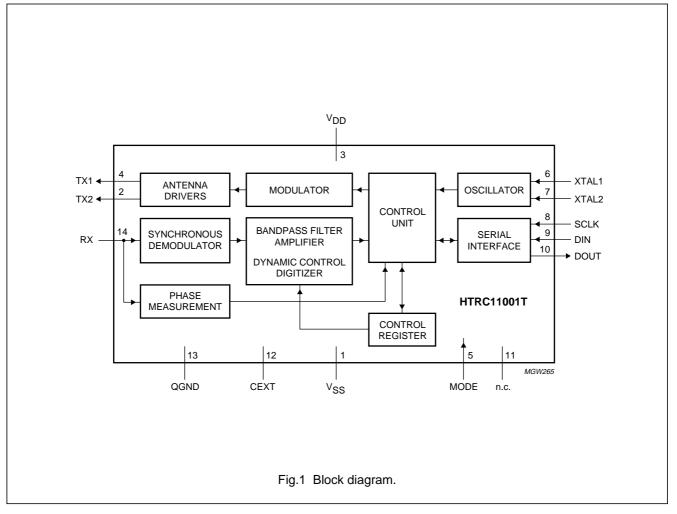

- 6 BLOCK DIAGRAM

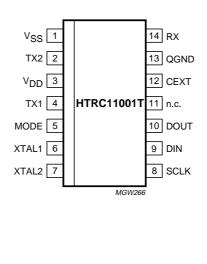

- 7 PINNING

- 8 FUNCTIONAL DESCRIPTION

- 8.1 Power supply

- 8.2 Antenna drivers

- 8.3 Diagnosis

- 8.4 Oscillator with programmable divider

- 8.5 Adaptive sampling time demodulator

- 8.6 Idle and Power-down mode

- 8.7 Serial interface

- 8.7.1 Communication protocol8.7.2 Glitch filter

- 8.8 Commands

- 8.8.1 Command READ\_TAG

- 8.8.2 Command WRITE\_TAG\_N

- 8.8.3 Command WRITE\_TAG

- 8.8.4 Command READ PHASE

- 8.8.5 Command SET\_SAMPLING\_TIME

- 8.8.6 Command GET\_SAMPLING\_TIME

- 8.8.7 Command SET\_CONFIG\_PAGE

- 8.8.8 Command GET\_CONFIG\_PAGE

- 9 LIMITING VALUES

- 10 DC CHARACTERISTICS

- 11 AC CHARACTERISTICS

- 12 APPLICATION INFORMATION

## HTRC11001T

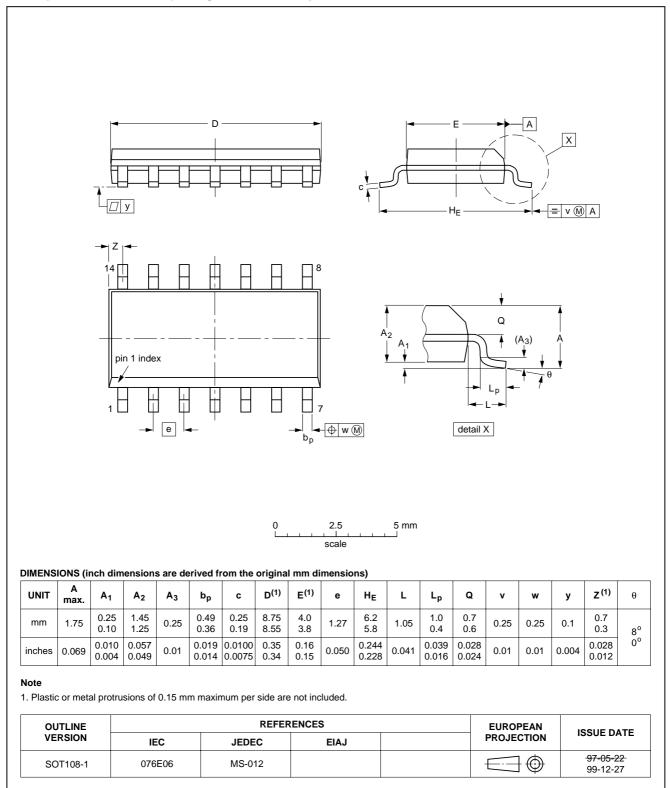

PACKAGE OUTLINE 13 SOLDERING 14 14.1 Introduction to soldering surface mount packages 14.2 Reflow soldering 14.3 Wave soldering 14.4 Manual soldering 14.5 Suitability of surface mount IC packages for wave and reflow soldering methods 15 DATA SHEET STATUS DEFINITIONS 16 17 DISCLAIMERS

### HTRC11001T

### **1 FEATURES**

- Combines all analog RFID reader hardware in one single chip

- · Optimized for HITAG transponder family

- · Robust antenna coil power driver stage with modulator

- High performance adaptive sampling time AM/PM demodulator (patent pending)

- Read and write function

- On-chip clock oscillator

- Antenna rupture and short circuit detection

- Low power consumption

- Very low power standby mode

- Low external component count

- Small package SO14.

### 2 APPLICATIONS

• RFID systems.

### **3 GENERAL DESCRIPTION**

HITAG<sup>(1)</sup> is the family name of the reader chip HTRC11001T to use with transponders which are based on the HITAG tag ICs (HT1ICS3002x or HT2ICS2002x).

(1) HITAG - is a trademark of Philips Semiconductors Gratkorn GmbH.

### 4 QUICK REFERENCE DATA

The receiver parameters (gain factors and filter cut-off frequencies) can be optimized to system and transponder requirements. The HTRC11001T is designed for easy integration into RF identification readers.

State-of-the-art technology allows almost complete integration of the necessary building blocks. A powerful antenna demodulator and driver, together with a low-noise adaptive sampling time demodulator, a programmable filter, amplifier and digitizer, build the complete transceiver unit, required to design high-performance readers.

A three-pin microcontroller interface is employed for programming the HTRC11001T as well as for the bidirectional communication with the transponders. The three-wire interface can be changed into a two-wire interface by connecting the data input and the data output.

Tolerance dependent zero amplitude modulation will cause severe problems in envelope detector systems, resulting in the need of very low tolerance reader antennas. These problems are solved by the new Adaptive Sampling Time (AST) technique.

| SYMBOL              | PARAMETER                                  | CONDITIONS   | MIN. | TYP. | MAX. | UNIT |

|---------------------|--------------------------------------------|--------------|------|------|------|------|

| V <sub>DD</sub>     | supply voltage                             |              | 4.5  | 5.0  | 5.5  | V    |

| f <sub>clk</sub>    | clock frequency                            | programmable | 4    | _    | 16   | MHz  |

| f <sub>res</sub>    | antenna resonant frequency                 |              | -    | 125  | _    | kHz  |

| I <sub>ant(p)</sub> | antenna driver output current (peak value) | continuous   | -    | _    | 200  | mA   |

| T <sub>amb</sub>    | ambient temperature                        |              | -40  | -    | +85  | °C   |

#### 5 ORDERING INFORMATION

| TYPE NUMBER |      | PACKAGE                                                   |          |  |  |  |  |  |  |

|-------------|------|-----------------------------------------------------------|----------|--|--|--|--|--|--|

|             | NAME | DESCRIPTION                                               | VERSION  |  |  |  |  |  |  |

| HTRC11001T  | SO14 | plastic small outlet package; 14 leads; body width 3.9 mm | SOT108-1 |  |  |  |  |  |  |

# HTRC11001T

### 6 BLOCK DIAGRAM

# HTRC11001T

### 7 PINNING

| SYMBOL          | PIN | DESCRIPTION                                                                                       |

|-----------------|-----|---------------------------------------------------------------------------------------------------|

| V <sub>SS</sub> | 1   | ground supply                                                                                     |

| TX2             | 2   | antenna driver output 2                                                                           |

| V <sub>DD</sub> | 3   | supply voltage (5 V stabilized)                                                                   |

| TX1             | 4   | antenna driver output 1                                                                           |

| MODE            | 5   | control input to enable filtering of serial clock and data input; for active antenna applications |

| XTAL1           | 6   | oscillator input 1                                                                                |

| XTAL2           | 7   | oscillator input 2                                                                                |

| SCLK            | 8   | serial clock input of microcontroller interface                                                   |

| DIN             | 9   | serial data input of microcontroller interface                                                    |

| DOUT            | 10  | serial data output of microcontroller interface                                                   |

| n.c.            | 11  | not connected                                                                                     |

| CEXT            | 12  | high-pass filter coupling capacitor connection                                                    |

| QGND            | 13  | internal analog virtual ground capacitor connection                                               |

| RX              | 14  | demodulator input                                                                                 |

Fig.2 Pin configuration.

2001 Nov 23

#### Product specification

### HTRC11001T

#### 8 FUNCTIONAL DESCRIPTION

#### 8.1 Power supply

The HTRC11001T works with an external 5 V  $\pm 10\%$  power supply at pin V\_{DD}. The maximum DC current is

10 mA +

$$\frac{2}{\pi}$$

× I<sub>ant(p)</sub> = 137 mA.

For optimum performance, the power supply connection should be bypassed to ground with a 100 nF capacitor close to the chip.

#### 8.2 Antenna drivers

The drivers deliver a square shaped voltage to the series resonant antenna circuit (see Fig.4). Due to the full bridge configuration of the drivers the output voltage  $V_{ant(p-p)}$  is approximately 10 V, corresponding to  $V_{ant(p)} = 5$  V. The current flowing through the antenna is sine shaped and the peak and RMS values are approximately:

$$I_{ant(p)} = \frac{4}{\pi} \times \frac{V_{ant(p)}}{R_{ant}}$$

$$I_{ant(rms)} = \frac{1}{\sqrt{2}} \times I_{ant(p)}$$

#### 8.3 Diagnosis

In order to detect an antenna short-circuit or open-circuit the antenna tap voltage is monitored.

An antenna fail condition is reported in the status bit ANTFAIL (see Table 5) if the antenna tap voltage does not go more negative than the diagnosis level voltage  $(V_{diag} = -1.15 \text{ V})$ . This condition is checked for every coil driver cycle.

#### 8.4 Oscillator with programmable divider

The crystal oscillator at pins XTAL1 and XTAL2 works with either crystal or ceramic resonators. It delivers the input clock frequency of 4, 8, 12 or 16 MHz. The oscillator frequency is divided by a programmable divider (selection bits FSEL1 and FSEL0) to obtain the carrier frequency of 125 kHz (see Table 3).

Alternatively, an external clock signal (CMOS compatible) may connected to pin XTAL1. For example, this clock signal can be derived from the microcontroller clock.

#### 8.5 Adaptive sampling time demodulator

The demodulator senses the absorption modulation applied by a transponder when inserted into the field. The signal is picked up at the antenna tap point between  $L_a$  and  $C_a$ . It is divided by  $R_v$  and the internal resistor  $R_{int}$  to a level on pin RX below 8 V (peak value) with respect to pin QGND (see Fig.4). Internally the signal is filtered with a second-order low-pass filter.

The antenna current and therefore the tap voltage is modulated by the transponder in amplitude and/or phase. This signal is fed into a synchronous demodulator recovering the baseband signal. The amplification and the bandpass filter edge frequencies of the demodulator can be adapted to different transponders via settings in the configuration pages (see Table 3).

The phase between the driver excitation signal and the antenna tap voltage depends on the antenna tuning. With optimum tuning, the phase of the antenna tap voltage is 90° off the antenna driver signal. Detuning of the antenna resonant circuit results in a change of this phase relationship. The built-in phase measurement unit allows the measurement of this phase relationship with a

resolution of  $\frac{1}{64} \times 360^\circ = 5.625^\circ$ . This can be used to

compute a sampling time that compensates the detuning of the reader antenna.

The phase measurement procedure can be carried out:

- Once before the first communication starts, if the position of the transponder does not change with respect to the reader antenna

- During the communication (after sending the write pulses and before receiving the answer of the transponder), if the tag is moving.

Before the system is switched into WRITE\_TAG mode, the demodulator has to be frozen. This is internally done by clamping the input of the filter amplifier unit to the level on pin QGND. Doing so avoids large transients in the amplifier and digitizer, which could affect settling times. In addition to the clamping, there exist other means in the HTRC11001T which allow further reduction of the settling times. All the parts of the circuitry which are associated with these functions are controlled by the bits FREEZE0, FREEZE1 and THRESET (see Table 2).

For more details concerning write timing, demodulator setting, power-up sequence, etc. please refer to the application note "AN 98080 Read/Write devices based on the HITAG Read/Write IC HTRC110".

### HTRC11001T

### 8.6 Idle and Power-down mode

The HTRC11001T can be switched into the Idle mode via setting bit PD = 1 and resetting bit  $PD_MODE = 0$  (see Table 3). In this Idle mode, only the oscillator and a few other system components are active.

It is also possible to switch the HTRC11001T completely off. This is achieved by the Power-down mode (bit PD = 1 and bit PD\_MODE = 1). Within this mode also the clock oscillator is switched off. This reduces the supply current of the HTRC11001T to less than 20  $\mu$ A.

### 8.7 Serial interface

The communication between the HTRC11001T and the microcontroller is done via a 3-wire digital interface. The interface is operated by the following signals:

- Clock pulse on pin SCLK

- Data input on pin DIN

- Data output on pin DOUT.

Pins SCLK and DIN are realized as Schmitt-trigger inputs. Pin DOUT is an open-drain output with an internal pull-up resistor.

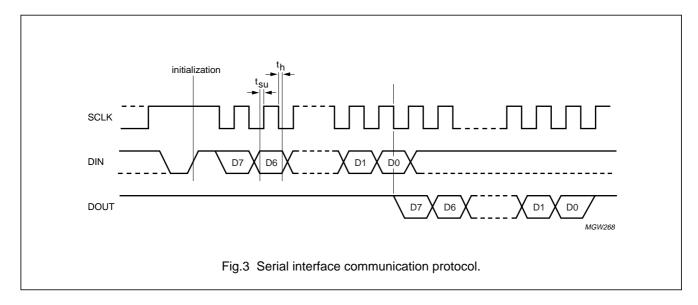

#### 8.7.1 COMMUNICATION PROTOCOL

Every communication between the HTRC11001T and the microcontroller begins with an initialization of the serial interface. The interface initialization condition is a LOW-to-HIGH transition on pin DIN while pin SCLK is at HIGH level (see Fig.3).

All commands transmitted to the HTRC11001T serial interface start with the Most Significant Bit (MSB).

Input DIN and output DOUT are valid when pin SCLK is at HIGH level.

### 8.7.2 GLITCH FILTER

Connecting pin MODE to  $V_{DD}$  enables digital filtering of the SCLK and the DIN input signals. This mode offers improved immunity against noise and interference (glitches) on these interface signals. It is intended to be used in the so called 'active antenna applications' where the microcontroller and the reader communicate via long signal lines (e.g. 1 meter).

In other applications pin MODE has to be connected to ground (pin  $\mathsf{V}_{SS}).$

For a detailed description of this feature, refer to the application note "AN 98080 Read/Write devices based on the HITAG Read/Write IC HTRC110".

# HTRC11001T

### 8.8 Commands

|                   | BIT 7 | BIT 6 | BIT5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 | REMARK                                         |

|-------------------|-------|-------|------|-------|-------|-------|-------|-------|------------------------------------------------|

|                   | MSB   |       |      |       |       |       |       | LSB   | REWARK                                         |

| READ_TAG          | 1     | 1     | 1    | _     | _     | _     | _     | _     | READ_TAG mode                                  |

| WRITE_TAG_N       | 0     | 0     | 0    | 1     | N3    | N2    | N1    | N0    | WRITE_TAG mode with<br>pulse width programming |

| WRITE_TAG         | 1     | 1     | 0    | _     | _     | _     | _     | _     | WRITE_TAG mode                                 |

| READ_PHASE        | 0     | 0     | 0    | 0     | 1     | 0     | 0     | 0     | read command                                   |

|                   | 0     | 0     | D5   | D4    | D3    | D2    | D1    | D0    | response                                       |

| SET_SAMPLING_TIME | 1     | 0     | D5   | D4    | D3    | D2    | D1    | D0    |                                                |

| GET_SAMPLING_TIME | 0     | 0     | 0    | 0     | 0     | 0     | 1     | 0     | read command                                   |

|                   | 0     | 0     | D5   | D4    | D3    | D2    | D1    | D0    | response                                       |

| SET_CONFIG_PAGE   | 0     | 1     | P1   | P0    | D3    | D2    | D1    | D0    | $4 \times 4$ configuration bits available      |

| GET_CONFIG_PAGE   | 0     | 0     | 0    | 0     | 0     | 1     | P1    | P0    | read command                                   |

|                   | X3    | X2    | X1   | X0    | D3    | D2    | D1    | D0    | response                                       |

### Table 1 Summary of the HTRC11001T command set

### 8.8.1 COMMAND READ\_TAG

| NAME         | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|--------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Command bits | 1     | 1     | 1     | -     | -     | _     | -     | _     |

This command is used to read the demodulated bit stream from a transponder.

After the assertion of the three command bits the HTRC11001T instantaneously switches to the READ\_TAG mode and transmits the demodulated, filtered and digitized data to the microcontroller. This data should be decoded by the microcontroller.

The READ\_TAG mode is terminated by a LOW-to-HIGH transition on pin SCLK.

#### 8.8.2 COMMAND WRITE\_TAG\_N

| NAME         | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|--------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Command bits | 0     | 0     | 0     | 1     | N3    | N2    | N1    | N0    |

This command is used to write data to a transponder.

If bits N3 to N0 are set to 0000, the signal on pin DIN is transparently switched to the drivers. A HIGH level on pin DIN corresponds to antenna drivers switched off and a LOW level corresponds to antenna drivers switched on.

For any binary number N between 0001 and 1111, the drivers are switched off at the next positive transition on pin DIN. This state is held for a time interval  $t = N \times T_0$  (for  $T_0 = 8 \ \mu$ s). This method relaxes the timing resolution requirements to the microcontroller and to the software implementation while providing an exact, selectable write pulse timing.

The WRITE\_TAG mode is terminated immediately by a LOW- to-HIGH transition on pin SCLK.

### HTRC11001T

#### 8.8.3 COMMAND WRITE\_TAG

| NAME         | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|--------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Command bits | 1     | 1     | 0     | _     | _     | _     | _     | _     |

This is the 3-bit short form of the previously described command WRITE\_TAG\_N. It allows to switch into the WRITE\_TAG mode with a minimum communication time.

The behaviour of the WRITE\_TAG command is identical to WRITE\_TAG\_N with two exceptions:

- WRITE\_TAG mode is entered after assertion of the third command bit

- No N parameter is specified with this command; instead the N value which was programmed with the most recent WRITE\_TAG\_N command is used. If no WRITE\_TAG\_N was issued so far, a default N = 0 (transparent mode) will be assumed.

#### 8.8.4 COMMAND READ\_PHASE

| NAME          | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Command bits  | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     |

| Response bits | 0     | 0     | D5    | D4    | D3    | D2    | D1    | D0    |

This command is used to read the antenna phase, which is measured at every carrier cycle.

The response bits D5 to D0 represent the phase (coded binary).

#### 8.8.5 COMMAND SET\_SAMPLING\_TIME

| NAME         | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|--------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Command bits | 1     | 0     | D5    | D4    | D3    | D2    | D1    | D0    |

This command specifies the demodulator sampling time t<sub>s</sub>. The sampling time is coded binary in bits D5 to D0.

#### 8.8.6 COMMAND GET\_SAMPLING\_TIME

| NAME          | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Command bits  | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     |

| Response bits | 0     | 0     | D5    | D4    | D3    | D2    | D1    | D0    |

This command is used to read back the sampling time t<sub>s</sub> set with SET\_SAMPLING\_TIME.

The response bits D5 to D0 represent the sampling time (coded binary).

# HTRC11001T

8.8.7 COMMAND SET\_CONFIG\_PAGE

| NAME    | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| Command | 0     | 1     | P1    | P0    | D3    | D2    | D1    | D0    |

This command is used to set the filter and amplifier parameters (cut-off frequencies and gain factors) and to select the operation mode. Bits P1 and P0 select one of four configuration pages.

Table 2

Configuration page bit names

| COMMAND           | BIT |   |    |    |         |                   |            |         |

|-------------------|-----|---|----|----|---------|-------------------|------------|---------|

| PAGE NUMBER       | 7   | 6 | P1 | P0 | D3      | D2                | D1         | D0      |

| SET_CONFIG_PAGE 0 | 0   | 1 | 0  | 0  | GAIN1   | GAIN0             | FILTERH    | FILTERL |

| SET_CONFIG_PAGE 1 | 0   | 1 | 0  | 1  | PD_MODE | PD                | HYSTERESIS | TXDIS   |

| SET_CONFIG_PAGE 2 | 0   | 1 | 1  | 0  | THRESET | ACQAMP            | FREEZE1    | FREEZE0 |

| SET_CONFIG_PAGE 3 | 0   | 1 | 1  | 1  | DISLP1  | DISSMART-<br>COMP | FSEL1      | FSEL0   |

Table 3

Description of the configuration page bits

| BIT NAME   | VALUE | DESCRIPTION                      | INITIAL<br>VALUE |

|------------|-------|----------------------------------|------------------|

| FILTERL    |       | main low-pass cut-off frequency  |                  |

|            | 0     | f <sub>L</sub> = 3 kHz           | 0                |

|            | 1     | f <sub>L</sub> = 6 kHz           |                  |

| FILTERH    |       | main high-pass cut-off frequency |                  |

|            | 0     | f <sub>H</sub> = 40 kHz          | 0                |

|            | 1     | f <sub>H</sub> = 160 kHz         |                  |

| GAIN0      |       | amplifier 0 gain factor          |                  |

|            | 0     | gain = 16                        | 0                |

|            | 1     | gain = 32                        |                  |

| GAIN1      |       | amplifier 1 gain factor          |                  |

|            | 0     | gain = 6.22                      |                  |

|            | 1     | gain = 31.5                      | 1                |

| TXDIS      |       | disable coil driver              |                  |

|            | 0     | coil driver active               | 0                |

|            | 1     | coil driver inactive             |                  |

| HYSTERESIS |       | data comparator hysteresis       |                  |

|            | 0     | hysteresis OFF                   | 0                |

|            | 1     | hysteresis ON                    |                  |

| PD         |       | Power-down mode enable           |                  |

|            | 0     | device active                    | 0                |

|            | 1     | device power-down                |                  |

2001 Nov 23

# HTRC11001T

| BIT NAME     | VALUE | DESCRIPTION                                                                                                                                                | INITIAL<br>VALUE |

|--------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| PD_MODE      |       | select Power-down mode                                                                                                                                     |                  |

|              | 0     | Idle mode                                                                                                                                                  | 0                |

|              | 1     | Power-down mode                                                                                                                                            |                  |

| FREEZE1,     |       | facility to achieve fast settling times (MSB and LSB)                                                                                                      |                  |

| FREEZE0      | 00    | normal operation                                                                                                                                           | 00               |

|              | 01    | main low-pass is frozen; main high-pass is pre-charged to level on pin QGND                                                                                |                  |

|              | 10    | main low-pass is frozen; time constant of main high-pass is reduced by a factor of 16 for bit FILTERH = 0 and by a factor of 8 for bit FILTERH = 1         |                  |

|              | 11    | main high-pass time constant is reduced by a factor of 16 for bit FILTERH = 0<br>and by a factor of 8 for bit FILTERH = 1; second high-pass is pre-charged |                  |

| ACQAMP       |       | store signal amplitude (see also bit AMPCOMP in Table 5)                                                                                                   |                  |

|              | 0     | set status bit AMPCOMP when the actual data signal amplitude is higher than the stored reference                                                           | 0                |

|              | 1     | store actual amplitude of the data signal as reference for later amplitude comparison                                                                      |                  |

| THRESET      |       | reset threshold generation of digitizer                                                                                                                    |                  |

|              | 0     | no reset                                                                                                                                                   | 0                |

|              | 1     | reset                                                                                                                                                      |                  |

| FSEL1, FSEL0 |       | clock frequency selection (MSB and LSB)                                                                                                                    |                  |

|              | 00    | 4 MHz                                                                                                                                                      | 00               |

|              | 01    | 8 MHz                                                                                                                                                      |                  |

|              | 10    | 12 MHz                                                                                                                                                     |                  |

|              | 11    | 16 MHz                                                                                                                                                     |                  |

| DISSMART-    |       | disable smart comparator                                                                                                                                   |                  |

| COMP         | 0     | smart comparator: on                                                                                                                                       | 0                |

|              | 1     | smart comparator: off                                                                                                                                      |                  |

| DISLP1       |       | disable low-pass 1                                                                                                                                         |                  |

|              | 0     | low-pass: on                                                                                                                                               | 0                |

|              | 1     | low-pass: off                                                                                                                                              |                  |

# HTRC11001T

| 8.8.8 | COMMAND GET_CC | ONFIG_PAG | E | <br> |

|-------|----------------|-----------|---|------|

|       |                |           |   |      |

| NAME          | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Command bits  | 0     | 0     | 0     | 0     | 0     | 1     | P1    | P0    |

| Response bits | Х3    | X2    | X1    | X0    | D3    | D2    | D1    | D0    |

This command has three functions:

- 1. Reading back the configuration parameters set by command SET\_CONFIG\_PAGE

- 2. Reading back the transmit pulse width programmed with command WRITE\_TAG\_N

- 3. Reading the system status information.

Bits P1 and P0 select one of four configuration pages.

The response bits (X3 to X0 and D3 to D0) contains the contents of the selected configuration page in its lower nibble.

For page 0 and page 1 the higher nibble reflects the current setting of the transmit pulse width N.

For page 2 and page 3 the system status information is returned in the higher nibble.

### Table 4 Configuration page bit names

| COMMAND           | BIT     |         |         |         |    |    |    |    |

|-------------------|---------|---------|---------|---------|----|----|----|----|

| PAGE NUMBER       | X3      | X2      | X1      | X0      | 3  | 2  | 1  | 0  |

| GET_CONFIG_PAGE 0 | N3      | N2      | N1      | N0      | D3 | D2 | D1 | D0 |

| GET_CONFIG_PAGE 1 | N3      | N2      | N1      | N0      | D3 | D2 | D1 | D0 |

| GET_CONFIG_PAGE 2 | 0 (RFU) | 0 (RFU) | AMPCOMP | ANTFAIL | D3 | D2 | D1 | D0 |

| GET_CONFIG_PAGE 3 | 0 (RFU) | 0 (RFU) | AMPCOMP | ANTFAIL | D3 | D2 | D1 | D0 |

Table 5

Description of the configuration page bits

| BIT NAME | VALUE | DESCRIPTION                                                      |  |

|----------|-------|------------------------------------------------------------------|--|

| D3 to D0 | XXXX  | contents of the selected configuration page                      |  |

| N3 to N0 | XXXX  | urrent setting of the transmit pulse width                       |  |

| ANTFAIL  |       | antenna failure                                                  |  |

|          | 0     | no antenna failure                                               |  |

|          | 1     | antenna failure                                                  |  |

| AMPCOMP  |       | amplitude comparison result (see also bit ACQAMP in Table 3)     |  |

|          | 0     | actual data signal amplitude is lower than the stored reference  |  |

|          | 1     | actual data signal amplitude is higher than the stored reference |  |

# HTRC11001T

### 9 LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 60134); note 1.

| SYMBOL              | PARAMETER                                                                  |      | MAX.                  | UNIT |

|---------------------|----------------------------------------------------------------------------|------|-----------------------|------|

| V <sub>n</sub>      | voltage at any pin (except pin RX)                                         | -0.3 | +6.5                  | V    |

| V <sub>n(max)</sub> | maximum voltage at any pin with respect to V <sub>DD</sub> (except pin RX) | -0.3 | V <sub>DD</sub> + 0.3 | V    |

| V <sub>RX</sub>     | voltage at pin RX                                                          | -10  | +12                   | V    |

| T <sub>j(max)</sub> | maximum junction temperature                                               | -    | 140                   | °C   |

| T <sub>stg</sub>    | storage temperature                                                        | -65  | +125                  | °C   |

#### Note

1. Stress above one or more of the limiting values may cause permanent damage to the device. These are stresses ratings only and operation of the device at these or at any other conditions above those given in Chapter 10 not implied. Exposure or limiting values for extended periods may affect device reliability.

### **10 DC CHARACTERISTICS**

All voltages are measured with respect to ground (pin V<sub>SS</sub>);  $T_{amb} = -40$  to +85 °C

| SYMBOL              | PARAMETER                         | CONDITIONS                                                      | MIN.                | TYP.                | MAX.                    | UNIT |

|---------------------|-----------------------------------|-----------------------------------------------------------------|---------------------|---------------------|-------------------------|------|

| Supply              | 1                                 |                                                                 | -                   | 4                   | 4                       | 1    |

| V <sub>DD</sub>     | supply voltage                    |                                                                 | 4.5                 | 5.0                 | 5.5                     | V    |

| I <sub>DD</sub>     | supply current                    | $V_{DD} = 5.5 \text{ V}; I_{TX1} = I_{TX2} = 0$                 | -                   | 4                   | 10                      | mA   |

| I <sub>idle</sub>   | idle current                      | V <sub>DD</sub> = 5.5 V; note 1                                 | -                   | 0.2                 | 0.4                     | mA   |

| I <sub>pd</sub>     | power-down current                | V <sub>DD</sub> = 5.5 V                                         | -                   | 7                   | 20                      | μA   |

| Driver out          | puts (pins TX1 and TX2)           |                                                                 |                     |                     |                         |      |

| I <sub>ant(p)</sub> | antenna driver output current     | permanent                                                       | -                   | _                   | 200                     | mA   |

| (peak value)        |                                   | pulse load; t <sub>on</sub> < 400 ms;<br>ratio on : off = 1 : 4 | -                   | _                   | 400                     | mA   |

| Ro                  | output resistance                 | both drivers together                                           | -                   | 2.5                 | 7                       | Ω    |

| Demodula            | tor input (pin RX)                |                                                                 |                     | ·                   |                         |      |

| VI                  | input voltage                     | with respect to pin QGND                                        | -8                  | -                   | +8                      | V    |

| V <sub>diag</sub>   | diagnosis level voltage           | with respect to pin QGND; $V_{DD} = 5 V$                        | -1.5                | -1.15               | -0.8                    | V    |

| V <sub>QGND</sub>   | potential on pin QGND             |                                                                 | 0.35V <sub>DD</sub> | 0.42V <sub>DD</sub> | 0.50V <sub>DD</sub>     | V    |

| R <sub>i</sub>      | internal demodulator<br>impedance |                                                                 | 17                  | 25                  | 33                      | kΩ   |

| Digital inp         | outs                              |                                                                 |                     | •                   |                         |      |

| V <sub>IH</sub>     | HIGH-level input voltage          |                                                                 | 0.7V <sub>DD</sub>  | -                   | V <sub>DD</sub> + 0.3 V | V    |

| V <sub>IL</sub>     | LOW-level input voltage           |                                                                 | -0.3                | -                   | 0.3V <sub>DD</sub>      | V    |

| Digital out         | tputs                             |                                                                 |                     |                     |                         |      |

| V <sub>OL</sub>     | LOW-level output voltage          | I <sub>OL(max)</sub> = 1 mA                                     | _                   | _                   | 0.4                     | V    |

| I <sub>OL</sub>     | LOW-level output current          | $V_{OL} \le 0.4 \text{ V}$                                      | 1                   | -                   | -                       | mA   |

#### Note

Downloaded from Arrow.com.

1. Power consumption of external quartz or any other component is not included.

2001 Nov 23

# HTRC11001T

### 11 AC CHARACTERISTICS

$T_{amb}$  = -40 to +85 °C.

| SYMBOL               | PARAMETER                        | CONDITIONS                           | MIN. | TYP. | MAX. | UNIT |

|----------------------|----------------------------------|--------------------------------------|------|------|------|------|

| Oscillator           | inputs (pins XTAL1 and XTAL2     | )                                    | •    | -    | •    | •    |

| f <sub>osc</sub>     | oscillator frequency             | depending on bits FSEL1<br>and FSEL0 | 4    | -    | 16   | MHz  |

| t <sub>st</sub>      | start-up time                    |                                      | -    | 4    | 10   | ms   |

| Ci                   | input capacitance on pin XTAL1   |                                      | -    | 5    | -    | pF   |

| R <sub>i</sub>       | input resistance                 | between pins XTAL1<br>and XTAL2      | 0.9  | 1.3  | 3.0  | MΩ   |

| External c           | lock input (pin XTAL1)           | •                                    | •    |      |      |      |

| f <sub>ext</sub>     | external clock frequency         | depending on bits FSEL1 and FSEL0    | 4    | -    | 16   | MHz  |

| δ                    | duty cycle                       |                                      | 40   | -    | 60   | %    |

| Serial inte          | rface                            | •                                    | •    |      |      |      |

| t <sub>su</sub>      | set-up time                      | pin MODE at V <sub>SS</sub>          | 50   | -    | -    | ns   |

| t <sub>h</sub>       | hold time                        | pin MODE at V <sub>SS</sub>          | 50   | -    | -    | ns   |

| Receiver (           | (pin RX)                         |                                      | •    | •    |      | •    |

| V <sub>RX(p-p)</sub> | sensitivity (peak-to-peak value) | receiver input                       | 2    | 1    | -    | mV   |

| t <sub>d</sub>       | receiver delay                   | bit FILTERL = 0                      | 290  | 310  | 340  | μs   |

|                      |                                  | bit FILTERL = 1                      | 160  | 175  | 190  | μs   |

| Demodula             | tor valid time                   |                                      |      |      |      |      |

| t <sub>rec</sub>     | demodulator recovery time        | after clock stable; note 1           | _    | -    | 5    | ms   |

|                      |                                  | after WRITE-pulse; note 1            | -    | _    | 500  | μs   |

|                      |                                  | after AST-step                       | -    | 0.7  | 1.5  | ms   |

| φ                    | phase measurement error          |                                      | -    | -    | ±5.7 | deg  |

Note

1. These short times require special command sequences. Please refer to the application note "AN 98080 Read/Write devices based on the HITAG Read/Write IC HTRC110".

# HTRC11001T

### **12 APPLICATION INFORMATION**

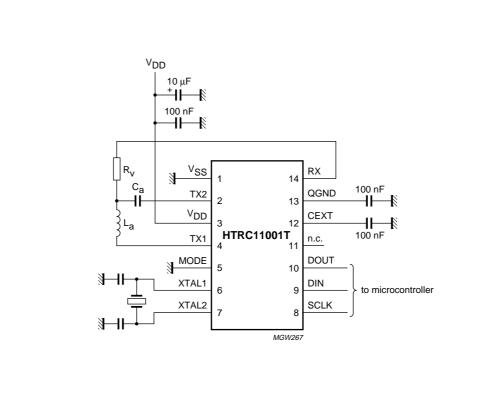

Figure 4 shows a minimal application circuitry for the HTRC11001T.

The reader coil L<sub>a</sub> together with the capacitor C<sub>a</sub> forms a series resonant LC circuit ( $f_0 = 125$  kHz). The high voltages in the LC circuit are divided to safe operating levels by R<sub>v</sub> and the internal resistor R<sub>i</sub> behind pin RX.

The two capacitors connected to pin XTAL1 and pin XTAL2 shall be the recommended values and types from the data sheet of the crystal. Alternatively to a crystal, a ceramic resonator can be used or an external clock source can be connected to pin XTAL1.

Fig.4 Minimum application circuitry.

HTRC11001T

### HITAG reader chip

### 13 PACKAGE OUTLINE

SO14: plastic small outline package; 14 leads; body width 3.9 mm

Downloaded from Arrow.com.

### SOT108-1

# HTRC11001T

### 14 SOLDERING

# 14.1 Introduction to soldering surface mount packages

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our *"Data Handbook IC26; Integrated Circuit Packages"* (document order number 9398 652 90011).

There is no soldering method that is ideal for all surface mount IC packages. Wave soldering can still be used for certain surface mount ICs, but it is not suitable for fine pitch SMDs. In these situations reflow soldering is recommended.

### 14.2 Reflow soldering

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement.

Several methods exist for reflowing; for example, convection or convection/infrared heating in a conveyor type oven. Throughput times (preheating, soldering and cooling) vary between 100 and 200 seconds depending on heating method.

Typical reflow peak temperatures range from 215 to 250 °C. The top-surface temperature of the packages should preferable be kept below 220 °C for thick/large packages, and below 235 °C for small/thin packages.

#### 14.3 Wave soldering

Conventional single wave soldering is not recommended for surface mount devices (SMDs) or printed-circuit boards with a high component density, as solder bridging and non-wetting can present major problems.

To overcome these problems the double-wave soldering method was specifically developed.

If wave soldering is used the following conditions must be observed for optimal results:

- Use a double-wave soldering method comprising a turbulent wave with high upward pressure followed by a smooth laminar wave.

- For packages with leads on two sides and a pitch (e):

- larger than or equal to 1.27 mm, the footprint longitudinal axis is preferred to be parallel to the transport direction of the printed-circuit board;

- smaller than 1.27 mm, the footprint longitudinal axis must be parallel to the transport direction of the printed-circuit board.

The footprint must incorporate solder thieves at the downstream end.

• For packages with leads on four sides, the footprint must be placed at a 45° angle to the transport direction of the printed-circuit board. The footprint must incorporate solder thieves downstream and at the side corners.

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured.

Typical dwell time is 4 seconds at 250 °C. A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

#### 14.4 Manual soldering

Fix the component by first soldering two diagonally-opposite end leads. Use a low voltage (24 V or less) soldering iron applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300 °C.

When using a dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds between 270 and 320  $^\circ\text{C}.$

# HTRC11001T

### 14.5 Suitability of surface mount IC packages for wave and reflow soldering methods

| PACKAGE                                             | SOLDERING METHOD                  |                       |  |  |

|-----------------------------------------------------|-----------------------------------|-----------------------|--|--|

| FACKAGE                                             | WAVE                              | REFLOW <sup>(1)</sup> |  |  |

| BGA, HBGA, LFBGA, SQFP, TFBGA                       | not suitable                      | suitable              |  |  |

| HBCC, HLQFP, HSQFP, HSOP, HTQFP, HTSSOP, HVQFN, SMS | not suitable <sup>(2)</sup>       | suitable              |  |  |

| PLCC <sup>(3)</sup> , SO, SOJ                       | suitable                          | suitable              |  |  |

| LQFP, QFP, TQFP                                     | not recommended <sup>(3)(4)</sup> | suitable              |  |  |

| SSOP, TSSOP, VSO                                    | not recommended <sup>(5)</sup>    | suitable              |  |  |

### Notes

- 1. All surface mount (SMD) packages are moisture sensitive. Depending upon the moisture content, the maximum temperature (with respect to time) and body size of the package, there is a risk that internal or external package cracks may occur due to vaporization of the moisture in them (the so called popcorn effect). For details, refer to the Drypack information in the "Data Handbook IC26; Integrated Circuit Packages; Section: Packing Methods".

- 2. These packages are not suitable for wave soldering as a solder joint between the printed-circuit board and heatsink (at bottom version) can not be achieved, and as solder may stick to the heatsink (on top version).

- 3. If wave soldering is considered, then the package must be placed at a 45° angle to the solder wave direction. The package footprint must incorporate solder thieves downstream and at the side corners.

- 4. Wave soldering is only suitable for LQFP, TQFP and QFP packages with a pitch (e) equal to or larger than 0.8 mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.65 mm.

- 5. Wave soldering is only suitable for SSOP and TSSOP packages with a pitch (e) equal to or larger than 0.65 mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.5 mm.

# HTRC11001T

### 15 DATA SHEET STATUS

| DATA SHEET STATUS <sup>(1)</sup> | PRODUCT<br>STATUS <sup>(2)</sup> | DEFINITIONS                                                                                                                                                                                                                                                                                                                        |

|----------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective data                   | Development                      | This data sheet contains data from the objective specification for product development. Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                                                        |

| Preliminary data                 | Qualification                    | This data sheet contains data from the preliminary specification.<br>Supplementary data will be published at a later date. Philips<br>Semiconductors reserves the right to change the specification without<br>notice, in order to improve the design and supply the best possible<br>product.                                     |

| Product data                     | Production                       | This data sheet contains data from the product specification. Philips<br>Semiconductors reserves the right to make changes at any time in order<br>to improve the design, manufacturing and supply. Changes will be<br>communicated according to the Customer Product/Process Change<br>Notification (CPCN) procedure SNW-SQ-650A. |

### Notes

- 1. Please consult the most recently issued data sheet before initiating or completing a design.

- 2. The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

### **16 DEFINITIONS**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

### 17 DISCLAIMERS

Life support applications — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

**Right to make changes** — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no licence or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

# Philips Semiconductors – a worldwide company

#### **Contact information**

For additional information please visit http://www.semiconductors.philips.com. Fax: +31 40 27 24825 For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com.

© Koninklijke Philips Electronics N.V. 2001

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Printed in The Netherlands

613502/02/pp**20**

Date of release: 2001 Nov 23

Document order number: 9397 750 08329

SCA73

Let's make things better.

Philips Semiconductors