#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (V <sub>CC</sub> to V <sub>EE</sub> )+6V |

|---------------------------------------------------------|

| All Other Pins(VCC + 0.3V) to (VEE - 0.3V)              |

| Output Short-Circuit Duration to VCC or VEEContinuous   |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)   |

| 5-Pin SOT23 (derate 7.1mW/°C above +70°C)571mW          |

| 8-Pin µMAX (derate 4.1mW/°C above +70°C)330mW           |

| 8-Pin SO (derate 5.88mW/°C above +70°C)471mW            |

| 10-Pin µMAX (derate 5.6mW/°C above +70° | ,              |

|-----------------------------------------|----------------|

| 14-Pin SO (derate 8.33mW/°C above +70°C | C)667mW        |

| Operating Temperature Range             | 40°C to +85°C  |

| Junction Temperature                    | +150°C         |

| Storage Temperature Range               | 65°C to +160°C |

| Lead Temperature (soldering, 10s)       | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS—TA = +25°C**

$(V_{CC} = +5.0V, V_{EE} = 0V, V_{CM} = 0V, V_{OUT} = V_{CC} / 2, \overline{SHDN} = V_{CC}, R_L = 100k\Omega$  tied to  $V_{CC} / 2$ , unless otherwise noted.)

| PARAMETER                          | SYMBOL                | CONDITIONS                                                             |                       |                    |     | TYP   | MAX   | UNITS |

|------------------------------------|-----------------------|------------------------------------------------------------------------|-----------------------|--------------------|-----|-------|-------|-------|

| Supply-Voltage Range               | Vcc                   | Inferred from PSRR test                                                |                       |                    | 2.4 |       | 5.5   | V     |

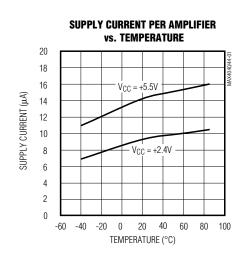

| Supply Current                     | 1                     | V <sub>CC</sub> = 2.4V                                                 |                       |                    |     | 10    |       |       |

| per Amplifier                      | Icc                   | V <sub>CC</sub> = 5.0V                                                 |                       |                    |     | 14    | 20    | μΑ    |

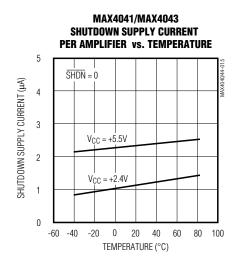

| Shutdown Supply                    | loo/ <del>outby</del> | SHDN = V <sub>EE</sub> , MAX4041                                       | V <sub>CC</sub> = 2.4 | V                  |     | 1.0   |       | μA    |

| Current per Amplifier              | ICC(SHDN)             | and MAX4043 only                                                       | $V_{CC} = 5.0$        | V                  |     | 2.0   | 5.0   | μΑ    |

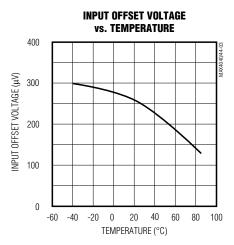

|                                    |                       |                                                                        | MAX4044E              | SD                 |     | ±0.20 | ±2.0  | mV    |

| Input Offset Voltage               | Vos                   | VEE ≤ VCM ≤ VCC                                                        | MAX404_E              | EU_                |     | ±0.25 | ±2.5  | IIIV  |

|                                    |                       |                                                                        | All other p           | ackages            |     | ±0.20 | ±1.50 | mV    |

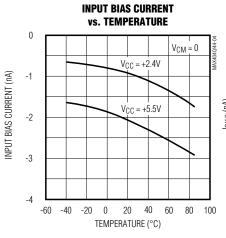

| Input Bias Current                 | lΒ                    | (Note 1)                                                               |                       |                    |     | ±2    | ±10   | nA    |

| Input Offset Current               | los                   | (Note 1)                                                               |                       |                    |     | ±0.5  | ±3.0  | nA    |

| Differential Input                 | DINI/DIEE)            | $ V_{IN+} - V_{IN-}  < 1.0V$                                           |                       |                    |     | 45    |       | MΩ    |

| Resistance                         | RIN(DIFF)             | $ V_{IN+} - V_{IN-}  > 2.5V$                                           |                       |                    |     | 4.4   |       | kΩ    |

| Input Common-Mode<br>Voltage Range | Vсм                   | Inferred from the CMRR test                                            |                       |                    | VEE |       | Vcc   | V     |

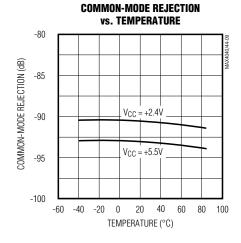

| Common-Mode                        | CMRR                  | \/== < \/o\                                                            | MAX404_E              | :U_                | 65  | 94    |       | dB    |

| Rejection Ratio                    | CIVINN                | V <sub>EE</sub> ≤ V <sub>CM</sub> ≤ V <sub>CC</sub> All other packages |                       |                    | 70  | 94    |       | ub    |

| Power-Supply<br>Rejection Ratio    | PSRR                  | 2.4V ≤ V <sub>CC</sub> ≤ 5.5V                                          |                       |                    | 75  | 85    |       | dB    |

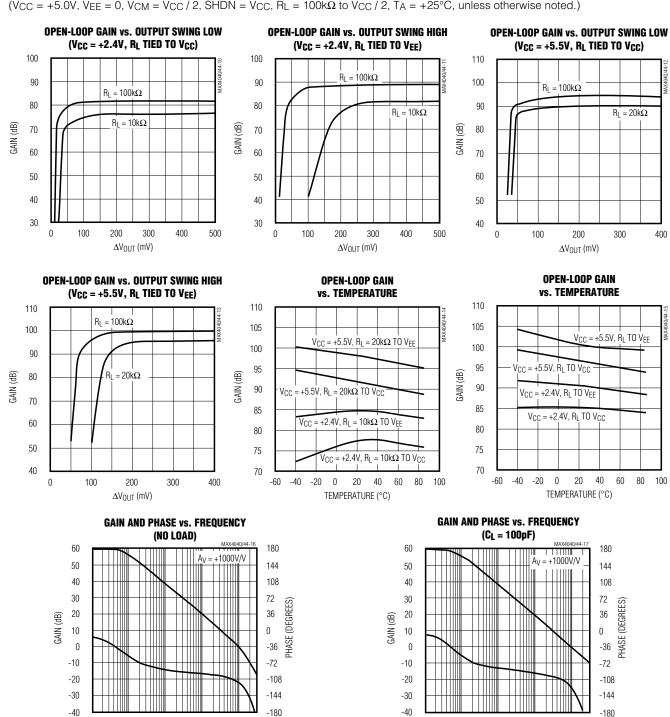

| Large-Signal                       | Λιω                   | (VFF + 0.2V) ≤ VOUT ≤ (VC                                              | . 0.21/)              | $R_L = 100k\Omega$ |     | 94    |       | dB    |

| Voltage Gain                       | Avol                  | (VEF + 0.2V) > VOU1 > (VC                                              | C - 0.2V)             | $R_L = 25k\Omega$  | 74  | 85    |       | UD.   |

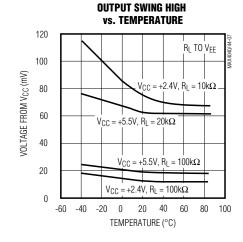

| Output Voltage                     | Voн                   | Specified as V <sub>CC</sub> - V <sub>OH</sub>                         |                       | $R_L = 100k\Omega$ |     | 10    |       | mV    |

| Swing High                         | VOH                   | Specified as IVCC - VOHT                                               |                       | $R_L = 25k\Omega$  |     | 60    | 90    | IIIV  |

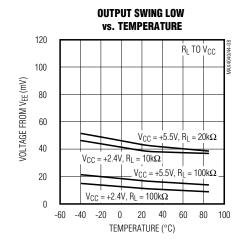

| Output Voltage                     | VOL                   | Specified as $ V_{EE} - V_{OL} $                                       |                       |                    |     | 10    |       | mV    |

| Swing Low                          | VOL.                  | Specified as $ VEE - VOL $ $R_L = 25k\Omega$                           |                       |                    | 40  | 60    | IIIV  |       |

| Output Short-Circuit               | lout(co)              | Sourcing Sinking                                                       |                       |                    |     | 0.7   |       | mA    |

| Current                            | IOUT(SC)              |                                                                        |                       |                    |     | 2.5   |       | 111/4 |

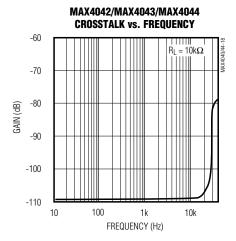

| Channel-to-Channel Isolation       |                       | Specified at DC, MAX4042/MAX4043/MAX4044 only                          |                       |                    |     | 80    |       | dB    |

### **ELECTRICAL CHARACTERISTICS—TA = +25°C (continued)**

$(V_{CC} = +5.0V, V_{EE} = 0V, V_{CM} = 0V, V_{OUT} = V_{CC} / 2, \overline{SHDN} = V_{CC}, R_L = 100k\Omega$  tied to  $V_{CC} / 2$ , unless otherwise noted.)

| PARAMETER                          | SYMBOL                            | CONDITIONS                                                | MIN                   | TYP  | MAX       | UNITS   |

|------------------------------------|-----------------------------------|-----------------------------------------------------------|-----------------------|------|-----------|---------|

| Output Leakage Current in Shutdown | IOUT(SHDN)                        | SHDN = V <sub>EE</sub> = 0, MAX4041/MAX4043 only (Note 2) |                       | 20   | 100       | nA      |

| SHDN Logic Low                     | VIL                               | MAX4041/MAX4043 only                                      |                       | (    | 0.3 x Vcc | V       |

| SHDN Logic High                    | VIH                               | MAX4041/MAX4043 only                                      | 0.7 x V <sub>CC</sub> |      |           | V       |

| SHDN Input Bias Current            | I <sub>IH</sub> , I <sub>IL</sub> | MAX4041/MAX4043 only                                      |                       | 40   | 120       | nA      |

| Gain Bandwidth Product             | GBW                               |                                                           |                       | 90   |           | kHz     |

| Phase Margin                       | $\Phi_{m}$                        |                                                           |                       | 68   |           | degrees |

| Gain Margin                        | Gm                                |                                                           |                       | 18   |           | dB      |

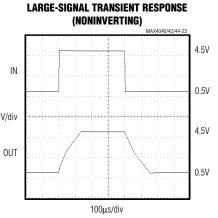

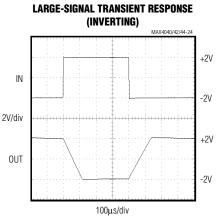

| Slew Rate                          | SR                                |                                                           |                       | 40   |           | V/ms    |

| Input Voltage Noise Density        | en                                | f = 1kHz                                                  |                       | 70   |           | nV/√Hz  |

| Input Current Noise Density        | in                                | f = 1kHz                                                  |                       | 0.05 |           | pA/√Hz  |

| Capacitive-Load Stability          |                                   | A <sub>VCL</sub> = +1V/V, no sustained oscillations       |                       | 200  |           | pF      |

| Power-Up Time                      | ton                               |                                                           |                       | 200  |           | μs      |

| Shutdown Time                      | t <u>shdn</u>                     | MAX4041 and MAX4043 only                                  |                       | 50   |           | μs      |

| Enable Time from Shutdown          | t <sub>EN</sub>                   | MAX4041 and MAX4043 only                                  |                       | 150  |           | μs      |

| Input Capacitance                  | CIN                               |                                                           |                       | 3    |           | pF      |

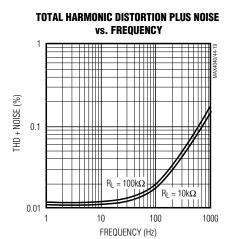

| Total Harmonic Distortion          | THD                               | $f_{IN} = 1kHz$ , $V_{OUT} = 2Vp-p$ , $AV = +1V/V$        |                       | 0.05 |           | %       |

| Settling Time to 0.01%             | ts                                | $A_V = +1V/V$ , $V_{OUT} = 2V_{STEP}$                     |                       | 50   |           | μs      |

### **ELECTRICAL CHARACTERISTICS—TA = TMIN to TMAX**

$(V_{CC} = +5.0V, V_{EE} = 0V, V_{CM} = 0V, V_{OUT} = V_{CC} / 2, \overline{SHDN} = V_{CC}, R_L = 100k\Omega \text{ tied to } V_{CC} / 2, \text{ unless otherwise noted.})$  (Note 3)

| PARAMETER                                | SYMBOL                | CONDITIONS                                                                           |            |  | TYP | MAX  | UNITS |

|------------------------------------------|-----------------------|--------------------------------------------------------------------------------------|------------|--|-----|------|-------|

| Supply-Voltage Range                     | V <sub>C</sub> C      | Inferred from PSRR test                                                              |            |  |     | 5.5  | V     |

| Supply Current<br>per Amplifier          | Icc                   |                                                                                      |            |  |     | 28   | μΑ    |

| Shutdown Supply<br>Current per Amplifier | I <sub>CC(SHDN)</sub> | SHDN = V <sub>EE</sub> , MAX4041 and MAX4043 only                                    |            |  |     | 6.0  | μА    |

|                                          |                       |                                                                                      | MAX4044ESA |  |     | ±4.5 |       |

| Input Offset Voltage                     | Vos                   | V <sub>EE</sub> ≤ V <sub>CM</sub> ≤ V <sub>CC</sub> MAX404_EU_<br>All other packages |            |  |     | ±5.0 | mV    |

|                                          |                       |                                                                                      |            |  |     | ±3.5 |       |

| Input Offset Voltage Drift               | TCvos                 |                                                                                      |            |  | 2   |      | μV/°C |

| Input Bias Current                       | ΙΒ                    | (Note 1)                                                                             |            |  |     | ±20  | nA    |

| Input Offset Current                     | los                   | (Note 1)                                                                             |            |  |     | ±8   | nA    |

#### **ELECTRICAL CHARACTERISTICS—TA = TMIN to TMAX (continued)**

$(V_{CC} = +5.0V, V_{EE} = 0V, V_{CM} = 0V, V_{OUT} = V_{CC} / 2, \overline{SHDN} = V_{CC}, R_L = 100k\Omega$  tied to  $V_{CC} / 2$ , unless otherwise noted.) (Note 3)

| PARAMETER                          | SYMBOL          | CONDITIONS                                                         |                    |     | TYP | MAX | UNITS |

|------------------------------------|-----------------|--------------------------------------------------------------------|--------------------|-----|-----|-----|-------|

| Input Common-Mode<br>Voltage Range | V <sub>CM</sub> | Inferred from the CMRR test                                        |                    | VEE |     | Vcc | ٧     |

| Common-Mode                        | CMRR            | VFF ≤ VCM ≤ VCC                                                    | MAX404_EU_         | 60  |     |     | ٩D    |

| Rejection Ratio                    | CIVIRR          | VEE S VCM S VCC                                                    | All other packages | 65  |     |     | dB    |

| Power-Supply<br>Rejection Ratio    | PSRR            | 2.4V ≤ V <sub>CC</sub> ≤ 5.5V                                      | 70                 |     |     | dB  |       |

| Large-Signal Voltage<br>Gain       | Avol            | $(V_{EE} + 0.2V) \le V_{OUT} \le (V_{CC} - 0.2V), R_L = 25k\Omega$ |                    |     |     |     | dB    |

| Output Voltage Swing<br>High       | V <sub>OH</sub> | Specified as VCC - VOH I,                                          |                    |     | 125 | mV  |       |

| Output Voltage Swing Low           | V <sub>OL</sub> | Specified as  VEE - VOL  , F                                       |                    |     | 75  | mV  |       |

Note 1: Input bias current and input offset current are tested with  $V_{CC} = +5.0V$  and  $+0.5V \le V_{CM} \le +4.5V$ .

Note 2: Tested for VEE ≤ VOUT ≤ VCC. Does not include current through external feedback network.

Note 3: All devices are 100% tested at  $T_A = +25^{\circ}C$ . All temperature limits are guaranteed by design.

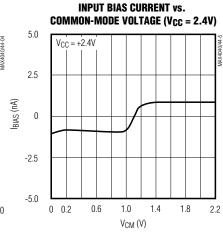

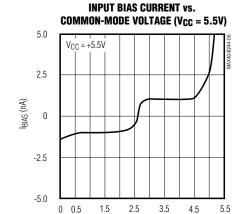

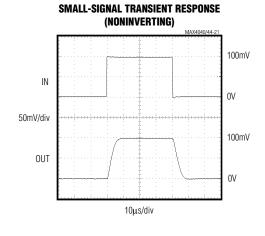

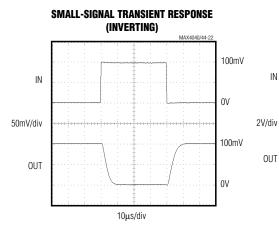

### Typical Operating Characteristics

$(V_{CC} = +5.0V, V_{EE} = 0, V_{CM} = V_{CC}/2, \overline{SHDN} = V_{CC}, R_L = 100k\Omega$  to  $V_{CC}/2, T_A = +25^{\circ}C$ , unless otherwise noted.)

### Typical Operating Characteristics (continued)

$(VCC = +5.0V, VEE = 0, VCM = VCC / 2, \overline{SHDN} = VCC, RL = 100k\Omega$  to  $VCC / 2, TA = +25^{\circ}C$ , unless otherwise noted.)

V<sub>CM</sub> (V)

### Typical Operating Characteristics (continued)

$(VCC = +5.0V, VEE = 0, VCM = VCC/2, \overline{SHDN} = VCC, R_L = 100k\Omega \text{ to } VCC/2, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

MIXIM

10

1k

FREQUENCY (Hz)

10k

100k

-180

-40

10

100

1k

FREQUENCY (Hz)

100k

### Typical Operating Characteristics (continued)

$(V_{CC} = +5.0V, V_{EE} = 0, V_{CM} = V_{CC}/2, \overline{SHDN} = V_{CC}, R_L = 100k\Omega$  to  $V_{CC}/2, T_A = +25^{\circ}C$ , unless otherwise noted.)

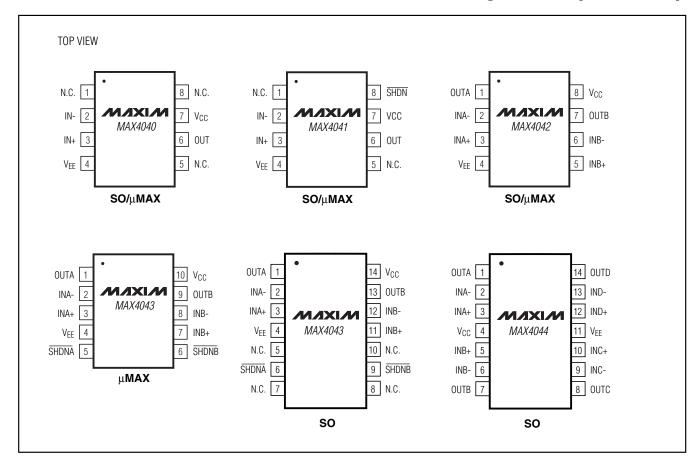

#### Pin Description

| PIN     |         |         |         |      |                |          |                 |                                                                                                                                                                |

|---------|---------|---------|---------|------|----------------|----------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX     | (4040   | MAX4041 | MAX4042 | MAX  | 4043           | MAX4044  | NAME            | FUNCTION                                                                                                                                                       |

| SOT23-5 | SO/µMAX | WAA4U41 | WAX4U42 | μMAX | SO             | WIAA4U44 |                 |                                                                                                                                                                |

| 1       | 6       | 6       | _       | _    | _              | _        | OUT             | Amplifier Output. High impedance when in shutdown mode.                                                                                                        |

| 2       | 4       | 4       | 4       | 4    | 4              | 11       | VEE             | Negative Supply. Tie to ground for single-supply operation.                                                                                                    |

| 3       | 3       | 3       | _       | _    | _              | _        | IN+             | Noninverting Input                                                                                                                                             |

| 4       | 2       | 2       | _       | _    | _              | _        | IN-             | Inverting Input                                                                                                                                                |

| 5       | 7       | 7       | 8       | 10   | 14             | 4        | Vcc             | Positive Supply                                                                                                                                                |

| _       | 1, 5, 8 | 1, 5    | _       | _    | 5, 7,<br>8, 10 | _        | N.C.            | No Connection. Not internally connected.                                                                                                                       |

| _       | _       | 8       | _       | _    | _              | _        | SHDN            | Shutdown Input. Drive high, or tie to V <sub>CC</sub> for normal operation. Drive to V <sub>EE</sub> to place device in shutdown mode.                         |

| _       | _       | _       | 1, 7    | 1, 9 | 1, 13          | 1, 7     | OUTA,<br>OUTB   | Outputs for Amplifiers A and B. High impedance when in shutdown mode.                                                                                          |

| _       | _       | _       | 2, 6    | 2, 8 | 2, 12          | 2, 6     | INA-,<br>INB-   | Inverting Inputs to Amplifiers A and B                                                                                                                         |

| _       | _       | _       | 3, 5    | 3, 7 | 3, 11          | 3, 5     | INA+,<br>INB+   | Noninverting Inputs to Amplifiers A and B                                                                                                                      |

| _       | _       | _       | _       | 5, 6 | 6, 9           | _        | SHDNA,<br>SHDNB | Shutdown Inputs for Amplifiers A and B. Drive high, or tie to V <sub>CC</sub> for normal operation. Drive to V <sub>EE</sub> to place device in shutdown mode. |

| _       | _       | _       | _       | _    | _              | 8, 14    | OUTC,<br>OUTD   | Outputs for Amplifiers C and D                                                                                                                                 |

| _       | _       | _       | _       | _    | _              | 9, 13    | INC-,<br>IND-   | Inverting Inputs to Amplifiers C and D                                                                                                                         |

| _       | _       | _       | _       | _    | _              | 10, 12   | INC+,<br>IND+   | Noninverting Inputs to Amplifiers C and D                                                                                                                      |

### Detailed Description

#### Rail-to-Rail Input Stage

The MAX4040–MAX4044 have rail-to-rail inputs and rail-to-rail output stages that are specifically designed for low-voltage, single-supply operation. The input stage consists of separate NPN and PNP differential stages, which operate together to provide a common-mode range extending to both supply rails. The crossover region of these two pairs occurs halfway between VCC and VEE. The input offset voltage is typically 200µV. Low operating supply voltage, low supply current, rail-to-rail common-mode input range, and rail-to-rail outputs make this family of operational amplifiers

an excellent choice for precision or general-purpose, low-voltage battery-powered systems.

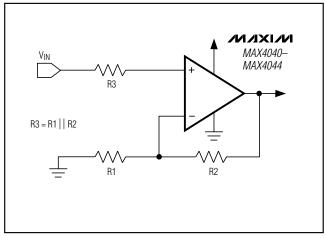

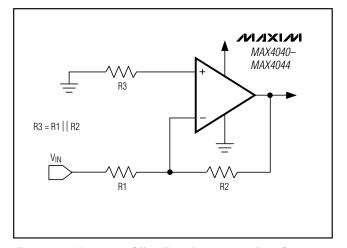

Since the input stage consists of NPN and PNP pairs, the input bias current changes polarity as the common-mode voltage passes through the crossover region. Match the effective impedance seen by each input to reduce the offset error caused by input bias currents flowing through external source impedances (Figures 1a and 1b). The combination of high source impedance plus input capacitance (amplifier input capacitance plus stray capacitance) creates a parasitic pole that produces an underdamped signal response. Reducing input capacitance or placing a small capacitor across the feedback resistor improves response in this case.

Figure 1a. Minimizing Offset Error Due to Input Bias Current (Noninverting)

Figure 1b. Minimizing Offset Error Due to Input Bias Current (Inverting)

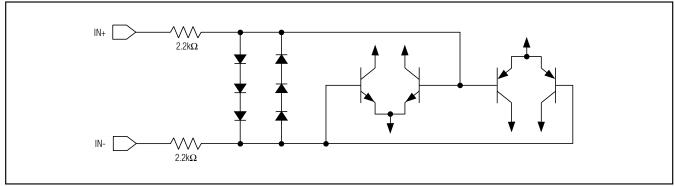

The MAX4040–MAX4044 family's inputs are protected from large differential input voltages by internal 2.2k $\Omega$  series resistors and back-to-back triple-diode stacks across the inputs (Figure 2). For differential input voltages (much less than 1.8V), input resistance is typically 45M $\Omega$ . For differential input voltages greater than 1.8V, input resistance is around 4.4k $\Omega$ , and the input bias current can be approximated by the following equation:

$$IBIAS = (VDIFF - 1.8V) / 4.4k\Omega$$

In the region where the differential input voltage approaches 1.8V, the input resistance decreases exponentially from  $45\text{M}\Omega$  to  $4.4\text{k}\Omega$  as the diode block begins conducting. Conversely, the bias current increases with the same curve.

#### Rail-to-Rail Output Stage

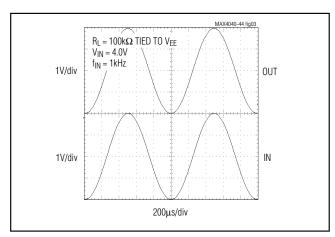

The MAX4040–MAX4044 output stage can drive up to a  $25k\Omega$  load and still swing to within 60mV of the rails. Figure 3 shows the output voltage swing of a MAX4040 configured as a unity-gain buffer, powered from a single +4.0V supply voltage. The output for this setup typically swings from (VEE + 10mV) to (VCC - 10mV) with a 100k $\Omega$  load.

### Applications Information

#### **Power-Supply Considerations**

The MAX4040–MAX4044 operate from a single +2.4V to +5.5V supply (or dual ±1.2V to ±2.75V supplies) and consume only 10µA of supply current per amplifier. A high power-supply rejection ratio of 85dB allows the amplifiers to be powered directly off a decaying battery voltage, simplifying design and extending battery life.

#### **Power-Up Settling Time**

The MAX4040–MAX4044 typically require 200µs to power up after V<sub>CC</sub> is stable. During this start-up time, the output is indeterminant. The application circuit should allow for this initial delay.

Figure 2. Input Protection Circuit

Figure 3. Rail-to-Rail Input/Output Voltage Range

#### **Shutdown Mode**

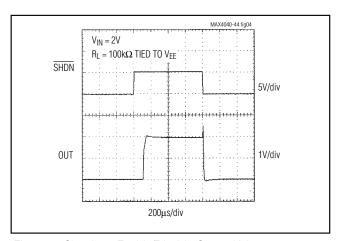

The MAX4041 (single) and MAX4043 (dual) feature a low-power shutdown mode. When the shutdown pin (SHDN) is pulled low, the supply current drops to 1µA per amplifier, the amplifier is disabled, and the outputs enter a high-impedance state. Pulling SHDN high or leaving it floating enables the amplifier. Take care to ensure that parasitic leakage current at the SHDN pin does not inadvertently place the part into shutdown mode when SHDN is left floating. Figure 4 shows the output voltage response to a shutdown pulse. The logic threshold for SHDN is always referred to Vcc / 2 (not to GND). When using dual supplies, pull SHDN to VEE to enter shutdown mode.

#### **Load-Driving Capability**

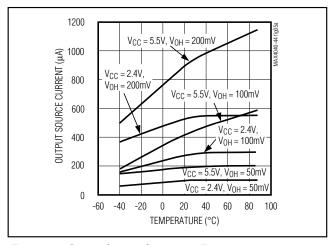

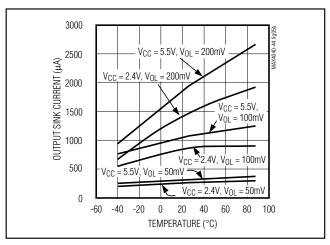

The MAX4040–MAX4044 are fully guaranteed over temperature and supply voltage to drive a maximum resistive load of  $25 k\Omega$  to VCC / 2, although heavier loads can be driven in many applications. The rail-to-rail output stage of the amplifier can be modeled as a current source when driving the load toward VCC, and as a current sink when driving the load toward VEE. The magnitude of this current source/sink varies with supply voltage, ambient temperature, and lot-to-lot variations of the units.

Figures 5a and 5b show the typical current source and sink capability of the MAX4040–MAX4044 family as a function of supply voltage and ambient temperature. The contours on the graph depict the output current value, based on driving the output voltage to within 50mV, 100mV, and 200mV of either power-supply rail.

Figure 4. Shutdown Enable/Disable Output Voltage

Figure 5a. Output Source Current vs. Temperature

Figure 5b. Output Sink Current vs. Temperature

For example, a MAX4040 running from a single +2.4V supply, operating at TA = +25°C, can source 240 $\mu$ A to within 100mV of VCC and is capable of driving a 9.6k $\Omega$  load resistor to VEE:

$$R_L = \frac{2.4V - 0.1V}{240\mu A} = 9.6k\Omega \text{ to } V_{EE}$$

The same application can drive a 4.6k $\Omega$  load resistor when terminated in VCC / 2 (+1.2V in this case).

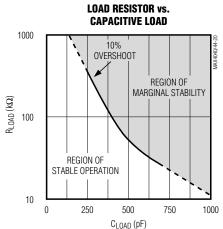

#### **Driving Capacitive Loads**

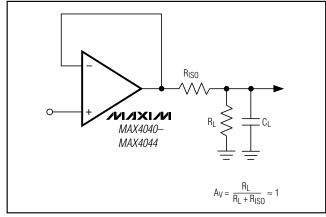

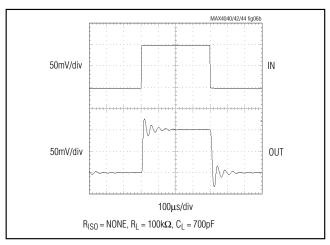

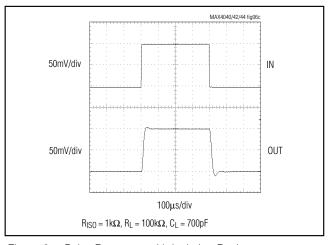

The MAX4040–MAX4044 are unity-gain stable for loads up to 200pF (see Load Resistor vs. Capacitive Load graph in *Typical Operating Characteristics*). Applications that require greater capacitive drive capability should use an isolation resistor between the output and the capacitive load (Figures 6a–6c). Note that this alternative results in a loss of gain accuracy because RISO forms a voltage divider with the load resistor.

#### **Power-Supply Bypassing and Layout**

The MAX4040–MAX4044 family operates from either a single +2.4V to +5.5V supply or dual  $\pm 1.2$ V to  $\pm 2.75$ V supplies. For single-supply operation, bypass the power supply with a 100nF capacitor to VEE (in this case GND). For dual-supply operation, both the VCC and VEE supplies should be bypassed to ground with separate 100nF capacitors.

Good PC board layout techniques optimize performance by decreasing the amount of stray capacitance at the op amp's inputs and output. To decrease stray capacitance, minimize trace lengths by placing external components as close as possible to the op amp. Surface-mount components are an excellent choice.

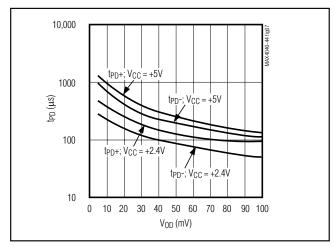

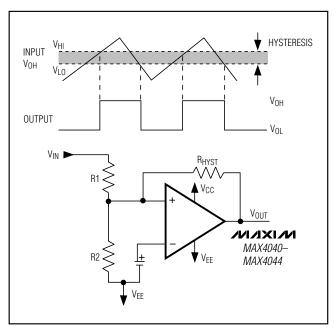

### Using the MAX4040-MAX4044 as Comparators

Although optimized for use as operational amplifiers, the MAX4040–MAX4044 can also be used as rail-to-rail I/O comparators. Typical propagation delay depends on the input overdrive voltage, as shown in Figure 7. External hysteresis can be used to minimize the risk of output oscillation. The positive feedback circuit, shown in Figure 8, causes the input threshold to change when the output voltage changes state. The two thresholds create a hysteresis band that can be calculated by the following equations:

VHYST = VHI - VLO

$V_{LO} = V_{IN} \times R2 / (R1 + (R1 \times R2 / R_{HYST}) + R2)$

VHI = [(R2 / R1 x V<sub>IN</sub>) + (R2 / R<sub>H</sub>YST) x V<sub>CC</sub>] / (1 + R1 / R2 + R2 / R<sub>H</sub>YST)

Figure 6a. Using a Resistor to Isolate a Capacitive Load from the Op Amp

Figure 6b. Pulse Response without Isolating Resistor

Figure 6c. Pulse Response with Isolating Resistor

Figure 7. Propagation Delay vs. Input Overdrive

The MAX4040-MAX4044 contain special circuitry to boost internal drive currents to the amplifier output stage. This maximizes the output voltage range over which the amplifiers are linear. In an open-loop comparator application, the excursion of the output voltage is so close to the supply rails that the output stage transistors will saturate, causing the quiescent current to increase from the normal 10 $\mu$ A. Typical quiescent currents increase to 35 $\mu$ A for the output saturating at VCC and 28 $\mu$ A for the output at VEE.

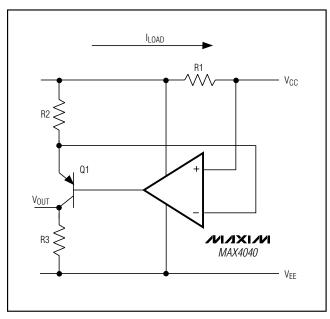

## Using the MAX4040-MAX4044 as Ultra-Low-Power Current Monitors

The MAX4040–MAX4044 are ideal for applications powered from a battery stack. Figure 9 shows an application circuit in which the MAX4040 is used for monitoring the current of a battery stack. In this circuit, a current load is applied, and the voltage drop at the battery terminal is sensed.

The voltage on the load side of the battery stack is equal to the voltage at the emitter of Q1, due to the feedback loop containing the op amp. As the load current increases, the voltage drop across R1 and R2 increases. Thus, R2 provides a fraction of the load current (set by the ratio of R1 and R2) that flows into the emitter of the PNP transistor. Neglecting PNP base current, this current flows into R3, producing a ground-referenced voltage proportional to the load current. Scale R1 to give a voltage drop large enough in comparison to Vos of the op amp, in order to minimize errors.

The output voltage of the application can be calculated using the following equation:

$VOUT = [ILOAD \times (R1 / R2)] \times R3$

Figure 8. Hysteresis Comparator Circuit

Figure 9. Current Monitor for a Battery Stack

For a 1V output and a current load of 50mA, the choice of resistors can be R1 =  $2\Omega$ , R2 =  $100k\Omega$ , R3 =  $1M\Omega$ . The circuit consumes less power (but is more susceptible to noise) with higher values of R1, R2, and R3.

### Pin Configurations (continued)

\_Chip Information

MAX4040/MAX4041 TRANSISTOR COUNT: 234 MAX4042/MAX4043 TRANSISTOR COUNT: 466

MAX4044 TRANSISTOR COUNT: 932 SUBSTRATE CONNECTED TO VEE

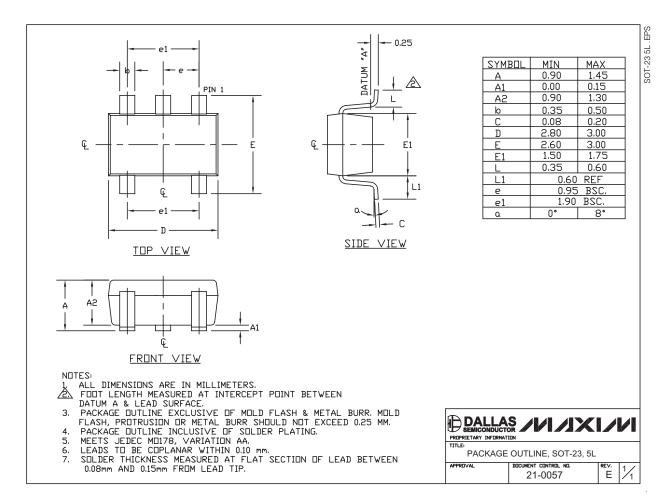

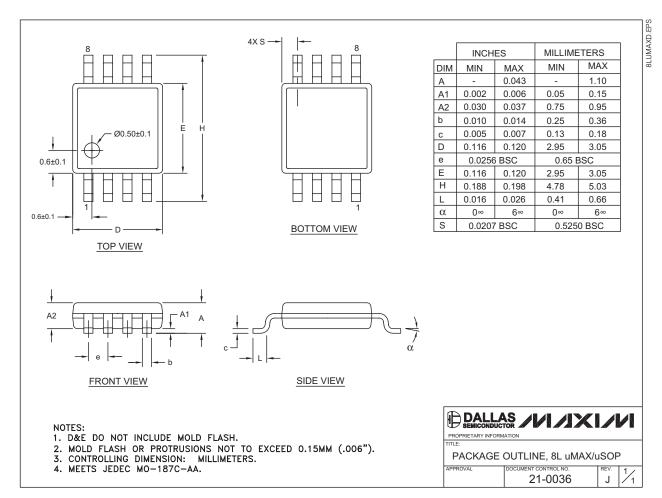

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

\_\_ /N/1XI/N

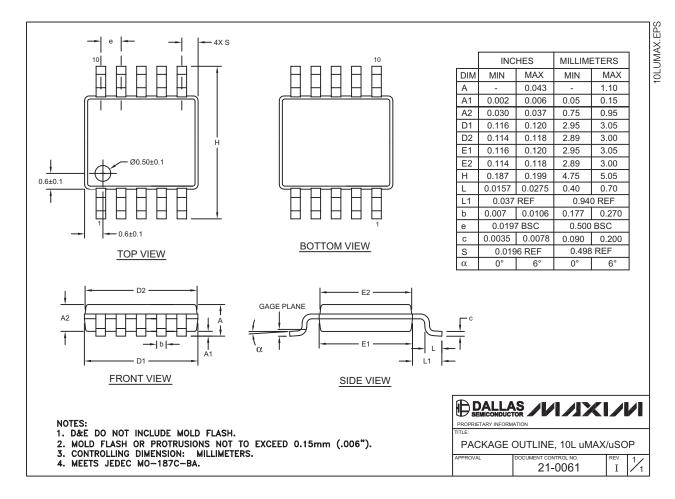

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

16 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600