Vitesse Corporate Headquarters 741 Calle Plano Camarillo, California 93012 United States

www.vitesse.com

Copyright© 2005–2006 by Vitesse Semiconductor Corporation

Vitesse Semiconductor Corporation ("Vitesse") retains the right to make changes to its products or specifications to improve performance, reliability or manufacturability. All information in this document, including descriptions of features, functions, performance, technical specifications and availability, is subject to change without notice at any time. While the information furnished herein is held to be accurate and reliable, no responsibility will be assumed by Vitesse for its use. Furthermore, the information contained herein does not convey to the purchaser of microelectronic devices any license under the patent right of any manufacturer.

Vitesse products are not intended for use in life support products where failure of a Vitesse product could reasonably be expected to result in death or personal injury. Anyone using a Vitesse product in such an application without express written consent of an officer of Vitesse does so at their own risk, and agrees to fully indemnify Vitesse for any damages that may result from such use or sale.

Vitesse Semiconductor Corporation is a registered trademark. All other products or service names used in this publication are for identification purposes only, and may be trademarks or registered trademarks of their respective companies. All other trademarks or registered trademarks mentioned herein are the property of their respective holders.

June 2006 Page 2 of 108

# **Contents**

| Rev | Revision History |                                             |    |

|-----|------------------|---------------------------------------------|----|

| 1   | Introduction     |                                             |    |

| 2   | Proc             | duct Overview                               | 15 |

|     | 2.1              | Features and Benefits                       |    |

|     | 2.2              | Block Diagram                               |    |

| 3   | Func             | ctional Descriptions                        | 18 |

|     | 3.1              | Operating Modes                             |    |

|     |                  | 3.1.1 SerDes MAC-to-Cat5 Mode MAC Interface | 19 |

|     |                  | 3.1.2 SGMII MAC-to-Cat5 Mode MAC Interface  | 20 |

|     |                  | 3.1.3 All Modes Cat5 Media Interface        | 21 |

|     | 3.2              | SerDes Media Interface                      |    |

|     | 3.3              | SGMII MAC-to-100BASE-FX Mode                |    |

|     | 3.4              | Automatic Media-Sense (AMS) Interface Mode  |    |

|     | 3.5              | Cat5 Auto-Negotiation                       |    |

|     | 3.6              | Manual MDI/MDI-X Setting                    |    |

|     | 3.7              | Automatic Crossover and Polarity Detection  |    |

|     | 3.8              | Link Speed Downshift                        |    |

|     | 3.9              | Transformer-less Ethernet                   |    |

|     | 3.10             | Ethernet In-line Powered Devices            |    |

|     | 3.11             | 802.3af PoE Support                         |    |

|     | 3.12             | ActiPHY Power Management                    |    |

|     |                  | 3.12.1 Low Power State                      |    |

|     |                  | 3.12.2 Link Partner Wake-up State           |    |

|     | 0.40             | 3.12.3 Normal Operating State               |    |

|     | 3.13             | Serial Management Interface                 |    |

|     |                  | 3.13.1 SMI Frames                           |    |

|     | 2 1 4            | 3.13.2 SMI Interrupts                       |    |

|     | 3.14             | LED Interface                               |    |

|     |                  | 3.14.1 LED Modes                            |    |

|     |                  | 3.14.3 Serial LED Mode                      |    |

|     | 3.15             | GPIO Pins                                   |    |

|     | 3.16             |                                             |    |

|     | 3.10             | Testing Features                            |    |

|     |                  | 3.16.2 CRC Counters                         |    |

|     |                  | 3.16.3 Far-end Loopback                     |    |

|     |                  | 3.16.4 Near-end Loopback                    |    |

|     |                  | 3.16.5 Connector Loopback                   |    |

|     |                  | 3.16.6 VeriPHY Cable Diagnostics            |    |

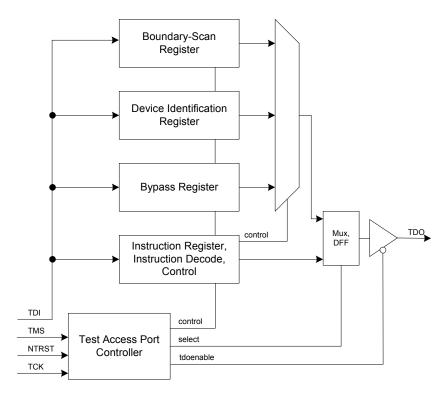

|     |                  | 3.16.7 IEEE 1149.1 JTAG Boundary Scan       |    |

|     |                  | 3.16.8 JTAG Instruction Codes               |    |

|     |                  | 3.16.9 Boundary Scan Register Cell Order    |    |

|     | 3 17             | 3                                           | 41 |

June 2006

| 4 | Conf | igurat | tion4                                             | 42 |

|---|------|--------|---------------------------------------------------|----|

|   | 4.1  |        | ers                                               |    |

|   |      | 4.1.1  | Reserved Registers                                | 43 |

|   |      |        | Reserved Bits                                     |    |

|   | 4.2  | IEEE S | tandard and Main Registers                        | 44 |

|   |      | 4.2.1  | Mode Control                                      | 45 |

|   |      |        | Mode Status                                       |    |

|   |      |        | Device Identification                             |    |

|   |      |        | Auto-Negotiation Advertisement                    |    |

|   |      |        | Link Partner Auto-Negotiation Capability          |    |

|   |      |        | Auto-Negotiation Expansion                        |    |

|   |      |        | Transmit Auto-Negotiation Next Page               |    |

|   |      |        | Auto-Negotiation Link Partner Next Page Receive   |    |

|   |      |        | 1000BASE-T Control                                |    |

|   |      |        | 1000BASE-T Status                                 |    |

|   |      |        | Main Registers Reserved Addresses                 |    |

|   |      |        | 1000BASE-T Status Extension 1                     |    |

|   |      |        | 100BASE-TX Status Extension                       |    |

|   |      |        | 1000BASE-T Status Extension 2                     |    |

|   |      |        | Bypass Control                                    |    |

|   |      |        | Reserved Address Space                            |    |

|   |      |        | Extended Control and Status                       |    |

|   |      |        | Extended PHY Control Set 1                        |    |

|   |      |        | Extended PHY Control Set 2                        |    |

|   |      |        | Interrupt Mask                                    |    |

|   |      |        | Interrupt Status                                  |    |

|   |      |        | MAC Interface Auto-Negotiation Control and Status |    |

|   |      |        | Device Auxiliary Control and Status               |    |

|   |      |        | LED Mode Select                                   |    |

|   |      |        | LED Behavior                                      |    |

|   | 4.3  |        | led Page Registers                                |    |

|   | 4.5  |        | Extended Page Access                              |    |

|   |      |        | SerDes Media Control                              |    |

|   |      |        | SerDes MAC Control                                |    |

|   |      |        | CRC Good Counter                                  |    |

|   |      |        | SIGDET Control                                    |    |

|   |      |        | Extended PHY Control                              |    |

|   |      |        | EEPROM Interface Status and Control               |    |

|   |      |        | EEPROM Data Read/Write                            |    |

|   |      |        | PoE and Miscellaneous Functionality               |    |

|   |      |        | VeriPHY Control 1                                 |    |

|   |      |        | VeriPHY Control 2                                 |    |

|   |      |        | VeriPHY Control 3                                 |    |

|   |      |        | Reserved Extended Registers                       |    |

|   |      |        | Ethernet Packet Generator Control 1               |    |

|   |      |        | Ethernet Packet Generator Control 1               |    |

|   | 1 1  |        |                                                   |    |

|   | 4.4  |        | al-Purpose I/O Registers                          |    |

|   |      |        | Reserved GPIO Registers                           |    |

|   |      |        | SIGDET Control Register                           |    |

|   |      |        | GPIO Input Register                               |    |

|   |      | 4.4.4  | GPIO Output Register                              | 12 |

June 2006 Page 4 of 108

|   |            | 4.4.5 GPIO Pin Configuration           |     |

|---|------------|----------------------------------------|-----|

|   |            | 4.4.6 100BASE-FX Control Register      |     |

|   | 4.5        | CMODE                                  |     |

|   |            | 4.5.1 CMODE Pins and Related Functions |     |

|   |            | 4.5.2 Functions and Related CMODE Pins |     |

|   |            | 4.5.3 CMODE Resistor Values            |     |

|   | 4.6        | EEPROM                                 |     |

|   |            | 4.6.1 EEPROM Contents Description      |     |

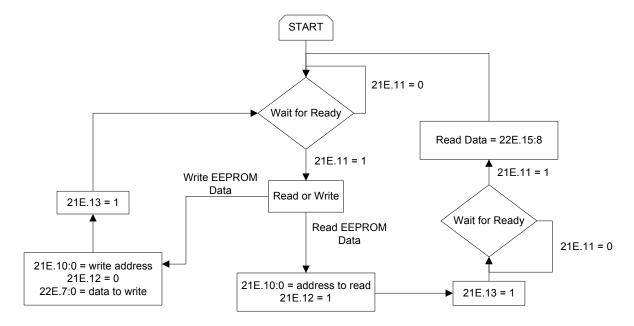

|   |            | 4.6.2 Read/Write Access to the EEPROM  | 79  |

| 5 | Elec       | ctrical Specifications                 | 81  |

| • | 5.1        | DC Characteristics                     |     |

|   | <b>.</b>   | 5.1.1 VDDIO at 3.3 V                   |     |

|   |            | 5.1.2 VDDIO at 2.5 V                   |     |

|   |            | 5.1.3 VDDIO at 1.8 V                   |     |

|   |            | 5.1.4 VDD at 3.3 V                     |     |

|   |            | 5.1.5 MAC and SerDes Outputs           |     |

|   |            | 5.1.6 MAC and SerDes Inputs            |     |

|   |            | 5.1.7 LED Pins                         |     |

|   |            | 5.1.8 JTAG Pins                        |     |

|   | 5.2        | Current Consumption                    |     |

|   | 5.3        | AC Characteristics                     |     |

|   |            | 5.3.1 Reference Clock Input            | 86  |

|   |            | 5.3.2 Clock Output                     |     |

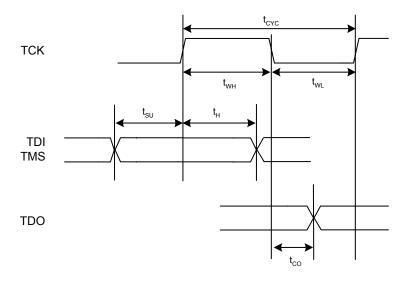

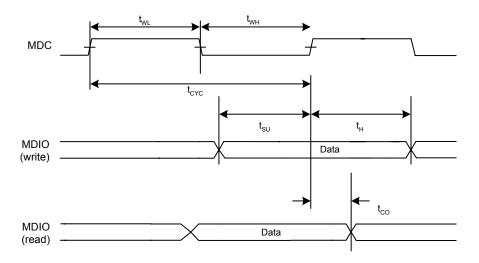

|   |            | 5.3.3 JTAG Interface                   |     |

|   |            | 5.3.4 SMI Interface                    | 88  |

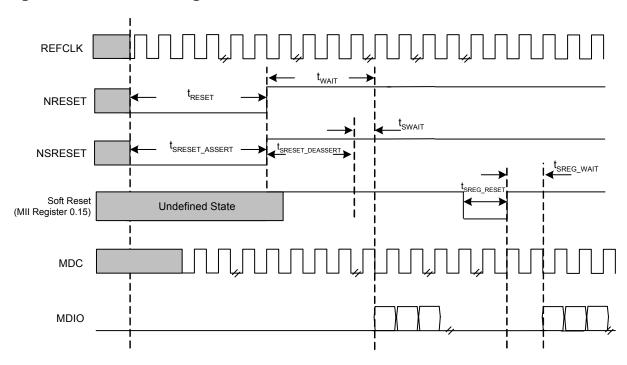

|   |            | 5.3.5 Device Reset                     | 89  |

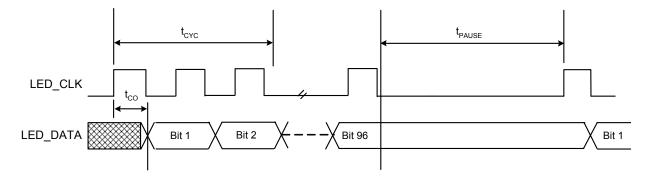

|   |            | 5.3.6 Serial LEDs                      | 90  |

|   | 5.4        | Operating Conditions                   | 91  |

|   | 5.5        | Stress Ratings                         | 91  |

| 6 | Pin        | Descriptions                           | 92  |

| • | 6.1        | Pin Diagram                            |     |

|   | 6.2        | Pin Identifications                    | 94  |

|   |            | 6.2.1 SerDes MAC Interface             | 94  |

|   |            | 6.2.2 SerDes Media Interface           | 95  |

|   |            | 6.2.3 GPIO and SIGDET                  | 96  |

|   |            | 6.2.4 Twisted Pair Interface           | 96  |

|   |            | 6.2.5 Serial Management Interface      | 97  |

|   |            | 6.2.6 JTAG                             | 98  |

|   |            | 6.2.7 Power Supply                     | 99  |

|   |            | 6.2.8 Miscellaneous                    | 101 |

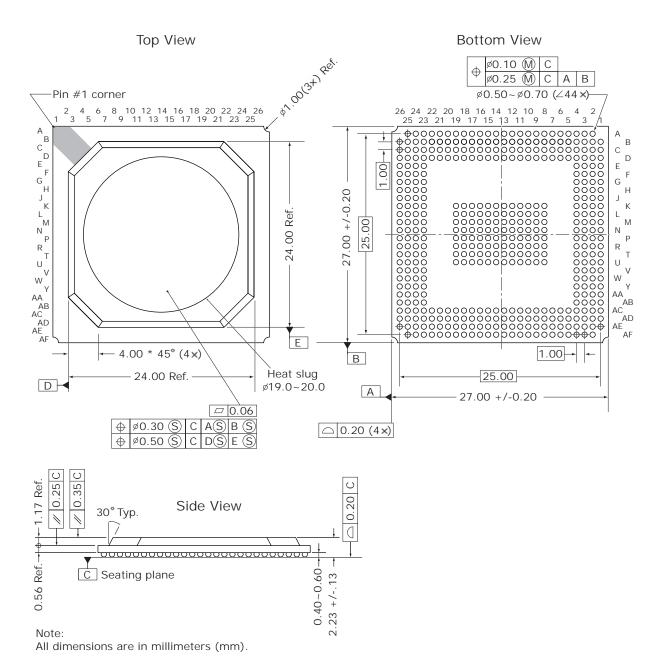

| 7 | Pac        | ckage Information                      | 102 |

| • |            |                                        |     |

|   | 7.1<br>7.2 | Package Drawing Thermal Specifications |     |

|   | 7.2<br>7.3 | Moisture Sensitivity                   |     |

|   | 1.3        | เพษารณา 6 ออกอเทิงแร่                  | 103 |

June 2006

| 8 | Des | 100                                        |     |

|---|-----|--------------------------------------------|-----|

|   | 8.1 | Remote Fault Status                        | 106 |

|   | 8.2 | ActiPHY Wake Timer Needs to be Set to '11' | 106 |

|   | 8.3 | DSP Optimization Script                    | 100 |

| 9 | Ord | lering Information                         | 108 |

June 2006 Page 6 of 108

# **Figures**

| Figure | 1.  | Typical Application                                     | 15 |

|--------|-----|---------------------------------------------------------|----|

| Figure | 2.  | High-level Block Diagram                                | 17 |

| Figure | 3.  | SerDes MAC Interface                                    | 20 |

| Figure | 4.  | SGMII MAC Interface                                     | 20 |

| Figure | 5.  | Cat5 Media Interface                                    | 21 |

| Figure | 6.  | Automatic Media Sense Block Diagram                     | 23 |

| Figure | 7.  | In-line Powered Ethernet Switch Diagram                 | 27 |

| Figure | 8.  | ActiPHY State Diagram                                   | 29 |

| Figure | 9.  | SMI Read Frame                                          | 30 |

| Figure | 10. | SMI Write Frame                                         | 31 |

| Figure | 11. | MDINT_n Configured as an Open-Drain (Active-low) Pin    | 32 |

| Figure | 12. | MDINT_n Configured as an Open-source (Active-high) Pin  | 32 |

| Figure | 13. | Far-end Loopback Diagram                                | 37 |

| Figure | 14. | Near-end Loopback Diagram                               | 37 |

| Figure | 15. | Connector Loopback Diagram                              | 38 |

| Figure | 16. | Test Access Port and Boundary Scan Architecture Diagram | 39 |

| Figure | 17. | Register Space Diagram                                  | 43 |

| Figure | 18. | EEPROM Read and Write Register Flow                     | 79 |

| Figure | 19. | JTAG Interface Timing                                   | 88 |

| Figure | 20. | SMI Interface Timing                                    | 89 |

| Figure | 21. | Reset Timing                                            | 90 |

| Figure | 22. | Serial LED Timing                                       | 90 |

| Figure | 23. | Pin Diagram, Left Side, Top                             | 92 |

| Figure | 24. | Pin Diagram, Right Side, Top                            | 93 |

| Figure | 25. | Package Drawing1                                        | 04 |

June 2006 Page 7 of 108

## **Tables**

| Table 1.  | Features and Benefits                                            | . 15 |

|-----------|------------------------------------------------------------------|------|

| Table 2.  | Operating Mode versus Speed                                      | . 18 |

| Table 3.  | AMS Media Preferences                                            | . 23 |

| Table 4.  | Supported MDI Pair Combinations                                  | . 25 |

| Table 5.  | LED Mode and Function Summary                                    | . 33 |

| Table 6.  | LED Serial Stream Order                                          | . 35 |

| Table 7.  | JTAG Device Identification Register Description                  | . 40 |

| Table 8.  | JTAG Interface Instruction Codes                                 | . 40 |

| Table 9.  | IEEE 802.3 Standard Registers                                    | . 44 |

| Table 10. | Main Registers                                                   |      |

| Table 11. | Mode Control, Address 0 (0x00)                                   |      |

| Table 12. | Mode Status, Address 1 (0x01)                                    | . 46 |

| Table 13. | Identifier 1, Address 2 (0x02)                                   | . 47 |

| Table 14. | Identifier 2, Address 3 (0x03)                                   | . 47 |

| Table 15. | Device Auto-Negotiation Advertisement, Address 4 (0x04)          | . 47 |

| Table 16. | Auto-Negotiation Link Partner Ability, Address 5 (0x05)          | . 48 |

| Table 17. | Auto-Negotiation Expansion, Address 6 (0x06)                     | . 48 |

| Table 18. | Auto-Negotiation Next Page Transmit, Address 7 (0x07)            | . 49 |

| Table 19. | Auto-Negotiation LP Next Page Receive, Address 8 (0x08)          | . 49 |

| Table 20. | 1000BASE-T Control, Address 9 (0x09)                             | . 50 |

| Table 21. | 1000BASE-T Status, Address 10 (0x0A)                             | . 50 |

| Table 22. | 1000BASE-T Status Extension 1, Address 15 (0x0F)                 | . 51 |

| Table 23. | 100BASE-TX Status Extension, Address 16 (0x10)                   | . 51 |

| Table 24. | 1000BASE-T Status Extension 2, Address 17 (0x11)                 |      |

| Table 25. | Bypass Control, Address 18 (0x12)                                |      |

| Table 26. | Extended Control and Status, Address 22 (0x16)                   | . 54 |

| Table 27. | Extended PHY Control 1, Address 23 (0x17)                        | . 55 |

| Table 28. | Extended PHY Control 2, Address 24 (0x18)                        | . 56 |

| Table 29. | Interrupt Mask, Address 25 (0x19)                                | . 57 |

| Table 30. | Interrupt Status, Address 26 (0x1A)                              | . 57 |

| Table 31. | MAC Auto-Negotiation Control and Status, Address 27 (0x1B)       | . 58 |

| Table 32. | Auxiliary Control and Status, Address 28 (0x1C)                  | . 59 |

| Table 33. | LED Mode Select, Address 29 (0x1D)                               | . 60 |

| Table 34. | Available LED Mode Settings                                      | . 61 |

| Table 35. | LED Behavior, Address 30 (0x1E)                                  | . 61 |

| Table 36. | Extended Registers Page Space                                    | . 63 |

| Table 37. | Extended Page Access, Address 31 (0x1F)                          | . 63 |

| Table 38. | SerDes Media Auto-Negotiation Control/Status, Address 16E (0x10) | . 64 |

| Table 39. | SerDes MAC Control, Address 17E (0x11)                           |      |

| Table 40. | CRC Good Counter, Address 18E (0x12)                             |      |

| Table 41. | SIGDET Control, Address 19E (0x13)                               |      |

| Table 42. | ActiPHY Control, Address 20E (0x14)                              |      |

| Table 43. | EEPROM Interface Status and Control, Address 21E (0x15)          |      |

| Table 44. | EEPROM Read or Write, Address 22E (0x16)                         |      |

| Table 45. | Extended PHY Control 4, Address 23E (0x17)                       | . 67 |

| Table 46. | VeriPHY Control Register 1, Address 24E (0x18)                   |      |

| Table 47. | VeriPHY Control Register 2, Address 25E (0x19)                   |      |

| Table 48. | VeriPHY Control Register 3, Address 26E (0x1A)                   |      |

|           |                                                                  |      |

June 2006 Page 8 of 108

| Table 49. | VeriPHY Control Register 3 Fault Codes                      | 69   |

|-----------|-------------------------------------------------------------|------|

| Table 50. | EPG Control Register 1, Address 29E (0x1D)                  |      |

| Table 51. | EPG Control Register 2, Address 30E (0x1E)                  |      |

| Table 52. | General-Purpose Registers Page Space                        |      |

| Table 53. | SIGDET Control, Address 13G (0x0D)                          |      |

| Table 54. | GPIO Input, Address 15G (0x0F)                              |      |

| Table 55. | GPIO Output, Address 16G (0x10)                             |      |

| Table 56. | GPIO Input/Output Configuration, Address 17G (0x11)         |      |

| Table 57. | 100BASE-FX Control, Address 18G (0x12)                      |      |

| Table 58. | CMODE Configuration Pins and Device Functions               |      |

| Table 59. | Device Functions and Associated CMODE Pins                  |      |

| Table 60. | CMODE Resistor Values and Resultant Bit Settings            |      |

| Table 61. | EEPROM Configuration Contents                               |      |

| Table 62. | DC Characteristics for Pins Referenced to VDDIO at 3.3 V    |      |

| Table 63. | DC Characteristics for Pins Referenced to VDDIO at 2.5 V    | . 82 |

| Table 64. | DC Characteristics for Pins Referenced to VDDIO at 1.8 V    |      |

| Table 65. | DC Characteristics for Pins Referenced to VDD33 at 3.30 V   |      |

| Table 66. | DC Characteristics for MAC_RDP/N_n and SER_DOP/N_n Pins     |      |

| Table 67. | DC Characteristics for MAC_TDP/N_n and SER_DIP/N_n Pins     | 84   |

| Table 68. | DC Characteristics for LED[3:0]_n Pins                      |      |

| Table 69. | DC Characteristics for JTAG Pins                            |      |

| Table 70. | Typical Current Consumption                                 |      |

| Table 71. | Current Consumption in SerDes/SGMII to 1000BASE-X Mode      | 86   |

| Table 72. | AC Characteristics for REFCLK Input                         | . 86 |

| Table 73. | AC Characteristics for REFCLK Input with 25 MHz Clock Input |      |

| Table 74. | AC Characteristics for the CLKOUT Pin                       | . 87 |

| Table 75. | AC Characteristics for the JTAG Interface                   |      |

| Table 76. | AC Characteristics for the SMI Interface                    | . 88 |

| Table 77. | AC Characteristics for Device Reset                         |      |

| Table 78. | AC Characteristics for Serial LEDs                          | . 90 |

| Table 79. | Recommended Operating Conditions                            | . 91 |

| Table 80. | Stress Ratings                                              |      |

| Table 81. | SerDes MAC Interface Pins                                   |      |

| Table 82. | SerDes Media Interface Pins                                 |      |

| Table 83. | GPIO and SIGDET Pins                                        |      |

| Table 84. | Twisted Pair Interface Pins                                 |      |

| Table 85. | SMI Pins                                                    | . 98 |

| Table 86. | JTAG Pins                                                   |      |

| Table 87. | Power Supply Pins                                           |      |

| Table 88. | Power Supply and Associated Function Pins                   |      |

| Table 89. | Miscellaneous Pins                                          |      |

| Table 90. | Thermal Resistances                                         | 105  |

| Table 91  | Ordering Information                                        | 108  |

June 2006 Page 9 of 108

# **Revision History**

This section describes the changes that were implemented in this document. The changes are listed by revision, starting with the most current publication.

### **Revision 4.0**

Revision 4.0 of this datasheet was published in June 2006. The following is a summary of the changes implemented in the datasheet.

- In the DC characteristics for VDDIO at 3.3 V, the output leakage ( $I_{OLEAK}$ ) was changed to match the same values as the input leakage ( $I_{ILEAK}$ ) with the same condition (internal resistor included). Specifically, the values were changed from  $-10~\mu A$  minimum and  $10~\mu A$  maximum to  $-42~\mu A$  minimum and  $42~\mu A$  maximum.

- In the DC characteristics for VDDIO at 2.5 V, the output leakage ( $I_{OLEAK}$ ) was changed to match the same values as the input leakage ( $I_{ILEAK}$ ) with the same condition (internal resistor included). Specifically, the values were changed from  $-10~\mu A$  minimum and  $10~\mu A$  maximum to  $-32~\mu A$  minimum and  $32~\mu A$  maximum.

- In the DC characteristics for VDDIO at 1.8 V, the output leakage ( $I_{OLEAK}$ ) was changed to match the same values as the input leakage ( $I_{ILEAK}$ ) with the same condition (internal resistor included). Specifically, the values were changed from  $-10~\mu A$  minimum and  $10~\mu A$  maximum to  $-23~\mu A$  minimum and  $23~\mu A$  maximum.

- In the DC characteristics for VDDIO at 1.8 V, for the output high and low voltage parameters, new conditions were added to correlate with the output high and low current drive strength. The output high current drive strength parameter was updated from 1.0 mA to 4.0 mA maximum. The output low current drive strength parameter was updated from –1.0 mA to –4.0 mA. For more information, see Table 64, page 82.

- In the DC characteristics for VDD33 at 3.30 V, the output leakage ( $I_{OLEAK}$ ) was changed to match the same values as the input leakage ( $I_{ILEAK}$ ) with the same condition (internal resistor included). Specifically, the values were changed from  $-10~\mu A$  minimum and  $10~\mu A$  maximum to  $-42~\mu A$  minimum and  $42~\mu A$  maximum.

- For the MAC and SerDes DC output characteristics, the output differential voltage was updated from 350 mV minimum, 1200 mV typical, and 1400 mV maximum to 700 mV minimum, 1000 mV typical, and 1200 mV maximum. The output rise and fall time was updated from 300 ps maximum to 200 ps maximum, and the typical value 120 ps was added. Random and deterministic jitter specifications (including footnotes) were removed and replaced with the total jitter specification. The total receive jitter tolerance parameter was added. For more information about these characteristics, see Table 66, page 83.

- In the DC characteristics for LED pins, a qualifier in the introductory paragraph was removed stating that these specifications are valid only when a voltage range of 1.3 V to 2.3 V is applied to the LED pins. For the output high and low voltage parameters, new conditions were added to correlate with the output high and low current drive strength. The output high current drive strength parameter was updated from 4.0 mA to 8.0 mA maximum. The output low current drive strength parameter was updated from -4.0 mA to -8.0 mA minimum. For more information, see Table 68, page 84.

June 2006 Page 10 of 108

- In the DC characteristics for JTAG pins, the output leakage (I<sub>OLEAK</sub>) was changed to match the same values as the input leakage (I<sub>ILEAK</sub>) with the same condition (internal resistor included). Specifically, the values were changed from

μA minimum and 10 μA maximum to -42 μA minimum and 42 μA maximum.

- For the current consumption specifications, the power consumption parameter was renamed from "worst case" to "full traffic conditions" to be technically accurate. The power consumption maximum was updated from TBD to 5.91 W in typical consumption mode and, for the SerDes/SGMII to 1000BASE-X mode, the maximum was updated from TBD to 1.05 W. Also, in the introductory text, a reference to 64-bit was corrected to 64-byte. For more information about current consumption, see Table 70, page 85 and Table 71, page 86.

- For the AC clock output characteristics, the total jitter values were changed from TBD to 217 ps typical and 491 ps maximum.

- In the stress ratings, the power supply voltage parameter was removed because it was redundant. For the DC input voltage on the VDD12 and VDD12A supply pins, the maximum was updated from 1.5 V to 1.4 V. The electrostatic discharge voltage was specified as meeting a Class 2 rating. For more information about the Class 2 rating, see Table 80, page 91.

- For the serial management interface (SMI) pins, it was clarified that EECLK and EEDAT are referenced to VDD33, not VDDIO.

### **Revision 2.2**

Revision 2.2 of this datasheet was published in March 2006. The following is a summary of the changes implemented in the datasheet:

#### **Introduction and Overview**

- The VSC8558 device now supports the 100BASE-FX communication speed.

- In the high-level block diagram, representation of the XTAL pin was corrected from "XTAL 1/2" to "XTAL1" and "XTAL2." Omission of the "1000" speed was corrected.

#### **Functional Descriptions**

- The figures for the SerDes MAC interface and SGMII MAC interface were clarified to show that the TDP and TDN pins are capacitors in series within the VSC8558 device.

- In the Cat5 Media Interface figure, the pinout order for the RJ45 was corrected.

- The bandwidth provided by the SerDes block was previously stated to be full-duplex. It can also be half-duplex.

- New information was added about how to manually force the device to use MDI/MDI-X.

- For better document organization, the power-over-Ethernet (PoE) information now has its own heading.

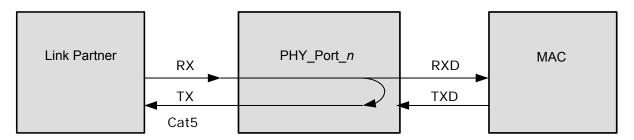

- In the far-end loopback diagram, the loopback arrow for the PHY port was redrawn closer to the MAC to more accurately portray the data path.

June 2006 Page 11 of 108

• For the JTAG IDCODE binary values, the device version number was corrected from 0000 to 0001. The model number was corrected to be 8558 (in binary).

#### **Configuration (Registers)**

- In the mode status register (address 1), the descriptions for bits 14:13 were corrected from 100BASE-X to 100BASE-TX.

- In the identifier 2 register (address 3), which enables device identification, the default for bits 9:4 was modified from 0010000 to 111000. The default for bits 3:0 was modified from 0000 to 0001.

- In the extended PHY control 1 register (address 23), missing bit information was added for the AMS preference parameter (bit 11), the media operating mode parameter (bits 10:8), and the force AMS override parameter (bits 7:6).

- In the interrupt mask register (address 25), missing bit information was added for the AMS media changed mask parameter (bit 4).

- In the interrupt status register (address 26), missing bit information was added for the AMS media changed status parameter (bit 4).

- In the LED mode select register (address 29), the missing LED mode settings for fiber\_link/activity and fiber\_activity were added.

- In the LED behavior register (address 30), missing bit information was added for the copper and fiber LED combine disable parameter (bit 15) and the activity output select parameter (bit 14).

- The missing SerDes media control register (address 16E) was added.

- In the SerDes MAC control register (address 17E), missing bit information was added for the SerDes media output swing control parameter (bits 7:5).

- The address for the CRC good counter register was corrected from 31E (0x1F) to 18E (0x12).

- The missing SIGDET control register (address 19E) was added.

- In the ActiPHY<sup>™</sup> control register (address 20E), bit 15, formerly reserved, is now used to disable the carrier extension. Missing bit information was added for the media mode status parameter (bits 7:6).

- A new SIGDET control register (address 13G) was added. It configures GPIO pins

7:0 to be either SIGDET pins for each port or GPIO pins.

- Information about the CMODE pins was expanded and corrected, including missing information for configuring media interface and SIGDET polarity.

#### **Electrical Specifications**

- In the DC characteristics for pins referenced to VDDIO at 1.8 V, the output low current drive strength parameter changed from maximum 4.5 mA to 1.0 mA. The output high current drive strength parameter changed from minimum –4.5 mA to –1.0 mA.

- In the DC characteristics for the MAC and SerDes output pins, the values for the output common mode voltage parameter were converted from volts to millivolts. The maximum for this parameter was modified from 600 mV to 610 mV.

June 2006 Page 12 of 108

- In the DC characteristics for the MAC and SerDes input pins, the minimum value for the peak-to-peak input differential voltage parameter was modified from 100 mV to 120 mV.

- In the DC characteristics for LED[3:0]\_n pins, the output low current drive strength parameter changed from maximum 8.0 mA to 4.0 mA. The output high current drive strength parameter changed from minimum –8.0 mA to –4.0 mA.

- For the current consumption specifications, information was removed explaining how to calculate the current consumption when using ActiPHY. This information is not required. Additional current consumption values were added, based on all eight ports running in SerDes/SGMII to 1000BASE-X mode.

- For the reference clock input specifications using the 25 MHz crystal clock input option, the maximum crystal equivalent series resistance was corrected from 300  $\Omega$  to 30  $\Omega$ .

- The device reset specifications were thoroughly updated to match the device.

#### **Pin Descriptions**

- For better organization, the GPIO and SIGDET pins are now listed in their own section; they were grouped with the SerDes MAC interface pins in the prior revision.

- In the list of JTAG pins, in the description for the NTRST (T3) pin, ground was incorrectly referred to as VSSIO; it is now corrected to VSS.

- In the description for the miscellaneous pins REF\_FILT\_A and REF\_FILT\_B, the external connection for these pins was corrected from a 2 k $\Omega$  resistor to 1  $\mu$ F capacitor.

- In the list of miscellaneous pins, several pins mistakenly listed as no connect (NC) were removed, because they are actually used for the SerDes media interface.

#### **Errata**

New errata were added, and all prior errata were removed because they no longer apply to this revision.

## **Revision 2.1**

Revision 2.1 of this datasheet was published in January 2006. The following is a summary of the changes implemented in the datasheet:

- Missing pin descriptions were replaced for the SerDes media interface pins.

- The body thickness dimensions were corrected in the package drawing.

### Revision 2.0

Revision 2.0 of this datasheet was published in September 2005. This was the first publication of the document.

June 2006 Page 13 of 108

# 1 Introduction

This document consists of descriptions and specifications for both functional and physical aspects of the VSC8558 Octal 10/100/1000BASE-T PHY with Dual 1.25 Gbps SerDes.

In addition to the datasheet, Vitesse maintains an extensive part-specific library of support and collateral materials that you may find useful in developing your own product. Depending upon the Vitesse device, this library may include:

- Software Development Kits with sample commands and scripts

- Reference designs showing the Vitesse device built in to applications in ways intended to exploit its relative strengths

- Presentations highlighting the operational features and specifications of the device to assist in developing your own product road map

- Input/Output Buffer Information specification (IBIS) models to help you create and support the interfaces available on the particular Vitesse product

- Application notes that provide detailed descriptions of the use of the particular Vitesse product to solve real-world problems

- White papers published by industry experts that provide ancillary and background information useful in developing products that take full advantage of Vitesse product designs and capabilities

- User guides that describe specific techniques for interfacing to the particular Vitesse products

Visit and register as a user on the Vitesse Web site to keep abreast of the latest innovations from research and development teams and the most current product and application documentation. The address of the Vitesse Web site is www.vitesse.com.

June 2006 Page 14 of 108

# 2 Product Overview

The VSC8558 device is a low-power, octal Gigabit Ethernet transceiver with dual, fully integrated 1.25 Gbps SerDes interfaces. It is designed for use in applications such as multiport switches and routers, where its compact ball grid array (BGA) packaging, low electromagnetic interference (EMI) line driver, and integrated line side termination resistors conserve both power and PC board space. Using the VSC8558 device in your design makes it possible to lower the component count of your PC board, sub-assembly, or device without sacrificing chip-centric capabilities or utility; which in turn can make it less expensive to produce and more cost-effective to deploy.

Vitesse's mixed signal and digital signal processing (DSP) architecture—a key operational feature of the VSC8558 device—assures robust performance even under less-than-favorable environmental conditions. It supports both half-duplex and full-duplex 10BASE-T, 100BASE-TX, and 1000BASE-T communication speeds over Category 5 (Cat5) unshielded twisted pair (UTP) cable at distances greater than 140 m, displaying excellent tolerance to NEXT, FEXT, echo, and other types of ambient environment and system electronic noise. This device also supports 100BASE-FX and 1000BASE-X to connect to fiber modules, such as GBICs and SFPs.

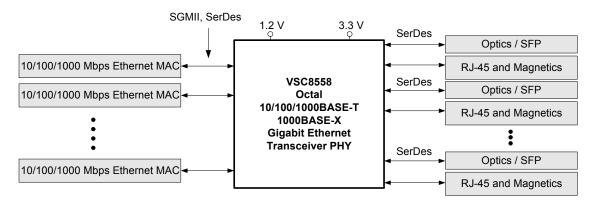

The following illustration shows a high-level, generic view of a VSC8558 application.

Figure 1. Typical Application

### 2.1 Features and Benefits

This section lists key aspects of the VSC8558 device functionality and design that distinguish it from similar products.

**Table 1.** Features and Benefits

| Feature                                                                       | Benefit                                                                                                                         |

|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 650 mW per port power consumption (when configured for 1000BASE-T operation)  | Lowers system cost by eliminating the need for extra heat-dissipating and power-processing components; simplifies system design |

| 27 mm x 27 mm, 444-pin BGA packaging                                          | Facilitates single row, high port density switch designs                                                                        |

| Patented, low EMI line driver with integrated line side termination resistors | Eliminates the need for as many as 384 passive components in 48-port switch applications                                        |

June 2006 Page 15 of 108

**Table 1.** Features and Benefits (continued)

| Feature                                                                                                                                                                                                                         | Benefit                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auto-Media Sense™ capability configurable per-port                                                                                                                                                                              | Detects and automatically configures port for operation with copper or fiber media; auto-enables 10/100/1000BASE-T fixed media ports, 1000BASE-X SFPs, 1000BASE-T SFPs, triple-speed SFPs, or backplanes |

| Dual, high-performance, 1.25 Gbps SerDes                                                                                                                                                                                        | Maximizes receive jitter tolerance and minimizes transmit jitter (in comparison to single SerDes architectures)                                                                                          |

| Compliance with IEEE standard 802.3 (10BASE-T, 100BASE-TX, 1000BASE-T, 1000BASE-X, 100BASE-FX)                                                                                                                                  | Ensures seamless deployment in devices throughout existing copper networks while maintaining excellent tolerance to ambient electronic noise and any substandard cabling                                 |

| Support for frame sizes greater than 16 kilobytes at all device throughput settings, programmable synchronization FIFO buffers                                                                                                  | Provides for maximum Jumbo frame sizes on custom SANs and LANs                                                                                                                                           |

| Four integrated and programmable LED direct drivers per port, on-chip filtering and support for bi-color LEDs                                                                                                                   | Eliminates the need for external components, lowers EMI generation, lowers design cost                                                                                                                   |

| Multiple built-in testing facilities, including near end, far end, and connector loopback; Ethernet packet generator with CRC error counter                                                                                     | Lowers system or device development and deployment costs; decreases time-to-market                                                                                                                       |

| Serial LED interface option                                                                                                                                                                                                     | Enables design flexibility                                                                                                                                                                               |

| Support for the CISCO specification for serial gigabit media-independent interface version 1.7 (SGMII (v1.7), for 1000BASE-X MACs, for IEEE standard 1149.1-1999 JTAG boundary scan, and for IEEE standard 1149.6 AC-JTAG scan. | Saves manufacturing and quality assurance costs                                                                                                                                                          |

| VeriPHY™ cable diagnostics                                                                                                                                                                                                      | Enables system managers to simplify deployment and improve Gigabit Ethernet network performance                                                                                                          |

June 2006 Page 16 of 108

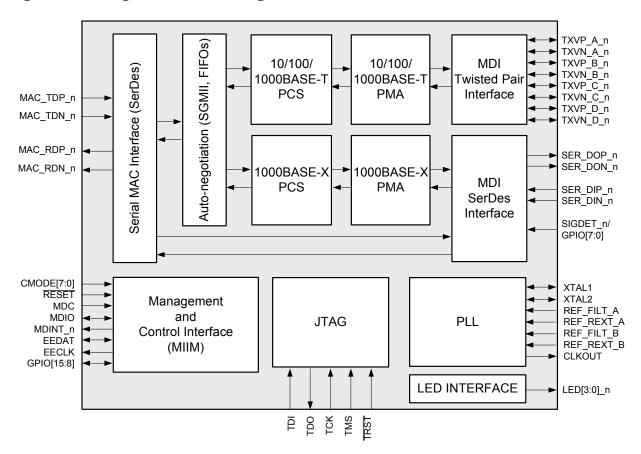

# 2.2 Block Diagram

The following illustration shows the primary functional blocks of the VSC8558 device.

Figure 2. High-level Block Diagram

June 2006 Page 17 of 108

# 3 Functional Descriptions

This section provides detailed information about how the VSC8558 device works, what configurations and operational features are available, and how to test its function. It includes descriptions of the various device interfaces and how to set them up.

With the information in this section, you can better determine which device setup parameters you must access to configure the VSC8558 device to work in your application. There are three ways to configure the VSC8558 device. You can access and set its internal memory registers, you can use a combination of the device CMODE pins and its registers, or you can configure and connect an external EEPROM to execute a configuration sequence upon system startup.

For information about VSC8558 device registers, see "Registers," page 42.

For information about the device CMODE pins, see "CMODE," page 73.

For information about using an EEPROM with the VSC8558 device, see "EEPROM," page 77.

# 3.1 Operating Modes

With respect to its function in your design, the VSC8558 device acts as the interface between a media access controller (MAC) and either Category 5 (Cat5) media, 100BASE-FX fiber media, or 1000BASE-X fiber media. Or, the VSC8558 device can act as a MAC-to-MAC pass-through device used to take advantage of auto-negotiation.

Depending upon the speed of data throughput required in your application, the MAC may be either a SerDes or an SGMII device, and can also be configured to support twisted pair Cat5 cabling, 1000BASE-X fiber optic cabling, or copper small form factor pluggable (SFP) devices.

The operating mode you choose when setting up the VSC8558 device is a function of which type of MAC is to be connected, which data throughput speeds are required in the application, and the type of Cat5 media support required. The following table shows the relationship between the VSC8558 device operating mode, the data throughput speed between the Vitesse device and the connected MAC, and the type of Cat5 media and device interface functions supported.

Table 2. Operating Mode versus Speed

| VSC8558 Mode                               | 10/100/1000<br>BASE-T<br>Support | 1000BASE-X<br>Fiber Optic<br>Support | 100BASE-FX<br>Support | 10/100/100<br>0BASE-T<br>Copper SFP<br>Support |

|--------------------------------------------|----------------------------------|--------------------------------------|-----------------------|------------------------------------------------|

| SerDes MAC-to-Cat5 Link Partner            | 1000BASE-T<br>Only               |                                      |                       |                                                |

| SGMII MAC-to-Cat5 Link Partner             | Yes                              |                                      |                       |                                                |

| SerDes MAC-to-SerDes with Auto-Negotiation |                                  | Yes                                  |                       | 1000BASE-T<br>only                             |

| SGMII MAC-to-SerDes with Auto-Negotiation  |                                  | Yes                                  |                       | 1000BASE-T<br>only                             |

June 2006 Page 18 of 108

Table 2. Operating Mode versus Speed (continued)

| VSC8558 Mode                                                       | 10/100/1000<br>BASE-T<br>Support | 1000BASE-X<br>Fiber Optic<br>Support | 100BASE-FX<br>Support | 10/100/100<br>OBASE-T<br>Copper SFP<br>Support |

|--------------------------------------------------------------------|----------------------------------|--------------------------------------|-----------------------|------------------------------------------------|

| SerDes MAC-to-SerDes with Pass-through                             |                                  | Yes <sup>(1)</sup>                   |                       | 1000BASE-T<br>only <sup>(1)</sup>              |

| SGMII MAC-to-SGMII with Pass-through                               |                                  | Yes <sup>(1)</sup>                   |                       | Yes <sup>(1)</sup>                             |

| SGMII MAC-to-100BASE-FX                                            |                                  |                                      | Yes <sup>(2)</sup>    |                                                |

| SerDes MAC with Automatic Media Sensing (AMS) and Auto Negotiation | 1000BASE-T<br>Only               | Yes                                  |                       |                                                |

| SGMII MAC with AMS and Auto Negotiation                            | Yes                              | Yes                                  |                       |                                                |

| SerDes MAC with AMS and Pass-through                               | 1000BASE-T<br>Only               | Yes <sup>(1)</sup>                   |                       | 1000BASE-T<br>only <sup>(1)</sup>              |

| SGMII MAC with AMS and Pass-through                                | Yes                              | Yes <sup>(1)</sup>                   |                       | Yes <sup>(1)</sup>                             |

<sup>1.</sup> The MAC used must be capable of supporting this media.

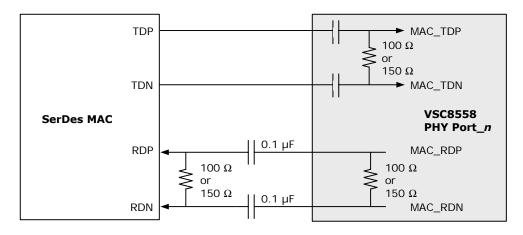

#### 3.1.1 SerDes MAC-to-Cat5 Mode MAC Interface

When connected to a SerDes MAC, the VSC8558 device provides data throughput at a rate of 1000 Mbps only; 10 Mbps and 100 Mbps rates are not supported. So to configure the device to operate in this mode, select the 1000BASE-T only setting in the registers, using the CMODE pin, or in the external EEPROM startup sequence.

For information about using the device registers to configure the VSC8558 device to operate in SerDes MAC-to-Cat5 mode, see "Mode Control," page 45.

For information about the device CMODE pins, see "CMODE," page 73.

For information about using an EEPROM with the VSC8558 device, see "EEPROM," page 77.

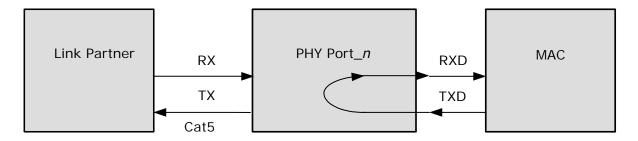

The following illustration shows a typical connection of the VSC8558 device to a SerDes MAC.

June 2006 Page 19 of 108

<sup>2.</sup> Support for this communication speed is facilitated by using the connections on the Cat5 copper pins. For more information about this mode, see "SGMII MAC-to-100BASE-FX Mode," page 22.

Figure 3. SerDes MAC Interface

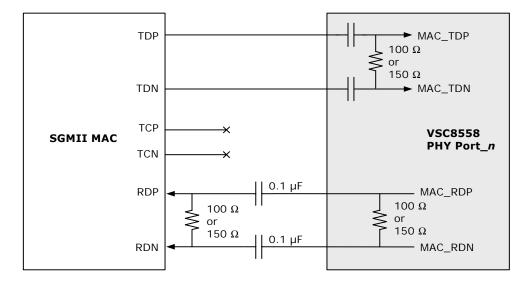

### 3.1.2 SGMII MAC-to-Cat5 Mode MAC Interface

When configured to detect and switch between 10BASE-T, 100BASE-T, and 1000BASE-T data rates, the VSC8558 device can be connected to an SGMII-compatible MAC.

For information about using the device registers to configure the VSC8558 device to operate in SerDes MAC-to-Cat5 Mode, see "Mode Control," page 45.

For information about the device CMODE pins, see "CMODE," page 73.

For information about using an EEPROM with the VSC8558 device, see "EEPROM," page 77.

The following illustration shows a typical connection of the VSC8558 device to an SGMII-compatible MAC.

Figure 4. SGMII MAC Interface

June 2006 Page 20 of 108

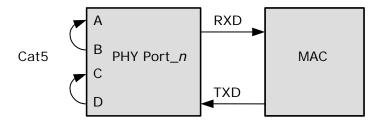

#### 3.1.3 All Modes Cat5 Media Interface

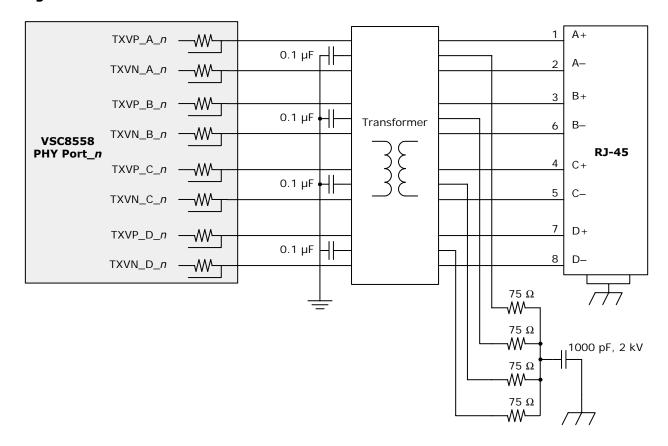

The VSC8558 device twisted pair interface is compliant with the IEEE standard 802.3-2000. Unlike many other gigabit PHYs, the VSC8558 device uses fully integrated, passive components (required to connect the PHY's Cat5 interface to an external 1:1 transformer). The following illustration shows the connections.

Figure 5. Cat5 Media Interface

# 3.2 SerDes Media Interface

The VSC8558 device SerDes Media Interface performs data serialization and deserialization functions using an integrated SerDes block. The interface operates at 1.25 Gbps speed, providing full-duplex and half-duplex 1000 Mbps bandwidth that can connect directly to 1000BASE-X-compliant optical devices as well as to 10/100/1000BASE-T copper SFP devices. The interface can be operated in two SerDes modes:

- SerDes with media interface PCS auto-negotiation capability

- · SerDes with pass-through

SerDes with media interface PCS auto-negotiation capability supports IEEE standard 802.3, clauses 36 and 37, which describes fiber auto-negotiation. In this mode, control and status of the SerDes media is displayed in the VSC8558 device registers 0 through

June 2006 Page 21 of 108

15 in a manner similar to what is described in the IEEE standard 802.3, clause 28. In this mode, connected copper SFPs can only operate at 1000BASE-T speed. A link in this mode is established by means of auto-negotiation (enabled or disabled) between the PHY and the link partner.

For information about how the VSC8558 LEDs operate in this mode, see "LED Behavior," page 34.

SerDes with Pass-Through Mode is a feature that links a fiber module or copper SFP directly to the SerDes interface of the MAC through the VSC8558 device. For example, to support 10/100/1000 copper SFPs, the MAC must be able to operate in SGMII Mode. Because the MAC controls the establishment of the link, PHY registers 0 through 15 and the PHY LEDs do not indicate link information when in SerDes Pass-Through Mode. In this case, the only supported LED operation is the force on and force off modes. A pass-through link is established when the SIGDET pin is asserted.

### 3.3 SGMII MAC-to-100BASE-FX Mode

The VSC8558 can support the 100BASE-FX communication speed to connect to fiber modules, such as GBICs and SFPs. This capability is facilitated by using the connections on the Cat5 copper pins.

This feature is enabled using register 18G. In this mode, the SIGDET pin is not used. Also relevant in this mode are the Link100 LED and the Link LED, as well as the device auto-negotiation advertisement register (address 4).

# 3.4 Automatic Media-Sense (AMS) Interface Mode

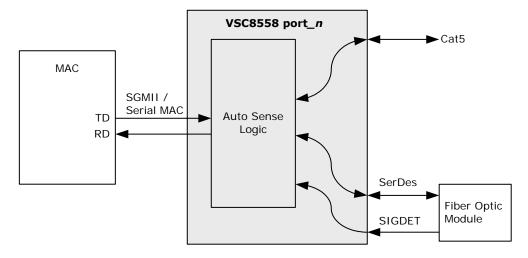

This mode can automatically set the media interface to Cat5 or to SerDes interface modes automatically. The active media mode chosen is based on the AMS preferences set in the device register 23, bit 11.

The following illustration shows a block diagram of the VSC8558 device AMS functionality.

June 2006 Page 22 of 108

Figure 6. Automatic Media Sense Block Diagram

With respect to the SerDes or Cat5 media preference settings, when both media interfaces attempt to establish a link, the preferred media interface overrides a link-up of the non-preferred media interface. For example, when the preference is set for SerDes Mode but not linked and if Cat5 media establishes a link, Cat5 becomes the active media interface. After the SerDes media interface establishes a link however, the Cat5 interface drops its link because SerDes media is the preferred setting. In this scenario, the SerDes preference determines the active media source until the SerDes link is lost. Cat5 media cannot link-up unless a SerDes media link is not established.

The following table lists the available AMS preferences.

Table 3. AMS Media Preferences

|                       | Cat5 Linked,        |                                   | Cat5 Linked,<br>SerDes | SerDes Linked,           | Both Cat5 and             |

|-----------------------|---------------------|-----------------------------------|------------------------|--------------------------|---------------------------|

| Preference<br>Setting | Fiber Not<br>Linked | SerDes Linked,<br>Cat5 Not Linked | Attempts to<br>Link    | Cat5 Attempts<br>to Link | SerDes Attempt<br>to Link |

| SerDes                | Cat5                | SerDes                            | SerDes                 | SerDes                   | SerDes                    |

| Cat5                  | Cat5                | SerDes                            | Cat5                   | Cat5                     | Cat5                      |

The status of the media mode selected by the AMS can be read from device register 20E, bits 7:6. It indicates whether copper media, SerDes media, or no media has been selected.

Each PHY has two auto-media sense modes. The difference between the modes is based on the SerDes media modes:

- · SerDes with auto-negotiation

- · SerDes with pass-through

For more information about SerDes media mode functionality with AMS enabled, see "SerDes Media Interface," page 21.

For AMS with SerDes auto-negotiation, the status and control of both the Cat5 and the SerDes media can be effected using registers 0 through 15. For AMS with SerDes

June 2006 Page 23 of 108

pass-through, only the Cat5 interface can have its interface control and status monitored. The SerDes media must then be controlled and monitored within the MAC.

## 3.5 Cat5 Auto-Negotiation

The VSC8558 device supports twisted pair auto-negotiation as defined by clause 28 of the IEEE standard 802.3-2000.

The auto-negotiation process consists of the evaluation of the advertised capabilities of the PHY and its link partner to determine the best possible operating mode; throughput speed, duplex configuration, and master or slave operating modes in the case of 1000BASE-T setups. Auto-negotiation also allows a connected MAC to communicate with its link partner MAC through the VSC8558 device using optional "next pages," setting attributes that may not otherwise be defined by the IEEE standard.

In installations where the Cat5 link partner does not support auto-negotiation, the VSC8558 automatically switches to use parallel detection to select the appropriate link speed.

Clearing VSC8558 device register 0, bit 12 disables clause 28 twisted-pair auto-negotiation. If auto-negotiation is disabled, the state of register bits 0.6, 0.13, and 0.8 determine the device operating speed and duplex mode. For more information about configuring auto-negotiation, see "IEEE Standard and Main Registers," page 44.

# 3.6 Manual MDI/MDI-X Setting

As an alternative to Auto MDI/MDI-X detection, you can force the PHY to be MDI or MDI-X by using the following scripts.

#### Format:

```

Phywrite ( register(dec), data(hex) )

Phywritemask ( register(dec), data(hex), mask(hex) )

```

#### To force MDI:

```

Phywrite ( 31, 0x2A30 )

Phywritemask ( 5, 0x0010, 0x0018 )

Phywrite ( 31, 0x0000 )

```

#### To force MDI-X:

```

Phywrite ( 31, 0x2A30 )

Phywritemask ( 5, 0x0018, 0x0018 )

Phywrite ( 31, 0x0000 )

```

#### To resume MDI/MDI-X setting based on register 18, bits 7 and 5:

```

Phywrite ( 31, 0x2A30 )

```

June 2006 Page 24 of 108

```

Phywritemask ( 5, 0x0000, 0x0018 )

Phywrite ( 31, 0x0000 )

```

# 3.7 Automatic Crossover and Polarity Detection

For trouble-free configuration and management of Ethernet links, the VSC8558 device includes a robust automatic, media-dependent and crossed media-dependent detection feature, Auto MDI/MDI-X, in all of its three available speeds (10BASE-T, 100BASE-T, and 1000BASE-T). The function is fully compliant with clause 40 of the IEEE standard 802.3-2002.

Additionally, the device detects and corrects polarity errors on all MDI pairs—a useful capability that exceeds the requirements of the standard.

Both Auto MDI/MDI-X detection and Polarity Correction are enabled in the device by default. You can change the default settings using device register bits 18.5:4. Status bits for each of these functions are located in register 28.

The VSC8558 device's automatic MDI/MDI-X algorithm will successfully detect, correct, and operate with any of the MDI wiring pair combinations listed in the following table.

#### **Table 4.** Supported MDI Pair Combinations

| RJ-45 Pin Pairings |      |      |      |                                             |

|--------------------|------|------|------|---------------------------------------------|

| 1, 2               | 3, 6 | 4, 5 | 7, 8 | Mode                                        |

| A                  | В    | С    | D    | Normal MDI                                  |

| В                  | А    | D    | С    | Normal MDI-X                                |

| A                  | В    | D    | С    | Normal MDI with pair swap on C and D pair   |

| В                  | А    | С    | D    | Normal MDI-X with pair swap on C and D pair |

**Note** The VSC8558 device can be configured to perform Auto MDI/MDI-X even when its Auto-negotiation feature is disabled (setting register 0.12 to 0) and the link is forced into 10/100 speeds. To enable this feature, set register 18.7 to 0.

# 3.8 Link Speed Downshift

For operation in cabling environments that are incompatible with 1000BASE-T, the VSC8558 device provides an automatic link speed "downshift" option. When enabled, the device automatically changes its 1000BASE-T auto-negotiation advertisement to the next slower speed after a set number of failed attempts at 1000BASE-T.

This is useful in setting up in networks using older cable installations that may include only pairs A and B and not pairs C and D.

You can configure and monitor link speed downshifting using register bits 20E.4:1. For more information, see "Extended PHY Control Set 1," page 55.

June 2006 Page 25 of 108

### 3.9 Transformer-less Ethernet

The Cat5 media interface supports 10/100/1000BT Ethernet for backplane applications such as those specified by the PICMG<sup>™</sup> 2.16 and ATCA<sup>™</sup> 3.0 specifications for eight-pin channels. With proper AC coupling, the typical Cat5 transformer can be removed and replaced with capacitors. For more information, see *Transformer-less Ethernet Concept and Applications*. This application note is available on the Vitesse Web site at www.vitesse.com.

### 3.10 Ethernet In-line Powered Devices

The VSC8558 device can detect legacy in-line powered devices in Ethernet network applications. Its in-line powered detection capability can be part of a system that allows for IP-phone and other devices such as wireless access points to receive power directly from their Ethernet cable, similar to office digital phones receiving power from a Private Branch Exchange (PBX) office switch over the telephone cabling. This can eliminate the need for an IP-phone to have an external power supply. It also enables the inline powered device to remain active during a power outage (assuming the Ethernet switch is connected to an uninterrupted power supply, battery, back-up power generator, or some other uninterruptible power source).

For more information about legacy in-line powered device detection, visit the Cisco Web site at www.cisco.com.

The following illustration shows an example of this type of application.

June 2006 Page 26 of 108

Gigabit Switch Processor Control SMI SGMII Interface In-line, VSC8558\_0 VSC8558\_1 VSC8558\_n Power-Over-Ethernet (PoE) Power Supply Transformer Transformer Transformer **RJ-45 RJ-45** RJ-45 I/F I/F I/F Cat5 Link Link Link Partner Partner Partner

Figure 7. In-line Powered Ethernet Switch Diagram

The following procedure describes the process that an Ethernet switch must perform in order to process in-line power requests made by a link partner (LP) that is, in turn, capable of receiving in-line power.

- 1. Enable the in-line powered device detection mode on each VSC8558 PHY using its serial management interface. Set register bit 23E.10 to 1.

- 2. Ensure that the VSC8558 device Auto-Negotiation Enable bit (register 0.12) is also set to 1. In the application, the device sends a special Fast Link Pulse (FLP) signal to the LP. Reading register bit 23E.9:8 will return 00 during the search for devices that require PoE.

- 3. The VSC8558 PHY monitors its inputs for the FLP signal looped back by the LP. An LP capable of receiving PoE will loopback the FLP pulses when it is in a powered-down state. This is reported when VSC8558 device register bit 23E.9:8 reads back 01. It can also be verified as an in-line power detection interrupt by reading VSC8558 device register bit 26.9, which should be a 1, and which will subsequently be cleared and the interrupt de-asserted after the read.

If an LP device does not loop back the FLP after a specific time, VSC8558 device register bit 23E.9:8 automatically resets to 10.

June 2006 Page 27 of 108

- 4. If the VSC8558 PHY reports that the LP needs PoE, the Ethernet switch must enable in-line power on this port, externally of the PHY.

- 5. The PHY automatically disables in-line powered device detection if the VSC8558 device register bit 23E.9:8 automatically resets to 10, and then automatically changes to its normal auto-negotiation process. A link is then auto-negotiated and established when the link status bit is set (register bit 1.2 is set to 1).

- 6. In the event of a link failure (indicated when VSC8558 device register bit 1.2 reads 0), the in-line power should be disabled to the in-line powered device external to the PHY. The VSC8558 PHY disables its normal auto-negotiation process and re-enables its in-line powered device detection mode.

# **3.11 802.3af PoE Support**

The VSC8558 device is also compatible with switch designs that are intended for use in systems that supply power to Data Terminal Equipment (DTE) by means of the MDI or twisted pair cable, as described in clause 33 of the IEEE standard 802.3af.

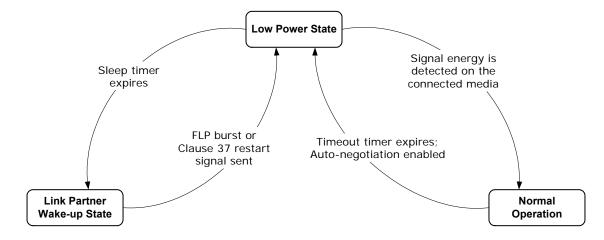

# 3.12 ActiPHY Power Management

In addition to the IEEE-specified power-down control bit (device register bit 0.11), the device also includes an ActiPHY™ power management mode for each PHY. This mode enables support for power-sensitive applications such as laptop computers with Wake-on-LAN™ capability. It utilizes a signal-detect function that monitors the media interface for the presence of a link to determine when to automatically power-down the PHY. The PHY "wakes up" at a programmable interval and attempts to "wake-up" the link partner PHY by sending a burst of FLP over copper media.

The ActiPHY™ power management mode in the VSC8558 device is enabled on a per-port basis during normal operation at any time by setting register bit 28.6 to 1.

There are three operating states possible when ActiPHY™ mode is enabled:

- Low power state

- · LP wake-up state

- Normal operating state (link up state)

The VSC8558 device switches between the low power state and LP wake-up state at a programmable rate (the default is two seconds) until signal energy has been detected on the media interface pins. When signal energy is detected, the PHY enters the normal operating state. If the PHY is in its normal operating state and the link fails, the PHY returns to the low power state after the link status time-out timer has expired. After reset, the PHY enters the low power state.

When auto-negotiation is enabled in the PHY, the ActiPHY state machine operates as described. If auto-negotiation is disabled and the link is forced to 10BT or 100BTX modes while the PHY is in its low power state, the PHY continues to transition between the low power and LP wake-up states until signal energy is detected on the media pins. At that time, the PHY transitions to the normal operating state and stays in that state even when the link is dropped. If auto-negotiation is disabled while the PHY is in the

June 2006 Page 28 of 108

normal operation state, the PHY stays in that state when the link is dropped and does not transition back to the low power state.

The following illustration shows the relationship between ActiPHY states and timers.

Figure 8. ActiPHY State Diagram

### 3.12.1 Low Power State

In the low power state, all major digital blocks are powered down. However the following functionality is provided:

- SMI interface (MDC, MDIO, MDINT\_n)

- CLKOUT

In this state, the PHY monitors the media interface pins for signal energy. The PHY comes out of low power state and transitions to the normal operating state when signal energy is detected on the media. This happens when the PHY is connected to one of the following:

- · Auto-Negotiation capable link partner

- Another PHY in Enhanced ActiPHY LP Wake-up state

In the absence of signal energy on the media pins, the PHY transitions from the low power state to the LP wake-up state periodically based on the programmable sleep timer (register bits 20E.14:13). The actual sleep time duration is randomized from – 80 milliseconds (ms) to +60 ms in order to avoid two linked PHYs in ActiPHY Mode entering a lock-up state during operation.

# 3.12.2 Link Partner Wake-up State

In this state, the PHY attempts to wake up the link partner. Up to three complete FLP bursts are sent on alternating pairs A and B of the Cat5 media for a duration based on the wake-up timer, which is set using register bits 20E.12:11.

June 2006 Page 29 of 108

In this state, the following functionality is provided:

- SMI interface (MDC, MDIO, MDINT\_n)

- CLKOUT

After sending signal energy on the relevant media, the PHY returns to the low power state.

### 3.12.3 Normal Operating State

In this state, the PHY establishes a link with a link partner. When the media is unplugged or the link partner is powered down, the PHY waits for the duration of the programmable link status time-out timer, which is set using register bit 28.7 and bit 28.2. It then enters the low power state.

# 3.13 Serial Management Interface

The VSC8558 device includes an IEEE 802.3-compliant serial management interface (SMI) that is affected by use of its MDC and MDIO pins. The SMI provides access to device control and status registers. The register set that controls the SMI consists of 32, 16-bit registers, including all required IEEE-specified registers. Also, there are additional pages of registers accessible by means of device register 31.

For more information, see "Extended Page Registers," page 62.

The SMI is a synchronous serial interface with bidirectional data on the MDIO pin being clocked on the rising edge of the MDC pin. The interface can be clocked at a rate from 0 MHz to 12.5 MHz, depending upon the total load on MDIO. An external, 2 k $\Omega$  pull-up resistor is required on the MDIO pin.

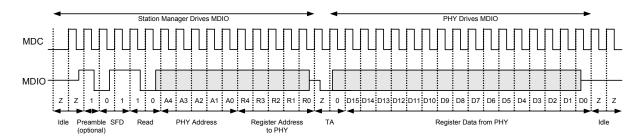

### 3.13.1 SMI Frames

Data is transferred over the SMI using 32-bit frames with an optional and arbitrary length preamble. The following illustrations show the SMI frame format for the read operation and write operation.

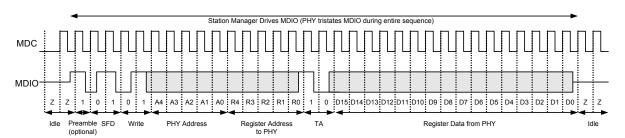

#### Figure 9. SMI Read Frame

June 2006 Page 30 of 108

Figure 10. SMI Write Frame

The following provides additional information about the terms used in Figure 9 and Figure 10.

**Idle** During idle, the MDIO node goes to a high-impedance state. This allows an external pull-up resistor to pull the MDIO node up to a logical 1 state. Because the idle mode should not contain any transitions on MDIO, the number of bits is undefined during idle.

**Preamble** By default, preambles are not expected or required. The preamble is a string of 1s. If it exists, the preamble must be at least one bit, but otherwise may be of an arbitrary length.

**Start of Frame (SFD)** A pattern of 01 indicates the start of frame. If not 01, all following bits are ignored until the next preamble pattern is detected.

**Read or Write Opcode** A pattern of 10 indicates a read. A 01 pattern indicates a write. If these bits are not either 01 or 10, all following bits are ignored until the next preamble pattern is detected.

**PHY Address** The particular VSC8558 responds to a message frame only when the received PHY address matches its physical address. The physical address is five bits long (4:0). Bits 4:3 are set by the CMODE pins. Bits 2:0 represent the PHY of the device being addressed.

**Register Address** The next five bits are the register address.

**Turn-around** The two bits used to avoid signal contention when a read operation is performed on the MDIO are called the turn-around (TA) bits. During read operations, the VSC8558 device drives the second TA bit, a logical 0.

**Data** The 16-bits read from or written to the device are considered the data or data stream. When data is being read from a PHY, it is valid at the output from one rising edge of MDC to the next rising edge of MDC. When data is being written to the PHY, it must be valid around the rising edge of MDC.

**Idle** The sequence is repeated.

## 3.13.2 SMI Interrupts

The SMI also includes an output interrupt signal, MDINT\_n, for signaling the Station Manager when certain events occur in the PHY. A separate MDINT\_n pin is included for each VSC8558 device PHY.

June 2006 Page 31 of 108

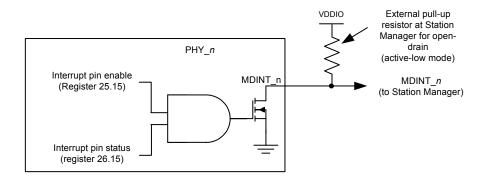

Each MDINT\_*n* pin can be configured for open-drain (active-low) by tying the pin to a pull-up resistor and to VDDIO. The following illustration shows this configuration.

Figure 11. MDINT\_n Configured as an Open-Drain (Active-low) Pin

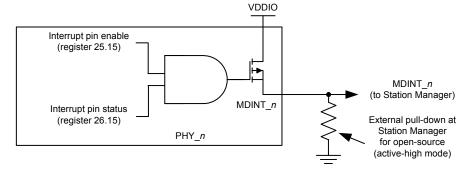

Alternatively, each MDINT\_n pin can be configured for open-source (active-high) by tying the pin to a pull-down resistor and to VSS. The following illustration shows this configuration.

Figure 12. MDINT\_n Configured as an Open-source (Active-high) Pin

If only one interrupt pin is required, each MDINT\_n pin can be tied together to a single pull-up or pull-down resistor in a wired-OR configuration.

When a PHY generates an interrupt, the MDINT\_n pin is asserted (driven high or low, depending on resistor connection) if the interrupt pin enable bit (MII Register 25.15) is set.

### 3.14 LED Interface

The VSC8558 device drives up to four LEDs directly for each PHY port. All LED outputs are active-low and are driven with 3.3 V from the VDD33 power supply. The pins, mainly used to sink current of the cathode side of an LED when active, can also source supply the anode portion of LEDs when not in the active state. This allows for two LED pins to be used to drive a multi-status, bi-colored LED.

June 2006 Page 32 of 108

### **3.14.1 LED Modes**

Each LED pin can be configured to display different status information. Set the LED mode either by using register 29 or with the CMODE pin setting. For additional operating flexibility, LED output functions can be set on a per-port basis. The following table summarizes LED functions.

**Table 5. LED Mode and Function Summary**

| Mode <sup>(1)</sup> | Function Name                | LED State <sup>(2)</sup> and Description                                                                                                                                                                |

|---------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                   | Link/Activity <sup>(3)</sup> | 1 = No link in any speed on any media interface. 0 = Valid link at any speed on any media interface. Blink or Pulse-stretch = Valid link at any speed on any media interface and with activity present. |

| 1                   | Link1000/Activity            | 1 = No link in 1000BASE-T. 0 = Valid 1000BASE-T link. Blink or Pulse-stretch = Valid 1000BASE-T link with activity present.                                                                             |

| 2                   | Link100/Activity             | 1 = No link in 100BASE-TX.<br>0 = Valid 100BASE-TX link.<br>Blink or Pulse-stretch = Valid 100BASE-TX link with activity present.                                                                       |

| 3                   | Link10/Activity              | 1 = No link in 10BASE-T. 0 = Valid 10BASE-T link. Blink or Pulse-stretch = Valid 10BASE-T link with activity present.                                                                                   |

| 4                   | Link100/1000/Activity        | 1 = No link in 100BASE-TX or 1000BASE-T. 0 = Valid 100BASE-TX or 1000BASE-T link. Blink or Pulse-stretch = Valid 100BASE-TX or 1000BASE-T link with activity present.                                   |

| 5                   | Link10/1000/Activity         | 1 = No link in 10BASE-T or 1000BASE-T. 0 = Valid 10BASE-T or 1000BASET-T link. Blink or Pulse-stretch = Valid 10BASE-T or 1000BASE-T link with activity present.                                        |

| 6                   | Link10/100/Activity          | 1 = No link in 10BASE-T or 100BASE-TX. 0 = Valid 10BASE-T or 100BASE-TX link. Blink or Pulse-stretch = Valid 10BASE-T or 100BASE-TX link with activity present.                                         |

| 7                   | Reserved                     |                                                                                                                                                                                                         |

| 8                   | Duplex/Collision             | 1 = Link established in half-duplex mode, or no link established. 0 = Link established in full-duplex mode. Blink or Pulse-stretch = Link established in half-duplex mode but collisions are present.   |

| 9                   | Collision                    | 1 = No collision detected.  Blink or Pulse-stretch = Collision detected.                                                                                                                                |

| 10                  | Activity                     | 1 = No activity present.  Blink or Pulse-stretch = Activity present (becomes TX activity present if register bit 30.14 is set to 1).                                                                    |

| 11                  | Reserved                     |                                                                                                                                                                                                         |