## **Ordering Information**

| Part Number | Voltage    | Mark Code | Temperature Range | Package <sup>(1)</sup> |

|-------------|------------|-----------|-------------------|------------------------|

| MIC2267YML  | Adjustable | 2267      | –40°C to +125°C   | 12-Pin 3mm x 3mm MLF®  |

#### Note:

1. Package is GREEN RoHS compliant. Lead finish is NiPdAu. Mold compound is halogen free.

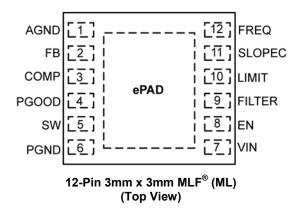

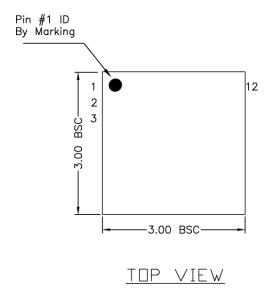

## **Pin Configuration**

## **Pin Description**

| Pin Number | Pin Name | Pin Function                                                                                                                                                                                        |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | AGND     | Analog Ground: The ground return for the low power blocks of the MIC2267.                                                                                                                           |

| 2          | FB       | Feedback (Input): Input to the error amplifier. Connect a resistor divider between VOUT and ground to adjust the output voltage.                                                                    |

| 3          | COMP     | Compensation Pin: Output of the internal gm error amplifier. Place a series connected, Resistor and Capacitor to GND for external compensation.                                                     |

| 4          | PGOOD    | Power Good (Output): Open drain of an N-Channel MOSFET. Connect a resistor to VIN or VOUT for power good signalling.                                                                                |

| 5          | SW       | Switch (Output): Internal power MOSFET output switches.                                                                                                                                             |

| 6          | PGND     | Power Ground: The ground return for the switching currents.                                                                                                                                         |

| 7          | VIN      | Power Supply Voltage (Input): Requires bypass capacitor to GND                                                                                                                                      |

| 8          | EN       | Enable/Delay (Input): Apply a Logic High to start the device. Apply Logic Low to stop the device; placing it in a low quiescent current mode.                                                       |

| 9          | FILTER   | Input Current Limit Filter: Place a capacitor to VIN to adjust the time constant for the input current limit filter.                                                                                |

| 10         | LIMIT    | Input Current Limit: Place a resistor to ground to adjust the average current limit from the input supply.                                                                                          |

| 11         | SLOPEC   | Slope Compensation: Sets current mode slope compensation                                                                                                                                            |

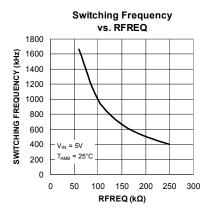

| 12         | FREQ     | Frequency Control: The switching frequency is adjusted from 400kHz to 1.5MHz with a resistor from this pin to ground.                                                                               |

| ePAD       | HS Pad   | Exposed Heatsink Pad: Thermal connection between die and external ground plane. A solid connection to a large ground plane is required for full output power. This pad must be connected to ground. |

## Absolute Maximum Ratings (1)

| Supply Voltage (V <sub>IN</sub> )                                                                                           | –0.3V to +6V                   |

|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Output Switch Voltage (V <sub>SW</sub> )                                                                                    |                                |

| Power Good Voltage (V <sub>PGOOD</sub> )                                                                                    | 0.3V to +6V                    |

| Enable Input Voltage (V <sub>EN</sub> )                                                                                     | 0.3V to V <sub>IN</sub>        |

| Feedback Voltage (V <sub>FB</sub> )                                                                                         | 0.3V to V <sub>IN</sub>        |

| AGND to PGND Voltage                                                                                                        | 0.3V to +0.3V                  |

| Switch Current (I <sub>SW</sub> )                                                                                           | Internally Limited             |

| Power Dissipation                                                                                                           | المحادمان البراام معمالير      |

| 1 OWCI DISSIPATION                                                                                                          | internally Limited             |

| Lead Temperature (soldering, 10sec.)                                                                                        |                                |

| Lead Temperature (soldering, 10sec.)<br>Storage Temperature (T <sub>s</sub> )                                               | 260°C<br>–65°C to +150°C       |

| Lead Temperature (soldering, 10sec.)<br>Storage Temperature (T <sub>s</sub> )<br>ESD Human Body Model Rating <sup>(3)</sup> | 260°C<br>65°C to +150°C<br>2kV |

| Lead Temperature (soldering, 10sec.)                                                                                        | 260°C<br>65°C to +150°C<br>2kV |

# Operating Ratings (2)

| Supply Voltage (V <sub>IN</sub> )                | +3.0V to +5.5V        |

|--------------------------------------------------|-----------------------|

| Power Good Voltage (V <sub>PGOOD</sub> )         | 0V to +5.5V           |

| Enable Input Voltage (V <sub>EN</sub> )          | 0V to V <sub>IN</sub> |

| Feedback Voltage (V <sub>FB</sub> )              | 0V to V <sub>IN</sub> |

| AGND to PGND Voltage                             | 0.3V to +0.3V         |

| Junction Temperature (T <sub>J</sub> )           | 40°C to +125°C        |

| Junction Thermal Resistance                      |                       |

| 3mm x 3mm MLF <sup>®</sup> -12(θ <sub>JA</sub> ) |                       |

| 3mm x 3mm MLF <sup>®</sup> -12( $\theta_{JC}$ )  | 27°C/W                |

|                                                  |                       |

# **Electrical Characteristics** (4)

$V_{\text{IN}} = V_{\text{EN}} = 5.0 \text{V}, \ V_{\text{OUT}} = 3.3 \text{V}, \ I_{\text{LOAD}} = 10 \text{mA}, \ C_{\text{IN}} = 10 \mu \text{F}, \ L = 4.7 \mu \text{H}, \ C_{\text{OUT}} = 47 \mu \text{F}, \ R_{\text{FREQ}} = 100 \text{k}\Omega; \ R_{\text{SLOPEC}} = 100 \text{k}\Omega, \ R_{\text{LIM}} = 100 \text{k}\Omega, \ R_{\text{COMP}} = 11.5 \text{k}\Omega, \ C_{\text{COMP}} = 15 \text{nF}, \ T_{\text{A}} = 25 ^{\circ}\text{C}; \ \textbf{bold} \ \ \text{values indicate} \\ = 40 ^{\circ}\text{C} \leq T_{\text{J}} \leq 125 ^{\circ}\text{C}; \ \ \text{unless noted}.$

| Parameter                              | Conditions                                                       | Min.                          | Тур. | Max. | Units |

|----------------------------------------|------------------------------------------------------------------|-------------------------------|------|------|-------|

| Power Input Supply                     |                                                                  |                               |      |      |       |

| Input Voltage Range (V <sub>IN</sub> ) |                                                                  | 3.0                           |      | 5.5  | V     |

| V <sub>IN</sub> UVLO Threshold         | Rising                                                           | 2.75                          | 2.9  | 3.0  | V     |

| V <sub>IN</sub> UVLO Hysteresis        |                                                                  |                               | 320  |      | mV    |

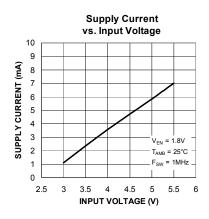

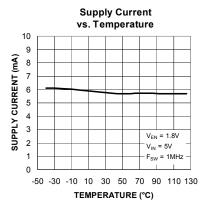

| Quiescent Current                      | PWM Mode, $V_{EN} > 1.8V$ , $V_{FB} = 0.9V$ , $I_{OUT} = 0A$     | = 0.9V, I <sub>OUT</sub> = 0A |      |      | mA    |

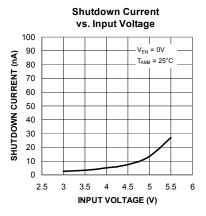

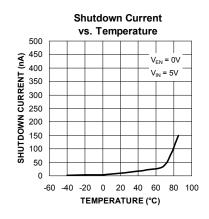

| Shutdown Current                       | V <sub>EN</sub> = 0V                                             |                               | 1    | 5    | μΑ    |

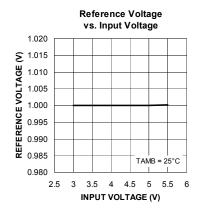

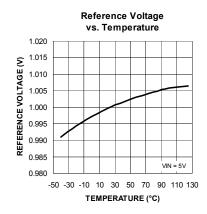

| Reference Voltage                      |                                                                  |                               |      |      |       |

| Feedback Voltage                       | ±2% over temperature                                             | 0.98                          | 1    | 1.02 | V     |

| Feedback Bias Current                  | V <sub>FB</sub> = 1V                                             |                               | 1    |      | nA    |

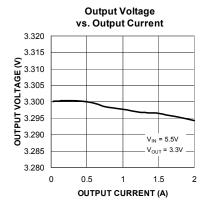

| Output Voltage Line Regulation         | $V_{IN} = V_{EN} = 4V \text{ to } 5.5V, I_{LOAD} = 100\text{mA}$ |                               | 0.2  |      | %     |

| Output Voltage Load Regulation         | 100mA < I <sub>LOAD</sub> < 1.2A                                 |                               | 0.2  |      | %     |

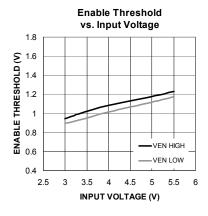

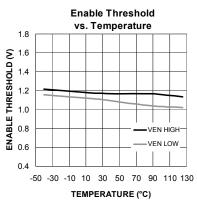

| Enable Control                         |                                                                  |                               |      |      |       |

| Enable Logic High Threshold            |                                                                  |                               | 1.2  | 1.8  | V     |

| Enable Logic Low Threshold             |                                                                  | 0.4                           | 1    |      | V     |

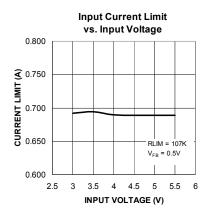

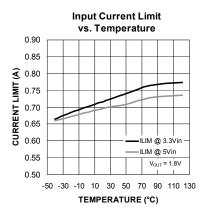

| Input Current Limit                    |                                                                  |                               |      |      |       |

|                                        | $V_{FB} = 0.5V$ , $R_{LIMIT} = 107k\Omega$                       | 0.5                           | 0.7  | 0.9  |       |

| Input Current Limit                    | $V_{FB} = 0.5V$ , $R_{LIMIT} = 68.1k\Omega$                      | 0.7                           | 1.1  | 1.5  | Α     |

|                                        | $V_{FB}$ = 0.5V, $R_{LIMIT}$ = 46.4k $\Omega$                    | 1.1                           | 1.6  | 2.1  |       |

#### Notes:

- 1. Exceeding the absolute maximum rating may damage the device.

- 2. The device is not guaranteed to function outside its operating rating.

- 3. Devices are ESD sensitive. Handling precautions recommended. Human body model,  $1.5k\Omega$  in series with 100pF.

- 4. Specification for packaged product only.

# **Electrical Characteristics** (4)

$V_{\text{IN}} = V_{\text{EN}} = 5.0 \text{V}, \ V_{\text{OUT}} = 3.3 \text{V}, \ I_{\text{LOAD}} = 10 \text{mA}, \ C_{\text{IN}} = 10 \mu \text{F}, \ L = 4.7 \mu \text{H}, \ C_{\text{OUT}} = 47 \mu \text{F}, \ R_{\text{FREQ}} = 100 \text{k}\Omega; \ R_{\text{SLOPEC}} = 100 \text{k}\Omega, \ R_{\text{LIM}} = 100 \text{k}\Omega, \ R_{\text{COMP}} = 11.5 \text{k}\Omega, \ C_{\text{COMP}} = 15 \text{nF}, \ T_{\text{A}} = 25 ^{\circ}\text{C}; \ \textbf{bold} \ \ \text{values indicate} \ -40 ^{\circ}\text{C} \leq T_{\text{J}} \leq 125 ^{\circ}\text{C}; \ \ \text{unless noted}.$

| Parameter                               | Conditions                                                 | Min. | Тур.     | Max. | Units |

|-----------------------------------------|------------------------------------------------------------|------|----------|------|-------|

| Soft Start                              |                                                            |      |          |      |       |

| Soft Start                              |                                                            |      | Adaptive |      |       |

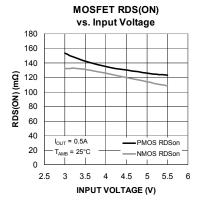

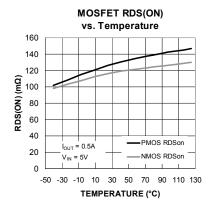

| Internal FETs                           |                                                            | ·    |          |      |       |

| Top MOSFET RDS(ON)                      | I <sub>SW</sub> = 500mA, V <sub>FB</sub> = 0.9V            |      | 136      | 225  | mΩ    |

| Bottom MOSFET RDS(ON)                   | I <sub>SW</sub> = 500mA, V <sub>FB</sub> = 1.1V            |      | 100      | 225  | mΩ    |

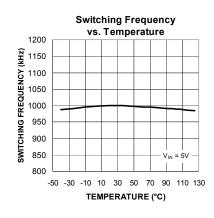

| Oscillator/PWM                          |                                                            | ·    |          |      |       |

|                                         | $R_{FREQ} = 250k\Omega$                                    | 0.32 | 0.4      | 0.48 |       |

| Oscillator Frequency                    | $R_{FREQ}$ = 100k $\Omega$                                 | 0.8  | 1        | 1.2  | MHz   |

|                                         | $R_{FREQ} = 60k\Omega$                                     | 1.2  | 1.5      | 1.8  |       |

| Maximum Duty Cycle                      | V <sub>FB</sub> < 0.5V                                     | 100  |          |      | %     |

| Thermal Protection                      | ·                                                          |      |          |      |       |

| Over Temperature Shutdown               |                                                            |      | 160      |      | °C    |

| Over Temperature Shutdown<br>Hysteresis |                                                            |      | 20       |      | °C    |

| Power Good                              | ·                                                          |      |          |      |       |

| Power Good Threshold                    | V <sub>OUT</sub> Rising (V <sub>OUT</sub> % below nominal) | 6.5  | 10       | 12.5 | %     |

| Power Good Output Low<br>Voltage        | V <sub>FB</sub> = 0.9V, I <sub>PGOOD</sub> = 5mA           |      | 130      | 200  | mV    |

| Power Cood Lookage Current              | V <sub>FB</sub> = 1.0V, V <sub>PGOOD</sub> = 5.5V          |      |          | 1    |       |

| Power Good Leakage Current              |                                                            |      |          | 2    | μA    |

#### Note:

<sup>4.</sup> Specification for packaged product only.

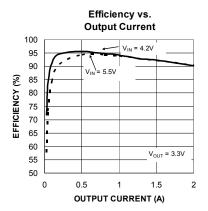

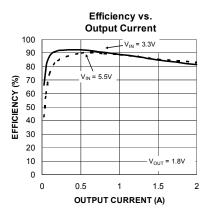

## **Typical Characteristics**

## **Typical Characteristics (Continued)**

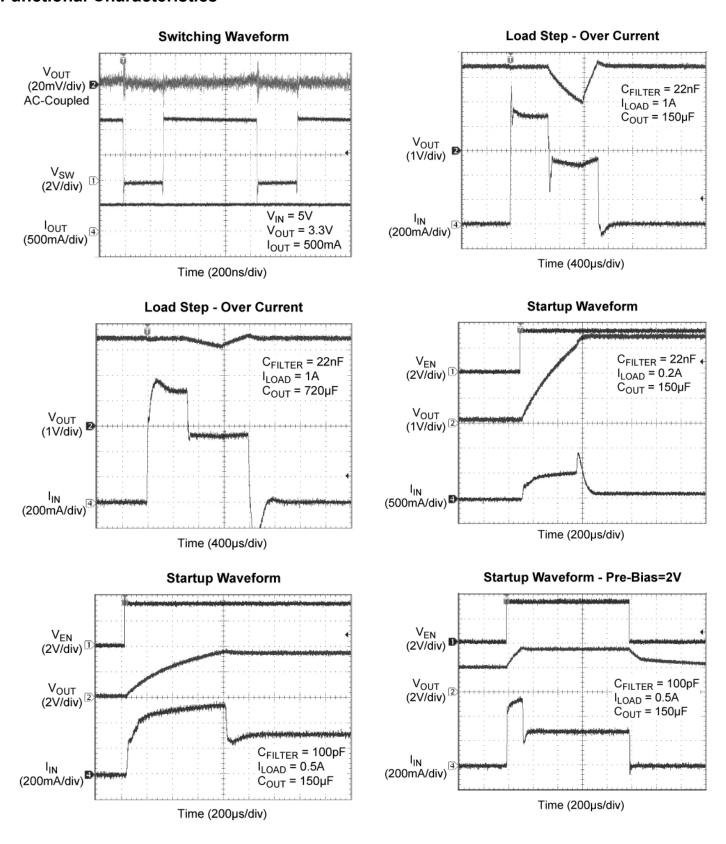

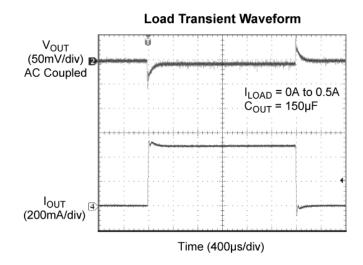

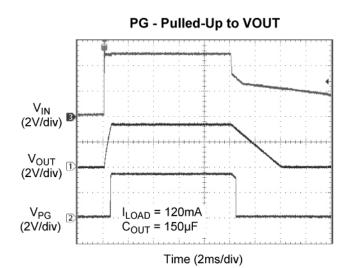

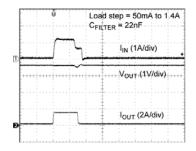

## **Functional Characteristics**

## **Functional Characteristics (Continued)**

# V<sub>OUT</sub> (50mV/div) 2 AC Coupled V<sub>IN</sub> (1V/div) I<sub>LOAD</sub> = 0.5A C<sub>OUT</sub> = 150μF Time (200μs/div)

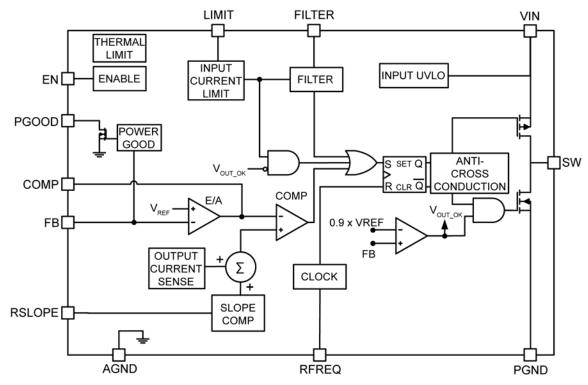

## **Functional Diagram**

Figure 1. MIC2267 Functional Block Diagram

## **Functional Description**

The MIC2267 is an input current limited, 2A synchronous buck regulator. The part offers control of the input average current limit and the time constant of the current limit response, allowing full control of the input current profile during load steps and plug in events. The P-Channel high side switch allows for 100% duty cycle operation. Optimization of the loop bandwidth can be achieved using the available connections to the slope compensation ramp and error amplifier nodes. For logic control and error flagging, the MIC2267 has an enable function and a Power Good function.

#### $V_{IN}$

The input supply  $(V_{IN})$  provides power to the internal power MOSFETs and the analog control circuitry. The  $V_{IN}$  operating range is 3V to 5.5V. A minimum bypass capacitor of  $10\mu F$  should be placed close to the input  $(V_{IN})$  pin and the ground (PGND) pin. Refer to the *Layout Recommendations* section for details on placing the input capacitor.

#### LIMIT

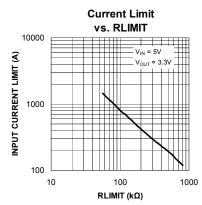

The current limit as set by the R<sub>LIMIT</sub> resistor (Nominally, I<sub>LIMIT</sub> = 75k/R<sub>LIMIT</sub>) is converted to the total charge allowed in one cycle (Q<sub>TOT</sub>). So if the current limit is 1A and the frequency is 1MHz, since Q = I x T, the total charge allowed Q<sub>TOT</sub> = 1 $\mu$ C. If for example, a 1 $\mu$ F capacitor C<sub>TOT</sub> is used to store this charge, since Q = C x V, the voltage would be 1V.

If a replica of the input current is then integrated and the resultant input charge per cycle:

$$Q_{IN} = \int_{O}^{T} I_{IN}(t).dt$$

Is stored on a similar 1µF capacitor  $C_{INT}$ , then input current limit is reached when the voltage on the  $C_{INT}$  capacitor reaches 1V, i.e.  $Q_{IN} \geq Q_{TOT}$ . Once this condition is satisfied and the FILTER delay time has elapsed, the P-Channel switch cycle is terminated. At the beginning of each cycle the integration storage capacitors are discharged. In the actual circuit the storage capacitor is in the order of 5pF and the replica current is scaled down accordingly.

This is, effectively, cycle by cycle input current limit where the average input current in each cycle is limited. The advantage of this scheme is that when the input current budget has been used up for that cycle and the top switch goes off, the output can still draw current from ground and switching continues in an efficient manor. Conventional input current limit schemes which utilize an input switch will effectively drop  $V_{\text{IN}}$  and leave the switcher at 100% duty cycle; in effect current limiting like an LDO current limits.

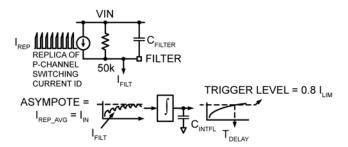

#### **FILTER**

The filter pin can be used to implement a delay to the input current limit, thus allowing acceptable bursts of current to pass, unaffected. However the magnitude of the over current will act to shorten the allowable pulse width; effectively regulating charge passed; thus for a given input capacitor, the droop during over current peaks can be kept constant.

The Delay circuit is an identical circuit to the LIMIT circuit except that the current being stored on the integrating capacitor is first sent through a single pole RC filter i.e. a replica of the P-Channel Drain current is fed into a parallel RC. The R is set internally to  $50k\Omega$  ( $\pm20\%$ ) and the C is the external ( $C_{\text{FILTER}}$ ). The FILTER current limit is set to 80% of the nominal input current limit, i.e., in the previous example, whereas the LIMIT circuit has to charge the storage capacitor  $C_{\text{INT}}$  to 1V, the FILTER current limit circuit only has to charge the integration storage capacitor  $C_{\text{INTFIL}}$  to 0.8V.

Figure 2. MIC2267 FILTER Pin Operation

The rising function after the integration block (voltage on  $C_{\mathsf{INTFIL}}$ ) is actually discharged to 0v each cycle, but for clarity, it is shown as an 'envelope' to show its rising characteristic.

$$T_{DELAY} = -In \left(1 - 0.8 \times \frac{I_{LIM}}{I_{IN}}\right) \times 50k\Omega \times C_{FILTER}$$

Typically, C<sub>INTFIL</sub> takes time to reach this 80% trip level. Therefore, asserting current limit on the current cycle is highly dependant on internal delays and the extremity of the over current. Therefore, if the filter circuit reaches the 80% trigger level in a given cycle (n), the actual current limit is allowed to work during the next cycle (n+1).

When  $V_{\text{OUT}}$  < 90%  $V_{\text{OUT}}$  nominal, e.g. during startup or large load transients, the filter/delay function is disabled. This is to allow a defined startup current limit and reduce voltage peaks.

#### **ENABLE (EN)**

This is the enable pin. Taking this pin above 1.8V will enable the part to begin switching. Taking this pin below 0.4V will put the part into the shutdown mode where nominally, the part will consume  $< 1\mu$ A.

#### POWER GOOD (PGOOD)

This is an open drain output which can be connected via a pull up resistor to  $V_{\text{OUT}}$  or an external voltage up to 5.5V. This pin is pulled low while the part is enabled and the output is below 90% of the nominal output voltage. When the trigger threshold of nominally >90% nominal  $V_{\text{OUT}}$  is crossed, the PGOOD N-Channel FET is switched off and the pin will be high impedance.

Note that the power good function is inactive while the part is in shutdown (EN=Low). I.E. If the PG pull up resistor is connected to VIN, PG will be high when EN is below the enable threshold.

#### **COMP**

COMP is the output connection of the voltage error transconductance amplifier. The MIC2267 is a current mode controller and therefore will require just a capacitor and resistor connected from COMP to AGND to create a single pole, single zero compensator to stabilize the loop. An additional capacitor from COMP to AGND can be added to reduce switching jitter due to high frequency switching noise entering the loop.

If desirable, slope compensation can be increased/ reduced to improve stability/transient response over a wide duty cycle range including 100%. In such cases, additional compensation may be added to this pin if required.

#### FΒ

Connect this pin to the junction of the output voltage feedback resistors. The regulation loop will set the output voltage to the correct level determined by these feedback resistor values. The output voltage will be:

$$V_{OUT} = V_{REF}(1+R1/R2)$$

For most applications, R2 can be set to 10k and R1 can be found by:

$$R1 = R2(V_{OUT}/V_{REF} - 1)$$

#### **SLOPEC**

To guarantee stability in a current mode controller operating at duty cycle >50%, a compensation ramp (m) is required. This ramp 'm' is added to the inductor current sense ramp (or alternatively, it can also be subtracted from the error voltage which has the same effect).

A resistor to ground from the SLOPEC pin sets the amplitude of 'm' over the switching period.

Ideally, the magnitude of the compensation ramp (m) is for many cases, set to  $\frac{1}{2}$  inductor discharge ramp (m2). I.E. m=  $\frac{1}{2}$  m2

Where:

$$m2 \propto Vo/L \times F_{SW}$$

and

$$m \propto 67700/R_{SLOPEC}$$

Therefore, for the ideal ½ m2 slope:

$$R_{SLOPEC}$$

= 2 x  $F_{SW}$  x L x 67700/Vout

Where duty cycle can approach 100%, excess phase shift in the loop can lead to a phenomenon called "sub-harmonic oscillation". Additional compensating slope 'm' may be required in these cases.

It can be shown that ensuring m = m2 will ensure stability regardless of voltage loop gain for the case where DC ~ 100%. Therefore, a value of  $R_{SLOPEC}$  =  $F_{SW.}X$  L x 67700/Vout will ensure stability at the expense of some line regulation.

#### **AGND and PGND**

Connect AGND to the quiet, signal reference points and decouple closely to the IC. Connect PGND to the high current carrying paths close to the  $C_{\text{OUT}}$  and  $C_{\text{IN}}$ . Refer to layout guide section later in the datasheet for more detailed information.

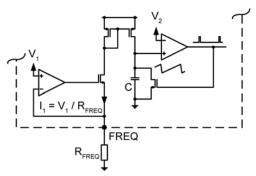

#### **FREQ**

A resistor  $R_{\text{FREQ}}$  from this pin to ground allows the frequency of the MIC2267 to be programmed over the range 400kHz to 1.5MHz.

Figure 3. MIC2267 FREQ Pin Internal Blocks

To set the frequency, this pin is forced to  $V_1$ , the resulting current through the resistor  $R_{\text{FREQ}}$  sets the internal reference current which charges a capacitor (C). At the beginning of the clock cycle, C begins charging. When it reaches  $V_2$ , a clock pulse is generated and C is discharged to ground; marking the beginning of the next clock cycle.

This produces a clock frequency F<sub>SW</sub> of:

$$F_{SW} = 1/(C \times R_{FREQ})$$

Where C = 10pF

#### SW

This is the center connection output of the P-channel and N-channel Power MOSFETs. Connect this pin to the Power inductor as close to the IC as possible. Refer to the *Layout Recommendations* section for details on placing the power inductor.

## **Application Information**

#### **FILTER**

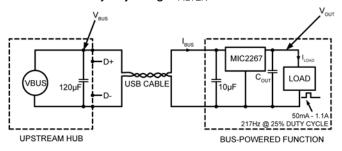

The USB 2.0 specification requires that current surges during transitions should result in a droop at an upstream USB port <330mV. In addition to the  $10\mu F$  allowable USB "device" input capacitance; there is also a mandatory  $120\mu F$  capacitor at each upstream Hub VBUS terminal. This presents a challenge as there is an amount of energy available within this hub capacitance that can be tapped only if the droop can somehow be limited remotely at the device end. Since the MIC2267 implements a charge limit system, this available energy can be utilized by adjusting  $C_{\rm FILTER}$ .

Figure 2. USB Bus Powered Function Example

Where actual  $C_{\text{BUS}}$  is higher than 120µF, the FILTER capacitor can be increased to allow greater current limit delay times. This can help further reduce the value of output bulk holdup capacitors ( $C_{\text{OUT}}$ ) in applications that require large, short term load pulses such as TDMA wireless data modems.

The FILTER capacitor should be placed as close as possible to the FILTER and VIN pins to set the input current limit delay time. Recommended minimum value is 100pF.

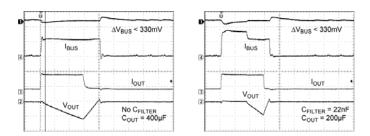

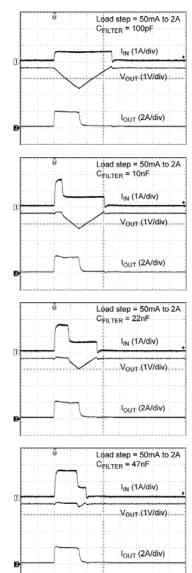

#### Effect of Changing FILTER Capacitor on Vout

$C_{OUT}$  = 447 $\mu$ F,  $V_{OUT}$  = 3.3V, Load pulse width = 600 $\mu$ s:

Reducing over current peak increases limit delay time in accordance with the T<sub>DELAY</sub> equation:

$$\textbf{T}_{\text{DELAY}} \approx -\text{In} \Biggl(1 - 0.8 \times \frac{\textbf{I}_{\text{LIM}}}{\textbf{I}_{\text{IN}}}\Biggr) \times 50 \text{k}\Omega \times \textbf{C}_{\text{FILTER}}$$

#### LIMIT

Resistor values of between  $750k\Omega$  and  $46k\Omega$  should be used to set the current limit between 0.1A and 1.6A. To set the nominal LIMIT resistor value:

$$R_{LIMIT} = 75k\Omega/I_{LIMIT}$$

In USB applications for example, two LIMIT resistors can be used to switch between 1 unit load (100mA) and 5 unit loads (500mA).

Due to a minimum on time implemented during current limit operation, there is lower limit to  $V_{OUT}$  where input current limit is regulated. When  $V_{OUT}$  sees a near short circuit at higher switching frequency,  $I_{IN}$  will be higher than the set  $I_{LIMIT}$ . Circuit losses will tend to keep this to a maximum of 250mA.

The limit can be found by:

$$V_{OUTMIN} = ((V_{IN} + 0.8) \cdot F_{SW} \cdot 200ns) - 0.8$$

e.g., for

$$V_{IN}$$

= 5v and  $F_{SW}$  = 1MHz,  $V_{OUTMIN}$  = 0.36V

#### **COMP**

As the MIC2267 uses a current mode control, the control loop only requires a single pole/zero compensator to optimise stability and transient response. The recommended values are  $11k\Omega$  and 15nF. An additional 680pF capacitor can also be added to reject switching frequency noise.

#### FB

Connect a resistor divider between the  $V_{\text{OUT}}$  load terminal connection and output ground reference connection to minimize resistive voltage drops affecting load regulation.

For most applications, R2 can be set to  $10k\Omega$  and R2 can be found by:

$$R1 = R2(V_{OUT}/V_{REF} - 1)$$

#### **SLOPEC**

Connect a resistor between this pin and AGND as close to the MIC2267 as possible to reduce the possibility of noise adding into the control loop.

As described in the theory of operation, the ideal slope can be calculated as:

$$R_{SLOPEC} = 2. F_{SW} . L . 67700/V_{OUT}$$

This value can be scaled towards  $\frac{1}{2}$  this value to ensure stability up to and including 100% duty cycle.

#### **FREQ**

Connect a resistor between this pin and AGND as close to the MIC2267 as possible to reduce the possibility of switching noise causing frequency jitter.

Set the nominal switching frequency using:

$$F_{SW} = 1/(C.R_{FREQ})$$

Where nominal C = 10pF

#### **INDUCTOR**

The MIC2267 was designed to work with  $3.3\mu H$  to  $10\mu H$  inductor values.

If a low ripple voltage output is a key design goal, then larger value inductors will reduce switching ripple current and output ripple voltage, but can also have larger DCR values in small packages; which can reduce efficiency. Inversely, if high efficiency is the key target, Lower value inductors will increase switching ripple current and therefore increase output ripple voltage, but will typically have lower DCR values in small packages and can improve efficiency.

As the MIC2267 uses input current limiting, care should be taken that during a short circuit condition, the inductor can operate with the power dissipated in it during this fault condition. Helpfully, The MIC2267 switches the low side driver off during a short circuit, which ensures most of the power dissipation occurs within the IC. e.g.:

$$P_{FAULT} = 5v \times 1A = 5W$$

$$V_{NFFT} \approx 0.7V$$

$$V_{L DCR} = I_{IN} x DCR = 1A x 50m\Omega = 0.05V$$

Power in the inductor DCR = 7% overall dissipation.

$$P_{L DCR} = 0.36W$$

The MIC2267 thermal limit protection will therefore limit the power in the inductor and protect from over dissipation. Protection is further improved by designing a low thermal resistance connection between the inductor and the IC. To achieve this, a short, wide PCB trace from the inductor to the SW pin is recommended. Connecting the inductor close to the SW pin is also good design practice as it minimizes the area available for radiating switching frequency harmonics around the local area of the switching regulator.

## $\mathbf{C}_{\text{IN}}$

Connect a ceramic capacitor of X5R or X7R dielectric from the VIN pin to PGND as close to the MIC2267 as possible to decouple the high di/dt switching current paths. A minimum value of  $10\mu\text{F}$  is recommended for most applications. An additional  $22\mu\text{F}$  can be useful in reducing ringing effects if long power leads are used to connect power.

#### Cout

Connect a ceramic capacitor of X5R or X7R dielectric from  $V_{\text{OUT}}$  to PGND as close as possible to the inductor and  $C_{\text{IN}}$  ground connection to reduce the effect of high di/dt ground currents from interfering with internal signals. A minimum of  $47\mu\text{F}$  is recommended for most applications. Additional bulk capacitance such as electrolytic, tantalum or ceramic can be added to improve transient performance and hold up during large load transients.

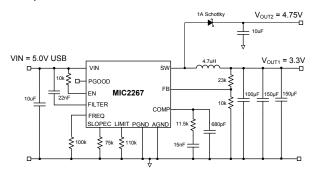

#### **5V Pass Through**

Some applications will require a legacy 5v supply to be available which also benefits from the current limit protection. The circuit in Figure 5 allows for a low current bias supply to be provided while still providing current limit protection.

Figure 3. Standard MIC2267 Circuit with Protected ~5v Bias Supply

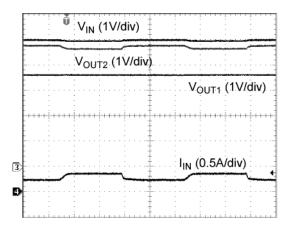

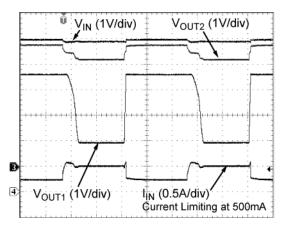

Below are some oscilloscope shots of the Pass through circuit operating under the following conditions:

#### Normal operation:

V<sub>OUT1</sub> = 3.3v @ 200mA Continuous Load

$V_{OUT2}$  = 4.75v @ 80mA to 200mA Pulsing Load

#### Over Current peaks applied:

$V_{OUT1}$  = 3.3v @ 200mA Continuous Load  $V_{OUT2}$  = 4.75V @ 80mA to 600mA Pulsing Load

Normal operation; no Over Current

Over Current Peaks applied on Vout2

## **PCB Layout Guidelines**

# To minimize EMI and output noise, follow these layout recommendations.

PCB Layout is critical to achieve reliable, stable and efficient performance. A ground plane is required to control EMI and minimize the inductance in power, signal and return paths.

The following guidelines should be followed to insure proper operation of the MIC2267 converter.

#### IC

- The 10μF ceramic capacitor, which is connected to the VIN pin, must be located right at the IC. The VIN pin is noise sensitive and placement of the capacitor is critical. Use wide traces to connect to the VIN and PGND pins.

- The signal ground pin (AGND) must be connected directly to the ground planes. The common connection of PGND and AGND should be at the LOAD GND terminal.

- 3. Place the IC close to the point of load (POL).

- 4. Use fat traces to route the input and output power lines.

- 5. Signal and power grounds should be kept separate and connected at only one location.

#### **Input Capacitor**

- 1. Place the input capacitor next.

- 2. Place the input capacitors on the same side of the board and as close to the IC as possible.

- 3. Keep both the VIN and PGND connections short.

- 4. Place several vias to the ground plane close to the input capacitor ground terminal.

- 5. Use either X7R or X5R dielectric input capacitors.

- Do not use Y5V or Z5U type capacitors.

- 7. Do not replace the ceramic input capacitor with any other type of capacitor. Any type of capacitor can be placed in parallel with the input capacitor.

- 8. If a Tantalum input capacitor is placed in parallel with the input capacitor, it must be recommended for switching regulator applications and the operating voltage must be derated by 50%.

- In "Hot Plug" applications, a Tantalum or Electrolytic bypass capacitor must be used to limit the overvoltage spike seen on the input supply with power is suddenly applied.

#### Inductor

- 1. Keep the inductor connection to the switch node (SW) short.

- Do not route any digital lines underneath or close to the inductor.

- 3. Keep the switch node (SW) away from the feedback (FB) pin.

- 4. To minimize noise, place a ground plane underneath the inductor.

#### **Output Capacitor**

- 1. Use a wide trace to connect the output capacitor ground terminal to the input capacitor ground terminal.

- Phase margin will change as the output capacitor value and ESR changes. Contact the factory if the output capacitor is different from what is shown in the BOM.

- The feedback trace should be separate from the power trace and connected as close as possible to the output capacitor. Sensing a long high current load trace can degrade the DC load regulation.

#### **RC Snubber**

1. Place the RC snubber on the same side of the board and as close to the SW pin as possible.

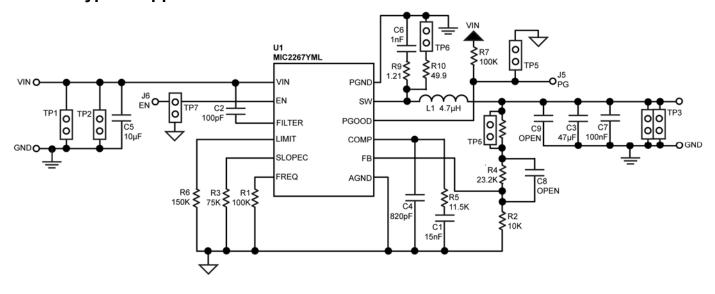

## **MIC2267 Typical Application Circuit**

## **Bill of Materials**

| Item   | Part Number          | Manufacturer                | Description                                                         | Qty. |

|--------|----------------------|-----------------------------|---------------------------------------------------------------------|------|

| L1     | VLF5014ST-4R7M1R7    | TDK <sup>(1)</sup>          | 4.7μH, 2A inductor                                                  | 1    |

| C3     | 12066D476MAT2A       | AVX <sup>(4)</sup>          | 47μF, 6.3V, X5R ceramic capacitor                                   | 1    |

| C9     | Not Fitted 1210 size |                             |                                                                     | 0    |

| C5     | 08056D106MAT2A       | AVX <sup>(4)</sup>          | 10μF, 6.3V, X5R ceramic capacitor                                   | 1    |

| C7     | 06033D104MAT2A       | AVX <sup>(4)</sup>          | 0.1μF, 25V ceramic capacitor                                        | 1    |

| C1     | 06033C153MAT2A       | AVX <sup>(4)</sup>          | 15nF, 25V, ceramic capacitor                                        | 1    |

| C6     | 06033C102MAT2A       | AVX <sup>(4)</sup>          | 1nF 25V, ceramic capacitor                                          | 1    |

| C2     | 06033A101KAT2A       | AVX <sup>(4)</sup>          | 100pF, 25V, COG ceramic capacitor                                   | 1    |

| C4     | 06035A821JAT2A       | AVX <sup>(4)</sup>          | 820pF, 50V, NPO ceramic capacitor                                   | 1    |

| C8     | Not Fitted 0603 size |                             |                                                                     | 0    |

| R1, R7 | CRCW06031003FRT1     | Vishay Dale <sup>(2)</sup>  | 100K (0603 size), 1%                                                | 2    |

| R2     | CRCW06031002FRT1     | Vishay Dale <sup>(2)</sup>  | 10K (0603 size), 1%                                                 | 1    |

| R3     | CRCW06037502FRT1     | Vishay Dale <sup>(2)</sup>  | 75K (0603 size), 1%                                                 | 1    |

| R4     | CRCW06032322FRT1     | Vishay Dale <sup>(2)</sup>  | 23.2K (0603 size), 1%                                               | 1    |

| R5     | CRCW06031152FRT1     | Vishay Dale <sup>(2)</sup>  | 11.5K (0603 size), 1%                                               | 1    |

| R6     | CRCW06031503FRT1     | Vishay Dale <sup>(2)</sup>  | 150K (0603 size), 1%                                                | 1    |

| R8     | CRCW060322R1FRT1     | Vishay Dale <sup>(2)</sup>  | 22.1 (0603 size), 1%                                                | 1    |

| R9     | CRCW08051R21FRT1     | Vishay Dale <sup>(2)</sup>  | 1.21Ω (0805 size), 1%                                               | 1    |

| R10    | CRCW060349R9FRT1     | Vishay Dale <sup>(2)</sup>  | 49.9Ω (0603 size), 1%                                               |      |

| U1     | MIC2267YML           | Micrel, Inc. <sup>(5)</sup> | Input Current Limiting Synch' Buck Regulator (12 pin 3mm x 3mm MLF) | 1    |

#### Notes:

1. TDK: www.tdk.com.

2. Vishay: www.vishay.com.

3. Murata: www.murata.com.

4. AVX: www.avx.com.

5. Micrel, Inc.: www.micrel.com.

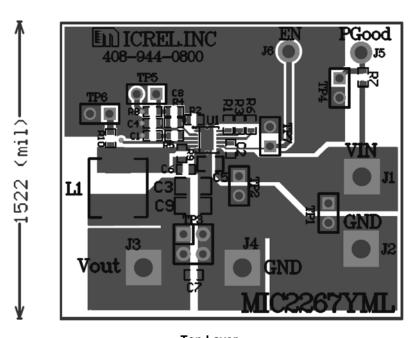

## **PCB Layout Recommendations**

Top Layer

**Bottom Layer**

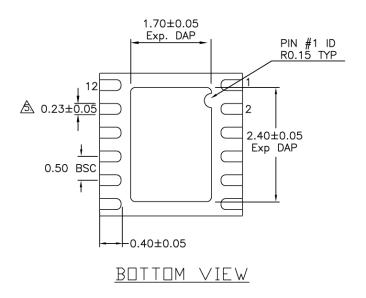

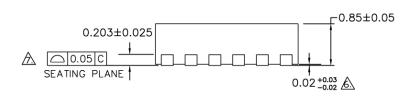

## **Package Information**

- ALL DIMENSIONS ARE IN MILLIMETERS.

MAX. PACKAGE WARPAGE IS 0.05 mm.

MAXIMUM ALLOWABE BURRS IS 0.076 mm IN ALL DIRECTIONS.

PIN #1 ID ON TOP WILL BE LASER/INK MAKKED.

DIMENSION APPLIES TO METALIZED TERMINAL AND IS MEASURED

BETWEEN 0.20 AND 0.25 mm FROM TERMINAL TIP.

APPLIED ONLY FOR TERMINALS.

- APPLIED ONLY FOR TERMINALS.

APPLIED FOR EXPOSED PAD AND TERMINALS.

SIDE VIEW

12-Pin MLF® (YML)

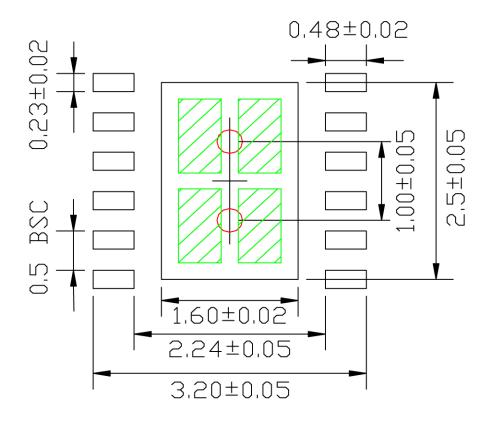

#### **Recommended Land Pattern**

#### LP # MLF33D-12LD-LP-1

All units are in mm

Tolerance ± 0.05 if not noted

**Red circle** indicates Thermal via. Size should be 0.300mm – 0.350mm in diameter, 1.00mm pitch and should connect to GND plane for maximum thermal performance.

**Green rectangle (with shaded area)** indicates Solder Stencil Opening on exposed pad area. Size should be 0.50mm x 0.95mm, 1.15mm pitch.

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

Micrel makes no representations or warranties with respect to the accuracy or completeness of the information furnished in this data sheet. This information is not intended as a warranty and Micrel does not assume responsibility for its use. Micrel reserves the right to change circuitry, specifications and descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Micrel's terms and conditions of sale for such products, Micrel assumes no liability whatsoever, and Micrel disclaims any express or implied warranty relating to the sale and/or use of Micrel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2011 Micrel, Incorporated.