### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND.)                     |     |

|-------------------------------------------------------|-----|

| V <sub>C</sub> C                                      | +6V |

| DE, RE, DI0.3V to -                                   | +6V |

| A, B8V to                                             | 13V |

| Short-Circuit Duration (RO, A, B) to GNDContinu       | ous |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |     |

| 8-Pin SO (derate 5.9mW/°C above +70°C)471             | пW  |

| 8-Pin µDFN (derate 4.8mW/°C above +70°C)380.6         |     |

| 40°C to +85°C  |

|----------------|

| +150°C         |

| 65°C to +150°C |

| +300°C         |

|                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

(VCC = +5V ±5%, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at V<sub>CC</sub> = +5V and T<sub>A</sub> = +25°C.) (Notes 1, 2)

| PARAMETER                                             | SYMBOL            | CONDITIO                                                                  | ONS             | MIN                    | TYP             | MAX  | UNITS |

|-------------------------------------------------------|-------------------|---------------------------------------------------------------------------|-----------------|------------------------|-----------------|------|-------|

| DRIVER                                                |                   |                                                                           |                 | •                      |                 |      |       |

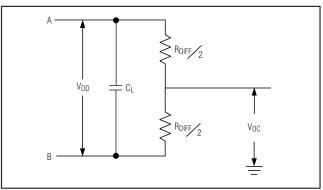

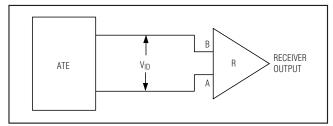

|                                                       |                   | $R_{DIFF} = 100\Omega$ , Figure 1                                         |                 | 2.0                    |                 | Vcc  |       |

| Differential Driver Output                            | V <sub>OD</sub>   | $R_{DIFF} = 54\Omega$ , Figure 1                                          |                 | 1.5                    |                 |      | V     |

|                                                       |                   | No load                                                                   |                 |                        |                 | Vcc  |       |

| Change in Magnitude of<br>Differential Output Voltage | ΔV <sub>OD</sub>  | $R_{\text{DIFF}} = 100\Omega \text{ or } 54\Omega, \text{ Fig}$           | ure 1 (Note 3)  |                        |                 | 0.2  | V     |

| Driver Common-Mode Output<br>Voltage                  | Voc               | $R_{\text{DIFF}} = 100\Omega \text{ or } 54\Omega, \text{ Fig}$           | ure 1           |                        | V <sub>CC</sub> | 3    | V     |

| Change in Magnitude of Common-Mode Voltage            | ΔV <sub>OC</sub>  | $R_{\text{DIFF}} = 100\Omega \text{ or } 54\Omega, \text{ Fig}$           | ure 1 (Note 3)  |                        |                 | 0.2  | V     |

| Input-High Voltage                                    | VIH               | DI, DE, RE                                                                |                 | 2.0                    |                 |      | V     |

| Input-Low Voltage                                     | VIL               | DI, DE, RE                                                                |                 |                        |                 | 0.8  | V     |

| Input Current                                         | I <sub>IN</sub>   | DI, DE, RE                                                                |                 |                        |                 | ±1   | μΑ    |

| Driver Short-Circuit Output                           | loon              | 0V <u>&lt;</u> V <sub>OUT</sub> <u>&lt;</u> +12V                          |                 | +50                    |                 | +250 | mA    |

| Current (Note 4)                                      | losp              | -7V <u>&lt;</u> V <sub>OUT</sub> <u>&lt;</u> 0V                           |                 | -250                   |                 | -50  | MA    |

| Driver Short-Circuit Foldback                         | loons             | $(V_{CC} - 1V) \leq V_{OUT} \leq +12V_{OUT}$                              | V               | 20                     |                 |      | mA    |

| Output Current Note 3)                                | losdf             | -7V ≤ V <sub>OUT</sub> ≤ 0V                                               |                 |                        |                 | -20  | IIIA  |

| RECEIVER                                              |                   |                                                                           |                 |                        |                 |      |       |

| Input Current (A and B)                               | la B              | DE = GND, V <sub>CC</sub> = GND                                           | $V_{IN} = +12V$ |                        |                 | 250  |       |

| input Current (A and B)                               | I <sub>A, B</sub> | or +5V                                                                    | $V_{IN} = -7V$  | -200                   |                 |      | μΑ    |

| Receiver-Differential-Threshold Voltage               | VTH               | -7V ≤ V <sub>CM</sub> ≤ +12V                                              |                 | -200                   |                 | -50  | mV    |

| Receiver Input Hysteresis                             | ΔVTH              | $V_A + V_B = 0V$                                                          |                 |                        | 25              |      | mV    |

| Output-High Voltage                                   | VOH               | I <sub>O</sub> = -1.6mA, V <sub>A</sub> - V <sub>B</sub> > V <sub>T</sub> | Н               | V <sub>C</sub> C - 1.5 |                 |      | V     |

## **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>CC</sub> = +5V ±5%, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at V<sub>CC</sub> = +5V and T<sub>A</sub> = +25°C.) (Notes 1, 2)

| PARAMETER                                | SYMBOL           | CONDITIONS                                    | MIN  | TYP | MAX  | UNITS |

|------------------------------------------|------------------|-----------------------------------------------|------|-----|------|-------|

| Output-Low Voltage                       | V <sub>OL</sub>  | $I_O = 1$ mA, $V_A - V_B < -V_{TH}$           |      |     | 0.4  | V     |

| Tri-State Output Current at Receiver     | I <sub>OZR</sub> | $0V \le V_O \le V_{CC}$                       |      |     | ±1   | μΑ    |

| Receiver Input Resistance                | RIN              | -7V ≤ V <sub>CM</sub> ≤ +12V                  | 48   |     |      | kΩ    |

| Receiver-Output Short-Circuit<br>Current | Iosr             | 0V ≤ V <sub>RO</sub> ≤ V <sub>CC</sub>        | ±7   |     | ±95  | mA    |

| POWER SUPPLY                             | •                |                                               |      |     |      |       |

| Supply Voltage                           | Vcc              |                                               | 4.75 |     | 5.25 | V     |

| Supply Current                           | Icc              | $DE = 1$ , $\overline{RE} = 0$ , no load      |      |     | 4.5  | mA    |

| Shutdown Supply Current                  | ISHDN            | $DE = 0, \overline{RE} = 1$                   |      |     | 10   | μΑ    |

| ESD PROTECTION                           |                  |                                               |      |     |      |       |

| ESD Protection (A, B)                    |                  | Air Gap Discharge IEC61000-4-2<br>(MAX13485E) |      | ±15 |      | kV    |

|                                          |                  | Human Body Model                              |      | ±15 |      |       |

| ESD Protection (All Other Pins)          |                  | Human Body Model                              |      | ±2  |      | kV    |

### SWITCHING CHARACTERISTICS—MAX13485E

$(V_{CC} = +5V \pm 5\%, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +5V \text{ and } T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                                          | SYMBOL                  | CONDITIONS                                                               | MIN | TYP | MAX  | UNITS |

|----------------------------------------------------|-------------------------|--------------------------------------------------------------------------|-----|-----|------|-------|

| DRIVER                                             |                         |                                                                          |     |     |      |       |

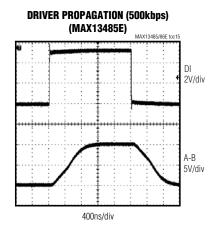

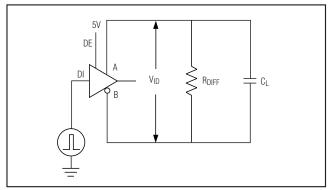

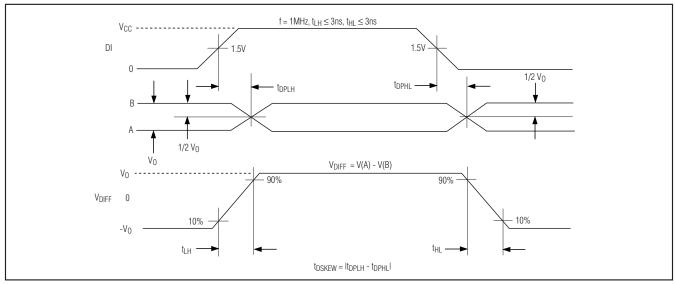

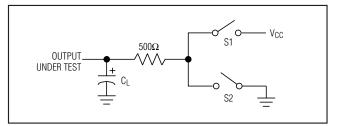

| Driver Propagation Delay                           | tDPLH                   | Doing 540 C. FONE Figures 2 and 2                                        | 200 |     | 1000 | 200   |

| Driver Propagation Delay                           | tDPHL                   | $R_{DIFF} = 54\Omega$ , $C_L = 50pF$ , Figures 2 and 3                   | 200 |     | 1000 | ns    |

| Driver-Differential Output Rise or                 | tHL                     | $R_{DIFF} = 54\Omega$ , $C_L = 50pF$ , Figures 2 and 3                   | 250 |     | 900  | ns    |

| Fall Time                                          | tLH                     | 11DIFF = 3432, GL = 30pr , rigures 2 and 3                               | 250 |     | 900  | 115   |

| Driver-Differential Output Skew<br>ltDPLH - tDPHLI | tdskew                  | $R_{\text{DIFF}}$ = 54 $\Omega$ , $C_{\text{L}}$ = 50pF, Figures 2 and 3 |     |     | 140  | ns    |

| Maximum Data Rate                                  |                         |                                                                          | 500 |     |      | kbps  |

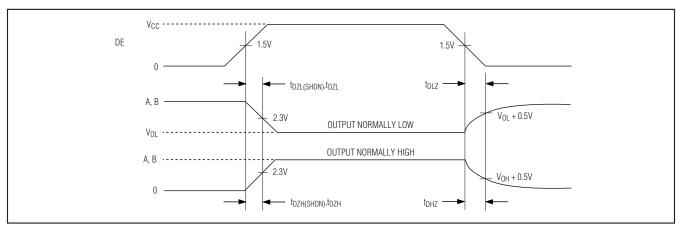

| Driver Enable to Output High                       | tdzh                    | Figures 4 and 5                                                          |     |     | 2500 | ns    |

| Driver Enable to Output Low                        | t <sub>DZL</sub>        | Figures 4 and 5                                                          |     |     | 2500 | ns    |

| Driver Disable Time from High                      | tDHZ                    | Figures 4 and 5                                                          |     |     | 100  | ns    |

| Driver Disable Time from Low                       | t <sub>DLZ</sub>        | Figures 4 and 5                                                          |     |     | 100  | ns    |

| Driver Enable from Shutdown to<br>Output High      | t <sub>DZH</sub> (SHDN) | Figures 4 and 5                                                          |     |     | 5500 | ns    |

| Driver Enable from Shutdown to Output Low          | t <sub>DZL</sub> (SHDN) | Figures 4 and 5                                                          |     |     | 5500 | ns    |

| Time to Shutdown                                   | tshdn                   |                                                                          | 50  | 340 | 700  | ns    |

| RECEIVER                                           |                         |                                                                          |     |     |      |       |

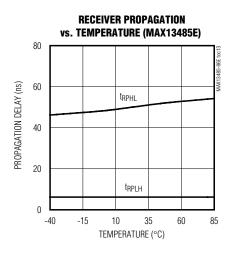

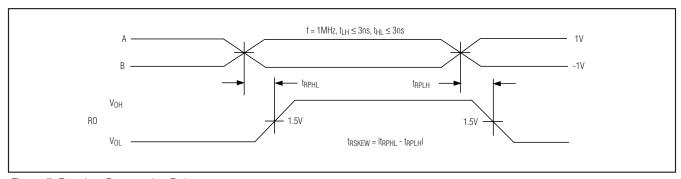

| Pageiver Propagation Polary                        | trplh                   | C. 15pc Figures 6 and 7                                                  |     |     | 80   | 200   |

| Receiver Propagation Delay                         | trphl                   | C <sub>L</sub> = 15pF, Figures 6 and 7                                   |     |     | 80   | ns    |

| Receiver Output Skew                               | trskew                  | C <sub>L</sub> = 15pF, Figure 7                                          |     |     | 13   | ns    |

| Maximum Data Rate                                  |                         |                                                                          | 500 |     |      | kbps  |

## **SWITCHING CHARACTERISTICS—MAX13485E (continued)**

$(V_{CC} = +5V \pm 5\%, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +5V \text{ and } T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                                    | SYMBOL           | CONDITIONS | MIN | TYP | MAX  | UNITS |

|----------------------------------------------|------------------|------------|-----|-----|------|-------|

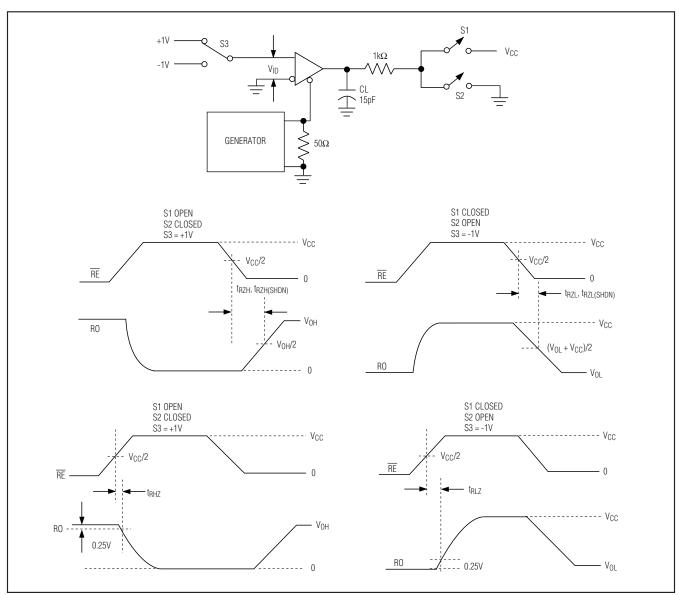

| Receiver Enable to Output High               | trzh             | Figure 8   |     |     | 50   | ns    |

| Receiver Enable to Output Low                | t <sub>RZL</sub> | Figure 8   |     |     | 50   | ns    |

| Receiver Disable Time from High              | trhz             | Figure 8   |     |     | 50   | ns    |

| Receiver Disable Time from Low               | t <sub>RLZ</sub> | Figure 8   |     |     | 50   | ns    |

| Receiver Enable from Shutdown to Output High | tRZH(SHDN)       | Figure 8   |     |     | 2200 | ns    |

| Receiver Enable from Shutdown to Output Low  | tRZL(SHDN)       | Figure 8   |     |     | 2200 | ns    |

| Time to Shutdown                             | tshdn            |            | 50  | 340 | 700  | ns    |

### **SWITCHING CHARACTERISTICS—MAX13486E**

$(V_{CC} = +5V \pm 5\%, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +5V \text{ and } T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                                       | SYMBOL                  | CONDITIONS                                                                 | MIN | TYP | MAX  | UNITS |

|-------------------------------------------------|-------------------------|----------------------------------------------------------------------------|-----|-----|------|-------|

| DRIVER                                          |                         |                                                                            |     |     |      |       |

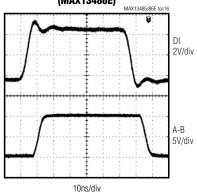

| Driver Presentian Delay                         | tdplh                   | Devel 540 Ct. FORE Figures 2 and 2                                         |     |     | 50   |       |

| Driver Propagation Delay                        | tDPHL                   | $R_{DIFF} = 54\Omega$ , $C_L = 50$ pF, Figures 2 and 3                     |     |     | 50   | ns    |

| Driver Differential Output Rise or              | tHL                     | Daves 540 Ct. FORE Figures 2 and 2                                         |     |     | 15   |       |

| Fall Time                                       | tLH                     | R <sub>DIFF</sub> = $54\Omega$ , C <sub>L</sub> = $50$ pF, Figures 2 and 3 |     |     | 15   | ns    |

| Differential Driver Output Skew ItDPLH - tDPHLI | tDSKEW                  | $R_{DIFF}$ = 54 $\Omega$ , $C_L$ = 50pF, Figures 2 and 3                   |     |     | 8    | ns    |

| Maximum Data Rate                               |                         |                                                                            | 16  |     |      | Mbps  |

| Driver Enable to Output High                    | tdzh                    | Figures 4 and 5                                                            |     |     | 50   | ns    |

| Driver Enable to Output Low                     | t <sub>DZL</sub>        | Figures 4 and 5                                                            |     |     | 50   | ns    |

| Driver Disable Time from High                   | tDHZ                    | Figures 4 and 5                                                            |     |     | 50   | ns    |

| Driver Disable Time from Low                    | t <sub>DLZ</sub>        | Figures 4 and 5                                                            |     |     | 50   | ns    |

| Driver Enable from Shutdown to Output High      | t <sub>DZH</sub> (SHDN) | Figures 4 and 5                                                            |     |     | 2200 | ns    |

| Driver Enable from Shutdown to Output Low       | tDZL(SHDN)              | Figures 4 and 5                                                            |     |     | 2200 | ns    |

| Time to Shutdown                                | tshdn                   |                                                                            | 50  | 340 | 700  | ns    |

| RECEIVER                                        |                         |                                                                            |     |     |      |       |

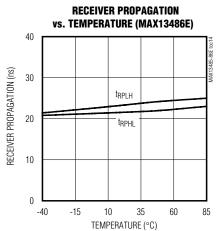

| Receiver Propagation Delay                      | trplh                   | C <sub>L</sub> = 15pF, Figures 6 and 7                                     |     |     | 80   | no    |

| neceiver Fropagation Delay                      | trphl                   | OL = 15pr, Figures 6 and 7                                                 |     |     | 80   | ns    |

| Receiver Output Skew                            | trskew                  | C <sub>L</sub> = 15pF, Figure 7                                            |     |     | 13   | ns    |

| Maximum Data Rate                               |                         |                                                                            | 16  |     |      | Mbps  |

### SWITCHING CHARACTERISTICS—MAX13486E (continued)

$(V_{CC} = +5V \pm 5\%, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +5V \text{ and } T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                                    | SYMBOL                  | CONDITIONS | MIN | TYP | MAX  | UNITS |

|----------------------------------------------|-------------------------|------------|-----|-----|------|-------|

| Receiver Enable to Output High               | trzh                    | Figure 8   |     |     | 50   | ns    |

| Receiver Enable to Output Low                | t <sub>RZL</sub>        | Figure 8   |     |     | 50   | ns    |

| Receiver Disable Time from High              | trhz                    | Figure 8   |     |     | 50   | ns    |

| Receiver Disable Time from Low               | t <sub>RLZ</sub>        | Figure 8   |     |     | 50   | ns    |

| Receiver Enable from Shutdown to Output High | tRZH(SHDN)              | Figure 8   |     |     | 2200 | ns    |

| Receiver Enable from Shutdown to Output Low  | t <sub>RZL</sub> (SHDN) | Figure 8   |     |     | 2200 | ns    |

| Time to Shutdown                             | tshdn                   |            | 50  | 340 | 700  | ns    |

Note 1: µDFN devices production tested at +25°C. Overtemperature limits are generated by design.

Note 2: All currents into the device are positive. All currents out of the device are negative. All voltages referred to device ground, unless otherwise noted.

**Note 3:**  $\Delta V_{OD}$  and  $\Delta V_{OC}$  are the changes in  $V_{OD}$  and  $V_{OC}$  when the DI input changes states.

**Note 4:** The short-circuit output current applied to peak current just prior to foldback current limiting. The short-circuit foldback output current applies during current limiting to allow a recovery from bus contention.

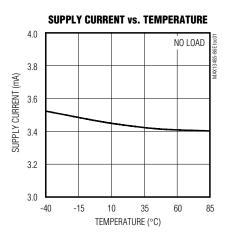

## \_Typical Operating Characteristics

$(V_{CC} = +5V, T_A = +25^{\circ}C, unless otherwise noted.)$

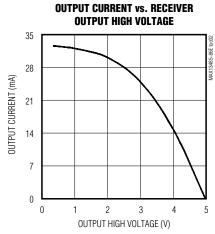

## Typical Operating Characteristics (continued)

$(V_{CC} = +5V, T_A = +25^{\circ}C, unless otherwise noted.)$

MIXIM

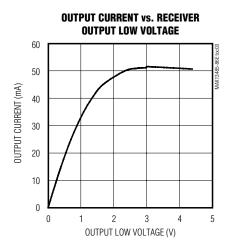

## Typical Operating Characteristics (continued)

$(V_{CC} = +5V, T_A = +25^{\circ}C, unless otherwise noted.)$

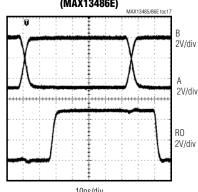

### DRIVER PROPAGATION (16Mbps) (MAX13486E)

### RECEIVER PROPAGATION (16Mbps) (MAX13486E)

### **Test Circuits and Waveforms**

Figure 1. Driver DC Test Load

Figure 2. Driver Timing Test Circuit

Figure 3. Driver Propagation Delays

## Test Circuits and Waveforms (continued)

Figure 4. Driver Enable and Disable Times

Figure 5. Driver-Enable and -Disable-Timing Test Load

Figure 6. Receiver Propagation Delay Test Circuit

Figure 7. Receiver Propagation Delays

## **Pin Description**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                                      |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | RO   | Receiver Output                                                                                                                                                                                                                                                                               |

| 2   | RE   | Receiver Output Enable. Drive $\overline{RE}$ low to enable RO. RO is high impedance when $\overline{RE}$ is high. Drive $\overline{RE}$ high and DE low to enter low-power shutdown mode. $\overline{RE}$ is a hot-swap input (see the <i>Hot-Swap Capability</i> section for more details). |

| 3   | DE   | Driver Output Enable. Drive DE high to enable the driver outputs. These outputs are high-impedance when DE is low. Drive $\overline{\text{RE}}$ high and DE low to enter low-power shutdown mode. DE is a hot-swap input (see the <i>Hot-Swap Capability</i> section for more details).       |

| 4   | DI   | Driver Input. Drive DI low to force noninverting output low and inverting output high. Drive DI high to force noninverting output high and inverting output low (see the <i>Function Tables</i> ).                                                                                            |

| 5   | GND  | Ground                                                                                                                                                                                                                                                                                        |

| 6   | А    | Noninverting Receiver Input and Noninverting Driver Output                                                                                                                                                                                                                                    |

| 7   | В    | Inverting Receiver Input and Inverting Driver Output                                                                                                                                                                                                                                          |

| 8   | Vcc  | Positive Supply, $V_{CC}$ = +5V ±5%. Bypass $V_{CC}$ to GND with a 0.1 $\mu$ F capacitor.                                                                                                                                                                                                     |

## **Function Tables**

|    |       |    | TRANSMITTING   |                |

|----|-------|----|----------------|----------------|

|    | INPUT |    | OUT            | PUT            |

| RE | DE    | DI | В              | А              |

| Χ  | 1     | 1  | 0              | 1              |

| Χ  | 1     | 0  | 1              | 0              |

| 0  | 0     | Χ  | HIGH IMPEDANCE | HIGH IMPEDANCE |

| 1  | 0     | Χ  | SHUTI          | OOWN           |

|    |     | RECEIVING  |                |

|----|-----|------------|----------------|

|    | INP | UT         | OUTPUT         |

| RE | DE  | A-B        | RO             |

| 0  | Χ   | ≥ -50mV    | 1              |

| 0  | Χ   | ≤ -200mV   | 0              |

| 0  | Χ   | OPEN/SHORT | 1              |

| 1  | 1   | Х          | HIGH IMPEDANCE |

| 1  | 0   | Х          | SHUTDOWN       |

X = Don't care, shutdown mode, driver, and receiver outputs are in high impedance.

## Test Circuits and Waveforms (continued)

Figure 8. Receiver Enable and Disable Times

MIXIM \_\_\_\_\_ MIXIM

## **Detailed Description**

The MAX13485E/MAX13486E half-duplex, high-speed transceivers for RS-485/RS-422 communication contain one driver and one receiver. These devices feature failsafe circuitry that guarantees a logic-high receiver output when receiver inputs are open or shorted, or when they are connected to a terminated transmission line with all drivers disabled (see the Fail-Safe section). The MAX13485E/MAX13486E also feature a hot-swap capability allowing line insertion without erroneous data transfer (see the Hot-Swap Capability section). The MAX13485E features reduced slew-rate drivers that minimize EMI and reduce reflections caused by improperly terminated cables, allowing error-free transmission up to 500kbps. The MAX13486E driver slew rate is not limited, making transmit speeds up to 16Mbps possible.

#### Fail-Safe

The MAX13485E/MAX13486E guarantee a logic-high receiver output when the receiver inputs are shorted or open, or when they are connected to a terminated transmission line with all drivers disabled. This is done by setting the receiver input threshold between -50mV and -200mV. If the differential receiver input voltage (A - B) is greater than or equal to -50mV, RO is logic-high. If (A - B) is less than or equal to -200mV, RO is logic-low. In the case of a terminated bus with all transmitters disabled, the receiver's differential input voltage is pulled to 0V by the termination. With the receiver thresholds of the MAX13485E/MAX13486E, this results is a logic-high with a 50mV minimum noise margin. Unlike previous fail-safe devices, the -50mV to -200mV threshold complies with the ±200mV EIA/TIA-485 standard.

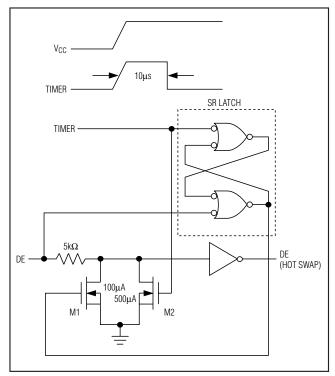

# Hot-Swap Capability Hot-Swap Inputs

When circuit boards are inserted into a hot or powered backplane, differential disturbances to the data bus can lead to data errors. Upon initial circuit-board insertion, the data communication processor undergoes its own power-up sequence. During this period, the processor's logic-output drivers are high impedance and are unable to drive the DE and  $\overline{\text{RE}}$  inputs of these devices to a defined logic level. Leakage currents up to  $\pm 10 \mu A$  from the high impedance state of the processor's logic drivers could cause standard CMOS enable inputs of a transceiver to drift to an incorrect logic level. Additionally, parasitic circuit-board capacitance could cause coupling of VCC or GND to the enable inputs. Without the hot-swap capability, these factors could improperly enable the transceiver's driver or receiver.

Figure 9. Simplified Structure of the Driver Enable Pin (DE)

When  $V_{CC}$  rises, an internal pulldown circuit holds DE low and  $\overline{RE}$  high. After the initial power-up sequence, the pulldown circuit becomes transparent, resetting the hot-swap tolerable input.

### Hot-Swap Input Circuitry

The enable inputs feature hot-swap capability. At the input there are two nMOS devices, M1 and M2 (Figure 9). When VCC ramps from zero, an internal 7µs timer turns on M2 and sets the SR latch, which also turns on M1. Transistors M2, a 1.5mA current sink, and M1, a 500 $\mu$ A current sink, pull DE to GND through a 5k $\Omega$ resistor. M2 is designed to pull DE to the disabled state against an external parasitic capacitance up to 100pF that can drive DE high. After 7µs, the timer deactivates M2 while M1 remains on, holding DE low against tristate leakages that can drive DE high. M1 remains on until an external source overcomes the required input current. At this time, the SR latch resets and M1 turns off. When M1 turns off, DE reverts to a standard highimpedance CMOS input. Whenever VCC drops below 1V, the hot-swap input is reset.

For  $\overline{RE}$  there is a complementary circuit employing two pMOS devices pulling  $\overline{RE}$  to  $V_{CC}$ .

Figure 10a. Human Body ESD Test Model

Figure 10b. Human Body Current Waveform

#### +15V ESD Protection

As with all Maxim devices, ESD-protection structures are incorporated on all pins to protect against electrostatic discharges encountered during handling and assembly. The driver outputs and receiver inputs of the MAX13485E/MAX13486E have extra protection against static electricity. Maxim's engineers have developed state-of-the-art structures to protect these pins against ESD of ±15kV without damage. The ESD structures withstand high ESD in all states: normal operation, shutdown, and powered down. After an ESD event, the MAX13485E/MAX13486E keep working without latchup or damage.

ESD protection can be tested in various ways. The transmitter outputs and receiver inputs of the MAX13485E/MAX13486E are characterized for protection to the following limits:

- ±15kV using the Human Body Model

- ±15kV using the Air Gap Discharge Method specified in IEC 61000-4-2 (MAX13485E only)

Figure 10c. IEC 61000-4-2 ESD Test Model

Figure 10d. IEC 61000-4-2 ESD Generator Current Waveform

#### ESD Test Conditions

ESD performance depends on a variety of conditions. Contact Maxim for a reliability report that documents test setup, test methodology, and test results.

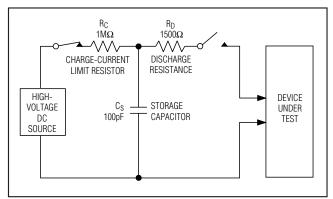

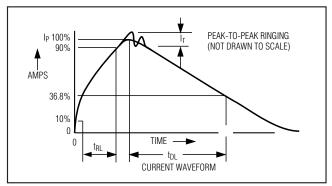

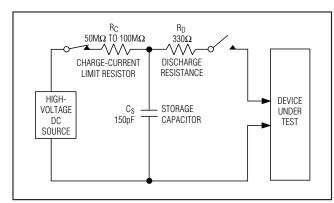

### Human Body Model

Figure 10a shows the Human Body Model, and Figure 10b shows the current waveform it generates when discharged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the test device through a 1.5k $\Omega$  resistor.

#### IEC 61000-4-2

The IEC 61000-4-2 standard covers ESD testing and performance of finished equipment. However, it does not specifically refer to integrated circuits. The MAX13485E/MAX13486E help equipment designs to meet IEC 61000-4-2, without the need for additional ESD-protection components.

The major difference between tests done using the Human Body Model and IEC 61000-4-2 is higher peak current in IEC 61000-4-2 because series resistance is lower in the IEC 61000-4-2 model. Hence, the ESD

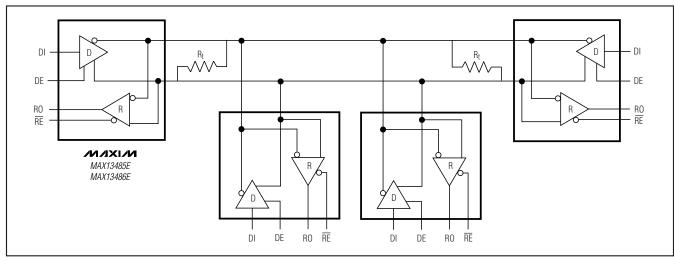

Figure 11. Typical Half-Duplex RS-485 Network

withstand voltage measured to IEC 61000-4-2 is generally lower than that measured using the Human Body Model. Figure 10c shows the IEC 61000-4-2 model, and Figure 10d shows the current waveform for the IEC 61000-4-2 ESD Contact Discharge test.

### Machine Model

The machine model for ESD tests all pins using a 200pF storage capacitor and zero discharge resistance.

The objective is to emulate the stress caused when I/O pins are contacted by handling equipment during test and assembly. Of course, all pins require this protection, not just RS-485 inputs and outputs.

The air-gap test involves approaching the device with a charged probe. The contact-discharge method connects the probe to the device before the probe is energized.

## \_Applications Information

#### 128 Transceivers on the Bus

The standard RS-485 receiver input impedance is  $12k\Omega$  (1-unit load), and the standard driver can drive up to 32-unit loads. The MAX13485E/MAX13486E have a 1/4-unit load receiver input impedance (48k $\Omega$ ), allowing up to 128 transceivers to be connected in parallel on one communication line. Any combination of these devices, as well as other RS-485 transceivers with a total of 32-unit loads or fewer, can be connected to the line.

#### **Reduced EMI and Reflections**

The MAX13485E features reduced slew-rate drivers that minimize EMI and reduce reflections caused by improperly terminated cables, allowing error-free data transmission up to 500kbps.

#### **Low-Power Shutdown Mode**

Low-power shutdown mode is initiated by bringing both  $\overline{RE}$  high and DE low. In shutdown, the devices draw a maximum of 10µA of supply current.

RE and DE can be driven simultaneously. The devices are guaranteed not to enter shutdown if RE is high and DE is low for less than 50ns. If the inputs are in this state for at least 700ns, the devices are guaranteed to enter shutdown.

Enable times tzH and tzL (see the *Switching Characteristics*) assume the devices were not in a low-power shutdown state. Enable times tzH(SHDN) and tzL(SHDN) assume the devices were in shutdown state. It takes drivers and receivers longer to become enabled from low-power shutdown mode (tzH(SHDN), tzL(SHDN)) than from driver-/receiver-disable mode (tzH, tzL).

### Line Length

The RS-485/RS-422 standard covers line lengths up to 4000ft.

#### **Typical Applications**

The MAX13485E/MAX13486E transceivers are designed for half-duplex, bidirectional data communications on multipoint bus transmission lines. Figure 11 shows typical network applications circuits. To minimize reflections, terminate the line at both ends in its characteristic impedance, and keep stub lengths off the main line as short as possible. The slew-rate-limited MAX13485E is more tolerant of imperfect termination.

Chip Information

PROCESS: BICMOS

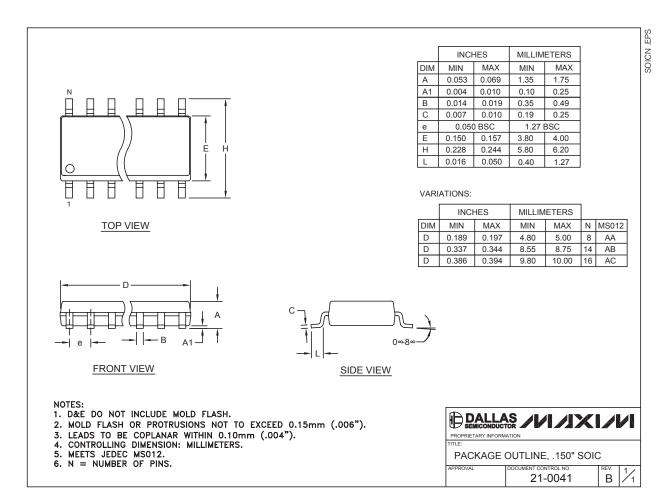

## Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

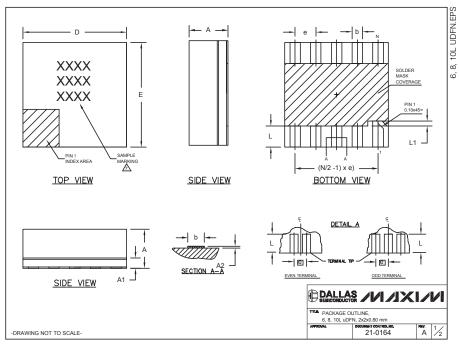

## Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

| SYMBOL   MIN.                                                                                              | e<br>0.65 BS<br>0.50 BS                                                       | SC 0.30                               | b (N/2-1) x e (0±0.05 1.30 REF. (5±0.05 1.50 REF. |

|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------|

| A1 0.15 A2 0.020 D 1.95 E 1.95 L 0.30 L1  PACKAGE VARIATION PKG. CODE N L622-1 6 L822-1 8                  | 0.20<br>0.025<br>2.00<br>2.00<br>0.40<br>0.10 REF.<br>NS  e  0.65 BS  0.50 BS | 0.25<br>0.035<br>2.05<br>2.05<br>0.50 | 0±0.05 1.30 REF.                                  |

| A2 0.020 D 1.95 E 1.95 L 0.30 L1  PACKAGE VARIATION PKG. CODE N L622-1 6 L822-1 8                          | 0.025<br>2.00<br>2.00<br>0.40<br>0.10 REF.                                    | 0.035<br>2.05<br>2.05<br>0.50         | 0±0.05 1.30 REF.                                  |

| D 1.95 E 1.95 L 0.30 L1  PACKAGE VARIATION PKG, CODE N L622-1 6 L822-1 8                                   | 2.00   2.00   0.40   0.10 REF.                                                | 2.05<br>2.05<br>0.50<br>0.50          | 0±0.05 1.30 REF.                                  |

| E 1.95 L 0.30 L1  PACKAGE VARIATION PKG. CODE N L622-1 6 L822-1 8                                          | 2.00<br>0.40<br>0.10 REF.<br>NS<br>e<br>0.65 BS<br>0.50 BS                    | 2.05<br>0.50                          | 0±0.05 1.30 REF.                                  |

| L 0.30 L1  PACKAGE VARIATION PKG. CODE N L622-1 6 L822-1 8                                                 | 0.40<br>0.10 REF.<br>NS<br>e<br>0.65 BS<br>0.50 BS                            | 0.50                                  | 0±0.05 1.30 REF.                                  |

| PACKAGE VARIATION PKG. CODE N L622-1 6 L822-1 8                                                            | 0.10 REF.  NS  e  0.65 BS  0.50 BS                                            | SC 0.30                               | 0±0.05 1.30 REF.                                  |

| PACKAGE VARIATION PKG. CODE N L622-1 6 L822-1 8                                                            | NS e 0.65 BS 0.50 BS                                                          | SC 0.30                               | 0±0.05 1.30 REF.                                  |

| PKG. CODE N<br>L622-1 6<br>L822-1 8                                                                        | e<br>0.65 BS<br>0.50 BS                                                       | SC 0.30                               | 0±0.05 1.30 REF.                                  |

| L822-1 8                                                                                                   | 0.50 BS                                                                       |                                       |                                                   |

| L822-1 8                                                                                                   | 0.50 BS                                                                       |                                       |                                                   |

|                                                                                                            |                                                                               | SC 0.25                               | 5±0.05 1.50 REF.                                  |

| L1022-1 10                                                                                                 | 0.40 BS                                                                       |                                       |                                                   |

|                                                                                                            | 1 3.40 00                                                                     | SC 0.20                               | 0±0.03 1.60 REF.                                  |

| S:<br>L DIMENSIONS ARE<br>IPLANARITY SHALL I<br>NRPAGE SHALL NOT<br>NCKAGE LENGTH/PAI<br>PECIAL CHARACTER! | NOT EXCEE<br>EXCEED (<br>CKAGE WID                                            | ED 0.08r<br>0.10mm.                   | mm.                                               |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

6 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2007 Maxim Integrated Products

is a registered trademark of Maxim Integrated Products, Inc.