## **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage                         | 30V  |

|----------------------------------------|------|

| Switch Voltage                         |      |

| LT1371                                 | 35V  |

| LT1371HV                               | 42V  |

| S/S, SHDN, SYNC Pin Voltage            | 30V  |

| Feedback Pin Voltage (Transient, 10ms) | ±10V |

| Feedback Pin Current 1                 | 0mA  |

| Negative Feedback Pin Voltage          |      |

| (Transient, 10ms) ±                    | ±10V |

|                                        |      |

| Operating Ambient Temperature Range  |                |

|--------------------------------------|----------------|

| Operating Junction Temperature Range |                |

| Commercial                           | 0°C to 125°C   |

| Industrial                           | -40°C to 125°C |

| Short Circuit                        | 0°C to 150°C   |

| Storage Temperature Range            | -65°C to 150°C |

| Lead Temperature (Soldering, 10 sec) | 300°C          |

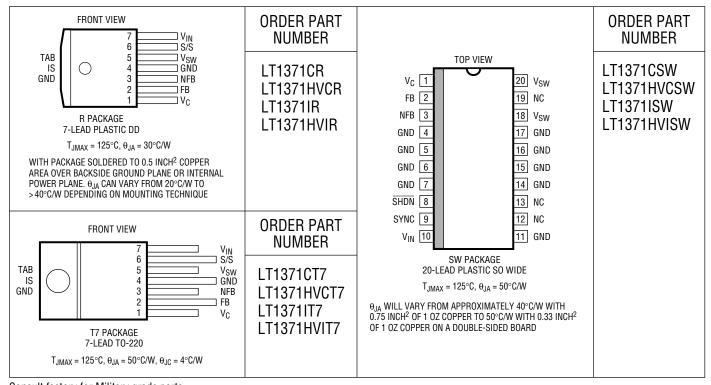

# PACKAGE/ORDER INFORMATION

Consult factory for Military grade parts.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 5V,  $V_{C}$  = 0.6V,  $V_{FB}$  =  $V_{REF}$ ,  $V_{SW}$ , S/S,  $\overline{SHDN}$ , SYNC and NFB pins open, unless otherwise noted.

| SYMBOL          | PARAMETER                         | CONDITIONS                            |   | MIN   | TYP   | MAX   | UNITS |

|-----------------|-----------------------------------|---------------------------------------|---|-------|-------|-------|-------|

| $V_{REF}$       | Reference Voltage                 | Measured at Feedback Pin              |   | 1.230 | 1.245 | 1.260 | V     |

|                 |                                   | $V_C = 0.8V$                          | • | 1.225 | 1.245 | 1.265 | V     |

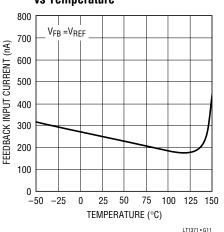

| I <sub>FB</sub> | Feedback Input Current            | $V_{FB} = V_{REF}$                    |   |       | 250   | 550   | nA    |

|                 |                                   |                                       | • |       |       | 900   | nA    |

|                 | Reference Voltage Line Regulation | $2.7V \le V_{IN} \le 25V, V_C = 0.8V$ | • |       | 0.01  | 0.03  | %/V   |

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 5V,  $V_{C}$  = 0.6V,  $V_{FB}$  =  $V_{REF}$ ,  $V_{SW}$ , S/S,  $\overline{SHDN}$ , SYNC and NFB pins open, unless otherwise noted.

| SYMBOL                                | PARAMETER                                              | CONDITIONS                                                                                                                                                                                                                                                                                      |   | MIN               | TYP              | MAX               | UNITS                    |

|---------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------------|------------------|-------------------|--------------------------|

| V <sub>NFB</sub>                      | Negative Feedback Reference Voltage                    | Measured at Negative Feedback Pin<br>Feedback Pin Open, V <sub>C</sub> = 0.8V                                                                                                                                                                                                                   | • | -2.540<br>-2.570  | -2.490<br>-2.490 | -2.440<br>-2.410  | V<br>V                   |

| I <sub>NFB</sub>                      | Negative Feedback Input Current                        | V <sub>NFB</sub> = V <sub>NFR</sub>                                                                                                                                                                                                                                                             | • | -45               | -30              | -15               | μΑ                       |

|                                       | Negative Feedback Reference Voltage<br>Line Regulation | $2.7V \le V_{IN} \le 25V, V_C = 0.8V$                                                                                                                                                                                                                                                           | • |                   | 0.01             | 0.05              | %/V                      |

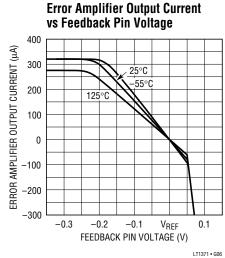

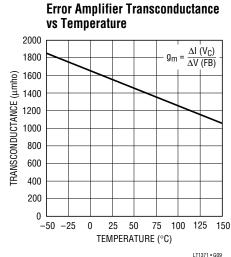

| g <sub>m</sub>                        | Error Amplifier Transconductance                       | $\Delta I_C = \pm 25 \mu A$                                                                                                                                                                                                                                                                     | • | 1100<br>700       | 1500             | 1900<br>2300      | μmho<br>μmho             |

|                                       | Error Amplifier Source Current                         | $V_{FB} = V_{REF} - 150 \text{mV}, V_{C} = 1.5 \text{V}$                                                                                                                                                                                                                                        | • | 120               | 200              | 350               | μΑ                       |

|                                       | Error Amplifier Sink Current                           | $V_{FB} = V_{REF} + 150 \text{mV}, V_{C} = 1.5 \text{V}$                                                                                                                                                                                                                                        | • |                   | 1400             | 2400              | μΑ                       |

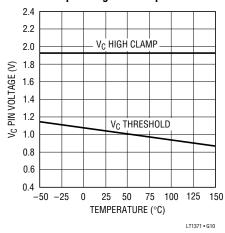

|                                       | Error Amplifier Clamp Voltage                          | High Clamp, V <sub>FB</sub> = 1V<br>Low Clamp, V <sub>FB</sub> = 1.5V                                                                                                                                                                                                                           |   | 1.70<br>0.25      | 1.95<br>0.40     | 2.30<br>0.52      | V<br>V                   |

| A <sub>V</sub>                        | Error Amplifier Voltage Gain                           |                                                                                                                                                                                                                                                                                                 |   |                   | 500              |                   | V/V                      |

| -                                     | V <sub>C</sub> Pin Threshold                           | Duty Cycle = 0%                                                                                                                                                                                                                                                                                 |   | 0.8               | 1                | 1.25              | V                        |

| f                                     | Switching Frequency                                    | $ 2.7V \le V_{\text{IN}} \le 25V \\ 0^{\circ}\text{C} \le T_{\text{J}} \le 125^{\circ}\text{C} \\ -40^{\circ}\text{C} \le T_{\text{J}} \le 0^{\circ}\text{C (I Grade)} $                                                                                                                        | • | 450<br>430<br>400 | 500<br>500       | 550<br>580<br>580 | kHz<br>kHz<br>kHz        |

|                                       | Maximum Switch Duty Cycle                              |                                                                                                                                                                                                                                                                                                 | • | 85                | 95               |                   | %                        |

|                                       | Switch Current Limit Blanking Time                     |                                                                                                                                                                                                                                                                                                 |   |                   | 130              | 260               | ns                       |

| BV                                    | Output Switch Breakdown Voltage                        | LT1371<br>LT1371HV<br>0° C ≤ T <sub>.I</sub> ≤ 125°C                                                                                                                                                                                                                                            | • | 35<br>42          | 47<br>47         |                   | V                        |

|                                       |                                                        | $-40^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq 0^{\circ}\text{C} \text{ (I Grade)}$                                                                                                                                                                                                         |   | 40                |                  |                   | V                        |

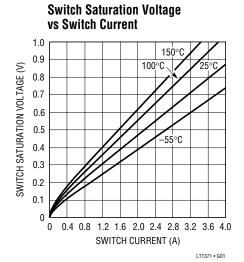

| $V_{SAT}$                             | Output Switch ON Resistance                            | I <sub>SW</sub> = 2A                                                                                                                                                                                                                                                                            | • |                   | 0.25             | 0.45              | Ω                        |

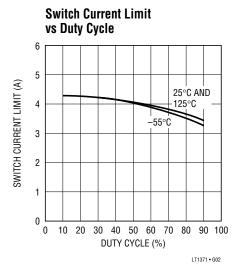

| I <sub>LIM</sub>                      | Switch Current Limit                                   | Duty Cycle = 50%<br>Duty Cycle = 80% (Note 1)                                                                                                                                                                                                                                                   | • | 3.0<br>2.6        | 3.8<br>3.4       | 5.4<br>5.0        | A<br>A                   |

| $\frac{\Delta l_{IN}}{\Delta l_{SW}}$ | Supply Current Increase During Switch ON Time          |                                                                                                                                                                                                                                                                                                 |   |                   | 15               | 25                | mA/A                     |

|                                       | Control Voltage to Switch Current<br>Transconductance  |                                                                                                                                                                                                                                                                                                 |   |                   | 4                |                   | A/V                      |

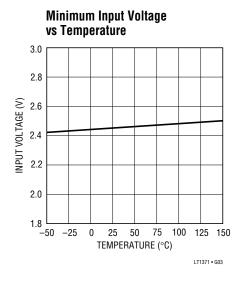

|                                       | Minimum Input Voltage                                  |                                                                                                                                                                                                                                                                                                 | • |                   | 2.4              | 2.7               | V                        |

| IQ                                    | Supply Current                                         | $2.7V \le V_{\text{IN}} \le 25V$                                                                                                                                                                                                                                                                | • |                   | 4                | 5.5               | mA                       |

|                                       | Shutdown Supply Current                                | $ \begin{array}{c} 2.7 \text{V} \leq \text{V}_{\text{IN}} \leq 25 \text{V},  \text{V}_{\text{S/S}} \leq 0.6 \text{V} \\ 0^{\circ}  \text{C} \leq \text{T}_{\text{J}} \leq 125^{\circ} \text{C} \\ -40^{\circ} \text{C} \leq \text{T}_{\text{J}} \leq 0^{\circ} \text{C (I Grade)} \end{array} $ | • |                   | 12               | 30<br>50          | μ <b>Α</b><br>μ <b>Α</b> |

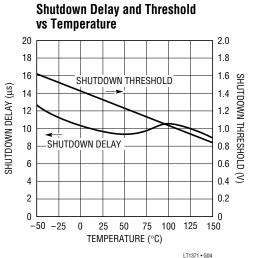

|                                       | Shutdown Threshold                                     | $2.7V \le V_{IN} \le 25V$                                                                                                                                                                                                                                                                       | • | 0.6               | 1.3              | 2                 | V                        |

|                                       | Shutdown Delay                                         |                                                                                                                                                                                                                                                                                                 | • | 5                 | 12               | 25                | μs                       |

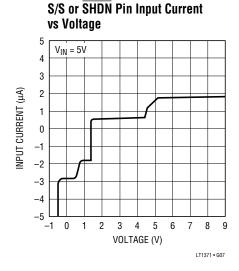

|                                       | S/S or SHDN Pin Input Current                          | $0V \le V_{S/S}$ or $V_{\overline{SHDN}} \le 5V$                                                                                                                                                                                                                                                | • | -10               |                  | 15                | μА                       |

|                                       | Synchronization Frequency Range                        |                                                                                                                                                                                                                                                                                                 | • | 600               |                  | 800               | kHz                      |

The  $\bullet$  denotes specifications which apply over the full operating temperature range.

**Note 1:** For duty cycles (DC) between 50% and 90%, minimum guaranteed switch current is given by  $I_{LIM}$  = 1.33 (2.75 – DC).

## TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

V<sub>C</sub> Pin Threshold and High Clamp Voltage vs Temperature

Feedback Input Current vs Temperature

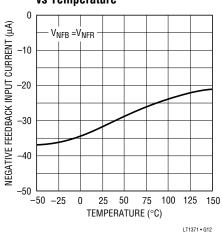

Negative Feedback Input Current vs Temperature

## PIN FUNCTIONS

$V_C$ : The Compensation pin is used for frequency compensation, current limiting and soft start. It is the output of the error amplifier and the input of the current comparator. Loop frequency compensation can be performed with an RC network connected from the  $V_C$  pin to ground.

**FB:** The Feedback pin is used for positive output voltage sensing and oscillator frequency shifting. It is the inverting input to the error amplifier. The noninverting input of this amplifier is internally tied to a 1.245V reference. Load on the FB pin should not exceed 250 $\mu$ A when NFB pin is used. See Applications Information.

**NFB**: The Negative Feedback pin is used for negative output voltage sensing. It is connected to the inverting input of the negative feedback amplifier through a 100k source resistor.

**S/S (R and T7 Packages Only):** Shutdown and Synchronization Pin. The S/S pin is logic level compatible. Shutdown is active low and the shutdown threshold is typically 1.3V. For normal operation, pull the S/S pin high, tie it to  $V_{IN}$  or

leave it floating. To synchronize switching, drive the S/S pin between 600kHz and 800kHz.

**SHDN:** (SW Package Only): The Shutdown pin is active low and the shutdown threshold is typically 1.3V. For normal operation, pull the SHDN pin high, tie it to  $V_{IN}$  or leave it floating.

**SYNC (SW Package Only):** To synchronize switching, drive the SYNC pin between 600kHz and 800kHz. If not used, the SYNC pin can be tied high, low or left floating.

$V_{IN}$ : Bypass Input Supply pin with a low ESR capacitor,  $10\mu F$  or more. The regulator goes into undervoltage lockout when  $V_{IN}$  drops below 2.5V. Undervoltage lockout stops switching and pulls the  $V_C$  pin low.

**V**<sub>SW</sub>: The Switch pin is the collector of the power switch and has large currents flowing through it. Keep the traces to the switching components as short as possible to minimize radiation and voltage spikes.

**GND:** Tie all Ground pins to a good quality ground plane.

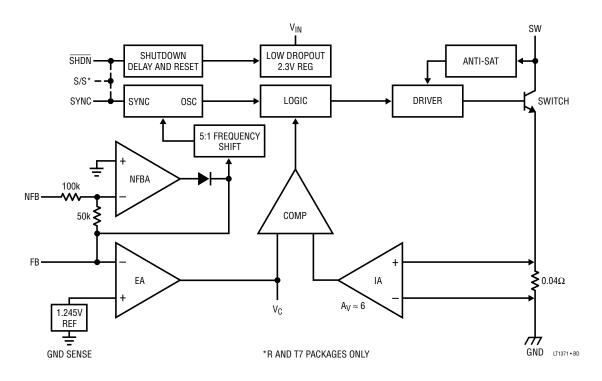

## **BLOCK DIAGRAM**

## **OPERATION**

The LT1371 is a current mode switcher. This means that switch duty cycle is directly controlled by switch current rather than by output voltage. Referring to the block diagram, the switch is turned ON at the start of each oscillator cycle. It is turned OFF when switch current reaches a predetermined level. Control of output voltage is obtained by using the output of a voltage sensing error amplifier to set current trip level. This technique has several advantages. First, it has immediate response to input voltage variations, unlike voltage mode switchers which have notoriously poor line transient response. Second, it reduces the 90° phase shift at mid-frequencies in the energy storage inductor. This greatly simplifies closed-loop frequency compensation under widely varying input voltage or output load conditions. Finally, it allows simple pulse-by-pulse current limiting to provide maximum switch protection under output overload or short conditions. A low dropout internal regulator provides a 2.3V supply for all internal circuitry. This low dropout design allows input voltage to vary from 2.7V to 25V with virtually no change in device performance. A

500kHz oscillator is the basic clock for all internal timing. It turns ON the output switch via the logic and driver circuitry. Special adaptive anti-sat circuitry detects onset of saturation in the power switch and adjusts driver current instantaneously to limit switch saturation. This minimizes driver dissipation and provides very rapid turnoff of the switch.

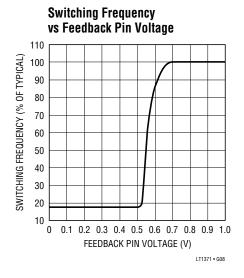

A 1.245V bandgap reference biases the positive input of the error amplifier. The negative input of the amplifier is brought out for positive output voltage sensing. The error amplifier has nonlinear transconductance to reduce output overshoot on start-up or overload recovery. When the feedback voltage exceeds the reference by 40mV, error amplifier transconductance increases 10 times, which reduces output overshoot. The feedback input also invokes oscillator frequency shifting, which helps protect components during overload conditions. When the feedback voltage drops below 0.6V, the oscillator frequency is reduced 5:1. Lower switching frequency allows full control of switch current limit by reducing minimum switch duty cycle.

Unique error amplifier circuitry allows the LT1371 to directly regulate negative output voltages. The negative feedback amplifier's 100k source resistor is brought out for negative output voltage sensing. The NFB pin regulates at -2.49V while the amplifier output internally drives the FB pin to 1.245V. This architecture, which uses the same main error amplifier, prevents duplicating functions and maintains ease of use. Consult LTC Marketing for units that can regulate down to -1.25V.

The error signal developed at the amplifier output is brought out externally. This pin  $(V_C)$  has three different

functions. It is used for frequency compensation, current limit adjustment and soft starting. During normal regulator operation this pin sits at a voltage between 1V (low output current) and 1.9V (high output current). The error amplifier is a current output  $(g_m)$  type, so this voltage can be externally clamped for lowering current limit. Likewise, a capacitor coupled external clamp will provide soft start. Switch duty cycle goes to zero if the  $V_{C}$  pin is pulled below the control pin threshold, placing the LT1371 in an idle mode.

## APPLICATIONS INFORMATION

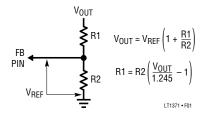

#### **Positive Output Voltage Setting**

The LT1371 develops a 1.245V reference ( $V_{REF}$ ) from the FB pin to ground. Output voltage is set by connecting the FB pin to an output resistor divider (Figure 1). The FB pin bias current represents a small error and can usually be ignored for values of R2 up to 7k. The suggested value for R2 is 6.19k. The NFB pin is normally left open for positive output applications. Positive fixed voltage versions are available (consult LTC Marketing).

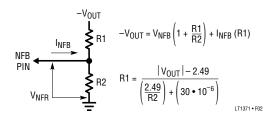

#### **Negative Output Voltage Setting**

The LT1371 develops a -2.49V reference ( $V_{NFR}$ ) from the NFB pin to ground. Output voltage is set by connecting the NFB pin to an output resistor divider (Figure 2). The  $-30\mu A$  NFB pin bias current ( $I_{NFB}$ ) can cause output voltage errors and should not be ignored. This has been accounted for in the formula in Figure 2. The suggested value for R2 is 2.49k. The FB pin is normally left open for negative output applications. See Dual Polarity Output Voltage Sensing for limitations on FB pin loading when using the NFB pin.

#### **Dual Polarity Output Voltage Sensing**

Certain applications benefit from sensing both positive and negative output voltages. One example is the "Dual Output Flyback Converter with Overvoltage Protection" circuit shown in the Typical Applications section. Each output voltage resistor divider is individually set as described above. When both the FB and NFB pins are used,

Figure 1. Positive Output Resistor Divider

Figure 2. Negative Output Resistor Divider

the LT1371 acts to prevent either output from going beyond its set output voltage. For example, in this application if the positive output were more heavily loaded than the negative, the negative output would be greater and would regulate at the desired set-point voltage. The positive output would sag slightly below its set-point voltage. This technique prevents either output from going unregulated high at no load. Please note that the load on the FB pin should not exceed 250µA when the NFB pin is used. This situation occurs when the resistor dividers are used at *both* FB and NFB. True load on FB is not the full divider current unless the positive output is shorted to ground. See Dual Output Flyback Converter application.

### **Shutdown and Synchronization**

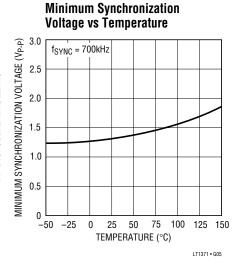

The 7-pin R and T7 package devices have a dual function S/S pin which is used for both shutdown and synchronization. The SW package device has both a Shutdown (SHDN) pin and a Synchronization (SYNC) pin which can be used separately or tied together. These pins are logic level compatible and can be pulled high, tied to  $V_{IN}$  or left floating for normal operation. A logic low on the S/S pin or SHDN pin activates shutdown, reducing the part's supply current to 12 $\mu$ A. Typical synchronization range is from 1.05 to 1.8 times the part's natural switching frequency, but is only guaranteed between 600kHz and 800kHz. A 12 $\mu$ s resetable shutdown delay network guarantees the part will not go into shutdown while receiving a synchronization signal when the functions are combined.

Caution should be used when synchronizing above 700kHz because at higher sync frequencies the amplitude of the internal slope compensation used to prevent subharmonic switching is reduced. This type of subharmonic switching only occurs when the duty cycle of the switch is above 50%. Higher inductor values will tend to eliminate problems.

#### **Thermal Considerations**

Care should be taken to ensure that the worst-case input voltage and load current conditions do not cause excessive die temperatures. Typical thermal resistance is 30°C/W for the R package and 50°C/W for the SW and T7 packages but these numbers will vary depending on the mounting techniques (copper area, air flow, etc.). Heat is transferred from the R and T7 packages via the tab and from the SW package via pins 4 to 7 and 14 to 17.

Average supply current (including driver current) is:

$I_{IN} = 4\text{mA} + DC [I_{SW}/60 + I_{SW} (0.004)]$

I<sub>SW</sub> = switch current

DC = switch duty cycle

Switch power dissipation is given by:

$\mathsf{P}_{\mathsf{SW}} = (\mathsf{I}_{\mathsf{SW}})^2 \; (\mathsf{R}_{\mathsf{SW}})(\mathsf{DC})$

R<sub>SW</sub> = output switch ON resistance

Total power dissipation of the die is the sum of supply current times supply voltage, plus switch power:

$$P_{D(TOTAL)} = (I_{IN})(V_{IN}) + P_{SW}$$

Surface mount heat sinks are also becoming available which can lower package thermal resistance by 2 or 3 times. One manufacturer is Wakefield Engineering who offers surface mount heat sinks for both the R package (DD) and SW package (SW20) and can be reached at (617) 245-5900.

### **Choosing the Inductor**

For most applications the inductor will fall in the range of  $2.2\mu H$  to  $22\mu H$ . Lower values are chosen to reduce physical size of the inductor. Higher values allow more output current because they reduce peak current seen by the power switch, which has a 3A limit. Higher values also reduce input ripple voltage and reduce core loss.

When choosing an inductor you might have to consider maximum load current, core and copper losses, allowable component height, output voltage ripple, EMI, fault current in the inductor, saturation and, of course, cost. The following procedure is suggested as a way of handling these somewhat complicated and conflicting requirements.

- 1. Assume that the average inductor current for a boost converter is equal to load current times V<sub>OUT</sub>/V<sub>IN</sub> and decide whether or not the inductor must withstand continuous overload conditions. If average inductor current at maximum load current is 1A, for instance, a 1A inductor may not survive a continuous 3A overload condition. Also be aware that boost converters are not short-circuit protected and that, under output short conditions, inductor current is limited only by the available current of the input supply.

- 2. Calculate peak inductor current at full load current to ensure that the inductor will not saturate. Peak current can be significantly higher than output current, especially with smaller inductors and lighter loads, so don't omit this step. Powdered iron cores are forgiving because they saturate softly, whereas ferrite cores

saturate abruptly and other core materials fall in between. The following formula assumes continuous mode operation but it errs only slightly on the high side for discontinuous mode, so it can be used for all conditions.

$$I_{PEAK} = (I_{OUT}) \left( \frac{V_{OUT}}{V_{IN}} \right) + \frac{V_{IN}(V_{OUT} - V_{IN})}{2(f)(L)(V_{OUT})}$$

V<sub>IN</sub> = Minimum Input Voltage f = 500kHz Switching Frequency

- 3. Decide if the design can tolerate an "open" core geometry, like a rod or barrel, which has high magnetic field radiation, or whether it needs a closed core, like a toroid, to prevent EMI problems. One would not want an open core next to a magnetic storage media, for instance! This is a tough decision because the rods or barrels are temptingly cheap and small and there are no helpful guidelines to calculate when the magnetic field radiation will be a problem.

- 4. Start shopping for an inductor which meets the requirements of core shape, peak current (to avoid saturation), average current (to limit heating) and fault current. If the inductor gets too hot, wire insulation will melt and cause turn-to-turn shorts. Keep in mind that all good things like high efficiency, low profile and high temperature operation will increase cost, sometimes dramatically.

- 5. After making an initial choice, consider the secondary things like output voltage ripple, second sourcing, etc. Use the experts in the LTC Applications Department if you feel uncertain about the final choice. They have experience with a wide range of inductor types and can tell you about the latest developments in low profile, surface mounting, etc.

#### **Output Capacitor**

The output capacitor is normally chosen by its effective series resistance (ESR), because this is what determines output ripple voltage. At 500kHz any polarized capacitor is essentially resistive. To get low ESR takes *volume*, so

physically smaller capacitors have high ESR. The ESR range needed for typical LT1371 applications is  $0.025\Omega$  to  $0.2\Omega$ . A typical output capacitor is an AVX type TPS,  $22\mu F$  at 25V (2 each), with a guaranteed ESR less than  $0.2\Omega$ . This is a "D" size surface mount solid tantalum capacitor. TPS capacitors are specially constructed and tested for low ESR, so they give the lowest ESR for a given volume. To further reduce ESR, multiple output capacitors can be used in parallel. The value in microfarads is not particularly critical, and values from  $22\mu F$  to greater than  $500\mu F$  work well, but you cannot cheat mother nature on ESR. If you find a tiny  $22\mu F$  solid tantalum capacitor, it will have high ESR and output ripple voltage will be terrible. Table 1 shows some typical solid tantalum surface mount capacitors.

Table 1. Surface Mount Solid Tantalum Capacitor ESR and Ripple Current

| E CASE SIZE           | ESR (MAX $\Omega$ ) | RIPPLE CURRENT (A) |

|-----------------------|---------------------|--------------------|

| AVX TPS, Sprague 593D | 0.1 to 0.3          | 0.7 to 1.1         |

| AVX TAJ               | 0.7 to 0.9          | 0.4                |

| D CASE SIZE           |                     |                    |

| AVX TPS, Sprague 593D | 0.1 to 0.3          | 0.7 to 1.1         |

| AVX TAJ               | 0.9 to 2.0          | 0.36 to 0.24       |

| C CASE SIZE           | •                   |                    |

| AVX TPS               | 0.2 (Typ)           | 0.5 (Typ)          |

| AVX TAJ               | 1.8 to 3.0          | 0.22 to 0.17       |

| B CASE SIZE           |                     |                    |

| AVX TAJ               | 2.5 to 10           | 0.16 to 0.08       |

Many engineers have heard that solid tantalum capacitors are prone to failure if they undergo high surge currents. This is historically true and AVX type TPS capacitors are specially tested for surge capability, but surge ruggedness is not a critical issue with the *output* capacitor. Solid tantalum capacitors fail during very high *turn-on* surges, which do not occur at the output of regulators. High *discharge* surges, such as when the regulator output is dead-shorted, do not harm the capacitors.

Single inductor boost regulators have large RMS ripple current in the output capacitor, which must be rated to handle the current. The formula to calculate this is:

Output Capacitor Ripple Current (RMS)

$$I_{RIPPLE} (RMS) = I_{OUT} \sqrt{\frac{DC}{1 - DC}}$$

$$= I_{OUT} \sqrt{\frac{V_{OUT} - V_{IN}}{V_{IN}}}$$

DC = Switch Duty Cycle

### **Input Capacitors**

The input capacitor of a boost converter is less critical due to the fact that the input current waveform is triangular and does not contain large squarewave currents as is found in the output capacitor. Capacitors in the range of  $10\mu F$  to  $100\mu F$ , with an ESR of  $0.2\Omega$  or less, work well up to full 3A switch current. Higher ESR capacitors may be acceptable at low switch currents. Input capacitor ripple current for a boost converter is :

$$I_{RIPPLE} = \frac{0.3(V_{IN})(V_{OUT} - V_{IN})}{(f)(L)(V_{OUT})}$$

f = 500kHz Switching Frequency

The input capacitor can see a very high surge current when a battery or high capacitance source is connected "live" and solid tantalum capacitors can fail under this condition. Several manufacturers have developed tantalum capacitors specially tested for surge capability (AVX TPS series, for instance) but even these units may fail if the input voltage approaches the maximum voltage rating of the capacitor during a high surge. AVX recommends derating capacitor voltage by 2:1 for high surge applications. Ceramic, OS-CON and aluminum electrolytic capacitors may also be used and have a high tolerance to turn-on surges.

### **Ceramic Capacitors**

Higher value, lower cost ceramic capacitors are now becoming available in smaller case sizes. These are tempting for switching regulator use because of their very low ESR. Unfortunately, the ESR is so low that it can cause loop stability problems. Solid tantalum capacitor ESR

generates a loop "zero" at 5kHz to 50kHz that is instrumental in giving acceptable loop phase margin. Ceramic capacitors remain capacitive to beyond 300kHz and usually resonate with their ESL before ESR becomes effective. They are appropriate for input bypassing because of their high ripple current ratings and tolerance of turn-on surges.

#### **Output Diode**

The suggested output diode (D1) is a 1N5821 Schottky or its Motorola equivalent MBR330. It is rated at 3A average forward current and 30V reverse voltage. Typical forward voltage is 0.6V at 3A. The diode conducts current only during switch OFF time. Peak reverse voltage for boost converters is equal to regulator output voltage. Average forward current in normal operation is equal to output current.

#### **Frequency Compensation**

Loop frequency compensation is performed on the output of the error amplifier ( $V_C$  pin) with a series RC network. The main pole is formed by the series capacitor and the output impedance ( $\approx 500 k\Omega$ ) of the error amplifier. The pole falls in the range of 2Hz to 20Hz. The series resistor creates a "zero" at 1kHz to 5kHz, which improves loop stability and transient response. A second capacitor, typically one-tenth the size of the main compensation capacitor, is sometimes used to reduce the switching frequency ripple on the  $V_C$  pin.  $V_C$  pin ripple is caused by output voltage ripple attenuated by the output divider and multiplied by the error amplifier. Without the second capacitor,  $V_C$  pin ripple is:

$$V_C$$

Pin Ripple =

$$\frac{1.245(V_{RIPPLE})(g_m)(R_C)}{(V_{OUT})}$$

$$\begin{split} &V_{RIPPLE} = Output \ ripple \ (V_{P-P}) \\ &g_m = Error \ amplifier \ transconductance \\ & (\approx \! 1500 \mu mho) \\ &R_C = Series \ resistor \ on \ V_C \ pin \\ &V_{OUT} = DC \ output \ voltage \end{split}$$

To prevent irregular switching,  $V_C$  pin ripple should be kept below  $50mV_{P-P}$ . Worst-case  $V_C$  pin ripple occurs at

maximum output load current and will also be increased if poor quality (high ESR) output capacitors are used. The addition of a 0.0047 $\mu$ F capacitor on the V<sub>C</sub> pin reduces switching frequency ripple to only a few millivolts. A low value for R<sub>C</sub> will also reduce V<sub>C</sub> pin ripple, but loop phase margin may be inadequate.

### **Layout Considerations**

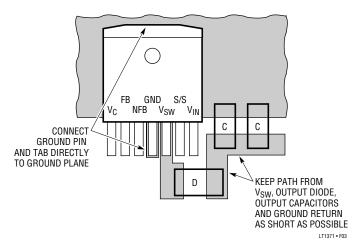

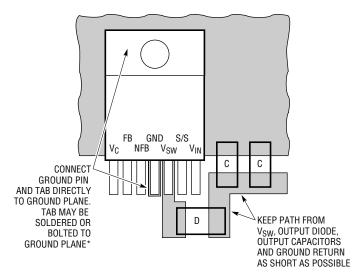

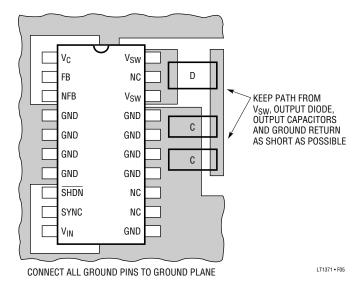

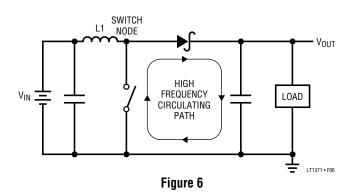

For maximum efficiency, LT1371 switch rise and fall times are made as short as possible. To prevent radiation and high frequency resonance problems, proper layout of the components connected to the switch node is essential. B field (magnetic) radiation is minimized by keeping output diode, Switch pin and output bypass capacitor leads as short as possible. Figures 3, 4 and 5 show recommended positions for these components. E field radiation is kept low by minimizing the length and area of all traces connected to the Switch pin. A ground plane should always be used under the switcher circuitry to prevent interplane coupling.

The high speed switching current path is shown schematically in Figure 6. Minimum lead length in this path is essential to ensure clean switching and low EMI. The path including the switch, output diode and output capacitor is the only one containing nanosecond rise and fall times. Keep this path as short as possible.

Figure 3. Layout Considerations—R Package

\*SEE T7 PACKAGE LAYOUT CONSIDERATIONS FOR VERTICAL MOUNTING OF THE T7 PACKAGE

LT1371 • F04

Figure 4. Layout Considerations—T7 Package

Figure 5. Layout Considerations—SW Package

### **T7 Package Layout Considerations**

Electrical connection to the tab of a T7 package is required for proper device operation. If the tab is tied directly to the ground plane (Figure 4) no other considerations are necessary. If the tab is not connected directly to the ground plane, as in a vertically mounted application, a separate electrical connection from the tab to a "floating node" is required. Ground returns for the  $V_{IN}$  capacitor,  $V_C$  components and output feedback resistor divider are then connected to the floating node. This is shown schematically in Figure 7. All other system ground connections are made to Pin 4.

The electrical connection from the T7 package tab to the floating node must be a low resistance ( $<0.1\Omega$ ), low inductance (<20nH) path which can be accomplished with a jumper wire or an electrically conductive heat sink.

Bolt the jumper wire directly to the tab using a solder tail to maintain low resistance. The jumper wire length should not exceed 3/4 inch of 24 AWG gauge wire or larger to minimize the inductance.

Vertically mounted electrically conductive heat sinks are available from many heat sink manufacturers. These heat sinks also have tabs that solder directly to the board creating the required low resistance, low inductance path from the tab to the floating node. The tab should be bolted

Figure 7. Tab Connections for Vertically Mounted T7 Package

or soldered directly to the heat sink to maintain low resistance. Heat sinks are available in clip-on styles but are only recommended if the tab to heat sink contact resistance can be maintained below  $0.1\Omega$  for the life of the product.

#### More Help

For more detailed information on switching regulator circuits, please see Application Note 19. Linear Technology also offers a computer software program, SwitcherCAD, to assist in designing switching converters. In addition, our Applications Department is always ready to lend a helping hand.

## TYPICAL APPLICATIONS

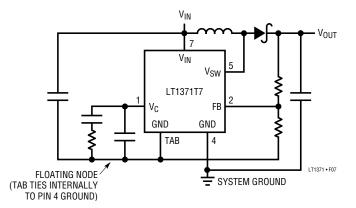

#### Positive-to-Negative Converter with Direct Feedback

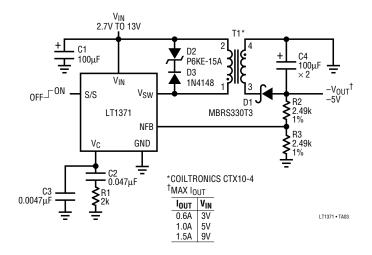

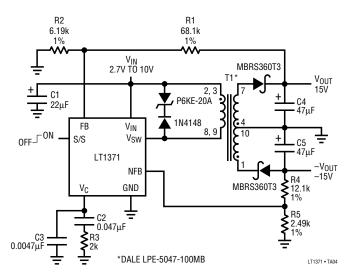

#### **Dual Output Flyback Converter with Overvoltage Protection**

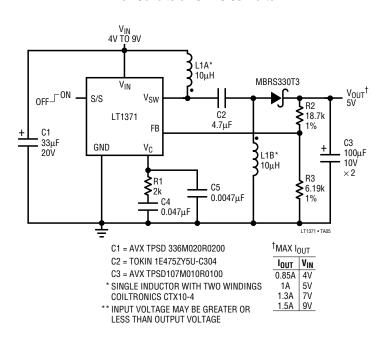

#### 2 Li-Ion Cells to 5V SEPIC Converter\*\*

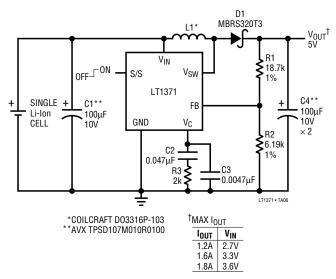

#### Single Li-Ion Cell to 5V

# TYPICAL APPLICATIONS

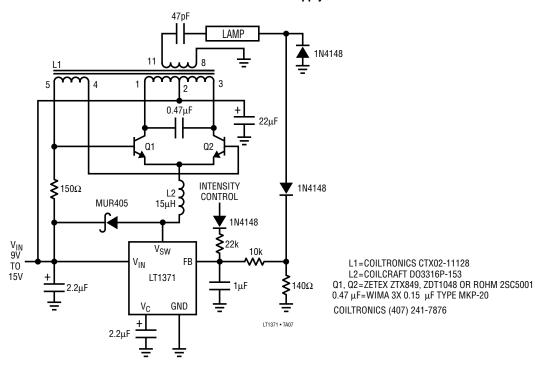

#### 20W CCFL Supply

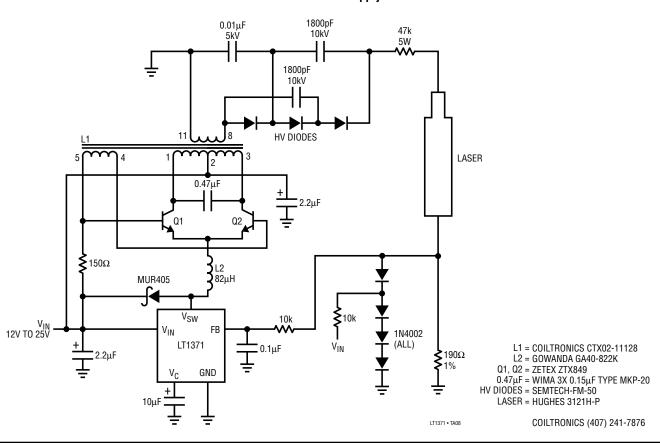

## **Laser Power Supply**

## PACKAGE DESCRIPTION

$\label{lem:decomposition} \textbf{Dimensions in inches (millimeters) unless otherwise noted.}$

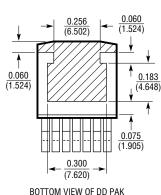

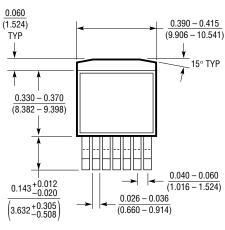

### R Package 7-Lead Plastic DD Pak

(LTC DWG # 05-08-1462)

BOTTOM VIEW OF DD PAK HATCHED AREA IS SOLDER PLATED COPPER HEAK SINK

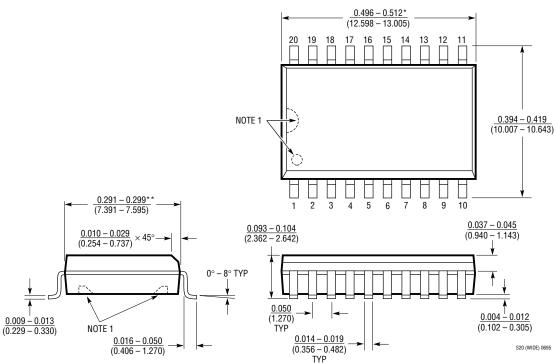

#### SW Package 20-Lead Plastic Small Outline (Wide 0.300)

(LTC DWG # 05-08-1620)

#### NOTE:

- 1. PIN 1 IDENT, NOTCH ON TOP AND CAVITIES ON THE BOTTOM OF PACKAGES ARE THE MANUFACTURING OPTIONS.

THE PART MAY BE SUPPLIED WITH OR WITHOUT ANY OF THE OPTIONS

- \*DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

- \*\*DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

## PACKAGE DESCRIPTION

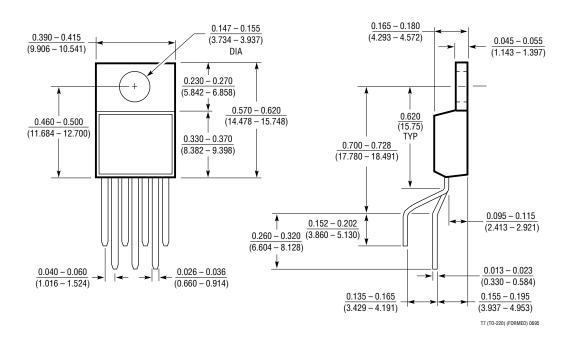

Dimensions in inches (millimeters) unless otherwise noted.

#### T7 Package 7-Lead Plastic T0-220 (Standard)

(LTC DWG # 05-08-1422)

# RELATED PARTS

| PART NUMBER | DESCRIPTION                                              | COMMENTS                                                  |

|-------------|----------------------------------------------------------|-----------------------------------------------------------|

| LT1171      | 100kHz 2.5A Boost Switching Regulator                    | Good for Up to V <sub>IN</sub> = 40V                      |

| LTC®1265    | 12V 1.2A Monolithic Buck Converter                       | Converts 5V to 3.3V at 1A with 90% Efficiency             |

| LT1302      | Micropower 2A Boost Converter                            | Converts 2V to 5V at 600mA in SO-8 Packages               |

| LT1372      | 500kHz 1.5A Boost Switching Regulator                    | Also Regulates Negative Flyback Outputs                   |

| LT1373      | Low Supply Current 250kHz 1.5A Boost Switching Regulator | 90% Efficient Boost Converter with Constant Frequency     |

| LT1376      | 500kHz 1.5A Buck Switching Regulator                     | Steps Down from Up to 25V Using 4.7µH Inductors           |

| LT1512      | 500kHz 1.5A SEPIC Battery Charger                        | Input Voltage May Be Greater or Less Than Battery Voltage |

| LT1513      | 500kHz 3A SEPIC Battery Charger                          | Input Voltage May Be Greater or Less Than Battery Voltage |