# **TABLE OF CONTENTS**

| Features                 | 1 |

|--------------------------|---|

| Applications             | 1 |

| General Description      | 1 |

| Functional Block Diagram | 1 |

| Revision History         | 2 |

| Specifications           | 3 |

| Absolute Maximum Ratings | 4 |

| Thermal Resistance       | 4 |

| ESD Caution              | 4 |

### **REVISION HISTORY**

| 11/2019—Rev. B to Rev. C |   |

|--------------------------|---|

| Changes to Figure 12     | 9 |

#### 11/2016—Rev. A to Rev. B

| Change to Serial Port Timing Section and Time From BCLK |

|---------------------------------------------------------|

| Falling Parameter; Table 7 10                           |

| Changes to Figure 19 Caption and Figure 21 Caption12    |

| Pin Configuration and Function Descriptions | .5 |

|---------------------------------------------|----|

| Typical Performance Characteristics         | .6 |

| Typical Application Circuit                 | .8 |

| Applications Information                    | .9 |

| Overview                                    | .9 |

| Clocking                                    | .9 |

| Serial Audio Output Interface               | .9 |

| Outline Dimensions 1                        | 3  |

| Ordering Guide 1                            | .3 |

### 7/2013—Rev. 0 to Rev. A

| Changes to Supply Current Test Conditions/Comments | 3  |

|----------------------------------------------------|----|

| Changes to Figure 5                                | 6  |

| Added Figure 6; Renumbered Sequentially            | 6  |

| Changes to Figure 14 and Figure 15                 | 10 |

| Changes to Figure 16, Figure 17, and Figure 18     | 11 |

| Changes to Figure 19, Figure 20, and Figure 21     | 12 |

1/2013—Revision 0: Initial Version

## **SPECIFICATIONS**

IOVDD = 1.8 V,  $T_A = 25^{\circ}C$ , BCLK = 3.072 MHz, output = 48 kHz,  $I^2S$  format, unless otherwise noted.

| Parameter                                   | Test Conditions/Comments              | Min   | Тур                | Max    | Unit         |

|---------------------------------------------|---------------------------------------|-------|--------------------|--------|--------------|

| DIGITAL INPUT/OUTPUT                        |                                       |       |                    |        |              |

| High Level Input Voltage (V <sub>IH</sub> ) |                                       |       | $0.7 \times IOVDD$ |        | V            |

| Low Level Input Voltage (V <sub>IL</sub> )  |                                       |       | $0.3 \times IOVDD$ |        | V            |

| Input Leakage, High (I <sub>IH</sub> )      | BCLK and LRCLK pins                   |       |                    | 1      | μΑ           |

| Input Leakage, Low (I⊥)                     | BCLK and LRCLK pins                   |       |                    | 1      | μA           |

| Input Capacitance                           |                                       |       |                    | 5      | pF           |

| SDATA                                       |                                       |       | 4.5                |        | mA           |

| PDM_CLK                                     |                                       |       | 9                  |        | mA           |

| PERFORMANCE                                 |                                       |       |                    |        |              |

| Dynamic Range                               | 20 Hz to 20 kHz, –60 dB input         |       |                    |        |              |

| With A-Weighted Filter (RMS)                |                                       |       | 110                |        | dB           |

| Signal-to-Noise-Ratio                       | A-weighted, fourth-order input        |       | 110                |        | dB           |

| Decimation Ratio                            |                                       |       | 64×                |        |              |

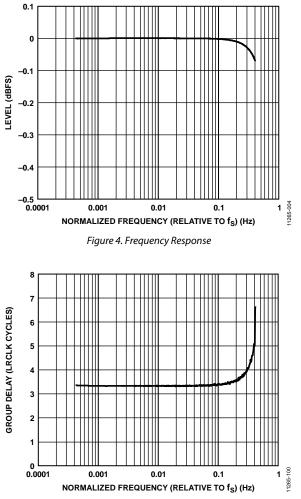

| Frequency Response                          | DC to 0.45 output fs                  | -0.1  |                    | +0.01  | dB           |

| Stop Band                                   |                                       |       | 0.566              |        | fs           |

| Stop-Band Attenuation                       |                                       | 60    |                    |        | dB           |

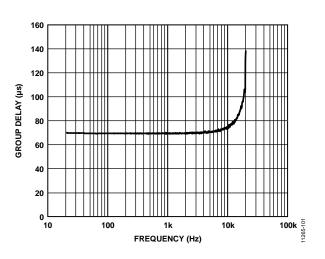

| Group Delay 0.02 fs input signal            |                                       |       | 3.31               |        | LRCLK cycles |

| Gain                                        | PDM to PCM                            |       | 0                  |        | dB           |

| Start-Up Time                               |                                       |       | 48                 |        | LRCLK cycles |

| Bit Width                                   | Internal and output                   |       | 20                 |        | Bits         |

| Interchannel Phase                          |                                       |       | 0                  |        | Degrees      |

| CLOCKING                                    |                                       |       |                    |        |              |

| Output Sampling Rate                        | fs LRCLK pulse rate                   | 4     | 48                 | 96     | kHz          |

| BCLK Frequency                              | f <sub>BCLK</sub>                     | 0.256 | 3.072              | 24.576 | MHz          |

| POWER SUPPLIES                              |                                       |       |                    |        |              |

| Supply Voltage Range                        | IOVDD                                 | 1.62  |                    | 3.6    | V            |

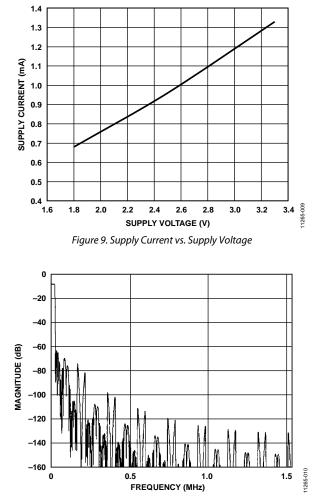

| Supply Current                              | IOVDD = 1.8 V                         |       | 0.67               |        | mA           |

|                                             | IOVDD = 3.3 V                         |       | 1.33               |        | mA           |

|                                             | IOVDD = 1.8 V, 16 kHz output          |       | 0.21               |        | mA           |

|                                             | IOVDD = 3.3 V, 16 kHz output          |       | 0.41               |        | mA           |

| Shutdown Current                            | IOVDD <sub>sD</sub> , no input clocks |       | 1                  |        | μA           |

## **ABSOLUTE MAXIMUM RATINGS**

Absolute maximum ratings apply at 25°C, unless otherwise noted.

#### Table 2.

| Parameter                            | Rating          |

|--------------------------------------|-----------------|

| IOVDD Supply Voltage                 | 3.6 V           |

| Input Voltage                        | 3.6 V           |

| ESD Susceptibility                   | 4 kV            |

| Storage Temperature Range            | –65°C to +150°C |

| Operating Temperature Range          | -40°C to +85°C  |

| Junction Temperature Range           | –65°C to +165°C |

| Lead Temperature (Soldering, 60 sec) | 300°C           |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### THERMAL RESISTANCE

$\theta_{JA}$  (junction to air) is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.  $\theta_{JA}$  is determined according to JESD51-9 on a 4-layer printed circuit board (PCB) with natural convection cooling.

#### Table 3. Thermal Resistance

| Package Type                    | θ」Α | Unit |

|---------------------------------|-----|------|

| 8-ball, 1.56 mm × 0.76 mm WLCSP | 90  | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 2. Pin Configuration (Top Side View)

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Туре   | Description                                              |  |

|---------|----------|--------|----------------------------------------------------------|--|

| A1      | PDM_DAT  | Input  | PDM Data Input                                           |  |

| A2      | PDM_CLK  | Output | PDM Clock Output                                         |  |

| B1      | SDATA    | Output | Serial Data Output for I <sup>2</sup> S/TDM              |  |

| B2      | BCLK     | Input  | Bit Clock for I <sup>2</sup> S/TDM                       |  |

| C1      | GND      | Ground | Ground                                                   |  |

| C2      | LRCLK    | Input  | Left/Right Clock for I <sup>2</sup> S/Frame Sync for TDM |  |

| D1      | IOVDD    | Supply | Input/Output and Digital Supply                          |  |

| D2      | CONFIG   | Input  | Configuration Pin                                        |  |

# **TYPICAL PERFORMANCE CHARACTERISTICS**

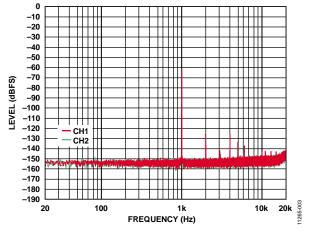

Figure 3. FFT,  $f_s = 48 \text{ kHz}$ , -60 dBFS Input

Figure 5. Group Delay vs. Normalized Frequency (Relative to f<sub>s</sub>)

Figure 6. Group Delay vs. Frequency,  $f_s = 48 \text{ kHz}$

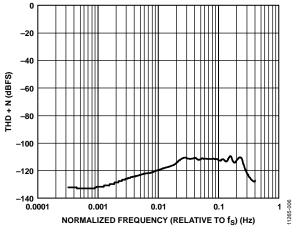

Figure 7. Total Harmonic Distortion + Noise (THD + N) vs. Normalized Frequency (Relative to f<sub>s</sub>)

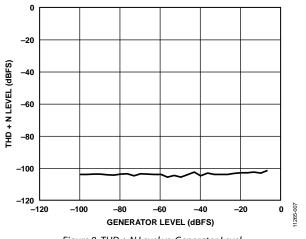

Figure 8. THD + N Level vs. Generator Level

## **Data Sheet**

# ADAU7002

Figure 10. Out-of-Band Frequency Response (48 kHz Output)

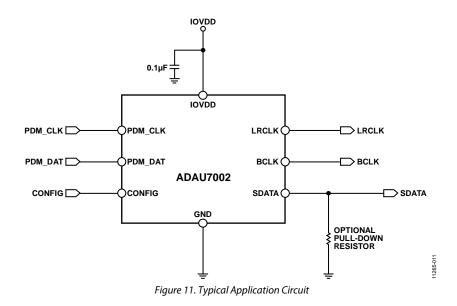

# **TYPICAL APPLICATION CIRCUIT**

## APPLICATIONS INFORMATION overview

The ADAU7002 provides stereo decimation from a 1-bit PDM source to a 20-bit PCM audio. The downsampling ratio is fixed at  $64\times$ . The 20-bit downsampled PCM audio is output via standard I<sup>2</sup>S or TDM formats.

The input source for the ADAU7002 can be any device that has a PDM output, such as a digital microphone. The output pins of these microphones can connect directly to the input pins of the ADAU7002.

### CLOCKING

The ADAU7002 requires a BCLK rate that is a minimum of 64× the LRCLK sample rate. BCLK rates of 128×, 192×, 256×, 384×, and 512× the LRCLK rate are also supported. The ADAU7002 automatically detects the ratio between BCLK and LRCLK and generates a PDM clock output at 64× the LRCLK rate. The minimum sample rate is 4 kHz, and the maximum is 96 kHz, which correspond to a PDM clock range of 256 kHz to 6.144 MHz. Internally, all processing is done at the PDM\_CLK rate.

When BCLK is removed, the ADAU7002 powers down automatically. When BCLK is not present, the PDM\_CLK output stops.

#### Table 6. TDM Slot Selection

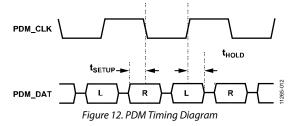

### Table 5. PDM Timing Parameters

| Parameter               | t <sub>MIN</sub> | t <sub>MAX</sub> | Unit |

|-------------------------|------------------|------------------|------|

| Data Setup Time, tSETUP | 10               |                  | ns   |

| Data Hold Time, tHOLD   | 7                |                  | ns   |

PDM data is latched on both edges of the clock.

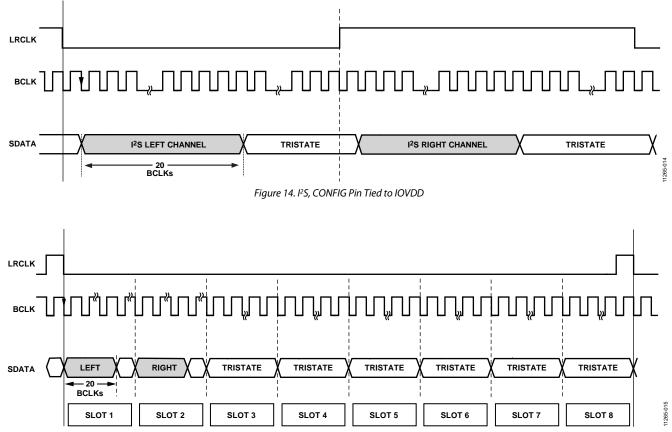

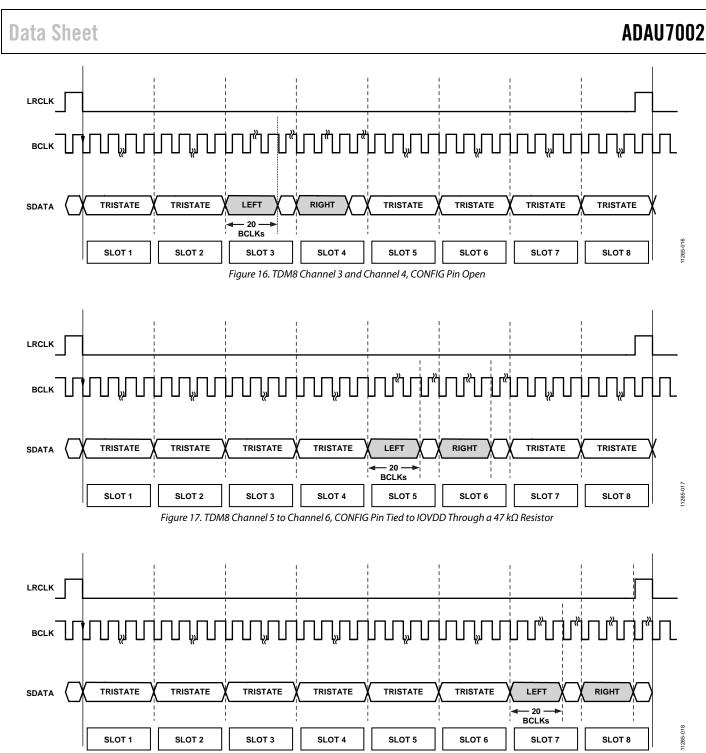

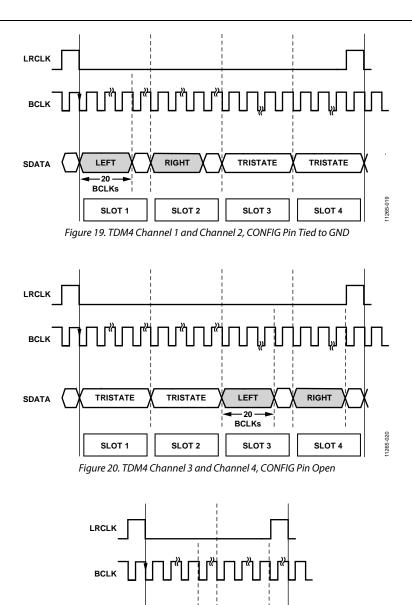

### SERIAL AUDIO OUTPUT INTERFACE

The ADAU7002 supports I<sup>2</sup>S and TDM serial output formats. Format selection and TDM slot placement is set with the CONFIG pin. The SDATA pin is in tristate mode, except when the port is driving serial data based on the CONFIG pin configuration.

| Device Setting                                 | CONFIG Pin Configuration                      |

|------------------------------------------------|-----------------------------------------------|

| I <sup>2</sup> S Format                        | Tie to IOVDD                                  |

| TDM Slot 1 to Slot 2 Used/Driven, 32-Bit Slots | Tie to GND                                    |

| TDM Slot 3 to Slot 4 Used/Driven, 32-Bit Slots | Open                                          |

| TDM Slot 5 to Slot 6 Used/Driven, 32-Bit Slots | Tie to IOVDD through a 47 k $\Omega$ resistor |

| TDM Slot 7 to Slot 8 Used/Driven, 32-Bit Slots | Tie to GND through a 47 k $\Omega$ resistor   |

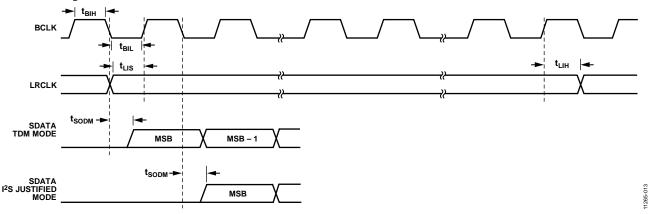

#### Serial Port Timing

Figure 13. Serial Port Timing Diagram

IOVDD = 1.62 V to 3.63 V, load capacitance = 25 pF, unless otherwise noted.

#### Table 7. I<sup>2</sup>S/TDM Timing Parameters

| Parameter              | Symbol            | t <sub>MIN</sub> | t <sub>MAX</sub> | Unit |

|------------------------|-------------------|------------------|------------------|------|

| BCLK Pulse Width High  | tвін              | 10               |                  | ns   |

| BCLK Pulse Width Low   | t <sub>BIL</sub>  | 10               |                  | ns   |

| LRCLK Setup Time       | t <sub>LIS</sub>  | 10               |                  | ns   |

| LRCLK Hold Time        | tlih              | 10               |                  | ns   |

| Time from BCLK Falling | t <sub>sodm</sub> |                  | 18               | ns   |

Figure 15. TDM8 Channel 1 and Channel 2, CONFIG Pin Tied to GND

Figure 18. TDM8 Channel 7 and Channel 8, CONFIG Pin Tied to GND Through a 47 k $\Omega$  Resistor

SDATA

LEFT

SLOT 1

Figure 21. TDM2 Channel 1 and Channel 2, CONFIG Pin Tied to GND

RIGHT

SLOT 2

1265-021

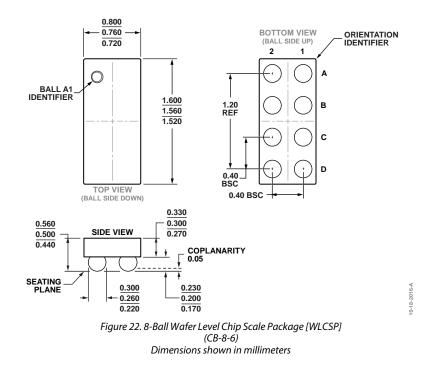

# **OUTLINE DIMENSIONS**

### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                                              | Package<br>Option | Marking Code |

|--------------------|-------------------|------------------------------------------------------------------|-------------------|--------------|

| ADAU7002ACBZ-R7    | -40°C to +85°C    | 8-Ball Wafer Level Chip Scale Package [WLCSP], 7" Tape and Reel  | CB-8-6            | BE           |

| ADAU7002ACBZ-RL    | -40°C to +85°C    | 8-Ball Wafer Level Chip Scale Package [WLCSP], 13" Tape and Reel | CB-8-6            | BE           |

| EVAL-ADAU7002Z     |                   | Evaluation Board                                                 |                   |              |

$^{1}$  Z = RoHS Compliant Part.

# NOTES

# NOTES

## NOTES

©2013–2019 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D11265-0-11/19(C)

www.analog.com