INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH CORTINA SYSTEMS<sup>®</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

EXCEPT AS PROVIDED IN CORTINA'S TERMS AND CONDITIONS OF SALE OF SUCH PRODUCTS, CORTINA ASSUMES NO LIABILITY WHATSOEVER, AND CORTINA DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF CORTINA PRODUCTS, INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Cortina products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Cortina Systems<sup>®</sup> and the Cortina Systems logo are the trademarks or registered trademarks of Cortina Systems, Inc. and its subsidiaries in the U.S. and other countries. Other names and brands may be claimed as the property of others.

Copyright © 2001–2007 Cortina Systems, Inc. All rights reserved.

Cortina Systems<sup>®</sup> LXT972M Single-Port 10/100 Mbps PHY Transceiver

# Contents

| 1.0 | Introd     | duction        | to This Document                                                   | 10 |

|-----|------------|----------------|--------------------------------------------------------------------|----|

|     | 1.1        | Docum          | ent Overview                                                       |    |

|     | 1.2        | Related        | d Documents                                                        | 10 |

| 2.0 | Block      | Diagra         | m                                                                  | 11 |

| 3.0 | Ball a     | nd Pin         | Assignments                                                        | 12 |

| 4.0 | Signa      | I Descr        | iptions                                                            | 16 |

| 5.0 | Funct      | tional D       | escription                                                         | 21 |

|     | 5.1        | Device         | Overview                                                           |    |

|     |            | 5.1.1          | Comprehensive Functionality                                        |    |

|     |            | 5.1.2          | Optimal Signal Processing Architecture                             |    |

|     | 5.2        |                | rk Media / Protocol Support                                        |    |

|     |            | 5.2.1          | 10/100 Network Interface                                           |    |

|     |            | 5.2.2          | MII Data Interface                                                 |    |

|     |            | 5.2.3          | Configuration Management Interface                                 |    |

|     | 5.3        | •              | ing Requirements                                                   |    |

|     |            | 5.3.1          | Power Requirements                                                 |    |

|     | <b>F</b> 4 | 5.3.2          | Clock Requirements                                                 |    |

|     | 5.4        |                | ation                                                              |    |

|     |            | 5.4.1<br>5.4.2 | MDIO Control Mode and Hardware Control Mode<br>Reduced-Power Modes |    |

|     |            | 5.4.2<br>5.4.3 | Reset                                                              |    |

|     |            | 5.4.3<br>5.4.4 | Hardware Configuration Settings                                    |    |

|     | 5.5        | -              | shing Link                                                         |    |

|     | 0.0        | 5.5.1          | Auto-Negotiation                                                   |    |

|     |            | 5.5.2          | Parallel Detection                                                 |    |

|     | 5.6        |                | eration                                                            |    |

|     | 0.0        | 5.6.1          | MII Clocks                                                         |    |

|     |            | 5.6.2          | Transmit Enable                                                    |    |

|     |            | 5.6.3          | Receive Data Valid                                                 |    |

|     |            | 5.6.4          | Carrier Sense                                                      |    |

|     |            | 5.6.5          | Error Signals                                                      |    |

|     |            | 5.6.6          | Collision                                                          |    |

|     |            | 5.6.7          | Loopback                                                           |    |

|     | 5.7        | 100 Mb         | ops Operation                                                      |    |

|     |            | 5.7.1          | 100BASE-X Network Operations                                       |    |

|     |            | 5.7.2          | Collision Indication                                               |    |

|     |            | 5.7.3          | 100BASE-X Protocol Sublayer Operations                             |    |

|     | 5.8        | 10 Mbp         | os Operation                                                       |    |

|     |            | 5.8.1          | 10BASE-T Preamble Handling                                         | 42 |

|     |            | 5.8.2          | 10BASE-T Carrier Sense                                             |    |

|     |            | 5.8.3          | 10BASE-T Dribble Bits                                              |    |

|     |            | 5.8.4          | 10BASE-T Link Integrity Test                                       |    |

|     |            | 5.8.5          | Link Failure                                                       |    |

|     |            | 5.8.6          | 10BASE-T SQE (Heartbeat)                                           |    |

|     |            | 5.8.7          | 10BASE-T Jabber                                                    | 43 |

|      |        | 5.8.8     | 10BASE-T Polarity Correction          | 43 |

|------|--------|-----------|---------------------------------------|----|

|      | 5.9    | Monito    | ring Operations                       |    |

|      |        | 5.9.1     | Monitoring Auto-Negotiation           | 43 |

|      |        | 5.9.2     | Monitoring Next Page Exchange         | 44 |

|      |        | 5.9.3     | LED Functions                         |    |

|      |        | 5.9.4     | LED Pulse Stretching                  |    |

|      | 5.10   | Bounda    | ary Scan (JTAG 1149.1) Functions      |    |

|      |        | 5.10.1    | Boundary Scan Interface               |    |

|      |        |           | State Machine                         |    |

|      |        | 5.10.3    |                                       |    |

|      |        |           | Boundary Scan Register                |    |

|      |        | 5.10.5    | Device ID Register                    | 46 |

| 6.0  | Appli  | cation l  | nformation                            | 47 |

|      | 6.1    | Magnet    | tics Information                      | 47 |

|      | 6.2    |           | I Twisted-Pair Interface              |    |

| 7.0  | Electi | rical Spo | ecifications                          | 51 |

|      | 7.1    | DC Ele    | ectrical Parameters                   | 51 |

|      | 7.2    |           | ning Diagrams and Parameters          |    |

| 8.0  | Regis  | ter Defi  | initions - IEEE Base Registers        | 64 |

| 9.0  | Regis  | ter Defi  | initions - Product-Specific Registers | 72 |

|      |        |           |                                       |    |

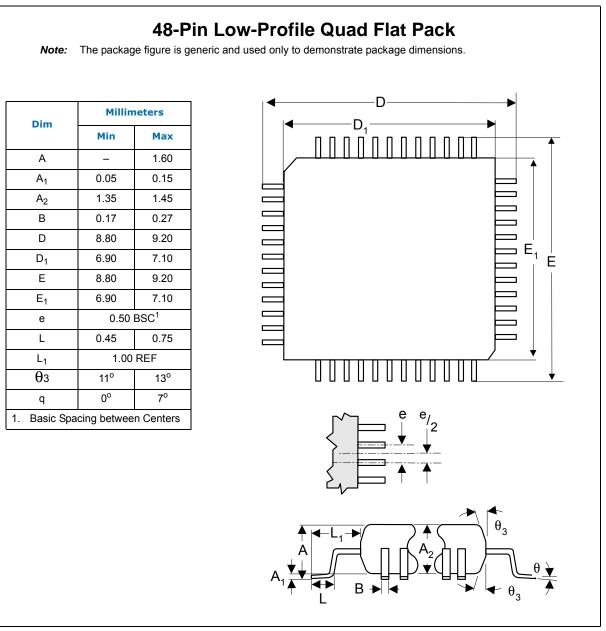

| 10.0 | Packa  | age Spe   | cifications                           | 80 |

# **Figures**

| 1  | Block Diagram                               | .11  |

|----|---------------------------------------------|------|

| 2  | 48-Pin LQFP Package: Pin Assignments        | .13  |

| 3  | Management Interface Read Frame Structure   | .24  |

| 4  | Management Interface Write Frame Structure  | .24  |

| 5  | Initialization Sequence                     | .26  |

| 6  | Link Establishment Overview                 | .29  |

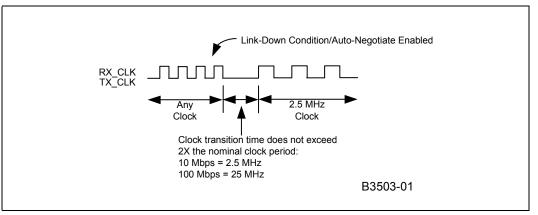

| 7  | Clocking for 10BASE-T                       | .31  |

| 8  | Clocking for 100BASE-X                      | .32  |

| 9  | Clocking for Link Down Clock Transition     | .32  |

| 10 | Loopback Paths                              | .34  |

| 11 | 100BASE-X Frame Format                      | .35  |

| 12 | 100BASE-TX Data Path                        | .36  |

| 13 | 100BASE-TX Reception with No Errors         | .36  |

| 14 | 100BASE-TX Reception with Invalid Symbol    | .37  |

| 15 | 100BASE-TX Transmission with No Errors      | .37  |

| 16 | 100BASE-TX Transmission with Collision      | .37  |

| 17 | Protocol Sublayers                          | . 38 |

| 18 | LED Pulse Stretching                        | .45  |

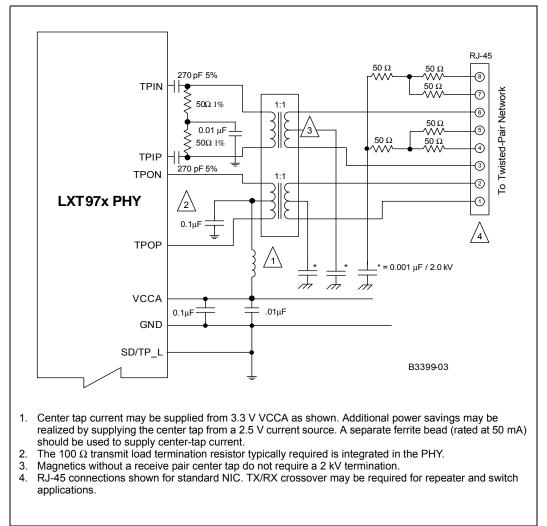

| 19 | Typical Twisted-Pair Interface - Switch     | .48  |

| 20 | Typical Twisted-Pair Interface - NIC        | .49  |

| 21 | Typical Media Independent Interface         | .50  |

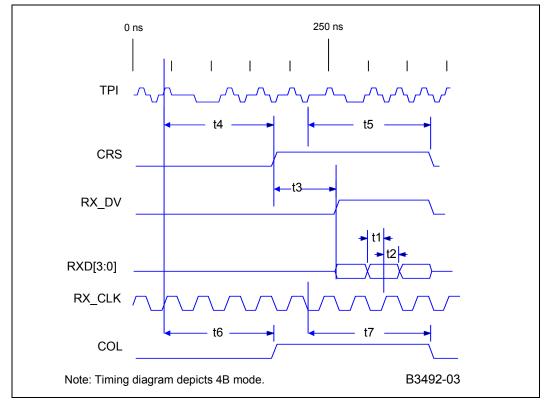

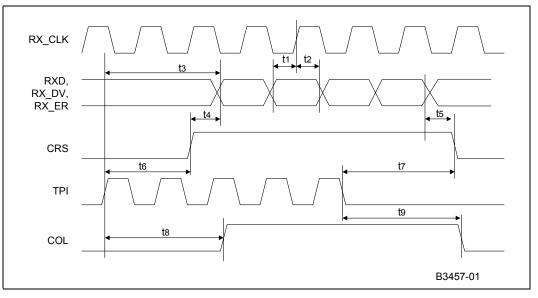

| 22 | 100BASE-TX Receive Timing                   | .55  |

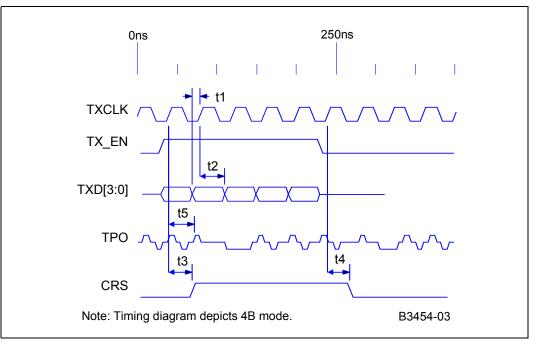

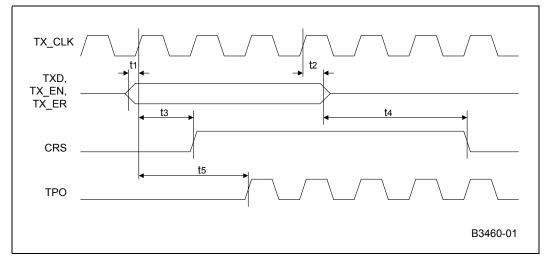

| 23 | 100BASE-TX Transmit Timing                  | .56  |

| 24 | 10BASE-T Receive Timing                     | .57  |

| 25 | 10BASE-T Transmit Timing                    | . 58 |

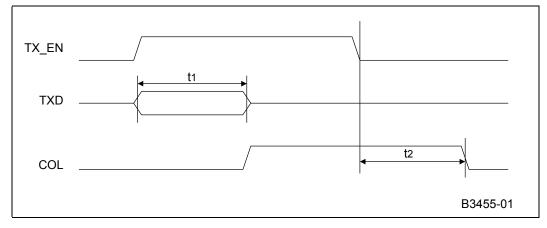

| 26 | 10BASE-T Jabber and Unjabber Timing         | . 59 |

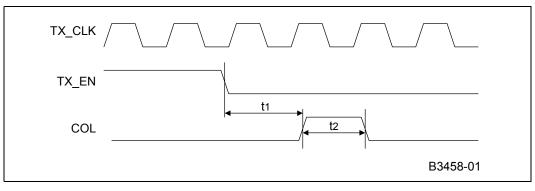

| 27 | 10BASE-T SQE (Heartbeat) Timing             |      |

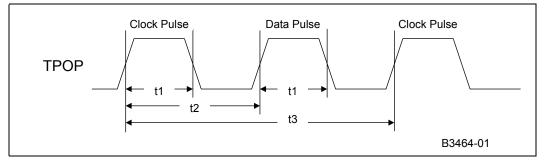

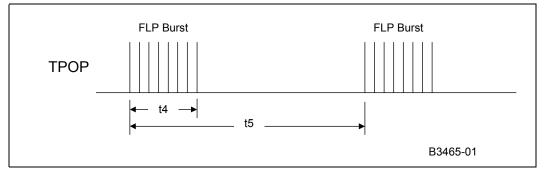

| 28 | Auto-Negotiation and Fast Link Pulse Timing |      |

| 29 | Fast Link Pulse Timing                      | .60  |

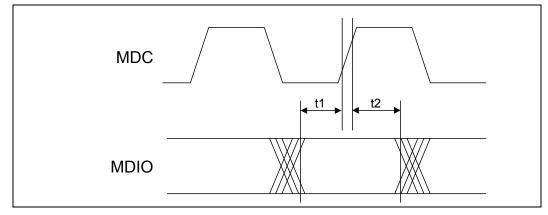

| 30 | MDIO Input Timing                           | .61  |

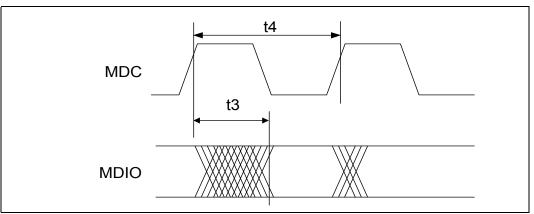

| 31 | MDIO Output Timing                          |      |

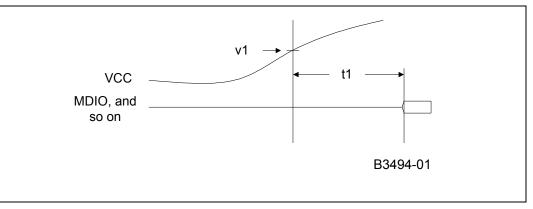

| 32 | Power-Up Timing                             | .62  |

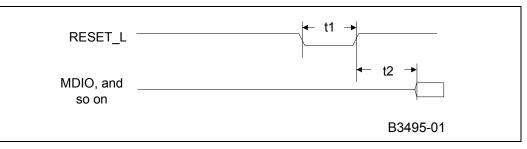

| 33 | RESET_L Pulse Width and Recovery Timing     |      |

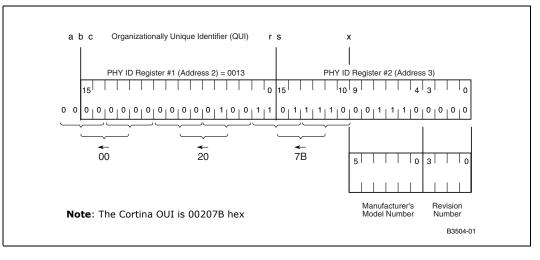

| 34 | PHY Identifier Bit Mapping                  |      |

| 35 | LQFP Package Specifications                 | .80  |

|    |                                             |      |

## **Tables**

| 1  | Related Documents                                                           | 10 |

|----|-----------------------------------------------------------------------------|----|

| 2  | PHY Signal Types                                                            |    |

| 3  | LQFP Numeric Pin List                                                       | 13 |

| 4  | PHY Signal Types                                                            | 16 |

| 5  | LXT972M: MII Data Interface Signal Descriptions                             | 17 |

| 6  | LXT972M: MII Controller Interface Signal Descriptions                       |    |

| 7  | LXT972M: Network Interface Signal Descriptions                              |    |

| 8  | LXT972M: Standard Bus and Interface Signal Descriptions                     |    |

| 9  | LXT972M: Configuration and LED Driver Signal Descriptions                   |    |

| 10 | LXT972M: Power, Ground, No-Connect Signal Descriptions                      |    |

| 11 | LXT972M: JTAG Test Signal Descriptions                                      |    |

| 12 | LXT972M:Pin Types and Modes                                                 |    |

| 13 | PHY Device Address Selections                                               | 24 |

| 14 | Hardware Configuration Settings                                             | 28 |

| 15 | Carrier Sense, Loopback, and Collision Conditions                           |    |

| 16 | 4B/5B Coding                                                                |    |

| 17 | BSR Mode of Operation                                                       |    |

| 18 | Device ID Register                                                          |    |

| 19 | Magnetics Requirements                                                      |    |

| 20 | I/O Pin Comparison of NIC and Switch RJ-45 Setups                           |    |

| 21 | Absolute Maximum Ratings                                                    |    |

| 22 | Recommended Operating Conditions                                            |    |

| 23 | Digital I/O Characteristics (Except for MII, XI/XO, and LED/CFG Pins)       |    |

| 24 | Digital I/O Characteristics <sup>1</sup> - MII Pins                         |    |

| 25 | I/O Characteristics - REFCLK/XI and XO Pins                                 |    |

| 26 | I/O Characteristics - LED/CFG Pins                                          | 53 |

| 27 | 100BASE-TX PHY Characteristics                                              | 53 |

| 28 | 10BASE-T PHY Characteristics                                                | 54 |

| 29 | 10BASE-T Link Integrity Timing Characteristics                              |    |

| 30 | Thermal Characteristics                                                     |    |

| 31 | 100BASE-TX Receive Timing Parameters - 4B Mode                              |    |

| 32 | 10BASE-T Receive Timing Parameters                                          |    |

| 33 | 10BASE-T Jabber and Unjabber Timing                                         |    |

| 34 | PHY 10BASE-T SQE (Heartbeat) Timing                                         |    |

| 35 | Auto-Negotiation and Fast Link Pulse Timing Parameters                      |    |

| 36 | MDIO Timing                                                                 |    |

| 37 | Power-Up Timing                                                             | 62 |

| 38 | RESET_L Pulse Width and Recovery Timing                                     | 63 |

| 39 | Register Set for IEEE Base Registers                                        |    |

| 40 | Control Register - Address 0, Hex 0                                         |    |

| 41 | MII Status Register #1 - Address 1, Hex 1                                   |    |

| 42 | PHY Identification Register 1 - Address 2, Hex 2                            |    |

| 43 | PHY Identification Register 2 - Address 3, Hex 3                            |    |

| 44 | Auto-Negotiation Advertisement Register - Address 4, Hex 4                  |    |

| 45 | Auto-Negotiation Link Partner Base Page Ability Register - Address 5, Hex 5 | 69 |

| 46 | Auto-Negotiation Expansion - Address 6, Hex 6                               |    |

| 47 | Auto-Negotiation Next Page Transmit Register - Address 7, Hex 7             |    |

| 48 | Auto-Negotiation Link Partner Next Page Receive Register - Address 8, Hex 8 |    |

|    |                                                                             |    |

| 49 | Register Set for Product-Specific Registers         | 72 |

|----|-----------------------------------------------------|----|

| 50 | Configuration Register - Address 16, Hex 10         | 72 |

| 51 | Status Register #2 - Address 17, Hex 11             | 73 |

| 52 | Interrupt Enable Register - Address 18, Hex 12      | 75 |

| 53 | Status Change Register - Address 19, Hex 13         | 75 |

| 54 | LED Configuration Register - Address 20, Hex 14     | 77 |

| 55 | Digital Configuration Register - Address 26, Hex 1A |    |

| 56 | Transmit Control Register - Address 30, Hex 1E      |    |

|    | -                                                   |    |

## **Revision History**

#### Revision 5.2 Revision Date: 13 September 2007

- Removed outdated Figure 3: 64-Pin Pb-Free LQFP Package: Pins Assignments

- · Removed the ordering information. This information is now available from www.cortina-systems.com.

#### Revision 5.1 Revision Date: 23 July 2007

Added Section 10.0, Package Specifications back into Datasheet.

#### Revision 5.0 Revision Date: 2 July 2007

First release of this document from Cortina Systems, Inc.

#### Revision 004 Revision Date: 01 January 2007

Internal release. No changes.

| Revision 003<br>Revision Date: 14 July 2004                                                                            |

|------------------------------------------------------------------------------------------------------------------------|

| Figure 3, LXT972M Transceiver Block Diagram - Deleted ECL Driver from figure.                                          |

| Section 5.1, Device Overview - Text changed.                                                                           |

| Section 5.2.1.1, Twisted-Pair Interface - Added text on MDI crossover.                                                 |

| Section 5.2.1.5, Remote Fault Detection and Reporting - Text changed.                                                  |

| Section 5.3.2.1, External Crystal/Oscillator - Text changed.                                                           |

| Table 37, Hardware Configuration Settings for Cortina Systems® LXT977 Transceiver - Bit value for 0.8 changed.         |

| Section 5.5.2, Parallel Detection - Text changed.                                                                      |

| Section 5.6.2, Transmit Enable - Text changed.                                                                         |

| Section 5.6.4, Carrier Sense - Text changed.                                                                           |

| Section 5.7.3.1.1, Preamble Handling - Text changed.                                                                   |

| Section 5.7.3.2.1, Link - Added text.                                                                                  |

| Section 5.7.3.2.2, Link Failure Override - Added text.                                                                 |

| Section 5.7.3.2.4, Receive Data Valid - Text changed.                                                                  |

| Section 5.7.3.3.2, Polarity Correction - Text changed.                                                                 |

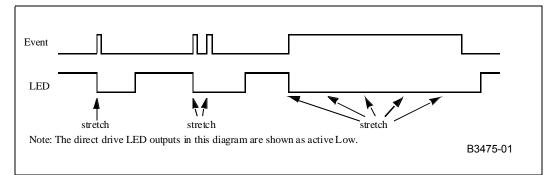

| Section 5.9.4, LED Pulse Stretching - Text changed.                                                                    |

| Table 123, Auto-Negotiation Next Page Transmit Register - Address 7, Hex 7 - Bits 7.10:0 and 7.13 changed.             |

| Table 124, Auto-Negotiation Link Partner Next Page Receive Register - Address 8, Hex 8 - Bits 8.18 and 8.10:0 changed. |

| Table 131, LED Configuration Register - Address 20, Hex 14 - Bit 20.0 changed.                                         |

#### Revision 002 Revision Date: 14 July 2004

Text changed.

Figure 3, *LXT972M Transceiver Block Diagram* - Deleted ECL Driver from figure.

Section 5.1, Device Overview - Text changed.

Cortina Systems<sup>®</sup> LXT972M Single-Port 10/100 Mbps PHY Transceiver

| Revision 002<br>Revision Date: 14 July 2004                                                                            |

|------------------------------------------------------------------------------------------------------------------------|

| Section 5.2.1.1, Twisted-Pair Interface - Added text on MDI crossover.                                                 |

| Section 5.2.1.5, Comment: for LXT972A/972M/977>Remote Fault Detection and Reporting - Text changed.                    |

| Section 5.3.2.1, External Crystal/Oscillator - Text changed.                                                           |

| Table 37, Hardware Configuration Settings for Cortina Systems® LXT977 Transceiver - Bit value for 0.8 changed.         |

| Section 5.5.2, Parallel Detection - Text changed.                                                                      |

| Section 5.6.2, Transmit Enable - Text changed.                                                                         |

| Section 5.6.4, Carrier Sense - Text changed.                                                                           |

| Section 5.7.3.1.1, Preamble Handling - Text changed.                                                                   |

| Section 5.7.3.2.1, Link - Added text.                                                                                  |

| Section 5.7.3.2.2, Link Failure Override - Added text.                                                                 |

| Section 5.7.3.2.4, Receive Data Valid - Text changed.                                                                  |

| Section 5.7.3.3.2, Polarity Correction - Text changed.                                                                 |

| Section 5.9.4, LED Pulse Stretching - Text changed.                                                                    |

| Table 123, Auto-Negotiation Next Page Transmit Register - Address 7, Hex 7 - Bits 7.10:0 and 7.13 changed.             |

| Table 124, Auto-Negotiation Link Partner Next Page Receive Register - Address 8, Hex 8 - Bits 8.18 and 8.10:0 changed. |

| Table 131, LED Configuration Register - Address 20, Hex 14 - Bit 20.0 changed.                                         |

|                                   | Revision 001<br>Revision Date: 02 July 2004 |  |

|-----------------------------------|---------------------------------------------|--|

| Initial release of this document. |                                             |  |

# **1.0** Introduction to This Document

This document includes information on the Cortina Systems<sup>®</sup> LXT972M Single-Port 10/ 100 Mbps PHY Transceiver (LXT972M PHY).

## **1.1 Document Overview**

This document includes the following subjects:

- 2.0, Block Diagram, on page 11

- 3.0, Ball and Pin Assignments, on page 12

- 4.0, Signal Descriptions, on page 16

- 5.0, Functional Description, on page 21

- 6.0, Application Information, on page 47

- 7.0, Electrical Specifications, on page 51

- 8.0, Register Definitions IEEE Base Registers, on page 64

- 9.0, Register Definitions Product-Specific Registers, on page 72

## **1.2 Related Documents**

### Table 1Related Documents

| Document Title                                                                                                  | Document<br>Number |

|-----------------------------------------------------------------------------------------------------------------|--------------------|

| Cortina Systems <sup>®</sup> LXT971A, LXT972A, LXT972M Single-Port 10/<br>100 Mbps PHY Specification Update     | 249354             |

| Cortina Systems <sup>®</sup> LXT971A, LXT972A, and LXT972M 3.3 V PHY Design and Layout Guide - Application Note | 249016             |

| Magnetic Manufacturers for Networking Product Applications -<br>Application Note                                | 248991             |

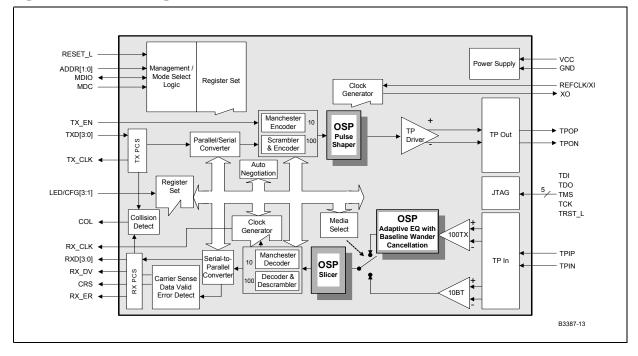

# 2.0 Block Diagram

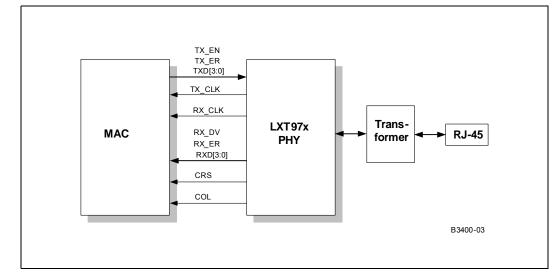

### Figure 1 Block Diagram

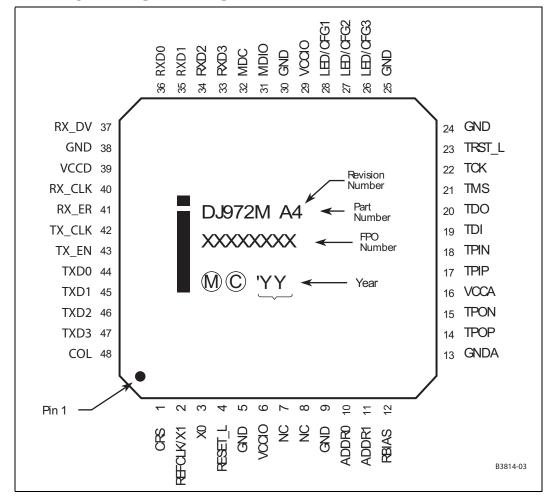

# 3.0 Ball and Pin Assignments

See the following diagrams for signal placement:

• Figure 2, 48-Pin LQFP Package: Pin Assignments, on page 13

See the following tables for signal lists:

• Table 3, LQFP Numeric Pin List, on page 13

**Note:** Table 2 list the signal type abbreviations used in the signal tables.

### Table 2PHY Signal Types

| Abbreviation | Definition    |

|--------------|---------------|

| AI           | Analog Input  |

| AO           | Analog Output |

| I            | Input         |

| I/O          | Input/Output  |

| 0            | Output        |

| OD           | Open Drain    |

#### Figure 2 48-Pin LQFP Package: Pin Assignments

#### Table 3LQFP Numeric Pin List (Sheet 1 of 2)

| Pin | Symbol    | Туре |

|-----|-----------|------|

| 1   | CRS       | 0    |

| 2   | REFCLK/XI | AI   |

| 3   | XO        | AO   |

| 4   | RESET_L   | I    |

| 5   | GND       | -    |

| 6   | VCCIO     | -    |

| 7   | NC        | -    |

| 8   | NC        | -    |

| 9   | GND       | -    |

| 10  | ADDR0     | I    |

### Table 3LQFP Numeric Pin List (Sheet 2 of 2)

| Pin | Symbol   | Туре |

|-----|----------|------|

| 11  | ADDR1    | I    |

| 12  | RBIAS    | AI   |

| 13  | GNDA     | -    |

| 14  | TPOP     | AO   |

| 15  | TPON     | AO   |

| 16  | VCCA     | -    |

| 17  | TPIP     | AI   |

| 18  | TPIN     | AI   |

| 19  | TDI      | I    |

| 20  | TDO      | 0    |

| 21  | TMS      | I    |

| 22  | ТСК      | I    |

| 23  | TRST_L   | I    |

| 24  | GND      | -    |

| 25  | GND      | -    |

| 26  | LED/CFG3 | I/O  |

| 27  | LED/CFG2 | I/O  |

| 28  | LED/CFG1 | I/O  |

| 29  | VCCIO    | -    |

| 30  | GND      | -    |

| 31  | MDIO     | I/O  |

| 32  | MDC      | I    |

| 33  | RXD3     | 0    |

| 34  | RXD2     | 0    |

| 35  | RXD1     | 0    |

| 36  | RXD0     | 0    |

| 37  | RX_DV    | 0    |

| 38  | GND      | -    |

| 39  | VCCD     | -    |

| 40  | RX_CLK   | 0    |

| 41  | RX_ER    | 0    |

| 42  | TX_CLK   | 0    |

| 43  | TX_EN    | I    |

| 44  | TXD0     | I    |

| 45  | TXD1     | I    |

| 46  | TXD2     | I    |

| 47  | TXD3     | I    |

| 48  | COL      | 0    |

## 4.0 Signal Descriptions

Cortina recommends the following configurations for unused pins:

- **Unused inputs.** Configure all unused inputs and unused multi-function pins for inactive states.

- · Unused outputs. Leave all unused outputs floating.

- No connects. Do not use pins designated as NC (no connect), and do not terminate them.

- **Note:** Table 4 list the signal type abbreviations used in the signal tables.

### Table 4 PHY Signal Types

| Abbreviation | Definition    |

|--------------|---------------|

| AI           | Analog Input  |

| AO           | Analog Output |

| I            | Input         |

| I/O          | Input/Output  |

| 0            | Output        |

| OD           | Open Drain    |

Tables in this section include the following:

- Table 5, LXT972M: MII Data Interface Signal Descriptions, on page 17

- Table 6, LXT972M: MII Controller Interface Signal Descriptions, on page 18

- Table 7, LXT972M: Network Interface Signal Descriptions, on page 18

- Table 8, *LXT972M: Standard Bus and Interface Signal Descriptions*, on page 18

- Table 9, LXT972M: Configuration and LED Driver Signal Descriptions, on page 18

- Table 10, LXT972M: Power, Ground, No-Connect Signal Descriptions, on page 19

- Table 11, LXT972M: JTAG Test Signal Descriptions, on page 19

- Table 12, *LXT972M:Pin Types and Modes*, on page 20

### Table 5 LXT972M: MII Data Interface Signal Descriptions

| LQFP<br>Pin#         | Symbol                       | Туре | Signal Description                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|----------------------|------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 47<br>46<br>45<br>44 | TXD3<br>TXD2<br>TXD1<br>TXD0 | I    | Transmit Data.<br>TXD is a group of parallel data signals that are driven by the MAC.<br>TXD[3:0] transition synchronously with respect to TX_CLK.<br>TXD[0] is the least-significant bit.                                                                                                                                                                                                     |  |  |

| 43                   | TX_EN                        | I    | Transmit Enable.<br>The MAC asserts this signal when it drives valid data on TXD.<br>This signal must be synchronized to TX_CLK.                                                                                                                                                                                                                                                               |  |  |

| 42                   | TX_CLK                       | 0    | Transmit Clock.<br>TX_CLK is sourced by the PHY in both 10 and 100 Mbps operations.<br>2.5 MHz for 10 Mbps operation<br>25 MHz for 100 Mbps operation.                                                                                                                                                                                                                                         |  |  |

| 33<br>34<br>35<br>36 | RXD3<br>RXD2<br>RXD1<br>RXD0 | 0    | <b>Receive Data.</b><br>RXD is a group of parallel signals that transition synchronously with respect to RX_CLK.<br>RXD[0] is the least-significant bit.                                                                                                                                                                                                                                       |  |  |

| 37                   | RX_DV                        | 0    | <b>Receive Data Valid.</b><br>The LXT972M PHY asserts this signal when it drives valid data on RXD.<br>This output is synchronous to RX_CLK.                                                                                                                                                                                                                                                   |  |  |

| 41                   | RX_ER                        | 0    | <b>Receive Error.</b><br>Signals a receive error condition has occurred.<br>This output is synchronous to RX_CLK.                                                                                                                                                                                                                                                                              |  |  |

| 40                   | RX_CLK                       | 0    | Receive Clock.         25 MHz for 100 Mbps operation.         2.5 MHz for 10 Mbps operation.         For details, see Section 5.3.2, Clock Requirements, on page 25 in the Functional Description section.                                                                                                                                                                                     |  |  |

| 48                   | COL                          | 0    | Collision Detected.<br>The LXT972M PHY asserts this output when a collision is detected.<br>This output remains High for the duration of the collision.<br>This signal is asynchronous and is inactive during full- duplex operation.                                                                                                                                                          |  |  |

| 1                    | CRS                          | 0    | <b>Carrier Sense</b> .<br>During half-duplex operation (register bit 0.8 = 0), the LXT972M PHY asserts this output when either transmitting or receiving data packets.<br>During full-duplex operation (register bit 0.8 = 1), CRS is asserted only during receive.<br>CRS assertion is asynchronous with respect to RX_CLK. CRS is de-<br>asserted on loss of carrier, synchronous to RX_CLK. |  |  |

### Table 6 LXT972M: MII Controller Interface Signal Descriptions

| LQFP<br>Pin# | Symbol | Туре | Signal Description                                                                               |

|--------------|--------|------|--------------------------------------------------------------------------------------------------|

| 32           | MDC    | I    | Management Data Clock.<br>Clock for the MDIO serial data channel.<br>Maximum frequency is 8 MHz. |

| 31           | MDIO   | I/O  | Management Data Input/Output.<br>Bidirectional serial data channel for PHY/STA communication.    |

### Table 7 LXT972M: Network Interface Signal Descriptions

| LQFP<br>Pin# | Symbol       | Туре | Signal Description                                                                                                                                                        |

|--------------|--------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14<br>15     | TPOP<br>TPON | AO   | Twisted-Pair Outputs, Positive and Negative.<br>During 100BASE-TX or 10BASE-T operation, TPOP/N pins drive IEEE<br>802.3 compliant pulses onto the line.                  |

| 17<br>18     | TPIP<br>TPIN | AI   | Twisted-Pair Inputs, Positive and Negative.<br>During 100BASE-TX or 10BASE-T operation, TPIP/N pins receive<br>differential 100BASE-TX or 10BASE-T signals from the line. |

### Table 8 LXT972M: Standard Bus and Interface Signal Descriptions

| LQFP<br>Pin# | Symbol | Туре | Signal Description  |

|--------------|--------|------|---------------------|

| 10           | ADDR0  | I    | Address.            |

| 11           | ADDR1  |      | Set device address. |

### Table 9LXT972M: Configuration and LED Driver Signal Descriptions (Sheet 1 of 2)

|   | LQFP<br>Pin# | Symbol                | Туре       | Signal Description                                                                                                                                                                         |

|---|--------------|-----------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ľ | Note: Im     | plement 10 k $\Omega$ | pull-up/pu | ill-down resistors if LEDs are not used in the design.                                                                                                                                     |

|   | 4            | RESET_L               | I          | Reset. This active Low input is Read with the control register Reset bit (register bit 0.15). The LXT972M PHY reset cycle is extended to 258 $\mu$ s (nominal) after reset is de-asserted. |

#### Table 9LXT972M: Configuration and LED Driver Signal Descriptions (Sheet 2 of 2)

| LQFP<br>Pin#   | Symbol                          | Туре         | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|---------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12             | RBIAS                           | AI           | Reference Current Bias.<br>This pin provides bias current for the internal circuitry. Must be tied to ground through a 22.1 k $\Omega$ , 1% resistor.                                                                                                                                                                                                                                                                                                              |

| 2<br>3         | REFCLK/XI<br>XO                 | Al and<br>AO | Reference Clock Input / Crystal Input and Crystal Output.<br>A 25 MHz crystal oscillator circuit can be connected across XI and XO. A clock can also be used at XI. Refer to Section 5.3.2, <i>Clock Requirements</i> , on page 25 in the Functional Description section.                                                                                                                                                                                          |

| 26<br>27<br>28 | LED/CFG3<br>LED/CFG2<br>LEDCFG1 | I/O          | LED Drivers 1-3.<br>These pins drive LED indicators. Each LED can display one of several<br>available status conditions as selected by the LED Configuration<br>Register. (For details, see Table 54, <i>LED Configuration Register -</i><br><i>Address 20, Hex 14</i> , on page 77.)<br>Configuration Inputs 1-3.<br>These pins also provide initial configuration settings. (For details, see<br>Table 14, <i>Hardware Configuration Settings</i> , on page 28.) |

### Table 10 LXT972M: Power, Ground, No-Connect Signal Descriptions

| LQFP<br>Pin#            | Symbol | Туре | Signal Description                                                                                                                                                    |  |

|-------------------------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 13                      | GNDA   | -    | Analog Ground.                                                                                                                                                        |  |

| 5, 9, 24,<br>25, 30, 38 | GND    | _    | Ground Input/Output.<br>Ground return for digital I/O circuits (VCCIO).                                                                                               |  |

| 6, 29                   | VCCIO  | _    | MII Power.<br>Requires either a 3.3 V or a 2.5 V supply. Must be supplied from the same source used to power the MAC on the other side of the MII.<br>VCCIO is 3.3 V. |  |

| 16                      | VCCA   | _    | Analog Power.<br>Requires a 3.3 V power supply.                                                                                                                       |  |

| 39                      | VCCD   | _    | Digital Power.<br>Requires a 3.3 V power supply.                                                                                                                      |  |

| 7, 8                    | NC     | _    | No Connection.<br>These pins are not used and must not be terminated.                                                                                                 |  |

#### Table 11 LXT972M: JTAG Test Signal Descriptions (Sheet 1 of 2)

| LQFP<br>Pin# | Symbol          | Туре      | Signal Description                                                                    |

|--------------|-----------------|-----------|---------------------------------------------------------------------------------------|

| Note: Th     | ese pins do not | need to b | be terminated If a JTAG port is not used.                                             |

| 19           | TDI             | I         | <b>Test Data Input</b> .<br>Test data sampled with respect to the rising edge of TCK. |

| 20           | TDO             | 0         | Test Data Output.<br>Test data driven with respect to the falling edge of TCK.        |

Cortina Systems<sup>®</sup> LXT972M Single-Port 10/100 Mbps PHY Transceiver

### Table 11 LXT972M: JTAG Test Signal Descriptions (Sheet 2 of 2)

| LQFP<br>Pin# | Symbol | Туре | Signal Description                                                 |

|--------------|--------|------|--------------------------------------------------------------------|

| 21           | TMS    | I    | Test Mode Select.                                                  |

| 22           | ТСК    | I    | Test Clock.<br>Clock input for boundary scan.                      |

| 23           | TRST_L | I    | Test Reset.<br>This active-low test reset input is sourced by ATE. |

### Table 12 LXT972M:Pin Types and Modes

| Modes                       | RXD3:0                     | RX_DV         | Tx/Rx<br>CLKS<br>Output | RX_ER<br>Output | COL<br>Output | CRS<br>Output | TXD3:0<br>Input | TX_EN<br>Input |

|-----------------------------|----------------------------|---------------|-------------------------|-----------------|---------------|---------------|-----------------|----------------|

| HWReset                     | DL                         | DL            | DH                      | DL              | DL            | DL            | ID              | ID             |

| SFTPWRDN                    | DL                         | DL            | Active                  | DL              | DL            | DL            | ID              | ID             |

| ISOLATE                     | HZ with<br>ID              | HZ with<br>ID | HZ with<br>ID           | HZ with<br>ID   | HZ with<br>ID | HZ with<br>ID | ID              | ID             |

| • DH = Drive                | DH = Driven High (Logic 1) |               |                         |                 |               |               |                 |                |

| • DL = Driven Low (Logic 0) |                            |               |                         |                 |               |               |                 |                |

| • HZ = High                 | Impedance                  |               |                         |                 |               |               |                 |                |

• ID = Internal Pull-Down (Weak)

LXT972M PHY Datasheet 302875, Revision 5.3 31 October 2007

# 5.0 Functional Description

This chapter has the following sections:

- Section 5.1, Device Overview, on page 21

- Section 5.2, Network Media / Protocol Support, on page 22

- Section 5.3, Operating Requirements, on page 25

- Section 5.4, Initialization, on page 25

- Section 5.5, Establishing Link, on page 28

- Section 5.6, MII Operation, on page 30

- Section 5.7, 100 Mbps Operation, on page 35

- Section 5.8, *10 Mbps Operation*, on page 42

- Section 5.9, Monitoring Operations, on page 43

- Section 5.10, Boundary Scan (JTAG 1149.1) Functions, on page 45

## 5.1 Device Overview

The LXT972M PHY is a single-port Fast Ethernet 10/100 PHY that supports 10 Mbps and 100 Mbps networks. It complies with applicable requirements of IEEE 802.3. It directly drives either a 100BASE-TX line or a 10BASE-T line.

### 5.1.1 Comprehensive Functionality

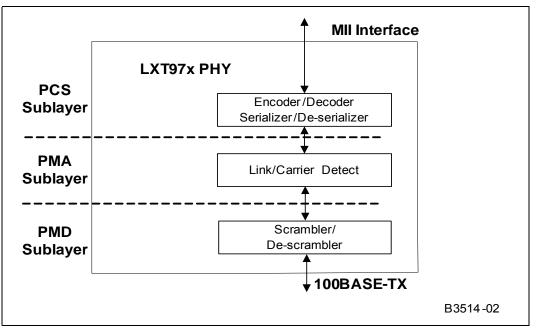

The LXT972M PHY provides a standard Media Independent Interface (MII) for 10/100 MACs. The LXT972M PHY performs all functions of the Physical Coding Sublayer (PCS) and Physical Media Attachment (PMA) sublayer as defined in the IEEE 802.3 100BASE-X standard. It also performs all functions of the Physical Media Dependent (PMD) sublayer for 100BASE-TX connections.

If the LXT972M PHY is not set for forced operation, it uses auto-negotiation/parallel detection to automatically determine line operating conditions. If the PHY device on the other side of the link supports auto-negotiation, the LXT972M PHY auto-negotiates with it using Fast Link Pulse (FLP) Bursts. If the PHY partner does not support auto-negotiation, the LXT972M PHY automatically detects the presence of either link pulses (10 Mbps PHY) or Idle symbols (100 Mbps PHY) and sets its operating conditions accordingly.

The LXT972M PHY provides half-duplex and full-duplex operation at 100 Mbps and 10 Mbps.

### 5.1.2 Optimal Signal Processing Architecture

The LXT972M PHY incorporates high-efficiency Optimal Signal Processing (OSP) design techniques, which combine optimal properties of digital and analog signal processing.

The receiver utilizes decision feedback equalization to increase noise and cross-talk immunity by as much as 3 dB over an ideal all-analog equalizer. Using OSP mixed-signal processing techniques in the receive equalizer avoids the quantization noise and calculation truncation errors found in traditional DSP-based receivers (typically complex DSP engines with A/D converters). This results in improved receiver noise and cross-talk performance.

The OSP signal processing scheme also requires substantially less computational logic than traditional DSP-based designs. This lowers power consumption and also reduces the logic switching noise generated by DSP engines. This logic switching noise can be a considerable source of EMI generated on the device's power supplies.

The OSP-based LXT972M PHY provides improved data recovery, EMI performance, and low power consumption.

## 5.2 Network Media / Protocol Support

This section includes the following:

- Section 5.2.1, 10/100 Network Interface

- Section 5.2.2, MII Data Interface

- Section 5.2.3, Configuration Management Interface

The LXT972M PHY supports both 10BASE-T and 100BASE-TX Ethernet over twisted-pair

### 5.2.1 10/100 Network Interface

The network interface port consists of two differential signal pairs. For specific pin assignments, see Section 4.0, *Signal Descriptions*, on page 16.

The LXT972M PHY output drivers can generate one of the following outputs:

- 100BASE-TX

- 10BASE-T

When not transmitting data, the LXT972M PHY generates IEEE 802.3-compliant link pulses or idle code. Depending on the mode selected, input signals are decoded as one of the following:

- 100BASE-TX

- 10BASE-T

Auto-negotiation/parallel detection or manual control is used to determine the speed of this interface.

### 5.2.1.1 Twisted-Pair Interface

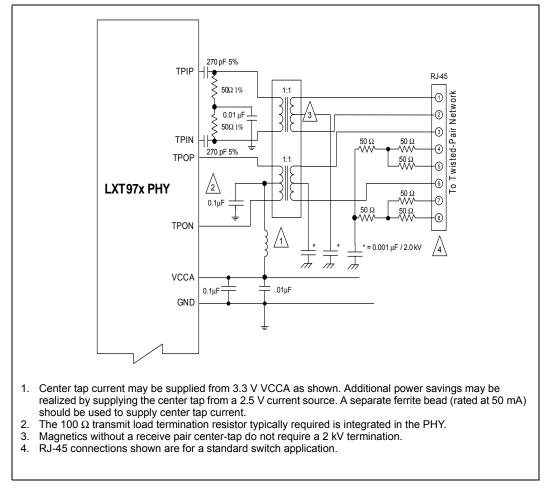

The LXT972M PHY supports either 100BASE-TX or 10BASE-T connections over 100  $\Omega$ , Category 5, Unshielded Twisted Pair (UTP) cable. When operating at 100 Mbps, the LXT972M PHY continuously transmits and receives MLT3 symbols. When not transmitting data, the LXT972M PHY generates "IDLE" symbols.

During 10 Mbps operation, Xilink\* Manchester-encoded data is exchanged. When no data is being exchanged, the line is left in an idle state. Link pulses are transmitted periodically to keep the link up.

Only a transformer, RJ-45 connector, load resistor and bypass capacitors are required to complete this interface. On the transmit side, the LXT972M PHY has an active internal termination and does not require external termination resistors. Cortina's waveshaping technology shapes the outgoing signal to help reduce the need for external EMI filters. Four slew rate settings allow the designer to match the output waveform to the magnetic

characteristics. On the receive side, the internal impedance is high enough that it has no practical effect on the external termination circuit. (For the slew rate settings, see Table 56, *Transmit Control Register - Address 30, Hex 1E*, on page 79.)

**Note:** The MDIX crossover (MDIX) is supported by board design.

### 5.2.1.2 Remote Fault Detection and Reporting

The LXT972M PHY supports the remote fault detection and reporting mechanisms. "Remote Fault" refers to a MAC-to-MAC communication function that is transparent to PHY layer devices. It is used only during auto-negotiation, and is applicable only to twisted-pair links.

**Remote Fault Detection.** register bit 4.13 in the Auto-Negotiation Advertisement Register is reserved for Remote Fault indications. It is typically used when re-starting the auto-negotiation sequence to indicate to the link partner that the link is down because the advertising device detected a local fault.

When the LXT972M PHY receives a Remote Fault indication from its partner during autonegotiation, the following occurs:

- register bit 5.13 in the Link Partner Base Page Ability Register is set.

- Remote Fault register bit 1.4 in the MII Status Register is set to pass this information to the local controller.

### 5.2.2 MII Data Interface

The LXT972M PHY supports a standard Media Independent Interface (MII). The MII consists of a data interface and a management interface. The MII Data Interface passes data between the LXT972M PHY and a Media Access Controller (MAC). Separate parallel buses are provided for transmit and receive. This interface operates at either 10 Mbps or 100 Mbps. The speed is set automatically, once the operating conditions of the network link have been determined. For details, see Section 5.6, *MII Operation*, on page 30.

**Increased MII Drive Strength.** A higher Media Independent Interface (MII) drive strength may be desired in some designs to drive signals over longer PCB trace lengths, or over high-capacitive loads, through multiple vias, or through a connector. The MII drive strength in the LXT972M PHY can be increased by setting register bit 26.11 through software control. Setting register bit 26.11 = 1 through the MDC/MDIO interface sets the MII pins (RXD[3:0], RX\_DV, RX\_CLK, RX\_ER, COL, CRS, and TX\_CLK) to a higher drive strength.

### **5.2.3 Configuration Management Interface**

The LXT972M PHY provides both an MDIO interface and a reduced hardware control interface for device configuration and management.

### 5.2.3.1 MDIO Management Interface

MDIO management interface topics include the following:

- Section 5.2.3.1.1, *MDIO Addressing*

- Section 5.2.3.1.2, MDIO Frame Structure

The LXT972M PHY supports the IEEE 802.3 MII Management Interface also known as the Management Data Input/Output (MDIO) Interface. This interface allows upper-layer devices to monitor and control the state of the LXT972M PHY. The MDIO interface consists of a physical connection, a specific protocol that runs across the connection, and an internal set of addressable registers.

Some registers are required and their functions are defined by the IEEE 802.3 standard. The LXT972M PHY also supports additional registers for expanded functionality. The LXT972M PHY supports multiple internal registers, each of which is 16 bits wide. Specific register bits are referenced using an "X.Y" notation, where X is the register number (0-31) and Y is the bit number (0-15).

### 5.2.3.1.1 MDIO Addressing

The MDIO addressing protocol allows a controller to communicate with multiple PHYs. Pins ADDR[1:0] determine the PHY device address that is selected (see Table 13).

| ADDR1<br>(Pin 11) | ADDR0<br>(Pin 10) | PHY Device<br>Address<br>Selected |

|-------------------|-------------------|-----------------------------------|

| 0                 | 0                 | 0                                 |

| 0                 | 1                 | 1                                 |

| 1                 | 0                 | 28                                |

| 1                 | 1                 | 29                                |

### Table 13 PHY Device Address Selections

### 5.2.3.1.2 MDIO Frame Structure

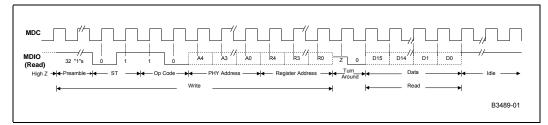

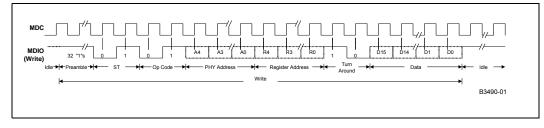

The physical interface consists of a data line (MDIO) and clock line (MDC). The frame structure is shown in Figure 3 and Figure 4 (Read and Write).

MDIO Interface timing is given in Section 7.0, *Electrical Specifications*.

Figure 3 Management Interface Read Frame Structure

### Figure 4 Management Interface Write Frame Structure

### 5.2.3.2 Hardware Control Interface

The LXT972M PHY provides a Hardware Control Interface for applications where the MDIO is not desired. The Hardware Control Interface uses the hardware configuration pins to set device configuration. For details, see Section 5.4.4, *Hardware Configuration Settings*, on page 28.

### 5.3 **Operating Requirements**

### **5.3.1 Power Requirements**

The LXT972M PHY requires three power supply inputs:

- VCCA

- VCCD

- VCCIO

The digital and analog circuits require 3.3 V supplies (VCCA and VCCD). These inputs may be supplied from a single source. Each supply input must be de-coupled to ground.

An additional supply may be used for the MII (VCCIO). The supply may be either 2.5 V or 3.3 V. Also, the inputs on the MII interface are tolerant to 5 V signals from the controller on the other side of the MII interface. For MII I/O characteristics, see Table 24, *Digital I/O Characteristics*<sup>1</sup> - *MII Pins*, on page 52.

- **Notes:** 1. Bring up power supplies as close to the same time as possible.

- 2. As a matter of good practice, keep power supplies as clean as possible.

### **5.3.2 Clock Requirements**

### 5.3.2.1 External Crystal/Oscillator

The LXT972M PHY requires a reference clock input that is used to generate transmit signals and recover receive signals. It may be provided by either of two methods: by connecting a crystal across the oscillator pins (XI and XO) with load capacitors, or by connecting an external clock source to pin XI.

The connection of a clock source to the XI pin requires the XO pin to be left open. To minimize transmit jitter, Cortina recommends a crystal-based clock instead of a derived clock (that is, a PLL-based clock).

A crystal is typically used in NIC applications. An external 25 MHz clock source, rather than a crystal, is frequently used in switch applications. For clock timing requirements, see Table 25, *I/O Characteristics - REFCLK/XI and XO Pins*, on page 53.

### 5.3.2.2 MDIO Clock

The MII management channel (MDIO) also requires an external clock. The managed data clock (MDC) speed is a maximum of 8 MHz.

### 5.4 Initialization

This section includes the following topics:

• Section 5.4.1, MDIO Control Mode and Hardware Control Mode

- Section 5.4.2, Reduced-Power Modes

- Section 5.4.3, *Reset*

- Section 5.4.4, Hardware Configuration Settings

When the LXT972M PHY is first powered on, reset, or encounters a link failure state, it checks the MDIO register configuration bits to determine the line speed and operating conditions to use for the network link.

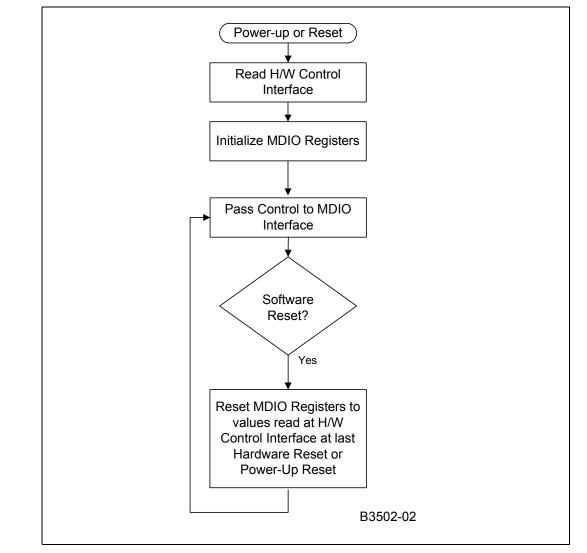

Figure 5 shows the LXT972M PHY initialization sequence. The configuration bits may be set by the Hardware Control or MDIO interface.

### 5.4.1 MDIO Control Mode and Hardware Control Mode

In the MDIO Control mode, the LXT972M PHY reads the Hardware Control Interface pins to set the initial (default) values of the MDIO registers. Once the initial values are set, bit control reverts to the MDIO interface.

The following modes are available using either Hardware Control or MDIO control:

- · Force network link operation to:

- 100BASE-TX, Full-Duplex

- 100BASE-TX, Half-Duplex

- 10BASE-T, Full-Duplex

- 10BASE-T, Half-Duplex

- Allow auto-negotiation/parallel-detection

On power-up or hardware reset, the LXT972M PHY reads the Hardware Control Interface pins and sets the MDIO registers accordingly.

The following modes are available using the Hardware Control:

- · Auto-negotiation-enabled advertising, either:

- 10/100 BASE-T Full/Half Duplex

- 10/100 BASE-T Half Duplex

- · Device ID enable

- · Link Hold-off

When the network link is forced to a specific configuration, the LXT972M PHY immediately begins operating the network interface as commanded. When auto-negotiation is enabled, the LXT972M PHY begins the auto-negotiation/parallel-detection operation.

### 5.4.2 Reduced-Power Modes

This section discusses the LXT972M PHY reduced-power modes.

### 5.4.2.1 Software Power Down

Software power-down control is provided by register bit 0.11 in the Control Register. During soft power-down, the following conditions are true:

- The network port is shut down.

- The MDIO registers remain accessible.

### 5.4.3 Reset

The LXT972M PHY provides both hardware and software resets, each of which manage differently the configuration control of auto-negotiation, speed, and duplex-mode selection.

For a software reset, register bit 0.15 = 1. For register bit definitions used for software reset, see Table 40, *Control Register - Address 0, Hex 0*, on page 65.

During a software reset, bit settings in Table 44, Auto-Negotiation Advertisement Register - Address 4, Hex 4, on page 68 are not re-read from the LXT972M PHY configuration pins. Instead, the bit settings revert to the values that were read in

during the last hardware reset. Therefore, any changes to pin values made since the last hardware reset are not detected during a software reset.

During a software reset, registers are available for reading. To see when the LXT972M PHY has completed reset, the reset bit can be polled (that is, register bit 0.15 = 0).

For pin settings used during a hardware reset, see Section 5.4.4, *Hardware Configuration Settings*. During a hardware reset, configuration settings for auto-negotiation and speed are read in from pins, and register information is unavailable for 1 ms after de-assertion of the reset.

### 5.4.4 Hardware Configuration Settings

The LXT972M PHY provides a hardware option to set the initial device configuration. As listed in Table 14, the hardware option uses the hardware configuration pins, the settings for which provide control bits.

| Desired Mode |                 |              | LED/CFG                      |   | Resulting register bit Values |                       |               |                        |                                            |                           |                                        |                     |

|--------------|-----------------|--------------|------------------------------|---|-------------------------------|-----------------------|---------------|------------------------|--------------------------------------------|---------------------------|----------------------------------------|---------------------|

|              |                 |              | Pin<br>Settings <sup>1</sup> |   |                               | Control Register      |               |                        | Auto-Negotiation Advertisement<br>Register |                           |                                        |                     |

| Auto-Neg.    | Speed<br>(Mbps) | Duplex       | 1                            | 2 | 3                             | Auto-<br>Neg.<br>0.12 | Speed<br>0.13 | Full-<br>Duplex<br>0.8 | 100<br>BASE-TX<br>Full-<br>Duplex<br>4.8   | 100<br>BASE-<br>TX<br>4.7 | 10<br>BASE-T<br>Full-<br>Duplex<br>4.6 | 10<br>BASE-T<br>4.5 |

|              | 10              | Half         | L                            | L | L                             | 0                     | 0             | 0                      |                                            |                           |                                        |                     |

| Disabled     |                 | Full         | L                            | L | Н                             |                       | 0             | 1                      |                                            | N/A                       |                                        |                     |

| Disabled     | 100             | Half         | L                            | Н | L                             |                       | 1             | 0                      | Auto-Negotiation<br>Advertisement          |                           |                                        |                     |

|              |                 | Full         | L                            | Н | Н                             |                       | 1             | 1                      |                                            |                           |                                        |                     |

| Enabled      | 100<br>Only     | Half         | Н                            | L | L                             | 1                     | 1             | 0                      | 0                                          | 1                         | 0                                      | 0                   |

|              |                 | Full/Half    | Н                            | L | Н                             |                       | 1             | 1                      | 1                                          | 1                         | 0                                      | 0                   |

|              | 10/100          | Half Only    | н                            | н | L                             |                       | 1             | 0                      | 0                                          | 1                         | 0                                      | 1                   |

|              |                 | Full or Half | Н                            | н | Н                             |                       | 1             | 1                      | 1                                          | 1                         | 1                                      | 1                   |

### Table 14 Hardware Configuration Settings

## 5.5 Establishing Link

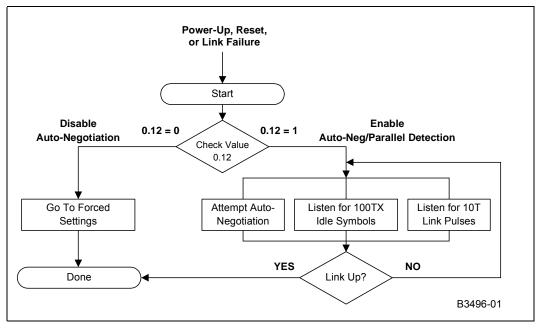

Figure 6 shows an overview of link establishment for the LXT972M PHY.

**Note:** When a link is established by using parallel detection, the LXT972M PHY sets the duplex mode to half-duplex, as defined by the IEEE 802.3 standard.

### 5.5.1 Auto-Negotiation

#### Figure 6 Link Establishment Overview

If not configured for forced operation, the LXT972M PHY attempts to auto-negotiate with its link partner by sending Fast Link Pulse (FLP) bursts. Each burst consists of up to 33 link pulses spaced 62.5 µs apart. Odd link pulses (clock pulses) are always present. Even link pulses (data pulses) may be absent or present to indicate a '0' or a '1'. Each FLP burst exchanges 16 bits of data, which are referred to as a "link code word". All devices that support auto-negotiation must implement the "Base Page" defined by the IEEE 802.3 standard (Registers 4 and 5).

The LXT972M PHY also supports the optional "Next Page" function as listed in Table 47, *Auto-Negotiation Next Page Transmit Register - Address 7, Hex 7*, on page 70 and Table 48, *Auto-Negotiation Link Partner Next Page Receive Register - Address 8, Hex 8*, on page 71.

### 5.5.1.1 Base Page Exchange

By exchanging Base Pages, the LXT972M PHY and its link partner communicate their capabilities to each other. Both sides must receive at least three consecutive identical base pages for negotiation to continue. Each side identifies the highest common capabilities that both sides support, and each side configures itself accordingly.

### 5.5.1.2 Manual Next Page Exchange

"Next Page Exchange" information is additional information that exceeds the information required by Base Page exchange and that is sent by "Next Pages". The LXT972M PHY fully supports the IEEE 802.3 standard method of negotiation through the Next Page exchange.

The Next Page exchange uses Register 7 to send information and Register 8 to receive it. Next Page exchange occurs only if both ends of the link partners advertise their ability to exchange Next Pages. register bit 6.1 is used to make manual next page exchange easier

for software. This register bit is cleared when a new negotiation occurs, preventing the user from reading an old value in Register 6 and assuming there is valid information in Registers 5 and 8.

### 5.5.1.3 Controlling Auto-Negotiation

When auto-negotiation is controlled by software, Cortina recommends the following steps:

- 1. After power-up, power-down, or reset, the power-down recovery time (specified in Table 38, *RESET\_L Pulse Width and Recovery Timing*, on page 63) must be exhausted before proceeding.

- 2. Set the Auto-Negotiation Advertisement register bits.

- 3. Enable auto-negotiation. (Set MDIO register bit 0.12 = 1.)

- 4. To ensure proper operation, enable or restart auto-negotiation as soon as possible after writing to Register 4.

### 5.5.2 Parallel Detection

In parallel with auto-negotiation, the LXT972M PHY also monitors for 10 Mbps Normal Link Pulses (NLP) or 100 Mbps Idle symbols. If either symbol is detected, the device automatically reverts to the corresponding speed in half-duplex mode. Parallel detection allows the LXT972M PHY to communicate with devices that do not support auto-negotiation.

When parallel detection resolves a link, the link must be established in half-duplex mode. According to IEEE standards, the forced link partner cannot be configured to full-duplex. If the auto-negotiation link partner does not advertise half-duplex capability at the speed of the forced link partner, link is not established. The IEEE Standard prevents full-duplex-to-half-duplex link connections.

### 5.6 MII Operation

This section includes the following topics:

- Section 5.6.1, *MII Clocks*

- Section 5.6.2, Transmit Enable

- Section 5.6.3, Receive Data Valid

- Section 5.6.4, Carrier Sense

- Section 5.6.5, Error Signals

- Section 5.6.6, Collision

- Section 5.6.7, Loopback

The LXT972M PHY implements the Media Independent Interface (MII) as defined by the IEEE 802.3 standard. Separate channels are provided for transmitting data from the MAC to the LXT972M PHY (TXD), and for passing data received from the line (RXD) to the MAC. Each channel has its own clock, data bus, and control signals.

The following signals are used to pass received data to the MAC:

- COL

- CRS

- RX\_CLK

- RX\_DV

- RX\_ER

- RXD[3:0]

The following signals are used to transmit data from the MAC:

- TX\_CLK

- TX\_EN

- TXD[3:0]

The LXT972M PHY supplies both clock signals as well as separate outputs for carrier sense and collision. Data transmission across the MII is normally implemented in 4-bit-wide nibbles.

### 5.6.1 MII Clocks

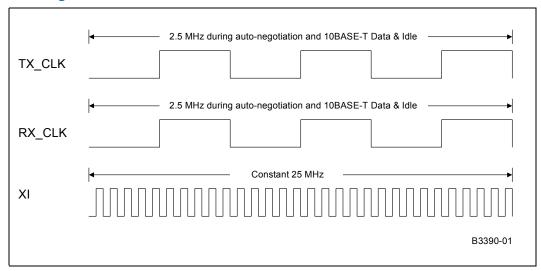

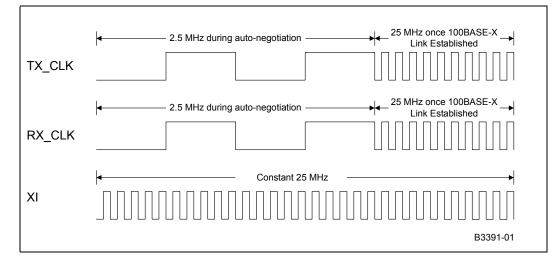

The LXT972M PHY is the master clock source for data transmission, and it supplies both MII clocks (RX\_CLK and TX\_CLK). It automatically sets the clock speeds to match link conditions.

- When the link is operating at 100 Mbps, the clocks are set to 25 MHz.

- When the link is operating at 10 Mbps, the clocks are set to 2.5 MHz.

Figure 7 through Figure 9 show the clock cycles for each mode.

**Note:** The transmit data and control signals must always be synchronized to TX\_CLK by the MAC. The LXT972M PHY samples these signals on the rising edge of TX\_CLK.

### Figure 7 Clocking for 10BASE-T

#### Figure 8 Clocking for 100BASE-X

### Figure 9 Clocking for Link Down Clock Transition

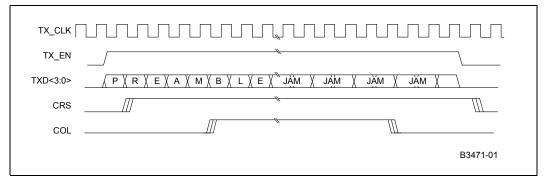

### 5.6.2 Transmit Enable

The MAC must assert TX\_EN the same time as the first nibble of preamble and de-assert TX\_EN after the last nibble of the packet.

### 5.6.3 Receive Data Valid

The LXT972M PHY asserts RX\_DV when it receives a valid packet. Timing changes depend on line operating speed:

- For 100BASE-TX links, RX\_DV is asserted from the first nibble of preamble to the last nibble of the data packet.

- For 10BASE-T links, the entire preamble is truncated. RX\_DV is asserted with the first nibble of the Start of Frame Delimiter (SFD) "5D" and remains asserted until the end of the packet.

### 5.6.4 Carrier Sense

Carrier Sense (CRS) is an asynchronous output.

- CRS is always generated when the LXT972M PHY receives a packet from the line.

- CRS is also generated when the LXT972M PHY is in half-duplex mode when a packet is transmitted.

Table 15 summarizes the conditions for assertion of carrier sense, data loopback, and collision signals. Carrier sense is not generated when a packet is transmitted and in full-duplex mode.

| Table 15 | <b>Carrier Sense</b> , | Loopback. | and Co | ollision | Conditions |

|----------|------------------------|-----------|--------|----------|------------|

|          | Guiller Schoe,         | LOOPDUCK, |        |          | Conditions |

| Duplex Condition                      | Carrier Sense                                                                                                | Test<br>Loop-<br>back <sup>1, 2</sup>                                                                                                                        | Operational<br>Loop-<br>back <sup>1, 2</sup>                                                                                                                                                              | Collision                                                                                                                                                                                                            |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Full-Duplex                           | Receive Only                                                                                                 | Yes                                                                                                                                                          | No                                                                                                                                                                                                        | None                                                                                                                                                                                                                 |

| Half-Duplex                           | Transmit or Receive                                                                                          | No                                                                                                                                                           | No                                                                                                                                                                                                        | Transmit and Receive                                                                                                                                                                                                 |

| Full-Duplex                           | Receive Only                                                                                                 | Yes                                                                                                                                                          | No                                                                                                                                                                                                        | None                                                                                                                                                                                                                 |

| Half-Duplex,<br>register bit 16.8 = 0 | Transmit or Receive                                                                                          | Yes                                                                                                                                                          | Yes                                                                                                                                                                                                       | Transmit and Receive                                                                                                                                                                                                 |

| Half-Duplex,<br>register bit 16.8 = 1 | Transmit or Receive                                                                                          | No                                                                                                                                                           | No                                                                                                                                                                                                        | Transmit and Receive                                                                                                                                                                                                 |

|                                       | Half-Duplex<br>Full-Duplex<br>Half-Duplex,<br>register bit 16.8 = 0<br>Half-Duplex,<br>register bit 16.8 = 1 | Half-DuplexTransmit or ReceiveFull-DuplexReceive OnlyHalf-Duplex,<br>register bit 16.8 = 0Transmit or ReceiveHalf-Duplex,<br>Half-Duplex,Transmit or Receive | Full-DuplexReceive OnlyYesHalf-DuplexTransmit or ReceiveNoFull-DuplexReceive OnlyYesHalf-Duplex,<br>register bit 16.8 = 0Transmit or ReceiveYesHalf-Duplex,<br>register bit 16.8 = 1Transmit or ReceiveNo | Full-DuplexReceive OnlyYesNoHalf-DuplexTransmit or ReceiveNoNoFull-DuplexReceive OnlyYesNoHalf-Duplex,<br>register bit 16.8 = 0Transmit or ReceiveYesYesHalf-Duplex,<br>register bit 16.8 = 1Transmit or ReceiveNoNo |

1. Test Loopback is enabled when register bit 0.14 = 1.

2. For descriptions of Test Loopback and Operational Loopback, see Section 5.6.7, Loopback, on page 33.

### 5.6.5 Error Signals

When the LXT972M PHY is in 100 Mbps mode and receives an invalid symbol from the network, it asserts RX\_ER and drives "0101" on the RXD pins.

The TX\_ER function that forces 'H' symbols out on the TPOP/TPON twisted pair is not implemented in the LXT972M PHY.

### 5.6.6 Collision

The LXT972M PHY asserts its collision signal asynchronously to any clock whenever the line state is half-duplex and the transmitter and receiver are active at the same time. Table 15 summarizes the conditions for assertion of carrier sense, data loopback, and collision signals.

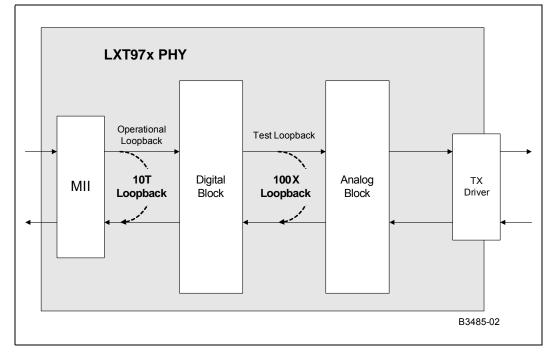

### 5.6.7 Loopback

The LXT972M PHY provides the following loopback functions:

- Section 5.6.7.1, Operational Loopback

- Section 5.6.7.2, Internal Digital Loopback (Test Loopback)

Figure 10 shows LXT972M PHY operational and test loopback paths. For more information on loopback functions, see Table 15, *Carrier Sense, Loopback, and Collision Conditions*, on page 33.)

#### Figure 10 Loopback Paths

### 5.6.7.1 Operational Loopback

- Operational loopback is provided for 10 Mbps half-duplex links when register bit 16.8

= 0. Data that the MAC (TXData) transmits loops back on the receive side of the MII (RXData).

- Operational loopback is not provided for 100 Mbps links, full-duplex links, or when Register 16.8 = 1.

### 5.6.7.2 Internal Digital Loopback (Test Loopback)

A test loopback function is provided for diagnostic testing of the LXT972M PHY. During test loopback, twisted-pair and fiber interfaces are disabled. Data transmitted by the MAC is internally looped back by the LXT972M PHY and returned to the MAC.

Test loopback is available for both 100BASE-TX and 10BASE-T operation, and is enabled by setting the following register bits:

- register bit 0.14 = 1 (Setting to enable loopback mode)

- register bit 0.8 = 1 (Setting for full-duplex mode)

- register bit 0.12 = 0 (Disable auto-negotiation)

**Note:** Parallel detection can resolve the PHY configuration.

## 5.7 100 Mbps Operation

### 5.7.1 **100BASE-X Network Operations**

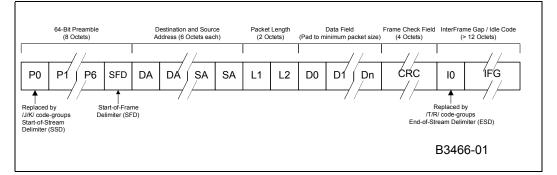

During 100BASE-X operation, the LXT972M PHY transmits and receives 5-bit symbols across the network link.

Figure 11 shows the structure of a standard frame packet in 100BASE-X mode. When the MAC is not actively transmitting data, the LXT972M PHY sends out Idle symbols on the line.

As Figure 11 shows, the MAC starts each transmission with a preamble pattern. As soon as the LXT972M PHY detects the start of preamble, it transmits a Start-of-Stream Delimiter (SSD, symbols J and K) to the network. It then encodes and transmits the rest of the packet, including the balance of the preamble, the SFD, packet data, and CRC.

Once the packet ends, the LXT972M PHY transmits the End-of-Stream Delimiter (ESD, symbols T and R) and then returns to transmitting Idle symbols.

For details on the symbols used, see 4B/5B coding listed in Table 16, *4B/5B Coding*, on page 39.

### Figure 11 100BASE-X Frame Format

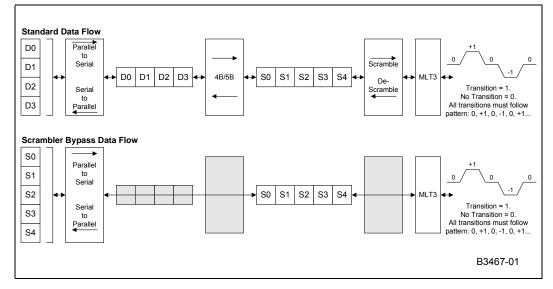

As shown in Figure 12, in 100BASE-TX mode, the LXT972M PHY scrambles and transmits the data to the network using MLT-3 line code. MLT-3 signals received from the network are de-scrambled, decoded, and sent across the MII to the MAC.

### Figure 12 100BASE-TX Data Path

Figure 13 shows normal reception with no errors.

#### Figure 13 100BASE-TX Reception with No Errors