# Contents

| 1 | Appl  | ication diagram                     |

|---|-------|-------------------------------------|

| 2 | Pin o | lescription                         |

| 3 | Elec  | trical specifications6              |

|   | 3.1   | Absolute maximum ratings 6          |

|   | 3.2   | Thermal data                        |

|   | 3.3   | Electrical specifications           |

| 4 | Char  | acterization curves                 |

| 5 | Outp  | out filter                          |

|   | 5.1   | Theoretical filter                  |

|   | 5.2   | Optimized filter 20                 |

| 6 | Pack  | age information                     |

| 7 | Trad  | emarks and other acknowledgments 24 |

| 8 | Revi  | sion history                        |

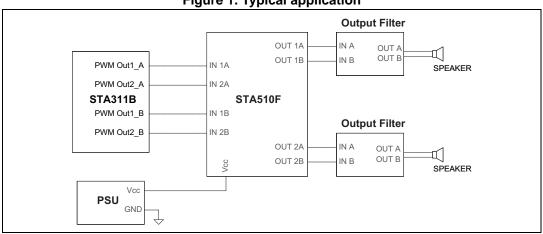

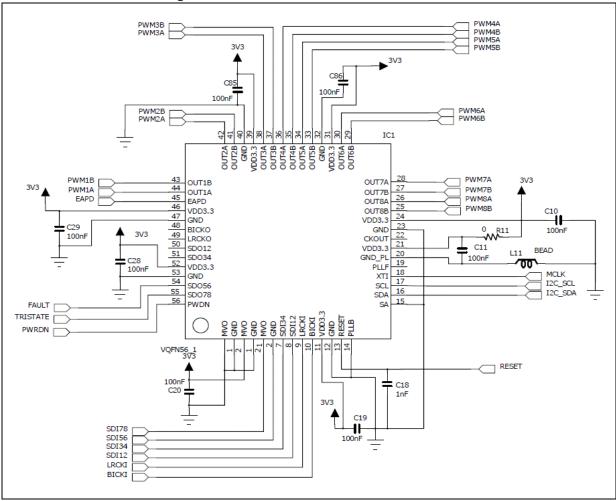

# 1 Application diagram

Figure 1. Typical application

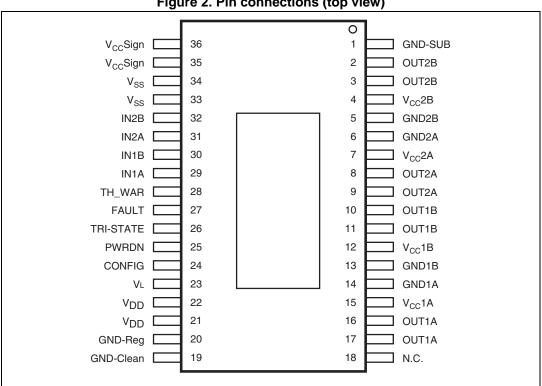

#### **Pin description** 2

#### Figure 2. Pin connections (top view)

Table 2. Pin list

| Pin    | Name    | Description           |

|--------|---------|-----------------------|

| 1      | GND-SUB | Substrate ground      |

| 2, 3   | OUT2B   | Output half-bridge 2B |

| 4      | Vcc2B   | Positive supply       |

| 5      | GND2B   | Negative supply       |

| 6      | GND2A   | Negative supply       |

| 7      | Vcc2A   | Positive supply       |

| 8, 9   | OUT2A   | Output half-bridge 2A |

| 10, 11 | OUT1B   | Output half-bridge 1B |

| 12     | Vcc1B   | Positive supply       |

| 13     | GND1B   | Negative supply       |

| 14     | GND1A   | Negative supply       |

| 15     | Vcc1A   | Positive supply       |

| 16, 17 | OUT1A   | Output half-bridge 1A |

| 18     | NC      | Not connected         |

| Pin    | Name      | Description                                |  |  |  |

|--------|-----------|--------------------------------------------|--|--|--|

| 19     | GND-clean | Logical ground                             |  |  |  |

| 20     | GND-Reg   | Ground for regulator Vdd                   |  |  |  |

| 21, 22 | Vdd       | 5-V regulator referred to ground           |  |  |  |

| 23     | VL        | High logical state setting voltage         |  |  |  |

| 24     | CONFIG    | Configuration                              |  |  |  |

| 25     | PWRDN     | Standby                                    |  |  |  |

| 26     | TRI-STATE | Hi-Z                                       |  |  |  |

| 27     | FAULT     | Fault pin advisor                          |  |  |  |

| 28     | TH-WAR    | Thermal warning advisor                    |  |  |  |

| 29     | IN1A      | Input of half-bridge 1A                    |  |  |  |

| 30     | IN1B      | Input of half-bridge 1B                    |  |  |  |

| 31     | IN2A      | Input of half-bridge 2A                    |  |  |  |

| 32     | IN2B      | Input of half-bridge 2B                    |  |  |  |

| 33, 34 | Vss       | 5-V regulator referred to +V <sub>CC</sub> |  |  |  |

| 35, 36 | VCCSIGN   | Signal positive supply                     |  |  |  |

Table 2. Pin list (continued)

#### Table 3. Pin values

| Pin                   | Logical value | Device status                                                    |  |  |  |

|-----------------------|---------------|------------------------------------------------------------------|--|--|--|

| FAULT <sup>(1)</sup>  | 0             | Fault detected (short-circuit, or thermal)                       |  |  |  |

| FAULI                 | 1             | Normal operation                                                 |  |  |  |

| TRI-STATE             | 0             | All power stages in Hi-Z state                                   |  |  |  |

| TRI-STATE             | 1             | Normal operation                                                 |  |  |  |

| PWRDN                 | 0             | Low-power mode                                                   |  |  |  |

| FWRDIN                | 1             | Normal operation                                                 |  |  |  |

| THWAR <sup>(1)</sup>  | 0             | Temperature of the IC = 130° C                                   |  |  |  |

|                       | 1             | Normal operation                                                 |  |  |  |

|                       | 0             | Normal operation                                                 |  |  |  |

| CONFIG <sup>(2)</sup> | 1             | OUT1A = OUT1B, OUT2A = OUT2B<br>(IF IN1A = IN1B and IN2A = IN2B) |  |  |  |

1. The pin is open collector. To have the high logic value, it needs a pull-up resistor.

2. CONFIG = 1 means connect pin 24 (CONFIG) to pins 21, 22 (Vdd).

# 3 Electrical specifications

### 3.1 Absolute maximum ratings

### Table 4. Absolute maximum ratings

| Symbol                            | Parameter                            | Value      | Unit |

|-----------------------------------|--------------------------------------|------------|------|

| V <sub>CC</sub>                   | DC supply voltage (pin 4, 7, 12, 15) | 44         | V    |

| V <sub>max</sub>                  | Maximum voltage on pins 23 to 32     | 5.5        | V    |

| ESD                               | Max ESD on pins (HBM)                | ±1000      | V    |

| T <sub>op</sub>                   | Operating temperature range          | 0 to 70    | °C   |

| T <sub>stg</sub> , T <sub>j</sub> | Storage and junction temperature     | -40 to 150 | °C   |

### 3.2 Thermal data

#### Table 5. Thermal data

| Symbol              | Parameter                                         | Min. | Тур. | Max. | Unit |

|---------------------|---------------------------------------------------|------|------|------|------|

| T <sub>j-case</sub> | Thermal resistance junction to case (thermal pad) |      | 1    | 2.5  | °C/W |

| T <sub>jSD</sub>    | Thermal shut-down junction temperature            |      | 150  |      | °C   |

| T <sub>warn</sub>   | Thermal warning temperature                       |      | 130  |      | °C   |

| t <sub>hSD</sub>    | Thermal shutdown hysteresis                       |      | 25   |      | °C   |

### 3.3 Electrical specifications

The results in *Table* 6 below are given for the conditions:  $V_L$  = 3.3 V,  $V_{CC}$  = 37 V and T = 25 °C unless otherwise specified.

| Symbol            | Parameter                                 | Condition                                                                                                    | Min. | Тур. | Max. | Unit |

|-------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------|------|------|------|------|

| R <sub>dsON</sub> | Power P-channel/N-channel<br>MOSFET RdsON | ld = 1 A                                                                                                     |      | 150  | 200  | mΩ   |

| I <sub>dss</sub>  | Power P-channel/N-channel leakage current |                                                                                                              |      |      | 100  | μA   |

| g <sub>N</sub>    | Power P-channel RdsON matching            | ld = 1 A                                                                                                     | 95   |      |      | %    |

| 9 <sub>P</sub>    | Power N-channel RdsON matching            | Id = 1 A                                                                                                     | 95   |      |      | %    |

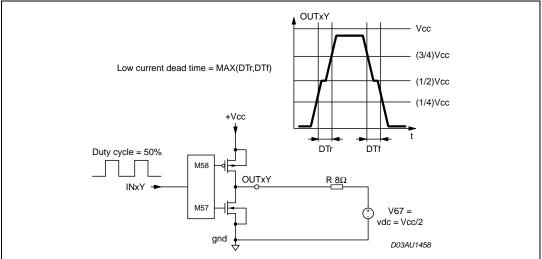

| Dt_s              | Low current deadtime (static)             | see test circuit Figure 3                                                                                    |      | 10   | 20   | ns   |

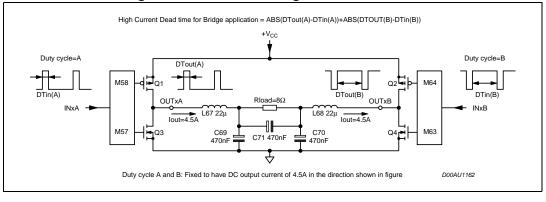

| Dt_d              | High current deadtime (dynamic)           | L = 22 $\mu$ H, C = 470 nF,<br>R <sub>L</sub> = 8 $\Omega$ , Id = 4.5 A,<br>see test circuit <i>Figure 4</i> |      |      | 50   | ns   |

| t <sub>d ON</sub> | Turn-on delay time                        | Resistive load                                                                                               |      |      | 100  | ns   |

| Symbol                     | Parameter                                                                      | Condition                                                                                  | Min.                          | Тур. | Max.                          | Unit |

|----------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------|------|-------------------------------|------|

| t <sub>d OFF</sub>         | Turn-off delay time                                                            | Resistive load                                                                             |                               |      | 100                           | ns   |

| t <sub>r</sub>             | Rise time                                                                      | Resistive load, as Figure 4                                                                |                               |      | 25                            | ns   |

| t <sub>f</sub>             | Fall time                                                                      | Resistive load, as Figure 4                                                                |                               |      | 25                            | ns   |

| V <sub>CC</sub>            | Supply voltage operating voltage                                               |                                                                                            | 10                            |      | 40                            | V    |

| V <sub>IN-High</sub>       | High level input voltage                                                       |                                                                                            | V <sub>L</sub> /2 +<br>300 mV |      |                               | V    |

| V <sub>IN-Low</sub>        | Low level input voltage                                                        |                                                                                            |                               |      | V <sub>L</sub> /2 –<br>300 mV | V    |

| I <sub>IN-H</sub>          | High level input current                                                       | Pin voltage = V <sub>L</sub>                                                               |                               | 1    |                               | μA   |

| I <sub>IN-L</sub>          | Low level input current                                                        | Pin voltage = 0.3 V                                                                        |                               | 1    |                               | μA   |

| I <sub>PWRDN-H</sub>       | High level PWRDN pin input current                                             | V <sub>L</sub> = 3.3 V                                                                     |                               | 35   |                               | μA   |

| V <sub>Low</sub>           | Low logical state voltage (pins<br>PWRDN, TRISTATE) (see <i>Table 7</i> )      | V <sub>L</sub> = 3.3 V                                                                     |                               |      | 0.8                           | V    |

| V <sub>High</sub>          | High logical state voltage (pins<br>PWRDN, TRISTATE) (see <i>Table 7</i> )     | V <sub>L</sub> = 3.3 V                                                                     | 1.7                           |      |                               | V    |

| I <sub>VCC-</sub><br>PWRDN | Supply current from V <sub>CC</sub> in power down                              | PWRDN = 0                                                                                  |                               |      | 3                             | mA   |

| I <sub>FAULT</sub>         | Output current pins FAULT -TH-<br>WARN when FAULT CONDITIONS                   | V <sub>PIN</sub> = 3.3 V                                                                   |                               | 1    |                               | mA   |

| I <sub>VCC-hiz</sub>       | Supply current from $V_{CC}$ in tri-state                                      | Pin TRI-STATE = 0                                                                          |                               | 22   |                               | mA   |

| I <sub>VCC</sub>           | Supply current from V <sub>CC</sub> in operation both channel switching)       | Input pulse width duty<br>cycle = 50%, switching<br>frequency = 384 kHz, no LC<br>filters; |                               | 70   |                               | mA   |

| I <sub>OUT-SH</sub>        | Overcurrent protection threshold I <sub>SC</sub> (short-circuit current limit) |                                                                                            | 5.5                           | 7    | 9                             | A    |

| V <sub>UV</sub>            | Undervoltage protection threshold                                              |                                                                                            |                               | 7    |                               | V    |

| t <sub>pw_min</sub>        | Output minimum pulse width                                                     | No load                                                                                    | 25                            |      | 40                            | ns   |

Table 6. Electrical specifications (continued)

| VL  | V <sub>Low</sub> max | V <sub>High</sub> min | Unit |

|-----|----------------------|-----------------------|------|

| 2.7 | 0.7                  | 1.5                   | V    |

| 3.3 | 0.8                  | 1.7                   | V    |

| 5   | 0.85                 | 1.85                  | V    |

Table 7.  $V_{low}$ ,  $V_{high}$  threshold variation with  $V_l$

| Table | 8. | Logic | truth | table |

|-------|----|-------|-------|-------|

|-------|----|-------|-------|-------|

| TRI-STATE | INxA | INxB | Q1  | Q2  | Q3  | Q4  | Output mode |

|-----------|------|------|-----|-----|-----|-----|-------------|

| 0         | х    | х    | OFF | OFF | OFF | OFF | Hi-Z        |

| 1         | 0    | 0    | OFF | OFF | ON  | ON  | DUMP        |

| 1         | 0    | 1    | OFF | ON  | ON  | OFF | NEGATIVE    |

| 1         | 1    | 0    | ON  | OFF | OFF | ON  | POSITIVE    |

| 1         | 1    | 1    | ON  | ON  | OFF | OFF | Not used    |

#### Figure 3. Test circuit for low current deadtime

### Figure 4. Test circuit for high current deadtime

DocID014268 Rev 4

Downloaded from Arrow.com.

8/26

Figure 5. STA311B connections with STA510F

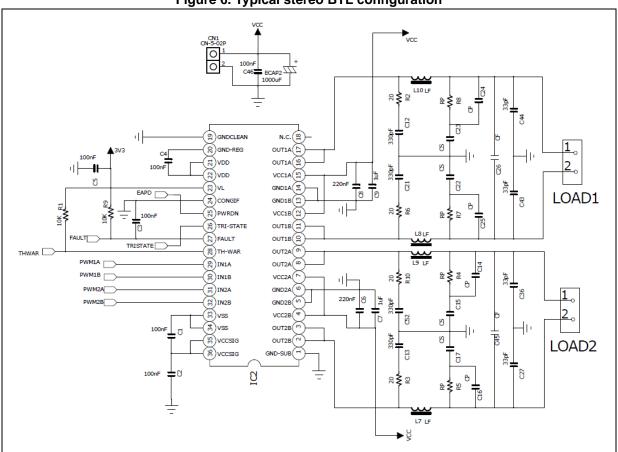

Figure 6. Typical stereo BTL configuration

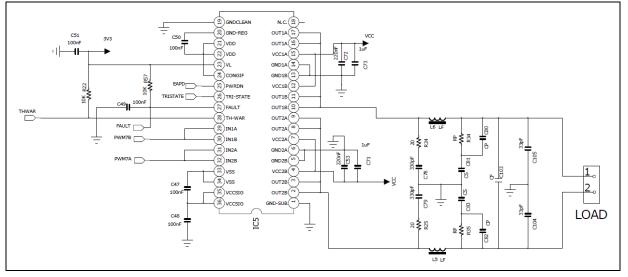

Figure 7. Typical mono BTL configuration

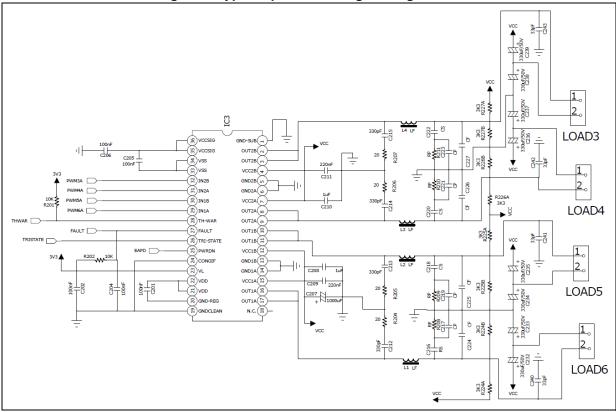

Figure 8. Typical quad half-bridge configuration

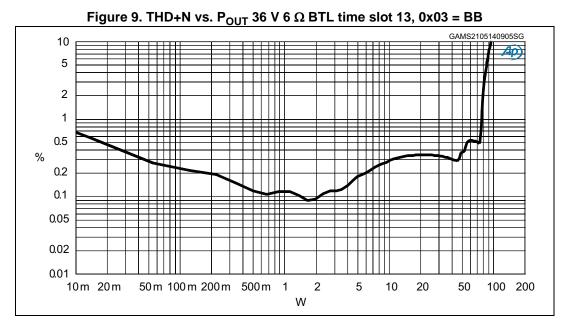

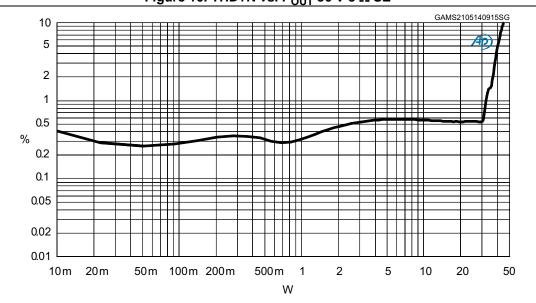

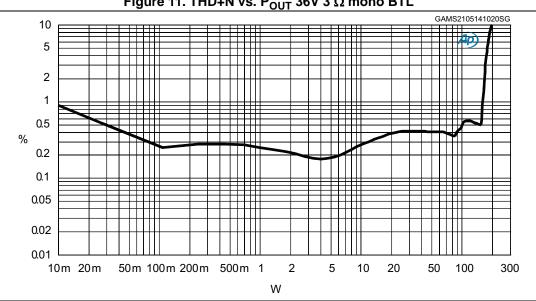

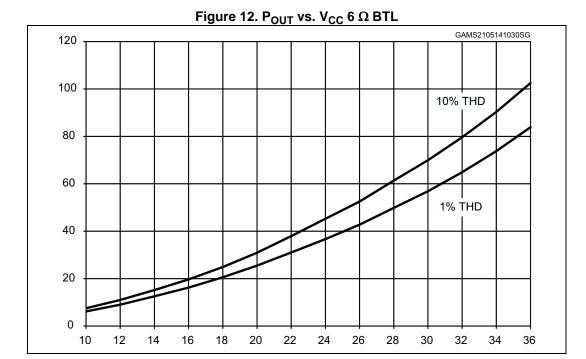

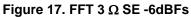

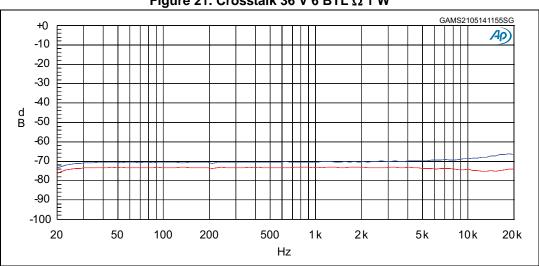

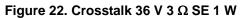

## 4 Characterization curves

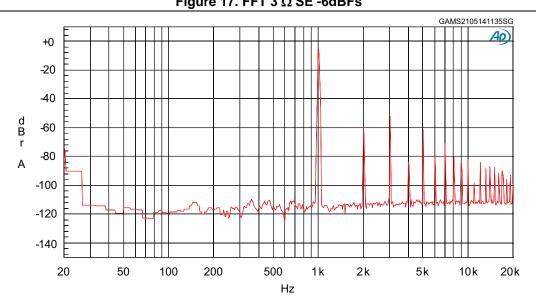

Figure 10. THD+N vs.  $P_{OUT}$  36 V 3  $\Omega$  SE

#### 12/26

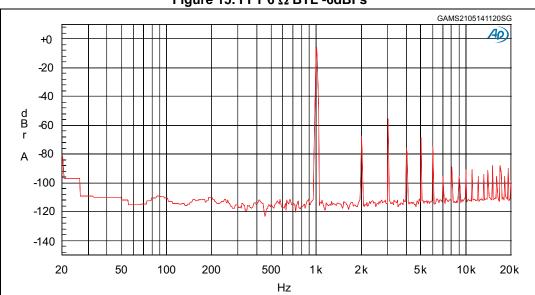

Figure 11. THD+N vs.  $\text{P}_{\text{OUT}}$  36V 3  $\Omega$  mono BTL

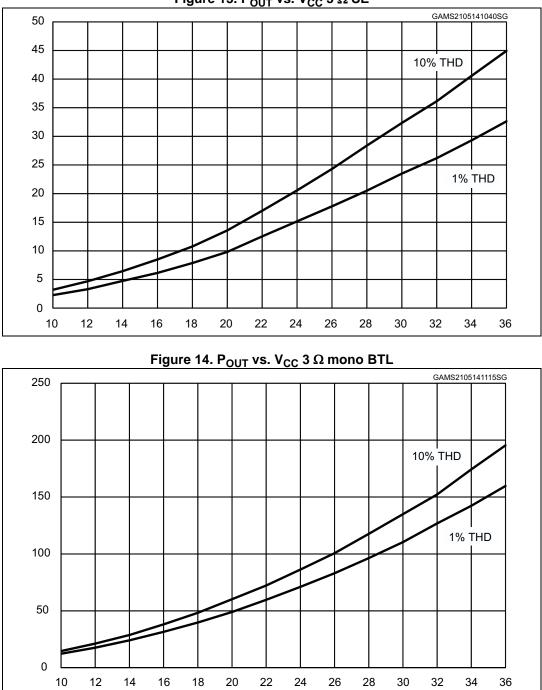

Figure 13.  $P_{OUT}$  vs.  $V_{CC}$  3  $\Omega$  SE

16/26

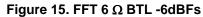

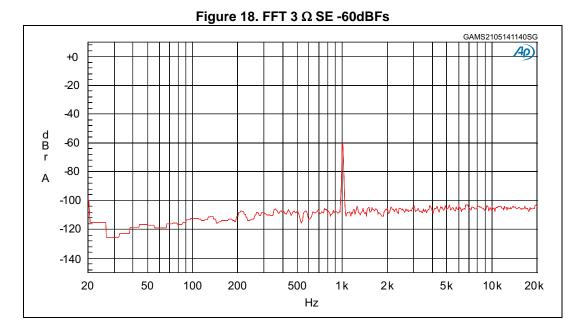

Figure 19. FFT 3 Ω mono BTL -6dBFs

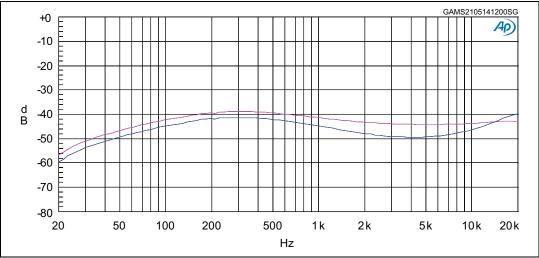

### 5 Output filter

The differential-mode damping of a hybrid filter under no-load conditions is not as good as a pure common-mode filter because most of the high-frequency current flows through the larger capacitor across the speaker terminals. Normally this isn't a problem because the speaker provides the differential-mode damping, but if the amplifier is operated without the speaker connected, for instance when doing testing in production line, then the damping will not be as good.

Care needs to be taken to insure that the damping of a hybrid filter is good enough to protect the amplifier under no-load conditions, thus avoiding peak of voltage that exceed the absolute maximum voltage of the amplifier.

Figure 23. Output filter frequency response with and without load connected to the amplifier

To allow the right filter selection both sets of coefficients are provided.

### 5.1 Theoretical filter

Perfect when using amplifiers always connected to speakers

| Table 9 | <b>Theoretical</b> | table SE |

|---------|--------------------|----------|

|---------|--------------------|----------|

| Load LC Low-Pa |       | ass Filter | Γ      | Damping networ | k     |

|----------------|-------|------------|--------|----------------|-------|

| Impedance      | LF    | CF         | CS     | СР             | RP    |

| 3              | 15 µH | 1 µF       | 100 nF | 100 nF         | 6.2 Ω |

| 4              | 22 µH | 680 nF     | 100 nF | 100 nF         | 6.2 Ω |

| 6              | 33 µH | 470 nF     | 100 nF | 100 nF         | 6.2 Ω |

| 8              | 47 µH | 330 nF     | 100 nF | 100 nF         | 6.2 Ω |

See Figure 8.

| Load      | LC Low-Pass Filter |        | Γ      | k      |       |

|-----------|--------------------|--------|--------|--------|-------|

| Impedance | LF                 | CF     | CS     | СР     | RP    |

| 3         | 10 µH              | 1 µF   | 220 nF | 220 nF | 3.3 Ω |

| 4         | 10 µH              | 1 µF   | 220 nF | 220 nF | 3.3 Ω |

| 6         | 15 µH              | 680 nF | 100 nF | 100 nF | 4.7 Ω |

| 8         | 22 µH              | 470 nF | 100 nF | 100 nF | 6.2 Ω |

Table 10. Theoretical table BTL

See Figure 6.

| Table 11. | Theoretical | table PBTL |

|-----------|-------------|------------|

|           | 1 HCOLCHOUL |            |

| Load      | LC Low-P | LC Low-Pass Filter |        | Damping network |       |  |

|-----------|----------|--------------------|--------|-----------------|-------|--|

| Impedance | LF       | CF                 | CS     | СР              | RP    |  |

| 3         | 10 µH    | 1 µF               | 220 nF | 220 nF          | 2.7 Ω |  |

| 4         | 10 µH    | 1 µF               | 220 nF | 220 nF          | 3.3 Ω |  |

| 6         | 15 µH    | 680 nF             | 100 nF | 100 nF          | 6.2 Ω |  |

| 8         | 22 µH    | 470 nF             | 100 nF | 100 nF          | 6.2 Ω |  |

See Figure 7.

## 5.2 Optimized filter

Suggest to avoid resonant peak when running amplifiers without load

| Load      | Load LC Low-P |        | Pass Filter Damp |        | k     |

|-----------|---------------|--------|------------------|--------|-------|

| Impedance | LF            | CF     | CS               | СР     | RP    |

| 3         | 15 µH         | 680 µF | 100 nF           | 100 nF | 6.2 Ω |

| 4         | 22 µH         | 470 nF | 100 nF           | 100 nF | 6.2 Ω |

| 6         | 33 µH         | 330 nF | 100 nF           | 100 nF | 6.2 Ω |

| 8         | 47 µH         | 220 nF | 100 nF           | 100 nF | 6.2 Ω |

Table 12. Filter optimized to minimize the peak SE

See Figure 8.

|           |                    | •      |        | •               |       |  |

|-----------|--------------------|--------|--------|-----------------|-------|--|

| Load      | LC Low-Pass Filter |        | Γ      | Damping network |       |  |

| Impedance | LF                 | CF     | CS     | СР              | RP    |  |

| 3         | 10 µH              | 680 nF | 220 nF | 220 nF          | 3.3 Ω |  |

| 4         | 10 µH              | 680 nF | 220 nF | 220 nF          | 3.3 Ω |  |

| 6         | 15 µH              | 470 nF | 100 nF | 100 nF          | 4.7 Ω |  |

| 8         | 22 µH              | 330 nF | 100 nF | 100 nF          | 6.2 Ω |  |

Table 13. Filter optimized to minimize the peak BTL

See Figure 6.

### Table 14. Filter optimized to minimize the peak PBTL

| Load      | LC Low-P | ass Filter | ſ      | Damping networ | k     |

|-----------|----------|------------|--------|----------------|-------|

| Impedance | LF       | CF         | CS     | СР             | RP    |

| 3         | 10 µH    | 680 nF     | 220 nF | 220 nF         | 2.7 Ω |

| 4         | 10 µH    | 680 nF     | 220 nF | 220 nF         | 3.3 Ω |

| 6         | 15 µH    | 470 nF     | 100 nF | 100 nF         | 6.2 Ω |

| 8         | 22 µH    | 330 nF     | 100 nF | 100 nF         | 6.2 Ω |

See Figure 7.

## 6 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

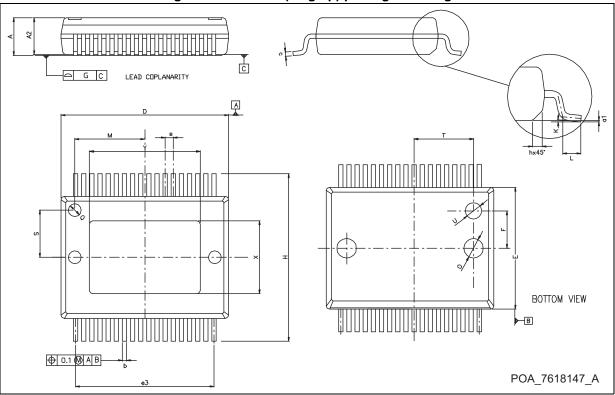

### Figure 24. PSSO36 (slug up) package drawing

| Table 15. PSSO36 (slug up) package dimensions |       |            |       |       |            |       |

|-----------------------------------------------|-------|------------|-------|-------|------------|-------|

| Dim.                                          | mm.   |            |       |       | inch.      |       |

| Dim.                                          | Min.  | Тур.       | Max.  | Min.  | Тур.       | Max.  |

| А                                             | 2.15  |            | 2.47  | 0.084 |            | 0.097 |

| A2                                            | 2.15  |            | 2.40  | 0.084 |            | 0.094 |

| a1                                            | 0     |            | 0.075 | 0     |            | 0.003 |

| b                                             | 0.18  |            | 0.36  | 0.007 |            | 0.014 |

| с                                             | 0.23  |            | 0.32  | 0.009 |            | 0.012 |

| D <sup>(1)</sup>                              | 10.10 |            | 10.50 | 0.398 |            | 0.413 |

| E <sup>(1)</sup>                              | 7.4   |            | 7.6   | 0.291 |            | 0.299 |

| е                                             |       | 0.50       |       |       | 0.020      |       |

| e3                                            |       | 8.50       |       |       | 0.035      |       |

| F                                             |       | 2.3        |       |       | 0.090      |       |

| G                                             |       |            | 0.10  |       |            | 0.004 |

| G1                                            |       |            | 0.06  |       |            | 0.002 |

| Н                                             | 10.10 |            | 10.50 | 0.398 |            | 0.413 |

| h                                             |       |            | 0.40  |       |            | 0.016 |

| L                                             | 0.55  |            | 0.85  | 0.022 |            | 0.033 |

| М                                             |       | 4.3        |       |       | 0.169      |       |

| Ν                                             |       | 10° (max.) |       |       | 10° (max.) |       |

| 0                                             |       | 1.2        |       | 0.047 |            |       |

| Q                                             |       | 0.8        |       |       | 0.031      |       |

| S                                             |       | 2.9        |       |       | 0.114      |       |

| Т                                             |       | 3.65       |       |       | 0.144      |       |

| U                                             |       | 1.0        |       |       | 0.039      |       |

| Х                                             | 4.10  |            | 4.70  | 0.161 |            | 0.185 |

| Y                                             | 6.50  |            | 7.10  | 0.256 |            | 0.279 |

Table 15. PSSO36 (slug up) package dimensions

1. "D and E" do not include mold flash or protrusion. Mold flash or protrusion shall not exceed 0.15 mm (0.006").

# 7 Trademarks and other acknowledgments

FFX is a STMicroelectronics proprietary digital modulation technology. ECOPACK is a registered trademark of STMicroelectronics.

24/26

# 8 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13-Dec-2007 | 1        | Initial release.                                                                                                                                                                                       |

| 28-Jun-2011 | 2        | Added part number STA510FTR to <i>Table 1: Device summary</i><br>Updated ECOPACK <sup>®</sup> text in <i>Section 6: Package information</i><br>Minor textual updates                                   |

| 02-Sep-2011 | 3        | Updated package to PowerSSO36 throughout datasheet<br>Corrected typographical error in <i>Features</i><br>Updated <i>Figure 1</i><br>Updated <i>Figure 2</i><br>Updated <i>Figure 21</i>               |

| 03-Jun-2014 | 4        | <ul> <li>Added:</li> <li>Figure 5 on page 9, Figure 6 on page 10, Figure 7 on page 10 and Figure 8 on page 11</li> <li>Section 4: Characterization curves</li> <li>Section 5: Output filter</li> </ul> |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

> ST and the ST logo are trademarks or registered trademarks of ST in various countries. Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2014 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

26/26