## Contents

| De | escription                                    | 1  |

|----|-----------------------------------------------|----|

| Fe | atures                                        | 1  |

| Ap | plications                                    | 1  |

| 1. | Pin Assignment                                | 3  |

| 2. | Pin Descriptions                              | 4  |

| 3. | Block Diagram                                 | 5  |

| 4. | Absolute Maximum Ratings                      | 6  |

| 5. | Recommended Operating Conditions              | 7  |

| 6. | Electrical Characteristics                    | 8  |

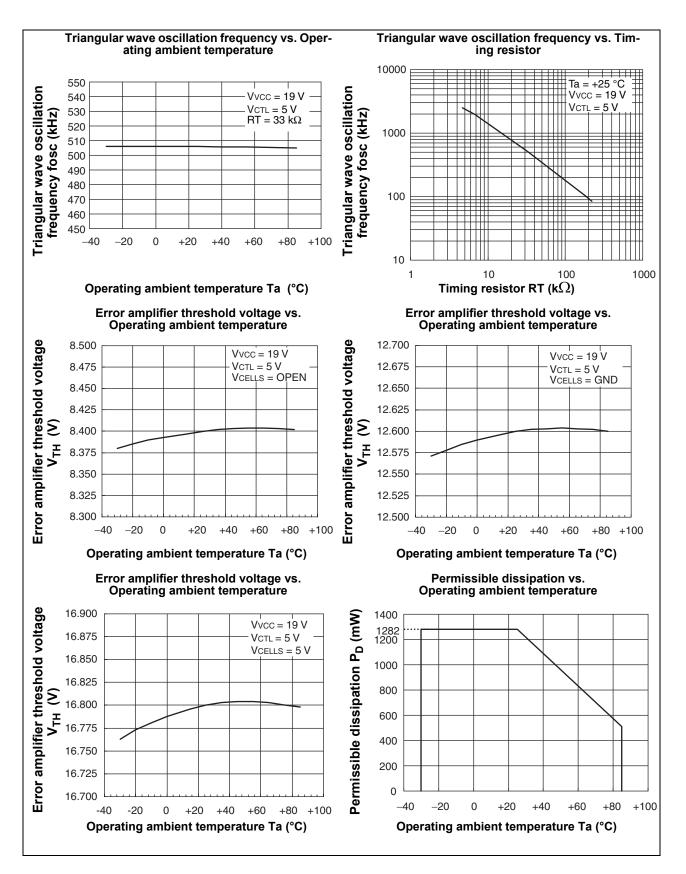

| 7. | Typical Characteristics                       | 12 |

| 8. | Functional Description                        | 14 |

|    | 8.1 DC/DC Converter Block                     |    |

|    | 8.2 Protection Functions                      | 16 |

| 9. | Transit Response When A Load Changes Suddenly | 21 |

| 10. | Connection Without Using The Current Amp1, Curren | nt |

|-----|---------------------------------------------------|----|

|     | Amp2 And The Error Amp1, Error Amp2               | 22 |

| 11. | Input/Output Pin Equivalent Circuit Diagram       | 23 |

| 12. | Typical Application Circuit                       | 26 |

| 13. | Application Note                                  | 30 |

| 14. | Reference Data                                    | 39 |

| 15. | Usage Precaution                                  | 41 |

| 16. | Ordering Information                              | 41 |

| 17. | RoHS Compliance Information                       | 41 |

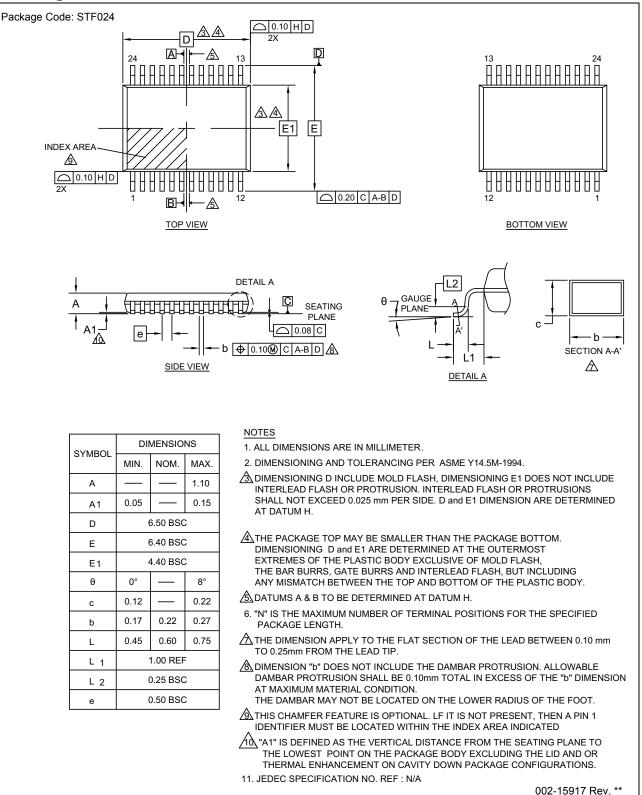

| 18. | Package Dimension                                 | 42 |

| 19. | Document History                                  | 43 |

| Sal | es, Solutions, and Legal Information              | 44 |

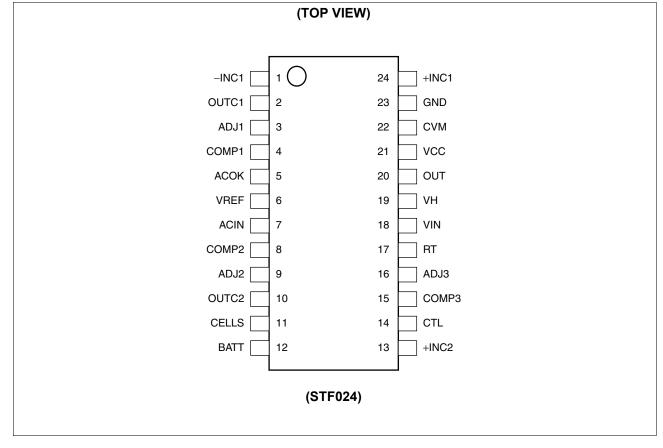

# 1. Pin Assignment

# 2. Pin Descriptions

| Pin No. | Pin Name | I/O | Description                                                                                                                                                                                                                                                                   |

|---------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | -INC1    | Ι   | Current detection amplifier (Current Amp1) inverted input pin.                                                                                                                                                                                                                |

| 2       | OUTC1    | 0   | Current detection amplifier (Current Amp1) output pin.                                                                                                                                                                                                                        |

| 3       | ADJ1     | I   | Error amplifier (Error Amp1) non-inverted input pin.                                                                                                                                                                                                                          |

| 4       | COMP1    | 0   | Error amplifier (Error Amp1) output pin.                                                                                                                                                                                                                                      |

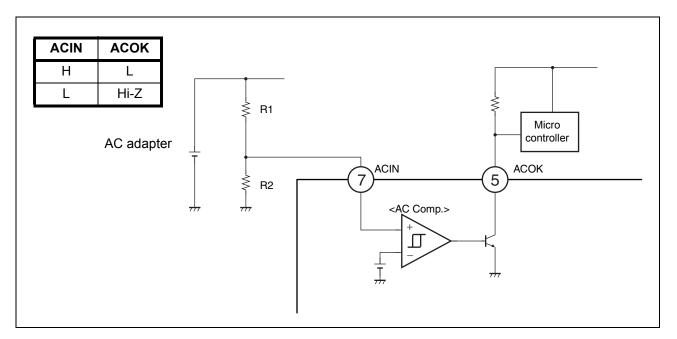

| 5       | ACOK     | 0   | AC adapter voltage detection block (AC Comp.) output pin.<br>ACIN = H : ACOK = L, ACIN = L : ACOK = Hi-Z                                                                                                                                                                      |

| 6       | VREF     | 0   | Reference voltage output pin.                                                                                                                                                                                                                                                 |

| 7       | ACIN     | I   | AC adapter voltage detection block (AC Comp.) input pin.                                                                                                                                                                                                                      |

| 8       | COMP2    | 0   | Error amplifier (Error Amp2) output pin.                                                                                                                                                                                                                                      |

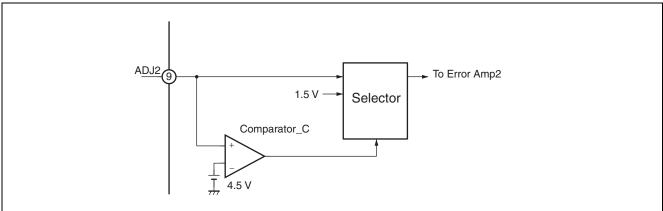

| 9       | ADJ2     | I   | Charge current control block setting input pin.<br>ADJ2 pin "GND to 4.4 V" : Charge current control block output = ADJ2 pin<br>voltage<br>ADJ2 pin "4.6 V to VREF" : Charge current control block output = 1.5 V                                                              |

| 10      | OUTC2    | 0   | Current detection amplifier (Current Amp2) output pin.                                                                                                                                                                                                                        |

| 11      | CELLS    | Ι   | Charge voltage setting switch pin (2 or 3 or 4 Cells).<br>CELLS = VREF: 4 Cells, CELLS = GND: 3 Cells, CELLS = OPEN: 2 Cells                                                                                                                                                  |

| 12      | BATT     | Ι   | Current detection amplifier (Current Amp2) inverted input pin.<br>Battery voltage input pin.                                                                                                                                                                                  |

| 13      | +INC2    | Ι   | Current detection amplifier (Current Amp2) non-inverted input pin.                                                                                                                                                                                                            |

| 14      | CTL      | Ι   | Power supply control pin.<br>Setting the CTL pin at "H" level places the DC/DC converter IC in the operating mode.<br>Setting the CTL pin at "L" level places the DC/DC converter IC in the standby mode.                                                                     |

| 15      | COMP3    | 0   | Error amplifier (Error Amp3) output pin.                                                                                                                                                                                                                                      |

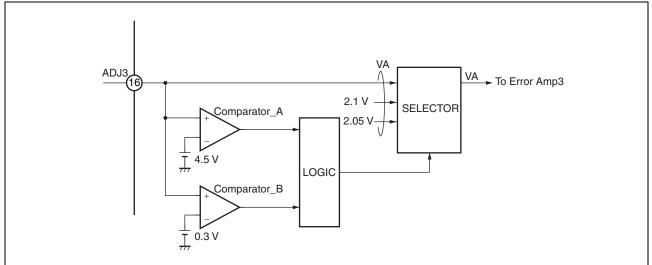

| 16      | ADJ3     | Ι   | Charge voltage control block setting input pin.<br>ADJ3 pin "GND to 0.2 V" : Charge voltage setting 4.10 V/Cell<br>ADJ3 pin "0.4 V to 4.4 V" : Charge voltage setting 2 × V <sub>ADJ3</sub> pin voltage/Cell<br>ADJ3 pin "4.6 V to VREF" : Charge voltage setting 4.20 V/Cell |

| 17      | RT       | -   | Triangular wAVe oscillation frequency setting resistor connection pin.                                                                                                                                                                                                        |

| 18      | VIN      | _   | Power supply pin for ACOK function block.                                                                                                                                                                                                                                     |

| 19      | VH       | 0   | Power supply pin for FET drive circuit (VH = VCC $- 6$ V)                                                                                                                                                                                                                     |

| 20      | OUT      | 0   | External FET gate drive pin.                                                                                                                                                                                                                                                  |

| 21      | VCC      | _   | Power supply pin for reference voltage , control circuit, and output circuit.                                                                                                                                                                                                 |

| 22      | CVM      | 0   | Constant voltage control state detection block (CV Comp.) output pin.                                                                                                                                                                                                         |

| 23      | GND      | _   | Ground pin.                                                                                                                                                                                                                                                                   |

| 24      | +INC1    | Ι   | Current detection amplifier (Current Amp1) non-inverted input pin.                                                                                                                                                                                                            |

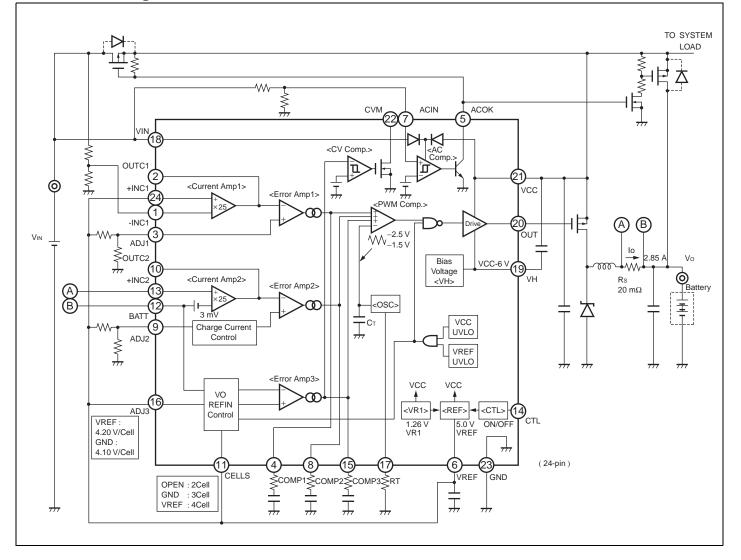

# 3. Block Diagram

| Deremeter             | Symbol           | Condition                                     |       | Rating                  | Unit |

|-----------------------|------------------|-----------------------------------------------|-------|-------------------------|------|

| Parameter Symbol      |                  | Condition                                     | Min   | Min Max                 |      |

| Power supply voltage  | Vv <sub>CC</sub> | VCC, VIN pin                                  | - 0.3 | + 28                    | V    |

|                       |                  | VCC, VIN pin, t $\leq$ 10 $\mu$ s             | - 0.3 | + 32                    | V    |

| Output current        | I <sub>OUT</sub> | OUT pin                                       | - 60  | + 60                    | mA   |

|                       |                  | OUT pin<br>Duty $\leq$ 5% (t = 1/fosc × Duty) | - 700 | + 700                   | mA   |

| CLT pin input voltage | V <sub>CTL</sub> | CTL pin                                       | - 0.3 | + 28                    | V    |

| Input voltage         | V <sub>INE</sub> | ADJ1, ADJ2, ADJ3, CELLS, ACIN<br>pin          | - 0.3 | V <sub>VREF</sub> + 0.3 | V    |

|                       | V <sub>INC</sub> | -INC1, +INC1, BATT, +INC2 pin                 | - 0.3 | + 28                    | V    |

| Power dissipation     | PD               | $Ta \leq +25^{\circ}$                         | -     | 1282* <sup>1,*2</sup>   | mW   |

|                       |                  | $Ta = +85^{\circ}$                            | -     | 512* <sup>1,*2</sup>    | mW   |

| Storage temperature   | T <sub>STG</sub> | -                                             | - 55  | + 125                   | °C   |

# 4. Absolute Maximum Ratings

\*1 : See the diagram of "Typical Characteristics. Maximum Power Dissipation vs. Operating Ambient Temperature", for the package power dissipation of Ta from + 25° C to + 85° C.

\*2 : When IC is mounted on a 10x10 cm two-layer square epoxy board.

**WARNING:** Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

# 5. Recommended Operating Conditions

| Deveneter                                  | Cumhal            | Condition                                           |      | Value | 11                         |     |

|--------------------------------------------|-------------------|-----------------------------------------------------|------|-------|----------------------------|-----|

| Parameter         Symbol         Condition |                   | Min                                                 | Тур  | Мах   | Unit                       |     |

| Power supply voltage                       | V <sub>VCC</sub>  | VCC, VIN pin                                        | 8    | —     | 25                         | V   |

| Reference voltage output current           | I <sub>VREF</sub> | —                                                   | -1   | —     | 0                          | mA  |

| VH pin output current                      | I <sub>VH</sub>   | -                                                   | 0    | —     | 30                         | mA  |

| Input voltage                              | V <sub>INE</sub>  | ADJ1 pin                                            | 0    | —     | V <sub>VREF</sub> -<br>1.5 | V   |

|                                            |                   | ADJ2 pin<br>(internal reference voltage<br>setting) | 4.6  | _     | V <sub>VREF</sub>          | V   |

|                                            |                   | ADJ2 pin<br>(external voltage setting)              | 0    | —     | 4.4                        | V   |

|                                            |                   | ADJ3 pin                                            | 0    | —     | 0.2                        | V   |

|                                            |                   | (internal reference voltage setting)                | 4.6  |       | V <sub>VREF</sub>          | V   |

|                                            |                   | ADJ3 pin<br>(external voltage setting)              | 0.4  | _     | 4.4                        | V   |

|                                            |                   | CELLS pin                                           | 0    | —     | V <sub>VREF</sub>          | V   |

|                                            | V <sub>INC</sub>  | +INC1, +INC2, -INC1, BATT<br>pin                    | 0    | —     | V <sub>VCC</sub>           | V   |

| ACIN pin input voltage                     | V <sub>ACIN</sub> | —                                                   | 0    | —     | 5                          | V   |

| ACOK pin output voltage                    | V <sub>ACOK</sub> | -                                                   | 0    | —     | 25                         | V   |

| ACOK pin output current                    | I <sub>ACOK</sub> | -                                                   | 0    | —     | 1                          | mA  |

| CTL pin input voltage                      | V <sub>CTL</sub>  | —                                                   | 0    | —     | 25                         | V   |

| Output current                             | I <sub>OUT</sub>  | OUT pin                                             | -45  | —     | + 45                       | mA  |

|                                            |                   | OUT pin<br>Duty $\leq$ 5% (t = 1 / fosc × Duty)     | -600 | —     | + 600                      | mA  |

| Switching frequency                        | f <sub>OSC</sub>  | -                                                   | 100  | 500   | 2000                       | kHz |

| Timing resistor                            | R <sub>RT</sub>   | RT pin                                              | 8.2  | 33    | 180                        | kΩ  |

| VH pin capacitor                           | C <sub>VH</sub>   | _                                                   | _    | 0.1   | 1.0                        | μF  |

| Reference voltage output capacitor         | C <sub>VREF</sub> | VREF pin                                            | —    | 0.1   | 1.0                        | μF  |

| Operating ambient temperature              | Та                | _                                                   | -30  | + 25  | + 85                       | °C  |

**WARNING:** The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

# 6. Electrical Characteristics

| $(Ta = +25^{\circ})$ | VCC $nin =$  | 19 V, VREF | nin = 0 mA                |

|----------------------|--------------|------------|---------------------------|

| (10 - 120            | , voo piii – |            | $p_{\rm m} = 0  {\rm mz}$ |

| D                                        | Description                           |                    | Pin  |                                                                                                           | Value |       |       |      |

|------------------------------------------|---------------------------------------|--------------------|------|-----------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| Parameter                                |                                       | Symbol No.         |      | Condition                                                                                                 | Min   | Тур   | Мах   | Unit |

| Reference                                | Threshold                             | V <sub>VREF1</sub> | 6    | _                                                                                                         | 4.963 | 5.000 | 5.037 | V    |

| Voltage Block<br>[REF]                   | voltage                               | V <sub>VREF2</sub> | 6    | $Ta = -10^{\circ} to +85^{\circ}$                                                                         | 4.950 | 5.000 | 5.050 | V    |

|                                          | Input stability                       | VREF<br>Line       | 6    | VCC pin = 8 V to 25 V                                                                                     | -     | 3     | 10    | mV   |

|                                          | Load stability                        | VREF<br>Load       | 6    | VREF pin = 0 mA to $-1$ mA                                                                                | -     | 1     | 10    | mV   |

|                                          | Short-circuit<br>output<br>current    | los                | 6    | VREF pin = 1 V                                                                                            | -25   | -12   | -6    | mA   |

| Triangular Wave<br>Oscillator Block      | Switching<br>frequency                | f <sub>osc</sub>   | 20   | RT pin = 33 k $\Omega$                                                                                    | 450   | 500   | 550   | kHz  |

| [OSC]                                    | Frequency<br>temperature<br>variation | df/fd⊤             | 20   | $Ta = -30^{\circ} \text{ to } +85^{\circ}$                                                                | _     | 1*    | -     | %    |

| Error Amplifier<br>Block                 | Input offset voltage                  | V <sub>IO</sub>    | 2, 3 | COMP1 pin = 2 V                                                                                           | -     | 1     | 5     | mV   |

| [Error Amp1]                             | Input bias<br>voltage                 | I <sub>ADJ1</sub>  | 3    | ADJ1 pin = 0 V                                                                                            | -100  | -     | -     | nA   |

|                                          | Transconduc-<br>tance                 | Gm                 | 15   | _                                                                                                         | -     | 20*   | -     | μA/V |

| Error Amplifier<br>Block                 | Threshold voltage                     | V <sub>TH1</sub>   | 10   | ADJ2 pin = VREF pin                                                                                       | -     | 1.5*  | -     | V    |

| [Error Amp2]                             | Transconduc-<br>tance                 | Gm                 | 15   | -                                                                                                         | -     | 20*   | -     | μA/V |

| Error Amplifier<br>Block<br>[Error Amp3] | Threshold<br>voltage<br>accuracy      | V <sub>TH1</sub>   | 12   | COMP3 pin = 2 V,<br>Ta = $+25^{\circ}$<br>ADJ3 pin = VREF pin<br>(4.20 V/Cell setting)                    | -0.5  | 0     | + 0.5 | %    |

|                                          |                                       | V <sub>TH2</sub>   | 12   | COMP3 pin = 2 V,<br>Ta = $-10^{\circ}$ to $+85^{\circ}$ ,<br>ADJ3 pin = VREF pin<br>(4.20 V/Cell setting) | -0.7  | 0     | + 0.7 | %    |

|                                          |                                       | V <sub>TH3</sub>   | 12   | COMP3 pin = 2 V,<br>Ta = $+25^{\circ}$<br>ADJ3 pin = GND,<br>(4.10 V/Cell setting)                        | -0.6  | 0     | + 0.6 | %    |

|                                          |                                       | V <sub>TH4</sub>   | 12   | COMP3 pin = 2 V,<br>Ta = $-10^{\circ}$ to +85°<br>ADJ3 pin = GND,<br>(4.10 V/Cell setting)                | -0.8  | 0     | + 0.8 | %    |

| Bara                                               | Parameter                             |                     | Pin    |                                                                   |      | Value |      | Unit |

|----------------------------------------------------|---------------------------------------|---------------------|--------|-------------------------------------------------------------------|------|-------|------|------|

|                                                    |                                       | Symbol No.          |        | Condition                                                         | Min  | Тур   | Мах  | Unit |

| Error Amplifier<br>Block<br>[Error Amp3]           | Input current                         | I <sub>BATTH1</sub> | 12     | ADJ3 pin = CELLS pin =<br>VREF pin<br>BATT pin = 16.8 V           | -    | 25.2  | 38   | μA   |

|                                                    |                                       | I <sub>BATTL</sub>  | 12     | VCC pin = 0 V, BATT pin =<br>16.8 V                               | -    | 0     | 1    | μA   |

|                                                    | Transconduc-<br>tance                 | Gm                  | 15     | _                                                                 | _    | 30*   | _    | μA/V |

| Current<br>Detection                               | Input current                         | I <sub>+INCH</sub>  | 13, 24 | +INC1 pin = +INC2 pin = 3 V to<br>VCC pin, $\Delta$ Vin = -100 mV | _    | 20    | 30   | μA   |

| Amplifier Block<br>[Current Amp1,<br>Current Amp2] |                                       | I_ <sub>INCH</sub>  | 1      | +INC1 pin = 3 V to VCC pin,<br>$\Delta$ Vin = -100 mV             | _    | 0.1   | 0.2  | μA   |

|                                                    |                                       | I <sub>+INCL</sub>  | 13, 24 | +INC1 pin = +INC2 pin = 0.1 V,<br>$\Delta$ Vin = -100 mV          | -225 | -150  | _    | μA   |

|                                                    |                                       | I_ <sub>INCL</sub>  | 1      | +INC1 pin = +INC2 pin = 0.1 V,<br>$\Delta Vin = -100 \text{ mV}$  | -255 | -170  | _    | μA   |

|                                                    | Input offset<br>voltage               | V <sub>OFF1</sub>   | 2      | +INC1 pin = 3 V to VCC pin                                        | -1   | 0     | 1    | mV   |

|                                                    |                                       | V <sub>OFF2</sub>   | 10     | +INC2 pin = $3 \text{ V}$ to VCC pin                              | 2    | 3     | 4    | mV   |

|                                                    |                                       | V <sub>OFF3</sub>   | 10     | +INC2 pin = 0 V to 3 V                                            | 1    | 3     | 5    | mV   |

|                                                    | Common mode<br>input<br>voltage range | V <sub>CM</sub>     | 2, 10  | _                                                                 | 0    | _     | Vvcc | V    |

|                                                    | Voltage gain                          | A <sub>V</sub>      | 2, 10  | +INC1 pin = +INC2 pin = 3 V to<br>VCC pin, $\Delta$ Vin = -100 mV | 24.5 | 25.0  | 25.5 | V/V  |

|                                                    | Frequency band width                  | BW                  | 2, 10  | $A_V = 0 dB$                                                      | _    | 2*    | _    | MHz  |

|                                                    | Output voltage                        | V <sub>OUTCH1</sub> | 2      | -                                                                 | 4.7  | 4.9   | _    | V    |

|                                                    |                                       | V <sub>OUTCH2</sub> | 10     | -                                                                 | 4.5  | 4.7   | _    | V    |

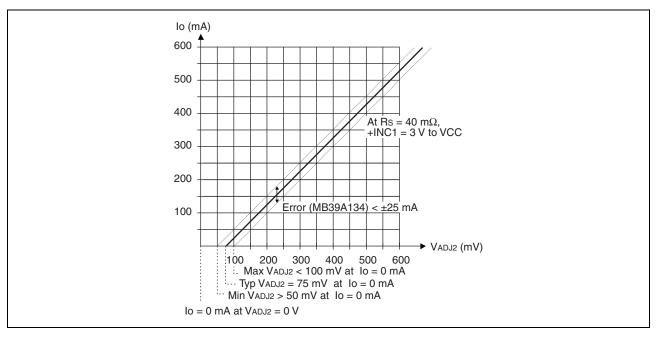

|                                                    |                                       | V <sub>OUTCL</sub>  | 2, 10  | _                                                                 | 50   | 75    | 100  | mV   |

|                                                    | Output source<br>current              | I <sub>SOURCE</sub> | 2, 10  | OUTC1 pin = OUTC2 pin = 2 V                                       | _    | -2    | -1   | mA   |

|                                                    | Output sink current                   | I <sub>SINK</sub>   | 2, 10  | OUTC1 pin = OUTC2 pin = 2 V                                       | 150  | 300   | _    | μA   |

| PWM Comp.                                          | Threshold                             | V <sub>TL</sub>     | 20     | Duty cycle = 0%                                                   | 1.4  | 1.5   | -    | V    |

| Block<br>[PWM Comp.]                               | voltage                               | $V_{TH}$            | 20     | Duty cycle = 100%                                                 | —    | 2.5   | 2.6  | V    |

## $(Ta = +25^\circ, VCC pin = 19 V, VREF pin = 0 mA)$

|                               |                                         | Symbol Pin          |     |                                                                 | 20,000                    | Value                     | - ,                       |      |

|-------------------------------|-----------------------------------------|---------------------|-----|-----------------------------------------------------------------|---------------------------|---------------------------|---------------------------|------|

| Parameter                     |                                         | Symbol              | No. | Condition                                                       | Min.                      | Тур.                      | Max.                      | Unit |

| Output Block<br>[OUT]         | Output source current                   | I <sub>SOURCE</sub> | 20  | OUT pin = 13 V,<br>Duty $\leq$ 5%<br>(t = 1/fosc $\infty$ Duty) | -                         | -400*                     | _                         | mA   |

|                               | Output sink current                     | I <sub>SINK</sub>   | 20  | OUT pin = 19V,<br>Duty $\leq$ 5%<br>(t = 1/fosc $\infty$ Duty)  | -                         | 400*                      | —                         | mA   |

|                               | Output ON                               | R <sub>OH</sub>     | 20  | OUT pin = $-45 \text{ mA}$                                      | —                         | 6.5                       | 9.8                       | Ω    |

|                               | resistance                              | R <sub>OL</sub>     | 20  | OUT pin = 45 mA                                                 | —                         | 5.0                       | 7.5                       | Ω    |

|                               | Rise time                               | tr1                 | 20  | OUT pin = 3300 pF                                               | —                         | 50*                       | —                         | ns   |

|                               | Fall time                               | tf1                 | 20  | OUT pin = 3300 pF                                               | —                         | 50*                       | —                         | ns   |

| Control Block                 | CTL input                               | V <sub>ON</sub>     | 14  | IC operation mode                                               | 2                         | (                         | 25                        | V    |

| [CTL]                         | voltage                                 | $V_{OFF}$           | 14  | IC standby mode                                                 | 0                         | (                         | 0.8                       | V    |

|                               | Input current                           | I <sub>CTLH</sub>   | 14  | CTL pin = 5 V                                                   | —                         | 100                       | 150                       | μA   |

|                               |                                         | I <sub>CTLL</sub>   | 14  | CTL pin = 0 V                                                   | —                         | 0                         | 1                         | μA   |

| Bias Voltage<br>Block<br>[VH] | Output<br>voltage                       | V <sub>H</sub>      | 19  | VCC pin = 8 V to 25 V,<br>VH pin = 0 to 30 mA                   | V <sub>VCC</sub> -<br>6.5 | V <sub>VCC</sub> -<br>6.0 | V <sub>VCC</sub> -<br>5.5 | V    |

| Under Voltage                 | Threshold voltage                       | V <sub>TLH</sub>    | 21  | VCC pin = _⊼                                                    | 6.0                       | 6.2                       | 6.4                       | V    |

| Lockout<br>Protection         |                                         | V <sub>THL</sub>    | 21  | VCC pin = ႃ                                                     | 5.0                       | 5.2                       | 5.4                       | V    |

| Circuit Block                 | Hysteresis width                        | V <sub>H</sub>      | 21  | VCC pin                                                         | -                         | 1.0*                      | —                         | V    |

| [UVLO]                        | Threshold voltage                       | V <sub>TLH</sub>    | 6   | VREF pin = _√                                                   | 2.6                       | 2.8                       | 3.0                       | V    |

|                               |                                         | V <sub>THL</sub>    | 6   | VREF pin = ¬Ł                                                   | 2.4                       | 2.6                       | 2.8                       | V    |

|                               | Hysteresis width                        | V <sub>H</sub>      | 6   | VREF pin                                                        | -                         | 0.2                       | —                         | V    |

| Over<br>Temperature           | Detection<br>temperature                | T <sub>TH</sub>     | 20  | _                                                               | _                         | + 150                     | -                         | °C   |

| Detection                     | Release<br>temperature                  | T <sub>TL</sub>     | 20  | _                                                               | —                         | + 125                     | _                         | °C   |

| AC Adapter                    | Threshold                               | V <sub>TLH</sub>    | 7   | -                                                               | 1.245                     | 1.270                     | 1.295                     | V    |

| Voltage<br>Detection Block    | voltage                                 | $V_{THL}$           | 7   | -                                                               | 1.215                     | 1.250                     | 1.285                     | V    |

| [AC Comp.]                    | Hysteresis width                        | V <sub>H</sub>      | 7   | _                                                               | —                         | 20                        | —                         | mV   |

|                               | ACOK<br>pin<br>output leak<br>current   | I <sub>LEAK</sub>   | 5   | ACOK pin = 25 V                                                 | _                         | 0                         | 1                         | μA   |

|                               | ACOK pin<br>output "L"<br>level voltage | V <sub>ACOKL</sub>  | 5   | ACOK pin = 1 mA                                                 | -                         | 0.9                       | 1.1                       | V    |

|                               | Current consumption                     | I <sub>VINL</sub>   | 18  | VIN pin = 19 V,<br>ACIN pin = 0 V                               | _                         | 0                         | 1                         | μA   |

|                               |                                         | I <sub>VINH</sub>   | 18  | VIN pin = 19 V,<br>ACIN pin = 5 V                               | —                         | 6                         | 10                        | μA   |

$(Ta = +25^\circ, VCC pin = 19 V, VREF pin = 0 mA)$

| Parameter                        |                      | Symbol            | Pin No. | Condition                                                             |                         | Value |                   |      |  |

|----------------------------------|----------------------|-------------------|---------|-----------------------------------------------------------------------|-------------------------|-------|-------------------|------|--|

|                                  |                      | Symbol Pin No     |         | Condition                                                             | Min.                    | Тур.  | Max.              | Unit |  |

| Charge Voltage                   | Input voltage        | V <sub>H</sub>    | 16      | At 4.20 V/Cell                                                        | 4.6                     | —     | V <sub>VREF</sub> | V    |  |

| Control Block                    |                      | V <sub>EXT</sub>  | 16      | At external setting                                                   | 0.4                     | _     | 4.4               | V    |  |

| Control]                         |                      | VL                | 16      | At 4.10 V/Cell                                                        | 0                       | _     | 0.2               | V    |  |

|                                  | Threshold            | V <sub>TL</sub>   | 16      | _                                                                     | 0.21                    | 0.3   | 0.39              | V    |  |

|                                  | voltage              | V <sub>TH</sub>   | 16      | _                                                                     | 4.41                    | 4.5   | 4.59              | V    |  |

|                                  | Input current        | I <sub>IN</sub>   | 16      | ADJ3 pin                                                              | -                       | 0     | 1                 | μA   |  |

|                                  | Input voltage        | V <sub>H</sub>    | 11      | At 4 Cells                                                            | V <sub>VREF</sub> - 0.4 | _     | V <sub>VREF</sub> | V    |  |

|                                  |                      | V <sub>M</sub>    | 11      | At 2 Cells                                                            | 2.4                     | —     | 2.6               | V    |  |

|                                  |                      | VL                | 11      | At 3 Cells                                                            | 0                       | _     | 0.3               | V    |  |

|                                  | Input current        | I <sub>INL</sub>  | 11      | CELLS = 0 V                                                           | -8.3                    | -5    | -                 | μA   |  |

|                                  |                      | I <sub>INH</sub>  | 11      | $CELLS = I_{VREF}$                                                    | -                       | 5     | 8.3               | μA   |  |

| Charge Current                   | Input voltage        | V <sub>H</sub>    | 9       | At normal charge                                                      | 4.6                     | _     | V <sub>VREF</sub> | V    |  |

| Control Block<br>[Charge Current |                      | V <sub>EXT</sub>  | 9       | At external setting                                                   | 0                       | _     | 4.4               | V    |  |

| Control]                         | Threshold voltage    | V <sub>TH</sub>   | 9       | _                                                                     | 4.41                    | 4.50  | 4.59              | V    |  |

|                                  | Input current        | I <sub>IN</sub>   | 9       | ADJ2 pin                                                              | -                       | 0     | 1                 | μA   |  |

| General                          | Standby<br>current   | I <sub>CCS1</sub> | 18      | VCC pin = 0 V,<br>CTL pin = 0 V,<br>ACIN pin = 5 V,<br>VIN pin = 19 V | _                       | 6     | 10                | μA   |  |

|                                  |                      | I <sub>CCS2</sub> | 21      | VIN pin = 0 V,<br>CTL pin = 0 V,<br>VCC pin = 19 V                    | -                       | 0     | 1                 | μA   |  |

|                                  | Power supply current | I <sub>CC</sub>   | 21      | CTL pin = 5 V                                                         | _                       | 2.7   | 4.0               | mA   |  |

(Ta =  $+25^{\circ}$ , VCC pin = 19 V, VREF pin = 0 mA)

\*: This parameter isn't be specified. This should be used as a reference to support designing the circuits.

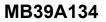

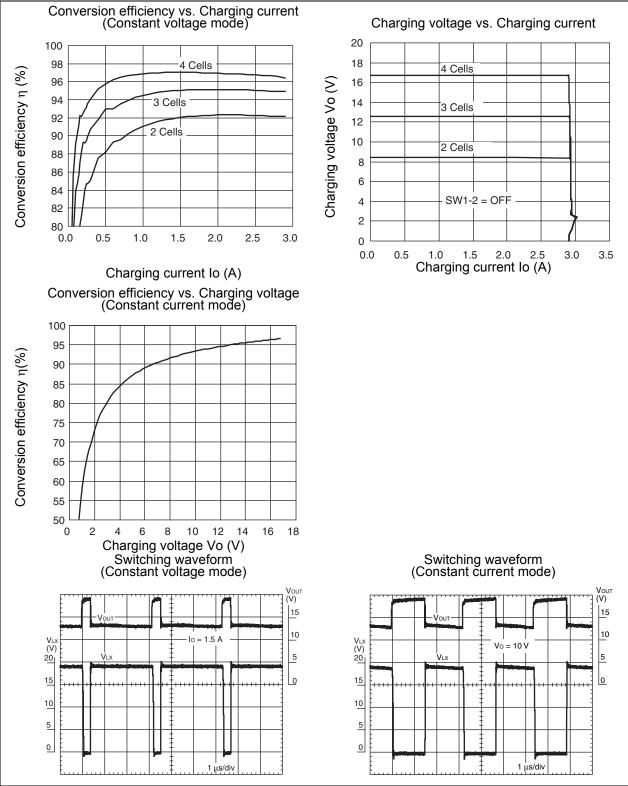

## 7. Typical Characteristics

Document Number: 002-08413 Rev. \*C

Document Number: 002-08413 Rev. \*C

## 8. Functional Description

MB39A134 is a DC/DC converter which uses pulse width modulation (PWM) for charging Li-ion battery and controls the charge voltage and current when charging the battery. It includes the charge control function for the battery and the AC adapter voltage detection function to stably supply the voltage from the AC adapter and the battery to the system.

- When controlling the charge voltage (constant voltage mode), the voltage entered in ADJ3 pin and CELLS pin can be used to set an arbitrary voltage. The error amplifier (Error Amp3) compares BATT pin voltage with the internal reference voltage to generate the PWM control signal for generating an arbitrary charge voltage.

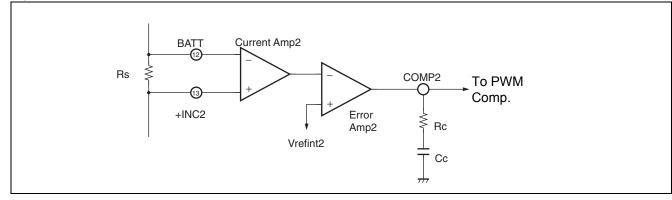

- When controlling the charge current (constant current mode), the current detection amplifier (Current Amp2) amplifies the voltage drop generated between both ends of the charge current sense resistance (R<sub>S</sub>) to 25 times and outputs it through OUTC2 pin. The error amplifier (Error Amp2) compares the output voltage from the current detection amplifier (Current Amp2) with the voltage set at ADJ2 pin to generate the PWM control signal for executing the constant current charge.

- When controlling the AC adapter power, the current detection amplifier (Current Amp1) amplifies the difference between -INC1 pin voltage and +INC1 pin voltage (V<sub>VREF</sub>) to 25 times and outputs it through OUTC1 pin when the output voltage of the AC adapter drops. The error amplifier (Error Amp1) compares the output voltage from the current detection amplifier (Current Amp1) with ADJ1 pin voltage to generate the PWM control signal for controlling the charge current so that AC adapter power can be kept constant.

The triangular wave voltage generated from the triangular wave oscillator is compared with the lowest potential of the output voltages from the error amplifier (Error Amp1, Error Amp2, and Error Amp3) and when the former is lower than the latter, the high side switching FET is set on.

In addition, AC Comp detects installation/removal of the AC adapter and its information is generated through ACOK pin.

## 8.1 DC/DC Converter Block

## 8.1.1 Reference Voltage Block (REF)

The reference voltage circuit (REF) uses the voltage supplied from the VCC pin (pin 21) to generate stable voltage (Typ 5.0 V) that has undergone temperature compensation. The generated voltage is used as the reference power supply for the internal circuitry of the IC.

This block can output load current of up to 1 mA from the reference voltage VREF pin (pin 6).

## 8.1.2 Triangular Wave Oscillator Block (OSC)

The triangular wave oscillator builds the capacitor for frequency setting into, and generates the triangular wave oscillation waveform by connecting the frequency setting resistor with the RT pin (pin 17). The triangular wave is input to the PWM comparator on the IC.

Triangular wave oscillation frequency: fosc

fosc (kHz) ≈ 17000 / RT (kΩ)

## 8.1.3 Error Amplifier Block (Error Amp1)

This amplifier detects the output signal from the current detection amplifier (Current Amp1) and outputs a PWM control signal. In addition, a stable phase compensation can be made available to the system by connecting the resistor and the capacitor to the COMP1 pin.

## 8.1.4 Error Amplifier Block (Error Amp2)

This amplifier detects the output signal from the current detection amplifier (Current Amp2), compares this to the output signal from the charge current control circuit, and outputs a PWM control signal to be used in controlling the charge current. In addition, a stable phase compensation can be made available to the system by connecting the resistor and the capacitor to the COMP2 pin.

## 8.1.5 Error Amplifier Block (Error Amp3)

This error amplifier (Error Amp3) detects the output voltage from the DC/DC converter, compares this to the output signal from the VO REFIN controller circuit, and outputs the PWM control signal.

Arbitrary output voltage from 2 Cell to 4 Cell can be set by connecting an external resistor of charging voltage to ADJ3 pin (pin 16). In addition, a stable phase compensation can be made available to the system by connecting the resistor and the capacitor to the COMP3 pin.

## 8.1.6 Current Detection Amplifier Block (Current Amp1)

The current detection amplifier (Current Amp1) amplifies the voltage difference between +INC1 pin (pin 24) and -INC1 pin (pin 1) 25 times and the signal is output to the following error amplifier (Error Amp1).

## 8.1.7 Current Detection Amplifier Block (Current Amp2)

The current detection amplifier (Current Amp2) detects a voltage drop on the both ends of the output sense resistor ( $R_S$ ) due to the flow of the charge current, using the +INC2 pin (pin 13) and BATT pin (pin 12). The signal amplified to 25 times is output to the following error amplifier (Error Amp2).

## 8.1.8 PWM Comparator Block (PWM Comp.)

The PWM comparator circuit (PWM Comp.) is a voltage-pulse width converter for controlling the output duty of the error amplifiers (Error Amp1 to Error Amp3) depending on their output voltage.

The PWM comparator circuit compares the triangular wave voltage generated by the triangular wave oscillator with the error amplifier output voltage and turns on the external output transistor (MOS FET), during the interval in which the triangular wave voltage is lower than the error amplifier output voltage.

## 8.1.9 Output Block (OUT)

The output circuit uses a totem-pole configuration capable of driving an external P-ch MOS FET.

The output "L" level sets the output amplitude to 6 V (Typ) using the voltage generated by the bias voltage block (VH).

This results in increasing conversion efficiency and suppressing the withstand voltage of the connected external transistor (MOSFET) even in a wide range of input voltages.

## 8.1.10 Power Supply Control Block (CTL)

Setting the CTL pin (pin 14) to "L" level places the IC in the standby mode. During the standby mode, only AC adapter detection function is operated. (The supply current is 6 µA at typical in the standby mode.)

| Table 1. CTL Function Table |               |                      |  |  |  |  |  |  |  |

|-----------------------------|---------------|----------------------|--|--|--|--|--|--|--|

| CTL                         | Power         | AC Adapter Detection |  |  |  |  |  |  |  |

| L                           | OFF (Standby) | ON (Active)          |  |  |  |  |  |  |  |

| Н                           | ON (Active)   | ON (Active)          |  |  |  |  |  |  |  |

### Table 1. CTL Function Table

### 8.1.11 Bias Voltage Block (VH)

The bias voltage circuit outputs  $V_{VCC} - 6 V$  (Typ) as the minimum potential of the output circuit. In the standby mode, this circuit outputs the potential equal to  $V_{VCC}$ .

## 8.2 **Protection Functions**

### 8.2.1 Under Voltage Lockout Protection Circuit Block (UVLO)

The transient state or a momentary decrease in supply voltage or internal reference voltage (VREF pin), which occurs when the power supply (VCC pin) is turned on, may cause malfunctions in the control IC, resulting in breakdown or deterioration of the system.

To prevent such malfunction, the under voltage lockout protection circuit detects internal reference voltage drop and fixes the OUT pin (pin 20) to the "H" level. The system restores when the power supply and the internal reference reaches less than the threshold voltage of the lockout protection circuit at the low voltage level.

### Protection circuit (UVLO) operation function table

When UVLO is operating (VCC or VREF voltage is lower than UVLO threshold voltage.), the logic of the following pin is fixed at the value shown.

| pin    | OUT |

|--------|-----|

| Status | Н   |

### 8.2.2 Over Temperature Detection

The circuit protects an IC from heat-destruction. If the temperature at the joint part reaches +150°C, the circuit changes the level of OUT pin to "H", and stops the voltage output.

In addition, if the temperature at the joint part drops to +125°C, the output restarts again.

Therefore, make sure to design the DC/DC power supply system so that the over heating protection does not start frequently.

### 8.2.3 Detection Functions

### AC adapter voltage detection block (AC Comp.)

The AC adapter voltage detection block (AC Comp.) detects that ACIN pin voltage is below 1.25 V (Typ) and sets ACOK pin in the AC adapter voltage detection block to Hi-Z. In addition, a higher voltage from either VCC pin or VIN pin is supplied as the IC power supply.

AC adapter detection voltage setting

$V_{IN} = Low \text{ to High}$  $Vth = (R1 + R2) / R2 \times 1.27 \text{ V}$  $V_{IN} = \text{High to Low}$  $Vth = (R1 + R2) / R2 \times 1.25 \text{ V}$

## 8.2.4 Setting the Charge Voltage

The charge voltage (DC/DC output) is set by the input voltage to ADJ3 pin (pin 16) and CELLS pin (pin 11). The ADJ3 pin (pin 16) can set charge voltage per cell. An arbitrary charge voltage is set when external resistor is set. It does not need external resistor when ADJ3 pin (pin 16) is input to VREF level or GND level by internal high accurate reference voltage. The CELLS pin (pin 11) can set the series battery number when the pin is input VREF, OPEN or GND level.

The setting of ADJ3 pin (pin 16), CELLS pin (pin 11) and charge voltage (DC/DC output) is shown below.

| ADJ3 Input Voltage                                  | CELLS | Charge Voltage       | Note                               |

|-----------------------------------------------------|-------|----------------------|------------------------------------|

| VREF pin                                            | OPEN  | 8.4 V                | 2 Cell × 4.20 V/Cell               |

| (ADJ3 ≥4.6 V)                                       | GND   | 12.6 V               | 3 Cell × 4.20 V/Cell               |

|                                                     | VREF  | 16.8 V               | 4 Cell × 4.20 V/Cell               |

| GND pin<br>(ADJ3 $\leq$ 0.2 V)                      | OPEN  | 8.2 V                | 2 Cell × 4.10 V/Cell               |

|                                                     | GND   | 12.3 V               | 3 Cell × 4.10 V/Cell               |

|                                                     | VREF  | 16.4 V               | 4 Cell × 4.10 V/Cell               |

| External voltage setting<br>(ADJ3 = 0.4 V to 4.4 V) | OPEN  | 4 × ADJ3 pin voltage | 2 Cell × 2 × ADJ3 pin voltage/Cell |

|                                                     | GND   | 6 × ADJ3 pin voltage | 3 Cell × 2 × ADJ3 pin voltage/Cell |

|                                                     | VREF  | 8 × ADJ3 pin voltage | 4 Cell × 2 × ADJ3 pin voltage/Cell |

• ADJ3 Pin Internal Circuit

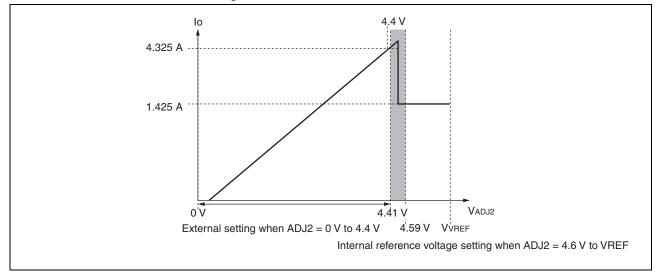

### 8.2.5 Setting the Charge Current

The Error amplifier block (Error Amp2) compares the output voltage of charge current control block set by ADJ2 pin (pin 9) with the output signal from the current detection amplifier (current Amp2), and outputs a PWM control signal to be used in controlling the maximum charge current for battery. When the current overflows the rated value, the current will be constantly charged to the rated value, and the charge voltage will drop.

Battery charge current setting voltage : ADJ2

Upper limit of charge current lo =

Charge current control block output voltage (V) -0.075

Current detection amplifier block voltage gain (25.0 V/V Typ) × sense resistor  ${\sf R}_S\left(\Omega\right)$

|                                                   | Charge Current                  |                                 | Charge Current                        |                                          |  |  |

|---------------------------------------------------|---------------------------------|---------------------------------|---------------------------------------|------------------------------------------|--|--|

| ADJ2 Input Voltage                                | Control Block<br>Output Voltage | $R_S = 40 \ m\Omega$            | $R_S = 20 \ m\Omega$                  | $R_S^{} = 15 \text{ m}\Omega$            |  |  |

| VREF<br>(ADJ2 > 4.6 V)                            | 1.5 V                           | 1.425 A                         | 2.85 A                                | 3.79 A                                   |  |  |

| External Voltage Setting<br>(ADJ2 = GND to 4.4 V) | V <sub>ADJ2</sub><br>(V)        | V <sub>ADJ2</sub> -0.075<br>(A) | 2 × (V <sub>ADJ2</sub> -0.075)<br>(A) | 2.66 × (V <sub>ADJ2</sub> -0.075)<br>(A) |  |  |

### • ADJ2 Pin Internal Circuit

• Example of charge current setting ( $R_S = 40 \text{ m}\Omega$ )

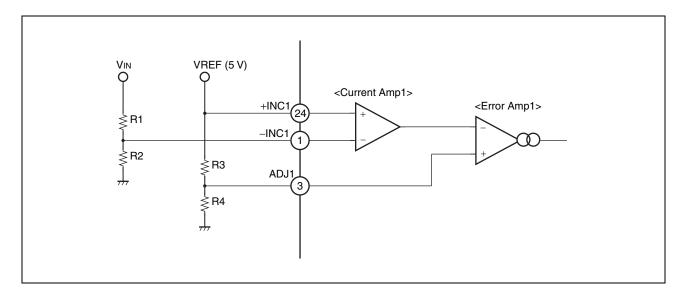

### 8.2.6 Setting Dynamically-Controlled-Charging

By connecting as shown in the example of the figure below, the AC adopter voltage (V<sub>IN</sub>) drops and becomes the calculated Vth, and then, the dynamically-controlled charging loop reduce the charge current to keep a settled power level.

AC adopter voltage in dynamically controlled charging mode:

$$Vth = VREF \times (1 - \frac{1}{A_V} \times \frac{R4}{R3 + R4}) \times \frac{R1 + R2}{R2}$$

VREF : Reference voltage (5.0 V Typ) A<sub>V</sub> : Current detection amplifier block voltage gain (25.0 V/V Typ)

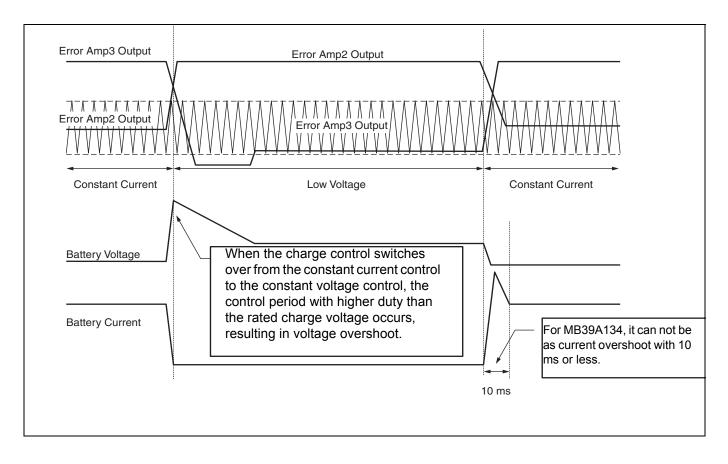

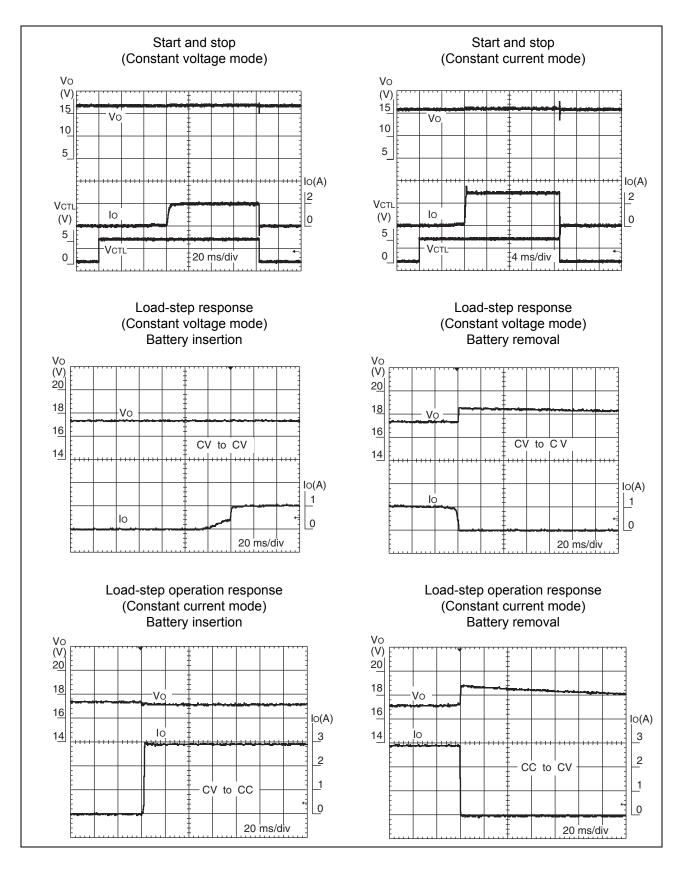

## 9. Transit Response When a Load Changes Suddenly

The constant voltage control loop and the constant current control loop are independent each other and when a load changes suddenly, these two control loops switch over each other.

Overshoot of the battery voltage and current is generated by the delay in the control loop when changing the mode.

The delay time is determined by the phase compensation components values.

When the constant current control switches over to the constant voltage control when removing the battery, the control period with higher duty than the rated charge voltage occurs, resulting in voltage overshoot. In such a period, since the battery is removed, no excessive voltage should be applied to the battery.

When the constant voltage control switches over to the constant current control when installing the battery, the control period with higher duty than the rated charge current occurs, resulting in current overshoot.

For MB39A134, it can not be as current overshoot with 10 ms or less.

## 10. Connection Without Using The Current Amp1, Current Amp2 and The Error Amp1, Error Amp2

When Current Amp1, 2 or Error Amp1, 2 are not used, please connect it as follows.

- +INC1 pin (pin 24), -INC1 pin (pin 1), ADJ1 pin (pin 3), and ADJ2 pin (pin 9) are connected with the VREF pin.

- +INC2 pin (pin 13) is connected with the pin BATT pin (pin 12).

- OUTC1 pin (pin 2) and OUTC2 pin (pin10) open.

# 11. Input/Output Pin Equivalent Circuit Diagram

Document Number: 002-08413 Rev. \*C

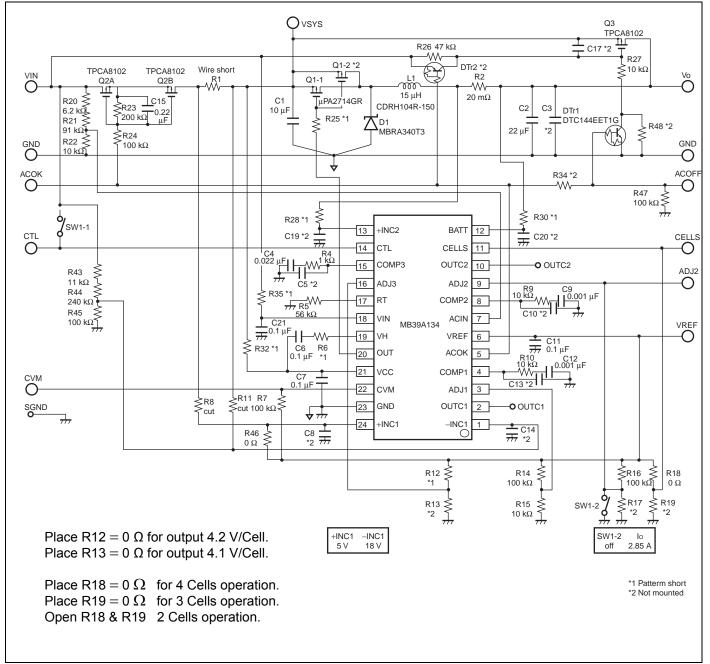

# **12. Typical Application Circuit**

### Parts List

| Com-<br>ponent | ltem              | Specification                    | Vendor  | Package        | Parts No.      | Remarks     |

|----------------|-------------------|----------------------------------|---------|----------------|----------------|-------------|

| M1             | IC                | MB39A134                         | Cypress | TSSOP-24       | -              |             |

| Q1-1           | P-ch FET          | VDS = -20 V,<br>ID = 7 A (Max)   | RENESAS | SOP-8          | μPA2714GR      |             |

| Q1-2           | P-ch FET          | —                                | _       | _              | —              | Not mounted |

| Q2A            | P-ch FET          | VDS = -30 V,<br>ID = 40 A (Max)  | TOSHIBA | SOP<br>Advance | TPCA8102       |             |

| Q2B            | P-ch FET          | VDS = -30 V,<br>ID = 40 A (Max)  | TOSHIBA | SOP<br>Advance | TPCA8102       |             |

| Q3             | P-ch FET          | VDS = -30 V,<br>ID = 40 A (Max)  | TOSHIBA | SOP<br>Advance | TPCA8102       |             |

| DTr1           | Transistor        | VCEO = 50 V                      | ON Semi | SC-75          | DTC144EET1G    |             |

| DTr2           | Transistor        | —                                | _       | _              | _              | Not mounted |

| D1             | Diode             | VF = 0.45 V (Max)<br>at IF = 3 A | ON Semi | RMDS           | MBRA340T3      |             |

| L1             | Inductor          | 15 μH 50 mW<br>Irms = 3.1 A      | SUMIDA  | SMD            | CDRH104R-150   |             |

| C1             | Ceramic Capacitor | 10 µF (25 V)                     | TDK     | 3225           | C3225X5R1E106K |             |

| C2             | Ceramic Capacitor | 22 µF (25 V)                     | TDK     | 3225           | C3225JC1E226M  |             |

| C3             | Ceramic Capacitor | -                                | -       | -              | -              | Not mounted |

| C4             | Ceramic Capacitor | 0.022 µF (50 V)                  | TDK     | 1608           | C1608JB1H223K  |             |

| C5             | Ceramic Capacitor | _                                | _       | _              | -              | Not mounted |

| C6             | Ceramic Capacitor | 0.1 µF (50 V)                    | TDK     | 1608           | C1608JB1H104K  |             |

| C7             | Ceramic Capacitor | 0.1 µF (50 V)                    | TDK     | 1608           | C1608JB1H104K  |             |

| C8             | Ceramic Capacitor | _                                | _       | _              | -              | Not mounted |

| C9             | Ceramic Capacitor | 0.001 µF (50 V)                  | TDK     | 1608           | C1608JB1H102J  |             |

| C10            | Ceramic Capacitor | _                                | _       | _              | -              | Not mounted |

| C11            | Ceramic Capacitor | 0.1 µF (50 V)                    | TDK     | 1608           | C1608JB1H104K  |             |

| C12            | Ceramic Capacitor | 0.001 µF (50 V)                  | TDK     | 1608           | C1608JB1H102J  |             |

| C13            | Ceramic Capacitor | _                                | _       | _              | -              | Not mounted |

| C14            | Ceramic Capacitor | _                                | 1       | _              | _              | Not mounted |

| C15            | Ceramic Capacitor | 0.22 µF (25 V)                   | TDK     | 1608           | C1608JB1H224K  |             |

| C17            | _                 | -                                | _       | _              | -              | Not mounted |

| C19            | Ceramic Capacitor | —                                | -       | _              | -              | Not mounted |

| C20            | Ceramic Capacitor | -                                | _       | _              | -              | Not mounted |

| C21            | Ceramic Capacitor | 0.1 µF (50 V)                    | TDK     | 1608           | C1608JB1H104K  |             |

| Com-<br>ponent | ltem     | Specification | Vendor    | Package | Parts No.   | Remarks       |

|----------------|----------|---------------|-----------|---------|-------------|---------------|

| R1             | Resistor | 0 Ω           | Mac-Eight | SMD     | MJP-0.2     | Wire short    |

| R2             | Resistor | 20 mΩ         | KOA       | SL1     | SL1TTE20L0D |               |

| R4             | Resistor | 1 kΩ          | SSM       | 1608    | RR0816P102D |               |

| R5             | Resistor | 56 kΩ         | SSM       | 1608    | RR0816P563D |               |

| R6             | Resistor | _             | _         | -       | _           | Pattern short |

| R7             | Resistor | 100 kΩ        | SSM       | 1608    | RR0816P104D |               |

| R8             | Resistor | (             | -         | -       | _           | Pattern cut   |

| R9             | Resistor | 10 kΩ         | SSM       | 1608    | RR0816P103D |               |

| R10            | Resistor | 10 kΩ         | SSM       | 1608    | RR0816P103D |               |

| R11            | Resistor | -             | _         | _       | _           | Pattern cut   |

| R12            | Resistor | _             | _         | -       | _           | Pattern short |

| R13            | Resistor | -             | _         | _       | _           | Not mounted   |

| R14            | Resistor | 100 kΩ        | SSM       | 1608    | RR0816P104D |               |

| R15            | Resistor | 10 kΩ         | SSM       | 1608    | RR0816P103D |               |

| R16            | Resistor | 100 kΩ        | SSM       | 1608    | RR0816P104D |               |

| R17            | Resistor | -             | _         | _       | _           | Not mounted   |

| R18            | Resistor | 0 Ω           | KOA       | 1608    | RK73Z1J     |               |

| R19            | Resistor | _             | -         | _       | _           | Not mounted   |

| R20            | Resistor | 6.2 kΩ        | SSM       | 1608    | RR0816P622D |               |

| R21            | Resistor | 91 kΩ         | SSM       | 1608    | RR0816P913D |               |

| R22            | Resistor | 10 kΩ         | SSM       | 1608    | RR0816P103D |               |

| R23            | Resistor | 200 kΩ        | SSM       | 1608    | RR0816P204D |               |

| R24            | Resistor | 100 kΩ        | SSM       | 1608    | RR0816P104D |               |

| R25            | Resistor | _             | -         | _       | _           | Pattern short |

| R26            | Resistor | 47 kΩ         | SSM       | 1608    | RR0816P473D |               |

| R27            | Resistor | 10 kΩ         | SSM       | 1608    | RR0816P103D |               |

| R28            | Resistor | -             | _         | _       | _           | Pattern short |

| R30            | Resistor | -             | _         | _       | _           | Pattern short |

| R32            | Resistor | -             | _         | _       | _           | Pattern short |

| R34            | _        | -             | _         | _       | -           | Not mounted   |

| R35            | Resistor | -             | _         | _       | -           | Pattern short |

| R43            | Resistor | 11 kΩ         | SSM       | 1608    | RR0816P113D |               |

| R44            | Resistor | 240 kΩ        | SSM       | 1608    | RR0816P244D |               |

| R45            | Resistor | 100 kΩ        | SSM       | 1608    | RR0816P104D |               |

| R46            | Resistor | 0 Ω           | KOA       | 1608    | RK73Z1J     |               |

| Compo-<br>nent | ltem       | Specification | Vendor    | Package | Parts No.   | Remarks     |

|----------------|------------|---------------|-----------|---------|-------------|-------------|

| R47            | Resistor   | 100 kΩ        | SSM       | 1608    | RR0816P104D |             |

| R48            | _          | _             | _         | -       | _           | Not mounted |

| SW1            | DIP SW     | SW            | MATSUKYU  | SMD     | DMS-2H      |             |

| PIN            | Wiring Pin | WT-2-1        | Mac-Eight | _       | WT-2-1      | 11-pin      |

Note : These components are recommended based on the operating tests authorized.

| RENESAS   | : Renesas Electronics Corporation |

|-----------|-----------------------------------|

| TOSHIBA   | : TOSHIBA Corporation             |

| ON Semi   | : ON Semiconductor                |

| SUMIDA    | : SUMIDA Corporation              |

| TDK       | : TDK Corporation                 |

| Mac-Eight | : Mac-Eight Co.,Ltd               |

| KOA       | : KOA Corporation                 |

| SSM       | : SUSUMU Co.,Ltd                  |

| MATSUKYU  | : Matsukyu Co.,Ltd                |

|           |                                   |

## **13. Application Note**

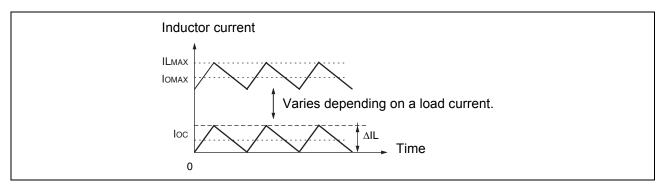

### Inductor selection

ī

The inductance value should be selected, as a reference, so that the peak-to-peal value of the inductor ripple current is 50% or less of the maximum charge current. In such a case, the inductance value can be obtained as follows :

$$L \ge \frac{V_{IN} - V_{O}}{LOR \times I_{OMAX}} \times \frac{V_{O}}{V_{IN} \times f_{OSC}}$$

| L                 |                                                                                   |

|-------------------|-----------------------------------------------------------------------------------|

| I <sub>OMAX</sub> | : Max. charge current [A]                                                         |

| LOR               | : Peak-to-peak value of inductor ripple current - max. charge current ratio (0.5) |

| V <sub>IN</sub>   | : Switching system power supply voltage [V]                                       |

| Vo                | : Charge voltage [V]                                                              |

| fosc              | : Switching frequency [Hz]                                                        |

The minimum charge current value (critical current value) without backward inductor current can be obtained as follow :

$$I_{OC} = \frac{V_O}{2 \times L} \times \frac{V_{IN} - V_O}{V_{IN} \times f_{OSC}}$$

| l <sub>oc</sub> | : Critical current [A] |

|-----------------|------------------------|

| L               | : Inductance value [H] |

- V<sub>IN</sub> : Switching system power supply voltage [V]

- V<sub>O</sub> : Charge voltage [V]

- fosc : Switching frequency [Hz]

To judge that the current passing through the inductor is below a rated value, it is necessary to obtain a maximum current value passing through the inductor. The maximum inductor current value can be obtained as follows :

$$|L_{MAX} \ge |_{OMAX} + \frac{\Delta |L|}{2}$$

| IL <sub>MAX</sub> | : Max. inductor current [A] |

|-------------------|-----------------------------|

| I <sub>OMAX</sub> | : Max. charge current [A]   |

△IL : Peak-to-peak value of inductor ripple current [A]

$$\Delta IL \geq \frac{V_{IN} - V_{O}}{L} \times \frac{V_{O}}{V_{IN} \times f_{OSC}}$$

### Switching FET Selection

If MB39A134 is used for the charger for a notebook PC, since the output voltage of an AC adapter, which is the input voltage of an switching FET, is 25 V or less, in general, a 30 V class MOS FET can be used as the switching FET. Obtain the maximum value of the current flowing through the switching FET in order to determine whether the current flowing through the switching FET is within the rated value. The maximum current flowing through the switching FET can be found by the following formula.

$$I_{\text{DMAX}} \ge I_{\text{OMAX}} + \frac{\Delta IL}{2}$$

I<sub>DMAX</sub>

: Max. switching FET drain current [A]

I<sub>OMAX</sub>

: Max. charge current [A]

∆IL

: Peak-to-peak value of inductor ripple current [A]

In addition, to judge that permissible switching FET loss is below the rated value, it is necessary to obtain the switching FET loss. To reduce switching FET loss as much as possible. when selecting a switching FET, take into consideration that the continuity loss is equal to the switching loss.

The switching FET continuity loss can be obtained by the following formula:

$$P_{Ron} = \frac{V_0}{V_{IN}} \times I_0^2 \times Ron$$

$\begin{array}{ll} \mathsf{P}_{\mathsf{Ron}} & : \mbox{ Switching FET continuity loss [W]} \\ \mathsf{I}_{\mathsf{O}} & : \mbox{ Charge current [A]} \\ \mathsf{V}_{\mathsf{IN}} & : \mbox{ Switching system power supply voltage [V]} \\ \mathsf{V}_{\mathsf{O}} & : \mbox{ Charge voltage [V]} \\ \mathsf{Ron} & : \mbox{ Switching FET on resistance } [\Omega] \end{array}$

The switching FET switching loss can be obtained simply as follows :

$$\mathsf{P}_{\mathsf{SW}} = \frac{1}{2} \times \mathsf{V}_{\mathsf{IN}} \times \mathsf{IL}_{\mathsf{MIN}} \times \mathsf{fosc} \times \mathsf{Tr} + \frac{1}{2} \times \mathsf{V}_{\mathsf{IN}} \times \mathsf{IL}_{\mathsf{MAX}} \times \mathsf{fosc} \times \mathsf{Tf}$$

$\begin{array}{ll} \mathsf{P}_{SW} & : \text{Switching FET switching loss [W]} \\ \mathsf{IL}_{\mathsf{MIN}} = \mathsf{I}_{\mathsf{OMAX}} - \Delta \mathsf{IL} \ / \ 2 : \text{Lower value of inductor current [A]} \\ \mathsf{IL}_{\mathsf{MAX}} = \mathsf{I}_{\mathsf{OMAX}} + \Delta \mathsf{IL} \ / \ 2 : \text{Upper value of inductor current [A]} \\ \mathsf{V}_{\mathsf{IN}} & : \text{Switching system power supply voltage [V]} \\ \mathsf{fosc} & : \text{Switching frequency [Hz]} \\ \mathsf{Tr} & : \text{Switching FET turn-on time [s]} \\ \mathsf{Tf} & : \text{Switching FET turn-off time [s]} \end{array}$

Flyback Diode Selection

Select the shot-key barrier diode (Flyback diode) with a small forward voltage as much as possible.

To judge that the current passing through the flyback diode is below the rated value, it is necessary to obtain the value of peak current passing through the flyback diode. The maximum current value of the flyback diode can be obtained as follows :

$$|f \ge I_{OMAX} + \frac{\Delta IL}{2}$$

I<sub>f</sub> : Forward current [A] I<sub>OMAX</sub> : Max. charge current [A] ∆IL : Peak-to-peak value of inductor ripple current [A]

Furthermore, to judge that permissible flyback diode loss is below a rated value, it is necessary to obtain the flyback diode loss. The flyback diode loss can be obtained as follows :

$$\mathsf{P}_{\mathsf{SBD}} = \mathsf{I}_{\mathsf{OMAX}} \times (1 - \frac{\mathsf{V}_{\mathsf{O}}}{\mathsf{V}_{\mathsf{IN}}}) \times \mathsf{Vf}$$

P<sub>SBD</sub> : Flyback diode loss [W]

I<sub>OMAX</sub> : Max. charge current [A]

V<sub>IN</sub> : Switching system power supply voltage [V]

V<sub>O</sub> : Charge voltage [V]

Vf : Forward voltage [V]

#### Output Capacitor Selection

Since a high ESR causes the output ripple voltage to increase, a low-ESR capacitor is needs to be used in order to reduce the output ripple voltage. Use a capacitor that has sufficient ratings to surge current generated when the battery is inserted or removed. Generally, the ceramic capacitor is used as the output capacitor.

With the switching ripple voltage taken into consideration, the minimum capacitance required can be found by the following formula.

$$Co \ge \frac{1}{2\pi \times fosc \times (-\frac{\Delta V_O}{\Delta IL} - ESR)}$$

- Co : Output capacitor [F]

- ESR : Serial resistance of output capacitor  $[\Omega]$

- $\Delta V_{O}$  : Switching ripple voltage [V]

- △IL : Peak-to-peak value of inductor ripple current [A]

- fosc : Switching frequency [Hz]

Since an overshoot occurs in the DC/DC converter output voltage when a battery being charged is removed, use a capacitor having sufficient withstand voltage. Generally, the capacitor having a rated withstand voltage higher than the maximum input voltage is sued.

Moreover, use a capacitor having sufficient tolerance for allowable ripple current. The allowable ripple current required can be found by the following formula.

Irms≥

$$\frac{\Delta IL}{2\sqrt{3}}$$

Irms : Acceptable ripple current (effective value) [A]

$\Delta IL$  : Peak-to-peak value of inductor ripple current [A]

### Input Capacitor Selection

Select an input capacitor that has an ESR as small as possible. A ceramic capacitor is ideal. If a high capacitance capacitor is needed for which there is no suitable ceramic capacitor use a polymer capacitor or a tantalum capacitor having a low ESR. The ripple voltage by the switching operation of the DC/DC converter is generated in the power supply voltage. Please consider the lower limit value of the input capacitor according to the allowable ripple voltage. The ripple voltage of the power supply can be easily found by the following formula.

$$\Delta V_{IN} = \frac{I_{OMAX}}{C_{IN}} \times \frac{V_O}{V_{IN} \times f_{OSC}} + ESR \times (I_{OMAX} + \frac{\Delta IL}{2})$$

| $\Delta V_{IN}$   | : Peak-to-peak value of switching system power supply ripple voltage [V] |

|-------------------|--------------------------------------------------------------------------|

| I <sub>OMAX</sub> | : Maximum charge current [A]                                             |

| C <sub>IN</sub>   | : Input capacitor [F]                                                    |

| V <sub>IN</sub>   | : Switching system power supply voltage [V]                              |

| V <sub>O</sub>    | : Charge voltage [V]                                                     |

| f <sub>OSC</sub>  | : Switching frequency [Hz]                                               |

| ESR               | : Series resistance component of input capacitor $[\Omega]$              |

| ΔIL               | : Peak-to-peak value of inductor ripple current [A]                      |

The ripple voltage of the power supply can be decreased by raising the switching frequency besides using the capacitor. The capacitor has the features in the frequency, temperature and bias voltage, so that the effect capacitance can be extremely small depending on the use conditions.

Please choose the one of having the enough margin for the input voltage and ripple current to ratings of the capacitor.

The acceptable ripple current is given by the following formula.

Irms

$$\geq I_{OMAX^{\star}} \frac{\sqrt{V_{O^{\star}}(V_{IN} - V_{O})}}{V_{IN}}$$

| Irms              | : Acceptable ripple current (effective value) [A] |

|-------------------|---------------------------------------------------|

| I <sub>OMAX</sub> | : Maximum charge current [A]                      |

| V <sub>IN</sub>   | : Switching system power supply voltage [V]       |

| V <sub>O</sub>    | : Charge voltage [V]                              |

|                   |                                                   |

· Designing Phase Compensation Circuit

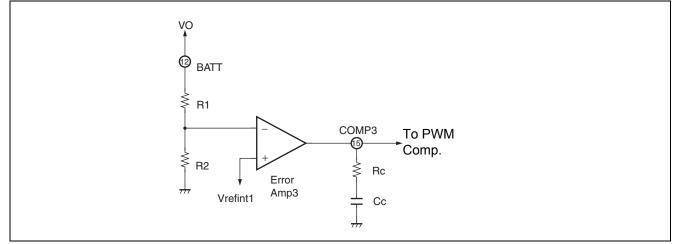

### (1) Constant Voltage (CV) Mode Phase Compensation Circuit

It is common to connect a 1-pole-1-zero phase compensation circuit to the output pin (COMP3) of the error amplifier 3 (gm amplifier). When a low-ESR capacitor, such as a ceramic capacitor, is used as the output capacitor, it is easier for the DC/DC converter to oscillate as the phase delay approaches 180 degrees due to the resonance frequency of LC. In this situation, perform phase compensation by connecting a RC phase lead compensator to the COMP3 pin, and between the -INE3 pin and the BATT pin.

Figure 1. 1pole-1zero Phase Compensation Circuit

Rc  $(\Omega)$  and Cc (F) of the phase lead circuit can be obtained by the following formula.

$$R_{C \approx} \frac{I_{O}}{190 \times 10^{-6} \times V_{IN}} \times \sqrt{\frac{L}{Co}}$$

$$C_{C \approx} \frac{\sqrt{L \times Co}}{R_{C}}$$

I<sub>O</sub> : Charge current [A]

- V<sub>IN</sub> : Switching system power supply voltage [V]

- L : Inductance value of inductor [H]

- Co : Output capacitor value [F]

- V<sub>O</sub> : Charge voltage [V]

In this situation, the crossover frequency fco [Hz] can be obtained by the following formula.

$$f_{CO} \approx 1 \times 10^{-5} \times \frac{V_{IN}}{V_O \times C_C}$$

### (2) Constant Current (CC) Mode Phase Compensation Circuit

Since the output capacitor impedance has a small influence to the loop response characteristics in this mode, the phase compensation circuit with 1pole-1zero is normally connected to the output pin (COMP2) of the error amplifier 2 (gm amplifier).

### Figure 2. 1pole-1zero Phase Compensation Circuit

$\text{Rc}\left(\Omega\right)$  and  $\text{Cc}\left(F\right)$  of the phase lead circuit can be obtained by the following formula.

$$R_{C \approx} 1.2 \times 10^4 \times \frac{f_{CO} \times L}{Rs \times V_{IN}}$$

$$C_{C \approx} \frac{\sqrt{L \times Co}}{R_{C}}$$

- Rs : Resistance value of charge current detection  $[\Omega]$

- V<sub>IN</sub> : Switching system power supply voltage [V]

L : Inductance value [H]

- Co : Output capacitance value [F]

- $f_{CO}$  : Crossover frequency [Hz]

Allowable Loss, and Thermal Design

In general, the allowable loss and thermal design of this IC can be ignored because this IC is highly effective. However, when this IC is used with high power supply voltage, high switching frequency, high load, or high temperature, it is necessary to take account of the allowable loss and thermal design while using this IC.

The IC internal loss  $(P_{IC})$  can be found by the following formula.

$\mathsf{P}_{\mathsf{IC}} = \mathsf{V}_{\mathsf{CC}} \mathsf{\times} \left(\mathsf{I}_{\mathsf{CC}} + \mathsf{Q}_{\mathsf{g}} \mathsf{\times} \mathsf{f}_{\mathsf{OSC}}\right)$

- P<sub>IC</sub> : IC's Internal loss [W]

- V<sub>CC</sub> : Power supply voltage (V<sub>IN</sub>) [V]

- I<sub>CC</sub> : Power supply current [A] (4.0 mA Max)

- $Q_g$  : Total amount of charges of all switching FETs [C] (when Vgs = 6 V)

- f<sub>OSC</sub> : Switching frequency [Hz]

The temperature at the joint part (Tj) can be obtained as follows :

$Tj = Ta + \theta ja \times P_{IC}$

- Tj : Joint part temperature [°C]

- Ta : Ambient temperature [°C]

- θja : TSSOP-24 package thermal resistance (78°C / W)

- P<sub>IC</sub> : IC's internal loss [W]

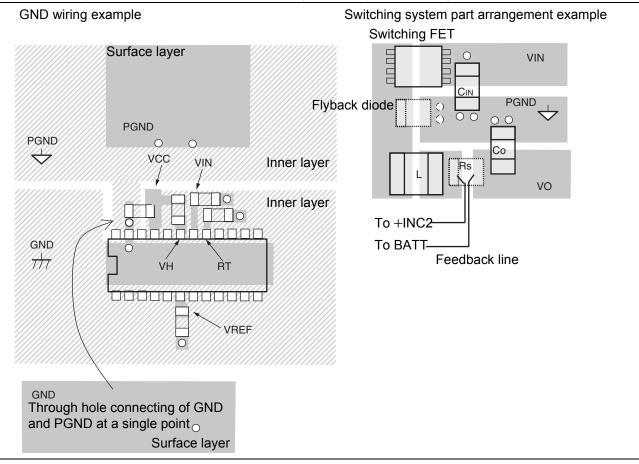

#### · Board Layout

When designing the layout, consider the points listed below. Take account of the following points when designing the board layout.

- Place a GND plane on the IC mounting surface whenever possible. Connect the controller GND to PGND only at one point of PGND in order to prevent a large current path from passing the controller GND.