# **TABLE OF CONTENTS**

| Features                                      |

|-----------------------------------------------|

| Applications1                                 |

| Functional Block Diagrams1                    |

| General Description                           |

| Revision History2                             |

| Specifications                                |

| Receiver Input Threshold Test Voltages 4      |

| Timing Specifications                         |

| Absolute Maximum Ratings                      |

| Thermal Resistance                            |

| ESD Caution                                   |

| Pin Configurations and Function Descriptions7 |

| Typical Performance Characteristics           |

| Test Circuits and Switching Characteristics   |

### **REVISION HISTORY**

| 1/16—Rev. A to Rev. B |  |

|-----------------------|--|

| Change to Table 6 6   |  |

#### 3/12-Rev. 0 to Rev. A

| Added ADN4691E and ADN4693E                          | .Universal |

|------------------------------------------------------|------------|

| Changes to Features Section, General Description Sec | tion,      |

| and Table 1                                          | 1          |

| Added Type 1 Receiver Parameters, Table 2            | 3          |

| Added Table 3, Renumbered Sequentially               | 4          |

| Added Type 1 Receiver Parameters, Table 5            |            |

|   | Driver Voltage and Current Measurements | 11   |

|---|-----------------------------------------|------|

|   | Driver Timing Measurements              | . 12 |

|   | Receiver Timing Measurements            | . 13 |

| Т | heory of Operation                      | . 14 |

|   | Half-Duplex/Full-Duplex Operation       | 14   |

|   | Three-State Bus Connection              | . 14 |

|   | Truth Tables                            | 14   |

|   | Glitch-Free Power-Up/Power-Down         | 15   |

|   | Fault Conditions                        | 15   |

|   | Receiver Input Thresholds/Fail-Safe     | . 15 |

| A | pplications Information                 | 16   |

| 0 | utline Dimensions                       | . 17 |

|   | Ordering Guide                          | . 17 |

|   |                                         |      |

| Added Table 7                                          | 6  |

|--------------------------------------------------------|----|

| Changes to Table 8                                     | 7  |

| Changes to Figure 33                                   | 13 |

| Added Table 12                                         | 14 |

| Changes to Receiver Input Thresholds/Fail-Safe Section |    |

| and Figure 36                                          | 15 |

| Changes to Ordering Guide                              | 17 |

|                                                        |    |

12/11—Revision 0: Initial Version

# **SPECIFICATIONS**

$V_{\rm CC}$  = 3.0 V to 3.6 V;  $R_{\rm L}$  = 50  $\Omega;$   $T_{\rm A}$  =  $T_{\rm MIN}$  to  $T_{\rm MAX}$  , unless otherwise noted.  $^1$

#### Table 2.

| Parameter                                                    | Symbol                                                                              | Min                  | Тур | Max             | Unit | Test Conditions/Comments                                                                                                                                   |

|--------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------|-----|-----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRIVER                                                       |                                                                                     |                      |     |                 |      |                                                                                                                                                            |

| Differential Outputs                                         |                                                                                     |                      |     |                 |      |                                                                                                                                                            |

| Differential Output Voltage Magnitude                        | V <sub>OD</sub>                                                                     | 480                  |     | 650             | mV   | See Figure 19                                                                                                                                              |

| $\Delta  V_{OD} $ for Complementary Output States            |                                                                                     | -50                  |     | +50             | mV   | See Figure 19                                                                                                                                              |

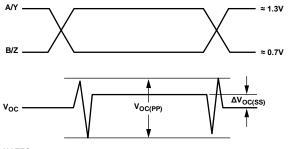

| Common-Mode Output Voltage (Steady State)                    | V <sub>OC(SS)</sub>                                                                 | 0.8                  |     | 1.2             | v    | See Figure 20, Figure 23                                                                                                                                   |

| $\Delta V_{OC(SS)}$ for Complementary Output States          | $\Delta V_{OC(SS)}$                                                                 | -50                  |     | +50             | mV   | See Figure 20, Figure 23                                                                                                                                   |

| Peak-to-Peak Voc                                             | V <sub>OC(PP)</sub>                                                                 |                      |     | 150             | mV   | See Figure 20, Figure 23                                                                                                                                   |

| Maximum Steady-State Open-Circuit Output<br>Voltage          | V <sub>A(O)</sub> , V <sub>B(O)</sub> ,<br>V <sub>Y(O)</sub> , or V <sub>Z(O)</sub> | 0                    |     | 2.4             | V    | See Figure 21                                                                                                                                              |

| Voltage Overshoot                                            |                                                                                     |                      |     |                 |      |                                                                                                                                                            |

| Low to High                                                  | VPH                                                                                 |                      |     | 1.2 Vss         | V    | See Figure 24, Figure 27                                                                                                                                   |

| High to Low                                                  | V <sub>PL</sub>                                                                     | -0.2 V <sub>ss</sub> |     |                 | V    | See Figure 24, Figure 27                                                                                                                                   |

| Output Current                                               |                                                                                     |                      |     |                 |      |                                                                                                                                                            |

| Short Circuit                                                | los                                                                                 |                      |     | 24              | mA   | See Figure 22                                                                                                                                              |

| High Impedance State, Driver Only                            | loz                                                                                 | -15                  |     | +10             | μA   | $-1.4 \text{ V} \le (\text{V}_{\text{Y}} \text{ or } \text{V}_{\text{Z}}) \le 3.8 \text{ V},$<br>other output = 1.2 V                                      |

| Power Off                                                    | I <sub>O(OFF)</sub>                                                                 | -10                  |     | +10             | μA   | $-1.4 \text{ V} \le (\text{V}_{\text{Y}} \text{ or } \text{V}_{\text{Z}}) \le 3.8 \text{ V},$<br>other output = 1.2 V, 0 V $\le$ V <sub>CC</sub> $\le 1.5$ |

| Output Capacitance                                           | C <sub>Y</sub> or C <sub>Z</sub>                                                    |                      | 3   |                 | pF   | $V_i = 0.4 \sin(30e^6\pi t) V + 0.5 V_i^2$<br>other output = 1.2 V, DE = 0 V                                                                               |

| Differential Output Capacitance                              | C <sub>YZ</sub>                                                                     |                      |     | 2.5             | pF   | $V_{AB} = 0.4 \sin(30e^6\pi t) V^2_{,2} DE = 0 V$                                                                                                          |

| Output Capacitance Balance (C <sub>Y</sub> /C <sub>z</sub> ) | C <sub>Y/Z</sub>                                                                    | 0.99                 |     | 1.01            | 14.1 |                                                                                                                                                            |

| Logic Inputs (DI, DE)                                        | <b>C</b> 172                                                                        | 0.22                 |     |                 |      |                                                                                                                                                            |

| Input High Voltage                                           | VIH                                                                                 | 2                    |     | Vcc             | v    |                                                                                                                                                            |

| Input Low Voltage                                            | VIL                                                                                 | GND                  |     | 0.8             | v    |                                                                                                                                                            |

| Input High Current                                           | Ін                                                                                  | 0                    |     | 10              | μA   | $V_{IH} = 2 V$                                                                                                                                             |

| Input Low Current                                            | IIL                                                                                 | 0                    |     | 10              | μΑ   | $V_{IL} = 0.8 V$                                                                                                                                           |

| RECEIVER                                                     |                                                                                     | •                    |     |                 | P. 1 |                                                                                                                                                            |

| Differential Inputs                                          |                                                                                     |                      |     |                 |      |                                                                                                                                                            |

| Differential Input Threshold Voltage                         |                                                                                     |                      |     |                 |      |                                                                                                                                                            |

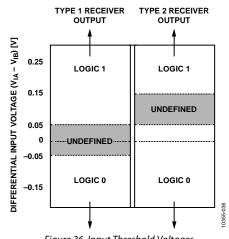

| Type 1 Receiver (ADN4691E, ADN4693E)                         | VTH                                                                                 | -50                  |     | +50             | mV   | See Table 3, Figure 36                                                                                                                                     |

| Type 2 Receiver (ADN4696E, ADN4697E)                         | VTH                                                                                 | 50                   |     | 150             | mV   | See Table 4, Figure 36                                                                                                                                     |

| Input Hysteresis                                             | • In                                                                                | 50                   |     | 150             |      | See Table 1, Figure 50                                                                                                                                     |

| Type 1 Receiver (ADN4691E, ADN4693E)                         | V <sub>HYS</sub>                                                                    |                      | 25  |                 | mV   |                                                                                                                                                            |

| Type 2 Receiver (ADN4696E, ADN4697E)                         | VHYS                                                                                |                      | 0   |                 | mV   |                                                                                                                                                            |

| Differential Input Voltage Magnitude                         |                                                                                     | 0.05                 | 0   | Vcc             | V    |                                                                                                                                                            |

| Input Capacitance                                            |                                                                                     | 0.05                 | 3   | VCC             | pF   | $V_1 = 0.4 \sin(30e^6\pi t) V + 0.5 V_1^2$                                                                                                                 |

| input capacitance                                            | CA OF CB                                                                            |                      | 2   |                 | рг   | other input = $1.2 \text{ V}$                                                                                                                              |

| Differential Input Capacitance                               | C <sub>AB</sub>                                                                     |                      |     | 2.5             | рF   | $V_{AB} = 0.4 \sin(30e^6\pi t) V^2$                                                                                                                        |

| Input Capacitance Balance (C <sub>A</sub> /C <sub>B</sub> )  | Сав<br>Са/в                                                                         | 0.99                 |     | 1.01            | р'   |                                                                                                                                                            |

| Logic Output RO                                              | CAVD                                                                                | 0.75                 |     |                 |      |                                                                                                                                                            |

| Output High Voltage                                          | Vон                                                                                 | 2.4                  |     |                 | v    | I <sub>он</sub> = -8 mA                                                                                                                                    |

| Output High voltage<br>Output Low Voltage                    | V <sub>OH</sub><br>V <sub>OL</sub>                                                  | 2.4                  |     | 0.4             | v    | $I_{OH} = -8 \text{ mA}$<br>$I_{OL} = 8 \text{ mA}$                                                                                                        |

|                                                              |                                                                                     | 10                   |     |                 | -    |                                                                                                                                                            |

| High Impedance Output Current                                | loz                                                                                 | -10                  |     | +15             | μA   | $V_0 = 0 V \text{ or } 3.6 V$                                                                                                                              |

|                                                              |                                                                                     |                      |     | .,              |      |                                                                                                                                                            |

| Input High Voltage                                           | ViH                                                                                 | 2                    |     | V <sub>cc</sub> | V    |                                                                                                                                                            |

| Input Low Voltage                                            | V <sub>IL</sub>                                                                     | GND                  |     | 0.8             | V    |                                                                                                                                                            |

| Input High Current                                           | I <sub>Н</sub>                                                                      | -10                  |     | 0               | μA   | $V_{IH} = 2 V$                                                                                                                                             |

| Input Low Current                                            | IL                                                                                  | -10                  |     | 0               | μΑ   | $V_{IL} = 0.8 V$                                                                                                                                           |

| Parameter                                                                                      | Symbol                           | Min  | Тур | Max  | Unit | Test Conditions/Comments                                                  |

|------------------------------------------------------------------------------------------------|----------------------------------|------|-----|------|------|---------------------------------------------------------------------------|

| BUS INPUT/OUTPUT                                                                               |                                  |      |     |      |      |                                                                           |

| Input Current                                                                                  |                                  |      |     |      |      |                                                                           |

| A (Receiver or Transceiver with Driver Disabled)                                               | IA                               | 0    |     | 32   | μΑ   | $V_B = 1.2 V$ , $V_A = 3.8 V$                                             |

|                                                                                                |                                  | -20  |     | +20  | μΑ   | $V_B = 1.2 V$ , $V_A = 0 V$ or 2.4 V                                      |

|                                                                                                |                                  | -32  |     | 0    | μΑ   | $V_B = 1.2 V, V_A = -1.4 V$                                               |

| B (Receiver or Transceiver with Driver Disabled)                                               | IB                               | 0    |     | 32   | μΑ   | $V_A = 1.2 V, V_B = 3.8 V$                                                |

|                                                                                                |                                  | -20  |     | +20  | μΑ   | $V_A = 1.2 V$ , $V_B = 0 V$ or 2.4 V                                      |

|                                                                                                |                                  | -32  |     | 0    | μΑ   | $V_A = 1.2 V, V_B = -1.4 V$                                               |

| Differential (Receiver or Transceiver with Driver<br>Disabled)                                 | I <sub>AB</sub>                  | -4   |     | +4   | μΑ   | $V_{\text{A}}=V_{\text{B}},1.4\text{V}\leq V_{\text{A}}\leq3.8\text{V}$   |

| Power-Off Input Current                                                                        |                                  |      |     |      |      | $0 \text{ V} \leq \text{V}_{CC} \leq 1.5 \text{ V}$                       |

| A (Receiver or Transceiver)                                                                    | I <sub>A(OFF)</sub>              | 0    |     | 32   | μA   | $V_B = 1.2 V$ , $V_A = 3.8 V$                                             |

|                                                                                                |                                  | -20  |     | +20  | μΑ   | $V_B = 1.2 V$ , $V_A = 0 V$ or 2.4 V                                      |

|                                                                                                |                                  | -32  |     | 0    | μA   | $V_B = 1.2 V, V_A = -1.4 V$                                               |

| B (Receiver or Transceiver)                                                                    | I <sub>B(OFF)</sub>              | 0    |     | 32   | μΑ   | $V_A = 1.2 V, V_B = 3.8 V$                                                |

|                                                                                                |                                  | -20  |     | +20  | μΑ   | $V_A = 1.2 V$ , $V_B = 0 V$ or 2.4 V                                      |

|                                                                                                |                                  | -32  |     | 0    | μΑ   | $V_A = 1.2 V, V_B = -1.4 V$                                               |

| Differential (Receiver or Transceiver)                                                         | I <sub>AB(OFF)</sub>             | -4   |     | +4   | μΑ   | $V_A = V_B$ , $1.4 \le V_A \le 3.8 V$                                     |

| Input Capacitance (Transceiver with Driver Disabled)                                           | C <sub>A</sub> or C <sub>B</sub> |      | 5   |      | pF   | $V_1 = 0.4 \sin(30e^6\pi t) V + 0.5 V^2$<br>other input = 1.2 V, DE = 0 V |

| Differential Input Capacitance (Transceiver with<br>Driver Disabled)                           | C <sub>AB</sub>                  |      |     | 3    | pF   | $V_{AB} = 0.4 \sin(30e^6\pi t) V^2 DE = 0 V$                              |

| Input Capacitance Balance (C <sub>A</sub> /C <sub>B</sub> ) (Transceiver with Driver Disabled) | C <sub>A/B</sub>                 | 0.99 |     | 1.01 |      | DE = 0 V                                                                  |

| POWER SUPPLY                                                                                   |                                  |      |     |      |      |                                                                           |

| Supply Current                                                                                 | lcc                              |      |     |      |      |                                                                           |

| Only Driver Enabled                                                                            |                                  |      | 13  | 22   | mA   | $DE, \overline{RE} = V_{CC}, R_L = 50 \Omega$                             |

| Both Driver and Receiver Disabled                                                              |                                  |      | 1   | 4    | mA   | $DE = 0 V$ , $\overline{RE} = V_{CC}$ , $R_L = no load$                   |

| Both Driver and Receiver Enabled                                                               |                                  |      | 16  | 24   | mA   | $DE = V_{CC}, \overline{RE} = 0 V, R_L = 50 \Omega$                       |

| Only Receiver Enabled                                                                          |                                  |      | 4   | 13   | mA   | DE, $\overline{\text{RE}} = 0 \text{ V}$ , $R_L = 50 \Omega$              |

$^1$  All typical values are given for  $V_{CC}$  = 3.3 V and  $T_A$  = 25°C.  $^2$  HP4194A impedance analyzer (or equivalent).

### **RECEIVER INPUT THRESHOLD TEST VOLTAGES**

$\overline{\text{RE}} = 0$  V, H = high, L = low

#### Table 3. Test Voltages for Type 1 Receiver

| Applied Voltages          |                                    | Input Voltage, Differential | Input Voltage, Common Mode | Receiver Output |  |

|---------------------------|------------------------------------|-----------------------------|----------------------------|-----------------|--|

| <b>V</b> <sub>A</sub> (V) | <b>V</b> <sub>B</sub> ( <b>V</b> ) | V <sub>ID</sub> (V)         | V <sub>IC</sub> (V)        | RO (V)          |  |

| 2.4                       | 0                                  | 2.4                         | 1.2                        | Н               |  |

| 0                         | 2.4                                | -2.4                        | 1.2                        | L               |  |

| 3.8                       | 3.75                               | 0.05                        | 3.775                      | н               |  |

| 3.75                      | 3.8                                | -0.05                       | 3.775                      | L               |  |

| -1.35                     | -1.4                               | 0.05                        | -1.375                     | н               |  |

| -1.4                      | -1.35                              | -0.05                       | -1.375                     | L               |  |

|                           | Applied Voltages   | Input Voltage, Differential | Input Voltage, Common Mode | <b>Receiver Output</b> |

|---------------------------|--------------------|-----------------------------|----------------------------|------------------------|

| <b>V</b> <sub>A</sub> (V) | V <sub>B</sub> (V) | V <sub>ID</sub> (V)         | V <sub>IC</sub> (V)        | RO (V)                 |

| +2.4                      | 0                  | +2.4                        | +1.2                       | Н                      |

| 0                         | +2.4               | -2.4                        | +1.2                       | L                      |

| +3.8                      | +3.65              | +0.15                       | +3.725                     | н                      |

| +3.8                      | +3.75              | +0.05                       | +3.775                     | L                      |

| -1.25                     | -1.4               | +0.15                       | -1.325                     | н                      |

| -1.35                     | -1.4               | +0.05                       | -1.375                     | L                      |

#### Table 4. Test Voltages for Type 2 Receiver

#### TIMING SPECIFICATIONS

$V_{CC}$  = 3.0 V to 3.6 V;  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.<sup>1</sup>

#### Table 5.

| Parameter                                              | Symbol                              | Min | Тур | Max | Unit | Test Conditions/Comments                                             |

|--------------------------------------------------------|-------------------------------------|-----|-----|-----|------|----------------------------------------------------------------------|

| DRIVER                                                 |                                     |     |     |     |      |                                                                      |

| Maximum Data Rate                                      |                                     | 200 |     |     | Mbps |                                                                      |

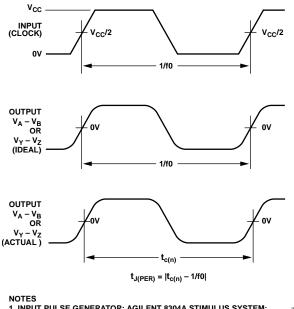

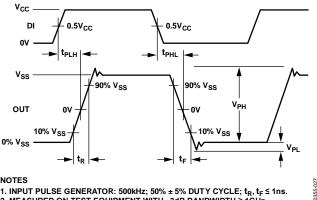

| Propagation Delay                                      | t <sub>PLH</sub> , t <sub>PHL</sub> | 1   | 1.5 | 2.4 | ns   | See Figure 24, Figure 27                                             |

| Differential Output Rise/Fall Time                     | t <sub>R</sub> , t <sub>F</sub>     | 1   |     | 1.6 | ns   | See Figure 24, Figure 27                                             |

| Pulse Skew  t <sub>PHL</sub> – t <sub>PLH</sub>        | t <sub>sK</sub>                     |     | 0   | 100 | ps   | See Figure 24, Figure 27                                             |

| Part-to-Part Skew <sup>2</sup>                         | t <sub>sk(PP)</sub>                 |     |     | 1   | ns   | See Figure 24, Figure 27                                             |

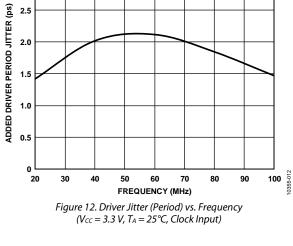

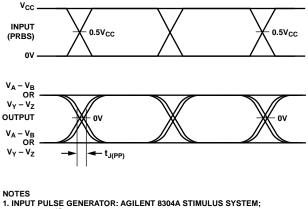

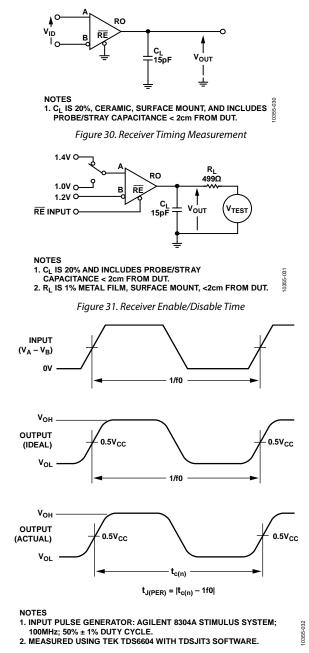

| Period Jitter, RMS (1 Standard Deviation) <sup>3</sup> | t <sub>J(PER)</sub>                 |     | 2   | 3   | ps   | 100 MHz clock input <sup>4</sup> (see Figure 26)                     |

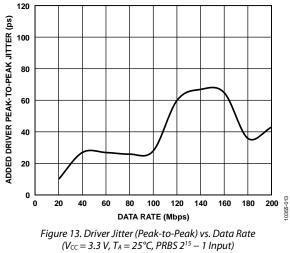

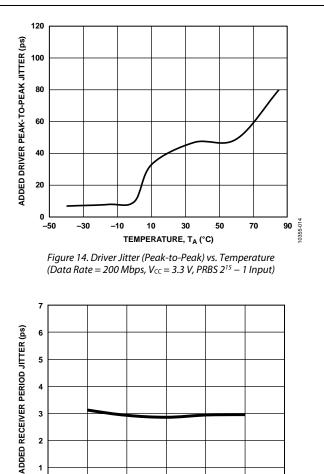

| Peak-to-Peak Jitter <sup>3, 5</sup>                    | t <sub>J(PP)</sub>                  |     | 30  | 130 | ps   | 200 Mbps 2 <sup>15</sup> – 1 PRBS input <sup>6</sup> (see Figure 29) |

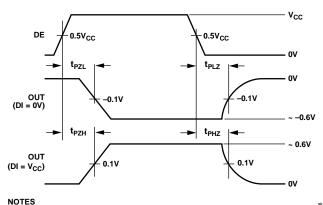

| Disable Time from High Level                           | t <sub>PHZ</sub>                    |     |     | 7   | ns   | See Figure 25, Figure 28                                             |

| Disable Time from Low Level                            | t <sub>PLZ</sub>                    |     |     | 7   | ns   | See Figure 25, Figure 28                                             |

| Enable Time to High Level                              | t <sub>PZH</sub>                    |     |     | 7   | ns   | See Figure 25, Figure 28                                             |

| Enable Time to Low Level                               | t <sub>PZL</sub>                    |     |     | 7   | ns   | See Figure 25, Figure 28                                             |

| RECEIVER                                               |                                     |     |     |     |      |                                                                      |

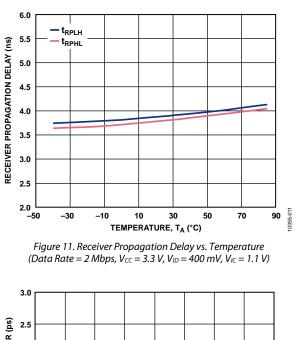

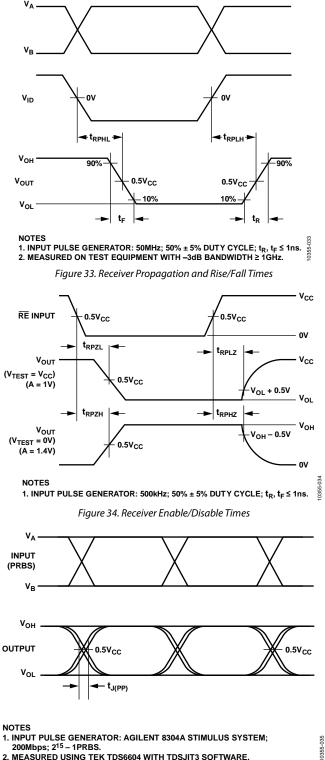

| Propagation Delay                                      | trplh, trphl                        | 2   | 4   | 6   | ns   | $C_L = 15 \text{ pF}$ (see Figure 30, Figure 33)                     |

| Rise/Fall Time                                         | t <sub>R</sub> , t <sub>F</sub>     | 1   |     | 2.3 | ns   | $C_L = 15 \text{ pF}$ (see Figure 30, Figure 33)                     |

| Pulse Skew  trphl – trplh                              | tsк                                 |     |     |     |      | $C_L = 15 \text{ pF}$ (see Figure 30, Figure 33)                     |

| Type 1 Receiver (ADN4691E, ADN4693E)                   |                                     |     | 100 | 300 | ps   |                                                                      |

| Type 2 Receiver (ADN4696E, ADN4697E)                   |                                     |     | 300 | 500 | ps   |                                                                      |

| Part-to-Part Skew <sup>2</sup>                         | t <sub>SK(PP)</sub>                 |     |     | 1   | ns   | $C_{L} = 15 \text{ pF}$ (see Figure 30, Figure 33)                   |

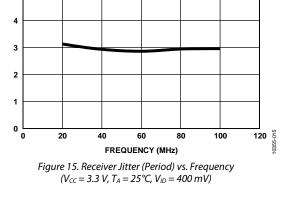

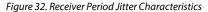

| Period Jitter, RMS (1 Standard Deviation) <sup>3</sup> | t <sub>J(PER)</sub>                 |     | 4   | 7   | ps   | 100 MHz clock input <sup>7</sup> (see Figure 32)                     |

| Peak-to-Peak Jitter <sup>3, 5</sup>                    | t <sub>J(PP)</sub>                  |     |     |     |      | 200 Mbps 2 <sup>15</sup> – 1 PRBS input <sup>8</sup> (see Figure 35) |

| Type 1 Receiver (ADN4691E, ADN4693E)                   | t <sub>J(PP)</sub>                  |     | 300 | 700 | ps   |                                                                      |

| Type 2 Receiver (ADN4696E, ADN4697E)                   |                                     |     | 450 | 800 | ps   |                                                                      |

| Disable Time from High Level                           | t <sub>RPHZ</sub>                   |     |     | 10  | ns   | See Figure 31, Figure 34                                             |

| Disable Time from Low Level                            | t <sub>RPLZ</sub>                   |     |     | 10  | ns   | See Figure 31, Figure 34                                             |

| Enable Time to High Level                              | t <sub>RPZH</sub>                   |     |     | 15  | ns   | See Figure 31, Figure 34                                             |

| Enable Time to Low Level                               | t <sub>RPZL</sub>                   |     |     | 15  | ns   | See Figure 31, Figure 34                                             |

<sup>1</sup> All typical values are given for  $V_{CC} = 3.3$  V and  $T_A = 25$ °C.

<sup>2</sup> t<sub>SKIPP</sub> is defined as the difference between the propagation delays of two devices between any specified terminals. This specification applies to devices at the same V<sub>cc</sub> and temperature, and with identical packages and test circuits.

<sup>3</sup> Jitter parameters are guaranteed by design and characterization. Values do not include stimulus jitter.

$^{4}$  t<sub>R</sub> = t<sub>F</sub> = 0.5 ns (10% to 90%), measured over 30,000 samples.

<sup>5</sup> Peak-to-peak jitter specifications include jitter due to pulse skew (t<sub>SK</sub>).

$^{6}$  t<sub>R</sub> = t<sub>F</sub> = 0.5 ns (10% to 90%), measured over 100,000 samples.

$^{7}$  |V<sub>ID</sub>| = 400 mV (ADN4696E, ADN4697E), V<sub>IC</sub> = 1.1 V, t<sub>R</sub> = t<sub>F</sub> = 0.5 ns (10% to 90%), measured over 30,000 samples.  $^{8}$  |V<sub>ID</sub>| = 400 mV (ADN4696E, ADN4697E), V<sub>IC</sub> = 1.1 V, t<sub>R</sub> = t<sub>F</sub> = 0.5 ns (10% to 90%), measured over 100,000 samples.

### **ABSOLUTE MAXIMUM RATINGS**

$T_{\rm A}$  =  $T_{\rm MIN}$  to  $T_{\rm MAX}$ , unless otherwise noted.

#### Table 6.

| Parameter                          | Rating          |

|------------------------------------|-----------------|

| V <sub>cc</sub>                    | –0.5 V to +4 V  |

| Digital Input Voltage (DE, RE, DI) | –0.5 V to +4 V  |

| Receiver Input (A, B) Voltage      |                 |

| Half-Duplex (ADN4691E, ADN4696E)   | –1.8 V to +4 V  |

| Full-Duplex (ADN4693E, ADN4697E)   | –4 V to +6 V    |

| Receiver Output Voltage (RO)       | –0.3 V to +4 V  |

| Driver Output (A, B, Y, Z) Voltage | –1.8 V to +4 V  |

| ESD Rating (A, B, Y, Z Pins)       |                 |

| HBM (Human Body Model)             |                 |

| Air Discharge                      | ±15 kV          |

| Contact Discharge                  | ±8 kV           |

| IEC 61000-4-2, Air Discharge       | ±10 kV          |

| IEC 61000-4-2, Contact Discharge   | ±8 kV           |

| ESD Rating (Other Pins, HBM)       | ±4 kV           |

| ESD Rating (All Pins)              |                 |

| FICDM                              | ±1.25 kV        |

| Operating Temperature Range        | -40°C to +85°C  |

| Storage Temperature Range          | –65°C to +150°C |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst case conditions, that is, a device soldered in a circuit board for surface-mount packages.

#### Table 7. Thermal Resistance

| Package Type | Αιθ | Unit |

|--------------|-----|------|

| 8-Lead SOIC  | 121 | °C/W |

| 14-Lead SOIC | 86  | °C/W |

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

### **PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS**

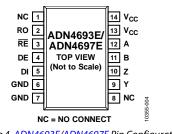

Figure 3. ADN4691E/ADN4696E Pin Configuration

#### **Table 8. Pin Function Descriptions**

Figure 4. ADN4693E/ADN4697E Pin Configuration

| ADN4691E/<br>ADN4696E<br>Pin No. <sup>1</sup> | ADN4693E/<br>ADN4697E<br>Pin No. <sup>1</sup> | Mnemonic        | Description                                                                                                                                                                       |

|-----------------------------------------------|-----------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                             | 2                                             | RO              | Receiver Output. Type 1 receiver (ADN4691E/ADN4693E), when enabled:                                                                                                               |

|                                               |                                               |                 | If A – B $\geq$ 50 mV, then RO = logic high. If A – B $\leq$ –50 mV, then RO = logic low.                                                                                         |

|                                               |                                               |                 | Type 2 receiver (ADN4696E/ADN4697E), when enabled:                                                                                                                                |

|                                               |                                               |                 | If A – B $\ge$ 150 mV, then RO = logic high. If A – B $\le$ 50 mV, then RO = logic low.                                                                                           |

|                                               |                                               |                 | Receiver output is undefined outside these conditions.                                                                                                                            |

| 2                                             | 3                                             | RE              | Receiver Output Enable. A logic low on this pin enables the receiver output, RO. A logic high on this pin places RO in a high impedance state.                                    |

| 3                                             | 4                                             | DE              | Driver Output Enable. A logic high on this pin enables the driver differential outputs. A logic low on this pin places the driver differential outputs in a high impedance state. |

| 4                                             | 5                                             | DI              | Driver Input. Half-duplex (ADN4691E/ADN4696E), when enabled:                                                                                                                      |

|                                               |                                               |                 | A logic low on DI forces A low and B high, whereas a logic high on DI forces A high and B low.                                                                                    |

|                                               |                                               |                 | Full-duplex (ADN4693E/ADN4697E), when enabled:                                                                                                                                    |

|                                               |                                               |                 | A logic low on DI forces Y low and Z high, whereas a logic high on DI forces Y high and Z low.                                                                                    |

| 5                                             | 6, 7                                          | GND             | Ground.                                                                                                                                                                           |

| N/A                                           | 9                                             | Y               | Noninverting Driver Output Y.                                                                                                                                                     |

| N/A                                           | 10                                            | Z               | Inverting Driver Output Z.                                                                                                                                                        |

| 6                                             | N/A                                           | А               | Noninverting Receiver Input A and Noninverting Driver Output A.                                                                                                                   |

| N/A                                           | 12                                            | А               | Noninverting Receiver Input A.                                                                                                                                                    |

| 7                                             | N/A                                           | В               | Inverting Receiver Input B and Inverting Driver Output B.                                                                                                                         |

| N/A                                           | 11                                            | В               | Inverting Receiver Input B.                                                                                                                                                       |

| 8                                             | 13, 14                                        | V <sub>cc</sub> | Power Supply (3.3 V $\pm$ 0.3 V).                                                                                                                                                 |

| N/A                                           | 1, 8                                          | NC              | No Connect. Do not connect to these pins.                                                                                                                                         |

<sup>1</sup> N/A means not applicable.

### **TYPICAL PERFORMANCE CHARACTERISTICS**

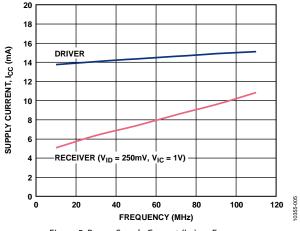

Figure 5. Power Supply Current ( $I_{CC}$ ) vs. Frequency ( $V_{CC} = 3.3 V$ ,  $T_A = 25^{\circ}C$ ; Receiver  $V_{ID} = 250 mV$ ,  $V_{IC} = 1 V$ )

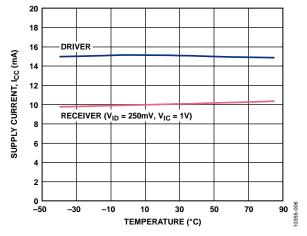

Figure 6. Power Supply Current vs. Temperature (Data Rate = 200 Mbps,  $V_{CC} = 3.3 V$ ; Receiver  $V_{ID} = 250 \text{ mV}$ ,  $V_{IC} = 1 V$ )

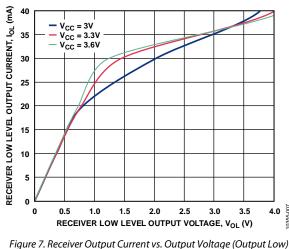

gure 7. Receiver Output Current vs. Output Voltage (Output Lov  $(T_A = 25^{\circ}C)$

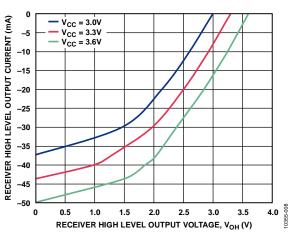

Figure 8. Receiver Output Current vs. Output Voltage (Output High)  $(T_A = 25^{\circ}C)$

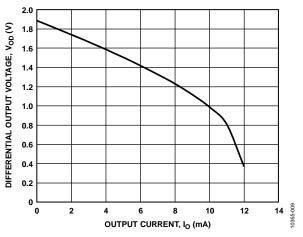

Figure 9. Driver Differential Output Voltage vs. Output Current  $(V_{CC} = 3.3 V, T_A = 25^{\circ}C)$

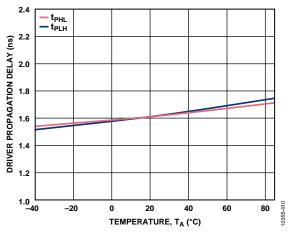

Figure 10. Driver Propagation Delay vs. Temperature (Data Rate = 2 Mbps, V<sub>CC</sub> = 3.3 V)

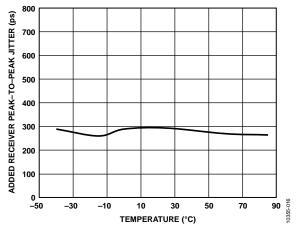

Figure 16. Receiver Jitter (Peak-to-Peak) vs. Temperature (Data Rate = 200 Mbps,  $V_{cc}$  = 3.3 V,  $V_{lc}$  = 400 mV,  $V_{lc}$  = 1.1 V, PRBS 2<sup>15</sup> - 1 Input)

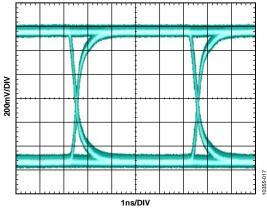

Figure 17. ADN4696E Driver Output Eye Pattern (Data Rate = 200 Mbps, PRBS  $2^{15} - 1$  Input,  $R_L = 50 \Omega$ )

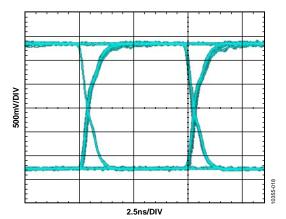

Figure 18. ADN4696E Receiver Output Eye Pattern (Data Rate = 200 Mbps, PRBS  $2^{15} - 1$  Input,  $C_L = 15$  pF)

# **TEST CIRCUITS AND SWITCHING CHARACTERISTICS**

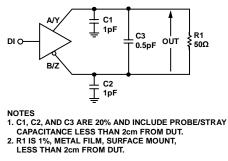

**DRIVER VOLTAGE AND CURRENT MEASUREMENTS**

Figure 19. Driver Voltage Measurement over Common-Mode Range

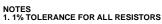

Figure 22. Driver Short Circuit

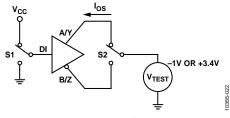

NOTES 1. C1, C2, AND C3 ARE 20% AND INCLUDE PROBE/STRAY CAPACITANCE LESS THAN 2cm FROM DUT. 2. R1 AND R2 ARE 1%, METAL FILM, SURFACE MOUNT, LESS THAN 2cm FROM DUT. GEF.

Figure 20. Driver Common-Mode Output Voltage Measurement

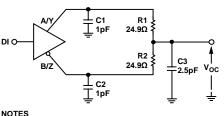

Figure 21. Maximum Steady-State Output Voltage Measurement

NOTES

1. INPUT PULSE GENERATOR: 500kHz; 50% ± 5% DUTY CYCLE; t<sub>R</sub>, t<sub>F</sub> ≤ 1ns. 2. V<sub>OC(PP)</sub> MEASURED ON TEST EQUIPMENT WITH –3dB BANDWIDTH ≥ 1GHz.  $\frac{80}{20}$

Figure 23. Driver Common-Mode Output Voltage (Steady State)

0355-028

0355-029

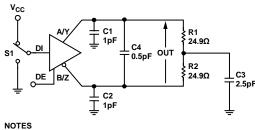

#### **DRIVER TIMING MEASUREMENTS**

Figure 24. Driver Timing Measurement

0355-024

0355-025

1. C1, C2, C3, AND C4 ARE 20% AND INCLUDE PROBE/STRAY CAPACITANCE LESS THAN 2cm FROM DUT. 2. R1 AND R2 ARE 1%, METAL FILM, SURFACE MOUNT, LESS THAN 2cm FROM DUT.

Figure 25. Driver Enable/Disable Time

| 1. INPUT PULSE GENERATOR: AGILENT 8304A STIMULUS SYSTEM; |  |

|----------------------------------------------------------|--|

| 100MHz; 50% ± 1% DUTY CYCLE.                             |  |

| 2. MEASURED USING TEK TDS6604 WITH TDSJIT3 SOFTWARE.     |  |

Figure 26. Driver Period Jitter Characteristics

NOTES 1. INPUT PULSE GENERATOR: 500kHz; 50% ± 5% DUTY CYCLE;  $t_R, t_F \le 1$ ns. 2. MEASURED ON TEST EQUIPMENT WITH -3dB BANDWIDTH ≥ 1GHz

Figure 27. Driver Propagation, Rise/Fall Times and Voltage Overshoot

### 1. INPUT PULSE GENERATOR: 500kHz; 50% $\pm$ 5% DUTY CYCLE; $t_R, t_F \leq$ 1ns. 2. MEASURED ON TEST EQUIPMENT WITH –3dB BANDWIDTH $\geq$ 1GHz.

Figure 28. Driver Enable/Disable Times

200Mbps; 2<sup>15</sup> – 1PRBS. 2. MEASURED USING TEK TDS6604 WITH TDSJIT3 SOFTWARE.

Figure 29. Driver Peak-to-Peak Jitter Characteristics

0355

#### **RECEIVER TIMING MEASUREMENTS**

2. MEASURED USING TEK TDS6604 WITH TDSJIT3 SOFTWARE.

Figure 35. Receiver Peak-to-Peak Jitter Characteristics

# THEORY OF OPERATION

The ADN4691E/ADN4693E/ADN4696E/ADN4697E are transceivers for transmitting and receiving multipoint, low voltage differential signaling (M-LVDS) at high speed (data rates up to 200 Mbps). Each device has a differential line driver and a differential line receiver, allowing each device to send and receive data.

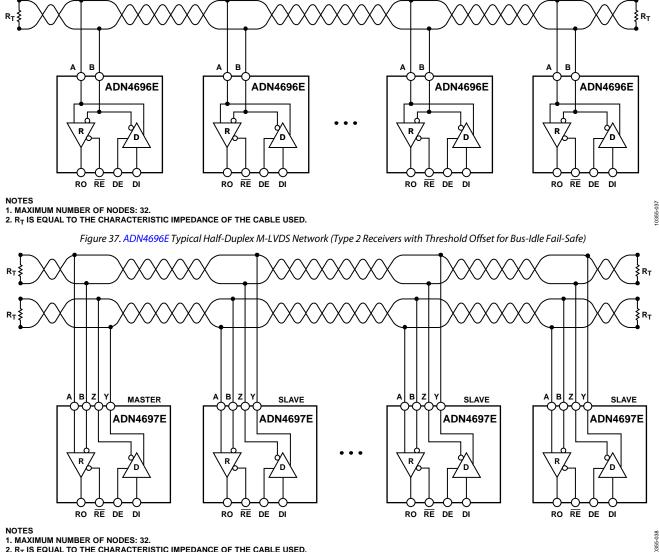

Multipoint LVDS expands on the established LVDS low voltage differential signaling method by allowing bidirectional communication between more than two nodes. Up to 32 nodes can connect on an M-LVDS bus.

### HALF-DUPLEX/FULL-DUPLEX OPERATION

Half-duplex operation allows a transceiver to transmit or receive, but not both at the same time. However, with fullduplex operation, a transceiver can transmit and receive simultaneously. The ADN4691E/ADN4696E are half-duplex devices in which the driver and the receiver share differential bus terminals. The ADN4693E/ADN4697E are full-duplex devices that have dedicated driver output and receiver input pins. Figure 37 and Figure 38 show typical half- and full-duplex bus topologies, respectively, for M-LVDS.

### THREE-STATE BUS CONNECTION

The outputs of the device can be placed in a high impedance state by disabling the driver or receiver. This allows several driver outputs to connect to a single M-LVDS bus. Note that, on each bus line, only one driver can be enabled at a time, but many receivers can be enabled at the same time.

The driver can be enabled or disabled using the driver enable pin (DE). DE enables the driver outputs when taken high; when taken low, DE puts the driver outputs into a high impedance state. Similarly, an active low receiver enable pin  $(\overline{RE})$  controls the receiver. Taking  $\overline{RE}$  low enables the receiver, whereas taking it high puts the receiver outputs into a high impedance state.

Truth tables for driver and receiver output states under various conditions are shown in Table 10, Table 11, Table 12, and Table 13.

### **TRUTH TABLES**

#### Table 9. Truth Table Abbreviations

| Abbreviation | Description          |

|--------------|----------------------|

| Н            | High level           |

| L            | Low level            |

| Х            | Don't care           |

| I            | Indeterminate        |

| Z            | High impedance (off) |

| NC           | Disconnected         |

### Driver, Half-Duplex (ADN4691E/ADN4696E)

#### Table 10. Transmitting (See Table 9 for Abbreviations)

|        |    | Inputs |   | Outputs |  |

|--------|----|--------|---|---------|--|

| Power  | DE | DI     | Α | В       |  |

| Yes    | Н  | Н      | Н | L       |  |

| Yes    | н  | L      | L | н       |  |

| Yes    | Н  | NC     | L | н       |  |

| Yes    | L  | х      | Z | Z       |  |

| Yes    | NC | х      | Z | Z       |  |

| ≤1.5 V | Х  | Х      | Z | Z       |  |

#### Driver, Full-Duplex (ADN4693E/ADN4697E)

|        | Inputs |    |   | Outputs | outs |

|--------|--------|----|---|---------|------|

| Power  | DE     | DI | Y | Z       |      |

| Yes    | Н      | н  | Н | L       |      |

| Yes    | Н      | L  | L | Н       |      |

| Yes    | Н      | NC | L | н       |      |

| Yes    | L      | х  | Z | Z       |      |

| Yes    | NC     | х  | Z | Z       |      |

| ≤1.5 V | Х      | Х  | Z | Z       |      |

#### Type 1 Receiver (ADN4691E/ADN4693E)

#### Table 12. Receiving (see Table 9 for Abbreviations)

|       | Inputs                 | Output |    |

|-------|------------------------|--------|----|

| Power | A – B                  | RE     | RO |

| Yes   | ≥50 mV                 | L      | Н  |

| Yes   | ≤–50 mV                | L      | L  |

| Yes   | –50 mV < A – B < 50 mV | L      | I  |

| Yes   | NC                     | L      | I  |

| Yes   | Х                      | н      | Z  |

| Yes   | Х                      | NC     | Z  |

| No    | Х                      | Х      | Z  |

#### Type 2 Receiver (ADN4696E/ADN4697E)

| Table 13. Receiving | (See Table 9 for Abbreviations) |

|---------------------|---------------------------------|

|---------------------|---------------------------------|

|       | Inputs                 | Output |    |

|-------|------------------------|--------|----|

| Power | A – B                  | RE     | RO |

| Yes   | ≥150 mV                | L      | Н  |

| Yes   | ≤50 mV                 | L      | L  |

| Yes   | 50 mV < A – B < 150 mV | L      | I  |

| Yes   | NC                     | L      | L  |

| Yes   | X                      | н      | Z  |

| Yes   | Х                      | NC     | Z  |

| No    | X                      | х      | Z  |

#### **GLITCH-FREE POWER-UP/POWER-DOWN**

To minimize disruption to the bus when adding nodes, the M-LVDS outputs of the device are kept glitch-free when the device is powering up or down. This feature allows insertion of devices onto a live M-LVDS bus because the bus outputs are not switched on before the device is fully powered. In addition, all outputs are placed in a high impedance state when the device is powered off.

### **FAULT CONDITIONS**

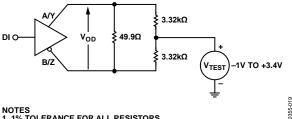

The ADN4691E/ADN4693E/ADN4696E/ADN4697E contain short-circuit current protection that protects the device under fault conditions in the case of short circuits on the bus. This protection limits the current in a fault condition to 24 mA at the transmitter outputs for short-circuit faults between –1 V and 3.4 V. Any network fault must clear to avoid data transmission errors and to ensure reliable operation of the data network and any devices that are connected to the network.

### **RECEIVER INPUT THRESHOLDS/FAIL-SAFE**

Two receiver types are available, both of which incorporate protection against short circuits.

The Type 1 receivers of the ADN4691E/ADN4693E incorporate 25 mV of hysteresis. This ensures that slow changing signals or a loss of input does not result in oscillation of the receiver output. Type 1 receiver thresholds are  $\pm 50$  mV; therefore, the state of the receiver output is indeterminate if the differential between A and B is about 0 V. This state occurs if the bus is idle (approximately 0 V on both A and B), with no drivers enabled on the attached nodes.

Type 2 receivers (ADN4696E/ADN4697E) have an open circuit and bus-idle fail-safe. The input threshold is offset by 100 mV so a logic low is present on the receiver output when the bus is idle or when the receiver inputs are open.

The different receiver thresholds for the two receiver types are illustrated in Figure 36. See Table 12 and Table 13 for receiver output states under various conditions.

Figure 36. Input Threshold Voltages

## APPLICATIONS INFORMATION

M-LVDS extends the low power, high speed, differential signaling of low voltage differential signaling (LVDS) to multipoint systems where multiple nodes are connected over short distances in a bus topology network.

With M-LVDS, a transmitting node drives a differential signal across a transmission medium such as a twisted pair cable. The transmitted differential signal allows other receiving nodes that are connected along the bus to detect a differential voltage that can then be converted back into a single-ended logic signal by the receiver.

The communication line is typically terminated at both ends by resistors  $(R_T)$ , the value of which is chosen to match the characteristic impedance of the medium (typically  $100 \Omega$ ).

For half-duplex multipoint applications such as the one shown in Figure 37, only one driver can be enabled at any time. Fullduplex nodes allow a master-slave topology as shown in Figure 38. In this configuration, a master node can concurrently send and receive data to/from slave nodes. At any time, only one slave node can have a driver enabled to concurrently transmit data back to the master node.

2. RT IS EQUAL TO THE CHARACTERISTIC IMPEDANCE OF THE CABLE USED.

Figure 38. ADN4697E Typical Full-Duplex M-LVDS Master-Slave Network (Type 2 Receivers with Threshold Offset for Bus-Idle Fail-Safe)

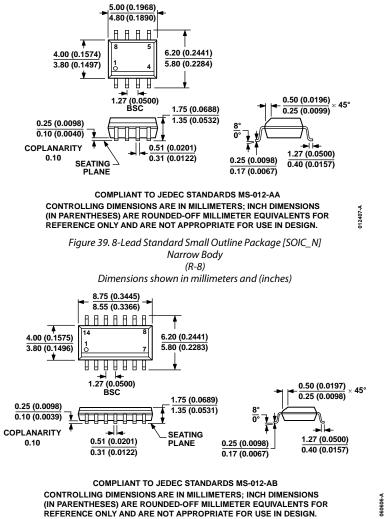

### **OUTLINE DIMENSIONS**

Figure 40. 14-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-14) Dimensions shown in millimeters and (inches)

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                                  | Package Option |

|--------------------|-------------------|------------------------------------------------------|----------------|

| ADN4691EBRZ        | -40°C to +85°C    | 8-Lead Standard Small Outline Package (SOIC_N)       | R-8            |

| ADN4691EBRZ-RL7    | –40°C to +85°C    | 8-Lead Standard Small Outline Package (SOIC_N)       | R-8            |

| ADN4693EBRZ        | -40°C to +85°C    | 14-Lead Standard Small Outline Package (SOIC_N)      | R-14           |

| ADN4693EBRZ-RL7    | -40°C to +85°C    | 14-Lead Standard Small Outline Package (SOIC_N)      | R-14           |

| ADN4696EBRZ        | -40°C to +85°C    | 8-Lead Standard Small Outline Package (SOIC_N)       | R-8            |

| ADN4696EBRZ-RL7    | -40°C to +85°C    | 8-Lead Standard Small Outline Package (SOIC_N)       | R-8            |

| ADN4697EBRZ        | –40°C to +85°C    | 14-Lead Standard Small Outline Package (SOIC_N)      | R-14           |

| ADN4697EBRZ-RL7    | -40°C to +85°C    | 14-Lead Standard Small Outline Package (SOIC_N)      | R-14           |

| EVAL-ADN469xEHDEBZ |                   | Evaluation Board for Half-Duplex (ADN4691E/ADN4696E) |                |

| EVAL-ADN469xEFDEBZ |                   | Evaluation Board for Full-Duplex (ADN4693E/ADN4697E) |                |

<sup>1</sup> Z = RoHS Compliant Part.

# NOTES

# NOTES

### NOTES

www.analog.com

Downloaded from Arrow.com.