# **TABLE OF CONTENTS**

| A <sup>2</sup> B Bus Features                                                                      |

|----------------------------------------------------------------------------------------------------|

| A <sup>2</sup> B Transceiver Features                                                              |

| Applications                                                                                       |

| Table of Contents                                                                                  |

| Revision History                                                                                   |

| General Description                                                                                |

| A <sup>2</sup> B Bus Details                                                                       |

| I <sup>2</sup> C Interface                                                                         |

| I <sup>2</sup> S/TDM Interface                                                                     |

| Pulse Density Modulation (PDM) Interface                                                           |

| GPIO Over Distance                                                                                 |

| Mailboxes                                                                                          |

| Data Slot Exchange Between Slaves                                                                  |

| Clock Sustain State                                                                                |

| Programmable Settings to Optimize EMC Performance                                                  |

| Specifications {                                                                                   |

| Operating Conditions                                                                               |

| Electrical Characteristics                                                                         |

| Power Supply Rejection Ratio (PSRR)                                                                |

| Timing Specifications                                                                              |

| Power-Up Sequencing Restrictions 16                                                                |

| A <sup>2</sup> B Bus System Specification                                                          |

| PDM Typical Performance Characteristics 18                                                         |

| Absolute Maximum Ratings 20                                                                        |

| Thermal Characteristics                                                                            |

| REVISION HISTORY                                                                                   |

| 7/2021—Rev. B to Rev. C                                                                            |

| Removed references to ambient temperature in:  Operating Conditions                                |

| Added statement on specification applicability to:  Operating Conditions                           |

| Added $I_{BUSDISC}$ and $C_{BUSDISC}$ specifications to  A <sup>2</sup> B Bus System Specification |

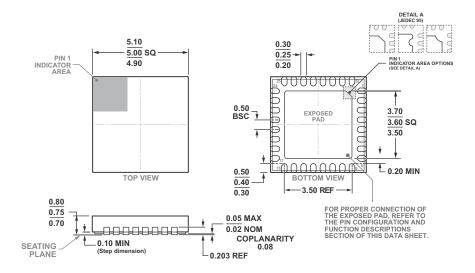

| Updated Figure 39 in Outline Dimensions                                                            |

| Changes to the Package Option column in                                                            |

| Automotive Products                                                                                |

| ESD Caution                                                          | 2]  |

|----------------------------------------------------------------------|-----|

| Test Circuits and Switching Characteristics                          | 2]  |

| Output Drive Currents                                                | 2]  |

| Test Conditions                                                      | 22  |

| Pin Configuration and Function Descriptions 2                        | 24  |

| Power Analysis                                                       | 28  |

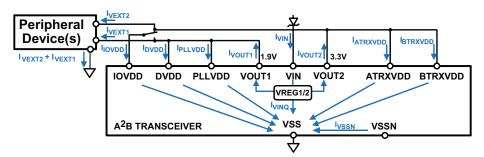

| Current Flow                                                         | 28  |

| VREG1 and VREG2 Output Currents                                      | 29  |

| Current at VIN (I <sub>VIN</sub> )                                   | 3(  |

| Power Dissipation                                                    | 3(  |

| Resistance Between Nodes                                             | 3(  |

| Voltage Regulator Current in Master Node or Local Powered Slave Node | 31  |

| Power Dissipation of A <sup>2</sup> B Bus                            | 3]  |

| Power Analysis of Bus Powered System                                 | 3 ] |

| Supply Voltage                                                       | 31  |

| Reducing Power Consumption                                           | 32  |

| Thermal Power                                                        | 32  |

| Designer Reference                                                   | 33  |

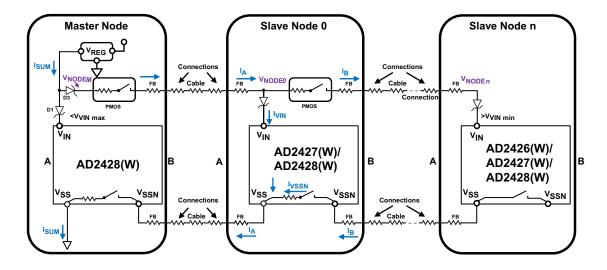

| V <sub>SENSE</sub> and Considerations for Diodes                     | 33  |

| Optional Add On Circuits                                             | 33  |

| Layout Guidelines                                                    | 34  |

| Outline Dimensions                                                   | 36  |

| Automotive Products                                                  | 37  |

| Ordering Guide                                                       | 38  |

|                                                                      |     |

# **GENERAL DESCRIPTION**

The Automotive Audio Bus  $(A^2B^{\$})$  provides a multichannel,  $I^2S/TDM$  link over distances of up to 15 m between nodes. It embeds bidirectional synchronous pulse-code modulation (PCM) data (for example, digital audio), clock, and synchronization signals onto a single differential wire pair.  $A^2B$  supports a direct point to point connection and allows multiple, daisy-chained nodes at different locations to contribute and/or consume time division multiplexed (TDM) channel content.

$A^2B$  is a single-master, multiple-slave system where the transceiver at the host controller is the master. The master generates clock, synchronization, and framing for all slave nodes. The master  $A^2B$  transceiver is programmable over a control port (I^2C) for configuration and read back. An extension of the control port protocol is embedded in the  $A^2B$  data stream, which grants direct access of registers and status information on slave transceivers as well as  $\rm I^2C$  to  $\rm I^2C$  communication over distance.

The transceiver can connect directly to general-purpose digital signal processors (DSPs), field-programmable gate arrays (FPGAs), application specific integrated circuits (ASICs), microphones, analog-to-digital converters (ADCs), digital-to-analog converters (DACs), and codecs through a multichannel I²S/TDM interface. It also provides a pulse density modulation (PDM) interface for direct connection of up to four PDM digital microphones.

Finally, the transceiver also supports an A<sup>2</sup>B bus powering feature, where the master node supplies voltage and current to the slave nodes over the same daisy-chained, twisted pair wire cable as used for the communication link.

Table 1. Product Comparison Guide

| Feature                                    | AD2420/             | AD2426/ | AD2427/ | AD2428/  | AD2429/ |

|--------------------------------------------|---------------------|---------|---------|----------|---------|

|                                            | AD2420W             | AD2426W | AD2427W | AD2428W  | AD2429W |

| Master capable                             | No                  | No      | No      | Yes      | Yes     |

| Number of slaves discoverable <sup>1</sup> | N/A                 | N/A     | N/A     | Up to 10 | Up to 2 |

| Functional TRX blocks                      | A only              | A only  | A + B   | A + B    | B only  |

| I <sup>2</sup> S/TDM support               | No                  | No      | No      | Yes      | Yes     |

| PDM microphone inputs                      | 2 mics <sup>2</sup> | 4 mics  | 4 mics  | 4 mics   | 4 mics  |

| Max node to node cable length              | 5 m                 | 15 m    | 15 m    | 15 m     | 5 m     |

<sup>&</sup>lt;sup>1</sup>N/A means not applicable.

<sup>&</sup>lt;sup>2</sup>PDM microphones must be connected to the DRX0/IO5 pin.

### A<sup>2</sup>B BUS DETAILS

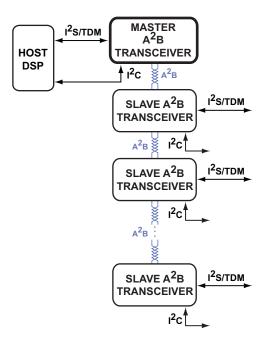

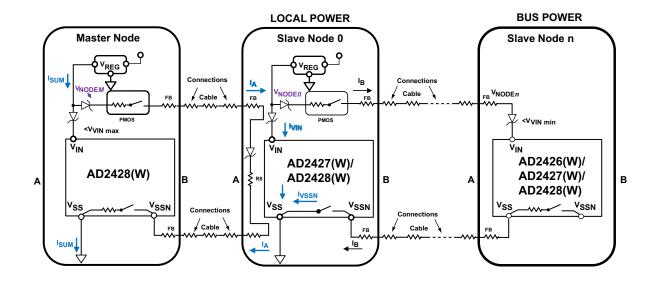

Figure 2 shows a single-master, multiple-slave A<sup>2</sup>B communications system with the master transceiver controlled by the host. The host generates a periodic synchronization signal on the I<sup>2</sup>S/TDM interface at a fixed frequency (typically 48 kHz) to which all A<sup>2</sup>B nodes synchronize.

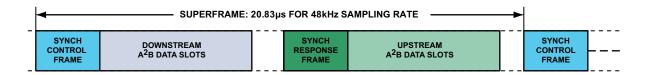

Communications along the A<sup>2</sup>B bus occur in periodic superframes. The superframe frequency is the same as the synchronization signal frequency, and data is transferred at a bit rate that is 1024 times faster (typically 49.152 MHz). Each superframe is divided into periods of downstream transmission, upstream transmission, and no transmission (where the bus is not driven). Data is exchanged over the A<sup>2</sup>B bus in up to 32 equal width slots for both upstream and downstream transmissions.

The A<sup>2</sup>B bus also communicates the following control and status information between nodes:

- I<sup>2</sup>C to I<sup>2</sup>C communication

- General-purpose input/output (GPIO)

- Interrupts

Figure 2. Communication System Block Diagram

In Figure 3, a superframe is shown with an initial period of downstream transmission and a later period of upstream transmission.

All signals on the A<sup>2</sup>B bus are line coded, and the master node forwards the synchronization signal downstream from the master transceiver to the last slave node transceiver in the form of a synchronization preamble. This preamble is followed by control data to build a synchronization control frame (SCF). Downstream, TDM synchronous data is added directly after the

control frame. Every slave can use or consume some of the downstream data and add data for downstream nodes. The last slave node transceiver responds after the response time with a synchronization response frame (SRF). Upstream synchronous data is added by each node directly after the response frame. Each node can also use or consume upstream data.

The embedded control and response frames allow the host to individually address each slave transceiver in the system. The host also enables access to remote peripheral devices that are connected to the slave transceivers via the  $\rm I^2C$  or SPI ports for  $\rm I^2C$  to  $\rm I^2C$  communication over distance between multiple nodes.

All nodes in an A<sup>2</sup>B system are sampled synchronously in the same A<sup>2</sup>B superframe. Synchronous I<sup>2</sup>S/TDM downstream data from the master arrives at all slaves in the same A<sup>2</sup>B superframe, and the upstream audio data of every node arrives synchronously in the same I<sup>2</sup>S/TDM frame at the master. The remaining audio phase differences between slaves can be compensated for by register-programmable fine adjustment of the SYNC pin signal delay.

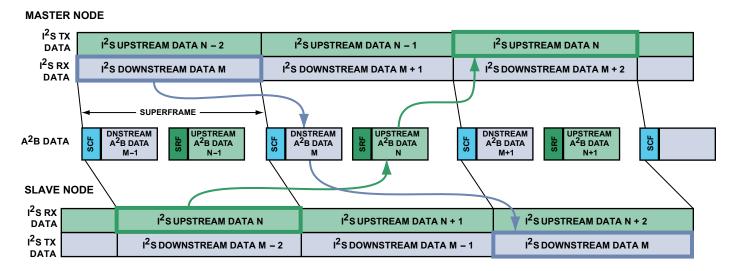

There is a sample delay incurred for data moving between the A<sup>2</sup>B bus and the I<sup>2</sup>S/TDM interfaces because data is received and transmitted over the I<sup>2</sup>S/TDM every sample period (typically 48 kHz). This timing relationship between samples over the A<sup>2</sup>B bus is shown in Figure 4.

Note in Figure 4, both downstream and upstream samples are named for the frame where they enter the A<sup>2</sup>B system as follows:

- Data transmitted by the master node transceiver in Superframe M creates Downstream Data M.

- Data transmitted by the slave node transceivers in Superframe N creates Upstream Data N.

- Data received over the I<sup>2</sup>S/TDM interface by the A<sup>2</sup>B transceiver is transmitted over the A<sup>2</sup>B bus in the next superframe.

- Data on the A<sup>2</sup>B bus is transmitted over the I<sup>2</sup>S/TDM interface of an A<sup>2</sup>B transceiver in the next superframe.

- Data transmitted across the A<sup>2</sup>B bus (master to slave or slave to master) has two frames of latency plus any internal delay that has accumulated in the transceivers as well as delays due to wire length. Therefore, overall latency is slightly over two samples (<50 µs at 48 kHz sample periods) from the I<sup>2</sup>S/TDM interface in one A<sup>2</sup>B transceiver to the I<sup>2</sup>S/TDM interface of another A<sup>2</sup>B transceiver.

To support and extend the A<sup>2</sup>B bus functions and performance, the transceivers have additional features, as described in the following sections.

Figure 3. A<sup>2</sup>B Superframe

Figure 4. A<sup>2</sup>B Bus Synchronous Data Exchange

## I<sup>2</sup>C INTERFACE

The  $I^2C$  interface in the transceiver provides access to the internal registers. Operation is not guaranteed above the  $V_{I2C\_VBUS}$  specification. The  $I^2C$  interface has the following features:

- Slave functionality in the A<sup>2</sup>B master

- Master or slave functionality in the A<sup>2</sup>B slave

- Multimaster support in the A<sup>2</sup>B slave

- 100 kbps or 400 kbps rate operation

- 7-bit addressing

- · Single-word and burst mode read and write operations

- Clock stretching

All transceivers can be accessed by a locally connected processor using the 7-bit  $I^2C$  device address (BASE\_ADDR) established by the logic levels applied to the ADR2/IO2 and ADR1/IO1 pins at power-on reset, thus providing for up to four master devices connecting to the same  $I^2C$  bus. A slave configured transceiver recognizes only this  $I^2C$  device address. A master configured transceiver, however, also recognizes a second  $I^2C$  device address for remote access to slave nodes over the  $A^2B$  bus (BUS\_ADDR). The least significant bit (LSB) of the 7-bit device address determines whether an  $I^2C$  data exchange uses the BASE\_ADDR (Bit I=0) to access the transceiver or

BUS\_ADDR (Bit 1=1) to access a bus node slave transceiver through a master configured AD2425W transceiver. See the AD2420(W)/6(W)/7(W)/8(W)/9(W) Automotive Audio Bus  $A^2B$  Transceiver Technical Reference for details.

## I<sup>2</sup>S/TDM INTERFACE

The I<sup>2</sup>S/TDM serial port operates in full-duplex mode, where both the transmitter and receiver operate simultaneously using the same critical timing bit clock (BCLK) and synchronization (SYNC) pins. A<sup>2</sup>B slave transceivers generate the timing signals on the BCLK and SYNC output pins. A<sup>2</sup>B master transceivers use the same BCLK and SYNC pins as inputs, which are driven by the host device. The I<sup>2</sup>S/TDM port includes the following features:

- Programmable clock and frame sync timing and polarity

- Numerous TDM operating modes

- 16- or 32-bit data width

- Simultaneous operation with PDM port

- Single- or dual-pin input/output (I/O)

## I<sup>2</sup>S Reduced Rate

Slave transceivers can run the I<sup>2</sup>S/TDM/PDM interface at a reduced rate frequency, with respect to the superframe rate. The reduced rate frequency is derived by dividing the superframe rate from a programmable set of values. Different slave nodes can be configured to run at different reduced I<sup>2</sup>S/TDM rates.

The transceiver provides an option for a processor to track the full rate audio frame, which contains new reduced rate samples. The IO7 pin can be used as a strobe, and the direction can be configured as an input or output.

## PULSE DENSITY MODULATION (PDM) INTERFACE

The PDM block on the transceiver converts a PDM input stream into pulse code modulated (PCM) data to be sent over the A²B bus and/or out to the local node through the I²S/TDM port. It supports high dynamic range microphones with high signal-to-noise ratio (SNR) and extended maximum sound pressure level. The PDM interface supports 12 kHz and 24 kHz frame rates in addition to a 48 kHz frame rate and can be used on both master and slave transceivers.

Even lower PDM sampling rates (for example, down to 375 Hz) are possible in combination with the reduced rate feature of the transceiver. The cutoff frequency of the high-pass filter in the transceiver PDM block is fixed to 1 Hz.

BCLK can be used to clock PDM microphones on a slave, but if PDMCLK/IO7 is used instead, the BCLK frequency can be set to a different frequency using the I<sup>2</sup>S/TDM registers. In this case, PDMCLK/IO7 is used as the PDM clock (PDMCLK) to capture PDM input on DRX0/DRX1. The clock rate from PDMCLK is 64× the SYNC frequency.

On a master node, BCLK is always an input, so the clock to PDM microphones that are attached to a master typically comes from PDMCLK/IO7. It is possible to use BCLK to drive the PDM clock inputs on a master node, but this restricts the possible TDM settings because BCLK is required to fall within the  $f_{\rm BCLK}$  specification in Table 4.

BCLK and PDMCLK/IO7 can also be used concurrently to clock PDM microphones at the same frequency and phase alignment, but with opposite polarity. Additionally, a register setting selects whether rising edge data or falling edge data is sampled first.

#### **GPIO OVER DISTANCE**

The transceiver supports general-purpose input/output (GPIO) between multiple nodes without host intervention after initial programming. The host is required only for initial setup of the GPIO bus ports. I/O pins of different nodes can be logically OR or AND gate combined.

## **MAILBOXES**

The transceiver supports interrupt driven, bidirectional message exchange between I<sup>2</sup>C master devices (microcontrollers) at different slave nodes and the host connected to the master node transceiver in two dedicated mailboxes. The mailboxes can be

used to customize handshaking among numerous nodes in a system to coordinate system events, such as synchronizing audio.

#### **DATA SLOT EXCHANGE BETWEEN SLAVES**

Using the DTX0 and DTX1 pins, slave transceivers can selectively output upstream or downstream data that originates from other nodes without the need for data slots to be routed through the master node. Receive data channels can be skipped based on a programmable offset, when the data is presented as upstream or downstream slots to the  $\rm A^2B$  bus.

### **CLOCK SUSTAIN STATE**

In the clock sustain state, audio signals of locally powered slave nodes are attenuated in the event of lost bus communication. When the bus loses communication and a reliable clock cannot be recovered by the slave node, the slave node transceiver enters the sustain state and, if enabled, signals this event to a GPIO pin.

In the clock sustain state, the phase-locked loop (PLL) of the slave node transceiver continues to run for 1024 SYNC periods, while attenuating the I<sup>2</sup>S DTX0 to DTX1 data from the current value to 0. After the 1024 SYNC periods, the slave node transceiver resets and reenters the power-up state.

# PROGRAMMABLE SETTINGS TO OPTIMIZE EMC PERFORMANCE

The following programmable features can be used to improve electromagnetic compatibility (EMC) performance.

### **Programmable LVDS Transmit Levels**

The low voltage differential signal (LVDS) transmitter can be set to transmit the signal at high, medium, or low levels. Higher transmit levels yield greater immunity to EMI, whereas lower transmit levels can reduce emissions from the twisted-pair cables that link A<sup>2</sup>B bus nodes together. The improved LVDS receiver (compared to other members of the AD242xW family) maintains robust operation when transmit levels are lowered.

## Spread-Spectrum Clocking

Spread-spectrum clocking can be used to reduce narrow-band emissions on a printed circuit board (PCB). Spread-spectrum clocking is disabled on the transceiver by default, but spread-spectrum clocking for all internal clocks can be enabled during discovery by a register write.

If spread-spectrum clocking support is enabled for the internal clocks, spread-spectrum clocking can also be enabled for both the  $\rm I^2S$  interface and the programmed CLKOUTs. Enabling spread-spectrum clocking for internal clocks, CLKOUTs, and the  $\rm I^2S$  interface may reduce narrow-band emissions by several dB on a particular node. When spread-spectrum clocking is enabled on a clock output, the time interval error (TIE) jitter on that clock increases.

## **Unique ID**

Each transceiver contains a unique ID, which can be read from registers using software. If a read of the unique ID fails, an interrupt can be generated.

## Support for Crossover or Straight Through Cabling

Straight through cables can be supported by swapping the dc coupling at the B-side connector. See the Designer Reference section for details about the reference schematics.

## **Data Only and Power Only Bus Operation**

The A<sup>2</sup>B bus can be operated without closing the PMOS switch to send a dc bias downstream. Conversely, a dc bias can also be sent downstream without the presence of data. These features are available for debug purposes only.

# **SPECIFICATIONS**

Specifications are subject to change without notice. For information about product specifications, contact your Analog Devices, Inc. representative.

# **OPERATING CONDITIONS**

All specifications and characteristics apply across the entire operating conditions range unless otherwise noted.

| Parameter         |                                                            | Conditions                                                                        | Min                    | Nominal | Max                    | Unit |

|-------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------|---------|------------------------|------|

| Power Suppl       | lies                                                       |                                                                                   |                        |         |                        |      |

| $V_{DVDD}$        | Digital Core Logic Supply Voltage                          |                                                                                   | 1.70                   | 1.90    | 1.98                   | V    |

| $V_{IOVDD}$       | Digital Input/Output (I/O) Supply<br>Voltage               | 3.3 V I/O                                                                         | 3.0                    | 3.3     | 3.63                   | V    |

|                   |                                                            | 1.8 V I/O                                                                         | 1.7                    | 1.9     | 1.98                   | V    |

| $V_{PLLVDD}$      | Phased-Locked Loops (PLL) Supply<br>Voltage                |                                                                                   | 1.7                    | 1.9     | 1.98                   | V    |

| $V_{TRXVDD}$      | Transceiver Supply Voltage                                 | Applies to the ATRXVDD and BTRXVDD pins                                           | 3.0                    | 3.3     | 3.63                   | V    |

| $V_{I2C\_VBUS}$   | External I <sup>2</sup> C Bus Voltage                      | 3.3 V V <sub>IOVDD</sub> , 1.8 V V <sub>IOVDD</sub>                               | 1.7                    | 1.9/3.3 | 3.63                   | V    |

| Voltage Reg       | ulator (VREG1, VREG2)                                      |                                                                                   |                        |         |                        |      |

| $V_{VIN}$         | Regulator Input Supply Voltage                             | Specification must be met at the VIN pin of each A <sup>2</sup> B bus transceiver | 3.7                    |         | 9.0                    | V    |

| $V_{RST}$         | V <sub>VIN</sub> Chip Reset Assertion Voltage<br>Threshold | V <sub>VIN</sub> dropping                                                         | 2.65                   |         | 2.97                   | V    |

| $V_{RSTN}$        | $V_{\text{VIN}}$ Chip Reset Deassertion Voltage Threshold  | V <sub>VIN</sub> rising                                                           | 3.11                   |         | 3.25                   | V    |

| Digital I/O       |                                                            |                                                                                   |                        |         |                        |      |

| $V_{IH}^{-1}$     | High Level Input Voltage                                   | V <sub>IOVDD</sub> = 1.98 V                                                       | $0.7 \times V_{IOVDD}$ |         |                        | V    |

|                   |                                                            | V <sub>IOVDD</sub> = 3.63 V                                                       | 2.2                    |         |                        | V    |

| $V_{IL}^{1}$      | Low Level Input Voltage                                    | $V_{IOVDD} = 1.70 \text{ V}$                                                      |                        |         | $0.3 \times V_{IOVDD}$ | V    |

|                   |                                                            | $V_{IOVDD} = 3.00 \text{ V}$                                                      |                        |         | 0.8                    | V    |

| $V_{IH\_I2C}^{2}$ |                                                            | V <sub>IOVDD</sub> = 3.63 V, 1.98 V                                               | $0.7 \times V_{IOVDD}$ |         |                        | V    |

| $V_{IL\_I2C}$     |                                                            | $V_{IOVDD} = 3.00 \text{ V}, 1.70 \text{ V}$                                      |                        |         | $0.3 \times V_{IOVDD}$ | V    |

| CONSUMER          | GRADE                                                      |                                                                                   |                        |         |                        |      |

| TJ                | Junction Temperature                                       |                                                                                   | 0                      |         | 105                    | °C   |

| INDUSTRIAL        | _ GRADE                                                    |                                                                                   |                        |         |                        |      |

| T <sub>J</sub>    | Junction Temperature                                       |                                                                                   | -40                    |         | +105                   | °C   |

| AUTOMOTIN         | /E GRADE <sup>3</sup>                                      |                                                                                   |                        |         |                        |      |

| T <sub>J</sub>    | Junction Temperature                                       |                                                                                   | -40                    |         | +125                   | °C   |

| 1. 1              | MOLIZIOT BOLIZ CVNG DTV0/IO2 DTV1                          | TO L DRIVETO - DRIVETO C LDRIVE LDRIVE - T                                        | 0/100                  |         |                        |      |

$<sup>^{1}</sup> Applies \ to \ PDMCLK/IO7, BCLK, SYNC, DTX0/IO3, DTX1/IO4, DRX0/IO5, DRX1/IO6, ADR1/IO1, ADR2/IO2, IRQ/IO0\ pins.$

<sup>&</sup>lt;sup>2</sup> Applies to SDA and SCL pins.

<sup>&</sup>lt;sup>3</sup> Automotive application use profile only. Not supported for nonautomotive use. Contact Analog Devices for more information.

## **ELECTRICAL CHARACTERISTICS**

All specifications and characteristics apply across the entire operating conditions range unless otherwise noted.

| Parameter                           |                                           | Conditions                                                                                                                | Min    | Тур    | Max    | Unit |

|-------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|------|

| Current                             |                                           |                                                                                                                           |        |        |        |      |

| $I_{\text{DVDD}}$                   | Digital Core Logic Supply Current         | $V_{DVDD} = 1.98 V$                                                                                                       | 9.0    | 10.5   | 12.0   | mA   |

| I <sub>PLLVDD</sub>                 | PLL Supply Current                        | $V_{PLLVDD} = 1.98 V$                                                                                                     | 0.5    | 1.1    | 1.5    | mA   |

| I <sub>TRXVDD</sub> <sup>1</sup>    | Transceiver Supply Current                | TX enabled, RX disabled, 100% duty cycle                                                                                  | 9.5    | 12.0   | 13.0   | mA   |

|                                     |                                           | $(I_{TXVDD}), V_{TRXVDD} = 3.63 \text{ V}$                                                                                |        |        |        |      |

|                                     |                                           | TX disabled, RX enabled, 100% duty cycle                                                                                  | 2.2    | 2.8    | 3.5    | mA   |

|                                     |                                           | $(I_{RXVDD}), V_{TRXVDD} = 3.63 V$                                                                                        |        |        |        |      |

|                                     |                                           | TX disabled, RX disabled, 0% activity level,                                                                              | 1.0    | 1.7    | 2.5    | mA   |

|                                     |                                           | $V_{TRXVDD} = 3.63 \text{ V}$                                                                                             |        |        |        |      |

| Voltage Regul                       | ator (VREG1, VREG2)                       |                                                                                                                           |        |        |        |      |

| $V_{VOUT1}$                         | V <sub>REG1</sub> Output Voltage          |                                                                                                                           | 1.80   | 1.90   | 1.98   | V    |

| $V_{\text{VOUT2}}$                  | V <sub>REG2</sub> Output Voltage          |                                                                                                                           | 3.15   | 3.30   | 3.45   | V    |

| I <sub>VOUT1</sub> <sup>2</sup>     | V <sub>REG1</sub> Output Current          |                                                                                                                           |        |        | 40.0   | mA   |

| I <sub>VOUT2</sub> <sup>2</sup>     | V <sub>REG2</sub> Output Current          |                                                                                                                           |        |        | 50.0   | mA   |

| I <sub>VEXT1</sub> <sup>3, 4</sup>  | V <sub>REG1</sub> External Device Current | I <sub>VOUT1</sub> – I <sub>PLLVDD</sub> – I <sub>DVDD</sub> – I <sub>IOVDD</sub> current<br>available to external device |        | 20     |        | mA   |

| I <sub>VEXT2</sub> 3, 4             | V <sub>REG2</sub> External Device Current | $I_{VOUT2} - I_{TRXVDD}$ current available to external                                                                    |        | 20     |        | mA   |

| VEXT2                               | V REG2 External Device Current            | device                                                                                                                    |        | 20     |        |      |

| $\Delta V_{OUT1}/\Delta V_{IN}$     | Line Regulation                           | $V_{VIN} = 3.7 \text{ V to VIN}$                                                                                          | 0      | 0.017  | 0.055  | %/V  |

| $\Delta V_{OUT2}/\Delta V_{IN}$     | Line Regulation                           | $V_{VIN} = 3.7 \text{ V to VIN}$                                                                                          | 0.013  | 0.030  | 0.060  | %/V  |

|                                     |                                           | V <sub>VIN</sub> = 5.0 V to 8 V                                                                                           | -0.025 | +0.005 | +0.055 | %/V  |

| $\Delta V_{OUT1}/\Delta I_{OUT1}$   | Load Regulation                           | $V_{VIN} = 5.0 \text{ V}, I_{VOUT1} = 1 \text{ mA to } 40 \text{ mA}$                                                     |        | 0.009  | 0.017  | %/mA |

| $\Delta V_{OUT2}/\Delta I_{OUT2}$   | Load Regulation                           | $V_{VIN} = 5.0 \text{ V}, I_{VOUT2} = 1 \text{ mA to } 50 \text{ mA}$                                                     |        | 0.008  | 0.015  | %/mA |

| I <sub>VINQ</sub>                   | Quiescent Current                         | $V_{VIN} = V_{IN}$ , $I_{VOUT1} = 0$ mA, $I_{VOUT2} = 0$ mA                                                               | 530    | 600    | 750    | μΑ   |

| I <sub>VIN</sub>                    | Operational Current                       | $V_{VIN} = V_{IN}$ , $I_{VOUT1} = 8$ mA, $I_{VOUT2} = 20$ mA                                                              |        |        | 29     | mA   |

| $C_{Load1}$                         | V <sub>REG1</sub> Load Capacitance        |                                                                                                                           | 1.0    |        | 25     | μF   |

| $C_{Load2}$                         | V <sub>REG2</sub> Load Capacitance        |                                                                                                                           | 2.2    |        | 25     | μF   |

| Digital I/O                         |                                           |                                                                                                                           |        |        |        |      |

| I <sub>IH</sub>                     | Input Leakage, High                       | $V_{IOVDD} = 3.63 \text{ V}, V_{IN} = 3.63 \text{ V}$                                                                     |        |        | 10.0   | μΑ   |

| $I_{\rm IL}$                        | Input Leakage, Low                        | $V_{IOVDD} = 3.63 \text{ V}, V_{IN} = 0 \text{ V}$                                                                        |        |        | 10.0   | μΑ   |

| l <sub>OZH_I2C</sub> <sup>5</sup>   | Three-State Leakage Current               | $V_{IOVDD} = 1.9 \text{ V}, V_{IN} = 3.63 \text{ V}$                                                                      |        |        | 10.0   | μΑ   |

| $V_{OH1.9}$                         | High Level Output Voltage                 | $V_{IOVDD} = 1.70 \text{ V}, I_{OH} = 1 \text{ mA}$                                                                       | 1.35   |        |        | V    |

| $V_{OH3.3}$                         | High Level Output Voltage                 | $V_{IOVDD} = 3.00 \text{ V}, I_{OH} = 1 \text{ mA}$                                                                       | 2.40   |        |        | V    |

| $V_{OL}^{6}$                        | Low Level Output Voltage                  | $V_{IOVDD} = 3.00 \text{ V}, I_{OL} = 1 \text{ mA}$                                                                       |        |        | 0.40   | V    |

| $V_{OL}^{6}$                        | Low Level Output Voltage                  | $V_{IOVDD} = 1.70 \text{ V}, I_{OL} = 1 \text{ mA}$                                                                       |        |        | 0.40   | V    |

| V <sub>OL_I2C</sub> <sup>5, 7</sup> | I <sup>2</sup> C Low Level Output Voltage | $V_{IOVDD} = 3.00 \text{ V}, I_{OL} = 1.5 \text{ mA}$                                                                     |        |        | 0.40   | V    |

| V <sub>OL_I2C</sub> <sup>5, 7</sup> | I <sup>2</sup> C Low Level Output Voltage | $V_{IOVDD} = 1.70 \text{ V}, I_{OL} = 1.5 \text{ mA}$                                                                     |        |        | 0.40   | V    |

| $C_{PD}$                            | Pin Capacitance                           |                                                                                                                           |        | 4.8    | 5      | рF   |

|                                     | Switch and A <sup>2</sup> B Bus Power     |                                                                                                                           |        |        |        |      |

| I <sub>VSSN</sub>                   | Internal V <sub>SSN</sub> Switch Current  | AD2426(W)/AD2427(W)/AD2428(W)                                                                                             |        |        | 300    | mA   |

| I <sub>VSSN</sub>                   | Internal V <sub>SSN</sub> Switch Current  | AD2420(W)/AD2429W                                                                                                         |        |        | 100    | mA   |

| R <sub>VSSN</sub>                   | Internal V <sub>SSN</sub> On Resistance   |                                                                                                                           |        |        | 1.2    | Ω    |

$<sup>^{1}</sup>$  Master and last slave only consume half the transceiver current because only one of the two TRX blocks is used.

$<sup>^{2}</sup>$  In a bus powered system,  $I_{VOUT}$  has a direct impact on  $I_{VSSN}$  and  $V_{VIN}$  in other nodes. For more information, see the Power Analysis section.

<sup>&</sup>lt;sup>3</sup> Consider the package thermal limits when dissipating current above typical limits. For more information, see the Thermal Characteristics section.

$<sup>^4</sup>$  Must comply with  $I_{VOUT1}$  and  $I_{VOUT2}$  maximum.

<sup>&</sup>lt;sup>5</sup> Applies to SDA and SCL pins.

<sup>&</sup>lt;sup>6</sup> Applies to BCLK, SYNC, DTX0/IO3, DTX1/IO4, DRX0/IO5, DRX1/IO6, ADR1/IO1, ADR2/IO2, IRQ/IO0, PDMCLK/IO7 pins.

<sup>&</sup>lt;sup>7</sup>The minimum I<sub>OL</sub> current is lower than the I<sup>2</sup>C specification because the SDA and SCL pins are designed for a limited number of I<sup>2</sup>C attached slave devices.

# Table 2. Differential Input/Output

| Parameter  |                                       | Conditions    | Min | Тур Мах | Unit |

|------------|---------------------------------------|---------------|-----|---------|------|

| LVDS       |                                       |               |     |         |      |

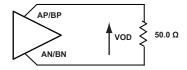

| $ V_{OD} $ | Differential Output Voltage Magnitude | See Figure 19 |     |         |      |

|            | High Transmit Level                   |               | 425 | 545     | mV   |

|            | Medium Transmit Level                 |               | 315 | 415     | mV   |

|            | Low Transmit Level                    |               | 210 | 305     | mV   |

| Receiver   |                                       |               |     |         |      |

| $V_{TH}$   | Differential Input Threshold Voltage  |               | -52 | +52     | mV   |

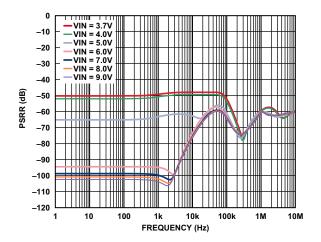

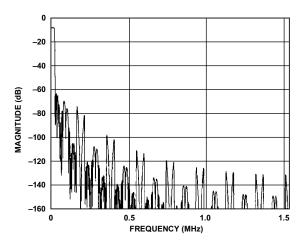

# **POWER SUPPLY REJECTION RATIO (PSRR)**

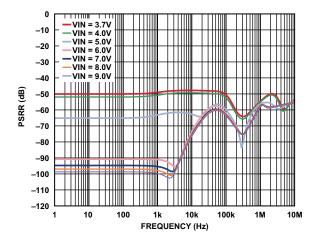

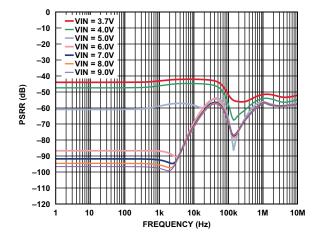

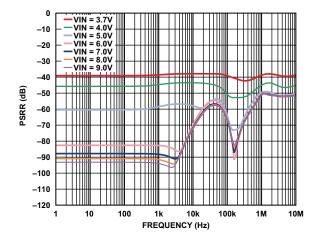

Typical PSRR at  $T_J$  = 40°C with load capacitance  $C_{LOAD}$  = 4.7  $\mu F \parallel 100~\mu F.$

Figure 5. VOUT1 PSRR, I<sub>VOUT1</sub> = 10 mA

Figure 6. VOUT1 PSRR, I<sub>VOUT1</sub> = 40 mA

Figure 7. VOUT2 PSRR, I<sub>VOUT2</sub> = 10 mA

Figure 8. VOUT2 PSRR,  $I_{VOUT2} = 50 \text{ mA}$

# **TIMING SPECIFICATIONS**

All specifications and characteristics apply across the entire operating conditions range unless otherwise noted.

Table 3. Clock and Reset Timing (A<sup>2</sup>B Master)

| Paramet                | er                                                              | Min  | Тур                     | Max  | Unit |

|------------------------|-----------------------------------------------------------------|------|-------------------------|------|------|

| Timing R               | equirements                                                     |      |                         |      |      |

| $f_{\text{SYNCM}}$     | SYNC Pin Input Frequency Continuous Clock                       | 43.6 | 44.1, 48.0              | 48.5 | kHz  |

| $t_{SYNCIJ}$           | SYNC Pin Input Jitter RMS TIE                                   |      | 0.29                    | 1.0  | ns   |

| $t_{\text{SYNCOJ}}$    | SYNC Pin Output Jitter RMS TIE                                  |      |                         | 2.6  | ns   |

| $f_{\text{SYSBCLK}}$   | Bus Clock                                                       |      | $1024 \times f_{SYNCM}$ |      | kHz  |

| t <sub>DNSYNCR</sub> 1 | Delay from First Missed SYNC to Reset (A <sup>2</sup> B Master) | 0.64 |                         | 0.74 | ms   |

| $t_{DNSCFR}^{1}$       | Delay from First Missed SCF to Reset (A <sup>2</sup> B Slave)   | 0.64 |                         | 0.74 | ms   |

| $t_{PLK}$              | PLL Lock Time                                                   |      | 7.5                     |      | ms   |

$<sup>^{\</sup>rm 1}$  Only consecutive missed SYNC or SCF transitions for the specified duration result in a reset.

# Table 4. Pulse Density Modulation Microphone Input Timing

| Parame              | ter                                          | Min   | Тур | Max  | Unit |

|---------------------|----------------------------------------------|-------|-----|------|------|

| Timing R            | Requirements                                 |       |     |      |      |

| $t_{\text{RISS}}$   | DRXn Input Setup Before BCLK                 | 12.0  |     |      | ns   |

| t <sub>RIHS</sub>   | DRXn Input Hold After BCLK                   | 0     |     |      | ns   |

| t <sub>RISS</sub>   | DRXn Input Setup Before PDMCLK               | 12.5  |     |      | ns   |

| t <sub>RIHS</sub>   | DRXn Input Hold After PDMCLK                 | 0     |     |      | ns   |

| Switchin            | g Characteristics                            |       |     |      |      |

| $f_{BCLK}$          | BCLK/PDMCLK Output Frequency                 | 3.05  |     | 3.18 | MHz  |

| t <sub>BCLKOJ</sub> | BCLK/PDMCLK Output Jitter RMS Cycle to Cycle |       |     | 175  | ps   |

| $t_{SOL}$           | BCLK/PDMCLK Output Pulse Width Low           | 161.0 |     |      | ns   |

# Table 5. GPIO Timing

| Parameter          |                    | Min                      | Тур | Max | Unit |

|--------------------|--------------------|--------------------------|-----|-----|------|

| Timing Requirement |                    |                          |     |     |      |

| $t_{FIPW}$         | Input Pulse Width  | t <sub>SYSBCLK</sub> + 1 |     |     | ns   |

| Switching C        | haracteristic      |                          |     |     |      |

| t <sub>FOPW</sub>  | Output Pulse Width | t <sub>SYSBCLK</sub> – 1 |     |     | ns   |

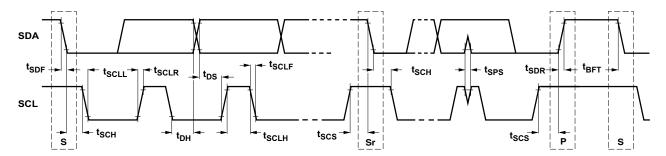

Table 6. I<sup>2</sup>C Port Timing

| Param             | Parameter Timing Requirements                 |     | Тур | Max | Unit |

|-------------------|-----------------------------------------------|-----|-----|-----|------|

| Timing            |                                               |     |     |     |      |

| $f_{\text{SCL}}$  | SCL Clock Frequency                           | 0   |     | 400 | kHz  |

| $t_{\text{SCLH}}$ | SCL Pulse Width High                          | 0.6 |     |     | μs   |

| $t_{\text{SCLL}}$ | SCL Pulse Width Low                           | 1.3 |     |     | μs   |

| $t_{\text{SCS}}$  | Start and Repeated Start Condition Setup Time | 0.6 |     |     | μs   |

| $t_{SCH}$         | Start Condition Hold Time                     | 0.6 |     |     | μs   |

| $t_{\text{SPS}}$  | Stop Condition Hold Time                      | 0.6 |     |     | μs   |

| $t_{DS}$          | Data Setup Time                               | 100 |     |     | ns   |

| $t_{DH}$          | Data Hold Time                                | 0.0 |     | 0.9 | μs   |

| $t_{\text{SCLR}}$ | SCL Rise Time                                 |     |     | 300 | ns   |

| $t_{\text{SCLF}}$ | SCL Fall Time                                 |     |     | 300 | ns   |

| $t_{\text{SDR}}$  | SDA Rise Time                                 |     |     | 300 | ns   |

| $t_{\text{SDF}}$  | SDA Fall Time                                 |     |     | 300 | ns   |

| $t_{BFT}$         | Bus-Free Time Between Stop and Start          | 1.3 |     |     | μs   |

Figure 9. I<sup>2</sup>C Port Timing

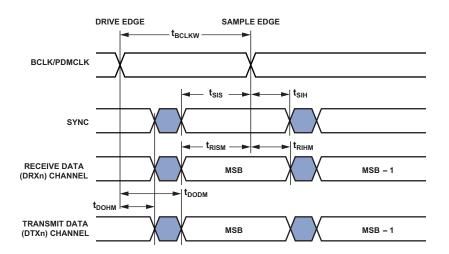

Table 7. I<sup>2</sup>S Timing

|                                 |                                                                            |      | 1.8 V |      | 3.3 V |            |

|---------------------------------|----------------------------------------------------------------------------|------|-------|------|-------|------------|

| Paramete                        | er                                                                         | Min  | Max   | Min  | Max   | Unit       |

| l <sup>2</sup> S Slave T        | iming Requirements (A <sup>2</sup> B Master)                               |      |       |      |       |            |

| t <sub>BCLKW</sub>              | BCLK Width                                                                 | 19.5 |       | 9.5  |       | ns         |

| t <sub>BCLKS</sub>              | BCLK Period                                                                | 39.0 |       | 19.0 |       | ns         |

| t <sub>SIS</sub> 1              | SYNC Input Setup Before BCLK Sample Edge                                   | 2.25 |       | 2.25 |       | ns         |

| t <sub>SIH</sub> 1              | SYNC Input Hold After BCLK Sample Edge                                     | 2.0  |       | 3.0  |       | ns         |

| t <sub>RISM</sub> 1             | DRXn Input Setup Before BCLK Sample Edge                                   | 0.5  |       | 0.5  |       | ns         |

| t <sub>RIHM</sub> 1             | DRXn Input Hold After BCLK Sample Edge                                     | 2.0  |       | 1.5  |       | ns         |

| t <sub>RISM</sub> 1             | DRX1 on DTX1 Input Setup Before BCLK Sample Edge                           | 4.0  |       | 4.5  |       | ns         |

| t <sub>RIHM</sub> 1             | DRX1 on DTX1 Input Hold After BCLK Sample Edge                             | 0.5  |       | 0.5  |       | ns         |

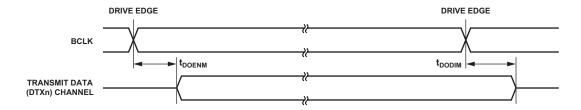

| <sup>2</sup> S Slave S          | witching Characteristics (A <sup>2</sup> B Master)                         |      |       |      |       |            |

| $t_{DODM}^2$                    | DTXn Output Delay After BCLK Drive Edge                                    |      | 15.25 |      | 12.0  | ns         |

| t <sub>DOHM</sub> <sup>2</sup>  | DTXn Output Hold After BCLK Drive Edge                                     | 3.0  |       | 3.0  |       | ns         |

| t <sub>DOENM</sub> 2            | DTXn Data Enable Delay After BCLK Drive Edge                               | 2.0  |       | 2.0  |       | ns         |

| t <sub>DODIM</sub> <sup>2</sup> | DTXn Data Disable Delay After BCLK Drive Edge                              |      | 13.0  |      | 8.0   | ns         |

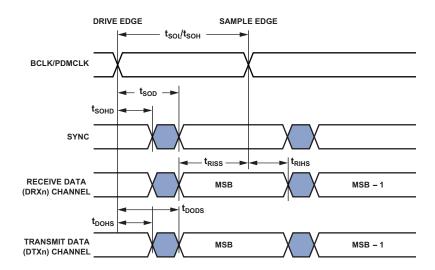

| l²S Master                      | Timing Requirements (A <sup>2</sup> B Slave)                               |      |       |      |       |            |

| t <sub>RISS</sub> 1             | DRXn Input Setup Before BCLK Sample Edge                                   | 0.0  |       | 0.0  |       | ns         |

| t <sub>RIHS</sub> 1             | DRXn Input Hold After BCLK Sample Edge                                     | 5.8  |       | 2.0  |       | ns         |

| t <sub>RISS</sub> 1             | DRX1 on DTX1 Input Setup Before BCLK Sample Edge                           | 2.5  |       | 4.5  |       | ns         |

| t <sub>RIHS</sub> 1             | DRX1 on DTX1 Input Hold After BCLK Sample Edge                             | 2.5  |       | 0.5  |       | ns         |

| l²S Master                      | Switching Characteristics (A <sup>2</sup> B Slave)                         |      |       |      |       |            |

| $f_{BCLK}$                      | BCLK Output Frequency <sup>3</sup>                                         |      | 25.0  |      | 50.0  | MHz        |

| t <sub>BCLKMOJ</sub>            | BCLK Output Jitter (RMS Cycle to Cycle, $f_{BCLKS} = 12.288 \text{ MHz}$ ) |      | 100   |      | 100   | ps         |

| $t_{SOL}/t_{SOH}$               | Transmit or Receive BCLK Duty Cycle                                        | 0.45 | 0.55  | 0.45 | 0.55  | $t_{BCLK}$ |

| t <sub>soJ</sub>                | SYNC Output Jitter (RMS Cycle to Cycle $f_{SYNCM} = 48 \text{ kHz}$ )      |      | 2.2   |      | 2.2   | ns         |

| t <sub>SOD</sub> <sup>2</sup>   | SYNC Output Delay After BCLK Drive Edge                                    |      | 6.5   |      | 6.5   | ns         |

| SOHD <sup>2</sup>               | SYNC Output Hold After BCLK Drive Edge                                     | 2.8  |       | 4.5  |       | ns         |

| t <sub>DODS</sub> <sup>2</sup>  | DTXn Output Delay After BCLK Drive Edge                                    |      | 10.8  |      | 9.25  | ns         |

| t <sub>DOHS</sub> <sup>2</sup>  | DTXn Output Hold After BCLK Drive Edge                                     | 5.5  |       | 6.0  |       | ns         |

<sup>&</sup>lt;sup>1</sup> Referenced to sample edge.

<sup>&</sup>lt;sup>2</sup> Referenced to drive edge.

$<sup>^{3}</sup>$  When  $V_{IOVDD} = 3.3$  V, the setup and hold timing at the 50 MHz maximum bit clock rate can be violated when interfacing with other I<sup>2</sup>S devices. The timing violations are seen when the A<sup>2</sup>B slave node is receiving and A<sup>2</sup>B master node is transmitting. In these modes, the maximum BCLK frequency of 50 MHz cannot be achieved.

Figure 10. I<sup>2</sup>S Slave (A<sup>2</sup>B Master) Timing

Figure 11. I<sup>2</sup>S Master (A<sup>2</sup>B Slave) Timing

Figure 12. 1<sup>2</sup>S Slave (A<sup>2</sup>B Master) Enable and Three-State Timing

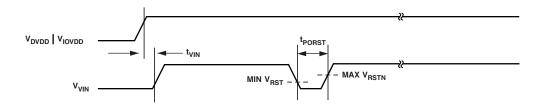

# POWER-UP SEQUENCING RESTRICTIONS

When externally supplied,  $V_{DVDD}$  and  $V_{IOVDD}$  must reach at least 90% of specification before  $V_{VIN}$  begins ramping. To avoid damage to input pins and to ensure correct sampling of the ADR1/ADR2 pins at start-up,  $V_{IOVDD}$  must be within specification before input signals are driven by external devices.

Table 8. Power-Up Timing

| Parameter          |                                                                                                                                           | Min | Max | Unit |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|

| Timing Req         | uirements                                                                                                                                 |     |     |      |

| t <sub>VIN</sub>   | When Externally Supplied, $V_{\text{DVDD}}$ and $V_{\text{IOVDD}}$ Must Reach 90% of Specification Before $V_{\text{VIN}}$ Begins Ramping | >0  |     | ms   |

| t <sub>PORST</sub> | Minimum Time Required for $V_{\text{VIN}}$ to be Held Below $V_{\text{RST}}$ to Assert Power on Reset                                     | 25  |     | ms   |

Figure 13. Power-Up Sequencing Timing with Externally Supplied  $V_{\rm DVDD}$  and  $V_{\rm IOVDD}$

# A<sup>2</sup>B BUS SYSTEM SPECIFICATION

Table 9. A<sup>2</sup>B System Specifications

| Parameter                                                                       | System Specification                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cable                                                                           | Unshielded, single, twisted pair wire (UTP) with 100 $\Omega$ differential impedance. EMC performance and full functionality under worst-case environmental conditions is confirmed with Leoni Dacar 545 cable (76D00305).                                                                                                  |

| Maximum Cable Length                                                            |                                                                                                                                                                                                                                                                                                                             |

| AD2428(W)Mastered System                                                        | 40 m total, 15 m between nodes.                                                                                                                                                                                                                                                                                             |

| AD2429(W) Mastered System                                                       | 10 m total, 5 m between nodes.                                                                                                                                                                                                                                                                                              |

| Maximum Number of Nodes                                                         |                                                                                                                                                                                                                                                                                                                             |

| AD2428(W) Mastered System                                                       | 11 nodes (1 master node and 10 slave nodes).                                                                                                                                                                                                                                                                                |

| AD2429(W) Mastered System                                                       | Three nodes (1 master node and 2 slave nodes).                                                                                                                                                                                                                                                                              |

| Maximum Number of Audio Slots                                                   |                                                                                                                                                                                                                                                                                                                             |

| AD2426(W)/AD2427(W)/AD2428(W) <sup>1</sup>                                      | 64 total, up to 32 upstream and 32 downstream slots, depending upon system design.                                                                                                                                                                                                                                          |

| AD2420(W)/AD2429(W) <sup>1</sup>                                                | AD2429(W): 4 upstream and 2 downstream slots, depending upon system design. AD2420(W): 2 upstream slots, depending upon system design.                                                                                                                                                                                      |

| Number of Audio Channels per Slave Node                                         | Individually programmable 0 to 32 upstream channels and 0 to 32 downstream channels.                                                                                                                                                                                                                                        |

| Synchronous A <sup>2</sup> B Data Slot Size                                     | 8, 12, 16, 20, 24, 28, or 32 bits to match I <sup>2</sup> S/TDM data-word lengths. Same slot size for all nodes. Upstream and downstream can choose different slot sizes. 12-, 16-, or 20-bit slot sizes can carry compressed data over the A <sup>2</sup> B bus for 16-, 20-, or 24-bit I <sup>2</sup> S/TDM word lengths. |

| Audio Sampling Frequency                                                        | 44.1 kHz to 48 kHz. All nodes sample synchronously. Slave node transceivers support sample rates $(f_s)$ of 1× (48 kHz), 2× (96 kHz) or 4× (192 kHz), individually configured per slave.                                                                                                                                    |

|                                                                                 | To support $2\times$ and $4\times$ sampling rates in slaves, the master uses two and four times the number of I <sup>2</sup> S/TDM data channels as the $1\times$ sampling frequency ( $f_{SYNCM}$ ) interface to the host.                                                                                                 |

|                                                                                 | Transceivers also support reduced rate sampling for 24 kHz, 12 kHz, 6 kHz, 4 kHz, 3 kHz, 2.4 kHz, 2 kHz, 1.71 kHz, or 1.5 kHz at a low latency 48 kHz superframe rate.                                                                                                                                                      |

| Discovery Time                                                                  | Less than 35 ms per node. Much less than 350 ms for total system startup in a system with 10 nodes. Includes register initialization.                                                                                                                                                                                       |

| Maximum I <sub>BUSDISC</sub> Bus Current per Node Prior to Discovery Completion | 60 mA. Measured at the negative bias switch.                                                                                                                                                                                                                                                                                |

| Maximum C <sub>BUSDISC</sub> Total Bus Capacitance                              | 70 μF. Capacitance measured between the N and P pins in the CON1-B connector terminal.                                                                                                                                                                                                                                      |

| Bit Error Detection                                                             | Robust error detection for control data and status data with 16-bit cyclic redundancy check (CRC).                                                                                                                                                                                                                          |

| Error Correction                                                                | Parity and line code error detection on synchronous data slots with audio error correction (repeat of last known good data).                                                                                                                                                                                                |

|                                                                                 | For 24-bit and 32-bit data channels, single error correction and double error detection (SECDED) of synchronous data slots is possible.                                                                                                                                                                                     |

| Failure Diagnostics <sup>1</sup>                                                | Location and cause of failure can be detected for A <sup>2</sup> B wires shorted to a high voltage (for example, positive terminal of car battery), shorted to ground, wires shorted to each other, wires reversed or open connection.                                                                                      |

| System EMI/EMC                                                                  | Meets or exceeds industry specifications for robustness (ISO 11452-2, ISO 11452-4, ISO 7637-3) and emissions (CISPR25).                                                                                                                                                                                                     |

| System ESD                                                                      | See IEC ESD ratings in Table 12 for terminals.                                                                                                                                                                                                                                                                              |

$<sup>^{1} \</sup> See \ the \ AD 2420(W)/6(W)/7(W)/8(W)/9(W) \ Automotive \ Audio \ Bus \ A^{2}B \ Transceiver \ Technical \ Reference \ for \ more \ information.$

## RMS Time Interval Error (TIE) Jitter

Clocks in an  $A^2B$  system are passed from the master to Slave 0, from Slave 0 to Slave 1, and so on. Each transceiver adds self jitter to the incoming jitter, which results in jitter growth from the master to the  $n^{th}$  slave. Table 10 illustrates typical rms TIE jitter growth.

Table 10. SYNC Output RMS TIE Jitter at Each Slave

| Slave Node | Тур  | Max  | Unit |

|------------|------|------|------|

| 1          | 1.57 |      | ns   |

| 2          | 1.79 |      | ns   |

| 3          | 1.91 |      | ns   |

| 4          | 2.04 |      | ns   |

| 5          | 2.15 |      | ns   |

| 6          | 2.27 |      | ns   |

| 7          | 2.44 |      | ns   |

| 8          | 2.47 |      | ns   |

| 9          | 2.58 |      | ns   |

| 10         | 2.70 | 5.50 | ns   |

## PDM TYPICAL PERFORMANCE CHARACTERISTICS

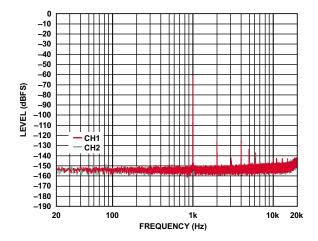

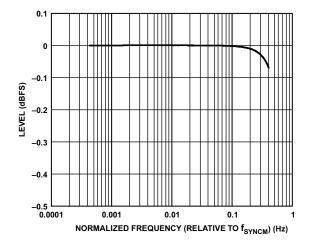

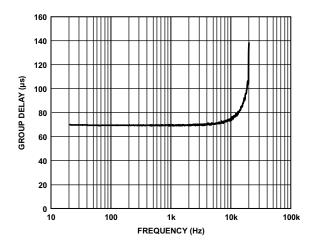

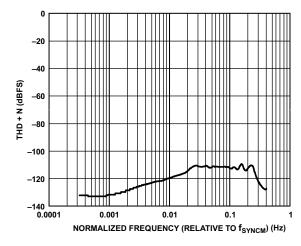

Figure 14 through Figure 18 and Table 11 describe typical PDM performance characteristics.

Figure 14. PDM FFT,  $f_{SYNCM} = 48 \text{ kHz}$ , -60 dB Frame Sync Input

Figure 15. PDM Frequency Response

Figure 16. PDM Group Delay vs. Frequency,  $f_{SYNCM} = 48 \text{ kHz}$

Figure 17. PDM Total Harmonic Distortion + Noise (THD + N) vs. Normalized Frequency (Relative to f<sub>SYNCM</sub>)

Figure 18. PDM Out of Band Frequency Response (48 kHz Output)

**Table 11. PDM Interface Performance Specifications**

| Parameter                    | Conditions                           | Min  | Тур   | Max   | Unit                      |

|------------------------------|--------------------------------------|------|-------|-------|---------------------------|

| Dynamic Range                | 20 Hz to 20 kHz, -60 dB input        |      |       |       |                           |

| With A-Weighted Filter (RMS) |                                      |      | 120   |       | dB                        |

| SNR                          | A-weighted, fourth-order input       |      | 120   |       | dB                        |

| Decimation Ratio             | Default is 64×                       | 64×  | 128×  | 256×  |                           |

| Frequency Response           | DC to 0.45 f <sub>SYNCM</sub>        | -0.1 |       | +0.01 | dB                        |

| Stop Band                    |                                      |      | 0.566 |       | f <sub>SYNCM</sub>        |

| Attenuation                  |                                      | 74   |       |       | dB                        |

| Group Delay                  | 0.02 f <sub>SYNCM</sub> input signal |      | 3.80  |       | f <sub>SYNCM</sub> cycles |

| Gain                         | PDM to PCM                           |      | 0     |       | dB                        |

| Start-Up Time <sup>1</sup>   |                                      |      | 48    |       | f <sub>SYNCM</sub> cycles |

| Bit Width                    | Internal and output                  |      | 24    |       | Bits                      |

<sup>&</sup>lt;sup>1</sup>The PDM start-up time is the time for the filters to settle after the PDM block is enabled. It is the time to wait before data is guaranteed to meet the specified performance.

## **ABSOLUTE MAXIMUM RATINGS**

Stresses at or above those listed in Table 12 can cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

Table 12. Absolute Maximum Ratings

| Parameter                                                  | Rating                                               |

|------------------------------------------------------------|------------------------------------------------------|

| VIN to VSS                                                 | -0.7 V to +30 V                                      |

| Power Supply IOVDD to VSS                                  | -0.3 V to +3.63 V                                    |

| Power Supply DVDD to VSS                                   | -0.3 V to +1.98 V                                    |

| Power Supply PLLVDD to VSS                                 | -0.3 V to +1.98 V                                    |

| Power Supply TRXVDD to VSS                                 | -0.3 V to +3.63 V                                    |

| Digital Pin Output Voltage Swing <sup>1</sup>              | $-0.3 \text{ V to V}_{\text{IOVDD}} + 0.5 \text{ V}$ |

| Input Voltage <sup>2, 3</sup>                              | -0.33 V to +3.63 V                                   |

| Input Voltage <sup>2, 4</sup>                              | -0.33 V to +2.10 V                                   |

| I <sup>2</sup> C Input Voltage <sup>2, 5</sup>             | -0.33 V to +5.5 V                                    |

| A <sup>2</sup> B Bus Terminal Voltage                      |                                                      |

| AP, AN, BP, and BN Pins                                    | -0.5 V to +4.1 V                                     |

| SENSE, SWP, VSSN Voltage to $V_{SS}$                       | +30 V maximum                                        |

| Storage Temperature Range                                  | -65°C to +150°C                                      |

| Junction Temperature While Biased                          | -40°C to +125°C                                      |

| ESD Rating HBM                                             |                                                      |

| VIN and SWP Pins                                           | ±2.5 kV                                              |

| AP, AN, BP, and BN Pins                                    | ±2.5 kV                                              |

| All Other Pins                                             | ±2.5 kV                                              |

| ESD Rating FICDM                                           |                                                      |

| All Pins                                                   | ±1.25 kV                                             |

| System ESD Rating CON1-A and CON1-B Terminals <sup>6</sup> |                                                      |

| IEC 61000-4-2, Air Discharge                               | ±15 kV                                               |

| IEC 61000-4-2, Contact Discharge                           | ±12 kV                                               |

| Digital Pin Output Current per Pin Group <sup>7</sup>      | 15 mA                                                |

<sup>&</sup>lt;sup>1</sup> Applies to BCLK, SYNC, DTX0/IO3, DTX1/DRX1/IO4, DRX0/IO5, DRX1/IO6, IRQ/IO0, ADR1/IO1, ADR2/IO2, PDMCLK/IO7.

Permanent damage can occur if the digital pin output current per pin group value is exceeded. For example, if three pins from Group 2 in Table 13 are sourcing or sinking 2 mA each, the total current for those pins is 6 mA. Up to 9 mA can be sourced or sunk by the remaining pins in the group without damaging the device.

**Table 13. Total Current Pin Groups**

| Group | Pins in Group                                  |

|-------|------------------------------------------------|

| 1     | IRQ/IO0, ADR1/IO1, ADR2/IO2                    |

| 2     | BCLK, SYNC, DTX0/IO3, DTX1/DRX1/IO4, DRX0/IO5, |

|       | DRX1/IO6, IO7                                  |

#### THERMAL CHARACTERISTICS

To determine the junction temperature on the application printed circuit board (PCB), use the following equations:

$$T_J = T_{CASE} + \Psi_{JT} \times P_D$$

where.

$T_I$  = junction temperature (°C).

$T_{CASE}$  = case temperature (°C) measured by customer at top center of package.

$\Psi_{TT}$  = values in Table 14.

$P_D$  = power dissipation.

Values of  $\theta_{JA}$  are provided for package comparison and PCB design considerations. Use  $\theta_{JA}$  for a first-order approximation of  $T_I$  by the following equation:

$$T_I = T_A + \theta_{IA} \times P_D$$

where  $T_A$  = ambient temperature (°C).

Values of  $\theta_{JC}$  are provided for package comparison and PCB design considerations when an external heat sink is required.

Values of  $\theta_{JB}$  are provided for package comparison and PCB design considerations.

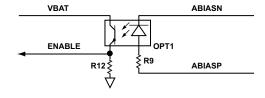

Thermal characteristics of the LFCSP\_SS package are shown in Table 14. See JESD51-13 for detailed parameter definitions. The junction to board measurement complies with JESD51-8. The junction to case measurement complies with MIL-STD-883 (Method 1012.1). All measurements use a 2S2P JEDEC test board.

Table 14. Thermal Characteristics

| Parameter             | Conditions                | Typical (°C/W) |

|-----------------------|---------------------------|----------------|

| $\theta_{JA}$         | Airflow = 0 m/s           | 31.6           |

| $\theta_{\text{JMA}}$ | Airflow = 1 m/s           | 28.8           |

| $\theta_{JMA}$        | Airflow = $2 \text{ m/s}$ | 28.1           |

| $\theta_{\text{JC}}$  | Airflow = $0 \text{ m/s}$ | 4.6            |

| $\theta_{\text{JB}}$  | Airflow = 0 m/s           | 14.7           |

| $\Psi_{	extsf{JT}}$   | Airflow = $0 \text{ m/s}$ | 0.20           |

| $\Psi_{\text{JT}}$    | Airflow = 1 m/s           | 0.27           |

| $\Psi_{	extsf{JT}}$   | Airflow = $2 \text{ m/s}$ | 0.30           |

$<sup>^2</sup>$ Only applies when the related power supply ( $V_{\rm IOVDD}$ ) is within specification. When the power supply is below specification, the range is the voltage being applied to that power domain  $\pm$  0.2 V.

$<sup>^3</sup>$  Applies when nominal  $V_{IOVDD}$  is 3.3 V.

$<sup>^4\,\</sup>text{Applies}$  when nominal  $V_{\text{IOVDD}}$  is 1.8 V.

<sup>&</sup>lt;sup>5</sup> Applies to SCL and SDA.

<sup>&</sup>lt;sup>6</sup>CON1-A and CON1-B are connectors.

<sup>&</sup>lt;sup>7</sup> For more information, see the following description and Table 13.

The 32-lead LFCSP\_SS package requires thermal trace squares and thermal vias to an embedded ground plane in the PCB. The exposed paddle must connect to ground for proper operation to data sheet specifications. Refer to JEDEC standard JESD51-5 for more information.

## **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

# TEST CIRCUITS AND SWITCHING CHARACTERISTICS

Figure 19 shows a line driver voltage measurement circuit of the differential line driver and receiver AP/AN and BP/BN pins.

Figure 19. Differential Line Driver Voltage Measurement

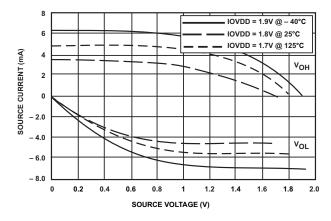

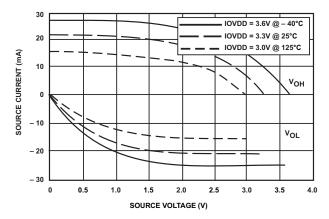

## **OUTPUT DRIVE CURRENTS**

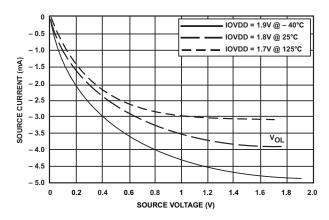

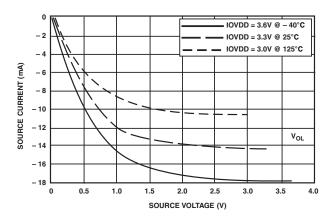

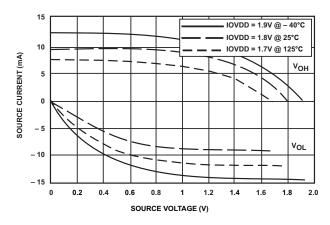

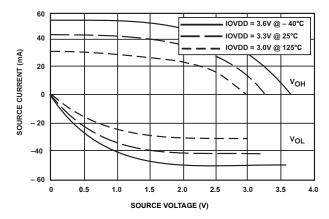

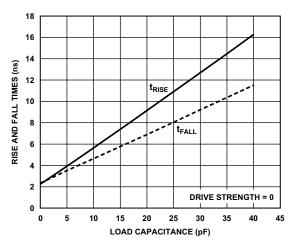

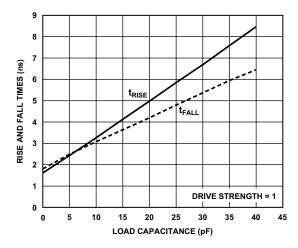

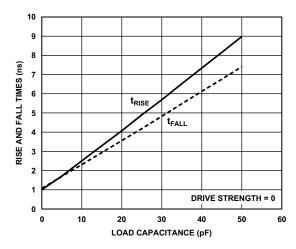

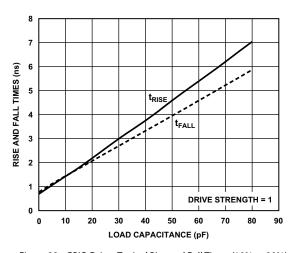

Figure 20 through Figure 25 show typical current voltage characteristics for the output drivers of the transceiver. The curves represent the current drive capability of the output drivers as a function of output voltage. Drive Strength 0 is DS0, and Drive Strength 1 is DS1.

Figure 20. GPIO, BCLK, and SYNC Drivers (DS0, 1.8 V IOVDD)

Figure 21. GPIO, BCLK, and SYNC Drivers (DS0, 3.3 V IOVDD)

Figure 22. I<sup>2</sup>C Drivers (1.8 V IOVDD)

Figure 23. 1<sup>2</sup>C Drivers (3.3 V IOVDD)

Figure 24. GPIO, BCLK, and SYNC Drivers (DS1, 1.8 V IOVDD)

Figure 25. GPIO, BCLK, and SYNC Drivers (DS1, 3.3 V IOVDD)

#### **TEST CONDITIONS**

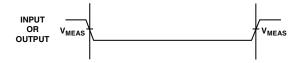

All timing parameters in this data sheet were measured under the conditions described in this section. Figure 26 shows the measurement point for ac measurements (except output enable/disable). The measurement point,  $V_{\text{MEAS}}$ , is  $V_{\text{IOVDD}}/2$  for  $V_{\text{IOVDD}}$  (nominal) = 3.3 V.

Figure 26. Voltage Reference Levels for AC Measurements (Except Output Enable/Disable)

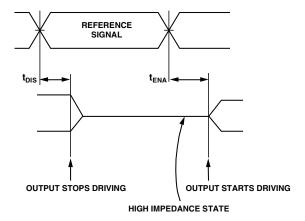

#### **Output Enable Time Measurement**

Output pins are considered enabled when they make a transition from a high impedance state to the point when they start driving.

The output enable time,  $t_{\rm ENA}$ , is the interval from the point when a reference signal reaches a high or low voltage level to the point when the output starts driving, as shown on the right side of Figure 27. If multiple pins are enabled, the measurement value is that of the first pin to start driving.

Figure 27. Output Enable/Disable

## **Output Disable Time Measurement**

Output pins are considered disabled when they stop driving, enter a high impedance state, and start to decay from the output high or low voltage. The output disable time,  $t_{DIS}$ , is the interval from when a reference signal reaches a high or low voltage level to the point when the output stops driving, as shown on the left side of Figure 27.

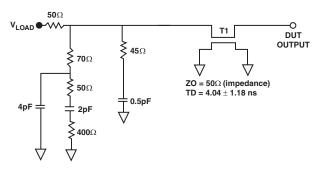

### **Capacitive Loading**

Output delays and holds are based on standard capacitive loads of an average of 6 pF on all pins (see Figure 28).  $V_{\rm LOAD}$  is equal to  $V_{\rm IOVDD}/2$ . Figure 29 through Figure 32 show how output rise time varies with capacitance. The delay and hold specifications given must be derated by a factor derived from these figures. The graphs in Figure 29 through Figure 32 cannot be linear outside the ranges shown.

#### TESTER PIN ELECTRONICS

#### NOTES