## **Pin Description**

| Pin#                                         | Name                                                         | I/O<br>Type    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|----------------------------------------------|--------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Input F                                      | Reference                                                    |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| C1<br>B2<br>A3<br>C3<br>B3<br>B4<br>C4<br>A4 | ref0<br>ref1<br>ref2<br>ref3<br>ref4<br>ref5<br>ref6<br>ref7 | I <sub>u</sub> | Input References 7:0 (LVCMOS, Schmitt Trigger). These input references are available to both the Tx DPLL and the Rx DPLL for synchronizing output clocks. All eight input references can lock to any multiple of 8 kHz up to 77.76 MHz including 25 MHz and 50 MHz. Input ref0 and ref1 have additional configurable pre-dividers allowing input frequencies of 62.5 MHz, 125 MHz, and 155.52 MHz. These pins are internally pulled up to $V_{\rm dd}$ .                                             |  |  |  |  |  |

| B1<br>A1<br>A2                               | sync0<br>sync1<br>sync2                                      | I <sub>u</sub> | Frame Pulse Synchronization References 2:0 (LVCMOS, Schmitt Trigger). These are optional frame pulse synchronization inputs associated with input references 0, 1 and 2. These inputs accept frame pulses in a clock format (50% duty cycle) or a basic frame pulse format with minimum pulse width of 5 ns. These pins are internally pulled up to $V_{\rm dd}$ .                                                                                                                                   |  |  |  |  |  |

| Outpu                                        | t Clocks and Fra                                             | ame Puls       | es                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| A9<br>B10                                    | diff0_p<br>diff0_n                                           | 0              | Differential Output Clock 0 (LVPECL). When in SONET/SDH mode, this output can be configured to provide any one of the available SONET/SDH clocks (6.48 MHz, 19.44 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 155.52 MHz, 311.04 MHz, 622.08 MHz). When in Ethernet mode, this output can be configured to provide any of the Ethernet clocks (25 MHz, 50 MHz, 62.5 MHz, 125 MHz, 156.25 MHz, 312.5 MHz). See "Output Clocks and Frame Pulses" section on page 22 more detail on clock frequency settings. |  |  |  |  |  |

| A10<br>B9                                    | diff1_p<br>diff1_n                                           | 0              | Differential Output Clock 1 (LVPECL). When in SONET/SDH mode, this output can be configured to provide any one of the available SONET/SDH clocks (6.48 MHz, 19.44 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 155.52 MHz, 311.04 MHz, 622.08 MHz). When in Ethernet mode, this output can be configured to provide any of the Ethernet clocks (25 MHz, 50 MHz, 62.5 MHz, 125 MHz, 156.25 MHz, 312.5 MHz). See "Output Clocks and Frame Pulses" section on page 22 more detail on clock frequency settings. |  |  |  |  |  |

| D10                                          | apll_clk0                                                    | 0              | APLL Output Clock 0 (LVCMOS). This output can be configured to provide any one of the SONET/SDH clock outputs up to 77.76 MHz or any of the Ethernet clock rates up to 125 MHz. The default frequency for this output is 77.76 MHz.                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| G10                                          | apll_clk1                                                    | 0              | APLL Output Clock 1 (LVCMOS). This output can be configured to provide any one of the SONET/SDH clock outputs up to 77.76 MHz or any of the Ethernet clock rates up to 125 MHz. The default frequency for this output is 19.44 MHz.                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| K9                                           | p0_clk0                                                      | 0              | Programmable Synthesizer 0 - Output Clock 0 (LVCMOS). This output can be configured to provide any frequency with a multiple of 8 kHz up to 100 MHz in addition to 2 kHz. The default frequency for this output is 2.048 MHz.                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| K7                                           | p0_clk1                                                      | 0              | <b>Programmable Synthesizer 0 - Output Clock 1 (LVCMOS).</b> This is a programmable clock output configurable as a multiple or division of the p0_clk0 frequency within the range of 2 kHz to 100 MHz. The default frequency for this output is 8.192 MHz.                                                                                                                                                                                                                                           |  |  |  |  |  |

| K8                                           | p0_fp0                                                       | 0              | Programmable Synthesizer 0 - Output Frame Pulse 0 (LVCMOS). This output can be configured to provide virtually any style of output frame pulse associated with the p0 clocks. The default frequency for this frame pulse output is 8 kHz.                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Pin#     | Name             | I/O<br>Type    | Description                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|----------|------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| J7       | p0_fp1           | 0              | Programmable Synthesizer 0 - Output Frame Pulse 1 (LVCMOS). This output can be configured to provide virtually any style of output frame pulse associated with the p0 clocks. The default frequency for this frame pulse output is 8 kHz                                                                                                                                                              |  |  |  |  |  |  |

| J10      | p1_clk0          | 0              | <b>Programmable Synthesizer 1 - Output Clock 0 (LVCMOS).</b> This output can be configured to provide any frequency with a multiple of 8 kHz up to 100 MHz in addition to 2 kHz. The default frequency for this output is 1.544 MHz (DS1).                                                                                                                                                            |  |  |  |  |  |  |

| K10      | p1_clk1          | 0              | <b>Programmable Synthesizer1 - Output Clock 1 (LVCMOS).</b> This is a programmable clock output configurable as a multiple or division of the p1_clk0 frequency within the range of 2 kHz to 100 MHz. The default frequency for this output is 3.088 MHz (2x DS1).                                                                                                                                    |  |  |  |  |  |  |

| E1       | ref_out          | 0              | Rx DPLL Selected Output Reference (LVCMOS). This is a buffered copy of the output of the reference selector for the Rx DPLL. Switching between input reference clocks at this output is not hitless.                                                                                                                                                                                                  |  |  |  |  |  |  |

| Contro   | ol               |                |                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| H5       | rst_b            | I              | Reset (LVCMOS, Schmitt Trigger). A logic low at this input resets the device. To ensure proper operation, the device must be reset after power-up. Reset should be asserted for a minimum of 300 ns.                                                                                                                                                                                                  |  |  |  |  |  |  |

| J5       | hs_en            | I <sub>u</sub> | Tx DPLL Hitless Switching Enable (LVCMOS, Schmitt Trigger). A logic high at this input enables hitless reference switching. A logic low disables hitless reference switching and re-aligns the Tx DPLL's output phase to the phase of the selected reference input. This feature can also be controlled through software registers. This pin is internally pulled up to Vdd.                          |  |  |  |  |  |  |

| C2<br>D2 | mode_0<br>mode_1 | I <sub>u</sub> | Tx DPLL Mode Select 1:0 (LVCMOS, Schmitt Trigger). During reset, the levels on these pins determine the default mode of operation for the Tx DPLL (Automatic, Normal, Holdover or Freerun). After reset, the mode of operation can be controlled directly with these pins, or by accessing the tx_dpll_modesel register (0x1F) through the serial interface. This pin is internally pulled up to Vdd. |  |  |  |  |  |  |

| K1       | diff0_en         | I <sub>u</sub> | <b>Differential Output 0 Enable (LVCMOS, Schmitt Trigger).</b> When set high, the differential LVPECL output 0 driver is enabled. When set low, the differential driver is tristated reducing power consumption. This pin is internally pulled up to Vdd.                                                                                                                                             |  |  |  |  |  |  |

| D3       | diff1_en         | I <sub>u</sub> | <b>Differential Output 1 Enable (LVCMOS, Schmitt Trigger).</b> When set high, the differential LVPECL output 1 driver is enabled. When set low, the differential driver is tristated reducing power consumption. This pin is internally pulled up to Vdd.                                                                                                                                             |  |  |  |  |  |  |

| Status   |                  |                |                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| H1       | lock             | 0              | <b>Lock Indicator (LVCMOS).</b> This is the lock indicator pin for the Tx DPLL. This output goes high when the Tx DPLL's output is frequency and phase locked to the input reference.                                                                                                                                                                                                                 |  |  |  |  |  |  |

| J1       | hold             | 0              | <b>Holdover Indicator (LVCMOS).</b> This pin goes high when the Tx DPLL enters the holdover mode.                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Pin #  | Name        | I/O<br>Type    | Description                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|--------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Serial | Interface   |                |                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| E2     | sck_scl     | I/B            | Clock for Serial Interface (LVCMOS). Serial interface clock. When $i2c_en = 0$ , this pin acts as the sck pin for the serial interface. When $i2c_en = 1$ , this pin acts as the scl pin (bidirectional) for the $I^2C$ interface.                                                                                                      |  |  |  |  |  |

| F1     | si_sda      | I/B            | <b>Serial Interface Input (LVCMOS).</b> Serial interface data pin. When $i2c_en = 0$ , this pin acts as the si pin for the serial interface. When $i2c_en = 1$ , this pin acts as the sda pin (bidirectional) for the $I^2C$ interface.                                                                                                 |  |  |  |  |  |

| G1     | so          | 0              | <b>Serial Interface Output (LVCMOS).</b> Serial interface data output. When i2c_en = 0, this pin acts as the so pin for the serial interface. When i2c_en = 1, this pin is unused and should be left unconnected.                                                                                                                       |  |  |  |  |  |

| E3     | cs_b_asel0  | I <sub>u</sub> | Chip Select for SPI/Address Select 0 for $I^2C$ (LVCMOS). When $i2c_en = 0$ , this pin acts as the chip select pin (active low) for the serial interface. When $i2c_en = 1$ , this pin acts as the asel0 pin for the $I^2C$ interface.                                                                                                  |  |  |  |  |  |

| F3     | asel1       | I <sub>u</sub> | Address Select 1 for $I^2C$ (LVCMOS). When $i2c_en = 1$ , this pin acts as the asel1 pin for the $I^2C$ interface. Internally pulled up to Vdd. Leave open when not in use.                                                                                                                                                             |  |  |  |  |  |

| F2     | asel2       | I <sub>u</sub> | Address Select 2 for $I^2C$ (LVCMOS). When $i2c_en = 1$ , this pin acts as the asel2 pin for the $I^2C$ interface. Internally pulled up to Vdd. Leave open when not in use.                                                                                                                                                             |  |  |  |  |  |

| G2     | int_b       | 0              | <b>Interrupt Pin (LVCMOS).</b> Indicates a change of device status prompting the processor to read the enabled interrupt service registers (ISR). This pin is an open drain, active low and requires an external pulled-up to Vdd.                                                                                                      |  |  |  |  |  |

| J2     | i2c_en      | I <sub>u</sub> | $I^2C$ Interface Enable (LVCMOS). If set high, the $I^2C$ interface is enabled, if set low, the SPI interface is enabled. Internally pull-up to Vdd.                                                                                                                                                                                    |  |  |  |  |  |

| APLL   | Loop Filter |                |                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| A6     | apll_filter | Α              | External Analog PLL Loop Filter terminal.                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| В6     | filter_ref0 | Α              | Analog PLL External Loop Filter Reference.                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| C6     | filter_ref1 | Α              | Analog PLL External Loop Filter Reference.                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| JTAG a | and Test    |                |                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| J4     | tdo         | 0              | <b>Test Serial Data Out (Output).</b> JTAG serial data is output on this pin on the falling edge of tck. This pin is held in high impedance state when JTAG scan is not enabled.                                                                                                                                                        |  |  |  |  |  |

| K2     | tdi         | I <sub>u</sub> | <b>Test Serial Data In (Input).</b> JTAG serial test instructions and data are shifted in on this pin. This pin is internally pulled up to Vdd. If this pin is not used then it should be left unconnected.                                                                                                                             |  |  |  |  |  |

| H4     | trst_b      | l <sub>u</sub> | <b>Test Reset (LVCMOS).</b> Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-Reset state. This pin should be pulsed low on power-up to ensure that the device is in the normal functional state. This pin is internally pulled up to Vdd. If this pin is not used then it should be connected to GND. |  |  |  |  |  |

| K3     | tck         | I              | <b>Test Clock (LVCMOS):</b> Provides the clock to the JTAG test logic. If this pin is not used then it should be pulled down to GND.                                                                                                                                                                                                    |  |  |  |  |  |

| Pin#                                         | Name               | I/O<br>Type    | Description                                                                                                                                                                                                                                                           |  |  |  |  |  |

|----------------------------------------------|--------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| J3                                           | tms                | l <sub>u</sub> | <b>Test Mode Select (LVCMOS).</b> JTAG signal that controls the state transitions of the TAP controller. This pin is internally pulled up to V <sub>DD</sub> . If this pin is not used then it should be left unconnected.                                            |  |  |  |  |  |

| Maste                                        | Clock              |                |                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| K4                                           | osci               | I              | Oscillator Master Clock Input (LVCMOS). This input accepts a 20 MHz reference from a clock oscillator (TCXO, OCXO). The stability and accuracy of the clock at this input determines the free-run accuracy and the long term holdover stability of the output clocks. |  |  |  |  |  |

| K5                                           | osco               | 0              | Oscillator Master Clock Output (LVCMOS). This pin must be left unconnected when the osci pin is connected to a clock oscillator.                                                                                                                                      |  |  |  |  |  |

| Miscel                                       | laneous            |                |                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| J6                                           | IC                 |                | Internal Connection. Connect to ground.                                                                                                                                                                                                                               |  |  |  |  |  |

| C5<br>B5<br>K6<br>H10                        | IC                 |                | Internal Connection. Leave unconnected.                                                                                                                                                                                                                               |  |  |  |  |  |

| H7<br>G3<br>E10<br>F10<br>D1                 | NC                 |                | No Connection. Leave Unconnected.                                                                                                                                                                                                                                     |  |  |  |  |  |

| Power                                        | and Ground         |                |                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| D9<br>E4<br>G8<br>G9<br>J8<br>J9<br>H6<br>H8 | V <sub>DD</sub>    | P P P P P      | Positive Supply Voltage. +3.3V <sub>DC</sub> nominal.                                                                                                                                                                                                                 |  |  |  |  |  |

| E8<br>F4                                     | $V_{CORE}$         | P<br>P         | Positive Supply Voltage. +1.8V <sub>DC</sub> nominal.                                                                                                                                                                                                                 |  |  |  |  |  |

| A5<br>A8<br>C10                              | AV <sub>DD</sub>   | P<br>P<br>P    | Positive Analog Supply Voltage. +3.3V <sub>DC</sub> nominal.                                                                                                                                                                                                          |  |  |  |  |  |

| B7<br>B8<br>H2                               | AV <sub>CORE</sub> | P<br>P<br>P    | Positive Analog Supply Voltage. +1.8V <sub>DC</sub> nominal.                                                                                                                                                                                                          |  |  |  |  |  |

| Pin# | Name             | I/O<br>Type | Description             |  |  |  |  |

|------|------------------|-------------|-------------------------|--|--|--|--|

| D4   | $V_{SS}$         | G           | Ground. 0 Volts.        |  |  |  |  |

| D5   | 33               | G           |                         |  |  |  |  |

| D6   |                  | G           |                         |  |  |  |  |

| D7   |                  | G<br>G      |                         |  |  |  |  |

| E5   |                  | G           |                         |  |  |  |  |

| E6   |                  | G<br>G      |                         |  |  |  |  |

| E7   |                  | G           |                         |  |  |  |  |

| F5   |                  | G<br>G      |                         |  |  |  |  |

| F6   |                  | G<br>G      |                         |  |  |  |  |

| F7   |                  | G           |                         |  |  |  |  |

| G4   |                  | G<br>G      |                         |  |  |  |  |

| G5   |                  | G           |                         |  |  |  |  |

| G6   |                  | G<br>G      |                         |  |  |  |  |

| G7   |                  | G           |                         |  |  |  |  |

| E9   |                  | G<br>G      |                         |  |  |  |  |

| F8   |                  | G           |                         |  |  |  |  |

| F9   |                  | G           |                         |  |  |  |  |

| H9   |                  | G           |                         |  |  |  |  |

| A7   | AV <sub>SS</sub> | G           | Analog Ground. 0 Volts. |  |  |  |  |

| C7   | 00               | G           |                         |  |  |  |  |

| C8   |                  | G           |                         |  |  |  |  |

| C9   |                  | G           |                         |  |  |  |  |

| D8   |                  | G<br>G      |                         |  |  |  |  |

| Н3   |                  | G           |                         |  |  |  |  |

- I Input

- I<sub>d</sub> Input, Internally pulled down

- Iu Input, Internally pulled up

- O Output

- A Analog

- P Power

- G Ground

## 1.0 Pin Diagram

**TOP VIEW**

| 1 | 1          | 2                  | 3                     | 4                  | 5                           | 6                    | 7                     | 8                           | 9                           | 10               |

|---|------------|--------------------|-----------------------|--------------------|-----------------------------|----------------------|-----------------------|-----------------------------|-----------------------------|------------------|

| Α | Sync1      | sync2              | ref2                  | ref7               | $\bigcirc$ AV <sub>DD</sub> | apll_filter          | O<br>AV <sub>SS</sub> | O<br>AV <sub>DD</sub>       | diff0_p                     | diff1_p          |

| В | sync0      | ref1               | ref4                  | ref5               | IC                          | filter_ref0          | AV <sub>CORE</sub>    | AV <sub>CORE</sub>          | O<br>diff1_n                | diff0_n          |

| С | ref0       | mode_0             | ref3                  | ref6               | IC                          | filter_ref1          | O<br>AV <sub>SS</sub> | O<br>AV <sub>SS</sub>       | $\bigcirc$ AV <sub>SS</sub> | AV <sub>DD</sub> |

| D | NC         | mode_1             | diff1_en              | $\bigvee_{V_{SS}}$ | $\bigvee_{V_{SS}}$          | O <sub>VSS</sub>     | $\bigvee_{V_{SS}}$    | $\bigcirc$ AV <sub>SS</sub> | $\bigvee_{V_{DD}}$          | apll_clk0        |

| E | ref_out    | sck/<br>scl        | cs_b/<br>asel0        | VDD                | $\bigvee_{V_{SS}}$          | ○<br>V <sub>SS</sub> | O <sub>VSS</sub>      | V <sub>CORE</sub>           | $\bigvee_{V_{SS}}$          | O<br>NC          |

| F | si/<br>sdh | asel2              | asel1                 | V <sub>CORE</sub>  | $\bigcup_{V_{SS}}$          | O <sub>Vss</sub>     | O <sub>VSS</sub>      | ○<br>V <sub>SS</sub>        | O <sub>VSS</sub>            | NC NC            |

| G | so         | int_b              | NC                    | $\bigvee_{V_{SS}}$ | $\bigvee_{V_{SS}}$          | $\bigvee_{V_{SS}}$   | $\bigvee_{V_{SS}}$    | $\bigvee_{V_{DD}}$          | $\bigvee_{V_{DD}}$          | apll_clk1        |

| Н | lock       | AV <sub>CORE</sub> | O<br>AV <sub>SS</sub> | trst_b             | rst_b                       | $\bigvee_{V_{DD}}$   | NC                    | $\bigvee_{V_{DD}}$          | O<br>V <sub>SS</sub>        | IC               |

| J | hold       | i2c_en             | tms                   | tdo                | hs_en                       | IC                   | <br>p0_fp1            | $\bigvee_{V_{DD}}$          | $\bigvee_{V_{DD}}$          | p1_clk0          |

| К | diff0_en   | tdi                | tck                   | osci               | osco                        | IC                   | p0_clk1               | p0_fp0                      | p0_clk0                     | p1_clk1          |

- A1 corner is identified with a dot.

## 2.0 Functional Description

The ZL30131 OC-192/STM-64 PDH/SONET/SDH/10GbE Network Interface Synchronizer is a highly integrated device that provides timing for both PDH/SONET/SDH and Ethernet network interface cards. A functional block diagram is shown in Figure 1.

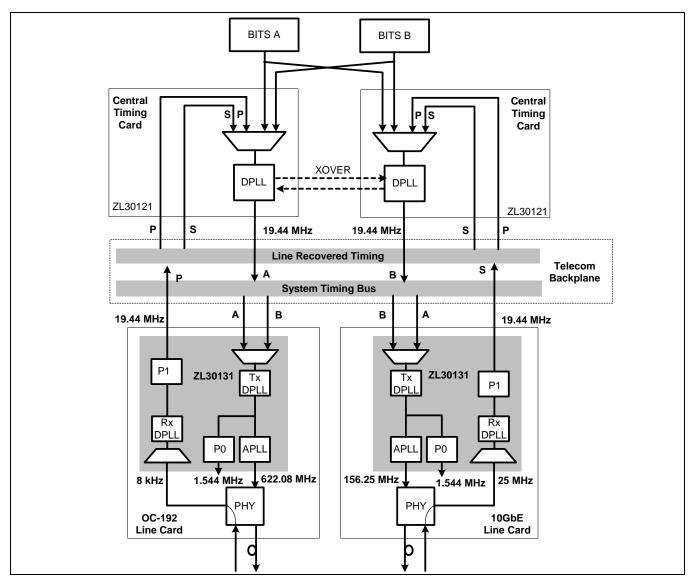

This device is ideally suited for designs that require both a transmit timing path (backplane to PHY) and a receive timing path (PHY to backplane). Each path is controlled with separate DPLLs (Tx DPLL, Rx DPLL) which are both independently configurable through the serial interface (SPI or I<sup>2</sup>C). A typical application of the ZL30131 is shown in Figure 2. In this application, the ZL30131 translates the 19.44 MHz clock from the telecom rate backplane (system timing bus), translates the frequency to 622.08 MHz or 156.25 MHz for the PHY Tx clock, and filters the jitter to ensure compliance with the related standards. A programmable synthesizer (P0) provides synchronous PDH clocks with multiples of 8 kHz for generating PDH interface clocks. On the receive path, the Rx DPLL and the P1 synthesizer translate the line recovered clock (8 kHz or 25 MHz) from the PHY to the 19.44 MHz telecom backplane (line recovered timing) for the central timing cards. The ZL30131 allows easy integration of Ethernet line rates with today's telecom backplanes.

Figure 2 - Typical Application of the ZL30131

## For more information about all Zarlink products visit our Web Site at www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE