## **ABSOLUTE MAXIMUM RATINGS**

| Symbol               | Parameter                                                              |                               | Value                   | Unit |

|----------------------|------------------------------------------------------------------------|-------------------------------|-------------------------|------|

| V <sub>CC</sub>      | DC Input Voltage                                                       |                               | -0.3 to 6               | V    |

| V <sub>OUTGATE</sub> | Max Gate Drive Output Voltage                                          |                               | -0.3 to V <sub>CC</sub> | V    |

| V <sub>INHIBIT</sub> | Max INHIBIT Voltage (*)                                                |                               | -0.6 to V <sub>CC</sub> | V    |

| V <sub>CK</sub>      | Clock Input Voltage Range (*)                                          | Clock Input Voltage Range (*) |                         | V    |

| I <sub>LX</sub>      | Switching Peak Current                                                 |                               | 2                       | Α    |

| P <sub>TOT</sub>     | Continuous Power Dissipation at T <sub>A</sub> =105°C without heatsink |                               | 270                     | mW   |

| ESD                  | Human Body Model                                                       | Pins 1,2, 4, 5, 6, 7, 8       | ±1                      | KV   |

|                      |                                                                        | Pin 3                         | ±0.9                    | KV   |

| T <sub>stg</sub>     | Storage Temperature Range                                              |                               | -55 to +150             | °C   |

| T <sub>op</sub>      | Operating Junction Temperature Range                                   |                               | -40 to +125             | °C   |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these condition is not implied.

(\*) A higher positive voltage level can be applied to the pin with a resistor which limits the current flowing into the pin to 10mA maximum

### THERMAL DATA

| Symbol               | Parameter                               | SO-8 | Unit |

|----------------------|-----------------------------------------|------|------|

| R <sub>thj-amb</sub> | Thermal Resistance Junction-case        | 40   | °C/W |

| R <sub>thj-amb</sub> | Thermal Resistance Junction-ambient (*) | 160  | °C/W |

<sup>(\*)</sup> This value is referred to one layer pcb board with minimum copper connections for the leads. a minimum value of 120 °C/W can be obtained improving thermal conductivity of the board

## **ORDERING CODES**

| TYPE    | SO-8      | SO-8 (T&R)   |

|---------|-----------|--------------|

| STSR2P  | STSR2PCD  | STSR2PCD-TR  |

| STSR2PM | STSR2PMCD | STSR2PMCD-TR |

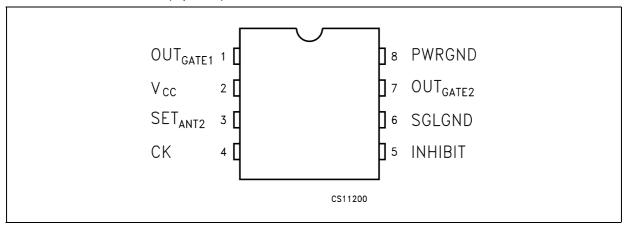

# **CONNECTION DIAGRAM** (top view)

47/ 2/12

# **PIN DESCRIPTION**

| Pin N° | Symbol               | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|--------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

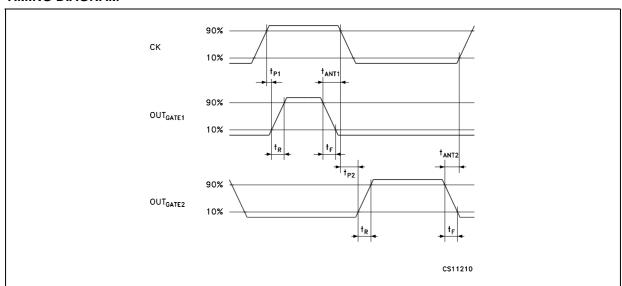

| 1      | OUT <sub>GATE1</sub> | Gate Drive signal for Rectifier MOSFET. Anticipation (t <sub>ANT1</sub> ) in turning off OUT <sub>GATE1</sub> is provided when the clock input goes to low level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 2      | V <sub>CC</sub>      | The supply voltage range from 4.5V to 5.5V allows applications with logic gate threshold mosfets. UVLO feature guarantees proper start-up while it avoids undesirable driving during eventual dropping of the supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 3      | SET <sub>ANT2</sub>  | The voltage on this pin sets the anticipation (t <sub>ANT1</sub> ) in turning off the OUT <sub>GATE2</sub> . It is possible to choose among three different anticipation times by discrete partitioning of the supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 4      | СК                   | This input provides synchronization for IC's operations, being the transitions between the two output conditions based on a positive threshold, equal for the two slopes. A smart internal control logic mechanism using a 15MHz internal oscillator generates proper anticipation timing at the turn-off of each output. This feature allows safe turn-off of Synchronous Rectifiers avoiding any eventual shoot-through situation on secondary side at both transitions. Smart clock revelation mechanism makes these operations independent by false triggering pulses generated in light load conditions and by particular demagnetization techniques. Absolute maximum voltage rating of the pin can be exceeded limiting the current flowing into the pin to 10mA max. |  |  |  |  |

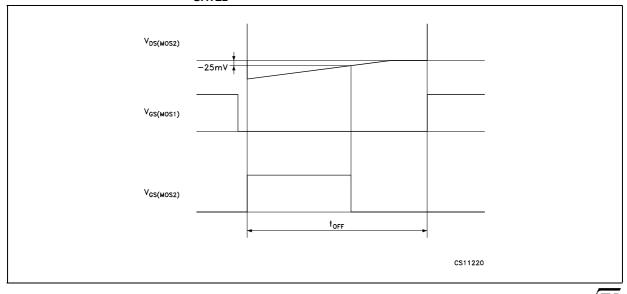

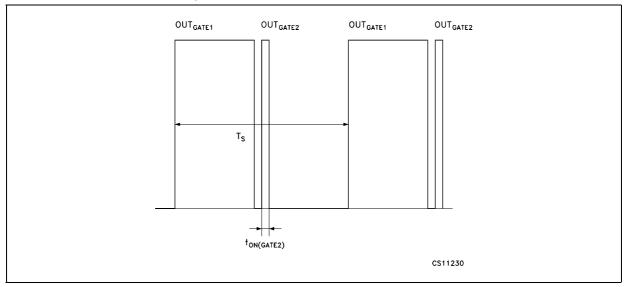

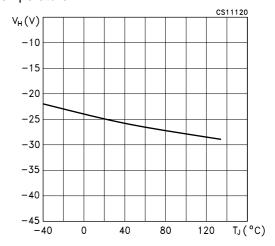

| 5      | INHIBIT              | This input enables OUT <sub>GATE2</sub> to work when its voltage is lower than the negative threshold voltage (V <sub>INHIBIT</sub> <v<sub>H). If V<sub>INHIBIT</sub>&gt;V<sub>H</sub> the OUT<sub>GATE2</sub> will be high for a minimum conduction time (t<sub>ON(GATE2)</sub>). In typical forward converter application, it is possible to turn off the freewheeling MOSFET when the current through it tends to reverse, allowing discontinuous conduction mode and providing protection to the converter from eventual sinking current from the load. Absolute maximum voltage rating of the pin can be exceeded limiting the current flowing into the pin to 10mA max.</v<sub>                                                                                        |  |  |  |  |

| 6      | SGLGND               | Reference for all the control logic signals. This pin is completely separated from the PWRGND to prevent eventual disturbances to affect the control logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 7      | OUT <sub>GATE2</sub> | Gate Drive signal for Freewheeling MOSFET. Anticipation [t <sub>ANT2</sub> ] in turning off OUT <sub>GATE2</sub> is provided when the clock input goes to high level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 8      | PWRGND               | Reference for power signals, this pin carries the full peak currents for the two outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

**ELECTRICAL CHARACTERISTICS** ( $V_{CC}$ =5V, CK= 250kHz,  $V_{INHIBIT}$  =-200mV,  $T_{J}$  =-40 to 125°C, unless otherwise specified.)

| Symbol                 | Parameter                                                  | Test Conditions                                 | Min. | Тур. | Max. | Unit         |

|------------------------|------------------------------------------------------------|-------------------------------------------------|------|------|------|--------------|

| SUPPLY IN              | IPUT AND UNDER VOLTAG                                      | E LOCK OUT                                      |      |      |      |              |

| $V_{CCON}$             | Start Threshold                                            |                                                 |      | 3.8  | 4    | V            |

| $V_{CCOFF}$            | Turn OFF Threshold After Start                             |                                                 | 3.5  | 3.6  |      | V            |

| V <sub>Z</sub>         | Zener Voltage                                              | CK=0V I <sub>Z</sub> = 2mA                      | 5.5  | 5.8  | 6    | V            |

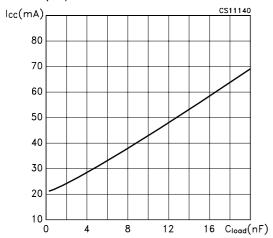

| I <sub>CC</sub>        | Unloaded Supply Current                                    | OUT <sub>GATE1,2</sub> = no load                |      | 22   | 30   | mA           |

|                        |                                                            | CK=0V OUT <sub>GATE1,2</sub> = no load          |      | 3    | 5    |              |

| GATE DRIV              | VER OUTPUTS                                                |                                                 | •    |      | •    |              |

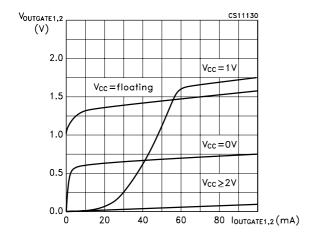

| V <sub>OL</sub>        | Output Low Voltage                                         | I <sub>OUTGATE1,2</sub> =-200mA                 |      | 0.10 | 0.16 | V            |

| V <sub>OH</sub>        | Output High Voltage                                        | I <sub>OUTGATE1,2</sub> =200mA                  | 4.70 | 4.85 |      | V            |

| I <sub>OUT</sub>       | Output Source Peak<br>Current                              |                                                 |      | 2    |      | Α            |

|                        | Output Sink Peak Current                                   |                                                 |      | 3.5  |      |              |

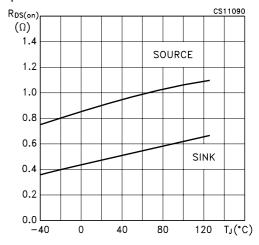

| R <sub>OUT</sub>       | Output Series Source<br>Resistance                         | I <sub>OUTGATE1,2</sub> =-200mA                 |      | 0.75 | 1.5  | Ω            |

|                        | Output Series Sink<br>Resistance                           | I <sub>OUTGATE1,2</sub> =200mA                  |      | 0.5  | 0.8  |              |

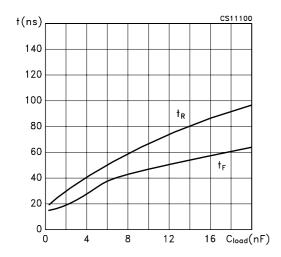

| $t_{R}$                | OUT <sub>GATE1,2</sub> Rise Time                           | C <sub>LOAD</sub> =5nF (Note 1)                 |      | 40   |      | ns           |

| t <sub>F</sub>         | OUT <sub>GATE1,2</sub> Fall Time                           | C <sub>LOAD</sub> =5nF (Note 1)                 |      | 30   |      | ns           |

| t <sub>P1</sub>        | Clock Propagation Delay to Turn ON of OUT <sub>GATE1</sub> | No Load                                         |      | 130  |      | ns           |

| t <sub>P2</sub>        | Clock Propagation Delay to Turn ON of OUT <sub>GATE2</sub> | No Load                                         |      | 50   |      | ns           |

| TURN-OFF               | ANTICIPATION TIME                                          |                                                 | l    | l    |      |              |

| t <sub>ANT1</sub>      | OUT <sub>GATE1</sub> Turn-off<br>Anticipation Time         | No Load                                         |      | 75   |      | ns           |

| t <sub>ANT2</sub>      | OUT <sub>GATE2</sub> Turn-off                              | $V_{ANT2} = 0$ to $1/3V_{CC}$ ; no load         |      | 75   |      | ns           |

|                        | Anticipation Time                                          | $V_{ANT2} = 1/3V_{CC}$ to $2/3V_{CC}$ ; no load |      | 150  |      |              |

|                        |                                                            | $V_{ANT2} = 2/3V_{CC}$ to $V_{CC}$ ; no load    |      | 225  |      |              |

| I <sub>SETANT2</sub>   | Leakage Current (Note 2)                                   | 7.11.12                                         | -0.1 |      | 0.1  | μΑ           |

|                        | JT <sub>GATE2</sub> ENABLE                                 |                                                 |      |      |      | · ·          |

| V <sub>H</sub>         | Threshold Voltage                                          | T <sub>J</sub> = 25°C                           | -30  | -25  |      | mV           |

| I <sub>H</sub>         | Leakage Current (Note 2)                                   | V <sub>INHIBIT</sub> = 200mV                    |      | -400 |      | nA           |

| 11                     | ,                                                          | V <sub>INHIBIT</sub> = -200mV                   |      |      | 1    | μΑ           |

| t <sub>ON(GATE2)</sub> | OUT <sub>GATE1</sub> Turn-off<br>Anticipation Time         | V <sub>INHIBIT</sub> = 200mVNo Load             |      | 250  |      | ns           |

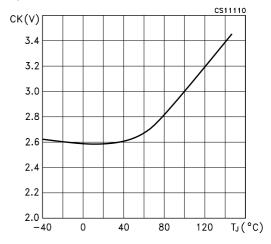

| V <sub>CK</sub>        | Reference Voltage                                          | T <sub>J</sub> = 25°C                           |      | 2.6  | 2.8  | V            |

| I <sub>CK</sub>        | LX Leakage Current                                         |                                                 |      | -    | 600  | μΑ           |

| D <sub>OFF</sub>       | Duty Cycle Shut Down                                       | $T_J = 25^{\circ}C$ for STSR2P                  | 13   | 14   |      | <del>%</del> |

| - OFF                  | Duty Cycle Turn ON after<br>Shut Down                      | $T_J = 25^{\circ}C$ for STSR2P                  | 1.0  | 18   | 20   | ,,,          |

| t <sub>PW</sub>        | Minimum Pulse Width                                        | STSR2PM                                         |      |      | 200  | ns           |

Note1:  $t_R$  is measured between 10% and 90% of the final voltage;  $t_F$  is measured between 90% and 10% on the initial voltage Note2: Parameter guaranteed by design

## **TIMING DIAGRAM**

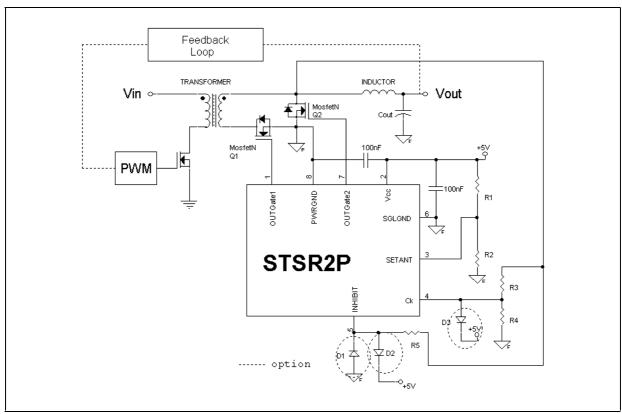

## APPLICATION INFORMATION: STSR2 IN FORWARD CONVERTER SECONDARY SIDE

- NOTES

1) Ceramic Capacitors C1 and C2 must be placed very close to the IC;

- 2) R1 and R2 set the anticipation time by partitioning the V<sub>CC</sub> voltage; 3) R3 and R4 is a resistor divider meant to provide the correct CK voltage range;

- 3) R3 and R4 is a resistor divider meant to provide the correct CR voltage range;

4) R5 limits the current flowing through diode D2 when Freewheeling drain voltage is high;

5) D1 could be necessary to protect INHIBIT pin from negative voltages.

6) D2 could be necessary to protect INHIBIT pin from voltages higher than V<sub>CC</sub>.

7) D3 could be necessary to protect CK pin from voltages higher than V<sub>CC</sub>.

8) SGLGND layout trace must not include OUT<sub>GATE1,2</sub> current paths.

9) A capacitor in parallel with R4 could be necessary to eliminate turn off voltage spike.

47/

### **EXAMPLE OF COMPONENTS SELECTION FOR A FORWARD CONVERTER**

Forward Specification:

$V_{IN} = 36 - 72V$

V<sub>OUT</sub>=3.3V

n=Np/Ns=4.5

$R_3$  and  $R_4$  are calculated assuring a minimum voltage of 2.8V at CK pin. At 36V input, the voltage on the secondary winding is 36/4.5=8V. Choosing  $R_3$ =1.5K $\Omega$ ,  $R_4$  results to be:

$$R_4 \ge \frac{V_{CK} \times R_3}{V_{IN} - I_{CK(2.8)} \times R_3 - V_{CK}} = 1k\Omega \times \frac{2.8V \times (1.5k\Omega)}{8V - 220\mu A \times 1.5k\Omega - 2.8V} = 862\Omega$$

$R_{\Delta}\!\!=\!\!1k\Omega$  is chosen. At 72V input the current at CK pin is calculated as:

$$I_{CK} = \frac{V_{IN(max)} - V_{CC} - 0.3}{R_3} = \frac{16 - 5 - 0.3}{1.5k\Omega} = 7.13mA$$

This value is below the maximum allowable current flowing into the CK pin (10mA). If the 10mA value is exceeded an external diode connected to  $V_{CC}$  must be added (D3).

$R_1$  and  $R_2$  values set the anticipation time for OUT<sub>GATE2</sub>. For  $R_1=\infty$  and  $R_2=0$ ,  $t_{ANT2}=75$ ns; for  $R_1=R_2=10$ k $\Omega$ ,  $t_{ANT2}=150$ ns; for  $R_1=0$  and  $R_2=\infty$ ,  $t_{ANT2}=225$ ns.

The RC group composed by  $R_5$  and the parasitic capacitance of Inhibit pin (typically 5pF) delays the signal on Inhibit comparator. This delay must be lower than 200ns. This condition imposes a maximum value for  $R_5$  of about  $20k\Omega$ .

In general a suggested value for  $R_5$  is  $10k\Omega$ . At 72V input, the secondary voltage is 16V, so the maximum current flowing into Inhibit pin is  $16V/10k\Omega=1.6mA$  which is below the maximum allowable current for the pin (10mA). If the 10mA value is exceeded an external diode (D2) connected to  $V_{CC}$  must be added.

The maximum negative voltage of -0.6V must be guaranteed for the Inhibit pin. If this negative voltage is exceeded the current must be limited to 50mA. If necessary, a diode (D1) connected to SGLGND can be added to satisfy this specification.

# INHIBIT OPERATION OF OUT GATE2 IN DISCONTINUOUS CONDUCTION MODE

# INHIBIT OPERATION OF $\mathsf{OUT}_{\mathsf{GATE2}}$

NOTE:  $V_{INHIBIT} = +200 \text{mV}$

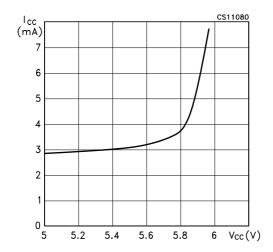

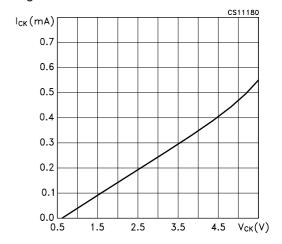

# **TYPICAL PERFORMANCE CHARACTERISTICS** (unless otherwise specified $T_i = 25$ °C

Figure 1 : Zener Characteristics

Figure 2: Rise and Fall Time vs Load Capacitor

Figure 3 :  $OUT_{GATE1,2}$  vs Characteristics

**Figure 4 :** Sink-Source ON Resistance vs Temperature

**Figure 5 :** Clock Threshold Voltage vs Temperature

**Figure 6 :** INHIBIT Threshold Voltage vs Temperature

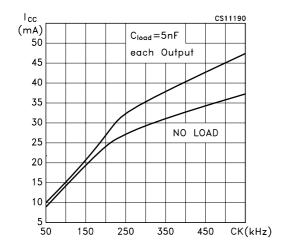

**Figure 7 :** Supply Current vs Load Capacitor (each output)

Figure 8 : Supply Current vs Clock Frequency

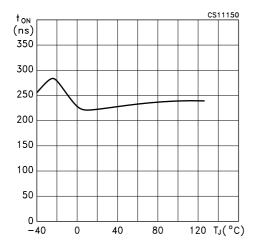

Figure 9 :  $T_{ON(GATE2)}$  vs Temperature

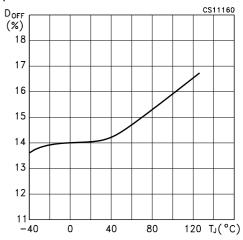

**Figure 10 :** Duty Cycle Shut Down vs Temperature

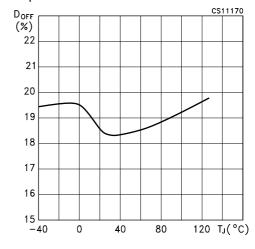

**Figure 11**: Duty Cycle Turn ON After Shut Down vs Temperature

**Figure 12 :** Clock Leakage Current vs Clock Voltage

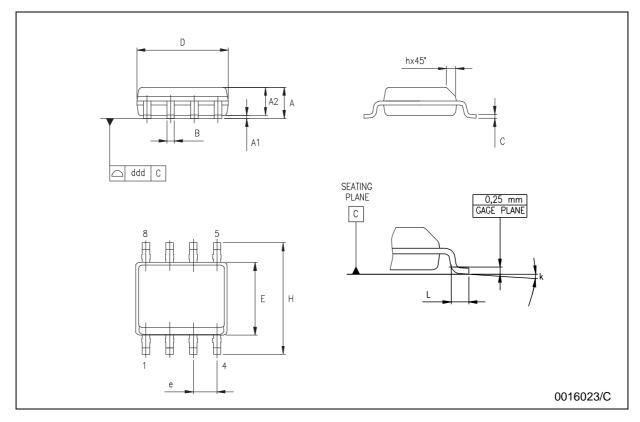

# **SO-8 MECHANICAL DATA**

| DIM. | mm.       |      |      | inch  |       |       |  |

|------|-----------|------|------|-------|-------|-------|--|

|      | MIN.      | TYP  | MAX. | MIN.  | TYP.  | MAX.  |  |

| А    | 1.35      |      | 1.75 | 0.053 |       | 0.069 |  |

| A1   | 0.10      |      | 0.25 | 0.04  |       | 0.010 |  |

| A2   | 1.10      |      | 1.65 | 0.043 |       | 0.065 |  |

| В    | 0.33      |      | 0.51 | 0.013 |       | 0.020 |  |

| С    | 0.19      |      | 0.25 | 0.007 |       | 0.010 |  |

| D    | 4.80      |      | 5.00 | 0.189 |       | 0.197 |  |

| E    | 3.80      |      | 4.00 | 0.150 |       | 0.157 |  |

| е    |           | 1.27 |      |       | 0.050 |       |  |

| Н    | 5.80      |      | 6.20 | 0.228 |       | 0.244 |  |

| h    | 0.25      |      | 0.50 | 0.010 |       | 0.020 |  |

| L    | 0.40      |      | 1.27 | 0.016 |       | 0.050 |  |

| k    | 8° (max.) |      |      |       |       |       |  |

| ddd  |           |      | 0.1  |       |       | 0.04  |  |

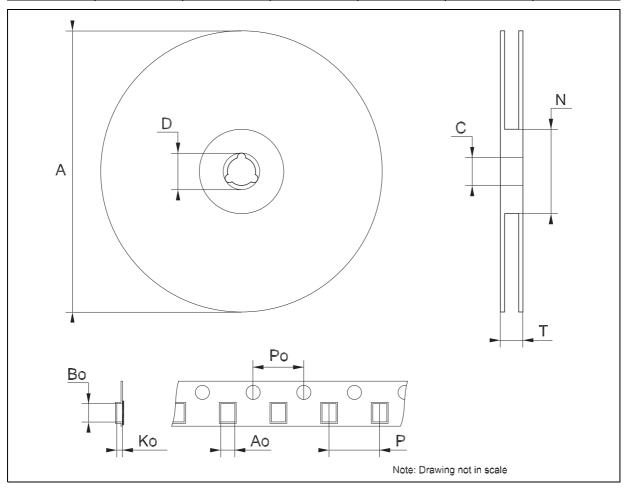

# Tape & Reel SO-8 MECHANICAL DATA

| DIM. | mm.  |     |      | inch  |      |        |  |

|------|------|-----|------|-------|------|--------|--|

|      | MIN. | TYP | MAX. | MIN.  | TYP. | MAX.   |  |

| А    |      |     | 330  |       |      | 12.992 |  |

| С    | 12.8 |     | 13.2 | 0.504 |      | 0.519  |  |

| D    | 20.2 |     |      | 0.795 |      |        |  |

| N    | 60   |     |      | 2.362 |      |        |  |

| Т    |      |     | 22.4 |       |      | 0.882  |  |

| Ao   | 8.1  |     | 8.5  | 0.319 |      | 0.335  |  |

| Во   | 5.5  |     | 5.9  | 0.216 |      | 0.232  |  |

| Ko   | 2.1  |     | 2.3  | 0.082 |      | 0.090  |  |

| Ро   | 3.9  |     | 4.1  | 0.153 |      | 0.161  |  |

| Р    | 7.9  |     | 8.1  | 0.311 |      | 0.319  |  |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics All other names are the property of their respective owners

© 2003 STMicroelectronics - All Rights Reserved STMicroelectronics GROUP OF COMPANIES

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.

http://www.st.com