# **Ordering Information**

| Part Number | Marking | Output<br>Voltage* | Junction<br>Temperature Range | Package              | Lead Finish |

|-------------|---------|--------------------|-------------------------------|----------------------|-------------|

| MIC2285AYMT | WPA     | Adj.               | –40° to +125°C                | 10-Pin 2x2 Thin MLF® | Pb-free     |

#### Note

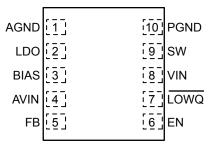

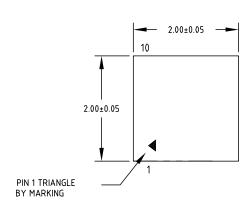

### **Pin Configuration**

10-Pin 2mm x 2mm Thin MLF® (MT)

### **Pin Description**

| Pin Number | Pin Name | Pin Function                                                                                                                                                                                                                                                           |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | AGND     | Analog (signal) Ground.                                                                                                                                                                                                                                                |

| 2          | LDO      | LDO Output (Output): Connect to V <sub>OUT</sub> for LDO mode operation.                                                                                                                                                                                               |

| 3          | BIAS     | Internal circuit bias supply. Must be decoupled to signal ground with a 0.1µF capacitor and should not be loaded.                                                                                                                                                      |

| 4          | AVIN     | Analog Supply Voltage (Input): Supply voltage for the analog control circuitry and LDO input power. Requires bypass capacitor to GND.                                                                                                                                  |

| 5          | FB       | Feedback. Input to the error amplifier. For the Adjustable option, connect to the external resistor divider network to set the output voltage. For fixed output voltage options, connect to $V_{\text{OUT}}$ and an internal resistor network sets the output voltage. |

| 6          | EN       | Enable (Input). Logic low will shut down the device, reducing the quiescent current to less than 5µA.                                                                                                                                                                  |

| 7          | LOWQ     | Enable LDO Mode (Input): Logic low enables the internal LDO and disables the PWM operation. Logic high enables the PWM mode and disables the LDO mode.                                                                                                                 |

| 8          | VIN      | Supply Voltage (Input): Supply voltage for the internal switches and drivers.                                                                                                                                                                                          |

| 9          | SW       | Switch (Output): Internal power MOSFET output switches.                                                                                                                                                                                                                |

| 10         | PGND     | Power Ground.                                                                                                                                                                                                                                                          |

<sup>\*</sup> For other voltage options available, please contact Micrel Marketing for details.

MLF® is a GREEN RoHS compliant package. Lead finish is NiPdAu. Mold compound is Halogen Free.

## Absolute Maximum Ratings<sup>(1)</sup>

#

### Operating Ratings<sup>(2)</sup>

| +2.7V to +5.5V          |

|-------------------------|

| 0.3V to V <sub>IN</sub> |

| -40°C to +125°C         |

|                         |

| 60°C/W                  |

|                         |

### **Electrical Characteristics**(4)

$V_{\text{IN}} = V_{\text{EN}} = V_{\text{LOWQ}} = 3.6 \text{V}; \ L = 0.47 \mu \text{H}; \ C_{\text{OUT}} = 10 \mu \text{F}; \ T_{\text{A}} = 25 ^{\circ} \text{C}, \ unless noted.} \ \textbf{Bold} \ \ values \ indicate} \ \ -40 ^{\circ} \text{C} \leq T_{\text{J}} \leq +125 ^{\circ} \text{C}$

| Parameter                                   | Condition                                                                                                                                   | Min                 | Тур        | Max                 | Units  |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|---------------------|--------|

| Supply Voltage Range                        |                                                                                                                                             | 2.7                 |            | 5.5                 | V      |

| Under-Voltage Lockout<br>Threshold          | (turn-on)                                                                                                                                   | 2.45                | 2.55       | 2.65                | V      |

| UVLO Hysteresis                             |                                                                                                                                             |                     | 100        |                     | mV     |

| Quiescent Current, PWM mode                 | V <sub>FB</sub> = 0.9 * V <sub>NOM</sub> (not switching)                                                                                    |                     | 790        | 900                 | μA     |

| Quiescent Current, LDO mode                 | $V_{LOWQ} = 0V; I_{OUT} = 0mA$                                                                                                              |                     | 20         | 29                  | μA     |

| Shutdown Current                            | V <sub>EN</sub> = 0V                                                                                                                        |                     | 0.01       | 5                   | μA     |

| [Adjustable] Feedback<br>Voltage            | ±1%<br>± 2% (over temperature)                                                                                                              | 0.99<br><b>0.98</b> | 1          | 1.01<br><b>1.02</b> | V      |

| [Fixed Output] Voltages                     | Nominal V <sub>OUT</sub> tolerance                                                                                                          | −1<br><b>−2</b>     |            | +1<br><b>+2</b>     | %<br>% |

| FB pin input current                        |                                                                                                                                             |                     | 1          |                     | nA     |

| Current Limit in PWM Mode                   | V <sub>FB</sub> = 0.9 * V <sub>NOM</sub>                                                                                                    | 0.75                | 1          | 1.85                | Α      |

| Output Voltage Line<br>Regulation           | $V_{OUT} > 2V$ ; $V_{IN} = V_{OUT} + 300$ mV to 5.5V; $I_{LOAD} = 100$ mA<br>$V_{OUT} < 2V$ ; $V_{IN} = 2.7$ V to 5.5V; $I_{LOAD} = 100$ mA |                     | 0.13       |                     | %      |

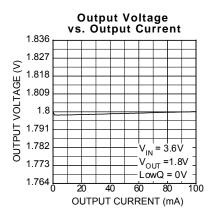

| Output Voltage Load<br>Regulation, PWM Mode | 20mA < I <sub>LOAD</sub> < 300mA                                                                                                            |                     | 0.2        | 0.8                 | %      |

| Output Voltage Load<br>Regulation, LDO Mode | $100\mu$ A < $I_{LOAD}$ < $50$ mA<br>$V_{LOWQ}$ = $0$ V                                                                                     |                     | 0.5        | 1                   | %      |

| Maximum Duty Cycle                          | $V_{FB} \le 0.4V$                                                                                                                           | 100                 |            |                     | %      |

| PWM Switch ON-<br>Resistance                | $I_{SW} = 50$ mA $V_{FB} = 0.7V_{FB\_NOM}$ (High Side Switch)<br>$I_{SW} = -50$ mA $V_{FB} = 1.1V_{FB\_NOM}$ (Low Side Switch)              |                     | 0.4<br>0.4 |                     | Ω<br>Ω |

| Oscillator Frequency                        |                                                                                                                                             | 7.2                 | 8          | 8.8                 | MHz    |

| LOWQ Threshold Voltage                      |                                                                                                                                             | 0.5                 | 0.85       | 1.3                 | V      |

| LOWQ Input Current                          |                                                                                                                                             |                     | 0.1        | 2                   | μΑ     |

| Enable Threshold                            |                                                                                                                                             | 0.5                 | 0.85       | 1.3                 | V      |

| Enable Input Current                        |                                                                                                                                             |                     | 0.1        | 2                   | μΑ     |

| LDO Dropout Voltage                         | I <sub>OUT</sub> = 50mA <b>Note 5</b>                                                                                                       |                     | 110        |                     | mV     |

| Parameter                      | Condition                                                              | Min | Тур | Max | Units |

|--------------------------------|------------------------------------------------------------------------|-----|-----|-----|-------|

| Output Voltage Noise           | $\overline{\text{LOWQ}}$ = 0V; C <sub>OUT</sub> = 10µF, 10Hz to 100kHz |     | 75  |     | μVrms |

| LDO Current Limit              | $\overline{\text{LOWQ}}$ = 0V; V <sub>OUT</sub> = 0V (LDO Mode)        | 60  | 120 |     | mA    |

| Over-Temperature<br>Shutdown   |                                                                        |     | 160 |     | °C    |

| Over-Temperature<br>Hysteresis |                                                                        |     | 20  |     | °C    |

#### Notes

- 1. Exceeding the absolute maximum rating may damage the device.

- 2. The device is not guaranteed to function outside its operating rating.

- 3. Devices are ESD sensitive. Handling precautions recommended. Human body model:  $1.5k\Omega$  in series with 100pF.

- 4. Specification for packaged product only.

- 5. Dropout voltage is defined as the input-to-output differential at which the output voltage drops 2% below its nominal value that is initially measured at a 1V differential. For outputs below 2.7V, the dropout voltage is the input-to-output voltage differential with a minimum input voltage of 2.7V.

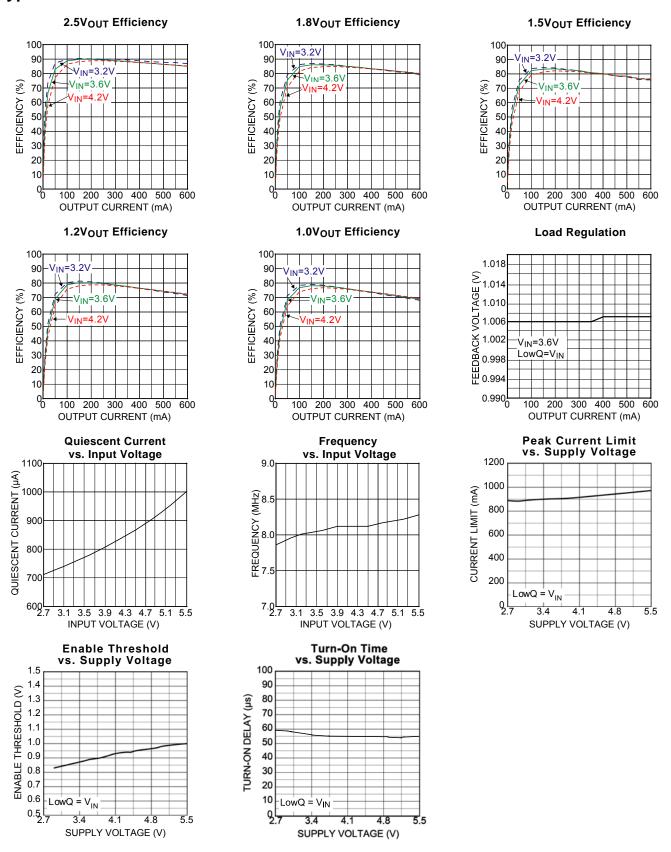

### **Typical Characteristics – PWM Mode**

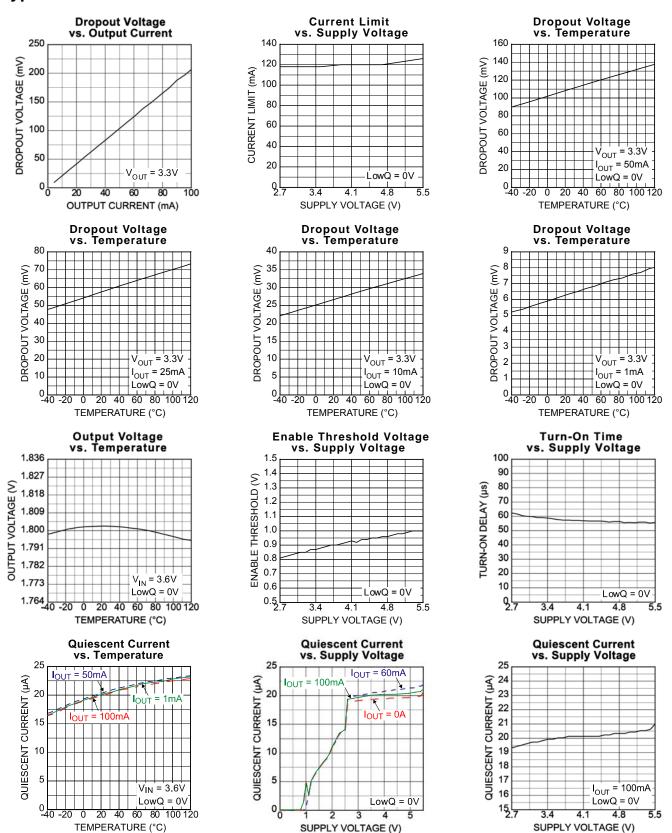

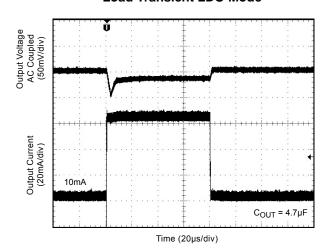

### **Typical Characteristics - LDO Mode**

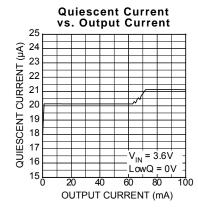

# **Typical Characteristics – LDO Mode (cont.)**

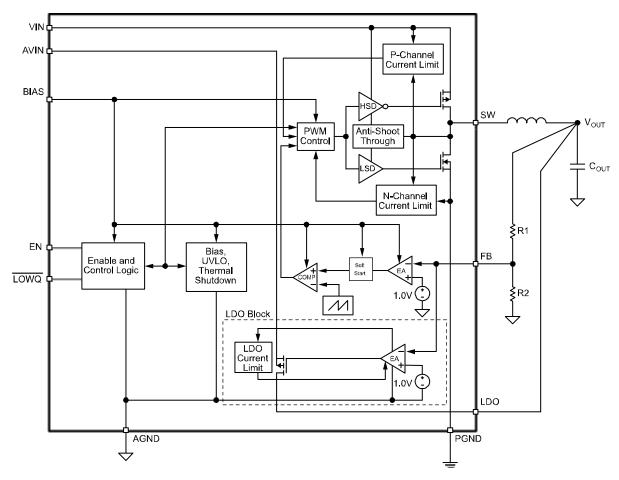

# **Functional Diagram**

MIC2285A Block Diagram

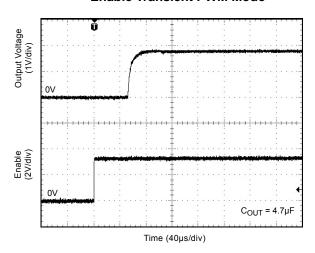

### **Functional Characteristics**

#### **Load Transient PWM Mode**

# egetioV tudtuo Designov formation Designov formation Designov formation Designov formation Designov formation Time (50hs/qin)

#### **Load Transient LDO Mode**

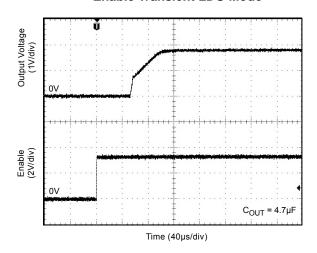

#### **Enable Transient PWM Mode**

#### **Enable Transient LDO Mode**

### **Functional Description**

#### VIN

VIN provides power to the MOSFETs for the switch mode regulator section, along with the current limiting sensing. Due to the high switching speeds, a 1µF capacitor is recommended close to VIN and the power ground (PGND) pin for bypassing. Please refer to layout recommendations.

#### **AVIN**

Analog  $V_{\text{IN}}$  (AVIN) provides power to the LDO section. AVIN and VIN must be tied together. Careful layout should be considered to ensure high frequency switching noise caused by VIN is reduced before reaching AVIN.

#### **LDO**

The LDO pin is the output of the linear <u>regulator</u> and should be connected to the output. In LOWQ mode (LOWQ<1.5V), the LDO provides the output voltage. In PWM mode (LOWQ>1.5V), the LDO pin is high impedance.

#### ΕN

The enable pin provides a logic level control of the output. In the off state, supply current of the device is greatly reduced (typically <1µA). Also, in the off state, the output drive is placed in a "tri-stated" condition, where both the high side P-channel MOSFET and the low-side N-channel are in an "off" or non-conducting state. Do not drive the enable pin above the supply voltage.

#### **LOWQ**

The  $\overline{LOWQ}$  pin provides a logic level control between the internal PWM mode and the low noise linear regulator mode. With  $\overline{LOWQ}$  pulled low (<0.5V), quiescent current of the device is greatly reduced by switching to a low noise linear regulator mode that has a typical  $I_Q$  of 20µA. In linear (LDO) mode, the output can deliver 60mA of current to the output. By placing  $\overline{LOWQ}$  high (>1.5V), this transitions the device into a constant frequency PWM buck regulator mode. This allows the device the ability to efficiently deliver up to 500mA of output current at the same output voltage.

#### **BIAS**

The BIAS pin supplies the power to the internal power to the control and reference circuitry. The bias is powered from the input voltage through an RC lowpass filter. The RC lowpass filter frequency must

be

$$\geq \frac{1}{2\pi(20.5\Omega)(100nF)}$$

.

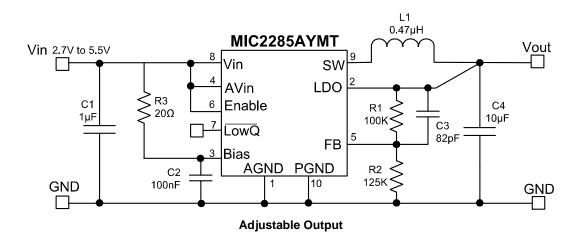

#### FB

The feedback pin (FB) provides the control path to control the output. For adjustable versions, a resistor divider connecting the feedback to the output is used to adjust the desired output voltage. The output voltage is calculated as follows:

$$V_{OUT} = V_{REF} \times \left(\frac{R1}{R2} + 1\right)$$

Where  $V_{REF}$  is equal to 1.0V.

A feedforward capacitor is recommended for most designs using the adjustable output voltage option. To reduce battery current draw, a 100K feedback resistor is recommended from the output to the FB pin (R1). Also, a feedforward capacitor should be connected between the output and feedback (across R1). The large resistor value and the parasitic capacitance of the FB pin can cause a high frequency pole that can reduce the overall system phase margin. By placing a feedforward capacitor, these effects can be significantly reduced. Typically, an 82pF small ceramic capacitor is recommended.

#### SW

The switch (SW) pin connects directly to the inductor and provides the switching current necessary to operate in PWM mode. Due to the high speed switching on this pin, the switch node should be routed away from sensitive nodes.

#### **PGND**

Power ground (PGND) is the ground path for the high current PWM mode. The current loop for the power ground should be as small as possible and separate from the Analog ground (AGND) loop. Refer to the layout considerations for more details.

#### **AGND**

Signal ground (AGND) is the ground path for the biasing and control circuitry. The current loop for the signal ground should be separate from the Power ground (PGND) loop. Refer to the layout considerations for more details.

### **Applications Information**

The MIC2285A is a 500mA PWM power supply that utilizes a LOWQ light load mode to maximize battery efficiency in light load conditions. This is achieved with a LOWQ control pin that when pulled low, shuts down all the biasing and drive current for the PWM regulator, drawing only 18µA of operating current. This allows the output to be regulated through the LDO output, capable of providing 60mA of output current. This method has the advantage of producing a clean, low current, ultra-low noise output in LOWQ mode. During LOWQ mode, the SW node becomes high impedance, blocking current flow. Other methods of reducing quiescent current, such as pulse frequency modulation (PFM), or bursting techniques, create large amplitude, low frequency ripple voltages that can be detrimental to system operation.

When more than 60mA is required, the LOWQ pin can be forced high, causing the MIC2285A to enter PWM mode. In this case, the LDO output makes a "hand-off" to the PWM regulator with virtually no variation in output voltage. The LDO output then turns off allowing up to 600mA of current to be efficiently supplied through the PWM output to the load.

#### **Input Capacitor**

A minimum 1 $\mu$ F ceramic is recommended on the VIN pin for bypassing. X5R or X7R dielectrics are recommended for the input capacitor. Y5V dielectrics lose most of their capacitance over temperature and are therefore, not recommended.

A minimum 1 $\mu$ F is recommended close to the VIN and PGND pins for high frequency filtering. Smaller case size capacitors are recommended due to their lower ESR and ESL. Please refer to layout recommendation section of data sheet for proper layout of the input capacitor.

#### **Output Capacitor**

The MIC2285A is optimized for a  $10\mu F$  output capacitor. A larger value can be used to improve transient response. The MIC2285A utilizes type III internal compensation and utilizes an internal high frequency zero to compensate for the double pole roll off of the LC filter. For this reason, larger output capacitors can create instabilities. X5R or X7R dielectrics are recommended for the output capacitor. Y5V dielectrics lose most of their capacitance over temperature and are therefore, not recommended.

In addition to a  $10\mu F$ , a small 10nF is recommended close to the load for high frequency filtering. Smaller case size capacitors are recommended due to their lower ESR and ESL.

#### **Inductor Selection**

The MIC2285A is designed for use with a 0.47µH inductor. Proper selection should ensure that the inductor can handle the maximum average and peak currents required by the load. Maximum current ratings of the inductor are generally given in two methods; permissible DC current and saturation current. Permissible DC current can be rated either for a 40°C temperature rise or a 10% to 20% loss in inductance. Ensure that the inductor selected can handle the maximum operating current. When saturation current is specified, make sure that there is enough margin that the peak current will not saturate the inductor. Peak inductor current can be calculated as follows:

$$I_{PK} = I_{OUT} + \frac{V_{OUT} \bigg(1 - \frac{V_{OUT}}{V_{IN}}\bigg)}{2 \times f \times L}$$

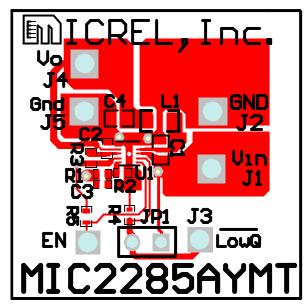

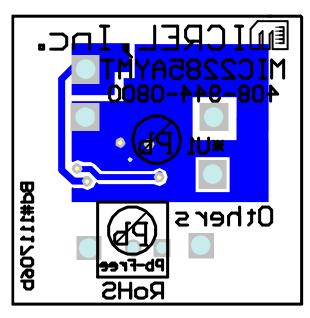

# **Layout Recommendation**

Top

**Bottom**

#### Note

The above figures demonstrate the recommended layout for the MIC2285A adjustable option.

### **Bill of Materials**

| Item | Part Number        | Manufacturer               | Description                                                          | Qty |

|------|--------------------|----------------------------|----------------------------------------------------------------------|-----|

| C1   | 06036D105MAT2      | AVX <sup>(1)</sup>         | 1uE Coromio Congoitor VED 6 2V 0602                                  | 1   |

| Ci   | GRM185R60J105KE21D | Murata <sup>(2)</sup>      | 1μF Ceramic Capacitor X5R, 6.3V 0603                                 | ı   |

| C2   | 0201ZD103MAT2      | AVX <sup>(1)</sup>         | 10nE Caramia Canagitar 6.2\/ 0201                                    | 1   |

| 02   | GRM033R10J103KA01D | Murata <sup>(2)</sup>      | 10nF Ceramic Capacitor, 6.3V 0201                                    | 1   |

| C3   | VJ0402A101KXAA     | Vishay <sup>(3)</sup>      | 100pF Ceramic Capacitor                                              | 1   |

| C4   |                    | AVX <sup>(1)</sup>         | 10μF Ceramic Capacitor X5R, 6.3V 0603                                | 1   |

| C4   |                    | Murata <sup>(2)</sup>      | Toμr Ceramic Capacitor XSK, 0.5V 0003                                | '   |

|      | LQM21PNR47M00      | Murata <sup>(2)</sup>      | $0.47 \mu H$ Inductor, $120 m\Omega$ $2.0 mm$ x $1.25 mm$ x $0.5 mm$ |     |

| L1   |                    | Murata <sup>(2)</sup>      | $0.47 \mu H$ Inductor, $97 m\Omega$ $3.2 mm$ x $2.5 mm$ x $1.55 mm$  | 1   |

|      |                    | Sumida <sup>(4)</sup>      | $0.47\mu H$ Inductor, $94m\Omega$ $3.2mm$ x $3.2mm$ x $1.55mm$       |     |

| R1   | CRCW04021002F      | Vishay-Dale <sup>(3)</sup> | 100kΩ 1% 0402 Resistor                                               | 1   |

|      | CRCW04026652F      | Vishay-Dale <sup>(3)</sup> | 66.5kΩ 1% 0402 Resistor for $2.5$ V <sub>OUT</sub>                   |     |

|      | CRCW04021243F      | Vishay-Dale <sup>(3)</sup> | 124kΩ 1% 0402 Resistor for 1.8 $V_{OUT}$                             |     |

| R2   | CRCW04022003F      | Vishay-Dale <sup>(3)</sup> | 200kΩ 1% 0402 Resistor for 1.5V $_{OUT}$                             | 1   |

|      | CRCW04024023F      | Vishay-Dale <sup>(3)</sup> | 402kΩ 1% 0402 Resistor for 1.2V $_{OUT}$                             |     |

|      |                    |                            | Open for 1.0V <sub>OUT</sub>                                         |     |

| R3   | CRCW040220R5F      | Vishay <sup>(3)</sup>      | 20Ω 1% 0402 Resistor                                                 | 1   |

| U1   | MIC2285AYMT        | Micrel <sup>(5)</sup>      | 8MHz Synchronous Buck Regulator with LOWQ <sup>®</sup> Mode          | 1   |

#### Notes:

AVX: www.avxcorp.com

Murata: www.murata.com

Vishay: www.vishay.com

Sumida: www.sumida.com

Micrel, Inc.: www.micrel.com

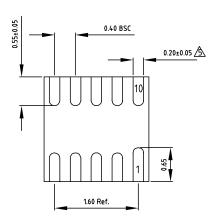

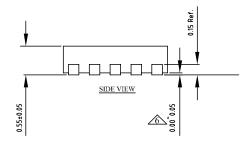

### **Package Information**

NOTE:

1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. MAX. PACKAGE WARPAGE IS 0.05 mm.

3. MAXIMUM ALLOWABE BURRS IS 0.076 mm IN ALL DIRECTIONS.

4. PIN #11D ON TOP WILL BE LASER/INK MARKED.

DIMENSION APPLIES TO METALIZED TERMINAL AND IS MEASURED BETWEEN 0.20 AND 0.25 mm FROM TERMINAL TIP.

APPLIED ONLY FOR TERMINALS.

SIDE VIEW

10-Pin 2mm x 2mm Thin MLF<sup>®</sup> (MT)

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2007 Micrel, Incorporated.