### **Specifications**

### **Maximum Ratings** at Ta = 25°C

| Parameter                   | Symbol               | Conditions                         | Ratings     | Unit |

|-----------------------------|----------------------|------------------------------------|-------------|------|

| Maximum supply voltage      | V <sub>CC</sub> max1 | sv <sub>CC</sub> , v <sub>DD</sub> | 5.5         | V    |

|                             | V <sub>CC</sub> max2 | LEDV <sub>DD</sub>                 | 6           | V    |

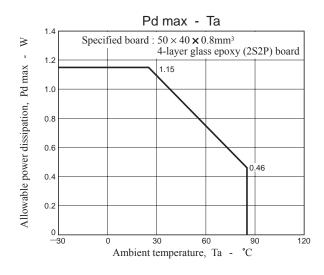

| Allowable power dissipation | Pd max               | Mounted on a board *               | 1.15        | W    |

| Operating temperature       | Topr                 |                                    | -30 to +85  | °C   |

| Storage temperature         | Tstg                 |                                    | -40 to +125 | °C   |

<sup>\*</sup> Designated board : 40mm×50mm×0.8mm, glass epoxy 4-layter board (2S2P)

### **Operating Conditions** at Ta = 25°C

| Parameter        | Symbol              | Conditions         | Ratings    | Unit |

|------------------|---------------------|--------------------|------------|------|

| Supply voltage 1 | V <sub>BAT</sub>    | sv <sub>CC</sub>   | 3 to 4.5   | V    |

| Supply voltage 2 | $V_{DD}$            | V <sub>DD</sub>    | 1.65 to 3  | V    |

| Supply voltage 3 | VLEDV <sub>DD</sub> | LEDV <sub>DD</sub> | 2.7 to 5.5 | V    |

$<sup>^{\</sup>star}$  Power application sequence : 1. V<sub>BAT</sub> 2. V<sub>DD</sub> V<sub>BAT</sub> > V<sub>DD</sub>, No restriction on VLEDV<sub>DD</sub>.

# Electrical Characteristics, Analog Block Ta = 25°C, $V_{BAT} = 3.7V$ , $V_{DD} = 2.6V$ , $LEDV_{DD} = 3.7V$ , unless otherwise specified

| Parameter                          | Symbol Conditions |                                                                                                   |          | Ratings |      | Linit |

|------------------------------------|-------------------|---------------------------------------------------------------------------------------------------|----------|---------|------|-------|

| Parameter Symbol                   |                   | Conditions                                                                                        | min      | typ     | max  | Unit  |

| Consumption current (SV            | CC+VDD+LEDVD      | D)                                                                                                |          |         |      |       |

| Consumption current 1              | I <sub>CC</sub> 1 | RESET: L                                                                                          |          | 0       | 5    | μΑ    |

| Consumption current 2              | I <sub>CC</sub> 2 | RESET : H, serial default                                                                         |          | 0.3     | 5    | μΑ    |

| Consumption current 3A             | ICC3A             | When STBY mode is released, RT external resistance value is 27kΩ                                  |          | 1.9     | 3    | mA    |

| Consumption current 3B             | ICC3B             | When STBY mode is released, RT external resistance value is $160 k\Omega$                         |          | 1       | 2    | mA    |

| LEDSW                              |                   |                                                                                                   |          |         |      |       |

| On resistance 1                    | Ron1              | ROW1 to 7 : IL = 425mA                                                                            |          | 1       | 2    | Ω     |

| On resistance 2                    | Ron2              | LEDO1, LED02 : IL = 20mA                                                                          |          | 2       | 4    | Ω     |

| LED current 1                      | ILED1             | COL1 to COL17 : V <sub>O</sub> = LEDV <sub>DD</sub> -0.5V<br>RT external resistance value : 27kΩ  | 20 22.5  |         | 25   | mA    |

| LED current 2                      | ILED2             | COL1 to COL17 : V <sub>O</sub> = LEDV <sub>DD</sub> -0.5V<br>RT external resistance value : 160kΩ | 2.8      | 3.8     | 4.8  | mA    |

| Leakage current 1                  | IL1               | ROW1 to ROW : V <sub>O</sub> = 5V                                                                 |          |         | 1    | μА    |

| Leakage current 2                  | IL2               | COL1 to COL17 : V <sub>O</sub> = 0V, LEDV <sub>DD</sub> = 5V                                      |          |         | 1    | μА    |

| Leakage current 3                  | IL3               | LEDO1, LED02 : V <sub>O</sub> = 5V                                                                |          |         | 1    | μΑ    |

| osc                                | •                 |                                                                                                   | '        | •       |      |       |

| Oscillator frequency               | F1                | When RT external resistance is 27kΩ, CT external capacitance is 120pF                             | 900 1000 |         | 1100 | kHz   |

| Oscillator frequency               | F1                |                                                                                                   |          | 1100    | kHz  |       |

| RT                                 | <u>.</u>          |                                                                                                   | '        | •       |      |       |

| Maximum. LED drive current setting | LI1               | RT external resistance : 27kΩ LED maximum drive current = 607.5/RT resistance                     | 20       | 22.5    | 25   | mA    |

Continued on next page.

$<sup>^{\</sup>star}$  Same level of voltage LEDV\_CC must be applied to the 4 pins as VLEDV\_DD voltage.

Continued from preceding page.

| Dorometer             | Cumbal             | Conditions                                                         |                      | Ratings |                      | Lloit |  |

|-----------------------|--------------------|--------------------------------------------------------------------|----------------------|---------|----------------------|-------|--|

| Parameter             | Symbol             | Conditions                                                         | min                  | typ     | max                  | Unit  |  |

| Control Circuit Block |                    |                                                                    |                      |         |                      |       |  |

| H level 1             | V <sub>INH</sub> 1 | Input H level, SDA, SCL                                            | V <sub>DD</sub> ×0.8 |         |                      | V     |  |

| L level 1             | V <sub>INL</sub> 1 | Input L level, SDA, SCL                                            | 0                    |         | V <sub>DD</sub> ×0.2 | V     |  |

| H level 2             | V <sub>INH</sub> 2 | Input H level, RESET, SCTL                                         | 1.5                  |         |                      | V     |  |

| L level 2             | V <sub>INL</sub> 2 | Input L level, RESET, SCTL                                         | 0                    |         | 0.3                  | V     |  |

| H input current 3     | I <sub>HIN</sub> 3 | Inflow-outflow current, when VBAT voltage is applied to RESET pin. | -1                   | 0       | 1                    | μА    |  |

| L input current 3     | I <sub>LIN</sub> 3 | Inflow-outflow current, when 0V is applied to RESET pin.           | -1                   | 0       | 1                    | μА    |  |

| H input current 4     | I <sub>HIN</sub> 4 | Inflow-outflow current, when VBAT voltage is applied to SCTL pin.  | 15                   | 47      | 75                   | μΑ    |  |

| L input current 4     | I <sub>LIN</sub> 4 | Inflow-outflow current, when 0V is applied to SCTL pin.            | -1                   | 0       | 1                    | μΑ    |  |

| H output level 1      | VH1                | INTO pin, H level, I <sub>O</sub> = 1mA                            | V <sub>DD</sub> -0.3 |         | $V_{DD}$             | V     |  |

| L output level 1      | VL1                | INTO pin, L level, I <sub>O</sub> = 1mA                            | 0                    |         | 0.3                  | V     |  |

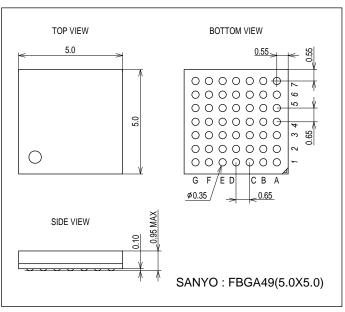

# **Package Dimensions**

unit: mm (typ)

3396

# **Pin Assignment**

Top view

|   | G                  | F     | E                | D                  | С               | В           | Α           |   |

|---|--------------------|-------|------------------|--------------------|-----------------|-------------|-------------|---|

| 1 | NC                 | COL16 | СТ               | SGND               | LEDGND<br>1     | ROW2        | TEST        | 1 |

| 2 | LEDV <sub>DD</sub> | COL17 | sv <sub>CC</sub> | SDA                | ROW1            | ROW3        | RT          | 2 |

| 3 | COL15              | COL14 | COL13            | SCL                | V <sub>DD</sub> | LEDGND<br>2 | ROW4        | 3 |

| 4 | LEDV <sub>DD</sub> | COL12 | COL11            | RESET              | INTO            | ROW5        | LEDGND<br>3 | 4 |

| 5 | COL10              | COL9  | COL4             | COL2               | GPI             | ROW6        | LEDGND<br>4 | 5 |

| 6 | LEDVDD             | COL8  | COL5             | COL3               | LEDO2           | LEDO1       | ROW7        | 6 |

| 7 | NC                 | COL7  | COL6             | LEDV <sub>DD</sub> | COL1            | LEDGND<br>5 | NC          | 7 |

|   | G                  | F     | Е                | D                  | С               | В           | Α           |   |

| Grid | PIN NAME           | Function                                                     | Protection diode<br>vs. LEDV <sub>DD</sub> | Protection diode<br>vs. SV <sub>CC</sub> | Protection diode vs. GND  o o o o o o o o o o o o o o o o o o |

|------|--------------------|--------------------------------------------------------------|--------------------------------------------|------------------------------------------|---------------------------------------------------------------|

| A1   | TEST               | TEST input pin                                               | · · · · · · · · · · · · · · · · · · ·      | 0                                        |                                                               |

| A2   | RT                 | Standard current setting resistance connection pin           |                                            |                                          |                                                               |

| A3   | ROW4               | ROW SW4                                                      | 0                                          |                                          |                                                               |

| A4   | LEDGND3            | ROW SW GND                                                   |                                            |                                          |                                                               |

| A5   | LEDGND4            | ROW SW GND                                                   |                                            |                                          |                                                               |

| A6   | ROW7               | ROW SW7                                                      | 0                                          |                                          | 0                                                             |

| A7   | NC                 | No connection                                                | _                                          |                                          |                                                               |

| B1   | ROW2               | ROW SW2                                                      | 0                                          |                                          | 0                                                             |

| B2   | ROW3               | ROW SW3                                                      | 0                                          |                                          |                                                               |

| B3   | LEDGND2            | ROW SW GND                                                   |                                            |                                          |                                                               |

| B4   | ROW5               | ROW SW5                                                      | 0                                          |                                          | 0                                                             |

| B5   | ROW6               | ROW SW6                                                      | 0                                          |                                          |                                                               |

| B6   | LEDO1              | LED driver 1                                                 | 0                                          |                                          |                                                               |

| B7   | LEDGND5            | LED driver 1  LEDO1,2 exclusive GND                          |                                            |                                          | 0                                                             |

| C1   | LEDGND3            | ROW SW GND                                                   | _                                          | -                                        |                                                               |

| C2   | ROW1               | ROW SW GND                                                   | 0                                          | -                                        |                                                               |

| C3   |                    |                                                              | 0                                          | 0                                        |                                                               |

| C4   | V <sub>DD</sub>    | Serial I/O supply voltage  INT output                        |                                            | 0                                        |                                                               |

|      | INTO               | i                                                            |                                            |                                          |                                                               |

| C5   | GPI                | Receiving melody synchronous signal input pin                |                                            | 0                                        |                                                               |

| C6   | LEDO2              | LED driver 2                                                 |                                            |                                          |                                                               |

| C7   | COL1               | COL SW1                                                      | 0                                          |                                          | 0                                                             |

| D1   | SGND               | Analog logic GND                                             |                                            |                                          |                                                               |

| D2   | SDA                | Serial data signal input                                     |                                            |                                          |                                                               |

| D3   | SCL                | Serial clock signal input                                    |                                            |                                          |                                                               |

| D4   | RESET              | Reset pin                                                    |                                            | 0                                        |                                                               |

| D5   | COL2               | COL SW2                                                      | 0                                          |                                          |                                                               |

| D6   | COL3               | COL SW3                                                      | 0                                          |                                          | 0                                                             |

| D7   | LEDV <sub>DD</sub> | Dot matrix LED drive voltage impression pin                  |                                            |                                          |                                                               |

| E1   | CT                 | Setting of frequency of transmitter capacitor connection pin |                                            |                                          | 0                                                             |

| E2   | sv <sub>cc</sub>   | Analog logic supply voltage                                  |                                            |                                          |                                                               |

| E3   | COL13              | COL SW13                                                     | 0                                          |                                          |                                                               |

| E4   | COL11              | COL SW11                                                     | 0                                          |                                          |                                                               |

| E5   | COL4               | COL SW4                                                      | 0                                          |                                          | 0                                                             |

| E6   | COL5               | COL SW5                                                      | 0                                          |                                          | 0                                                             |

| E7   | COL6               | COL SW6                                                      | 0                                          |                                          |                                                               |

| F1   | COL16              | COL SW16                                                     | 0                                          |                                          | 0                                                             |

| F2   | COL17              | COL SW17                                                     | 0                                          |                                          | 0                                                             |

| F3   | COL14              | COL SW14                                                     | 0                                          |                                          | 0                                                             |

| F4   | COL12              | COL SW12                                                     | 0                                          |                                          | 0                                                             |

| F5   | COL9               | COL SW9                                                      | 0                                          |                                          | 0                                                             |

| F6   | COL8               | COL SW8                                                      | 0                                          |                                          | 0                                                             |

| F7   | COL7               | COL SW7                                                      | 0                                          |                                          | 0                                                             |

| G1   | NC                 | No connection                                                |                                            |                                          |                                                               |

| G2   | LEDV <sub>DD</sub> | Dot matrix LED drive voltage impression pin                  |                                            |                                          |                                                               |

| G3   | COL15              | COL SW15                                                     | 0                                          |                                          | 0                                                             |

| G4   | LEDV <sub>DD</sub> | Dot matrix LED drive voltage impression pin                  |                                            |                                          |                                                               |

| G5   | COL10              | COL SW10                                                     | 0                                          |                                          | 0                                                             |

| G6   | LEDVDD             | Dot matrix LED drive voltage impression pin                  |                                            |                                          |                                                               |

| G7   | NC                 | No connection                                                |                                            |                                          |                                                               |

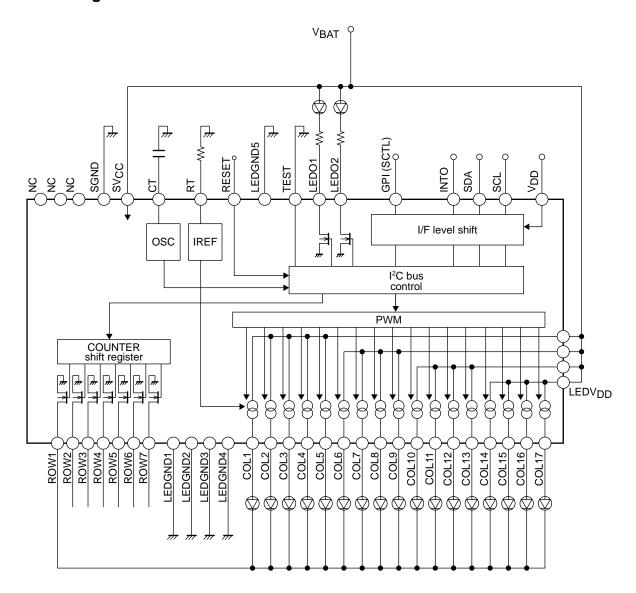

### **Block Diagram**

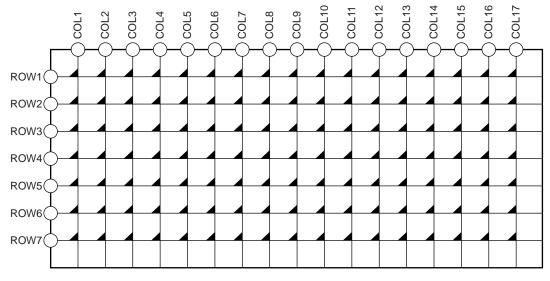

Dynamic Display

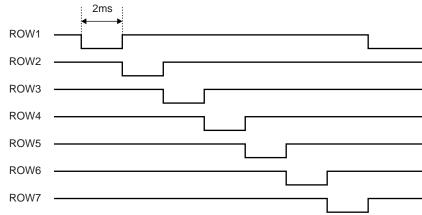

#### Dot Matrix LED $5 \times 15$

Dynamic Display

### **Pin Functions**

| Pin No.  | Pin name       | Pin Description                                                                                                                                                                                                                                                                                                   | Equivalent Circuit                    |

|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| A1       | TEST           | Test signal input pin.  Be sure to connect the pin to GND.                                                                                                                                                                                                                                                        | A1 pin                                |

| A2       | RT             | Reference current setting resistor connection pin.  By connecting the external resistor between this pin and GND, the reference current is generated. The pin voltage is about 0.61V. Change of this current value enables change of the oscillation frequency and LED driver current value (COL1 to COL17 only). | SV <sub>CC</sub> A2 pin               |

| A3       | ROW4           | N-channel driver output pins 1 to 7 for row (cathode) drive.                                                                                                                                                                                                                                                      | 40 40 84 80                           |

| A6       | ROW7           | Must be connected to GND when not to be used.                                                                                                                                                                                                                                                                     | A3, A6, B1, B2,<br>B4, B5, C2 pin     |

| B1       | ROW2           |                                                                                                                                                                                                                                                                                                                   | Β4, B3, G2 piii                       |

| B2       | ROW3           |                                                                                                                                                                                                                                                                                                                   |                                       |

| B4       | ROW5           |                                                                                                                                                                                                                                                                                                                   |                                       |

| B5       | ROW6           |                                                                                                                                                                                                                                                                                                                   |                                       |

| C2       | ROW1           |                                                                                                                                                                                                                                                                                                                   | , , , , , , , , , , , , , , , , , , , |

| A4       | LEDGND3        | ROW SW GND.                                                                                                                                                                                                                                                                                                       |                                       |

| A5       | LEDGND4        | ROW SW GND.                                                                                                                                                                                                                                                                                                       |                                       |

| A7       | NC             | No connection.                                                                                                                                                                                                                                                                                                    |                                       |

| G1       |                |                                                                                                                                                                                                                                                                                                                   |                                       |

| G7       |                |                                                                                                                                                                                                                                                                                                                   |                                       |

| B3       | LEDGND2        | ROW SW GND.                                                                                                                                                                                                                                                                                                       |                                       |

| B6<br>C6 | LEDO1<br>LEDO2 | Open drain output pins for LED drive.  Must be connected to GND when not to be used.                                                                                                                                                                                                                              | B6, C6 pin                            |

|          |                |                                                                                                                                                                                                                                                                                                                   | <b>1</b> € <b>1</b>                   |

| B7       | LEDGND5        | GND pin dedicated for LEDO1 and LEDO2.                                                                                                                                                                                                                                                                            |                                       |

| C1       | LEDGND1        | ROW SW GND.                                                                                                                                                                                                                                                                                                       |                                       |

| C3       | $V_{DD}$       | Power supply for serial I/F.                                                                                                                                                                                                                                                                                      |                                       |

| C4       | INTO           | Interrupt signal output pin.                                                                                                                                                                                                                                                                                      | V <sub>DD</sub> SV <sub>CC</sub>      |

|          |                |                                                                                                                                                                                                                                                                                                                   |                                       |

Continued on next page.

| Pin No.  | n preceding page. Pin name | Pin Description                                                                                               | Equivalent Circuit                             |

|----------|----------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| C5       | GPI                        |                                                                                                               | Equivalent Offcult                             |

| C5       | GPI                        | Ringing tone synchronization signal input pin.  Must be connected to GND when not to be used.                 | SVBAT                                          |

|          |                            |                                                                                                               | C5 pin                                         |

|          |                            |                                                                                                               |                                                |

| C7<br>D5 | COL1<br>COL2               | P-channel driver output pins 1 to 17 for column (anode) drive.  Must be connected to GND when not to be used. |                                                |

| D6       | COL3                       |                                                                                                               |                                                |

| E3       | COL13                      |                                                                                                               | LEDV <sub>DD</sub>                             |

| E4       | COL11                      |                                                                                                               |                                                |

| E5       | COL4                       |                                                                                                               | C7 D5 D6                                       |

| E6       | COL5                       |                                                                                                               | C7, D5, D6,<br>E3, E4, E5,                     |

| E7       | COL6                       |                                                                                                               | E3, E4, E3, E6, E7, F1,                        |

| F1       | COL16                      |                                                                                                               | F2, F3, F4,                                    |

| F2       | COL17                      |                                                                                                               | F5, F6, F7,                                    |

| F3       | COL14                      |                                                                                                               | G3, G5 pin                                     |

| F4       | COL12                      |                                                                                                               | <b>↑</b>                                       |

| F5       | COL9                       |                                                                                                               |                                                |

| F6       | COL8                       |                                                                                                               | <i>m</i>                                       |

| F7       | COL7<br>COL15              |                                                                                                               |                                                |

| G3<br>G5 | COL15                      |                                                                                                               |                                                |

| D7       | LEDV <sub>DD</sub>         | Dot matrix LED drive voltage supply pins.                                                                     |                                                |

| G2       | 222400                     | Bot many ELB anto totago cappi, pino.                                                                         |                                                |

| G4       |                            |                                                                                                               |                                                |

| G6       |                            |                                                                                                               |                                                |

| D1       | SGND                       | Analog circuit GND pin.                                                                                       |                                                |

| D2       | SDA                        | Serial data signal input pin.                                                                                 | V <sub>DD</sub> 🔾                              |

|          |                            |                                                                                                               | <b>→</b>                                       |

|          |                            |                                                                                                               | D2 pin                                         |

|          |                            |                                                                                                               |                                                |

|          |                            |                                                                                                               | <del>  • • • • • • • • • • • • • • • • •</del> |

|          |                            |                                                                                                               |                                                |

|          |                            |                                                                                                               |                                                |

|          |                            |                                                                                                               |                                                |

|          |                            |                                                                                                               |                                                |

| D3       | SCL                        | Serial clock signal input pin.                                                                                |                                                |

| DЗ       | SUL                        | Serial Glock Signal Iliput pili.                                                                              | V <sub>DD</sub>                                |

|          |                            |                                                                                                               |                                                |

|          |                            |                                                                                                               | D3 pin                                         |

|          |                            |                                                                                                               |                                                |

|          |                            |                                                                                                               |                                                |

|          |                            |                                                                                                               |                                                |

|          |                            |                                                                                                               |                                                |

|          |                            |                                                                                                               |                                                |

|          |                            |                                                                                                               | m m                                            |

|          |                            |                                                                                                               |                                                |

Continued on next page.

| Continued from | preceding page.  |                                                                                                                                                |                         |

|----------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Pin No.        | Pin name         | Pin Description                                                                                                                                | Equivalent Circuit      |

| D4             | RESET            | Reset signal input pin. Reset state when low.                                                                                                  | SV <sub>CC</sub> D4 pin |

| E1             | СТ               | Oscillator frequency setting capacitor connection pin. The oscillation frequency can be adjusted by changing the value of capacitor at CT pin. | SV <sub>CC</sub> E1 pin |

| E2             | sv <sub>CC</sub> | Analog circuit power supply.                                                                                                                   |                         |

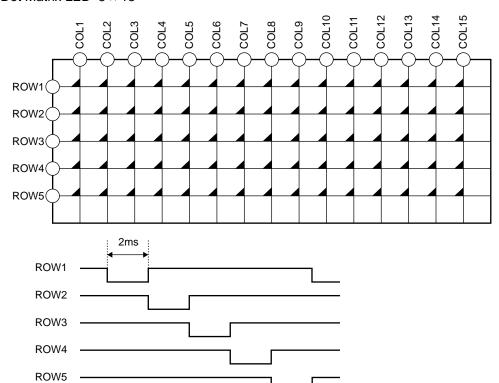

### **Serial Bus Communication Specifications**

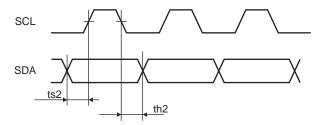

I<sup>2</sup>C serial transfer timing conditions

### Standard mode

| Parameter                 | symbol | Conditions                                     | min | typ | max  | unit |

|---------------------------|--------|------------------------------------------------|-----|-----|------|------|

| SCL clock frequency       | fscl   | SCL clock frequency                            | 0   |     | 100  | kHz  |

| Data set up time          | ts1    | SCL setup time relative to the fall of SDA     | 4.7 |     |      | μS   |

|                           | ts2    | SDA setup time relative to the rise of SCL     | 250 |     |      | ns   |

|                           | ts3    | SCL setup time relative to the rise of SDA     | 4.0 |     |      | μS   |

| Data hold time            | th1    | SCL data hold time relative to the fall of SDA | 4.0 |     |      | μS   |

|                           | th2    | SDA hold time relative to the fall of SCL      | 0   |     |      | μS   |

| Pulse width               | twL    | SCL pulse width for the L period               | 4.7 |     |      | μS   |

|                           | twH    | SCL pulse width for the H period               | 4.0 |     |      | μS   |

| Input waveform conditions | ton    | SCL and SDA (input) rise time                  |     |     | 1000 | ns   |

|                           | tof    | SCL and SDA (input) fall time                  |     |     | 300  | ns   |

| Bus free time             | tbuf   | Time between STOP and START conditions         | 4.7 |     |      | μS   |

# High-speed mode

| Parameter                 | Symbol | Conditions                                     | min | typ | max | unit |

|---------------------------|--------|------------------------------------------------|-----|-----|-----|------|

| SCL clock frequency       | fscl   | SCL clock frequency                            | 0   |     | 400 | kHz  |

| Data setup time           | ts1    | SCL setup time relative to the fall of SDA     | 0.6 |     |     | μS   |

|                           | ts2    | SDA setup time relative to the rise of SCL     | 100 |     |     | ns   |

|                           | ts3    | SCL setup time relative to the rise of SDA     | 0.6 |     |     | μS   |

| Data hold time            | th1    | SCL data hold time relative to the fall of SDA | 0.6 |     |     | μS   |

|                           | th2    | SDA hold time relative to the fall of SCL      | 0   |     |     | μS   |

| Pulse width               | twL    | SCL pulse width for the L period               | 1.3 |     |     | μS   |

|                           | twH    | SCL pulse width for the H period               | 0.6 |     |     | μS   |

| Input waveform conditions | ton    | SCL and SDA (input) rise time                  |     |     | 300 | ns   |

|                           | tof    | SCL and SDA (input) fall time                  |     |     | 300 | ns   |

| Bus free time             | tbuf   | Time between STOP and START conditions         | 1.3 |     |     | μS   |

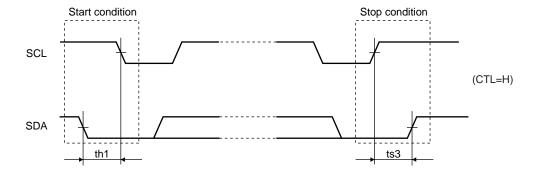

#### I<sup>2</sup>C bus transmission method

Start and stop conditions

In the I<sup>2</sup>C bus, SDA must basically be kept in the constant state while SCL is "H" as shown below during data transfer.

When data transfer is not made, both SCL and SDA are in the "H" state.

When SCL = SDA = "H", change of SDA from "H" to "L" enables the start conditions to start access.

When SCL is "H", change of SDA from "L" to "H" enables the stop conditions to stop access.

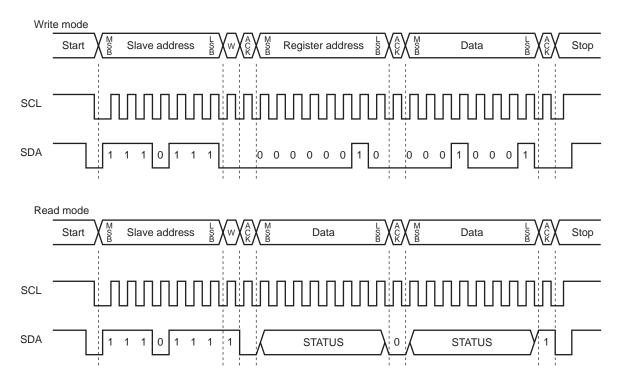

#### Data transfer and acknowledgement response

After establishment of start conditions, data transfer is made by one byte (8 bits).

Data transfer enables continuous transfer of any number of bytes.

Each time the 8-bit data is transferred, the ACK signal is sent from the receive side to the send side.

The ACK signal is issued when SDA on the send side is released and SDA on the receive side is set "L" immediately after fall of the clock pulse at the SCL eighth bit of data transfer to "L".

When the next 1-byte transfer is left in the receive state after transmission of the ACK signal from the receive side, the receive side releases SDA at fall of the SCL ninth clock.

In the I<sup>2</sup>C bus, there is no CE signal. Instead, 7-bit slave address is assigned to each device and the first byte of transfer is assigned to the command (R/W) representing the 7-bit slave address and subsequent transfer direction. The 7-bit address is transferred sequentially from MSB and if the eighth bit is "L", the second byte is WRITE mode and if "H", the second byte is READ mode.

In the READ mode, the ACK signal issued immediately before sending the stop condition must be 1. In LV5230, the slave address is specified as (1110111).

#### Serial modes setting

address: 00h CTRL1

| 00h CTRL1     | D7   | D6 | D5     | D4    | D3 | D2    | D1      | D0      |

|---------------|------|----|--------|-------|----|-------|---------|---------|

| Register name | STBY | -  | MXMODE | MSWEN | -  | DFCLR | FADECLR | SCRLCLR |

| R/W           | W    |    | W      | W     |    | W     | W       | W       |

| Default       | 0    |    | 0      | 0     |    | 0     | 0       | 0       |

D0: SCRLCLR Scroll interrupt signal clear

0 : Scroll interrupt signal stays active.

1 : Scroll interrupt signal cleared. \* Automatically updated to 0 after being set to 1.

D1: FADECLR Fade interrupt signal clear

0 : Fade interrupt signal stays active.

1 : Fade interrupt signal cleared. \* Automatically updated to 0 after being set to 1.

D2: DFCLR Pallete fade interrupt signal clear

0 : Pallete fade interrupt signal stays active.

1 : Pallete fade interrupt signal cleared. \* Automatically updated to 0 after being set to 1.

D4: MSWEN Ringing tone synchronization enable

0 : Ringing tone synchronization enabled. \* GPI = L : All LEDs turned off, GPI = H : Normal operation

1 : Ringing tone synchronization disabled.

D5: MXMODE LED matrix mode switchingr

0:7 × 17 LED matrix 1:5 × 15 LED matrix

D7: STBY Standby mode

0 : Standby 1 : Operation

address: 01h CTRL2

| 01h CTRL2     | D7     | D6 | D5   | D4   | D3 | D2     | D1     | D0   |

|---------------|--------|----|------|------|----|--------|--------|------|

| Register name | LEDOFF | =  | LED2 | LED1 | -  | ROTHEN | ROTVEN | PAGE |

| R/W           | W      |    | W    | W    |    | W      | W      | W    |

| Default       | 0      |    | 0    | 0    |    | 0      | 0      | 0    |

D0: PAGE Display page

0 : Frame 1 displayed 1 : Frame 2 displayed

D1: ROTVEN Vertical rotation

0 : Normal display

1 : Vertically rotated display

D2: ROTHEN Horizontal rotation

0 : Normal display

1 : Horizontally rotated display

D4: LED1 LED1 enable

0 : LED1 turned off 1 : LED1 turned on

D5: LED2 LED2 enable

0 : LED2 turned off 1 : LED2 turned on

D7: LEDOFF Screen display ON/OFF

0: Normal operation

1 : All matrix LEDs turned off

address: 02h DOTMODE

| 02h DOTMODE   | D7    | D6      | D5 | D4 | D3        | D2        | D1        | D0        |

|---------------|-------|---------|----|----|-----------|-----------|-----------|-----------|

| Register name | DOTEN | DOTMODE | =  | =  | DOTSP [3] | DOTSP [2] | DOTSP [1] | DOTSP [0] |

| R/W           | W     | W       |    |    | W         | W         | W         | W         |

| Default       | 0     | 0       |    |    | 0         | 0         | 0         | 0         |

D3-D0 : DOTSP Flashing/brightness inversion speed

| D3 | D2 | D1 | D0 |           |            |

|----|----|----|----|-----------|------------|

| 0  | 0  | 0  | 0  | ON: 0.05s | OFF: 0.05s |

| 0  | 0  | 0  | 1  | ON: 0.10s | OFF: 0.10s |

| 0  | 0  | 1  | 0  | ON: 0.15s | OFF: 0.15s |

| 0  | 0  | 1  | 1  | ON: 0.20s | OFF: 0.20s |

| 0  | 1  | 0  | 0  | ON: 0.25s | OFF: 0.25s |

| 0  | 1  | 0  | 1  | ON: 0.30s | OFF: 0.30s |

| 0  | 1  | 1  | 0  | ON: 0.35s | OFF: 0.35s |

| 0  | 1  | 1  | 1  | ON: 0.40s | OFF: 0.40s |

| 1  | 0  | 0  | 0  | ON: 0.45s | OFF: 0.45s |

| 1  | 0  | 0  | 1  | ON: 0.50s | OFF: 0.50s |

| 1  | 0  | 1  | 0  | ON: 0.55s | OFF: 0.55s |

| 1  | 0  | 1  | 1  | ON: 0.60s | OFF: 0.60s |

| 1  | 1  | 0  | 0  | ON: 0.65s | OFF: 0.65s |

| 1  | 1  | 0  | 1  | ON: 0.70s | OFF: 0.70s |

| 1  | 1  | 1  | 0  | ON: 0.75s | OFF: 0.75s |

| 1  | 1  | 1  | 1  | ON: 0.80s | OFF: 0.80s |

D6: DOTMODE Flashing/brightness inversion display switching

0 : Flashing

1 : Brightness inversion

D7: DOTEN Flashing/brightness inversion display enable

### $address: 03h\ AUTOPAGE$

| 03h AUTOPAGE  | D7   | D6 | D5 | D4 | D3       | D2       | D1       | D0       |

|---------------|------|----|----|----|----------|----------|----------|----------|

| Register name | PGEN | -  | -  | -  | PGSP [3] | PGSP [2] | PGSP [1] | PGSP [0] |

| R/W           | W    |    |    |    | W        | W        | W        | W        |

| Default       | 0    |    |    |    | 0        | 0        | 0        | 0        |

# D3 top D0: PGSP Page switching speed

| D3 | D2 | D1 | D0 |               |               |

|----|----|----|----|---------------|---------------|

| 0  | 0  | 0  | 0  | Page1 : 0.05s | Page2 : 0.05s |

| 0  | 0  | 0  | 1  | Page1 : 0.10s | Page2 : 0.10s |

| 0  | 0  | 1  | 0  | Page1 : 0.15s | Page2 : 0.15s |

| 0  | 0  | 1  | 1  | Page1 : 0.20s | Page2 : 0.20s |

| 0  | 1  | 0  | 0  | Page1 : 0.25s | Page2 : 0.25s |

| 0  | 1  | 0  | 1  | Page1 : 0.30s | Page2 : 0.30s |

| 0  | 1  | 1  | 0  | Page1 : 0.35s | Page2 : 0.35s |

| 0  | 1  | 1  | 1  | Page1 : 0.40s | Page2 : 0.40s |

| 1  | 0  | 0  | 0  | Page1 : 0.45s | Page2 : 0.45s |

| 1  | 0  | 0  | 1  | Page1 : 0.50s | Page2 : 0.50s |

| 1  | 0  | 1  | 0  | Page1 : 0.55s | Page2 : 0.55s |

| 1  | 0  | 1  | 1  | Page1 : 0.60s | Page2 : 0.60s |

| 1  | 1  | 0  | 0  | Page1 : 0.65s | Page2 : 0.65s |

| 1  | 1  | 0  | 1  | Page1 : 0.70s | Page2 : 0.70s |

| 1  | 1  | 1  | 0  | Page1 : 0.75s | Page2 : 0.75s |

| 1  | 1  | 1  | 1  | Page1 : 0.80s | Page2 : 0.80s |

D7: PGEN Automatic page switching enable

address: 04h SCCON1

| 04h SCCON1    | D7   | D6        | D5        | D4     | D3       | D2       | D1       | D0       |

|---------------|------|-----------|-----------|--------|----------|----------|----------|----------|

| Register name | SCEN | SCDIR [1] | SCDIR [0] | SCMODE | SCSP [3] | SCSP [2] | SCSP [1] | SCSP [0] |

| R/W           | W    | W         | W         | W      | W        | W        | W        | W        |

| Default       | 0    | 0         | 0         | 0      | 0        | 0        | 0        | 0        |

D3 to D0 : SCSP Scroll speed per dot

| D3 | D2 | D1 | D0 |       |

|----|----|----|----|-------|

| 0  | 0  | 0  | 0  | 50ms  |

| 0  | 0  | 0  | 1  | 100ms |

| 0  | 0  | 1  | 0  | 150ms |

| 0  | 0  | 1  | 1  | 200ms |

| 0  | 1  | 0  | 0  | 250ms |

| 0  | 1  | 0  | 1  | 300ms |

| 0  | 1  | 1  | 0  | 350ms |

| 0  | 1  | 1  | 1  | 400ms |

| 1  | 0  | 0  | 0  | 450ms |

| 1  | 0  | 0  | 1  | 500ms |

| 1  | 0  | 1  | 0  | 550ms |

| 1  | 0  | 1  | 1  | 600ms |

| 1  | 1  | 0  | 0  | 650ms |

| 1  | 1  | 0  | 1  | 700ms |

| 1  | 1  | 1  | 0  | 750ms |

| 1  | 1  | 1  | 1  | 800ms |

D4: SCMODE Page mode when scrolling

0 : Scrolls and displays the current page repeatedly.

1 : Scrolls and displays the current and other pages alternately.

D6 to D5 : SCDIR Scroll direction

| D6 | D5 |       |

|----|----|-------|

| 0  | 0  | Right |

| 0  | 1  | Left  |

| 1  | 0  | Up    |

| 1  | 1  | Down  |

D7: SCEN Scroll enable

address: 05h SCCON2

| 05h SCCON2    | D7   | D6 | D5        | D4        | D3        | D2        | D1        | D0        |

|---------------|------|----|-----------|-----------|-----------|-----------|-----------|-----------|

| Register name | SCGO | -  | SCCNT [5] | SCCNT [4] | SCCNT [3] | SCCNT [2] | SCCNT [1] | SCCNT [0] |

| R/W           | W    |    | W         | W         | W         | W         | W         | W         |

| Default       | 0    |    | 0         | 0         | 0         | 0         | 0         | 0         |

D0 to D5: SCCNT Scroll increment

$17 \times 7 \text{ mode}$

When SCCON1.SCDIR = 0 or 1 : 1 to 34 When SCCON1.SCDIR = 2 or 3 : 1 to 14

$15 \times 5$  mode

When SCCON1.SCDIR = 0 or 1 : 1 to 30 When SCCON1.SCDIR = 2 or 3 : 1 to 10

\* Scrolls one page when SCCNT = 0.

D7: SCGO Scroll start

0 : Standby

1 : Scroll start

<sup>\*</sup> The scrolled state is maintained until SCCON1 and SCEN are set low.

address: 06h FADECON

| 06h FADECON   | D7     | D6     | D5     | D4      | D3       | D2       | D1       | D0       |

|---------------|--------|--------|--------|---------|----------|----------|----------|----------|

| Register name | FADEEN | FADEGO | FADEIO | FADEMOD | FDSP [3] | FDSP [2] | FDSP [1] | FDSP [0] |

| R/W           | W      | W      | W      | W       | W        | W        | W        | W        |

| Default       | 0      | 0      | 0      | 0       | 0        | 0        | 0        | 0        |

D3 to D0 : FDSP Fade speed per 1 grayscale level (It takes (following set value × 64) seconds to complete fading)

| D3 | D2 | D1 | D0 |      |

|----|----|----|----|------|

| 0  | 0  | 0  | 0  | 2ms  |

| 0  | 0  | 0  | 1  | 4ms  |

| 0  | 0  | 1  | 0  | 6ms  |

| 0  | 0  | 1  | 1  | 8ms  |

| 0  | 1  | 0  | 0  | 10ms |

| 0  | 1  | 0  | 1  | 12ms |

| 0  | 1  | 1  | 0  | 14ms |

| 0  | 1  | 1  | 1  | 16ms |

| 1  | 0  | 0  | 0  | 18ms |

| 1  | 0  | 0  | 1  | 20ms |

| 1  | 0  | 1  | 0  | 22ms |

| 1  | 0  | 1  | 1  | 24ms |

| 1  | 1  | 0  | 0  | 26ms |

| 1  | 1  | 0  | 1  | 28ms |

| 1  | 1  | 1  | 0  | 30ms |

| 1  | 1  | 1  | 1  | 32ms |

D4: FADEMOD Single/continuous switching

0 : Single fade-in/fade-out operation

1 : Fade-in/fade-out operation repeated

D5: FADEIO Fade-in/fade-out switching

0 : Fade in 1 : Fade out

D6: FADEGO Fade-in/fade-out start

0: Standby

1 : Fade-in/fade-out operation start

D7: FADEEN Fade-in/fade-out enable

0 : Disable 1 : Enable

\* The interrupt flag is set high after a fade operation has completed. Manual clearing is required.

\* All LEDs are turned off if FADEEN is set to 1 when FADEO is set to 0. If GO is set to 1 in that state, fade-in operation starts and LEDs are turned on.

address: 07h ROWSW

| 07h ROWSW     | D7      | D6     | D5     | D4     | D3     | D2     | D1     | D0     |

|---------------|---------|--------|--------|--------|--------|--------|--------|--------|

| Register name | ROWSWEN | ROWSW7 | ROWSW6 | ROWSW5 | ROWSW4 | ROWSW3 | ROWSW2 | ROWSW1 |

| R/W           | W       | W      | W      | W      | W      | W      | W      | W      |

| Default       | 0       | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

D0: ROWSW1 Row 1 display ON/OFF

0 : ON 1 : OFF

D1: ROWSW2 Row 2 display ON/OFF

0 : ON 1 : OFF

D2: ROWSW3 Row 3 display ON/OFF

0 : ON 1 : OFF

D3: ROWSW4 Row 4 display ON/OFF

0 : ON 1 : OFF

D4: ROWSW5 Row 5 display ON/OFF

0 : ON 1 : OFF

D5: ROWSW6 Row 6 display ON/OFF

0 : ON 1 : OFF

D6: ROWSW7 Row 7 display ON/OFF

0 : ON 1 : OFF

D7: ROWSWEN Each row ON/OFF enable

address: 08h COLSW1

| 08h COLSW1    | D7      | D6 | D5 | D4 | D3 | D2 | D1 | D0      |

|---------------|---------|----|----|----|----|----|----|---------|

| Register name | COLSWEN | =  | -  | -  | -  | -  | -  | COLSW17 |

| R/W           | W       |    |    |    |    |    |    | W       |

| Default       | 0       |    |    |    |    |    |    | 0       |

D0: COLSW17 Row 17 display ON/OFF

0 : ON 1 : OFF

D7: COLSWEN Column ON/OFF enable

0 : Disable 1 : Enable

address: 09h COLSW2

| 09h COLSW2    | D7      | D6      | D5      | D4      | D3      | D2      | D1      | D0     |

|---------------|---------|---------|---------|---------|---------|---------|---------|--------|

| Register name | COLSW16 | COLSW15 | COLSW14 | COLSW13 | COLSW12 | COLSW11 | COLSW10 | COLSW9 |

| R/W           | W       | W       | W       | W       | W       | W       | W       | W      |

| Default       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0      |

D0: COLSW9 Column 9 display ON/OFF

0 : ON 1 : OFF

D1: COLSW10 Column 10 display ON/OFF

0 : ON 1 : OFF

D2: COLSW11 Column 11 display ON/OFF

0 : ON 1 : OFF

D3: COLSW12 Column 12 display ON/OFF

0 : ON 1 : OFF

D4: COLSW13 Column 13 display ON/OFF

0 : ON 1 : OFF

D5: COLSW14 Column 14 display ON/OFF

0 : ON 1 : OFF

D6: COLSW15 Column 15 display ON/OFF

0 : ON 1 : OFF

D7: COLSW16 Column 16 display ON/OFF

0 : ON 1 : OFF

address: 0Ah COLSW3

| 0Ah COLSW3    | D7     | D6     | D5     | D4     | D3     | D2     | D1     | D0     |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

| Register name | COLSW8 | COLSW7 | COLSW6 | COLSW5 | COLSW4 | COLSW3 | COLSW2 | COLSW1 |

| R/W           | W      | W      | W      | W      | W      | W      | W      | W      |

| Default       | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

D0: COLSW1 Column 1 display ON/OFF

0 : ON 1 : OFF

D1: COLSW2 Column 2 display ON/OFF

0 : ON 1 : OFF

D2: COLSW3 Column 3 display ON/OFF

0 : ON 1 : OFF

D3: COLSW4 Column 4 display ON/OFF

0 : ON 1 : OFF

D4: COLSW5 Column 5 display ON/OFF

0 : ON 1 : OFF

D5: COLSW6 Column 6 display ON/OFF

0 : ON 1 : OFF

D6: COLSW7 Column 7 display ON/OFF

0 : ON 1 : OFF

D7: COLSW8 Column 8 display ON/OFF

0 : ON 1 : OFF

address: 0Bh DFCON1

| 0Bh DFCON1    | D7   | D6   | D5 | D4 | D3    | D2        | D1        | D0        |

|---------------|------|------|----|----|-------|-----------|-----------|-----------|

| Register name | DFEN | DFGO | -  | -  | DFDIR | DFNUM [2] | DFNUM [1] | DFNUM [0] |

| R/W           | W    | W    |    |    | W     | W         | W         | W         |

| Default       | 0    | 0    |    |    | 0     | 0         | 0         | 0         |

D2 to D0: DFNUM Number of palette to be faded to

0 : Invalid

1 to 7 : Correspond to PWMDUTY1 to PWMDUTY7.

D3: DFDIR Fading direction

0 : Fade in 1 : Fade out

D6: DFGO Fade start

0 : Standby 1 : Start

D7: DFEN Fade enable

0 : Disable 1 : Enable

address: 0Ch DFCON2

| 0Ch DFCON2    | D7 | D6 | D5 | D4 | D3       | D2       | D1       | D0       |

|---------------|----|----|----|----|----------|----------|----------|----------|

| Register name | -  | -  | -  | -  | DFSP [3] | DFSP [2] | DFSP [1] | DFSP [0] |

| R/W           |    |    |    |    | W        | W        | W        | W        |

| Default       |    |    |    |    | 0        | 0        | 0        | 0        |

### D3 to D0: DFSP Fading speed per grayscale

| D3 | D2 | D1 | D0 |      |

|----|----|----|----|------|

| 0  | 0  | 0  | 0  | 2ms  |

| 0  | 0  | 0  | 1  | 4ms  |

| 0  | 0  | 1  | 0  | 6ms  |

| 0  | 0  | 1  | 1  | 8ms  |

| 0  | 1  | 0  | 0  | 10ms |

| 0  | 1  | 0  | 1  | 12ms |

| 0  | 1  | 1  | 0  | 14ms |

| 0  | 1  | 1  | 1  | 16ms |

| 1  | 0  | 0  | 0  | 18ms |

| 1  | 0  | 0  | 1  | 20ms |

| 1  | 0  | 1  | 0  | 22ms |

| 1  | 0  | 1  | 1  | 24ms |

| 1  | 1  | 0  | 0  | 26ms |

| 1  | 1  | 0  | 1  | 28ms |

| 1  | 1  | 1  | 0  | 30ms |

| 1  | 1  | 1  | 1  | 32ms |

<sup>\*</sup> The interrupt flag is set high after a fade operation has completed. Manual clearing is required.

address: 0Dh MAXDUTY

| 0Dh MAXDUTY   | D7 | D6 | D5        | D4        | D3        | D2        | D1        | D0        |

|---------------|----|----|-----------|-----------|-----------|-----------|-----------|-----------|

| Register name | -  | -  | MXDTY [5] | MXDTY [4] | MXDTY [3] | MXDTY [2] | MXDTY [1] | MXDTY [0] |

| R/W           |    |    | W         | W         | W         | W         | W         | W         |

| Default       |    |    | 0         | 0         | 0         | 0         | 0         | 0         |

D5 to D0: MXDTY Maximum DUTY value

n:0 to 63 Maximum DUTY value  $(n/64) \times 100[\%]$

\* 100[%] when n = 63.

address: 10h PWMDUTY1

| 10h PWMDUTY1  | D7 | D6 | D5        | D4        | D3        | D2        | D1        | D0        |

|---------------|----|----|-----------|-----------|-----------|-----------|-----------|-----------|

| Register name | =  | -  | DUTY1 [5] | DUTY1 [4] | DUTY1 [3] | DUTY1 [2] | DUTY1 [1] | DUTY1 [0] |

| R/W           |    |    | W         | W         | W         | W         | W         | W         |

| Default       |    |    | 0         | 0         | 0         | 0         | 0         | 0         |

D5 to D0: DUTY1 DUTY value for brightness 1 setting

n: 0 to 63 DUTY value  $((n + 1)/64) \times 100$  [%]

\* 0 [%] when n = 0.

address: 11h PWMDUTY2

| 11h PWMDUTY2  | D7 | D6 | D5        | D4        | D3        | D2        | D1        | D0        |

|---------------|----|----|-----------|-----------|-----------|-----------|-----------|-----------|

| Register name | ı  | -  | DUTY2 [5] | DUTY2 [4] | DUTY2 [3] | DUTY2 [2] | DUTY2 [1] | DUTY2 [0] |

| R/W           |    |    | W         | W         | W         | W         | W         | W         |

| Default       |    |    | 0         | 0         | 0         | 0         | 0         | 0         |

D5 to D0: DUTY2 DUTY value for brightness 2 setting

n: 0 to 63 DUTY value  $((n + 1)/64) \times 100$  [%]

\* 0 [%] when n = 0.

address: 12h PWMDUTY3

| 12h PWMDUTY3  | D7 | D6 | D5        | D4        | D3        | D2        | D1        | D0        |

|---------------|----|----|-----------|-----------|-----------|-----------|-----------|-----------|

| Register name | -  | -  | DUTY3 [5] | DUTY3 [4] | DUTY3 [3] | DUTY3 [2] | DUTY3 [1] | DUTY3 [0] |

| R/W           |    |    | W         | W         | W         | W         | W         | W         |

| Default       |    |    | 0         | 0         | 0         | 0         | 0         | 0         |

D5 to D0: DUTY3 DUTY value for brightness 3 setting

n: 0 to 63 DUTY value  $((n + 1)/64) \times 100$  [%]

\* 0 [%] when n = 0.

address: 13h PWMDUTY4

| 13h PWMDUTY4  | D7 | D6 | D5        | D4        | D3        | D2        | D1        | D0        |

|---------------|----|----|-----------|-----------|-----------|-----------|-----------|-----------|

| Register name | -  | -  | DUTY4 [5] | DUTY4 [4] | DUTY4 [3] | DUTY4 [2] | DUTY4 [1] | DUTY4 [0] |

| R/W           |    |    | W         | W         | W         | W         | W         | W         |

| Default       |    |    | 0         | 0         | 0         | 0         | 0         | 0         |

D5 to D0: DUTY4 DUTY value for brightness 4 setting

n: 0 to 63 DUTY value  $((n + 1)/64) \times 100$  [%]

\* 0 [%] when n = 0.

address: 14h PWMDUTY5

| 14h PWMDUTY5  | D7 | D6 | D5        | D4        | D3        | D2        | D1        | D0        |

|---------------|----|----|-----------|-----------|-----------|-----------|-----------|-----------|

| Register name | -  | -  | DUTY5 [5] | DUTY5 [4] | DUTY5 [3] | DUTY5 [2] | DUTY5 [1] | DUTY5 [0] |

| R/W           |    |    | W         | W         | W         | W         | W         | W         |

| Default       |    |    | 0         | 0         | 0         | 0         | 0         | 0         |

D5 to D0: DUTY5 DUTY factor value for brightness 5 setting

n: 0 to 63 DUTY value  $((n + 1)/64) \times 100$  [%]

\* 0 [%] when n = 0.

address: 15h PWMDUTY6

| 15h PWMDUTY6  | D7 | D6 | D5        | D4        | D3        | D2        | D1        | D0        |

|---------------|----|----|-----------|-----------|-----------|-----------|-----------|-----------|

| Register name | -  | -  | DUTY6 [5] | DUTY6 [4] | DUTY6 [3] | DUTY6 [2] | DUTY6 [1] | DUTY6 [0] |

| R/W           |    |    | W         | W         | W         | W         | W         | W         |

| Default       |    |    | 0         | 0         | 0         | 0         | 0         | 0         |

D5 to D0: DUTY6 DUTY factor value for brightness 6 setting

$n:0 \text{ to } 63 \;\; DUTY \; value \; ((n+1)/64) \times 100 \; [\%]$

\* 0 [%] when n = 0.

address: 16h PWMDUTY7

| 16h PWMDUTY7  | D7 | D6 | D5        | D4        | D3        | D2        | D1        | D0        |

|---------------|----|----|-----------|-----------|-----------|-----------|-----------|-----------|

| Register name | =  | -  | DUTY7 [5] | DUTY7 [4] | DUTY7 [3] | DUTY7 [2] | DUTY7 [1] | DUTY7 [0] |

| R/W           |    |    | W         | W         | W         | W         | W         | W         |

| Default       |    |    | 0         | 0         | 0         | 0         | 0         | 0         |

D5 to D0: DUTY7 DUTY factor value for brightness 7 setting

n: 0 to 63 DUTY value  $((n + 1)/64) \times 100$  [%]

\* 0 [%] when n = 0.

address: 20h to 9Dh FRAMEDATA

| 20h to 9Dh FRAMEDATA | D7  | D6      | D5      | D4      | D3  | D2      | D1      | D0      |

|----------------------|-----|---------|---------|---------|-----|---------|---------|---------|

| Register name        | BRn | LMn [2] | LMn [1] | LMn [0] | BRm | LMm [2] | LMm [1] | LMm [0] |

| R/W                  | W   | W       | W       | W       | W   | W       | W       | W       |

| Default              | 0   | 0       | 0       | 0       | 0   | 0       | 0       | 0       |

D2 to D0: LM11m Frame 1: vertical 1st: horizontal (n + 1) th LED brightness

| D2 | D1 | D0 |                                           |

|----|----|----|-------------------------------------------|

| 0  | 0  | 0  | Off                                       |

| 0  | 0  | 1  | On at brightness set by PWMDUTY1 register |

| 0  | 1  | 0  | On at brightness set by PWMDUTY2 register |

| 0  | 1  | 1  | On at brightness set by PWMDUTY3 register |

| 1  | 0  | 0  | On at brightness set by PWMDUTY4 register |

| 1  | 0  | 1  | On at brightness set by PWMDUTY5 register |

| 1  | 1  | 0  | On at brightness set by PWMDUTY6 register |

| 1  | 1  | 1  | On at brightness set by PWMDUTY7 register |

D3: BR11m Frame 1: vertical 1: horizontal (n + 1) th LED flashing/brightness inversion enable

0 : Flashing/brightness inversion disabled1 : Flashing/brightness inversion enabled

D6 to D4: LM11n Frame 1: vertical 1: horizontal (n) th LED brightness

| D2 | D1 | D0 |                                           |

|----|----|----|-------------------------------------------|

| 0  | 0  | 0  | Off                                       |

| 0  | 0  | 1  | On at brightness set by PWMDUTY1 register |

| 0  | 1  | 0  | On at brightness set by PWMDUTY2 register |

| 0  | 1  | 1  | On at brightness set by PWMDUTY3 register |

| 1  | 0  | 0  | On at brightness set by PWMDUTY4 register |

| 1  | 0  | 1  | On at brightness set by PWMDUTY5 register |

| 1  | 1  | 0  | On at brightness set by PWMDUTY6 register |

| 1  | 1  | 1  | On at brightness set by PWMDUTY7 register |

D7: BR11n Frame 1: vertical 1: horizontal (n) th LED flashing/brightness inversion enable

0 : Flashing/brightness inversion disabled1 : Flashing/brightness inversion enabled

<sup>\*</sup> These are used for each LED data. One register is loaded with two LEDs data. See the table on the following page for the storage address of each dot.

Frame Data Register Tables xxH : higher-order 4 bits of register xx xxL : lower-order 4 bits of register xx

### $17\times7\ mode$

#### Frame 1

|   | -   |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  | 14  | 15  | 16  | 17  |

| 1 | 20H | 20L | 21H | 21L | 22H | 22L | 23H | 23L | 24H | 24L | 25H | 25L | 26H | 26L | 27H | 27L | 28H |

| 2 | 29H | 29L | 2AH | 2AL | 2BH | 2BL | 2CH | 2CL | 2DH | 2DL | 2EH | 2EL | 2FH | 2FL | 30H | 30L | 31H |

| 3 | 32H | 32L | 33H | 33L | 34H | 34L | 35H | 35L | 36H | 36L | 37H | 37L | 38H | 38L | 39H | 39L | ЗАН |

| 4 | 3BH | 3BL | 3CH | 3CL | 3DH | 3DL | 3EH | 3EL | 3FH | 3FL | 40H | 40L | 41H | 41L | 42H | 42L | 43H |

| 5 | 44H | 44L | 45H | 45L | 46H | 46L | 47H | 47L | 48H | 48L | 49H | 49L | 4AH | 4AL | 4BH | 4BL | 4CH |

| 6 | 4DH | 4DL | 4EH | 4EL | 4FH | 4FL | 50H | 50L | 51H | 51L | 52H | 52L | 53H | 53L | 54H | 54L | 55H |

| 7 | 56H | 56L | 57H | 57L | 58H | 58L | 59H | 59L | 5AH | 5AL | 5BH | 5BL | 5CH | 5CL | 5DH | 5DL | 5EH |

### Frame 2

|   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  | 14  | 15  | 16  | 17  |

|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1 | 5FH | 5FL | 60H | 60L | 61H | 61L | 62H | 62L | 63H | 63L | 64H | 64L | 65H | 65L | 66H | 66L | 67H |

| 2 | 68H | 68L | 69H | 69L | 6AH | 6AL | 6BH | 6BL | 6CH | 6CL | 6DH | 6DL | 6EH | 6EL | 6FH | 6FL | 70H |

| 3 | 71H | 71L | 72H | 72L | 73H | 73L | 74H | 74L | 75H | 75L | 76H | 76L | 77H | 77L | 78H | 78L | 79H |

| 4 | 7AH | 7AL | 7BH | 7BL | 7CH | 7CL | 7DH | 7DL | 7EH | 7EL | 7FH | 7FL | 80H | 80L | 81H | 81L | 82H |

| 5 | 83H | 83L | 84H | 84L | 85H | 85L | 86H | 86L | 87H | 87L | 88H | 88L | 89H | 89L | 8AH | 8AL | 8BH |

| 6 | 8CH | 8CL | 8DH | 8DL | 8EH | 8EL | 8FH | 8FL | 90H | 90L | 91H | 91L | 92H | 92L | 93H | 93L | 94H |

| 7 | 95H | 95L | 96H | 96L | 97H | 97L | 98H | 98L | 99H | 99L | 9AH | 9AL | 9BH | 9BL | 9CH | 9CL | 9DH |

### $15 \times 5 \text{ mode}$

### Frame 1

|   | •   |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  | 14  | 15  |

| 1 | 20H | 20L | 21H | 21L | 22H | 22L | 23H | 23L | 24H | 24L | 25H | 25L | 26H | 26L | 27H |

| 2 | 29H | 29L | 2AH | 2AL | 2BH | 2BL | 2CH | 2CL | 2DH | 2DL | 2EH | 2EL | 2FH | 2FL | 30H |

| 3 | 32H | 32L | 33H | 33L | 34H | 34L | 35H | 35L | 36H | 36L | 37H | 37L | 38H | 38L | 39H |

| 4 | 3BH | 3BL | 3CH | 3CL | 3DH | 3DL | 3EH | 3EL | 3FH | 3FL | 40H | 40L | 41H | 41L | 42H |

| 5 | 44H | 44L | 45H | 45L | 46H | 46L | 47H | 47L | 48H | 48L | 49H | 49L | 4AH | 4AL | 4BH |

### Frame 2

|   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  | 14  | 15  |

|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1 | 4DH | 4DL | 4EH | 4EL | 4FH | 4FL | 50H | 50L | 51H | 51L | 52H | 52L | 53H | 53L | 54H |

| 2 | 56H | 56L | 57H | 57L | 58H | 58L | 59H | 59L | 5AH | 5AL | 5BH | 5BL | 5CH | 5CL | 5DH |

| 3 | 5FH | 5FL | 60H | 60L | 61H | 61L | 62H | 62L | 63H | 63L | 64H | 64L | 65H | 65L | 66H |

| 4 | 68H | 68L | 69H | 69L | 6AH | 6AL | 6BH | 6BL | 6CH | 6CL | 6DH | 6DL | 6EH | 6EL | 6FH |

| 5 | 71H | 71L | 72H | 72L | 73H | 73L | 74H | 74L | 75H | 75L | 76H | 76L | 77H | 77L | 78H |

address: FFh STATUS

| FFh STATUS    | D7 | D6 | D5 | D4 | D3 | D2   | D1    | D0    |

|---------------|----|----|----|----|----|------|-------|-------|

| Register name | -  | -  | =  | -  | =  | DFIF | FEDIF | SCRIF |

| R/W           |    |    |    |    |    | R    | R     | R     |

| Default       | Х  | Х  | X  | Х  | X  |      |       |       |

D0: SCRIF End of scroll interrupt occurrence flag

- 0: No end of scroll interrupt has occurred.

- 1: An end of scroll interrupt has occurred.

- \* The flag needs to be cleared manually (CTRL1.SCRLCLR).

D1: FEDIF End of fade interrupt occurrence flag

- 0: No end of fade interrupt has occurred.

- 1 : An end of fade interrupt has occurred.

- \* The flag needs to be cleared manually (CTRL1.FADECLR).

D2: DFIF End of palette fade interrupt occurrence flag

- 0 : No end of palette fade interrupt has occurred.

- 1 : An end of palette fade interrupt has occurred.

- \* The flag needs to be cleared manually (CTRL1.DFCLR).

The OR of SCRIF, FEDIF and DFIF appear at the interrupt pin.

\* The addresses used here are all dummy and not used in actual communications.

- SANYO Semiconductor Co.,Ltd. assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein.

- SANYO Semiconductor Co.,Ltd. strives to supply high-quality high-reliability products, however, any and all semiconductor products fail or malfunction with some probability. It is possible that these probabilistic failures or malfunction could give rise to accidents or events that could endanger human lives, trouble that could give rise to smoke or fire, or accidents that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO Semiconductor Co.,Ltd. products described or contained herein are controlled under any of applicable local export control laws and regulations, such products may require the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written consent of SANYO Semiconductor Co.,Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO Semiconductor Co.,Ltd. product that you intend to use.