#### **Pin Configurations**

| ions               | j |    | ~ ~                    |    |                     |      |

|--------------------|---|----|------------------------|----|---------------------|------|

| REF0               |   | 1  | $\smile$               | 48 | V <sub>DDREF</sub>  |      |

| REF1               |   | 2  |                        | 47 | REF2                |      |

| V <sub>SS</sub>    |   | 3  |                        | 46 | V <sub>DDAPIC</sub> |      |

| XTALIN             |   | 4  |                        | 45 | APIC0               |      |

| XTALOUT            |   | 5  |                        | 44 | APIC1               |      |

| V <sub>SS</sub>    |   | 6  |                        | 43 | V <sub>SS</sub>     |      |

| PCICLK_F           |   | 7  |                        | 42 | RESERVED            |      |

| PCICLK1            | Г | 8  |                        | 41 | V <sub>DDCPU</sub>  |      |

| V <sub>DDPCI</sub> |   | 9  | ew)                    | 40 | CPUCLK0             |      |

| PCICLK2            |   | 10 | i N                    | 39 | CPUCLK1             |      |

| PCICLK3            |   | 11 | 48-pin SSOP (Top View) | 38 | V <sub>SS</sub>     |      |

| V <sub>SS</sub>    |   | 12 | P                      | 37 | V <sub>DDCPU</sub>  |      |

| PCICLK4            | Г | 13 | SSC                    | 36 | CPUCLK2             |      |

| PCICLK5            |   | 14 | Li                     | 35 | CPUCLK3             |      |

| V <sub>DDPCI</sub> |   | 15 | 48-                    | 34 | V <sub>SS</sub>     |      |

| PCICLK6            |   | 16 | •                      | 33 | AV <sub>DD</sub>    |      |

| PCICLK7            |   | 17 |                        | 32 | V <sub>SS</sub>     |      |

| V <sub>SS</sub>    |   | 18 |                        | 31 | PCI_STOP            |      |

| AV <sub>DD</sub>   |   | 19 |                        | 30 | CPU_STOP            |      |

| V <sub>SS</sub>    |   | 20 |                        | 29 | PWR_DWN             |      |

| V <sub>DDUSB</sub> |   | 21 |                        | 28 | N/C                 |      |

| USBCLK0            |   | 22 |                        | 27 | SEL0                |      |

| USBCLK1            |   | 23 |                        | 26 | SEL1                |      |

| V <sub>SS</sub>    | 9 | 24 |                        | 25 | SEL100 CY22         | 80-1 |

| REF0               |   | 1  | $\bigcirc$      | 48 |    | V <sub>DDREF</sub>  |            |

|--------------------|---|----|-----------------|----|----|---------------------|------------|

| REF1               |   | 2  |                 | 47 | 5  | REF2                |            |

| V <sub>SS</sub>    |   | 3  |                 | 46 |    | V <sub>DDAPIC</sub> |            |

| XTALIN             |   | 4  |                 | 45 |    | APIC0               |            |

| XTALOUT            |   | 5  |                 | 44 |    | APIC1               |            |

| V <sub>SS</sub>    |   | 6  |                 | 43 |    | V <sub>SS</sub>     |            |

| PCICLK_F           |   | 7  |                 | 42 |    | RESERVED            |            |

| PCICLK1            |   | 8  | ~               | 41 |    | V <sub>DDCPU</sub>  |            |

| V <sub>DDPCI</sub> |   | 9  | lew             | 40 |    | CPUCLK0             |            |

| PCICLK2            |   | 10 | SSOP (Top View) | 39 |    | CPUCLK1             |            |

| PCICLK3            |   | 11 | £               | 38 |    | V <sub>SS</sub>     |            |

| V <sub>SS</sub>    |   | 12 | Р               | 37 |    | V <sub>DDCPU</sub>  |            |

| PCICLK4            |   | 13 | SS              | 36 |    | CPUCLK2             |            |

| PCICLK5            |   | 14 | 48-pin          | 35 |    | CPUCLK3             |            |

| V <sub>DDPCI</sub> |   | 15 | 48-             | 34 |    | V <sub>SS</sub>     |            |

| PCICLK6            |   | 16 |                 | 33 |    | AV <sub>DD</sub>    |            |

| PCICLK7            |   | 17 |                 | 32 |    | V <sub>SS</sub>     |            |

| V <sub>SS</sub>    |   | 18 |                 | 31 |    | PCI_STOP            |            |

| AV <sub>DD</sub>   | Г | 19 |                 | 30 |    | CPU_STOP            |            |

| V <sub>SS</sub>    |   | 20 |                 | 29 |    | PWR_DWN             |            |

| V <sub>DDUSB</sub> |   | 21 |                 | 28 |    | SEL_SS              |            |

| USBCLK0            |   | 22 |                 | 27 | Ц. | SEL0                |            |

| USBCLK1            |   | 23 |                 | 26 |    | SEL1                | CY2280-11S |

| V <sub>SS</sub>    | Ц | 24 |                 | 25 | μ  | SEL100              | CY2280-21S |

#### **Pin Summary**

| Name                   | Pins                                 | Description                                                                                       |

|------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------|

| V <sub>DDPCI</sub>     | 15, 9                                | 3.3V Digital voltage supply for PCI clocks                                                        |

| V <sub>DDUSB</sub>     | 21                                   | 3.3V Digital voltage supply for USB clocks                                                        |

| V <sub>DDREF</sub>     | 48                                   | 3.3V Digital voltage supply for REF clocks                                                        |

| V <sub>DDAPIC</sub>    | 46                                   | 2.5V Digital voltage supply for APIC clocks                                                       |

| V <sub>DDCPU</sub>     | 41, 37                               | 2.5V Digital voltage supply for CPU clocks                                                        |

| AV <sub>DD</sub>       | 33, 19                               | Analog voltage supply, 3.3V                                                                       |

| V <sub>SS</sub>        | 3, 6, 12, 18, 20, 24, 32, 34, 38, 43 | Ground                                                                                            |

| XTALIN <sup>[1]</sup>  | 4                                    | Reference crystal input                                                                           |

| XTALOUT <sup>[1]</sup> | 5                                    | Reference crystal feedback                                                                        |

| PCI_STOP               | 31                                   | Active LOW control input to stop PCI clocks                                                       |

| CPU_STOP               | 30                                   | Active LOW control input to stop CPU clocks                                                       |

| PWR_DWN                | 29                                   | Active LOW control input to power down device                                                     |

| SEL_SS                 | 28                                   | Spread spectrum select input (-11S and -21S options)                                              |

| N/C                    | 28                                   | Spread spectrum select input (-1 option)                                                          |

| SEL0                   | 27                                   | CPU frequency select input, bit 0 (see Function Table)                                            |

| SEL1                   | 26                                   | CPU frequency select input, bit 1 (see Function Table)                                            |

| SEL100                 | 25                                   | CPU frequency select input, selects between 100 MHz and 66.6 MHz (see Function Table)             |

| CPUCLK[0:3]            | 40, 39, 36, 35                       | CPU clock outputs                                                                                 |

| PCICLK[1:7]            | 8, 10, 11, 13, 14, 16, 17            | PCI clock outputs, at one-half or one-third the CPU frequency of 66.6 MHz or 100 MHz respectively |

| PCICLK_F               | 7                                    | Free-running PCI clock output                                                                     |

| APIC[0:1]              | 45, 44                               | APIC clock outputs                                                                                |

| REF[0:2]               | 1, 2, 47                             | 3.3V Reference clock outputs                                                                      |

| USBCLK[0:1]            | 22, 23                               | USB clock outputs                                                                                 |

| RESERVED               | 42                                   | Reserved                                                                                          |

| Note:                  | 1                                    |                                                                                                   |

1. For best accuracy, use a parallel-resonant crystal,  $C_{LOAD}$  = 18 pF.

### Function Table (-11S Option)

| SEL100 | SEL1 | SEL0 | SEL_SS <sup>[2]</sup> | CPU/PCI<br>Ratio | CPUCLK    | PCICLK_F<br>PCICLK | REF                 | APIC                | USBCLK |

|--------|------|------|-----------------------|------------------|-----------|--------------------|---------------------|---------------------|--------|

| 0      | 0    | 0    | N/A                   | 2                | Hi-Z      | Hi-Z               | Hi-Z                | Hi-Z                | Hi-Z   |

| 0      | 0    | 1    | N/A                   | 2                | Reserved  | Reserved           | 14.318 MHz          | 14.318 MHz          | 48 MHz |

| 0      | 1    | 0    | N/A                   | 2                | Reserved  | Reserved           | 14.318 MHz          | 14.318 MHz          | 48 MHz |

| 0      | 1    | 1    | 0 (downspread)        | 2                | 66.66 MHz | 33.33 MHz          | 14.318 MHz          | 14.318 MHz          | 48 MHz |

| 0      | 1    | 1    | 1 (no spread)         | 2                | 66.66 MHz | 33.33 MHz          | 14.318 MHz          | 14.318 MHz          | 48 MHz |

| 1      | 0    | 0    | N/A                   | 3                | TCLK/2    | TCLK/6             | TCLK <sup>[3]</sup> | TCLK <sup>[3]</sup> | TCLK/2 |

| 1      | 0    | 1    | N/A                   | 3                | Reserved  | Reserved           | 14.318 MHz          | 14.318 MHz          | 48 MHz |

| 1      | 1    | 0    | N/A                   | 3                | Reserved  | Reserved           | 14.318 MHz          | 14.318 MHz          | 48 MHz |

| 1      | 1    | 1    | 0 (downspread)        | 3                | 100 MHz   | 33.33 MHz          | 14.318 MHz          | 14.318 MHz          | 48 MHz |

| 1      | 1    | 1    | 1 (no spread)         | 3                | 100 MHz   | 33.33 MHz          | 14.318 MHz          | 14.318 MHz          | 48 MHz |

### Function Table (-21S Option)

| SEL100 | SEL1 | SEL0 | SEL_SS <sup>[2]</sup> | CPU/PCI<br>Ratio | CPUCLK    | PCICLK_F<br>PCICLK | REF                 | APIC                   | USBCLK |

|--------|------|------|-----------------------|------------------|-----------|--------------------|---------------------|------------------------|--------|

| 0      | 0    | 0    | N/A                   | 2                | Hi-Z      | Hi-Z               | Hi-Z                | Hi-Z                   | Hi-Z   |

| 0      | 0    | 1    | N/A                   | 2                | Reserved  | Reserved           | 14.318 MHz          | Reserved               | 48 MHz |

| 0      | 1    | 0    | N/A                   | 2                | Reserved  | Reserved           | 14.318 MHz          | Reserved               | 48 MHz |

| 0      | 1    | 1    | 0 (downspread)        | 2                | 66.66 MHz | 33.33 MHz          | 14.318 MHz          | 16.67 MHz              | 48 MHz |

| 0      | 1    | 1    | 1 (no spread)         | 2                | 66.66 MHz | 33.33 MHz          | 14.318 MHz          | 16.67 MHz              | 48 MHz |

| 1      | 0    | 0    | N/A                   | 3                | TCLK/2    | TCLK/6             | TCLK <sup>[3]</sup> | TCLK/12 <sup>[3]</sup> | TCLK/2 |

| 1      | 0    | 1    | N/A                   | 3                | Reserved  | Reserved           | 14.318 MHz          | Reserved               | 48 MHz |

| 1      | 1    | 0    | N/A                   | 3                | Reserved  | Reserved           | 14.318 MHz          | Reserved               | 48 MHz |

| 1      | 1    | 1    | 0 (downspread)        | 3                | 100 MHz   | 33.33 MHz          | 14.318 MHz          | 16.67 MHz              | 48 MHz |

| 1      | 1    | 1    | 1 (no spread)         | 3                | 100 MHz   | 33.33 MHz          | 14.318 MHz          | 16.67 MHz              | 48 MHz |

#### **Actual Clock Frequency Values**

| Clock Output | Target Frequency<br>(MHz) | Actual Frequency<br>(MHz) | РРМ   |

|--------------|---------------------------|---------------------------|-------|

| CPUCLK       | 66.67                     | 66.654                    | –195  |

| CPUCLK       | 100                       | 99.77                     | -2346 |

| USBCLK       | 48.0                      | 48.008                    | 167   |

### **Power Management Logic**

| CPU_STOP | PCI_STOP | PWR_DWN | CPUCLK  | PCICLK  | PCICLK_F | Other<br>Clocks | Osc.    | PLLs    |

|----------|----------|---------|---------|---------|----------|-----------------|---------|---------|

| Х        | Х        | 0       | Low     | Low     | Low      | Low             | Off     | Off     |

| 0        | 0        | 1       | Low     | Low     | Running  | Running         | Running | Running |

| 0        | 1        | 1       | Low     | Running | Running  | Running         | Running | Running |

| 1        | 0        | 1       | Running | Low     | Running  | Running         | Running | Running |

| 1        | 1        | 1       | Running | Running | Running  | Running         | Running | Running |

Notes:

2. Target frequency is modulated by percentage shown (max.) when SEL\_SS = 0.

3. TCLK supplied on the XTALIN pin in Test Mode.

#### **Maximum Ratings**

| (Above which the useful life may be impa lines, not tested.) | ired. For user guide-          |

|--------------------------------------------------------------|--------------------------------|

| Supply Voltage                                               | –0.5 to + 7.0V                 |

| Input Voltage                                                | –0.5V to V <sub>DD</sub> + 0.5 |

| Storage Temperature (Non-Condensing)65°C to +150°C |

|----------------------------------------------------|

| Junction Temperature+150°C                         |

| Package Power Dissipation1W                        |

| Static Discharge Voltage                           |

### **Operating Conditions**<sup>[4]</sup>

| Parameter                                                                          | Description                                                                                    | Min.   | Max.                 | Unit |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------|----------------------|------|

| AV <sub>DD</sub> , V <sub>DDPCI</sub> ,<br>V <sub>DDUSB</sub> , V <sub>DDREF</sub> | Analog and Digital Supply Voltage                                                              | 3.135  | 3.465                | V    |

| V <sub>DDCPU</sub>                                                                 | CPU Supply Voltage                                                                             | 2.375  | 2.625                | V    |

| V <sub>DDAPIC</sub>                                                                | APIC Supply Voltage                                                                            | 2.375  | 2.625                | V    |

| T <sub>A</sub>                                                                     | Operating Temperature, Ambient                                                                 | 0      | 70                   | °C   |

| CL                                                                                 | Max. Capacitive Load on<br>CPUCLK<br>PCICLK<br>APIC, REF<br>USB                                |        | 20<br>30<br>20<br>20 | pF   |

| f <sub>(REF)</sub>                                                                 | Reference Frequency, Oscillator Nominal Value                                                  | 14.318 | 14.318               | MHz  |

| t <sub>PU</sub>                                                                    | Power-up time for all VDD's to reach minimum specified voltage (power ramps must be monotonic) | 0.05   | 50                   | ms   |

### Electrical Characteristics Over the Operating Range

| Parameter         | Description                                         | Test Conditions                                                                          | 5                         |            | Min. | Max. | Unit |

|-------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------|------------|------|------|------|

| V <sub>IH</sub>   | High-level Input Voltage                            | Except Crystal Inputs <sup>[5]</sup>                                                     |                           |            | 2.0  |      | V    |

| V <sub>IL</sub>   | Low-level Input Voltage                             | Except Crystal Inputs <sup>[5]</sup>                                                     |                           |            |      | 0.8  | V    |

| V <sub>OH</sub>   | High-level Output Voltage <sup>[6]</sup>            | $V_{DDCPU} = V_{DDAPIC} = 2.375V$                                                        | I <sub>OH</sub> = 12 mA   | CPUCLK     | 2.0  |      | V    |

|                   |                                                     |                                                                                          | I <sub>OH</sub> = 18 mA   | APIC       |      |      |      |

| V <sub>OL</sub>   | Low-level Output Voltage <sup>[6]</sup>             | $V_{DDCPU} = V_{DDAPIC} = 2.375V$                                                        | I <sub>OL</sub> = 12 mA   | CPUCLK     |      | 0.4  | V    |

|                   |                                                     |                                                                                          | I <sub>OL</sub> = 18 mA   | APIC       |      |      |      |

| V <sub>OH</sub>   | High-level Output Voltage <sup>[6]</sup>            | V <sub>DDPCI</sub> , AV <sub>DD</sub> , V <sub>DDREF</sub> , V <sub>DDUSB</sub> = 3.135V | I <sub>OH</sub> = 14.5 mA | PCICLK     | 2.4  |      | V    |

|                   |                                                     |                                                                                          | I <sub>OH</sub> = 16 mA   | USBCLK     |      |      |      |

|                   |                                                     |                                                                                          | I <sub>OH</sub> = 16 mA   | REF        |      |      |      |

| V <sub>OL</sub>   | Low-level Output Voltage <sup>[6]</sup>             | V <sub>DDPCI</sub> , AV <sub>DD</sub> , V <sub>DDREF</sub> , V <sub>DDUSB</sub> = 3.135V | I <sub>OL</sub> = 9.4 mA  | PCICLK     |      | 0.4V | V    |

|                   |                                                     |                                                                                          | I <sub>OL</sub> = 9 mA    | USBCLK     |      |      |      |

|                   |                                                     |                                                                                          | I <sub>OL</sub> = 9 mA    | REF        |      |      |      |

| I <sub>IH</sub>   | Input High Current                                  | $V_{IH} = V_{DD}$                                                                        |                           |            | -10  | +10  | μΑ   |

| IIL               | Input Low Current                                   | $V_{IL} = 0V$                                                                            |                           |            |      | 10   | μΑ   |

| I <sub>OZ</sub>   | Output Leakage Current                              | Three-state                                                                              |                           |            | -10  | +10  | μΑ   |

| I <sub>DD25</sub> | Power Supply Current for 2.5V Clocks <sup>[6]</sup> | $V_{DDCPU} = 2.625V, V_{IN} = 0 \text{ or } V_{DD}, \text{ Loaded}$                      | Outputs, CPU :            | = 66.6 MHz |      | 70   | mA   |

| I <sub>DD25</sub> | Power Supply Current for 2.5V Clocks <sup>[6]</sup> | $V_{DDCPU}$ = 2.625V, $V_{IN}$ = 0 or $V_{DD}$ , Loaded                                  | Outputs, CPU              | = 100 MHz  |      | 100  | mA   |

| I <sub>DD33</sub> | Power Supply Current for 3.3V Clocks <sup>[6]</sup> | $V_{DD}$ = 3.465V, $V_{IN}$ = 0 or $V_{DD}$ , Loaded Ou                                  | tputs                     |            |      | 170  | mA   |

| I <sub>DDS</sub>  | Power-down Current <sup>[6]</sup>                   | Current draw in power-down state                                                         |                           |            |      | 500  | μΑ   |

Notes:

Electrical parameters are guaranteed with these operating conditions.

Crystal Inputs have CMOS thresholds.

Parameter is guaranteed by design and characterization. Not 100% tested in production.

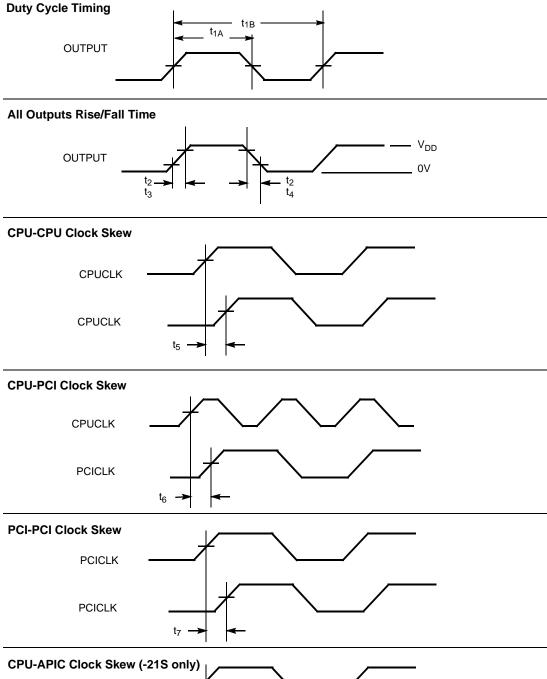

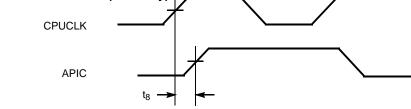

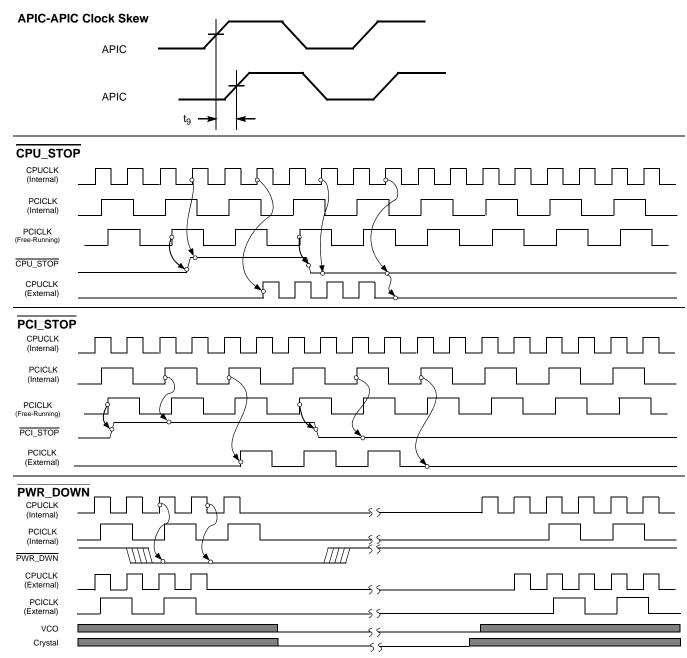

# Switching Characteristics<sup>[6, 7]</sup>

| Parameter       | Output            | Description                                           | Test Conditions                                                | ;                | Min. Typ. Max. |     | Unit |      |

|-----------------|-------------------|-------------------------------------------------------|----------------------------------------------------------------|------------------|----------------|-----|------|------|

| t <sub>1</sub>  | All               | Output Duty Cycle <sup>[8]</sup>                      | $t_1 = t_{1A} \div t_{1B}$                                     |                  | 45             | 50  | 55   | %    |

| t <sub>2</sub>  | CPUCLK,<br>APIC   | CPU and APIC Clock<br>Rising and Falling Edge<br>Rate | Between 0.4V and 2.0V                                          | -1,-11S,<br>-21S | 1.0            |     | 4.0  | V/ns |

| t <sub>2</sub>  | PCICLK            | PCI Clock Rising and<br>Falling Edge Rate             | Between 0.4V and 2.4V                                          | -1,-11S,<br>-21S | 1.0            |     | 4.0  | V/ns |

| t <sub>2</sub>  | USBCLK,<br>REF    | USB, REF Rising and<br>Falling Edge Rate              | Between 0.4V and 2.4V                                          | ·                | 0.5            |     | 2.0  | V/ns |

| t <sub>3</sub>  | CPUCLK            | CPU Clock Rise Time                                   | Between 0.4V and 2.0V                                          | -1,-11S,<br>-21S | 0.4            |     | 1.6  | ns   |

| t <sub>4</sub>  | CPUCLK            | CPU Clock Fall Time                                   | Between 2.0V and 0.4V                                          | -1,-11S,<br>-21S | 0.4            |     | 1.6  | ns   |

| t <sub>5</sub>  | CPUCLK            | CPU-CPU Clock Skew                                    | Measured at 1.25V                                              |                  |                | 100 | 175  | ps   |

| t <sub>6</sub>  | CPUCLK,<br>PCICLK | CPU-PCI Clock Skew <sup>[9]</sup>                     | Measured at 1.25V for 2.5V clocks, and at 1.5V for 3.3V clocks | -1,-11S,<br>-21S | 1.5            |     | 4.0  | ns   |

| t <sub>7</sub>  | PCICLK,<br>PCICLK | PCI-PCI Clock Skew                                    | Measured at 1.5V                                               |                  |                |     | 250  | ps   |

| t <sub>8</sub>  | CPUCLK,<br>APIC   | CPU-APIC Clock<br>Skew <sup>[10]</sup>                | Measured at 1.25V for 2.5V clocks                              | -21S             | 2.0            |     | 4.5  | ns   |

| t <sub>9</sub>  | APIC              | APIC-APIC Clock Skew                                  | Measured at 1.25V                                              |                  |                | 100 | 175  | ps   |

| t <sub>10</sub> | CPUCLK            | Cycle-Cycle Clock Jitter                              | Measured at 1.25V                                              | -1,-11S,<br>-21S |                | 200 | 250  | ps   |

| t <sub>11</sub> | PCICLK            | Cycle-Cycle Clock Jitter                              | Measured at 1.5V                                               | •                |                | 250 | 500  | ps   |

| t <sub>12</sub> | CPUCLK,<br>PCICLK | Power-up Time                                         | CPU, PCI clock stabilization fro                               | om               |                |     | 3    | ms   |

Notes:

All parameters specified with loaded outputs.

Buty cycle is measured at 1.5V when V<sub>DD</sub> = 3.3V. When V<sub>DD</sub> = 2.5V, duty cycle is measured at 1.25V.

PCI lags CPU for -11S and -21S options.

APIC lags CPU for -21S option.

#### **Switching Waveforms**

#### Switching Waveforms (continued)

Shaded section on the VCO and Crystal waveforms indicates that the VCO and crystal oscillator are active, and there is a valid clock.

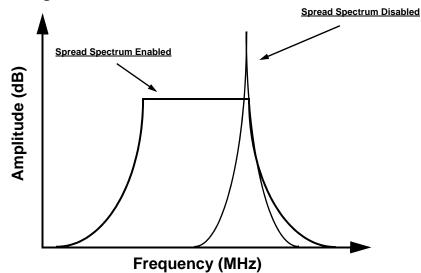

## Spread Spectrum Clocking

#### Table 2.

| Description                                     | Configuration   | Outputs        | Min. | Max. | Unit |

|-------------------------------------------------|-----------------|----------------|------|------|------|

| Modulation Frequency                            | All (except -1) |                | 30.0 | 33.0 | kHz  |

| Down Spread Margin at the Fundamental Frequency | -11S            | CPU, PCI       | 0.0  | -0.6 | %    |

| Down Spread Margin at the Fundamental Frequency | -21S            | CPU, PCI, APIC | 0.0  | -0.6 | %    |

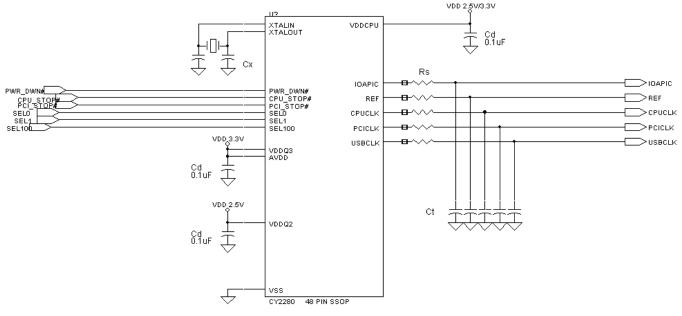

### **Application Information**

Clock traces must be terminated with either series or parallel termination, as is normally done.

#### **Application Circuit**

Cd = DECOUPLING CAPACITORS

Ct = OPTIONAL EMI-REDUCING CAPACITORS

Cx = OPTIONAL LOAD MATCHING CAPACITOR

Rs = SERIES TERMINATING RESISTORS

#### Summary

- A parallel-resonant crystal should be used as the reference to the clock generator. The operating frequency and C<sub>LOAD</sub> of this crystal should be as specified in the data sheet. Optional trimming capacitors may be needed if a crystal with a different C<sub>LOAD</sub> is used. Footprints must be laid out for flexibility.

- Surface mount, low-ESR, ceramic capacitors should be used for filtering. Typically, these capacitors have a value of 0.1 μF. In some cases, smaller value capacitors may be required.

- The value of the series terminating resistor satisfies the following equation, where Rtrace is the loaded characteristic impedance of the trace, Rout is the output impedance of the clock generator (specified in the data sheet), and Rseries is the series terminating resistor.

Rseries > Rtrace Rout

- Footprints must be laid out for optional EMI-reducing capacitors, which should be placed as close to the terminating resistor as is physically possible. Typical values of these capacitors range from 4.7 pF to 22 pF.

- A Ferrite Bead may be used to isolate the Board V<sub>DD</sub> from the clock generator V<sub>DD</sub> island. Ensure that the Ferrite Bead offers greater than 50Ω impedance at the clock frequency, under loaded DC conditions. Please refer to the application note "Layout and Termination Techniques for Cypress Clock Generators" for more details.

- If a Ferrite Bead is used, a 10 μF–22 μF tantalum bypass capacitor should be placed close to the Ferrite Bead. This capacitor prevents power supply droop during current surges.

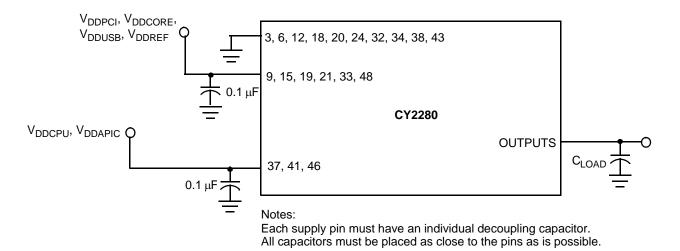

### **Test Circuit**

#### **Ordering Information**

| Ordering Code | Package Name | Package Type | Operating Range |

|---------------|--------------|--------------|-----------------|

| CY2280PVC-1   | O48          | 48-Pin SSOP  | Commercial      |

| CY2280PVC-11S | O48          | 48-Pin SSOP  | Commercial      |

| CY2280PVC-21S | O48          | 48-Pin SSOP  | Commercial      |

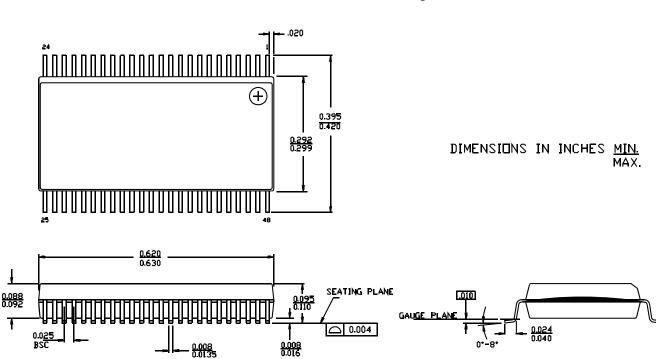

#### Package Diagram

48-Lead Shrunk Small Outline Package O48

While SLI has reviewed all information herein for accuracy and reliability, Spectra Linear Inc. assumes no responsibility for the use of any circuitry or for the infringement of any patents or other rights of third parties which would result from each use. This product is intended for use in normal commercial applications and is not warranted nor is it intended for use in life support, critical medical instruments, or any other application requiring extended temperature range, high reliability, or any other extraordinary environmental requirements unless pursuant to additional processing by Spectra Linear Inc., and expressed written agreement by Spectra Linear Inc. Spectra Linear Inc. reserves the right to change any circuitry or specification without notice.

Rev 1.0, November 25, 2006