**Data Sheet**

## AD9361

## **TABLE OF CONTENTS**

| Features                                                                           | Theory of Operation                | 33 |

|------------------------------------------------------------------------------------|------------------------------------|----|

| Applications1                                                                      | General                            | 33 |

| Functional Block Diagram                                                           | Receiver                           | 33 |

| General Description                                                                | Transmitter                        | 33 |

| Revision History                                                                   | Clock Input Options                | 33 |

| Specifications                                                                     | Synthesizers                       | 34 |

| Current Consumption—VDD_Interface8                                                 | Digital Data Interface             | 34 |

| Current Consumption—VDDD1P3_DIG and VDDAx                                          | Enable State Machine               | 34 |

| (Combination of all 1.3 V Supplies)10                                              | SPI Interface                      | 35 |

| Absolute Maximum Ratings15                                                         | Control Pins                       | 35 |

| Reflow Profile                                                                     | GPO Pins (GPO_3 to GPO_0)          | 35 |

| Thermal Resistance                                                                 | Auxiliary Converters               | 35 |

| ESD Caution                                                                        | Powering the AD9361                | 35 |

| Pin Configuration and Function Descriptions16                                      | Packaging and Ordering Information | 36 |

| Typical Performance Characteristics                                                | Outline Dimensions                 | 36 |

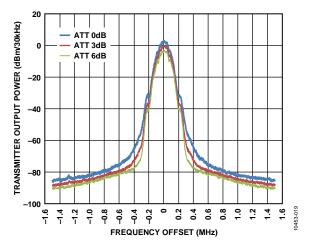

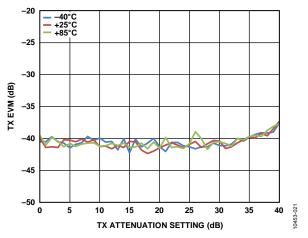

| 800 MHz Frequency Band20                                                           | Ordering Guide                     | 36 |

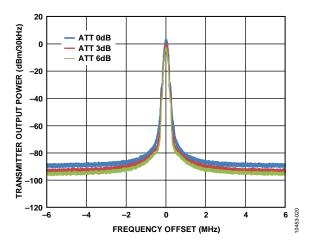

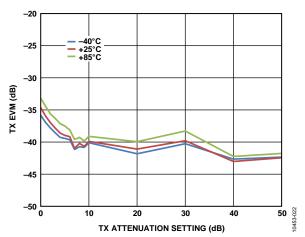

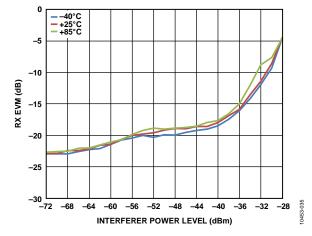

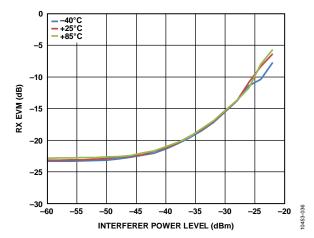

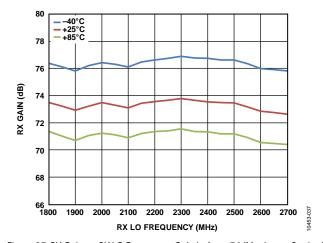

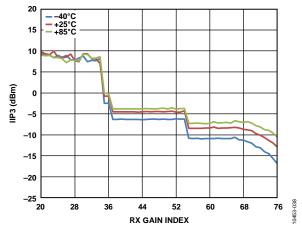

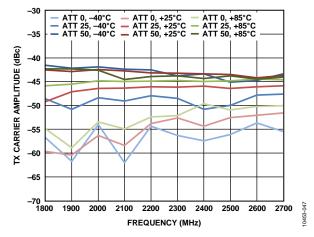

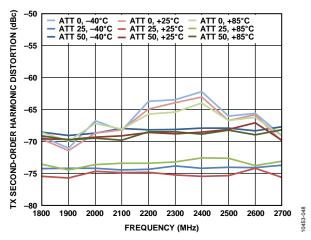

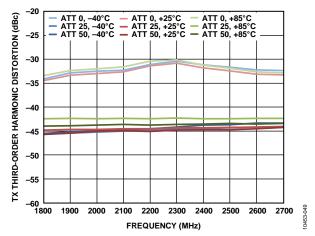

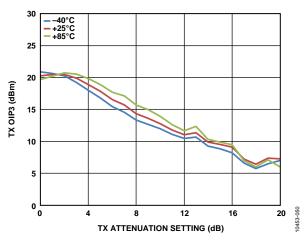

| 2.4 GHz Frequency Band                                                             | -                                  |    |

| 5.5 GHz Frequency Band                                                             |                                    |    |

| REVISION HISTORY                                                                   |                                    |    |

| 11/2016—Rev. E to Rev. F                                                           | 11/2013—Rev. C to Rev. D           |    |

| Changes to Features Section and General Description Section. 1                     | Changes to Ordering Guide          | 36 |

| Change to Transmitter—General, Center Frequency Parameter, Minimum Column, Table 1 | 9/2013—Revision C: Initial Version |    |

| 1                                                                                  | 7,2020 Alevidian G. Immin verdidi  |    |

| 11/2014—Rev. D to Rev. E                                                           |                                    |    |

## **SPECIFICATIONS**

$Electrical\ characteristics\ at\ VDD\_GPO = 3.3\ V,\ VDD\_INTERFACE = 1.8\ V,\ and\ all\ other\ VDDx\ pins = 1.3\ V,\ T_A = 25^{\circ}C,\ unless\ otherwise\ noted.$

Table 1.

| Parameter <sup>1</sup>                                | Symbol | Min | Тур            | Max  | Unit    | Test Conditions/<br>Comments |

|-------------------------------------------------------|--------|-----|----------------|------|---------|------------------------------|

| RECEIVERS, GENERAL                                    |        |     |                |      |         |                              |

| Center Frequency                                      |        | 70  |                | 6000 | MHz     |                              |

| Gain                                                  |        |     |                |      |         |                              |

| Minimum                                               |        |     | 0              |      | dB      |                              |

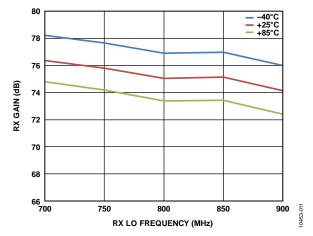

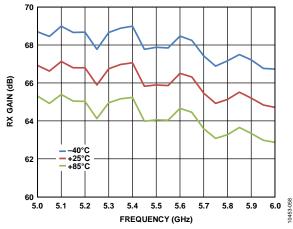

| Maximum                                               |        |     | 74.5           |      | dB      | At 800 MHz                   |

|                                                       |        |     | 73.0           |      | dB      | At 2300 MHz (RX1A, RX2A)     |

|                                                       |        |     | 72.0           |      | dB      | At 2300 MHz (RX1B,           |

|                                                       |        |     |                |      |         | RX1C, RX2B, RX2C)            |

|                                                       |        |     | 65.5           |      | dB      | At 5500 MHz (RX1A, RX2A)     |

| Gain Step                                             |        |     | 1              |      | dB      |                              |

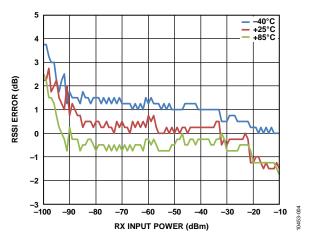

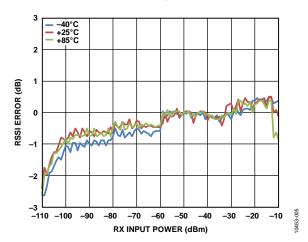

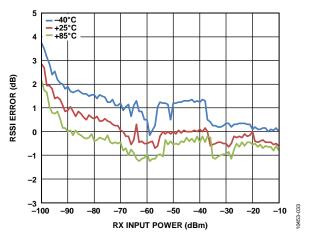

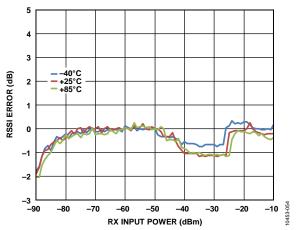

| Received Signal Strength<br>Indicator                 | RSSI   |     |                |      |         |                              |

| Range                                                 |        |     | 100            |      | dB      |                              |

| Accuracy                                              |        |     | ±2             |      | dB      |                              |

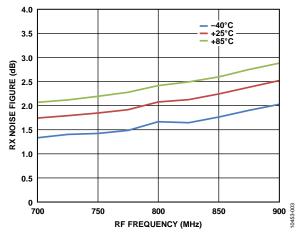

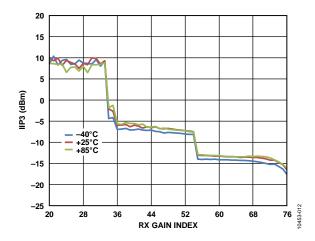

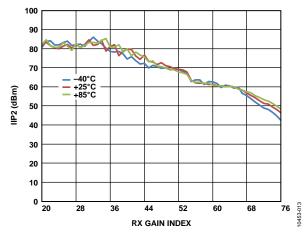

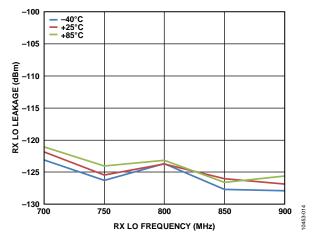

| RECEIVERS, 800 MHz                                    |        |     |                |      |         |                              |

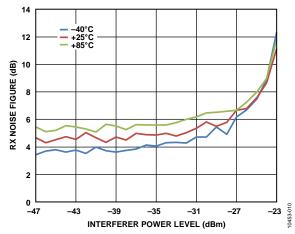

| Noise Figure                                          | NF     |     | 2              |      | dB      | Maximum RX gain              |

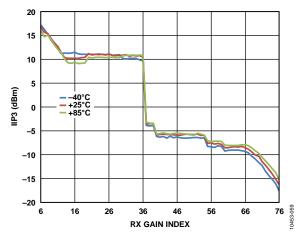

| Third-Order Input Intermodulation<br>Intercept Point  | IIP3   |     | -18            |      | dBm     | Maximum RX gain              |

| Second-Order Input<br>Intermodulation Intercept Point | IIP2   |     | 40             |      | dBm     | Maximum RX gain              |

| Local Oscillator (LO) Leakage                         |        |     | -122           |      | dBm     | At RX front-end input        |

| Quadrature                                            |        |     |                |      |         |                              |

| Gain Error                                            |        |     | 0.2            |      | %       |                              |

| Phase Error                                           |        |     | 0.2            |      | Degrees |                              |

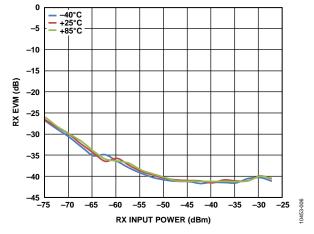

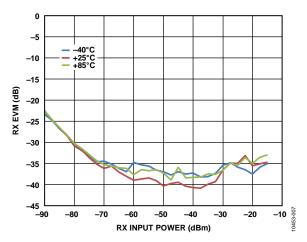

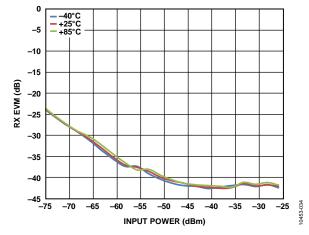

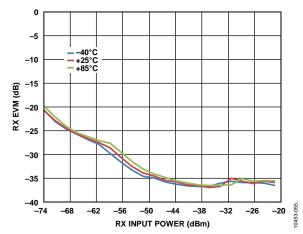

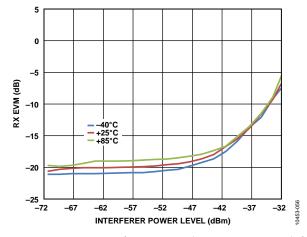

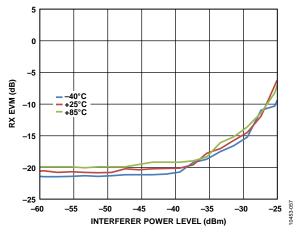

| Modulation Accuracy (EVM)                             |        |     | -42            |      | dB      | 19.2 MHz reference clock     |

| Input S <sub>11</sub>                                 |        |     | -10            |      | dB      |                              |

| RX1 to RX2 Isolation                                  |        |     |                |      |         |                              |

| RX1A to RX2A, RX1C to RX2C                            |        |     | 70             |      | dB      |                              |

| RX1B to RX2B                                          |        |     | 55             |      | dB      |                              |

| RX2 to RX1 Isolation                                  |        |     |                |      |         |                              |

| RX2A to RX1A, RX2C to RX1C                            |        |     | 70             |      | dB      |                              |

| RX2B to RX1B                                          |        |     | 55             |      | dB      |                              |

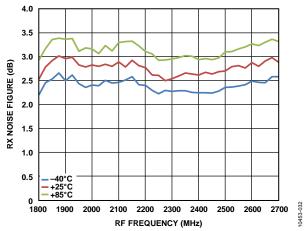

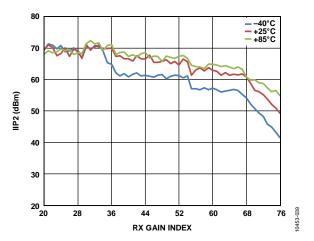

| RECEIVERS, 2.4 GHz                                    |        |     |                |      |         |                              |

| Noise Figure                                          | NF     |     | 3              |      | dB      | Maximum RX gain              |

| Third-Order Input Intermodulation<br>Intercept Point  | IIP3   |     | -14            |      | dBm     | Maximum RX gain              |

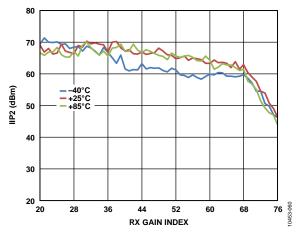

| Second-Order Input<br>Intermodulation Intercept Point | IIP2   |     | 45             |      | dBm     | Maximum RX gain              |

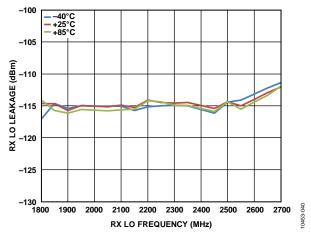

| LO Leakage                                            |        |     | -110           |      | dBm     | At receiver front-end input  |

| Quadrature                                            |        |     |                |      |         | •                            |

| Gain Error                                            |        |     | 0.2            |      | %       |                              |

| Phase Error                                           |        |     | 0.2            |      | Degrees |                              |

| Modulation Accuracy (EVM)                             |        |     | -42            |      | dB      | 40 MHz reference clock       |

| Input S <sub>11</sub>                                 |        |     | -10            |      | dB      |                              |

| RX1 to RX2 Isolation                                  |        |     |                |      |         |                              |

| RX1A to RX2A, RX1C to RX2C                            |        |     | 65             |      | dB      |                              |

| RX1B to RX2B                                          |        |     | 50             |      | dB      |                              |

| RX2 to RX1 Isolation                                  |        |     | - <del>-</del> |      |         |                              |

| RX2A to RX1A, RX2C to RX1C                            |        |     | 65             |      | dB      |                              |

| RX2B to RX1B                                          |        |     | 50             |      | dB      |                              |

| Parameter <sup>1</sup>                                  | Symbol | Min    | Тур        | Max  | Unit          | Test Conditions/<br>Comments            |

|---------------------------------------------------------|--------|--------|------------|------|---------------|-----------------------------------------|

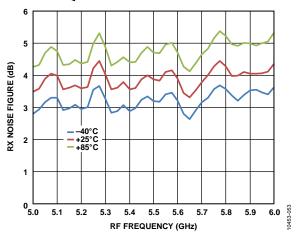

| RECEIVERS, 5.5 GHz                                      |        |        |            |      |               |                                         |

| Noise Figure                                            | NF     |        | 3.8        |      | dB            | Maximum RX gain                         |

| Third-Order Input Intermodulation<br>Intercept Point    | IIP3   |        | -17        |      | dBm           | Maximum RX gain                         |

| Second-Order Input<br>Intermodulation Intercept Point   | IIP2   |        | 42         |      | dBm           | Maximum RX gain                         |

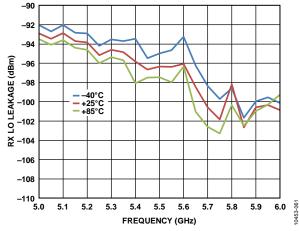

| LO Leakage<br>Quadrature                                |        |        | <b>-95</b> |      | dBm           | At RX front-end input                   |

| Gain Error                                              |        |        | 0.2        |      | %             |                                         |

| Phase Error                                             |        |        | 0.2        |      |               |                                         |

|                                                         |        |        | -37        |      | Degrees<br>dB | 40 MHz reference clock                  |

| Modulation Accuracy (EVM)                               |        |        | -37        |      | ав            | (doubled internally for RF synthesizer) |

| Input S <sub>11</sub>                                   |        |        | -10        |      | dB            |                                         |

| RX1A to RX2A Isolation                                  |        |        | 52         |      | dB            |                                         |

| RX2A to RX1A Isolation                                  |        |        | 52         |      | dB            |                                         |

| TRANSMITTERS—GENERAL                                    |        |        |            |      |               |                                         |

| Center Frequency                                        |        | 46.875 |            | 6000 | MHz           |                                         |

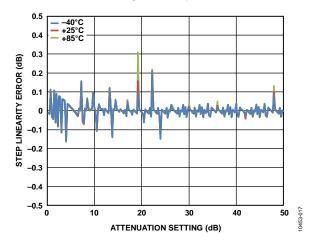

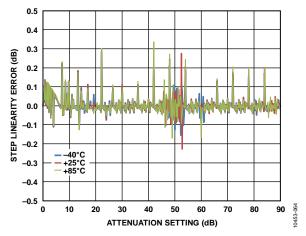

| Power Control Range                                     |        |        | 90         |      | dB            |                                         |

| Power Control Resolution                                |        |        | 0.25       |      | dB            |                                         |

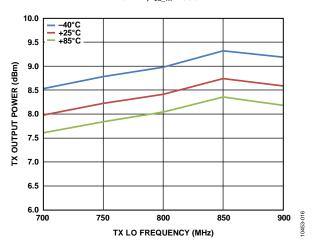

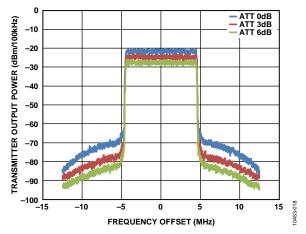

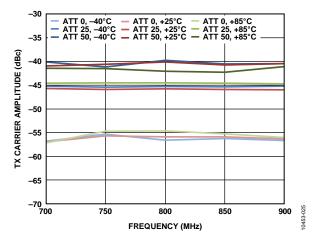

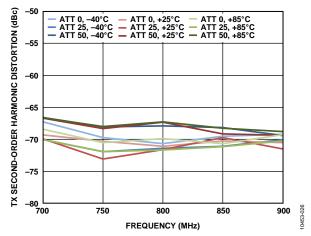

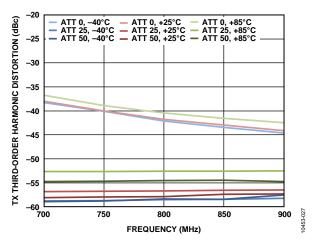

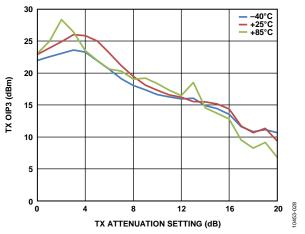

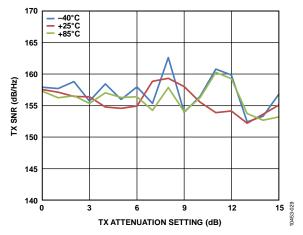

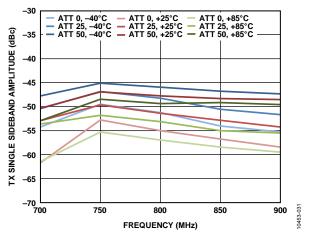

| TRANSMITTERS, 800 MHz                                   |        |        |            |      |               |                                         |

| Output S <sub>22</sub>                                  |        |        | -10        |      | dB            |                                         |

| Maximum Output Power                                    |        |        | 8          |      | dBm           | 1 MHz tone into 50 Ω load               |

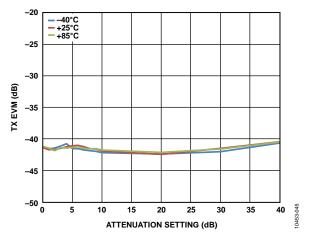

| Modulation Accuracy (EVM)                               |        |        | -40        |      | dB            | 19.2 MHz reference cloc                 |

| Third-Order Output                                      | OIP3   |        | 23         |      | dBm           | 13.2 WITE TETETETICE CIOC               |

| Intermodulation Intercept Point                         | Oli 3  |        | 25         |      | dbiii         |                                         |

| Carrier Leakage                                         |        |        | -50        |      | dBc           | 0 dB attenuation                        |

| carrier seamage                                         |        |        | -32        |      | dBc           | 40 dB attenuation                       |

| Noise Floor                                             |        |        | -157       |      | dBm/Hz        | 90 MHz offset                           |

| Isolation                                               |        |        | 137        |      | dbiii, i iz   | JO WILL OUTSEL                          |

| TX1 to TX2                                              |        |        | 50         |      | dB            |                                         |

| TX2 to TX1                                              |        |        | 50         |      | dB            |                                         |

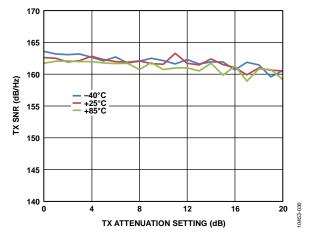

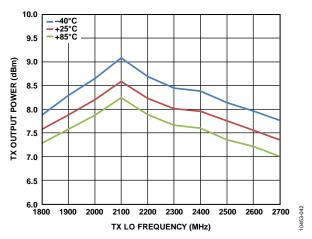

| TRANSMITTERS, 2.4 GHz                                   |        |        |            |      | u u           |                                         |

| Output S <sub>22</sub>                                  |        |        | -10        |      | dB            |                                         |

| Maximum Output Power                                    |        |        | 7.5        |      | dBm           | 1 MHz tone into 50 Ω load               |

| Modulation Accuracy (EVM)                               |        |        | -40        |      | dB            | 40 MHz reference clock                  |

| Third-Order Output Intermod-<br>ulation Intercept Point | OIP3   |        | 19         |      | dBm           | 40 MHZ Telefelice clock                 |

| Carrier Leakage                                         |        |        | -50        |      | dBc           | 0 dB attenuation                        |

| came: zeamage                                           |        |        | -32        |      | dBc           | 40 dB attenuation                       |

| Noise Floor                                             |        |        | -156       |      | dBm/Hz        | 90 MHz offset                           |

| Isolation                                               |        |        | .50        |      | 33,           | 70 mm 12 0m300                          |

| TX1 to TX2                                              |        |        | 50         |      | dB            |                                         |

| TX2 to TX1                                              |        |        | 50         |      | dB            |                                         |

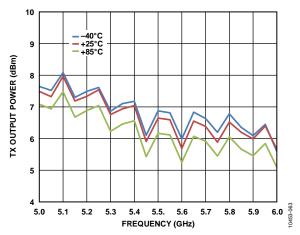

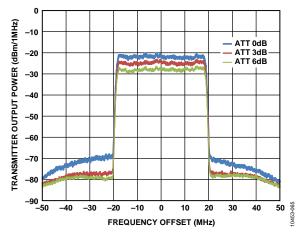

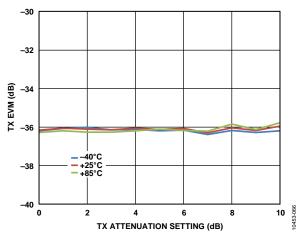

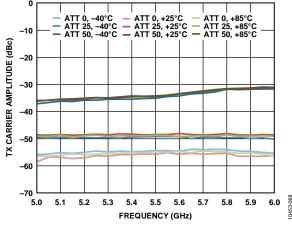

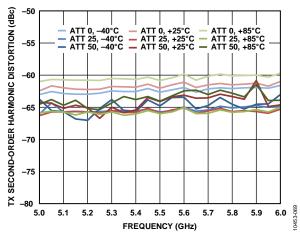

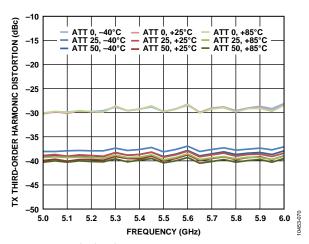

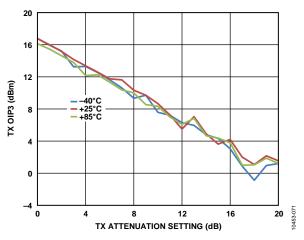

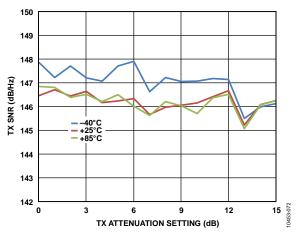

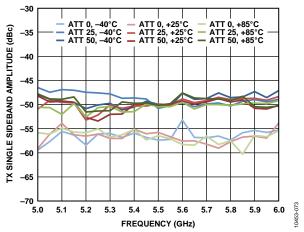

| TRANSMITTERS, 5.5 GHz                                   |        |        |            |      |               |                                         |

| Output S <sub>22</sub>                                  |        |        | -10        |      | dB            |                                         |

| Maximum Output Power                                    |        |        | 6.5        |      | dBm           | 7 MHz tone into 50 Ω load               |

| Modulation Accuracy (EVM)                               |        |        | -36        |      | dB            | 40 MHz reference clock                  |

| Modulation Accuracy (LVM)                               |        |        | -30        |      | ub            | (doubled internally for RF synthesizer) |

| Third-Order Output<br>Intermodulation Intercept Point   | OIP3   |        | 17         |      | dBm           |                                         |

| Carrier Leakage                                         |        |        | −50<br>−30 |      | dBc<br>dBc    | 0 dB attenuation<br>40 dB attenuation   |

| Noise Floor                                             |        |        | -151.5     |      | dBm/Hz        | 90 MHz offset                           |

| Isolation                                               |        |        |            |      |               |                                         |

| TX1 to TX2                                              |        |        | 50         |      | dB            |                                         |

| TX2 to TX1                                              |        |        | 50         |      | dB            |                                         |

| Parameter <sup>1</sup>                   | Symbol | Min                 | Тур               | Max                     | Unit  | Test Conditions/<br>Comments                                                                     |

|------------------------------------------|--------|---------------------|-------------------|-------------------------|-------|--------------------------------------------------------------------------------------------------|

| TX MONITOR INPUTS (TX_MON1,              |        |                     |                   |                         |       |                                                                                                  |

| TX_MON2)                                 |        |                     | _                 |                         |       |                                                                                                  |

| Maximum Input Level                      |        |                     | 4                 |                         | dBm   |                                                                                                  |

| Dynamic Range                            |        |                     | 66                |                         | dB    |                                                                                                  |

| Accuracy                                 |        |                     | 1                 |                         | dB    |                                                                                                  |

| LO SYNTHESIZER                           |        |                     |                   |                         |       |                                                                                                  |

| LO Frequency Step                        |        |                     | 2.4               |                         | Hz    | 2.4 GHz, 40 MHz<br>reference clock                                                               |

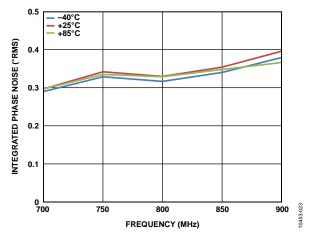

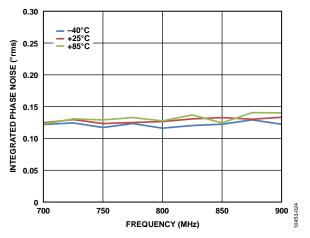

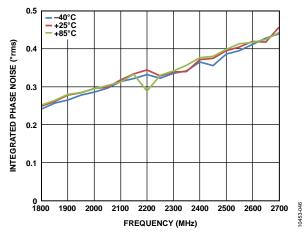

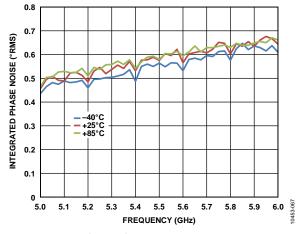

| Integrated Phase Noise                   |        |                     |                   |                         |       |                                                                                                  |

| 800 MHz                                  |        |                     | 0.13              |                         | °rms  | 100 Hz to 100 MHz,<br>30.72 MHz reference clock<br>(doubled internally for RF<br>synthesizer)    |

| 2.4 GHz                                  |        |                     | 0.37              |                         | ° rms | 100 Hz to 100 MHz,<br>40 MHz reference clock                                                     |

| 5.5 GHz                                  |        |                     | 0.59              |                         | ° rms | 100 Hz to 100 MHz,                                                                               |

|                                          |        |                     |                   |                         |       | 40 MHz reference clock<br>(doubled internally for RF<br>synthesizer)                             |

| REFERENCE CLOCK (REF_CLK)                |        |                     |                   |                         |       | REF_CLK is either the input<br>to the XTALP/XTALN pins<br>or a line directly to the<br>XTALN pin |

| Input                                    |        |                     |                   |                         |       |                                                                                                  |

| Frequency Range                          |        | 19                  |                   | 50                      | MHz   | Crystal input                                                                                    |

|                                          |        | 10                  |                   | 80                      | MHz   | External oscillator                                                                              |

| Signal Level                             |        |                     | 1.3               |                         | V p-p | AC-coupled external oscillator                                                                   |

| AUXILIARY CONVERTERS                     |        |                     |                   |                         |       |                                                                                                  |

| ADC                                      |        |                     |                   |                         |       |                                                                                                  |

| Resolution                               |        |                     | 12                |                         | Bits  |                                                                                                  |

| Input Voltage                            |        |                     |                   |                         |       |                                                                                                  |

| Minimum                                  |        |                     | 0.05              |                         | V     |                                                                                                  |

| Maximum                                  |        |                     | VDDA1P3_BB - 0.05 |                         | ٧     |                                                                                                  |

| DAC                                      |        |                     |                   |                         |       |                                                                                                  |

| Resolution                               |        |                     | 10                |                         | Bits  |                                                                                                  |

| Output Voltage                           |        |                     |                   |                         |       |                                                                                                  |

| Minimum                                  |        |                     | 0.5               |                         | V     |                                                                                                  |

| Maximum                                  |        |                     | VDD_GPO - 0.3     |                         | V     |                                                                                                  |

| Output Current                           |        |                     | 10                |                         | mA    |                                                                                                  |

| DIGITAL SPECIFICATIONS (CMOS)            |        |                     |                   |                         |       |                                                                                                  |

| Logic Inputs                             |        |                     |                   |                         |       |                                                                                                  |

| Input Voltage                            |        |                     |                   |                         |       |                                                                                                  |

| High                                     |        | VDD_INTERFACE × 0.8 |                   | VDD_INTERFACE           | V     |                                                                                                  |

| Low                                      |        | 0                   |                   | VDD_INTERFACE × 0.2     | V     |                                                                                                  |

| Input Current                            |        |                     |                   | VDD_IIVIEIII /ICE × 0.2 | *     |                                                                                                  |

| High                                     |        | -10                 |                   | +10                     | μΑ    |                                                                                                  |

| Low                                      |        | _10<br>_10          |                   | +10                     | _     |                                                                                                  |

| Logic Outputs                            |        | -10                 |                   | +10                     | μΑ    |                                                                                                  |

| Output Voltage                           |        |                     |                   |                         |       |                                                                                                  |

|                                          |        | VDD_INTERFACE × 0.8 |                   |                         | V     |                                                                                                  |

| High<br>Low                              |        | VDD_INTERFACE X 0.6 |                   | VDD INTEREACE VAN       | V     |                                                                                                  |

| DIGITAL SPECIFICATIONS (LVDS)            |        |                     |                   | VDD_INTERFACE × 0.2     | V     |                                                                                                  |

| Logic Inputs                             |        |                     |                   |                         |       |                                                                                                  |

| Input Voltage Range                      |        | 825                 |                   | 1575                    | mV    | Each differential input in the pair                                                              |

| Input Differential Voltage<br>Threshold  |        | -100                |                   | +100                    | mV    | are pui                                                                                          |

| Receiver Differential Input<br>Impedance |        |                     | 100               |                         | Ω     |                                                                                                  |

| Parameter <sup>1</sup>                               | Symbol                 | Min                      | Тур  | Max                   | Unit | Test Conditions/<br>Comments          |

|------------------------------------------------------|------------------------|--------------------------|------|-----------------------|------|---------------------------------------|

| Logic Outputs                                        |                        |                          |      |                       |      |                                       |

| Output Voltage                                       |                        |                          |      |                       |      |                                       |

| High                                                 |                        |                          |      | 1375                  | mV   |                                       |

| Low                                                  |                        | 1025                     |      |                       | mV   |                                       |

| Output Differential Voltage                          |                        | 150                      |      |                       | mV   | Programmable in 75 mV steps           |

| Output Offset Voltage                                |                        |                          | 1200 |                       | mV   |                                       |

| GENERAL-PURPOSE OUTPUTS                              |                        |                          |      |                       |      |                                       |

| Output Voltage                                       |                        |                          |      |                       |      |                                       |

| High                                                 |                        | $VDD_GPO \times 0.8$     |      |                       | V    |                                       |

| Low                                                  |                        |                          |      | $VDD\_GPO \times 0.2$ | V    |                                       |

| Output Current                                       |                        |                          | 10   |                       | mA   |                                       |

| SPI TIMING                                           |                        |                          |      |                       |      | VDD_INTERFACE = 1.8 V                 |

| SPI_CLK                                              |                        |                          |      |                       |      |                                       |

| Period                                               | <b>t</b> <sub>CP</sub> | 20                       |      |                       | ns   |                                       |

| Pulse Width                                          | t <sub>MP</sub>        | 9                        |      |                       | ns   |                                       |

| SPI_ENB Setup to First SPI_CLK<br>Rising Edge        | t <sub>SC</sub>        | 1                        |      |                       | ns   |                                       |

| Last SPI_CLK Falling Edge to<br>SPI_ENB Hold         | t <sub>HC</sub>        | 0                        |      |                       | ns   |                                       |

| SPI_DI                                               |                        |                          |      |                       |      |                                       |

| Data Input Setup to SPI_CLK                          | ts                     | 2                        |      |                       | ns   |                                       |

| Data Input Hold to SPI_CLK                           | t <sub>H</sub>         | 1                        |      |                       | ns   |                                       |

| SPI_CLK Rising Edge to Output<br>Data Delay          |                        |                          |      |                       |      |                                       |

| 4-Wire Mode                                          | tco                    | 3                        |      | 8                     | ns   |                                       |

| 3-Wire Mode                                          | tco                    | 3                        |      | 8                     | ns   |                                       |

| Bus Turnaround Time, Read                            | t <sub>HZM</sub>       | t <sub>H</sub>           |      | tco (max)             | ns   | After BBP drives the last address bit |

| Bus Turnaround Time, Read                            | t <sub>HZS</sub>       | 0                        |      | t <sub>CO (max)</sub> | ns   | After AD9361 drives the last data bit |

| DIGITAL DATA TIMING (CMOS),<br>VDD_INTERFACE = 1.8 V |                        |                          |      |                       |      |                                       |

| DATA_CLK Clock Period                                | <b>t</b> <sub>CP</sub> | 16.276                   |      |                       | ns   | 61.44 MHz                             |

| DATA_CLK and FB_CLK Pulse<br>Width                   | t <sub>MP</sub>        | 45% of t <sub>CP</sub>   |      | 55% of $t_{CP}$       | ns   |                                       |

| TX Data                                              |                        |                          |      |                       |      | TX_FRAME, P0_D, and P1_D              |

| Setup to FB_CLK                                      | t <sub>STX</sub>       | 1                        |      |                       | ns   |                                       |

| Hold to FB_CLK                                       | t <sub>HTX</sub>       | 0                        |      |                       | ns   |                                       |

| DATA_CLK to Data Bus Output<br>Delay                 | t <sub>DDRX</sub>      | 0                        |      | 1.5                   | ns   |                                       |

| DATA_CLK to RX_FRAME Delay                           | t <sub>DDDV</sub>      | 0                        |      | 1.0                   | ns   |                                       |

| Pulse Width                                          |                        | _                        |      |                       |      |                                       |

| ENABLE                                               | tenpw                  | t <sub>CP</sub>          |      |                       | ns   | EDD in don ENCA4                      |

| TXNRX                                                | t <sub>TXNRXPW</sub>   | t <sub>CP</sub>          |      |                       | ns   | FDD independent ENSM mode             |

| TXNRX Setup to ENABLE                                | t <sub>TXNRXSU</sub>   | 0                        |      |                       | ns   | TDD ENSM mode                         |

| Bus Turnaround Time                                  |                        |                          |      |                       |      |                                       |

| Before RX                                            | t <sub>RPRE</sub>      | $2 \times t_{\text{CP}}$ |      |                       | ns   | TDD mode                              |

| After RX                                             | t <sub>RPST</sub>      | $2 \times t_{\text{CP}}$ |      |                       | ns   | TDD mode                              |

| Capacitive Load                                      |                        |                          | 3    |                       | pF   |                                       |

| Capacitive Input                                     | 1                      | 1                        | 3    |                       | pF   |                                       |

| Parameter <sup>1</sup>                                                | Symbol                 | Min                    | Тур      | Max                    | Unit      | Test Conditions/<br>Comments                   |

|-----------------------------------------------------------------------|------------------------|------------------------|----------|------------------------|-----------|------------------------------------------------|

| DIGITAL DATA TIMING (CMOS),<br>VDD_INTERFACE = 2.5 V                  |                        |                        |          |                        |           |                                                |

| DATA_CLK Clock Period                                                 | t <sub>CP</sub>        | 16.276                 |          |                        | ns        | 61.44 MHz                                      |

| DATA_CLK and FB_CLK Pulse Width                                       | t <sub>MP</sub>        | 45% of t <sub>CP</sub> |          | 55% of t <sub>CP</sub> | ns        |                                                |

| TX Data                                                               |                        |                        |          |                        |           | TX_FRAME, P0_D, and P1_D                       |

| Setup to FB_CLK                                                       | t <sub>STX</sub>       | 1                      |          |                        | ns        | 1125                                           |

| Hold to FB_CLK                                                        | t <sub>HTX</sub>       | 0                      |          |                        | ns        |                                                |

| DATA_CLK to Data Bus Output<br>Delay                                  | t <sub>DDRX</sub>      | 0                      |          | 1.2                    | ns        |                                                |

| DATA_CLK to RX_FRAME Delay Pulse Width                                | t <sub>DDDV</sub>      | 0                      |          | 1.0                    | ns        |                                                |

| ENABLE                                                                | t <sub>ENPW</sub>      | t <sub>CP</sub>        |          |                        | ns        |                                                |

| TXNRX                                                                 | ttxnrxpw               | t <sub>CP</sub>        |          |                        | ns        | FDD independent ENSM mode                      |

| TXNRX Setup to ENABLE Bus Turnaround Time                             | t <sub>TXNRXSU</sub>   | 0                      |          |                        | ns        | TDD ENSM mode                                  |

| Before RX                                                             | t <sub>RPRE</sub>      | 2×t <sub>CP</sub>      |          |                        | ns        | TDD mode                                       |

| After RX                                                              | t <sub>RPST</sub>      | 2×tcp                  |          |                        | ns        | TDD mode                                       |

| Capacitive Load                                                       | -/11.51                |                        | 3        |                        | pF        |                                                |

| Capacitive Input                                                      |                        |                        | 3        |                        | pF        |                                                |

| DIGITAL DATA TIMING (LVDS)                                            |                        |                        | -        |                        | <u> </u>  |                                                |

| DATA_CLK Clock Period                                                 | <b>t</b> <sub>CP</sub> | 4.069                  |          |                        | ns        | 245.76 MHz                                     |

| DATA_CLK and FB_CLK Pulse Width                                       | t <sub>MP</sub>        | 45% of t <sub>CP</sub> |          | 55% of t <sub>CP</sub> | ns        |                                                |

| TX Data                                                               |                        |                        |          |                        |           | TX_FRAME and TX_D                              |

| Setup to FB_CLK                                                       | t <sub>STX</sub>       | 1                      |          |                        | ns        |                                                |

| Hold to FB_CLK                                                        | t <sub>HTX</sub>       | 0                      |          |                        | ns        |                                                |

| DATA_CLK to Data Bus Output<br>Delay                                  | t <sub>DDRX</sub>      | 0.25                   |          | 1.25                   | ns        |                                                |

| DATA_CLK to RX_FRAME Delay Pulse Width                                | t <sub>DDDV</sub>      | 0.25                   |          | 1.25                   | ns        |                                                |

| ENABLE                                                                | t <sub>ENPW</sub>      | t <sub>CP</sub>        |          |                        | ns        |                                                |

| TXNRX                                                                 | t <sub>TXNRXPW</sub>   | t <sub>CP</sub>        |          |                        | ns        | FDD independent ENSM                           |

| 170.400                                                               | CIANNAFW               | C                      |          |                        | 1.5       | mode                                           |

| TXNRX Setup to ENABLE Bus Turnaround Time                             | t <sub>TXNRXSU</sub>   | 0                      |          |                        | ns        | TDD ENSM mode                                  |

| Before RX                                                             | t                      | 2 × t <sub>CP</sub>    |          |                        | ns        |                                                |

| After RX                                                              | t <sub>RPRE</sub>      | 2 × t <sub>CP</sub>    |          |                        | ns        |                                                |

|                                                                       | T <sub>RPST</sub>      | Z X LCP                | 3        |                        | IIS<br>DE |                                                |

| Capacitive Load  Capacitive Input                                     |                        |                        | 3        |                        | pF<br>pF  |                                                |

| SUPPLY CHARACTERISTICS                                                | 1                      |                        | <u> </u> |                        | рі        |                                                |

|                                                                       |                        | 1.267                  | 1.3      | 1.33                   | V         |                                                |

| 1.3 V Main Supply Voltage<br>VDD_INTERFACE Supply<br>Nominal Settings |                        | 1.207                  | 1.5      | 1.33                   | V         |                                                |

| CMOS                                                                  |                        | 1.14                   |          | 2.625                  | V         |                                                |

| LVDS                                                                  |                        | 1.71                   |          | 2.625                  | ľ         |                                                |

| VDD_INTERFACE Tolerance                                               |                        | _5                     |          | +5                     | %         | Tolerance is applicable to any voltage setting |

| VDD_GPO Supply Nominal<br>Setting                                     |                        | 1.3                    |          | 3.3                    | V         | When unused, must be set to 1.3 V              |

| VDD_GPO Tolerance                                                     |                        | -5                     |          | +5                     | %         | Tolerance is applicable to any voltage setting |

| Current Consumption                                                   |                        |                        |          |                        |           |                                                |

| VDDx, Sleep Mode                                                      | 1                      |                        | 180      |                        | μΑ        | Sum of all input currents                      |

| VDD_GPO                                                               |                        |                        | 50       |                        | μΑ        | No load                                        |

<sup>&</sup>lt;sup>1</sup> When referencing a single function of a multifunction pin in the parameters, only the portion of the pin name that is relevant to the specification is listed. For full pin names of multifunction pins, refer to the Pin Configuration and Function Descriptions section.

## CURRENT CONSUMPTION—VDD\_INTERFACE

Table 2. VDD\_INTERFACE = 1.2 V

| Parameter     | Min Typ Max | Unit | Test Conditions/Comments       |

|---------------|-------------|------|--------------------------------|

| SLEEP MODE    | 45          | μΑ   | Power applied, device disabled |

| 1RX, 1TX, DDR |             |      |                                |

| LTE10         |             |      |                                |

| Single Port   | 2.9         | mA   | 30.72 MHz data clock, CMOS     |

| Dual Port     | 2.7         | mA   | 15.36 MHz data clock, CMOS     |

| LTE20         |             |      |                                |

| Dual Port     | 5.2         | mA   | 30.72 MHz data clock, CMOS     |

| 2RX, 2TX, DDR |             |      |                                |

| LTE3          |             |      |                                |

| Dual Port     | 1.3         | mA   | 7.68 MHz data clock, CMOS      |

| LTE10         |             |      |                                |

| Single Port   | 4.6         | mA   | 61.44 MHz data clock, CMOS     |

| Dual Port     | 5.0         | mA   | 30.72 MHz data clock, CMOS     |

| LTE20         |             |      |                                |

| Dual Port     | 8.2         | mA   | 61.44 MHz data clock, CMOS     |

| GSM           |             |      |                                |

| Dual Port     | 0.2         | mA   | 1.08 MHz data clock, CMOS      |

| WiMAX 8.75    |             |      |                                |

| Dual Port     | 3.3         | mA   | 20 MHz data clock, CMOS        |

| WiMAX 10      |             |      |                                |

| Single Port   |             |      |                                |

| TDD RX        | 0.5         | mA   | 22.4 MHz data clock, CMOS      |

| TDD TX        | 3.6         | mA   | 22.4 MHz data clock, CMOS      |

| FDD           | 3.8         | mA   | 44.8 MHz data clock, CMOS      |

| WiMAX 20      |             |      |                                |

| Dual Port     |             |      |                                |

| FDD           | 6.7         | mA   | 44.8 MHz data clock, CMOS      |

Table 3. VDD\_INTERFACE = 1.8 V

| Parameter     | Min Typ | Max U | Init | Test Conditions/Comments       |

|---------------|---------|-------|------|--------------------------------|

| SLEEP MODE    | 84      | μ     | Α    | Power applied, device disabled |

| 1RX, 1TX, DDR |         |       |      |                                |

| LTE10         |         |       |      |                                |

| Single Port   | 4.5     | m     | ١A   | 30.72 MHz data clock, CMOS     |

| Dual Port     | 4.1     | m     | nΑ   | 15.36 MHz data clock, CMOS     |

| LTE20         |         |       |      |                                |

| Dual Port     | 8.0     | m     | nΑ   | 30.72 MHz data clock, CMOS     |

| 2RX, 2TX, DDR |         |       |      |                                |

| LTE3          |         |       |      |                                |

| Dual Port     | 2.0     | m     | ١A   | 7.68 MHz data clock, CMOS      |

| LTE10         |         |       |      |                                |

| Single Port   | 8.0     | m     | ١A   | 61.44 MHz data clock, CMOS     |

| Dual Port     | 7.5     | m     | ıΑ   | 30.72 MHz data clock, CMOS     |

| LTE20         |         |       |      |                                |

| Dual Port     | 14.0    | m     | ١A   | 61.44 MHz data clock, CMOS     |

| GSM           |         |       |      |                                |

| Dual Port     | 0.3     | m     | nΑ   | 1.08 MHz data clock, CMOS      |

| WiMAX 8.75    |         |       |      |                                |

| Dual Port     | 5.0     | m     | nΑ   | 20 MHz data clock, CMOS        |

| Parameter                  | Min | Тур  | Max | Unit | Test Conditions/Comments  |

|----------------------------|-----|------|-----|------|---------------------------|

| WiMAX 10                   |     |      |     |      |                           |

| Single Port                |     |      |     |      |                           |

| TDD RX                     |     | 0.7  |     | mA   | 22.4 MHz data clock, CMOS |

| TDD TX                     |     | 5.6  |     | mA   | 22.4 MHz data clock, CMOS |

| FDD                        |     | 6.0  |     | mA   | 44.8 MHz data clock, CMOS |

| WiMAX 20                   |     |      |     |      |                           |

| Dual Port                  |     |      |     |      |                           |

| FDD                        |     | 10.7 |     | mA   | 44.8 MHz data clock, CMOS |

| P-P56                      |     |      |     |      |                           |

| 75 mV Differential Output  |     | 14.0 |     | mA   | 240 MHz data clock, LVDS  |

| 300 mV Differential Output |     | 35.0 |     | mA   | 240 MHz data clock, LVDS  |

| 450 mV Differential Output |     | 47.0 |     | mA   | 240 MHz data clock, LVDS  |

#### Table 4. VDD\_INTERFACE = 2.5 V

| Parameter                  | Min | Тур  | Max | Unit | <b>Test Conditions/Comments</b> |

|----------------------------|-----|------|-----|------|---------------------------------|

| SLEEP MODE                 |     | 150  |     | μΑ   | Power applied, device disabled  |

| 1RX, 1TX, DDR              |     |      |     |      |                                 |

| LTE10                      |     |      |     |      |                                 |

| Single Port                |     | 6.5  |     | mA   | 30.72 MHz data clock, CMOS      |

| Dual Port                  |     | 6.0  |     | mA   | 15.36 MHz data clock, CMOS      |

| LTE20                      |     |      |     |      |                                 |

| Dual Port                  |     | 11.5 |     | mA   | 30.72 MHz data clock, CMOS      |

| 2RX, 2TX, DDR              |     |      |     |      |                                 |

| LTE3                       |     |      |     |      |                                 |

| Dual Port                  |     | 3.0  |     | mA   | 7.68 MHz data clock, CMOS       |

| LTE10                      |     |      |     |      |                                 |

| Single Port                |     | 11.5 |     | mA   | 61.44 MHz data clock, CMOS      |

| Dual Port                  |     | 10.0 |     | mA   | 30.72 MHz data clock, CMOS      |

| LTE20                      |     |      |     |      |                                 |

| Dual Port                  |     | 20.0 |     | mA   | 61.44 MHz data clock, CMOS      |

| GSM                        |     |      |     |      |                                 |

| Dual Port                  |     | 0.5  |     | mA   | 1.08 MHz data clock, CMOS       |

| WiMAX 8.75                 |     |      |     |      |                                 |

| Dual Port                  |     | 7.3  |     | mA   | 20 MHz data clock, CMOS         |

| WiMAX 10                   |     |      |     |      |                                 |

| Single Port                |     |      |     |      |                                 |

| TDD RX                     |     | 1.3  |     | mA   | 22.4 MHz data clock, CMOS       |

| TDD TX                     |     | 8.0  |     | mA   | 22.4 MHz data clock, CMOS       |

| FDD                        |     | 8.7  |     | mA   | 44.8 MHz data clock, CMOS       |

| WiMAX 20                   |     |      |     |      |                                 |

| Dual Port                  |     |      |     |      |                                 |

| FDD                        |     | 15.3 |     | mA   | 44.8 MHz data clock, CMOS       |

| P-P56                      |     |      |     |      |                                 |

| 75 mV Differential Output  |     | 26.0 |     | mA   | 240 MHz data clock, LVDS        |

| 300 mV Differential Output |     | 45.0 |     | mA   | 240 MHz data clock, LVDS        |

| 450 mV Differential Output |     | 58.0 |     | mA   | 240 MHz data clock, LVDS        |

## CURRENT CONSUMPTION—VDDD1P3\_DIG AND VDDAx (COMBINATION OF ALL 1.3 V SUPPLIES)

Table 5. 800 MHz, TDD Mode

| Parameter        | Min Typ | Max Unit | Test Conditions/Comments |

|------------------|---------|----------|--------------------------|

| 1RX              |         |          |                          |

| 5 MHz Bandwidth  | 180     | mA       | Continuous RX            |

| 10 MHz Bandwidth | 210     | mA       | Continuous RX            |

| 20 MHz Bandwidth | 260     | mA       | Continuous RX            |

| 2RX              |         |          |                          |

| 5 MHz Bandwidth  | 265     | mA       | Continuous RX            |

| 10 MHz Bandwidth | 315     | mA       | Continuous RX            |

| 20 MHz Bandwidth | 405     | mA       | Continuous RX            |

| 1TX              |         |          |                          |

| 5 MHz Bandwidth  |         |          |                          |

| 7 dBm            | 340     | mA       | Continuous TX            |

| –27 dBm          | 190     | mA       | Continuous TX            |

| 10 MHz Bandwidth |         |          |                          |

| 7 dBm            | 360     | mA       | Continuous TX            |

| –27 dBm          | 220     | mA       | Continuous TX            |

| 20 MHz Bandwidth |         |          |                          |

| 7 dBm            | 400     | mA       | Continuous TX            |

| –27 dBm          | 250     | mA       | Continuous TX            |

| 2TX              |         |          |                          |

| 5 MHz Bandwidth  |         |          |                          |

| 7 dBm            | 550     | mA       | Continuous TX            |

| –27 dBm          | 260     | mA       | Continuous TX            |

| 10 MHz Bandwidth |         |          |                          |

| 7 dBm            | 600     | mA       | Continuous TX            |

| −27 dBm          | 310     | mA       | Continuous TX            |

| 20 MHz Bandwidth |         |          |                          |

| 7 dBm            | 660     | mA       | Continuous TX            |

| –27 dBm          | 370     | mA       | Continuous TX            |

Table 6. TDD Mode, 2.4 GHz

| Parameter        | Min Typ | Max | Unit | Test Conditions/Comments |  |

|------------------|---------|-----|------|--------------------------|--|

| 1RX              |         |     |      |                          |  |

| 5 MHz Bandwidth  | 175     |     | mA   | Continuous RX            |  |

| 10 MHz Bandwidth | 200     |     | mA   | Continuous RX            |  |

| 20 MHz Bandwidth | 240     |     | mA   | Continuous RX            |  |

| 2RX              |         |     |      |                          |  |

| 5 MHz Bandwidth  | 260     |     | mA   | Continuous RX            |  |

| 10 MHz Bandwidth | 305     |     | mA   | Continuous RX            |  |

| 20 MHz Bandwidth | 390     |     | mA   | Continuous RX            |  |

| 1TX              |         |     |      |                          |  |

| 5 MHz Bandwidth  |         |     |      |                          |  |

| 7 dBm            | 350     |     | mA   | Continuous TX            |  |

| –27 dBm          | 160     |     | mA   | Continuous TX            |  |

| 10 MHz Bandwidth |         |     |      |                          |  |

| 7 dBm            | 380     |     | mA   | Continuous TX            |  |

| −27 dBm          | 220     |     | mA   | Continuous TX            |  |

| 20 MHz Bandwidth |         |     |      |                          |  |

| 7 dBm            | 410     |     | mA   | Continuous TX            |  |

| –27 dBm          | 260     |     | mA   | Continuous TX            |  |

| 2TX              |         |     |      |                          |  |

| 5 MHz Bandwidth  |         |     |      |                          |  |

| 7 dBm            | 580     |     | mA   | Continuous TX            |  |

| −27 dBm          | 280     |     | mA   | Continuous TX            |  |

| 10 MHz Bandwidth |         |     |      |                          |  |

| 7 dBm            | 635     |     | mA   | Continuous TX            |  |

| –27 dBm          | 330     |     | mA   | Continuous TX            |  |

| 20 MHz Bandwidth |         |     |      |                          |  |

| 7 dBm            | 690     |     | mA   | Continuous TX            |  |

| –27 dBm          | 390     |     | mA   | Continuous TX            |  |

Table 7. TDD Mode, 5.5 GHz

| Parameter        | Min Typ | Max | Unit | Test Conditions/Comments |

|------------------|---------|-----|------|--------------------------|

| 1RX              |         |     |      |                          |

| 5 MHz Bandwidth  | 175     |     | mA   | Continuous RX            |

| 40 MHz Bandwidth | 275     |     | mA   | Continuous RX            |

| 2RX              |         |     |      |                          |

| 5 MHz Bandwidth  | 270     |     | mA   | Continuous RX            |

| 40 MHz Bandwidth | 445     |     | mA   | Continuous RX            |

| 1TX              |         |     |      |                          |

| 5 MHz Bandwidth  |         |     |      |                          |

| 7 dBm            | 400     |     | mA   | Continuous TX            |

| –27 dBm          | 240     |     | mA   | Continuous TX            |

| 40 MHz Bandwidth |         |     |      |                          |

| 7 dBm            | 490     |     | mA   | Continuous TX            |

| –27 dBm          | 385     |     | mA   | Continuous TX            |

| 2TX              |         |     |      |                          |

| 5 MHz Bandwidth  |         |     |      |                          |

| 7 dBm            | 650     |     | mA   | Continuous TX            |

| –27 dBm          | 335     |     | mA   | Continuous TX            |

| 40 MHz Bandwidth |         |     |      |                          |

| 7 dBm            | 820     |     | mA   | Continuous TX            |

| –27 dBm          | 500     |     | mA   | Continuous TX            |

Table 8. FDD Mode, 800 MHz

| Parameter        | Min Typ | Max | Unit | Test Conditions/Comments |

|------------------|---------|-----|------|--------------------------|

| 1RX, 1TX         |         |     |      |                          |

| 5 MHz Bandwidth  |         |     |      |                          |

| 7 dBm            | 490     |     | mA   |                          |

| −27 dBm          | 345     |     | mA   |                          |

| 10 MHz Bandwidth |         |     |      |                          |

| 7 dBm            | 540     |     | mA   |                          |

| –27 dBm          | 395     |     | mA   |                          |

| 20 MHz Bandwidth |         |     |      |                          |

| 7 dBm            | 615     |     | mA   |                          |

| –27 dBm          | 470     |     | mA   |                          |

| 2RX, 1TX         |         |     |      |                          |

| 5 MHz Bandwidth  |         |     |      |                          |

| 7 dBm            | 555     |     | mA   |                          |

| –27 dBm          | 410     |     | mA   |                          |

| 10 MHz Bandwidth |         |     |      |                          |

| 7 dBm            | 625     |     | mA   |                          |

| –27 dBm          | 480     |     | mA   |                          |

| 20 MHz Bandwidth |         |     |      |                          |

| 7 dBm            | 740     |     | mA   |                          |

| –27 dBm          | 600     |     | mA   |                          |

| 1RX, 2TX         |         |     |      |                          |

| 5 MHz Bandwidth  |         |     |      |                          |

| 7 dBm            | 685     |     | mA   |                          |

| –27 dBm          | 395     |     | mA   |                          |

| 10 MHz Bandwidth |         |     |      |                          |

| 7 dBm            | 755     |     | mA   |                          |

| –27 dBm          | 465     |     | mA   |                          |

| 20 MHz Bandwidth |         |     |      |                          |

| 7 dBm            | 850     |     | mA   |                          |

| –27 dBm          | 570     |     | mA   |                          |

| 2RX, 2TX         |         |     |      |                          |

| 5 MHz Bandwidth  |         |     |      |                          |

| 7 dBm            | 790     |     | mA   |                          |

| –27 dBm          | 495     |     | mA   |                          |

| 10 MHz Bandwidth |         |     |      |                          |

| 7 dBm            | 885     |     | mA   |                          |

| –27 dBm          | 590     |     | mA   |                          |

| 20 MHz Bandwidth |         |     |      |                          |

| 7 dBm            | 1020    |     | mA   |                          |

| –27 dBm          | 730     |     | mA   |                          |

Table 9. FDD Mode, 2.4 GHz

| Parameter        | Min Typ | Max Unit | Test Conditions/Comments |

|------------------|---------|----------|--------------------------|

| 1RX, 1TX         |         |          |                          |

| 5 MHz Bandwidth  |         |          |                          |

| 7 dBm            | 500     | mA       |                          |

| –27 dBm          | 350     | mA       |                          |

| 10 MHz Bandwidth |         |          |                          |

| 7 dBm            | 540     | mA       |                          |

| –27 dBm          | 390     | mA       |                          |

| 20 MHz Bandwidth |         |          |                          |

| 7 dBm            | 620     | mA       |                          |

| –27 dBm          | 475     | mA       |                          |

| 2RX, 1TX         |         |          |                          |

| 5 MHz Bandwidth  |         |          |                          |

| 7 dBm            | 590     | mA       |                          |

| –27 dBm          | 435     | mA       |                          |

| 10 MHz Bandwidth |         |          |                          |

| 7 dBm            | 660     |          |                          |

| –27 dBm          | 510     | mA       |                          |

| 20 MHz Bandwidth |         |          |                          |

| 7 dBm            | 770     | mA       |                          |

| –27 dBm          | 620     | mA       |                          |

| 1RX, 2TX         |         | mA       |                          |

| 5 MHz Bandwidth  |         |          |                          |

| 7 dBm            | 730     | mA       |                          |

| –27 dBm          | 425     | mA       |                          |

| 10 MHz Bandwidth |         |          |                          |

| 7 dBm            | 800     | mA       |                          |

| –27dBm           | 500     | mA       |                          |

| 20 MHz Bandwidth |         |          |                          |

| 7 dBm            | 900     | mA       |                          |

| –27 dBm          | 600     | mA       |                          |

| 2RX, 2TX         |         | mA       |                          |

| 5 MHz Bandwidth  |         |          |                          |

| 7 dBm            | 820     |          |                          |

| –27 dBm          | 515     | mA       |                          |

| 10 MHz Bandwidth |         |          |                          |

| 7 dBm            | 900     | mA       |                          |

| –27 dBm          | 595     | mA       |                          |

| 20 MHz Bandwidth |         |          |                          |

| 7 dBm            | 1050    | mA       |                          |

| –27 dBm          | 740     | mA       |                          |

### Table 10. FDD Mode, 5.5 GHz

| Parameter       | Min | Тур | Max | Unit | Test Conditions/Comments |

|-----------------|-----|-----|-----|------|--------------------------|

| 1RX, 1TX        |     |     |     |      |                          |

| 5 MHz Bandwidth |     |     |     |      |                          |

| 7 dBm           |     | 550 |     | mA   |                          |

| –27 dBm         |     | 385 |     | mA   |                          |

| 2RX, 1TX        |     |     |     |      |                          |

| 5 MHz Bandwidth |     |     |     |      |                          |

| 7 dBm           |     | 645 |     | mA   |                          |

| –27 dBm         |     | 480 |     | mA   |                          |

| 1RX, 2TX        |     |     |     |      |                          |

| 5 MHz Bandwidth |     |     |     |      |                          |

| 7 dBm           |     | 805 |     | mA   |                          |

| –27 dBm         |     | 480 |     | mA   |                          |

| 2RX, 2TX        |     |     |     |      |                          |

| 5 MHz Bandwidth |     |     |     |      |                          |

| 7 dBm           |     | 895 |     | mA   |                          |

| –27 dBm         |     | 575 |     | mA   |                          |

#### **ABSOLUTE MAXIMUM RATINGS**

Table 11.

| 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1              |                                 |

|------------------------------------------------------|---------------------------------|

| Parameter                                            | Rating                          |

| VDDx to VSSx                                         | -0.3 V to +1.4 V                |

| VDD_INTERFACE to VSSx                                | -0.3 V to +3.0 V                |

| VDD_GPO to VSSx                                      | −0.3 V to +3.9 V                |

| Logic Inputs and Outputs to<br>VSSx                  | -0.3 V to VDD_INTERFACE + 0.3 V |

| Input Current to Any Pin<br>Except Supplies          | ±10 mA                          |

| RF Inputs (Peak Power)                               | 2.5 dBm                         |

| TX Monitor Input Power (Peak Power)                  | 9 dBm                           |

| Package Power Dissipation                            | $(T_{JMAX} - T_A)/\theta_{JA}$  |

| Maximum Junction<br>Temperature (T <sub>JMAX</sub> ) | 110°C                           |

| Operating Temperature Range                          | –40°C to +85°C                  |

| Storage Temperature Range                            | −65°C to +150°C                 |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

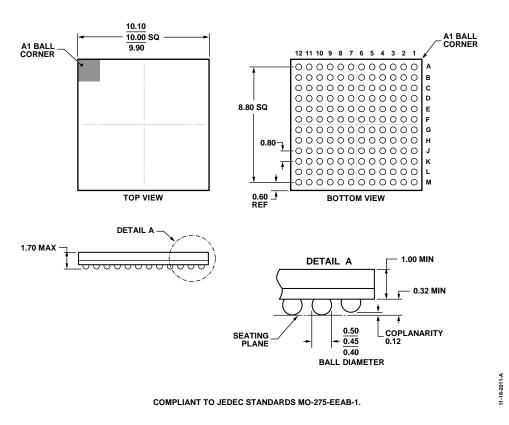

#### **REFLOW PROFILE**

The AD9361 reflow profile is in accordance with the JEDEC JESD20 criteria for Pb-free devices. The maximum reflow temperature is 260°C.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

Table 12. Thermal Resistance

| Package<br>Type | Airflow<br>Velocity<br>(m/sec) | <b>θ</b> <sub>JA</sub> <sup>1, 2</sup> | <b>θ</b> <sub>JC</sub> <sup>1,3</sup> | <b>θ</b> <sub>JB</sub> <sup>1, 4</sup> | Ψ <sub>л</sub> <sup>1,2</sup> | Unit |

|-----------------|--------------------------------|----------------------------------------|---------------------------------------|----------------------------------------|-------------------------------|------|

| 144-Ball        | 0                              | 32.3                                   | 9.6                                   | 20.2                                   | 0.27                          | °C/W |

| CSP_BGA         | 1.0                            | 29.6                                   |                                       |                                        | 0.43                          | °C/W |

|                 | 2.5                            | 27.8                                   |                                       |                                        | 0.57                          | °C/W |

<sup>&</sup>lt;sup>1</sup> Per JEDEC JESD51-7, plus JEDEC JESD51-5 2S2P test board.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

$<sup>^{\</sup>rm 2}$  Per JEDEC JESD51-2 (still air) or JEDEC JESD51-6 (moving air).

$<sup>^{\</sup>rm 3}$  Per MIL-STD 883, Method 1012.1.

<sup>&</sup>lt;sup>4</sup> Per JEDEC JESD51-8 (still air).

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

|   | 1                | 2                          | 3                            | 4               | 5         | 6         | 7                  | 8                  | 9                 | 10                         | 11                 | 12                |

|---|------------------|----------------------------|------------------------------|-----------------|-----------|-----------|--------------------|--------------------|-------------------|----------------------------|--------------------|-------------------|

| A | RX2A_N           | RX2A_P                     | NC                           | VSSA            | TX_MON2   | VSSA      | TX2A_N             | TX2A_P             | TX2B_N            | TX2B_P                     | VDDA1P1_<br>TX_VCO | TX_EXT_<br>LO_IN  |

| В | VSSA             | VSSA                       | AUXDAC1                      | GPO_3           | GPO_2     | GPO_1     | GPO_0              | VDD_GPO            | VDDA1P3_<br>TX_LO | VDDA1P3_<br>TX_VCO_<br>LDO | TX_VCO_<br>LDO_OUT | VSSA              |

| С | RX2C_P           | VSSA                       | AUXDAC2                      | TEST/<br>ENABLE | CTRL_IN0  | CTRL_IN1  | VSSA               | VSSA               | VSSA              | VSSA                       | VSSA               | VSSA              |

| D | RX2C_N           | VDDA1P3_<br>RX_RF          | VDDA1P3_<br>RX_TX            | CTRL_OUT0       | CTRL_IN3  | CTRL_IN2  | P0_D9/<br>TX_D4_P  | P0_D7/<br>TX_D3_P  | P0_D5/<br>TX_D2_P | P0_D3/<br>TX_D1_P          | P0_D1/<br>TX_D0_P  | VSSD              |

| E | RX2B_P           | VDDA1P3_<br>RX_LO          | VDDA1P3_<br>TX_LO_<br>BUFFER | CTRL_OUT1       | CTRL_OUT2 | CTRL_OUT3 | P0_D11/<br>TX_D5_P | P0_D8/<br>TX_D4_N  | P0_D6/<br>TX_D3_N | P0_D4/<br>TX_D2_N          | P0_D2/<br>TX_D1_N  | P0_D0/<br>TX_D0_N |

| F | RX2B_N           | VDDA1P3_<br>RX_VCO_<br>LDO | VSSA                         | CTRL_OUT6       | CTRL_OUT5 | CTRL_OUT4 | VSSD               | P0_D10/<br>TX_D5_N | VSSD              | FB_CLK_P                   | VSSD               | VDDD1P3_<br>DIG   |

| G | RX_EXT_<br>LO_IN | RX_VCO_<br>LDO_OUT         | VDDA1P1_<br>RX_VCO           | CTRL_OUT7       | EN_AGC    | ENABLE    | RX_<br>FRAME_N     | RX_<br>FRAME_P     | TX_<br>FRAME_P    | FB_CLK_N                   | DATA_<br>CLK_P     | VSSD              |

| Н | RX1B_P           | VSSA                       | VSSA                         | TXNRX           | SYNC_IN   | VSSA      | VSSD               | P1_D11/<br>RX_D5_P | TX_<br>FRAME_N    | VSSD                       | DATA_<br>CLK_N     | VDD_<br>INTERFACE |

| J | RX1B_N           | VSSA                       | VDDA1P3_<br>RX_SYNTH         | SPI_DI          | SPI_CLK   | CLK_OUT   | P1_D10/<br>RX_D5_N | P1_D9/<br>RX_D4_P  | P1_D7/<br>RX_D3_P | P1_D5/<br>RX_D2_P          | P1_D3/<br>RX_D1_P  | P1_D1/<br>RX_D0_P |

| к | RX1C_P           | VSSA                       | VDDA1P3_<br>TX_SYNTH         | VDDA1P3_<br>BB  | RESETB    | SPI_ENB   | P1_D8/<br>RX_D4_N  | P1_D6/<br>RX_D3_N  | P1_D4/<br>RX_D2_N | P1_D2/<br>RX_D1_N          | P1_D0/<br>RX_D0_N  | VSSD              |

| L | RX1C_N           | VSSA                       | VSSA                         | RBIAS           | AUXADC    | SPI_DO    | VSSA               | VSSA               | VSSA              | VSSA                       | VSSA               | VSSA              |

| М | RX1A_P           | RX1A_N                     | NC                           | VSSA            | TX_MON1   | VSSA      | TX1A_P             | TX1A_N             | TX1B_P            | TX1B_N                     | XTALP              | XTALN             |

| · | 7 ANIAL 00       |                            | O DOWED                      |                 |           |           |                    |                    |                   |                            |                    |                   |

□ ANALOG I/O □ DC POWER

□ DIGITAL I/O □ GROUND

□ NO CONNECT

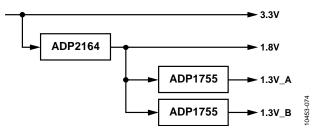

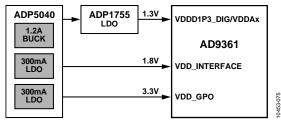

Figure 2. Pin Configuration, Top View