# **TABLE OF CONTENTS**

| Features1                                         |

|---------------------------------------------------|

| Applications                                      |

| Functional Block Diagram 1                        |

| General Description                               |

| Revision History                                  |

| Specifications                                    |

| I <sup>2</sup> C Timing Specifications            |

| Absolute Maximum Ratings6                         |

| ESD Caution6                                      |

| Pin Configuration and Function Descriptions       |

| Typical Performance Characteristics               |

| Theory of Operation                               |

| The Switch (Mux/Demux/Unicast/Bicast/Loopback) 16 |

| Receivers                                         |

| Loss of Signal (LOS)                              |

| Transmitters21                                    |

| AD8155 Power Consumption                                                  |

|---------------------------------------------------------------------------|

| I <sup>2</sup> C Control Interface                                        |

| Serial Interface General Functionality                                    |

| I <sup>2</sup> C Interface Data Transfers: Data Write                     |

| I <sup>2</sup> C Interface Data Transfers: Data Read                      |

| Applications Information                                                  |

| Output Compliance                                                         |

| Signal Levels and Common-Mode Shift for AC-Coupled and DC-Coupled Outputs |

| Supply Sequencing                                                         |

| Single Supply vs. Multiple Supply Operation                               |

| Initialization Sequence for Low Power and LOS_INT Operation               |

| Printed Circuit Board (PCB) Layout Guidelines 31                          |

| Register Map                                                              |

| Outline Dimensions                                                        |

| Ordering Guide35                                                          |

### **REVISION HISTORY**

7/09—Revision 0: Initial Version

# **SPECIFICATIONS**

$V_{CC} = V_{TTI} = V_{TTO} = 1.8 \text{ V}, DV_{CC} = 3.3 \text{ V}, V_{EE} = 0 \text{ V}, R_L = 50 \Omega$ , basic configuration 1, data rate = 6.5 Gbps, data pattern = PRBS7, accoupled inputs and outputs, differential input swing = 800 mV p-p,  $T_A = 25$ °C, unless otherwise noted.

Table 1.

| Parameter                                                     | Conditions                                                                                           | Min | Тур                   | Max            | Unit           |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----|-----------------------|----------------|----------------|

| DYNAMIC PERFORMANCE                                           |                                                                                                      |     |                       |                |                |

| Data Rate/Channel (NRZ)                                       |                                                                                                      | DC  |                       | 6.5            | Gbps           |

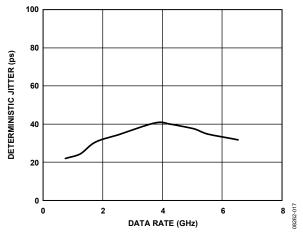

| Deterministic Jitter (No<br>Channel)                          | Data rate = 6.5 Gbps, EQ setting = 0                                                                 |     | 22                    |                | ps p-p         |

| Random Jitter (No Channel)                                    | RMS, data rate = 6.5 Gbps                                                                            |     | 1                     |                | ps             |

| Residual Deterministic Jitter                                 | Data rate 6.5 Gbps, 20 inch FR4                                                                      |     | 30                    |                | ps p-p         |

| with Receive Equalization                                     | Data rate 6.5 Gbps, 40 inch FR4                                                                      |     | 40                    |                | ps p-p         |

| Residual Deterministic Jitter                                 | Data rate 6.5 Gbps, 10 inch FR4                                                                      |     | 35                    |                | ps p-p         |

| with Transmit Preemphasis                                     | Data rate 6.5 Gbps, 30 inch FR4                                                                      |     | 42                    |                | ps p-p         |

| Propagation Delay                                             | 50% input to 50% output (maximum EQ)                                                                 |     | 700                   |                | ps             |

| Lane-to-Lane Skew                                             | Signal path and switch architecture is balanced and symmetric (maximum EQ)                           |     | 90                    |                | ps             |

| Switching Time                                                | 50% logic switching to 50% output data                                                               |     | 150                   |                | ns             |

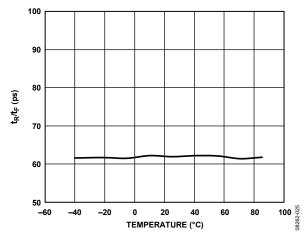

| Output Rise/Fall Time                                         | 20% to 80% (PE = lowest setting)                                                                     |     | 62                    |                | ps             |

| INPUT CHARACTERISTICS                                         |                                                                                                      |     |                       |                |                |

| Differential Input Voltage                                    | $V_{ICM}^2 = V_{CC} - 0.6 \text{ V}, V_{CC} = V_{MIN} \text{ to } V_{MAX}, T_A = T_{MIN} \text{ to}$ | 200 |                       | 2000           | mV p-p         |

| Swing                                                         | T <sub>MAX</sub> ,                                                                                   |     |                       |                | diff           |

|                                                               | LOS control register = 0x05                                                                          |     |                       |                |                |

| Input Voltage Range                                           | Single-ended absolute voltage level, V <sub>L</sub> minimum                                          |     | V <sub>FF</sub> + 0.6 |                | V              |

|                                                               | Single-ended absolute voltage level, V <sub>H</sub> maximum                                          |     | $V_{CC} + 0.3$        |                | V              |

| OUTPUT CHARACTERISTICS                                        |                                                                                                      |     | 100 1 115             |                |                |

| Output Voltage Swing                                          | Differential, PE = 0, default output level, @ dc                                                     | 590 | 725                   | 820            | mV p-p         |

| Output Voltage Range, Single-<br>Ended Absolute Voltage Level | TX_HEADROOM = 0, V <sub>L</sub> minimum                                                              |     | V <sub>cc</sub> – 1.1 |                | V              |

|                                                               | TX_HEADROOM = 0, V <sub>H</sub> maximum                                                              |     | $V_{CC} + 0.6$        |                | V              |

|                                                               | TX_HEADROOM = 1, V <sub>L</sub> minimum                                                              |     | $V_{CC}-1.3$          |                | V              |

|                                                               | TX_HEADROOM = 1, V <sub>H</sub> maximum                                                              |     | $V_{CC} + 0.6$        |                | V              |

| Output Current                                                | Port A/B/C, PE_A/B/C = minimum                                                                       |     | 16                    |                | mA             |

|                                                               | Port A/B/C, PE_A/B/C = 6 dB, $V_{OD}$ = 800 mV p-p                                                   |     | 32                    |                | mA             |

| TERMINATION CHARACTERISTICS                                   |                                                                                                      |     |                       |                |                |

| Resistance                                                    | Differential, $V_{CC} = V_{MIN}$ to $V_{MAX}$ , $T_A = T_{MIN}$ to $T_{MAX}$                         | 90  | 100                   | 110            | Ω              |

| LOS CHARACTERISTICS                                           |                                                                                                      |     |                       |                |                |

| DC Assert Level                                               |                                                                                                      |     | 50                    |                | mV p-p<br>diff |

| DC Deassert Level                                             |                                                                                                      |     | 300                   |                | mV p-p<br>diff |

| LOS to Output Squelch                                         | LOS control = 0, $V_{ID}$ = 0 to 50% OP/ON settling, $V_{CC}$ = 1.8 V                                |     | 21                    |                | ns             |

| LOS to Output Enable                                          | LOS control = 0, data present to first valid transition, $V_{CC} = 1.8 \text{ V}$                    |     | 67                    |                | ns             |

| POWER SUPPLY                                                  |                                                                                                      |     |                       |                |                |

| Operating Range                                               |                                                                                                      |     |                       |                |                |

| Vcc                                                           | $V_{EE} = 0 \text{ V, TX\_HEADROOM} = 0$                                                             | 1.6 | 1.8 to 3.3            | 3.6            | V              |

|                                                               | $V_{EE} = 0 \text{ V, TX\_HEADROOM} = 1$                                                             | 2.2 | 3.3                   | 3.6            | V              |

| DVcc                                                          | $DV_{CC} \ge V_{CC}, V_{EE} = 0 V$                                                                   | 1.6 | 1.8 to 3.3            | 3.6            | V              |

| V <sub>TTI</sub>                                              |                                                                                                      | 1.2 |                       | $V_{CC} + 0.3$ | V              |

| $V_{TTO}$                                                     |                                                                                                      | 1.2 |                       | $V_{CC} + 0.3$ | V              |

| Parameter                          | Conditions                                                         | Min                  | Тур                  | Max                  | Unit |

|------------------------------------|--------------------------------------------------------------------|----------------------|----------------------|----------------------|------|

| Supply Current                     |                                                                    |                      |                      |                      |      |

| Icc                                |                                                                    |                      |                      |                      |      |

| $V_{CC} = 1.8 V$                   | $LB_x = 0$ , $PE = 0$ dB on all ports, low power mode <sup>3</sup> |                      | 233                  | 270                  | mA   |

|                                    | $LB_x = 1$ , $PE = 6$ dB on all ports, low power mode <sup>3</sup> |                      | 406                  | 480                  | mA   |

|                                    | $LB_x = 0$ , $PE = 0$ dB on all ports, default                     |                      | 350                  | 410                  | mA   |

|                                    | LB_x = 1, PE = 6 dB on all ports, default                          |                      | 690                  | 800                  | mA   |

| $V_{CC} = 3.3 V$                   | $LB_x = 0$ , $PE = 0$ dB on all ports, low power mode <sup>3</sup> |                      | 254                  | 300                  | mA   |

|                                    | $LB_x = 1$ , $PE = 6$ dB on all ports, low power mode <sup>3</sup> |                      | 435                  | 500                  | mA   |

|                                    | $LB_x = 0$ , $PE = 0$ dB on all ports, default                     |                      | 380                  | 450                  | mA   |

|                                    | LB_x = 1, PE = 6 dB on all ports, default                          |                      | 735                  | 850                  | mA   |

| Iπο                                |                                                                    |                      |                      |                      |      |

| $V_{TTO} = 1.8 V$                  | $LB_x = 0$ , $PE = 0$ dB on all ports, low power mode <sup>3</sup> |                      | 66                   | 82                   | mA   |

|                                    | $LB_x = 1$ , $PE = 6$ dB on all ports, low power mode <sup>3</sup> |                      | 186                  | 226                  | mA   |

|                                    | $LB_x = 0$ , $PE = 0$ dB on all ports, default                     |                      | 66                   | 82                   | mA   |

|                                    | LB_x = 1, PE = 6 dB on all ports, default                          |                      | 183                  | 225                  | mA   |

| $V_{TTO} = 3.3 V$                  | $LB_x = 0$ , $PE = 0$ dB on all ports, low power mode <sup>3</sup> |                      | 69                   | 85                   | mA   |

|                                    | $LB_x = 1$ , $PE = 6$ dB on all ports, low power mode <sup>3</sup> |                      | 195                  | 230                  | mA   |

|                                    | $LB_x = 0$ , $PE = 0$ dB on all ports, default                     |                      | 69                   | 84                   | mA   |

|                                    | LB_x = 1, PE = 6 dB on all ports, default                          |                      | 193                  | 230                  | mA   |

| lπı                                |                                                                    |                      | 10                   | 20                   | mA   |

| <b>I</b> DVCC                      |                                                                    |                      | 2                    | 4                    | mA   |

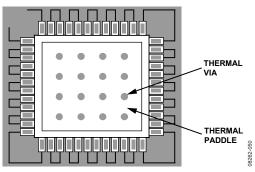

| THERMAL CHARACTERISTICS            |                                                                    |                      |                      |                      |      |

| Operating Temperature Range        |                                                                    | -40                  |                      | +85                  | °C   |

| $	heta_{JA}$                       | Still air; JEDEC 4-layer test board, exposed pad soldered          |                      | 21.2                 |                      | °C/W |

| $	heta_{JC}$                       | Still air; thermal resistance through exposed pad                  |                      | 1.1                  |                      | °C/W |

| Maximum Junction Temperature       |                                                                    |                      |                      | 125                  | °C   |

| LOGIC CHARACTERISTICS <sup>4</sup> | I <sup>2</sup> C, SDA, SCL, control pins                           |                      |                      |                      |      |

| Input High (V <sub>H</sub> )       | DV <sub>CC</sub> = 3.3 V                                           | $0.7 \times DV_{CC}$ |                      | $DV_CC$              | V    |

| Input Low (V <sub>IL</sub> )       | DV <sub>CC</sub> = 3.3 V                                           | VEE                  |                      | $0.3 \times DV_{CC}$ | V    |

| Input High (V <sub>IH</sub> )      | DV <sub>CC</sub> = 1.8 V                                           |                      | $0.8 \times DV_{CC}$ | $DV_CC$              | V    |

| Input Low (V <sub>IL</sub> )       | DV <sub>CC</sub> = 1.8 V                                           | VEE                  | $0.2 \times DV_{CC}$ |                      | V    |

| Output High (V <sub>он</sub> )     | 2 kΩ pull-up resistor to DV <sub>CC</sub>                          |                      | $DV_CC$              |                      | V    |

| Output Low (V <sub>OL</sub> )      | $I_{OL} = +3 \text{ mA}$                                           | VEE                  |                      | 0.4                  | V    |

$<sup>^1</sup>$  Bicast is off, loopback is off on all ports, preemphasis is set to minimum on all ports, and equalization is set to minimum on all ports.  $^2$  V<sub>ICM</sub> is the input common-mode voltage.  $^3$  Low power mode is obtained by following the steps identified in the Initialization Sequence for Low Power and LOS\_INT Operation section.  $^4$  EQ control pins (EQ\_A, EQ\_B, EQ\_C) require 5 kΩ in series when DV<sub>CC</sub> > V<sub>CC</sub>.

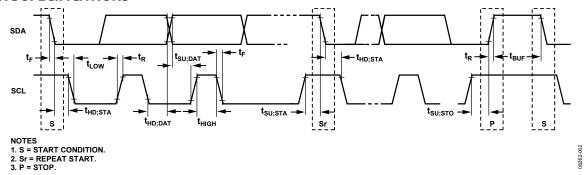

### **I<sup>2</sup>C TIMING SPECIFICATIONS**

Figure 2. I<sup>2</sup>C Timing Diagram

Table 2. I<sup>2</sup>C Timing Parameters

| Parameter                                          | Symbol              | Min | Max  | Unit |

|----------------------------------------------------|---------------------|-----|------|------|

| SCL Clock Frequency                                | f <sub>SCL</sub>    | 0   | 400+ | kHz  |

| Hold Time for a Start Condition                    | t <sub>HD;STA</sub> | 0.6 |      | μs   |

| Setup Time for a Repeated Start Condition          | t <sub>su;sta</sub> | 0.6 |      | μs   |

| Low Period of the SCL Clock                        | t <sub>LOW</sub>    | 1.3 |      | μs   |

| High Period of the SCL Clock                       | tнібн               | 0.6 |      | μs   |

| Data Hold Time                                     | t <sub>HD;DAT</sub> | 0   |      | μs   |

| Data Setup Time                                    | t <sub>su;dat</sub> | 10  |      | ns   |

| Rise Time for Both SDA and SCL                     | t <sub>R</sub>      | 1   | 300  | ns   |

| Fall Time for Both SDA and SCL                     | t <sub>F</sub>      | 1   | 300  | ns   |

| Setup Time for Stop Condition                      | t <sub>su;sto</sub> | 0.6 |      | μs   |

| Bus Free Time Between a Stop and a Start Condition | t <sub>BUF</sub>    | 1   |      | μs   |

| Bus Free Time After a Reset                        |                     | 1   |      | μs   |

| Reset Pulse Width                                  |                     | 10  |      | ns   |

| Capacitance for Each I/O Pin                       | Ci                  | 5   | 7    | pF   |

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 3.

| Parameter                           | Rating                                                     |

|-------------------------------------|------------------------------------------------------------|

| V <sub>CC</sub> to V <sub>EE</sub>  | 3.7 V                                                      |

| DV <sub>CC</sub> to V <sub>EE</sub> | 3.7 V                                                      |

| V <sub>TTI</sub>                    | Lower of $(V_{CC} + 0.6 \text{ V})$ or $3.6 \text{ V}$     |

| V <sub>TTO</sub>                    | Lower of $(V_{CC} + 0.6 \text{ V})$ or $3.6 \text{ V}$     |

| Vcc to DVcc                         | 0.6 V                                                      |

| Internal Power Dissipation          | 4.85 W                                                     |

| Differential Input Voltage          | 2.0 V                                                      |

| Logic Input Voltage                 | $V_{EE} - 0.3 \text{ V} < V_{IN} < V_{CC} + 0.6 \text{ V}$ |

| Storage Temperature Range           | −65°C to +125°C                                            |

| Junction Temperature                | 125°C                                                      |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

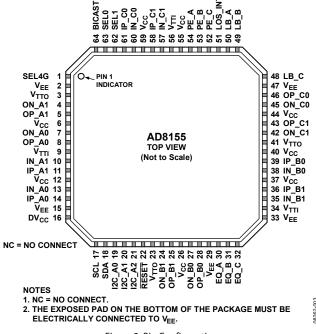

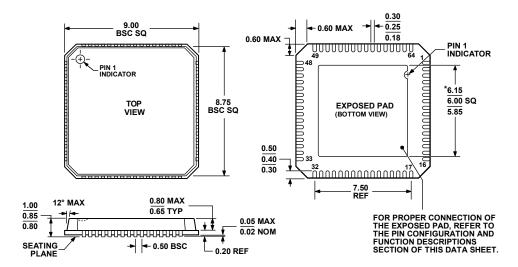

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No.                       | Mnemonic         | Type    | Description                                                                                          |

|-------------------------------|------------------|---------|------------------------------------------------------------------------------------------------------|

| 1                             | SEL4G            | Control | Set Transmitter for Low Speed PE, Active High.                                                       |

| 2, 15, 29, 33, 47, ePAD       | V <sub>EE</sub>  | Power   | Negative Supply. The exposed pad on the bottom of the package must be electrically connected to VEE. |

| 3, 23, 41                     | Vπo              | Power   | Port A, Port B, and Port C Output Termination Supply.                                                |

| 4                             | ON_A1            | Output  | High Speed Output Complement.                                                                        |

| 5                             | OP_A1            | Output  | High Speed Output.                                                                                   |

| 6, 12, 26, 37, 40, 44, 55, 59 | V <sub>cc</sub>  | Power   | Positive Supply.                                                                                     |

| 7                             | ON_A0            | Output  | High Speed Output Complement.                                                                        |

| 8                             | OP_A0            | Output  | High Speed Output.                                                                                   |

| 9, 34, 56                     | V <sub>TTI</sub> | Power   | Port A, Port B, and Port C Input Termination Supply.                                                 |

| 10                            | IN_A1            | Input   | High Speed Input Complement.                                                                         |

| 11                            | IP_A1            | Input   | High Speed Input.                                                                                    |

| 13                            | IN_A0            | Input   | High Speed Input Complement.                                                                         |

| 14                            | IP_A0            | Input   | High Speed Input.                                                                                    |

| 16                            | DV <sub>cc</sub> | Power   | Digital Power Supply.                                                                                |

| 17                            | SCL              | Control | I <sup>2</sup> C Clock Input.                                                                        |

| 18                            | SDA              | Control | I <sup>2</sup> C Data Input/Output.                                                                  |

| 19                            | I2C_A0           | Control | I <sup>2</sup> C Address Input (LSB).                                                                |

| 20                            | I2C_A1           | Control | I <sup>2</sup> C Address Input.                                                                      |

| 21                            | I2C_A2           | Control | I <sup>2</sup> C Address Input (MSB).                                                                |

| 22                            | RESET            | Control | Device Reset, Active Low.                                                                            |

| 24                            | ON_B1            | Output  | High Speed Output Complement.                                                                        |

| 25                            | OP_B1            | Output  | High Speed Output.                                                                                   |

| 27                            | ON_B0            | Output  | High Speed Output Complement.                                                                        |

| 28                            | OP_B0            | Output  | High Speed Output.                                                                                   |

| Pin No. | Mnemonic | Туре      | Description                                                                                                       |  |

|---------|----------|-----------|-------------------------------------------------------------------------------------------------------------------|--|

| 30      | EQ_A     | Control   | Port A Equalizer Control Input.                                                                                   |  |

| 31      | EQ_B     | Control   | Port B Equalizer Control Input.                                                                                   |  |

| 32      | EQ_C     | Control   | Port C Equalizer Control Input.                                                                                   |  |

| 35      | IN_B1    | Input     | High Speed Input Complement.                                                                                      |  |

| 36      | IP_B1    | Input     | High Speed Input.                                                                                                 |  |

| 38      | IN_B0    | Input     | High Speed Input Complement.                                                                                      |  |

| 39      | IP_B0    | Input     | High Speed Input.                                                                                                 |  |

| 42      | ON_C1    | Output    | High Speed Output Complement.                                                                                     |  |

| 43      | OP_C1    | Output    | High Speed Output.                                                                                                |  |

| 45      | ON_C0    | Output    | High Speed Output Complement.                                                                                     |  |

| 46      | OP_C0    | Output    | High Speed Output.                                                                                                |  |

| 48      | LB_C     | Control   | Port A Loopback Control Input, Active High.                                                                       |  |

| 49      | LB_B     | Control   | Port B Loopback Control Input, Active High.                                                                       |  |

| 50      | LB_A     | Control   | Port C Loopback Control Input, Active High.                                                                       |  |

| 51      | LOS_INT  | Interrupt | Loss of Signal Interrupt, Active High. Initialization sequenc required; see the Applications Information section. |  |

| 52      | PE_C     | Control   | Port A Preemphasis Control Input, Active High.                                                                    |  |

| 53      | PE_B     | Control   | Port B Preemphasis Control Input, Active High.                                                                    |  |

| 54      | PE_A     | Control   | Port C Preemphasis Control Input, Active High.                                                                    |  |

| 57      | IN_C1    | Input     | High Speed Input Complement.                                                                                      |  |

| 58      | IP_C1    | Input     | High Speed Input.                                                                                                 |  |

| 60      | IN_C0    | Input     | High Speed Input Complement.                                                                                      |  |

| 61      | IP_C0    | Input     | High Speed Input.                                                                                                 |  |

| 62      | SEL1     | Control   | Lane 1 A/B Switch Control Input.                                                                                  |  |

| 63      | SEL0     | Control   | Lane 0 A/B Switch Control Input.                                                                                  |  |

| 64      | BICAST   | Control   | Enable Bicast for Port A and Port B Outputs, Active High.                                                         |  |

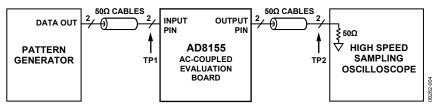

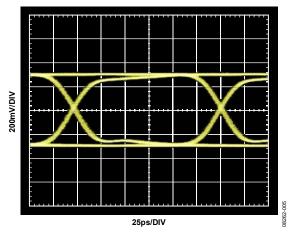

# TYPICAL PERFORMANCE CHARACTERISTICS

Figure 4. Standard Test Circuit (No Channel)

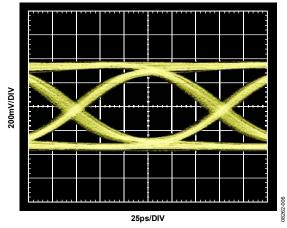

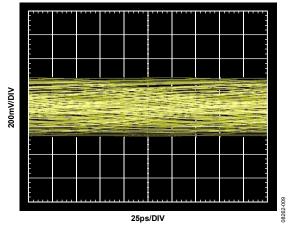

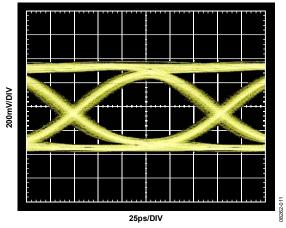

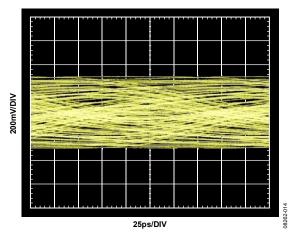

Figure 5. 6.5 Gbps Input Eye (TP1 from Figure 4)

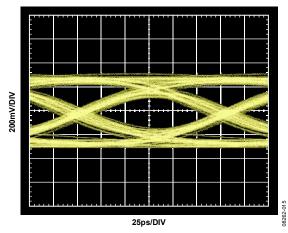

Figure 6. 6.5 Gbps Output Eye, No Channel (TP2 from Figure 4)

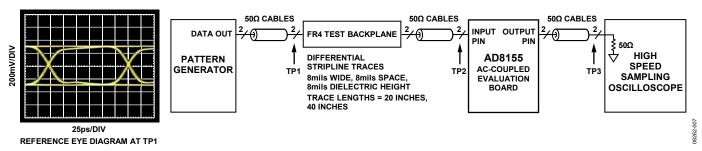

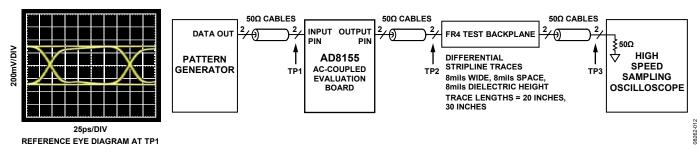

Figure 7. Input Equalization Test Circuit

Figure 8. 6.5 Gbps Input Eye, 20 Inch FR4 Input Channel (TP2 from Figure 7)

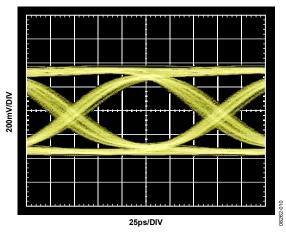

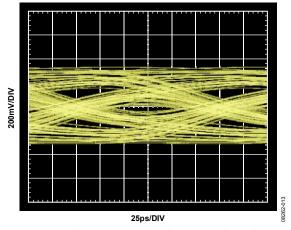

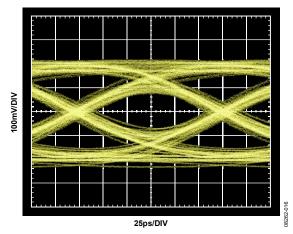

Figure 10. 6.5 Gbps Output Eye, 20 Inch FR4 Input Channel (TP3 from Figure 7)

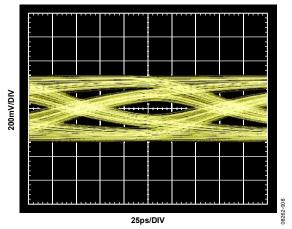

Figure 9. 6.5 Gbps Input Eye, 40 Inch FR4 Input Channel (TP2 from Figure 7)

Figure 11. 6.5 Gbps Output Eye, 40 Inch FR4 Input Channel (TP3 from Figure 7)

Figure 12. Output Preemphasis Test Circuit

Figure 13. 6.5 Gbps Output Eye, 20 Inch FR4 Input Channel, PE = 0 (TP3 from Figure 12)

Figure 14. 6.5 Gbps Output Eye, 30 Inch FR4 Input Channel, PE = 0 (TP3 from Figure 12)

Figure 15. 6.5 Gbps Output Eye, 20 Inch FR4 Input Channel, PE = Best Setting, Default Output Level (TP3 from Figure 12)

Figure 16. 6.5 Gbps Output Eye, 30 Inch FR4 Input Channel, PE = Best Setting, 200 mV Output Level (TP3 from Figure 12)

Figure 17. Deterministic Jitter vs. Data Rate

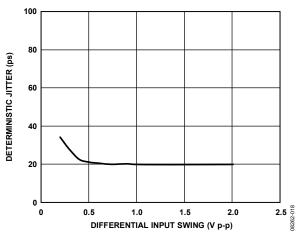

Figure 18. Deterministic Jitter vs. Input Swing

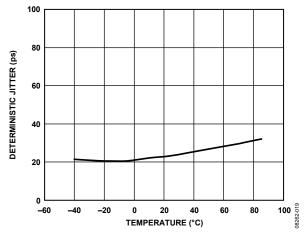

Figure 19. Deterministic Jitter vs. Temperature

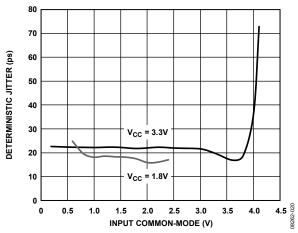

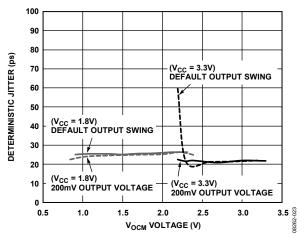

Figure 20. Deterministic Jitter vs. Input Common Mode

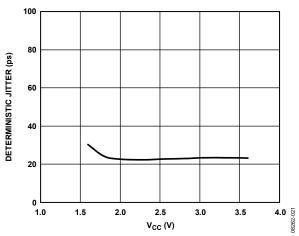

Figure 21. Deterministic Jitter vs. Vcc

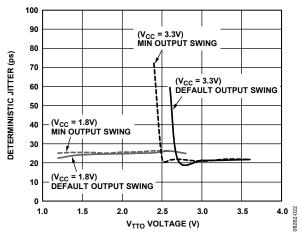

Figure 22. Deterministic Jitter vs. Output Termination Voltage ( $V_{TTO}$ )

Figure 23. Deterministic Jitter vs. Output Common-Mode Voltage (Vocm)

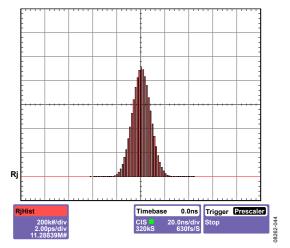

Figure 24. Random Jitter Histogram

Figure 25.  $t_R/t_F$  vs. Temperature

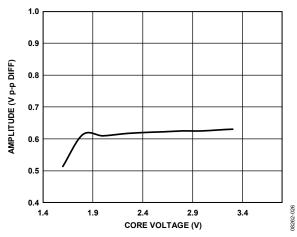

Figure 26. Output Amplitude (Default Setting) vs. Vcc

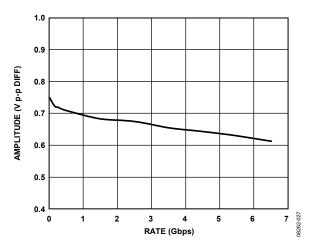

Figure 27. Output Amplitude vs. Rate

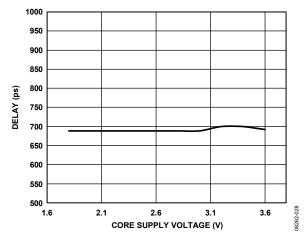

Figure 28. Propagation Delay vs. Core Supply

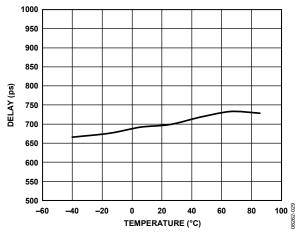

Figure 29. Propagation Delay vs. Temperature

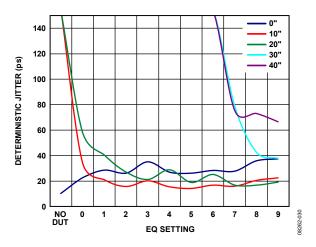

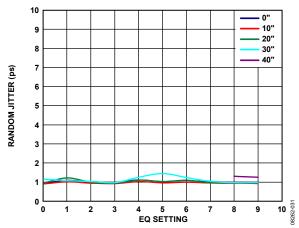

Figure 30. Deterministic Jitter vs. EQ Setting

Figure 31. Random Jitter vs. EQ Setting vs. Trace

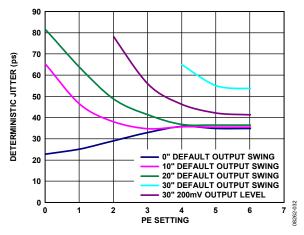

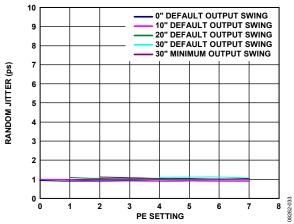

Figure 32. Deterministic Jitter vs. PE Setting

Figure 33. Random Jitter vs. PE Setting

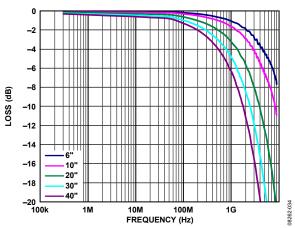

Figure 34. S21 Test Traces

### THEORY OF OPERATION

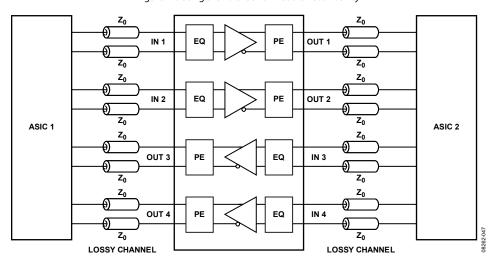

The AD8155 is a buffered, asynchronous, three-port transceiver that allows 2:1 multiplexing and 1:2 demultiplexing among its ports. The 1:2 demux path supports bicast operation, allowing the AD8155 to operate as a port replicator as well as a redundancy switch. The AD8155 offers loopback on each lane, allowing the part to be configured as a six-lane equalizer or redriver with FFE.

Figure 35. Mux/Demux Paths, Port A to Port C

The part offers extensively programmable transmit output levels and preemphasis settings as well as squelch or full disable. The receivers integrate a programmable, multizero transfer function for aggressive equalization and a programmable loss-of-signal feature. The AD8155 provides a balanced, high speed switch core that maintains low lane-to-lane skew while preserving edge rates.

The I/O on-chip termination resistors are tied to user-settable supplies for increased flexibility. The AD8155 supports a wide primary supply range; V<sub>CC</sub> can be set from 1.8 V to 3.3 V. These

features, together with programmable transmitter output levels, allow for a wide range of dc- and ac-coupled I/O configurations.

The AD8155 supports several control and configuration modes, shown in Table 5. The pin control mode offers access to a subset of the total feature list but allows for a much simplified control scheme. Table 6 compares the features in all control modes.

The primary advantage of using the serial control interface is that it allows finer resolution in setting receive equalization, transmitter preemphasis, loss-of-signal (LOS) behavior, and output levels.

By default, the AD8155 starts in the pin control mode. Strobing the  $\overline{\text{RESET}}$  pin sets all on-chip registers to their default values and uses pins to configure switch connectivity, PE, and EQ levels. In mixed mode, switch connectivity is still controlled through the SEL[1:0], LB\_[A:C], and BICAST pins. The user can override PE and EQ settings in mixed mode. In serial mode, all functions are accessed through registers and the control pin inputs are ignored, except RESET .

The AD8155 register set is controlled through a 2-wire  $I^2C$  interface. The AD8155 acts only as an  $I^2C$  slave device. The 7-bit slave address for the AD8155  $I^2C$  interface contains the static value b1010 for the upper four bits. The lower three bits are controlled by the input pins,  $I^2C_A[2:0]$ .

**Table 5. Control Interface Mode Register**

| Address | Default | Register Name  | Bit | Bit Name  | Functionality Description                                                                                                      |

|---------|---------|----------------|-----|-----------|--------------------------------------------------------------------------------------------------------------------------------|

| 0x0F    | 0x00    | Control        | 7:2 | Reserved  | Set to 0.                                                                                                                      |

|         |         | interface mode | 1:0 | Mode[1:0] | 00: toggle pin control. Asynchronous control through toggle pins only.                                                         |

|         |         |                |     |           | 10: mixed control. Switch configuration via toggle pins, register-based control through the I <sup>2</sup> C serial interface. |

|         |         |                |     |           | 11: serial control. Register-based control through the I <sup>2</sup> C serial interface.                                      |

Table 6. Features Available Through Toggle Pin or Serial Control

| Feature                    | Pin Control                     | Serial Control                                      |

|----------------------------|---------------------------------|-----------------------------------------------------|

| Switch Features            |                                 |                                                     |

| BICAST                     | One pin                         | One bit                                             |

| A/B Lane Select            | Two pins                        | Two bits                                            |

| Loopback                   | Three pins                      | Three bits                                          |

| Rx Features                |                                 |                                                     |

| EQ Levels                  | Two settings                    | 10 settings                                         |

| N/P Swap                   | Not available                   | Available                                           |

| Squelch                    | Enabled                         | Three bits                                          |

| Tx Features                |                                 |                                                     |

| Programmable Output Levels | ±400 mV diff fixed <sup>1</sup> | ±200 mV diff/±300 mV diff/±400 mV diff/±600 mV diff |

| PE Levels                  | Two settings                    | >7 settings                                         |

<sup>1 ±400</sup> mV diff indicates a 400 mV amplitude signal measured between two differential nodes. The voltage swing at differential I/O pins is described in this data sheet both in terms of the differentially measured voltage range (±400 mV diff, for example) and in terms of peak-to-peak differential swing, denoted as mV p-p diff. An output level setting of ±400 mV diff delivers a differential peak-to-peak output voltage of 800 mV p-p diff.

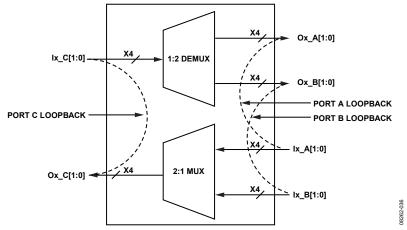

# THE SWITCH (MUX/DEMUX/UNICAST/BICAST/LOOPBACK)

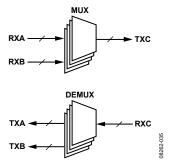

The mux and demux functions of the AD8155 can be controlled either with the toggle pins or through the register map. The multiplexer path switches received data from Input Port A or Input Port B to Output Port C. The SEL[1:0] pins allow switching lanes independently. The demultiplexer path switches received data from Input Port C to Output Port A, Output Port B, or (if bicast mode is enabled) to both Output Port A and Output Port B.

Table 7. Port Selection and Configuration with All Loopbacks Disabled

| BICAST | SELx | Output<br>Port A | Output<br>Port B | Output<br>Port C |

|--------|------|------------------|------------------|------------------|

| 0      | 0    | Ix_C[1:0]        | Idle             | lx_A[1:0]        |

| 0      | 1    | ldle             | lx_C[1:0]        | Ix_B[1:0]        |

| 1      | 0    | lx_C[1:0]        | lx_C[1:0]        | lx_A[1:0]        |

| _1     | 1    | lx_C[1:0]        | lx_C[1:0]        | lx_B[1:0]        |

When the device is in unicast mode, the output lanes on either Port A or Port B are in an idle state. In the idle state, the transmitter output current is set to 0, and the P and N sides of the lane are pulled up to the output termination voltage through the on-chip termination resistors. To save power, the unused receiver automatically disables.

The AD8155 supports port-level loopback, illustrated in Figure 36. The loopback control pins override the lane select (SEL[1:0]) and bicast control (BICAST) pin settings at the port level. In serial control mode, Bits [6:4] of Register 0x01 control loopback and are equivalent to asserting Pin LB\_A, Pin LB\_B, and Pin LB\_C. Table 8 summarizes the different loopback configurations.

The loopback feature is useful for system debug, self-test, and initialization, allowing system ASICs to compare Tx and Rx data sent over a single bidirectional link. Loopback can also be used to configure the device as a two- to six-lane receive equalizer or backplane redriver.

Figure 36. Port-Level Loopback

Table 8. Switch Connectivity vs. Loopback, BICAST, and Port Select Settings

| LB_A | LB_B | LB_C | BICAST | SEL[1:0] | Output Port A | Output Port B | Output Port C |

|------|------|------|--------|----------|---------------|---------------|---------------|

| 0    | 0    | 0    | 0      | 00       | lx_C[1:0]     | Idle          | lx_A[1:0]     |

| 0    | 0    | 0    | 0      | 11       | Idle          | Ix_C[1:0]     | lx_B[1:0]     |

| 0    | 0    | 0    | 1      | 00       | lx_C[1:0]     | Ix_C[1:0]     | lx_A[1:0]     |

| 0    | 0    | 0    | 1      | 1        | Ix_C[1:0]     | Ix_C[1:0]     | lx_B[1:0]     |

| 0    | 0    | 1    | 0      | 00       | lx_C[1:0]     | Idle          | lx_C[1:0]     |

| 0    | 0    | 1    | 0      | 11       | Idle          | Ix_C[1:0]     | lx_C[1:0]     |

| 0    | 0    | 1    | 1      | 00       | Ix_C[1:0]     | Ix_C[1:0]     | Ix_C[1:0]     |

| 0    | 0    | 1    | 1      | 11       | Ix_C[1:0]     | Ix_C[1:0]     | Ix_C[1:0]     |

| 0    | 1    | 0    | 0      | 00       | Ix_C[1:0]     | Ix_B[1:0]     | lx_A[1:0]     |

| 0    | 1    | 0    | 0      | 11       | Idle          | Ix_B[1:0]     | lx_B[1:0]     |

| 0    | 1    | 0    | 1      | 00       | Ix_C[1:0]     | Ix_B[1:0]     | lx_A[1:0]     |

| 0    | 1    | 0    | 1      | 11       | Ix_C[1:0]     | Ix_B[1:0]     | lx_B[1:0]     |

| 0    | 1    | 1    | 0      | 00       | Ix_C[1:0]     | Ix_B[1:0]     | lx_C[1:0]     |

| 0    | 1    | 1    | 0      | 11       | Idle          | Ix_B[1:0]     | Ix_C[1:0]     |

| 0    | 1    | 1    | 1      | 00       | Ix_C[1:0]     | Ix_B[1:0]     | lx_C[1:0]     |

| 0    | 1    | 1    | 1      | 11       | Ix_C[1:0]     | Ix_B[1:0]     | Ix_C[1:0]     |

| 1    | 0    | 0    | 0      | 00       | lx_A[1:0]     | Idle          | lx_A[1:0]     |

| 1    | 0    | 0    | 0      | 11       | Ix_A[1:0]     | Ix_C[1:0]     | lx_B[1:0]     |

| 1    | 0    | 0    | 1      | 00       | lx_A[1:0]     | Ix_C[1:0]     | lx_A[1:0]     |

| 1    | 0    | 0    | 1      | 11       | Ix_A[1:0]     | Ix_C[1:0]     | lx_B[1:0]     |

| 1    | 0    | 1    | 0      | 00       | lx_A[1:0]     | Idle          | lx_C[1:0]     |

| 1    | 0    | 1    | 0      | 11       | lx_A[1:0]     | Ix_C[1:0]     | lx_C[1:0]     |

| 1    | 0    | 1    | 1      | 00       | lx_A[1:0]     | Ix_C[1:0]     | lx_C[1:0]     |

| 1    | 0    | 1    | 1      | 11       | lx_A[1:0]     | Ix_C[1:0]     | lx_C[1:0]     |

| 1    | 1    | 0    | 0      | 00       | lx_A[1:0]     | Ix_B[1:0]     | lx_A[1:0]     |

| 1    | 1    | 0    | 0      | 11       | Ix_A[1:0]     | Ix_B[1:0]     | lx_B[1:0]     |

| 1    | 1    | 0    | 1      | 00       | lx_A[1:0]     | Ix_B[1:0]     | lx_A[1:0]     |

| 1    | 1    | 0    | 1      | 11       | Ix_A[1:0]     | Ix_B[1:0]     | lx_B[1:0]     |

| 1    | 1    | 1    | 0      | 00       | Ix_A[1:0]     | lx_B[1:0]     | Ix_C[1:0]     |

| 1    | 1    | 1    | 0      | 11       | Ix_A[1:0]     | lx_B[1:0]     | Ix_C[1:0]     |

| 1    | 1    | 1    | 1      | 00       | Ix_A[1:0]     | lx_B[1:0]     | Ix_C[1:0]     |

| 1    | 1    | 1    | 1      | 11       | Ix_A[1:0]     | Ix_B[1:0]     | lx_C[1:0]     |

### **RECEIVERS**

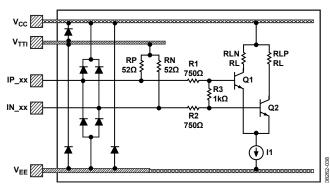

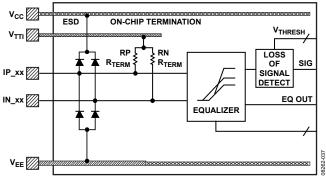

The AD8155 receivers incorporate 50  $\Omega$  on-chip termination, ESD protection, and a multizero equalization function capable of delivering up to 18 dB of boost at 4.25 GHz. The AD8155 can compensate signal degradation at 6.5 Gbps from over 40 inches of FR4 backplane trace. The receive path also incorporates a loss-of-signal (LOS) function that squelches the associated transmitter when the midband differential voltage falls below a specified threshold value. Finally, the receivers implement a sign-swapping option (P/N swap), which allows the user to invert the sign of the input signal path and eliminates the need for board-level crossovers in the receive channels.

### Input Structure and Allowed Input Levels

The AD8155 tolerates an input common-mode range (measured with zero differential input) of

$$V_{EE} + 0.6 \text{ V} < V_{ICM} < V_{CC} + 0.3 \text{ V}$$

Typical supply configurations include, but are not limited to, those listed in Table 9.

**Table 9. Typical Input Supply Configurations**

| Configuration                         | <b>DV</b> <sub>cc</sub> | <b>V</b> cc | V <sub>TTI</sub> |

|---------------------------------------|-------------------------|-------------|------------------|

| Low V <sub>™</sub> , AC-Coupled Input | 3.3 V – 1.8 V           | 1.8 V       | 1.6 V            |

| Single 1.8 V Supply                   | 3.3 V – 1.8 V           | 1.8 V       | 1.8 V            |

| 3.3 V Core                            | 3.3 V                   | 3.3 V       | 1.8 V            |

| Single 3.3 V Supply                   | 3.3 V                   | 3.3 V       | 3.3 V            |

When dc-coupling with LVDS, CML, or ECL signals, it can be advantageous to operate with split or negative supplies (see the Applications Information section). In these applications, it is necessary to observe the maximum voltage ratings between  $V_{\rm CC}$  and  $V_{\rm EE}$  and to select supply voltages for  $V_{\rm TTO}$  and  $V_{\rm TTI}$  in the range of  $V_{\rm CC}$  to  $V_{\rm EE}$  to avoid activating the ESD protection devices.

Figure 37. Simplified Receiver Input Structure

#### **Equalizer Settings**

Every input lane offers a low power, asynchronous, programmable receive equalizer for NRZ data up to 6.5 Gbps. The pin control interface allows two levels of receive equalization. Register-based control allows the user 10 equalizer settings. Register and pin control boost settings are listed in Table 10. Equalization capability and resulting jitter performance are illustrated in Figure 30, Figure 31, and Figure 34. Figure 34 shows the loss characteristic of various reference channels, and Figure 30 and Figure 31 show resulting DJ and RJ performance vs. equalizer setting against these channels.

The two LSBs of Register 0x41, Register 0x81, and Register 0xC1 allow programming of all the equalizers in a port simultaneously (see Table 13). The 0x42, 0x82, and 0xC2 registers allow per-lane programming of the equalizers (see Table 22). Be aware that writing to the port-level equalizer registers updates and overwrites per-lane settings.

**Table 10. Equalizer Settings**

| <b>Equalization Boost (dB)</b> | EQ Register Setting | EQ Pin |

|--------------------------------|---------------------|--------|

| 0                              | 0                   | 0      |

| 2                              | 1                   | N/A    |

| 4                              | 2                   | N/A    |

| 6                              | 3                   | N/A    |

| 8                              | 4                   | 1      |

| 10                             | 5                   | N/A    |

| 12                             | 6                   | N/A    |

| 14                             | 7                   | N/A    |

| 16                             | 8                   | N/A    |

| 18                             | 9                   | N/A    |

Figure 38. Functional Diagram of the AD8155 Receiver

#### Lane Disables

By default, the receivers and transmitters enable in an on-demand fashion according to the state of the SEL[1:0], LB\_[A:C], and BICAST pins or to the state of the equivalent registers in serial control mode. Register 0x40, Register 0x80, and Register 0xC0 implement per-lane disables for the receivers, and Register 0x48, Register 0x88, and Register 0xC8 implement per-lane transmitter disables. These disables override the default settings. Each bit in the register is named for the lane and function it disables. For example, RXDIS B0 disables the receiver on Lane 0 of Port B whereas TXDIS C1 disables the Lane 1 transmitter of Port C (see Table 11).

### Lane Inversion: P/N Swap

The receiver P/N swap function is a convenience intended to allow the user to implement the equivalent of a board-level routing crossover in a much smaller area while eliminating vias (impedance discontinuities) that compromise the high frequency integrity of the signal path. Using this feature to correct an inversion downstream of the receiver may require the user to be aware of the sign of the data when switching connectivity (the mux/demux path). The feature is available on a per-lane setting through Register 0x44, Register 0x84, and Register 0xC4. Setting the bit true flips the sign sense of the P and N inputs for the associated lane. The default setting is 0 (no inversion).

Table 11. Per-Lane Disables

| Address | Port   | Default | Register Name     | Bit | Bit Name       | Functionality Description            |

|---------|--------|---------|-------------------|-----|----------------|--------------------------------------|

| 0x40    | Port A | 0x00    | RX[A/B/C] disable | 7:4 | Reserved       | Set to 0                             |

| 0x80    | Port B | 0x00    |                   | 3:2 | Reserved       |                                      |

| 0xC0    | Port C | 0x00    |                   | 1   | RXDIS [A/B/C]1 | 0: RX Port [A/B/C], Lane 1, enabled  |

|         |        |         |                   |     |                | 1: RX Port [A/B/C], Lane 1, disabled |

|         |        |         |                   | 0   | RXDIS [A/B/C]0 | 0: RX Port [A/B/C], Lane 0, enabled  |

|         |        |         |                   |     |                | 1: RX Port [A/B/C], Lane 0, disabled |

| 0x48    | Port A | 0x00    | TX[A/B/C] disable | 7:4 | Reserved       | Set to 0                             |

| 0x88    | Port B | 0x00    |                   | 3:2 | Reserved       |                                      |

| 0xC8    | Port C | 0x00    |                   | 1   | TXDIS [A/B/C]1 | 0: TX Port [A/B/C], Lane 1, enabled  |

|         |        |         |                   |     |                | 1: TX Port [A/B/C], Lane 1, disabled |

|         |        |         |                   | 0   | TXDIS [A/B/C]0 | 0: TX Port [A/B/C], Lane 0, enabled  |

|         |        |         |                   |     |                | 1: TX Port [A/B/C], Lane 0, disabled |

Table 12. Lane Inversion

| Address | Port   | Default | Register Name      | Bit | Bit Name   | Functionality Description |

|---------|--------|---------|--------------------|-----|------------|---------------------------|

| 0x44    | Port A | 0x00    | RX[A/B/C] P/N swap | 7:2 | Reserved   | Set to 0                  |

| 0x84    | Port B | 0x00    |                    | 1   | PN[A/B/C]1 | 0: Lane 1, noninverted    |

| 0xC4    | Port C | 0x00    |                    |     |            | 1: Lane 1, inverted       |

|         |        |         |                    | 0   | PN[A/B/C]0 | 0: Lane 0, noninverted    |

|         |        |         |                    |     |            | 1: Lane 0, inverted       |

**Table 13. Port-Level EQ Setting**

|         |        | ` 0     |                      |     |                |                           |

|---------|--------|---------|----------------------|-----|----------------|---------------------------|

| Address | Port   | Default | Register Name        | Bit | Bit Name       | Functionality Description |

| 0x41    | Port A | 0x00    | RX[A/B/C] EQ setting | 7:4 | Reserved       | Set to 0                  |

| 0x81    | Port B | 0x00    |                      | 3:0 | [A/B/C]EQ[3:0] |                           |

| 0xC1    | Port C | 0x00    |                      |     |                |                           |

### LOSS OF SIGNAL (LOS)

The serial control interface allows access to the AD8155 loss of signal features (LOS is not available in pin control mode). Each receiver includes a low power, loss-of-signal detector. The loss-of-signal circuit monitors the received data stream and generates a system interrupt when the received signal power falls below a fixed threshold. The threshold is 50 mV p-p diff, referred to the input pins. The LOS circuit monitors the equalized receive waveform and integrates the rms power of the equalized waveform over a selectable interval of either 2 ns or 10 ns. The detectors are enabled on a per-port basis with Bit 0 of the RXA/B/C LOS control registers (0x51, 0x91, 0xD1).

By default, when the receiver detects an LOS event, it squelches its associated transmitter, lowering the output current to submicroamps. This prevents the high gain, wide bandwidth signal path from turning low level system noise on an undriven input pair into a source of hostile crosstalk at the transmitter. The squelch feature can be disabled with Bit 3 of the global squelch control register (0x04).

The LOS\_INT pin evaluates a logical OR of all LOS status register bits for all enabled receivers (LOS status registers are located at 0x45, 0x85, and 0xC5). The upper two bits in the RXA, RXB, and RXC LOS status registers are sticky, whereas the two LSBs are continuously updated to indicate the instantaneous status of LOS for an enabled receiver. The sticky bits are cleared by writing 0 to the RXA, RXB, and RXC LOS status registers. The LOS\_INT pin remains high after an LOS event until all sticky registers are cleared and all active status registers (for example, Bits[1:0]) read 0. The LOS\_INT pin requires that an initialization sequence be enabled (see the Applications Information section).

The LOS\_INT pin can be used to generate an interrupt for the system control software. In a standard implementation, when LOS\_INT goes high, the system software registers the interrupt and polls the RXA, RXB, and RXC LOS status registers to determine which input lost signal and whether the signal has been restored.

Table 14. Global Loss-of-Signal Squelch Control Register

| Address | Default | Register Name       | Bit | Bit Name   | <b>Functionality Description</b> |

|---------|---------|---------------------|-----|------------|----------------------------------|

| 0x04    | 0x0F    | Global Squelch Ctrl | 7:4 | Reserved   | Set to 0                         |

|         |         |                     | 3   | GSQLCH_ENB | 0: LOS auto squelch disabled     |

|         |         |                     |     |            | 1: LOS auto squelch enabled      |

|         |         |                     | 2:0 | Reserved   | Set to 1                         |

Table 15. Port-Level Loss-of-Signal Control Registers

| Address | Port   | Default | Register Name | Bit | Bit Name | Functionality Description           |

|---------|--------|---------|---------------|-----|----------|-------------------------------------|

| 0x51    | Port A | 0x05    | RX[A/B/C] LOS | 7:3 | Reserved | Set to 0                            |

| 0x91    | Port B | 0x05    | control       | 2   | LOS_FILT | 0: LOS filter time constant = 2 ns  |

| 0xD1    | Port C | 0x05    |               |     |          | 1: LOS filter time constant = 10 ns |

|         |        |         |               | 1   | Reserved | Set to 0                            |

|         |        |         |               | 0   | LOS_ENB  | 0: LOS disabled                     |

|         |        |         |               |     |          | 1: LOS enabled                      |

Table 16. Port-Level Loss-of-Signal Status Registers

| Address      | Port             | Default          | Register Name           | Bit | Bit Name                  | Functionality Description                                                                                                                                                                        |

|--------------|------------------|------------------|-------------------------|-----|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x45         | Port A           | Read only        |                         | 7:6 | Reserved                  |                                                                                                                                                                                                  |

| 0x85<br>0xC5 | Port B<br>Port C | Write 0 to clear | RX[A/B/C] LOS<br>status | 5:4 | LOS[A/B/C][1:0]<br>sticky | 00: LOS event has not occurred. 01: LOS event has occurred on Lane 0. 10: LOS event has occurred on Lane 1. 11: LOS event has occurred on both lanes. Read only; write 0 to clear.               |

|              |                  |                  |                         | 3:2 | Reserved                  |                                                                                                                                                                                                  |

|              |                  |                  |                         | 1:0 | LOS[A/B/C][1:0]<br>active | <ul><li>00: active signals on both lanes.</li><li>01: inactive signal on Lane 0.</li><li>10: inactive signal on Lane 1.</li><li>11: inactive signals on both lanes.</li><li>Read only.</li></ul> |

#### **TRANSMITTERS**

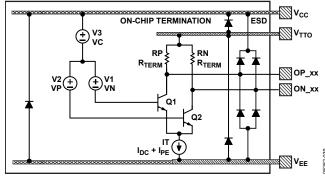

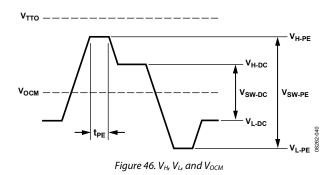

The AD8155 transmitter offers programmable preemphasis, programmable output levels, output disable, and transmit squelch. The SEL4G pin lets the user lower the transmitter frequency of maximum boost from 3.25 GHz to 2.0 GHz, allowing the AD8155 to offer exceptional transmit channel compensation for legacy applications (4.5 Gbps and slower).

Figure 39. Simplified Transmitter Structure

### **Output Level Programming and Output Structure**

The output level of the transmitter of each lane is independently programmable. In pin control mode, a default output amplitude of 800 mV p-p diff (±400 mV diff) is delivered (see Table 17). Register-based control allows the user to set the transmitter output levels on a per-port or per-lane basis to four predefined levels. Port-level programming overwrites lane-level configuration. The ALEV, BLEV, and CLEV bits in Register 0x49, Register 0x89, and Register 0xC9, respectively, are used to set the output levels for all transmitters. The A[1:0]OLEV[1:0], B[1:0]OLEV[1:0], and C[1:0]OLEV[1:0] bits in Register 0x4C, Register 0x8C, and Register 0xCC allow per-lane settings (see Table 22).

**Table 17. Predefined Output Levels**

| [A/B/C][1:0]OLEV[1] | [A/B/C][1:0]OLEV[0] | Output Level  |

|---------------------|---------------------|---------------|

| 0                   | 0                   | ±200 mV diff  |

| 0                   | 1                   | ±300 mV diff  |

| 1                   | 0                   | ±400 mV diff  |

|                     |                     | (default)     |

| 1                   | 1                   | ± 600 mV diff |

Note that the choice of output level influences the output common-mode level. A 600 mV diff output level with a full PE range requires a supply and output termination voltage of 2.5 V or higher ( $V_{\text{TTO}}, V_{\text{CC}} \ge 2.5 \text{ V}$ ).

### **Preemphasis**

Transmitter preemphasis levels can be set by pin control or through the control registers. Pin control allows two settings of PE, 0 dB and 6 dB. The control registers provide seven levels of PE. Note that a larger range of boost settings is available for lower output levels. Note that toggle pin control of PE is limited to the 400 mV diff output level settings. Table 18 lists the available preemphasis settings for each output level.

Preemphasis can be programmed per port or per lane. Register 0x49, Register 0x89, and Register 0xC9 set all outputs in a port at once. Registers 0x4A, 0x8A, and 0xCA allow setting PE on a per-lane basis. The following equation sets preemphasis boost:

$$Gain[dB] = 20 \times \log_{10}(1 + \frac{V_{SW-PE} - V_{SW-DC}}{V_{SW-DC}})$$

(1)

**Table 18. Setting Transmitter Preemphasis**

| Tuble 10. betti |            |         |             |          |

|-----------------|------------|---------|-------------|----------|

| Output Level    | Pin        | Bit     | PE<br>Boost | PE Boost |

| (mV diff)       | PE_[A/B/C] | PE[2:0] | (%)         | (dB)     |

| 200             | N/A        | 000     | 0           | 0        |

| 200             | N/A        | 001     | 50          | 3.52     |

| 200             | N/A        | 010     | 100         | 6.02     |

| 200             | N/A        | 011     | 150         | 7.96     |

| 200             | N/A        | 100     | 200         | 9.54     |

| 200             | N/A        | 101     | 250         | 10.88    |

| 200             | N/A        | 110     | 300         | 12.04    |

| 300             | N/A        | 000     | 0           | 0        |

| 300             | N/A        | 001     | 33          | 2.5      |

| 300             | N/A        | 010     | 67          | 4.44     |

| 300             | N/A        | 011     | 100         | 6.02     |

| 300             | N/A        | 100     | 133         | 7.36     |

| 300             | N/A        | 101     | 167         | 8.52     |

| 300             | N/A        | 110     | 200         | 9.54     |

| 400             | 0          | 000     | 0           | 0        |

| 400             | N/A        | 001     | 25          | 1.94     |

| 400             | N/A        | 010     | 50          | 3.52     |

| 400             | N/A        | 011     | 75          | 4.86     |

| 400             | 1          | 100     | 100         | 6.02     |

| 400             | N/A        | 101     | 125         | 7.04     |

| 400             | N/A        | 110     | 150         | 7.96     |

| 600             | N/A        | 000     | 0           | 0        |

| 600             | N/A        | 001     | 17          | 1.34     |

| 600             | N/A        | 010     | 33          | 2.5      |

| 600             | N/A        | 011     | 50          | 3.52     |

| 600             | N/A        | 100     | 67          | 4.44     |

| 600             | N/A        | 101     | 83          | 5.26     |

| 600             | N/A        | 110     | 100         | 6.02     |

#### Squelch and Disable

Each transmitter is equipped with disable and squelch controls. Disable is a full power-down state: the transmitter current is reduced to zero and the output pins pull up to  $V_{\rm TTO}$ , but there is a delay of approximately 1  $\mu s$  associated with reenabling the transmitter. Squelch keeps the output current enabled such that both output pins are at the output common-mode voltage. The transmitter recovers from squelch in less than 64 ns.

### Speed Select

The SEL4G pin lets the user lower the transmitter frequency of maximum boost from 3.25 GHz to 2.0 GHz, allowing the AD8155 to offer exceptional transmit channel compensation for legacy applications (4.5 Gbps and slower). SEL4G = 1 lowers the

frequency of maximum boost without sacrificing the amount of boost delivered.

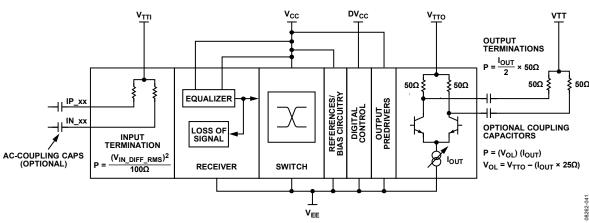

### **AD8155 POWER CONSUMPTION**

There are several sections of the AD8155 that draw varying power depending on the supply voltages, the type of I/O coupling used, and the status of the AD8155 operation. Figure 40 shows a block diagram of these sections. An initialization sequence is required to enable the AD8155 in a low power mode (see the Applications Information section).

The first section consists of the input termination resistors. The power dissipated in the termination resistors is due to the input differential swing and any common-mode current resulting from dc-coupling the input.

In the next section (the receiver section), each input is powered only when it is selected, and the disable bits are set to 0. If a receiver is not selected, it is powered down. Thus, the total number of active inputs affects the total power consumption. Furthermore, the loss-of-signal detection circuits can be disabled independent of the receiver for even greater power savings.

The core of the device performs the multiplexer and demultiplexer switching functions. It draws a fixed quiescent current of 2 mA whenever the AD8155 is powered from  $V_{\rm CC}$  to  $V_{\rm EE}$ . The switch draws an additional  $4\times4.6$  mA in normal mux/demux operation and an additional  $6\times4.6$  mA with all ports in loopback or with bicast selected. The switch core can be disabled to save power.

An output predriver section draws a current,  $I_{\text{PRED}},$  that is related to the programmed output current,  $I_{\text{TTO}}.$  The predriver current always flows from  $V_{\text{CC}}$  to  $V_{\text{EE}}.$  It is treated separately from the output current, which flows from  $V_{\text{TTO}}$  and may not be the same voltage as  $V_{\text{CC}}.$

The final section is the outputs section. For an individual output, the programmed output current flows through two separate paths. One is the on-chip termination resistor, and the other is the transmission line and the destination termination resistor. The nominal parallel impedance of these two paths is 25  $\Omega$ . The sum of these two currents flows through the switches and the current source of the AD8155 output circuit and out through  $V_{EE}$ . The power dissipated in the transmission line and the destination resistor is not dissipated in the AD8155 but must be supplied from the power supply and is a factor in overall system power. The current in the on-chip termination resistors and the output current source dissipate power in the AD8155 itself.

### **Outputs**

The output current is set by a combination of output level and preemphasis settings (see Table 19). For the two logic switch states, this current flows through an on-chip termination resistor and a parallel path to the destination device and its termination resistor. The power in this parallel path is not dissipated by the AD8155. With preemphasis enabled, some current always flows in both the P and N termination resistors. This preemphasis current gives rise to an output commonmode shift, which varies with ac-coupling or dc-coupling and which is calculated for both cases in Table 19.

Perhaps the most direct method for calculating power dissipated in the output is to calculate the power that would be dissipated if all of  $I_{TOT}$  were to flow on-die from  $V_{TTO}$  to  $V_{EE}$  and to subtract from this the power dissipated off die in the destination device termination resistors and the channel. For this purpose, the destination device and channel can be modeled as  $50~\Omega$  load resistors,  $R_{L}$ , in parallel with the AD8155 termination resistors.

Figure 40. AD8155 Power Distribution Block Diagram

### **Power Saving Considerations**

Whereas the AD8155 power consumption is very low compared to similar devices, careful control of its operating conditions can yield further power savings. Significant power reduction can be realized by operating the part at a lower voltage. Compared to 3.3 V operation, a supply voltage of 1.8 V can result in power savings of ~45%. There is no performance penalty when operting at lower voltage. An initialization sequence is required to enable the AD8155 in a low power mode (see the Applications Information section).

A second measure is to disable transmitters when they are not being used. This can be done on a static basis if the output is not used or on a dynamic basis if the output does not have a constant stream of traffic. On transmit disable (Register 0x48, Register 0x88, Register 0xC8), both the predriver and output switch currents are disabled. The LOS-activated squelch disables only the output switch current,  $I_{\text{TOT}}$ . Superior power

saving is achieved by using the TX and RX disable registers to turn off an unused lane as opposed to relying on the AD8155 transmit squelch feature.

Because the majority of the power dissipated is in the output stage, some of its flexibility can be used to lower the power consumption. First, the output current and output preemphasis settings can be programmed to the smallest amount required to maintain BER performance. If an output circuit always has a short length and the receiver has good sensitivity, then a lower output current can be used.

It is also possible to lower the voltage on  $V_{\rm TTO}$  to lower the power dissipation. The amount that  $V_{\rm TTO}$  can be lowered is dependent on the lowest of all the output's  $V_{\rm OL}$  and  $V_{\rm CC}$ . This is determined by the output that is operating at the highest programmed output current. Table 1 and Table 19 list minimum output levels.

### I<sup>2</sup>C CONTROL INTERFACE

### SERIAL INTERFACE GENERAL FUNCTIONALITY

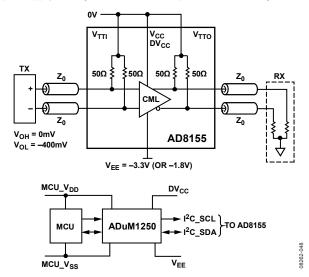

The AD8155 register set is controlled through a 2-wire I<sup>2</sup>C interface. The AD8155 acts only as an I<sup>2</sup>C slave device. The 7-bit slave address for the AD8155 I2C interface contains the static value b1010 for the upper four bits. The lower three bits are controlled by the input pins, I2C\_A[2:0].

Therefore, the I<sup>2</sup>C bus in the system must include an I<sup>2</sup>C master to configure the AD8155 and other I<sup>2</sup>C devices that may be on the bus. Data transfers are controlled through the use of the two I<sup>2</sup>C wires: the SCL input clock pin and the SDA bidirectional data pin.

The AD8155  $I^2C$  interface can be run in the standard (64 kHz) and fast (400 kHz) modes. The SDA line changes value only when the SCL pin is low, with two exceptions. To indicate the beginning or continuation of a transfer, the SDA pin is driven low while the SCL pin is high, and to indicate the end of a transfer, the SDA line is driven high while the SCL line is high. Therefore, it is important to control the SCL clock to toggle only when the SDA line is stable unless indicating a start, repeated start, or stop condition.

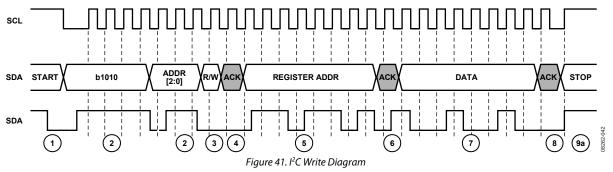

### I<sup>2</sup>C INTERFACE DATA TRANSFERS: DATA WRITE

To write data to the AD8155 register set, a microcontroller or any other I<sup>2</sup>C master must send the appropriate control signals to the AD8155 slave device. The following steps must be taken, where the signals are controlled by the I<sup>2</sup>C master, unless otherwise specified. For a diagram of the procedure, see Figure 41.

- Send a start condition (while holding the SCL line high, pull the SDA line low).

- 2. Send the AD8155 part address (seven bits) whose upper four bits are the static value b1010 and whose lower three bits are controlled by the I2C\_A[2:0] input pins. This transfer should be MSB first.

- 3. Send the write indicator bit (0).

- 4. Wait for the AD8155 to acknowledge the request.

- Send the register address (eight bits) to which data is to be written. This transfer should be MSB first.

- 6. Wait for the AD8155 to acknowledge the request.

- 7. Send the data (eight bits) to be written to the register whose address was set in Step 5. This transfer should be MSB first.

- 8. Wait for the AD8155 to acknowledge the request.

- 9. Do one or more of the following:

- Send a stop condition (while holding the SCL line high, pull the SDA line high) and release control of the bus.

- b. Send a repeated start condition (while holding the SCL line high, pull the SDA line low) and continue with Step 2 in this procedure to perform another write.

- c. Send a repeated start condition (while holding the SCL line high, pull the SDA line low) and continue with Step 2 of the read procedure (in the I<sup>2</sup>C Interface Data Transfers: Data Read section) to perform a read from another address.

- d. Send a repeated start condition (while holding the SCL line high, pull the SDA line low) and continue with Step 8 of the read procedure (in the I<sup>2</sup>C Interface Data Transfers: Data Read section) to perform a read from the same address set in Step 5.

In Figure 41, the AD8155 write process is shown. The SCL signal is shown along with a general write operation and a specific example. In this example, the value 0x92 is written to Address 0x6D of an AD8155 device with a part address of 0x53. The part address is seven bits wide and is composed of the AD8155 static upper four bits (b1010) and the pin-programmable lower three bits (I2C\_A[2:0]). The address pins are set to b011. In Figure 41, the corresponding step number is visible in the circle under the waveform. The SCL line is driven by the I<sup>2</sup>C master and never by the AD8155 slave. As for the SDA line, the data in the shaded polygons is driven by the AD8155, whereas the data in the nonshaded polygons is driven by the I<sup>2</sup>C master. The end phase case shown is that of Step 9a.

It is important to note that the SDA line changes only when the SCL line is low, except for the case of sending a start, stop, or repeated start condition (Step 1 and Step 9 in this case).

#### I<sup>2</sup>C INTERFACE DATA TRANSFERS: DATA READ

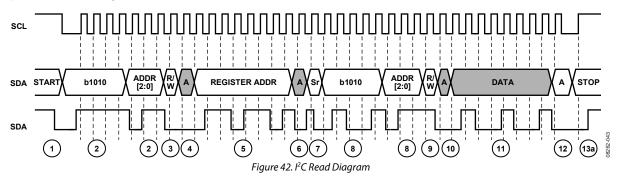

To read data from the AD8155 register set, a microcontroller or any other I<sup>2</sup>C master must send the appropriate control signals to the AD8155 slave device. The following steps must be taken, where the signals are controlled by the I<sup>2</sup>C master, unless otherwise specified. For a diagram of the procedure, see Figure 42.

- 1. Send a start condition (while holding the SCL line high, pull the SDA line low).

- Send the AD8155 part address (seven bits) whose upper four bits are the static value b1010 and whose lower three bits are controlled by the I2C\_A[2:0] input pins. This transfer should be MSB first.

- 3. Send the write indicator bit (0).

- 4. Wait for the AD8155 to acknowledge the request.

- 5. Send the register address (eight bits) from which data is to be read. This transfer should be MSB first. The register address is kept in memory in the AD8155 until the part is reset or the register address is written over with the same procedure (Step 1 to Step 6).

- 6. Wait for the AD8155 to acknowledge the request.

- 7. Send a repeated start condition (while holding the SCL line high, pull the SDA line low).

- 8. Send the AD8155 part address (seven bits) whose upper four bits are the static value b1010 and whose lower three bits are controlled by the I2C\_A[2:0] input pins. This transfer should be MSB first.

- 9. Send the read indicator bit (1).

- 10. Wait for the AD8155 to acknowledge the request.

- 11. The AD8155 then serially transfers the data (eight bits) held in the register indicated by the address set in Step 5.

- 12. Acknowledge the data.

- 13. Do one or more of the following:

- a. Send a stop condition (while holding the SCL line high, pull the SDA line high) and release control of the bus.

- Send a repeated start condition (while holding the SCL line high, pull the SDA line low) and continue with Step 2 of the write procedure (see the I<sup>2</sup>C Interface Data Transfers: Data Write section) to perform a write.

- c. Send a repeated start condition (while holding the SCL line high, pull the SDA line low) and continue with Step 2 of this procedure to perform a read from another address.

- d. Send a repeated start condition (while holding the SCL line high, pull the SDA line low) and continue with Step 8 of this procedure to perform a read from the same address.

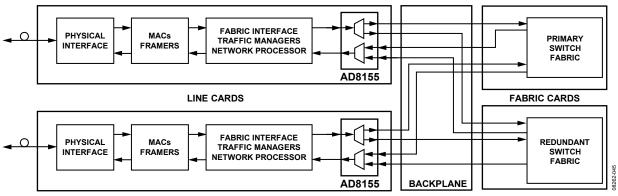

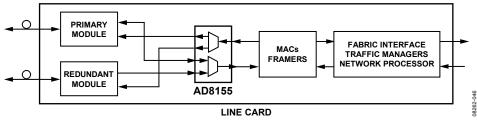

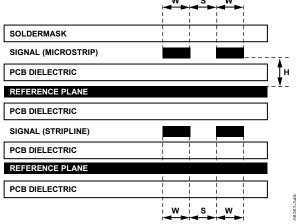

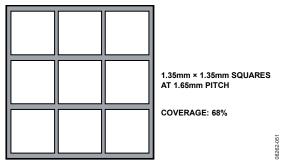

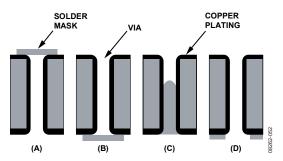

In Figure 42, the AD8155 read process is shown. The SCL signal is shown along with a general read operation and a specific example. In this example, the value 0x49 is read from Address 0x6D of an AD8155 device with a 0x53 part address. The part address is seven bits wide and is composed of the AD8155 static upper four bits (b1010) and the pin-programmable lower three bits (I2C\_A[2:0]). The address pins are set to b011. In Figure 42, the corresponding step number is visible in the circle under the waveform. The SCL line is driven by the I²C master and never by the AD8155 slave. As for the SDA line, the data in the shaded polygons is driven by the AD8155, whereas the data in the nonshaded polygons is driven by the I²C master. The end phase case shown is that of Step 13a.