# **ST-NXP Wireless**

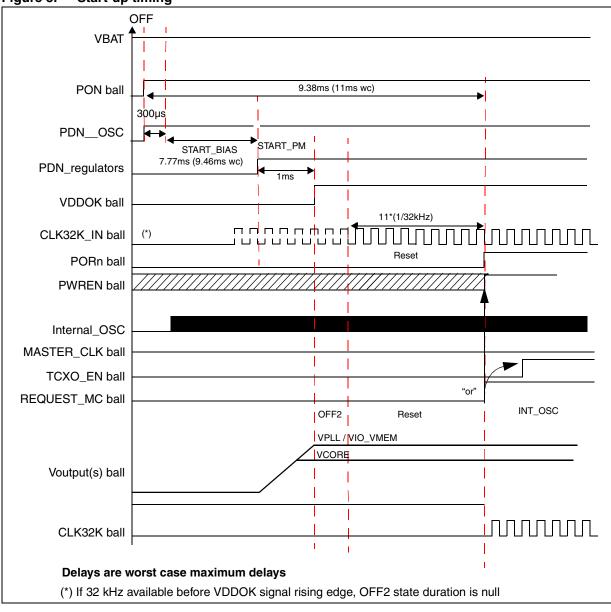

# STw4811M STw4811N

# Power management for multimedia processors

# Features

- 2 step-down converters

- 1 to 1.45 V with 15 steps at 700 mA

- 1.8 V at 600 mA for general purpose usage

- 3 low-drop output regulators for different uses

- PLL analog supplies:

1.05 V, 1.2 V, 1.3 V 1.8 V 10 mA

- Processor analog functions:

2.5 V 10 mA

- Auxiliary device:

- 1.5 V, 1.8V , 2.5 V, 2.8 V 150 mA

- USB OTG module

- Full and low speed USB OTG transceiver

- Charge-pump (5 V, 100 mA) for USB cable

- Mass memory cards (SD/MMC/SDIO)

- 1 linear regulator: 1.8 V, 1.85 V, 2.6 V,

2.7 V, 2.85 V, 3 V, 3.3 V 150 mA

- Level shifter

- Miscellaneous

- 32 kHz control for multimedia processor

- Processor supply monitoring

- Processor reset control

- 2 serial I2C interfaces

# Applications

- ST Nomadik<sup>TM</sup> STn881x

- Multimedia processor

- Mobile phones, PDA, videophone

# Description

STw4811 is a power management companion chip for multimedia processors used in portable applications. It supplies the multimedia processor including its memories and peripherals. STw4811 supports the main mass memory standard cards. SDIO<sup>TM</sup> is also supported and allows to connect multimedia peripherals like cameras.

1/85

# Contents

| 1 | Overv   | view      |                                                |

|---|---------|-----------|------------------------------------------------|

| 2 | Funct   | ional bl  | ock diagram                                    |

| 3 | Ball ir | nformati  | ion                                            |

|   | 3.1     | Ball con  | nections                                       |

|   | 3.2     | Ball fund | ctions                                         |

| 4 | Funct   | ional de  | escription                                     |

|   | 4.1     | Introduc  | tion                                           |

|   | 4.2     | Digital c | ontrol module                                  |

|   |         | 4.2.1     | State machine                                  |

|   |         | 4.2.2     | POWER OFF / VDDOK                              |

|   |         | 4.2.3     | Sleep mode                                     |

|   |         | 4.2.4     | I2C Interface                                  |

|   |         | 4.2.5     | Control registers                              |

|   |         | 4.2.6     | IT generation                                  |

|   |         | 4.2.7     | Clock switching and control                    |

|   | 4.3     | Power m   | nanagement module 40                           |

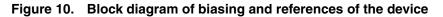

|   |         | 4.3.1     | Bandgap, biasing and references                |

|   |         | 4.3.2     | VCORE regulator: DC/DC STEP- DOWN regulator    |

|   |         | 4.3.3     | VIO_VMEM regulator: DC/DC step- down regulator |

|   |         | 4.3.4     | VPLL                                           |

|   |         | 4.3.5     | VANA                                           |

|   |         | 4.3.6     | VAUX                                           |

|   |         | 4.3.7     | Power supply monitoring                        |

|   |         | 4.3.8     | Power supply domains                           |

|   |         | 4.3.9     | Thermal shut-down                              |

|   | 4.4     | USB OT    | G module                                       |

|   |         | 4.4.1     | Block diagram                                  |

|   |         | 4.4.2     | Modes and operations                           |

|   |         | 4.4.3     | USB enable control                             |

|   | 4.5     | SD/MM     | C/SDIO module                                  |

|   |         | 4.5.1     | SD/MMC/SDIO LDO supply                         |

|   |      | 4.5.2     | Level shifters                                                   |

|---|------|-----------|------------------------------------------------------------------|

| 5 | Elec | trical ar | nd timing characteristics 56                                     |

|   | 5.1  | Absolu    | Ite maximum rating                                               |

|   | 5.2  | Packag    | ge dissipation                                                   |

|   | 5.3  | Power     | supply                                                           |

|   |      | 5.3.1     | Operating conditions                                             |

|   |      | 5.3.2     | VREF18                                                           |

|   |      | 5.3.3     | VCORE DC/DC step-down converter                                  |

|   |      | 5.3.4     | VIO_VMEM DC/DC step-down converter                               |

|   |      | 5.3.5     | LDO regulators61                                                 |

|   |      | 5.3.6     | Power supply monitoring64                                        |

|   | 5.4  | Digital   | specifications                                                   |

|   |      | 5.4.1     | CMOS input/output static characteristics: I2C interface          |

|   |      | 5.4.2     | CMOS input/output dynamic characteristics: I2C interface         |

|   |      | 5.4.3     | CMOS input/output static characteristics: VIO level              |

|   |      | 5.4.4     | CMOS input/output static characteristics: V <sub>BAT</sub> level |

|   |      | 5.4.5     | CMOS input/output static characteristics: VMMC level             |

|   | 5.5  | USB C     | OTG transceiver                                                  |

|   | 5.6  | SD/MN     | IC/SDIO card interface                                           |

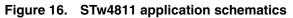

| 6 | Арр  | lication  | information                                                      |

|   | 6.1  | Compo     | onents list                                                      |

|   | 6.2  | Applica   | ation schematics                                                 |

| 7 | Pack | kage me   | chanical data                                                    |

|   | 7.1  | TFBG/     | A 84 balls                                                       |

|   | 7.2  | VFBG      | A 84 balls                                                       |

| 8 | Orde | ering inf | formation                                                        |

| 9 | Revi | sion his  | story                                                            |

# List of tables

| Table 1.  | STw4811 ball connections                                                  | . 10 |

|-----------|---------------------------------------------------------------------------|------|

| Table 2.  | STw4811 balls function.                                                   | . 11 |

| Table 3.  | Device ID                                                                 | . 21 |

| Table 4.  | Register address.                                                         | . 21 |

| Table 5.  | Register data                                                             | . 21 |

| Table 6.  | Register general information.                                             | . 22 |

| Table 7.  | Register summary                                                          | . 23 |

| Table 8.  | Power control register                                                    | . 23 |

| Table 9.  | USB register address                                                      | . 24 |

| Table 10. | Vendor ID and Product ID: Read only                                       | . 24 |

| Table 11. | USB control register 1 (address = 04h set and 05h clearh)                 | . 25 |

| Table 12. | USB control register 2 (address = 06h set and 07h clearh)                 | . 26 |

| Table 13. | USB Interrupt source register (address = 08h)                             |      |

| Table 14. | USB interrupt latch registers (address = 0Ah set and 0Bh clearh)          |      |

| Table 15. | USB interrupt enable low register (address = 0Ch and 0Dh)                 |      |

| Table 16. | USB interrupt enable high register (address = 0Eh and 0Fh)                |      |

| Table 17. | USB EN register (address = 10h)                                           |      |

| Table 18. | Configuration 1 register (11h).                                           |      |

| Table 19. | Power control register - General information (address = 1Eh)              |      |

| Table 20. | Power control register - General information (address = 1Fh)              |      |

| Table 21. | Power control register mapping                                            |      |

| Table 22. | Power control register at address 05h                                     |      |

| Table 23. | Power control register at address 06h                                     |      |

| Table 24. | Power control register at address 07h                                     |      |

| Table 25. | Power control register at address 08h                                     |      |

| Table 26. | Power control register at address 09h                                     |      |

| Table 27. | Power control register at address 0Ah                                     |      |

| Table 28. | Configuration 2 register at address = 20h                                 |      |

| Table 29. | VCORE_sleep register at address = 21h                                     |      |

| Table 30. | Power supply domains                                                      |      |

| Table 31. | Thermal threshold values                                                  |      |

| Table 32. | Data transmission via USB control register 1 (DAT_SE0 mode) - Suspend = 0 |      |

| Table 33. | Data transmission via USB control register 1 (DAT_SE0 mode) - Suspend = 1 |      |

| Table 34. | Data receiver via USB control register 1                                  |      |

| Table 35. | STw4811 absolute maximum ratings                                          |      |

| Table 36. | Package dissipation                                                       |      |

| Table 37. | Operating conditions (temperature range: -30 to +85 °C)                   |      |

| Table 38. | VREF18                                                                    |      |

| Table 39. | VCORE DC/DC step-down converter                                           | . 58 |

| Table 40. | VIO_VMEM DC/DC step-down converter.                                       |      |

| Table 41. | LDO regulators - VPLL                                                     |      |

| Table 42. | LDO regulators - VANA                                                     |      |

| Table 43. | LDO regulators - VAUX                                                     |      |

| Table 44. | Power supply monitoring                                                   |      |

| Table 45. | CMOS input/output static characteristics: I <sup>2</sup> C interface      |      |

| Table 46. | CMOS input/output dynamic characteristics: I <sup>2</sup> C interface     |      |

| Table 47. | VIO level: USB and control I/Os                                           | . 66 |

| Table 48. | VIO level: MMC interface                                                  |      |

|           |                                                                           |      |

| Table 49. | CMOS input/output static characteristics: VBAT level           | 68 |

|-----------|----------------------------------------------------------------|----|

| Table 50. | CMOS input/output static characteristics VMMC level            | 69 |

| Table 51. | USB OTG transceiver                                            | 70 |

| Table 52. | SD/MMC/SDIO card interface.                                    | 73 |

| Table 53. | Components list                                                | 76 |

| Table 54. | Recommended coils                                              | 76 |

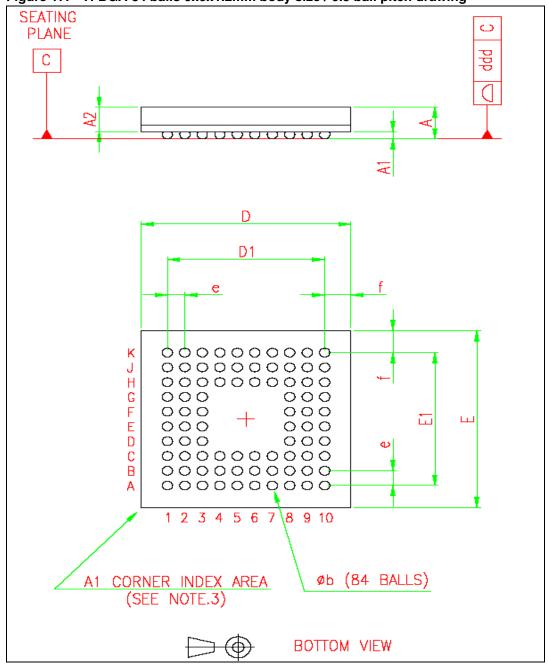

| Table 56. | TFBGA 84 balls 6x6x1.2mm body size / 0.5 ball pitch dimensions | 79 |

| Table 57. | VFBGA 84 balls / 4.6x4.6x1.0 mm body size / 0.4 mm ball pitch  | 81 |

| Table 58. | Order codes                                                    | 83 |

| Table 59. | Document revision history                                      | 84 |

# List of figures

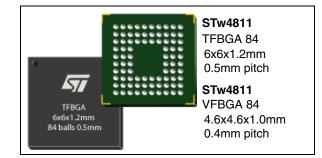

| Figure 1.  | Typical mobile multimedia system                                |

|------------|-----------------------------------------------------------------|

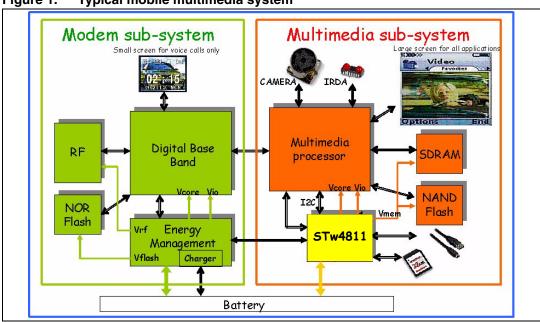

| Figure 2.  | STw4811 block diagram                                           |

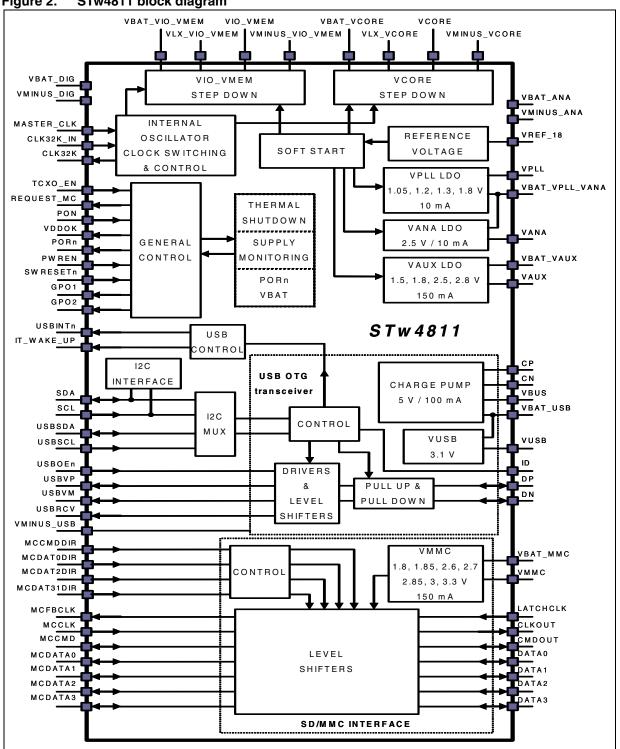

| Figure 3.  | Start-up timing                                                 |

| Figure 4.  | Switching power to sleep timing                                 |

| Figure 5.  | VDDOK block diagram                                             |

| Figure 6.  | I2C interface block diagram 20                                  |

| Figure 7.  | Control interface: I2C format                                   |

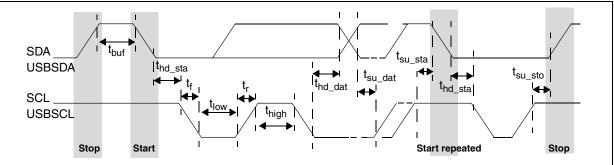

| Figure 8.  | Control interface: I2C timing                                   |

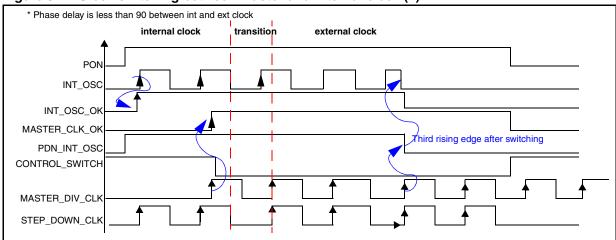

| Figure 9.  | Clock switching between master and internal clock (1)           |

| Figure 10. | Block diagram of biasing and references of the device           |

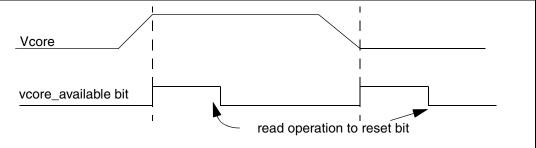

| Figure 11. | 'vcore_available' bit behavior                                  |

| Figure 12. | Thermal threshold temperatures for 'it_warn' bit and VDDOK ball |

| Figure 13. | USB OTG transceiver block diagram 46                            |

| Figure 14. | SD/MMC/SDIO block diagram                                       |

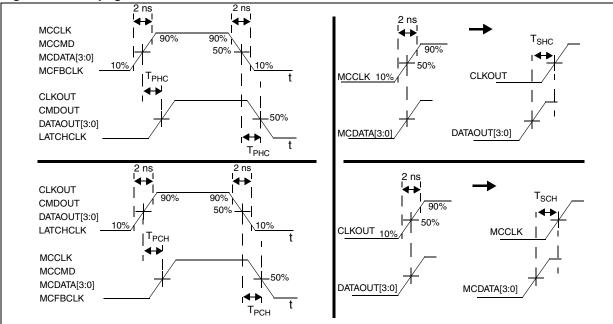

| Figure 15. | Propagation and clock/data skew times                           |

| Figure 16. | STw4811 application schematics                                  |

| Figure 17. | TFBGA 84 balls 6x6x1.2mm body size / 0.5 ball pitch drawing     |

| Figure 18. | VFBGA 84 balls 4.6x4.6x1.0 mm ball pitch 0.4 drawing82          |

|            |                                                                 |

# 1 Overview

The STw4811 power management device has the following features:

- Power management module

- 1 step-down converter for processor core (1 V to 1.45 V with 15 steps at 700 mA)

- 1 step-down converter (1.8 V at 600 mA) for general purpose usage such as processor input/output supply, external memory, DDR and SDRAM and peripherals

- 1 low-drop output regulator for analog supplies, such as PLL (1.05 V, 1.2 V, 1.3 V, 1.8 V at 10 mA)

- 1 low-drop output regulator for processor analog functions (2.5 V at 10 mA)

- 1 low-drop output regulator for auxiliary devices (1.5 V, 1.8 V, 2.5 V, 2.8 V at 150 mA)

- Auxiliary device

- STw4811M: Vaux OFF at start up

- STw4811N: Vaux ON at start up

- USB OTG module

- Full and low speed USB OTG transceiver

- 1 linear regulator 3.1 V supplying transceiver

- 1 charge-pump (5 V at 100 mA) supplying VBUS line of the USB cable

- Mass memory cards (SD/MMC/SDIO)

- 1 linear regulator (1.8 V, 1.85 V, 2.6 V, 2.7 V, 2.85 V, 3 V, 3.3 V at 150 mA)

- Level shifters

- Miscellaneous

- 32 kHz control for multimedia processor

- Processor supply monitoring

- Processor reset control

- 2 serial I2C interfaces

Figure 1. Typical mobile multimedia system

8/85

#### **Functional block diagram** 2

#### Figure 2. STw4811 block diagram

# **3** Ball information

# 3.1 Ball connections

|   | 1              | 2                   | 3                   | 4                 | 5              | 6             | 7                 | 8             | 9                | 10               |

|---|----------------|---------------------|---------------------|-------------------|----------------|---------------|-------------------|---------------|------------------|------------------|

| Α | CLK32K_IN      | VMINUS_<br>VIO_VMEM | VLX_VIO_<br>VMEM    | VBAT_VIO_<br>VMEM | VIO_VMEM       | VAUX          | VANA              | VPLL          | VREF_18          | VCORE            |

| в | "Reserved"     | REQUEST_<br>MC      | VMINUS_<br>VIO_VMEM | VBAT_VIO_<br>VMEM | VMINUS_<br>ANA | VBAT_<br>VAUX | "Reserved"        | "Reserved"    | "Reserved"       | VMINUS_<br>VCORE |

| с | TCXO_EN        | IT_WAKE_<br>UP      | VMINUS_<br>DIG      | VLX_VIO_<br>VMEM  | "Reserved"     | VBAT_ANA      | VBAT_<br>VPLL_ANA | PON           | VMINUS_<br>VCORE | VLX_<br>VCORE    |

| D | VBAT_DIG       | MASTER_<br>CLK      | "reserved"          |                   |                |               |                   | VLX_<br>VCORE | VBAT_<br>VCORE   | VBAT_<br>VCORE   |

| E | DATAOUT0       | DATAOUT<br><1>      | DATAOUT<br><2>      |                   |                |               |                   | ID            | DP               | DN               |

| F | DATAOUT<br><3> | CMDOUT              | LATCHCLK            |                   |                |               |                   | "Reserved"    | VBAT_USB         | VUSB             |

| G | CLKOUT         | MCCLK               | MCCMD<br>DIR        |                   |                |               |                   | "Reserved"    | USBSCL           | VBUS             |

| н | MCCMD          | MCDATA<br><3>       | MCDATA<br><1>       | MCDATA31<br>DIR   | MCFBCLK        | PWREN         | SDA               | USBINTn       | USBSDA           | СР               |

| J | MCDATA<br><2>  | VDDOK               | PORN                | VBAT_<br>MMC      | GPO1           | SCL           | USBVP             | USBVM         | VMINUS_<br>USB   | CN               |

| к | MCDATA0        | MCDAT0<br>DIR       | CLK32K              | SW_<br>RESET      | VMMC           | GPO2          | USBRCV            | USBOEn        | MCDAT2<br>DIR    | "Reserved"       |

# Table 1. STw4811 ball connections

# 3.2 Ball functions

STw4811 includes the following ball types

- VDDD/VDDA: digital/analog power supply

- VSSD/VSSA: digital/analog ground supply

- DO/DI/DIO: digital output / digital input / digital input output

- DOz: digital output with high impedance capability

- AO/AI/AIO: analog output / analog input / analog input-output

- G: to be connected to ground

- O: to be left open

- Int-Ref: associated to internal reference

Table 2 details the ballout.

| Ball      | Ball name  | Ball type                           | Description                                                                                                                   |  |  |  |

|-----------|------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| General s | supplies   |                                     |                                                                                                                               |  |  |  |

| D1        | VBAT_DIG   | VDDD-VBAT                           | Battery supply for digital/oscillator                                                                                         |  |  |  |

| C3        | VMINUS_DIG | VSSD                                | Ground for digital and oscillator                                                                                             |  |  |  |

| C6        | VBAT_ANA   | VDDA-VBAT                           | Battery supply for analog                                                                                                     |  |  |  |

| B5        | VMINUS_ANA | VSSA                                | Ground for analog                                                                                                             |  |  |  |

| F9        | VBAT_USB   | VDDA-VBAT                           | Battery supply for USB block                                                                                                  |  |  |  |

| J9        | VMINUS_USB | VSSA                                | Ground for USB block                                                                                                          |  |  |  |

| A9        | VREF_18    | Int-Ref                             | Internal reference                                                                                                            |  |  |  |

| Control b | alls       |                                     |                                                                                                                               |  |  |  |

| C8        | PON        | DI(VBAT)<br>Pull down 1.5M $\Omega$ | Power-on and reset                                                                                                            |  |  |  |

| K4        | SW_RESETn  | DI(VIO_VMEM)<br>Pull up 1.5MΩ       | Software reset. Reset all registers except<br>power control and configuration 2 (address<br>20h) registers when SW_RESETn = 0 |  |  |  |

| J2        | VDDOK      | DO(VIO_VMEM)                        | Supply monitoring for multimedia processors.<br>Interruption for high temperature warning                                     |  |  |  |

| J3        | PORn       | DO(VIO_VMEM)                        | Multimedia processor Resetn                                                                                                   |  |  |  |

| H6        | PWREN      | DI(VIO_VMEM)<br>Pull Up 1.5MΩ       | Sleep mode from multimedia processor                                                                                          |  |  |  |

| C1        | TCXO_EN    | DI(VIO_VMEM)<br>Pull Down 1.5MΩ     | Request of master clock from modem part                                                                                       |  |  |  |

| B2        | REQUEST_MC | DO(VIO_VMEM)                        | Request to master clock oscillator                                                                                            |  |  |  |

| J6        | SCL        | DI(VIO_VMEM)                        | Clock for Main I2C interface                                                                                                  |  |  |  |

| H7        | SDA        | DIO(VIO_VMEM)                       | SDA for Main I2C interface                                                                                                    |  |  |  |

| D2        | MASTER_CLK | Al Pull Down 1.5M $\Omega$          | 26 MHz, 13 MHz or 19.2 MHz from modem                                                                                         |  |  |  |

| A1        | CLK32K_IN  | DI(VIO_VMEM)<br>Pull down 1.5MΩ     | 32 kHz input                                                                                                                  |  |  |  |

| K3        | CLK32K     | DO(VIO_VMEM)                        | 32 kHz to multimedia processor                                                                                                |  |  |  |

### Table 2.STw4811 balls function

| Table 2.<br>Ball | STw4811 balls func<br>Ball name | Ball type                        | Description                                                                                                                            |

|------------------|---------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

|                  |                                 | Ball type                        | Description                                                                                                                            |

| General s        | supplies                        |                                  |                                                                                                                                        |

| Regulato         | r balls                         |                                  |                                                                                                                                        |

| A4<br>B4         | VBAT_VIO_VMEM                   | VDDA-VBAT                        | Battery power supply for step down VIO_VMEM                                                                                            |

| A2<br>B3         | VMINUS_VIO_VMEM                 | VSSA                             | Ground for step down VIO_VMEM                                                                                                          |

| A3<br>C4         | VLX_VIO_VMEM                    | AIO                              | BUCK of step down VIO_VMEM                                                                                                             |

| A5               | VIO_VMEM                        | AI                               | VIO_VMEM Feed back input                                                                                                               |

| D9<br>D10        | VBAT_VCORE                      | VDDA-VBAT                        | Battery power supply for step down VCORE                                                                                               |

| B10<br>C9        | VMINUS_VCORE                    | VSSA                             | Ground for step down VCORE                                                                                                             |

| C10<br>D8        | VLX_VCORE                       | AIO                              | BUCK of step-down VCORE                                                                                                                |

| A10              | VCORE                           | AI                               | VCORE sense                                                                                                                            |

| C7               | VBAT_VPLL_ANA                   | VDDA-VBAT                        | Battery supply for VPLL, VANA                                                                                                          |

| A7               | VANA                            | AO                               | VANA output                                                                                                                            |

| A8               | VPLL                            | AO                               | VPLL output                                                                                                                            |

| A6               | VAUX                            | AO                               | VAUX output                                                                                                                            |

| B6               | VBAT_VAUX                       | VDDA-VBAT                        | Battery supply for VAUX                                                                                                                |

| USB balls        | 5                               |                                  |                                                                                                                                        |

| C2               | IT_WAKE_UP                      | DO (Open drain)                  | Interrupt to modem or APE for wake-up due to USB plug                                                                                  |

| К8               | USBOEn                          | DIO(VIO_VMEM)<br>Pull down 1.5MΩ | Output enable of the differential driver in the USB mode                                                                               |

| J7               | USBVP                           | DIO(VIO_VMEM)<br>Pull down 1.5MΩ | Data input in the USB transmit mode, positive<br>data input the single-ended transmit mode, or<br>TXD in UART mode                     |

| J8               | USBVM                           | DIO(VIO_VMEM)<br>Pull Down 1.5MΩ | Single-ended zero input in the USB transmit<br>mode, negative data input in the single-ended<br>transmit mode, or RXD in the UART mode |

| K7               | USBRCV                          | DO(VIO_VMEM)                     | Differential receiver output                                                                                                           |

| E9               | DP                              | AIO(VUSB)                        | Positive data line in the USB mode, or serial data input in the UART mode                                                              |

| E10              | DN                              | AIO(VUSB)                        | Negative data line in the USB mode, or serial data output in the UART mode.                                                            |

| E8               | ID                              | AI(VBAT-USB)                     | ID ball of the USB detector used for protocol identification.                                                                          |

# Table 2. STw4811 balls function (continued)

12/85

| Ball           | STw4811 balls fur<br>Ball name | Ball type                           | Description                                                                                                                        |  |  |  |

|----------------|--------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| General        |                                |                                     |                                                                                                                                    |  |  |  |

| H10            | СР                             | AIO(VBUS)                           | C plus flying capacitor<br>(VBUS level 4.4 to 5.25)                                                                                |  |  |  |

| J10            | CN                             | AIO(VBUS)                           | C minus flying capacitor (VBUS Level)                                                                                              |  |  |  |

| G10            | VBUS                           | AIO(VBUS)                           | USB cable supply (VBUS Level)                                                                                                      |  |  |  |

| F10            | VUSB                           | AIO                                 | Decoupling capacitor for USB internal regulator                                                                                    |  |  |  |

| G9             | USBSCL                         | DI(VIO_VMEM)                        | Clock for dedicated USB I2C                                                                                                        |  |  |  |

| H9             | USBSDA                         | DIO(VIO_VMEM)                       | SDA for dedicated USB I2C                                                                                                          |  |  |  |

| H8             | USBINTn                        | DO(VIO_VMEM)                        | Interrupt to multimedia processor for USB or accessory plug                                                                        |  |  |  |

| SD/MMC/        | SDIO balls                     | ·                                   |                                                                                                                                    |  |  |  |

| G3             | MCCMDDIR                       | DI(VIO_VMEM)<br>Pull down 1.5MΩ     | CMD direction.<br>- "high": CMD signal from processor to card<br>- "Low": CMD signal from card to processor                        |  |  |  |

| K2             | MCDAT0DIR                      | DI(VIO_VMEM)<br>Pull down 1.5MΩ     | DATA0 direction<br>- "high": DATA0 signal from processor to card<br>- "Low": DATA0 signal from card to processor                   |  |  |  |

| K9             | MCDAT2DIR                      | DI(VIO_VMEM)<br>Pull down 1.5MΩ     | DATA2 direction<br>- "high": DATA2 signal from processor to card<br>- "Low": DATA2 signal from card to processor                   |  |  |  |

| H4             | MCDAT31DIR                     | DI(VIO_VMEM)<br>Pull down 1.5MΩ     | DATA(3,1) direction<br>- "high": DATA(3,1) signal from processor to<br>card<br>- "Low": DATA(3,1) signal from card to<br>processor |  |  |  |

| G2             | MCCLK                          | DI(VIO_VMEM)<br>Pull Down 1.5MΩ     | Host clock, between processor and STw4811, to the card (processor clock).                                                          |  |  |  |

| H5             | MCFBCLK                        | DO(VIO_VMEM)                        | Host feedback clock between STw4811 and processor, to re-synchronize data in processor.                                            |  |  |  |

| H1             | MCCMD                          | DIO(VIO_VMEM)<br>Pull Up 1.5MΩ      | Bidirectional command/response signal between processor and STw4811.                                                               |  |  |  |

| K1             | MCDATA0                        | DIO(VIO_VMEM)<br>Pull Up1.5MΩ       | Bidirectional data0 between processor and STw4811                                                                                  |  |  |  |

| H2<br>H3<br>J1 | MCDATA[3:1]                    | DIO(VIO_VMEM)<br>Pull up 1.5MΩ      | Bidirectional data [3:1] between processor and STw4811.                                                                            |  |  |  |

| F3             | LATCHCLK                       | DI(VMMC)<br>Pull down 1.5M $\Omega$ | Host feedback clock to STw4811, to re-<br>synchronize data in processor.                                                           |  |  |  |

| G1             | CLKOUT                         | DO(VMMC)                            | Host clock, between STw4811 and card (processor clock).                                                                            |  |  |  |

| F2             | CMDOUT                         | DIO(VMMC)<br>Pull up 1.5MΩ          | Bidirectional command/response signal between STw4811 and processor.                                                               |  |  |  |

# Table 2. STw4811 balls function (continued)

| Ball                                    | Ball name                   | Ball type                  | Description                                       |

|-----------------------------------------|-----------------------------|----------------------------|---------------------------------------------------|

| General s                               | supplies                    |                            |                                                   |

| E1                                      | DATAOUT0                    | DIO(VMMC)<br>Pull up 1.5MΩ | Bidirectional data0 between STw4811 and card      |

| F1<br>E3<br>E2                          | DATAOUT[3:1]                | DIO(VMMC)<br>Pull up 1.5MΩ | Bidirectional data[3:1] between STw4811 and card. |

| J4                                      | VBAT_MMC                    | VDDA-VBAT                  | Battery supply for VMMC                           |

| K5                                      | VMMC AIO VMMC supply output |                            | VMMC supply output                                |

| Other bal                               | ls                          |                            |                                                   |

| J5                                      | GPO1                        | AO                         | General purpose output                            |

| K6                                      | GPO2                        | AO                         | General purpose output                            |

| B9<br>D3                                | "Reserved"                  | G                          | To be connected to ground                         |

| B1<br>B7<br>B8<br>C5<br>F8<br>G8<br>K10 | "Reserved"                  | 0                          | To be left open                                   |

|--|

14/85

# 4 **Functional description**

# 4.1 Introduction

The STw4811 integrates all the power supplies for a multimedia processor as well as memories and peripherals:

- Two switched mode power supply regulators: one for the multimedia processor core, one for multimedia processor I/Os and memories

- Three low-drop output regulators for multimedia processor analog supplies (PLL and others) and auxiliary components

- USB OTG FS/LS physical interface

- MMC card power supplies and level shifters

- Multimedia processor supply monitoring / power-on reset and power supply alarms / interrupt management

- Two serial I2C communication interfaces; one to control the devices (SDA, SCL) and one to control the USB (USBSDA, USBSCL).

# 4.2 Digital control module

This module describes the interfaces used to program the device and the related registers.

# 4.2.1 State machine

Description of each states: (*Figure 3.*)

**OFF:** In this mode the STw4811 is switched off. Off is when PON=0, when battery level is under 2.4 V or when thermal shutdown is activated. There is no multimedia processor power supply. The only active cell is the USB cable detection and  $V_{BAT}$  level detection.

**OSC\_START:** Oscillator is enabled and the power up module is waiting for the rising edge of the internal signal OSC\_OK to start power up sequence. This state duration is  $300 \ \mu$ s.

**START\_BIAS:** Bias, reference and thermal shut-down are enabled, a counter is activated to wait for rising edge of internal signals PDN\_regulators. This state duration has a typical value of 7.77 ms and a worst case value of 9.46 ms.

**START\_PM:** after a 1 ms wait, multimedia processor power supplies are available (VIO\_VMEM, VCORE, VPLL, and VANA). The device can allow I2C communication, output power supply monitoring and application (USB,SD/MMC/SDIO).

**OFF2:** STw4811 is waiting for the 32 kHz multimedia processor signal. This state has an indeterminate duration. If 32kHz is present during the states describes above, it has no effect. The 32 kHz signal is taken into account by STw4811 only when the 'VDDOK' ball is high, that is at the end of START\_PM state.

**RESET:** STw4811 forces a reset during 11\*1/32 kHz period before setting PORn high.

**INT\_OSC:** The STw4811 can work without MASTER\_CLK via its internal oscillator. The device waits for an external clock detection before switching to the external clock. When receiving a rising edge on PWREN ball (coming from multimedia processor) or on TCXO\_EN ball (coming from modem), STw4811 answers by asserting to "1" the

REQUEST\_MC ball. STw4811 remains in internal oscillator mode until it receives the external clock signal on MASTER\_CLK ball (optional).

**EXT\_CLK:** if MASTER\_CLK is used, when detected, the STw4811 uses this clock as reference and switches off its internal oscillator. MASTERCLK should remain connected up to sleep mode.

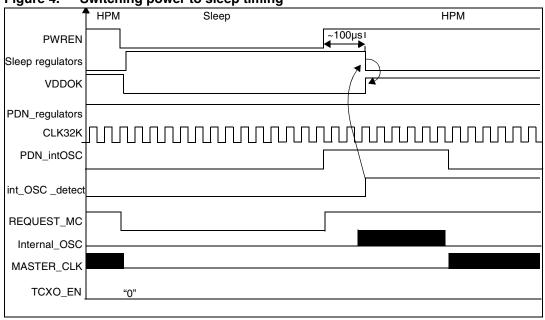

**SLEEP:** sleep mode is required by multimedia processor by setting a PWREN at low level. Then VDDOK is forced to 0, regulators (VCORE, VIO\_VMEM) switch to sleep mode and wait for PWREN at high level (*Figure 4*).

**WAKE-UP:** from sleep mode, the multimedia processor requests to switch back to high power mode. Thus the device restarts its internal oscillator and then switches regulators from SLEEP to high power mode and informs multimedia processor with VDDOK at high level (*Figure 4*).

Note:

The default state of VAUX is different for STw4811M and for STw4811N.

- VAUX default state is OFF at start up for STw4811M.

- VAUX default state is ON at start up for STw4811N.

VAUX can be programmed in high power mode only by asserted pdn\_vaux bit to "1" (Table 18).

If MASTER\_CLK is used instead of internal oscillator all the features are not supported in sleep mode (see Section 4.2.3).

Figure 3. Start-up timing

All regulators are started with PDN\_regulators or EN\_regulators but can be switched off from the beginning or during application by software, 'pdn\_(regulator)' or 'en\_(regulator)' bits (*Table 18, Table 24*, and *Table 25*).

Figure 4. Switching power to sleep timing

# **Register reset**

In the event of a hardware reset coming from the modem, PON ball set to "0", all registers are reset at initial value when PON ball goes back to "1" level.

A software reset from multimedia processor of STw4811, through SW\_RESETn ball set to "0", resets all registers except power control register (at address 1E & 1F) and the configuration 2 register at address 20h.

#### Main clock oscillator control

REQUEST\_MC is an OR output gate between PWREN (coming from multimedia processor) and TCXO\_EN (coming from modem supply), it is synchronized on 32 kHz, except during power-up where PWREN is masked and considered as high.

REQUEST\_MC enabled or disabled the master clock oscillator device.

18/85

# 4.2.2 POWER OFF / VDDOK

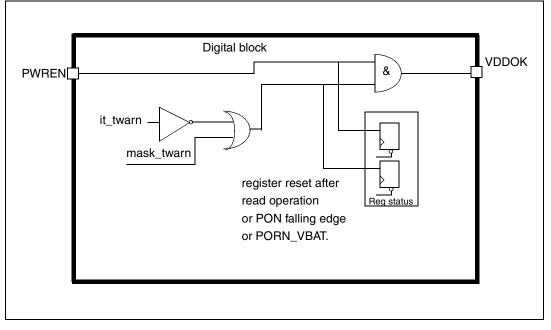

- In case of VDDOK falling edge due to under voltage on VCORE or VIO\_VMEM detection, or 'it\_twarn' bit set to "1" (*Table 18*); the multimedia processor is then reset (PORn low during a minimum time of 333 µs) and restarted with no time-out. (see *Figure 5*). In case of VDDOK falling edge because PWREN balls equals "0", there is no reset (PORn still high).

- In case of PON falling edge (STw4811 switched off from modem); the multimedia processor is also reset with no time-out. We consider that clean switch off between modem and multimedia processor is done by software directly.

# 4.2.3 Sleep mode

STw4811 goes into sleep mode by different ways. Whether VCORE, VIO\_VMEM and VAUX are programmed to sleep mode or not is indicated in *Table 26* and *Table 27*.

Taking in account the bit programming from *Table 26* and *Table 27*, sleep mode is summarized with the following formula:

SLEEP = ('vxxx\_sleep' x PWREN) + ('vxxx\_force\_sleep') = 1 (vxxx = vcore or vio\_vmem or vaux)

Note: The configuration vxxx\_sleep = 0 (device in active mode) and vxxx\_force\_sleep = 1 (device in sleep mode, but no priority level on this bit) is forbidden.

If the master clock is used in high power mode when switching to sleep mode, the following features are not available:

Bit 1 (vcore\_sleep) and bit 2 (vio\_vmem\_sleep) in power control register address 9 must be at high level

(VIO\_VMEM and VCORE cannot remain in high power mode)

USB charge pump is not available in sleep mode: bit 5 in USB control register address 07h must be set

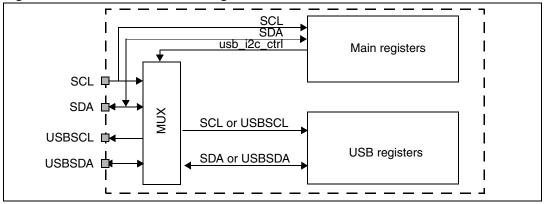

# 4.2.4 I2C Interface

The device supports two I2C bus interfaces. One main interface (SDA,SCL) controls power management and all programmable functions, the second interface (USBSDA, USBSCL) is dedicated to USB control. STw4811 allows to work with only the main I2C interface to control all the functions, including the USB, via 'usb\_i2c\_ctrl' bit of *power control* register (*Table 23*). I2C interface is used to read status information from inside the device.

*Flags, interrupt* and *write* registers are used to configure the device functions (threshold, clock division, output voltage, etc....). By default, the main I2C interface (SCL,SDA) controls the main registers and USB I2C interface (USBSCL, USBSDA) controls *USB* registers.

Figure 6. I2C interface block diagram

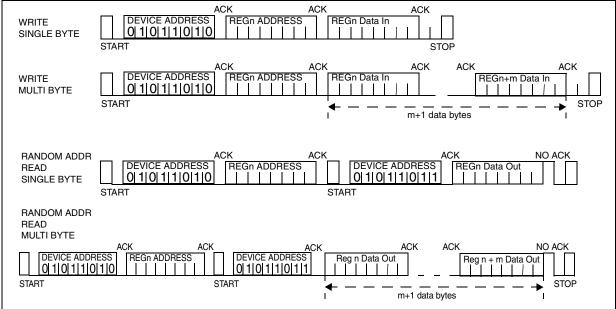

Both I2C are configured as slave serial interface compatible with I2C registered trademark of Phillips Inc. (version 2.1).

### I2C interface description

Note: When not using the USB I2C interface, the two pins USBSCL and USCSDA must be connected to the VIO voltage.

STw4811 I2C is a slave serial interface with a serial data line (SDA or USBSDA) and a serial clock line (SCL or USBSCL):

- SCL / USBSCL: input clock used to shift data

- SDA / USBSDA: input/output bidirectional data transfers

It is composed of:

- One filter to reject spikes on the bus data line and preserve data integrity

- Bidirectional data transfers up to 400kbit/s (fast mode) via SDA or USBSDA signal

The SDA or USBSDA signal contains the input/output control and data signals that are shifted in the device, MSB first. The first bit must be high (START) followed by the Device ID (7 bits) and Read/Write bit control (1 indicates read access, a logical 0 indicates a write access).

- Device ID in write mode: 5Ah (01011010)

- Device ID in read mode: 5Bh (01011011)

Then STw4811 sends an acknowledge at the end of an 8 bit transfer. The next 8 bits correspond to the register address followed by another acknowledge. The 8-bit data field is sent last, followed by a last acknowledge.

#### Table 3. **Device ID** b7 b6 b5 b4 b3 b2 b1 b0 AdrID6 AdrID5 AdrID4 AdrID3 AdrID2 AdrID1 AdrID0 R/W

# Table 4. Register address

| b7      | b6      | b5      | b4      | b3      | b2      | b1      | b0      |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RegADR7 | RegADR6 | RegADR5 | RegADR4 | RegADR3 | RegADR2 | RegADR1 | RegADR0 |

#### Table 5. Register data

| b7    | b6    | b5    | b4    | b3    | b2    | b1    | b0    |

|-------|-------|-------|-------|-------|-------|-------|-------|

| DATA7 | DATA6 | DATA5 | DATA4 | DATA3 | DATA2 | DATA1 | DATA0 |

#### **I2C** interface modes

# Figure 7. Control interface: I2C format

### Figure 8. Control interface: I2C timing

# 4.2.5 Control registers

Control registers have the following functions:

- select level of regulation for multimedia processor supply

- control the USB interface

- control the SD/MMC/SDIO interface

- control the state machine

#### Table 6. Register general information

| Address    | Comment                                        | I2C control                                 |

|------------|------------------------------------------------|---------------------------------------------|

| 00h to 10h | USB registers (Table 9 to Table 17)            | USBSDA / USBSCL or SDA / SCL <sup>(1)</sup> |

| 11h        | Configuration 1 register (Table 18)            | SDA / SCL                                   |

| 12h to 1Dh | Reserved registers                             |                                             |

| 1Eh to 1Fh | Power control registers (Table 19 to Table 27) | SDA / SCL                                   |

| 20h        | Configuration 2 register (Table 28)            | SDA / SCL                                   |

| 21h        | VCORE_sleep (Table 29)                         | SDA/SCL                                     |

1. Controlled by USB\_I2C\_CTRL bit of *power control* register (*Table 23*)

# **Register summary**

| Table 7. | Register summary |

|----------|------------------|

|          |                  |

| Register                    | Addr.      | 7             | 6                | 5                                                               | 4                | 3                 | 2                 | 1              | 0             |

|-----------------------------|------------|---------------|------------------|-----------------------------------------------------------------|------------------|-------------------|-------------------|----------------|---------------|

| Vendor ID                   | 00h        | 1             | 0                | 0                                                               | 0                | 0                 | 0                 | 1              | 1             |

| Vendorind                   | 01h        | 0             | 0                | 0                                                               | 0                | 0                 | 1                 | 0              | 0             |

| Product ID                  | 02h        | 0             | 0                | 0                                                               | 1                | 0                 | 0                 | 0              | 1             |

| Tioddelib                   | 03h        | 0             | 1                | 0                                                               | 0                | 0                 | 0                 | 0              | 0             |

| USB control register 1      | 04h<br>05h | Not used      | uart_en          | oe_int_en                                                       | bdis_<br>acon_en | not used          | dat_se0           | suspend        | speed         |

| USB control<br>register 2   | 06h<br>07h | vbus_<br>chrg | vbus_<br>dischrg | vbus_<br>drv                                                    | id_gnd           | dn_<br>pulldown   | dp_<br>pulldown   | dn_<br>pullup  | dp_<br>pullup |

| USB interrupt source        | 08h        | cr_int        | bdis_<br>acon    | id_float                                                        | dn_hi            | id_gnd_<br>forced | dp_hi             | sess_vld       | vbus_vld      |

| USB interrupt<br>latch      | 0Ah<br>0Bh | cr_int        | bdis_<br>acon    | id_float                                                        | dn_hi            | id_gnd_<br>forced | dp_hi             | sess_vld       | vbus_vld      |

| USB interrupt<br>mask false | 0Ch<br>0Dh | cr_int        | bdis_<br>acon    | id_float                                                        | dn_hi            | id_gnd_<br>forced | dp_hi             | sess_vld       | vbus_vld      |

| USB interrupt<br>mask true  | 0Eh<br>0Fh | cr_int        | bdis_<br>acon    | id_float                                                        | dn_hi            | id_gnd_<br>forced | dp_hi             | sess_vld       | vbus_vld      |

| USB EN                      | 10h        | Not used      | B_sess_<br>end   | Not used                                                        |                  |                   | th_<br>Bdevice    | usb_en         | not used      |

| Configuration 1             | 11h        | pdn_<br>vaux  | it_warn          | monitoring<br>vio mmc_ls_<br>vmem status<br>vcore vmmc_sel[2:0] |                  |                   |                   | pdn_<br>vmmc   |               |

| Configuration 2             | 20h        | not used      |                  | not used                                                        |                  |                   | external_<br>vmmc | mask_<br>twarn |               |

| Vcore_Sleep                 | 21h        | not used      |                  | vcore_<br>available vcore_sleep[3:0]                            |                  |                   |                   |                |               |

# Table 8.Power control register

| Addr. | 15  | 14          | 13   | 12 | 11         | 10          | 9 | 8          |

|-------|-----|-------------|------|----|------------|-------------|---|------------|

| 1Fh   |     | Not used    |      |    |            |             |   | ess 2 bits |

| Addr. | 7   | 7 6 5 4 3 2 |      |    |            |             |   |            |

| 1 Eh  | reg | address 3   | bits |    | data din/o | lout 4 bits |   | ena write  |

## Registers controlled by I2C USB bus

The registers described in this chapter are controlled through the USB serial I2C interface, USBSCL and USBSDA balls.

These registers can also be controlled through the main I2C interface, SCL and SDA balls by setting to "1" 'usb\_i2c\_ctrl' bit in *power control* register (*Table 23*).

| Address    | Register                 | Туре |

|------------|--------------------------|------|

| 00h - 01h  | Vendor ID                | R    |

| 02h - 03h  | Product ID               | R    |

| 04h set    | USB control register 1   | R/W  |

| 05h clearh | USB control register 1   | R/W  |

| 06h set    | USB control register 2   | R/W  |

| 07h clearh | USB control register 2   | R/W  |

| 08h        | USB interrupt source     | R    |

| 09h        | Not used                 |      |

| 0Ah set    | USB interrupt latch      | R/W  |

| 0Bh clearh | USB interrupt latch      | R/W  |

| 0Ch set    | USB interrupt mask false | R/W  |

| 0Dh clearh | USB interrupt mask false | R/W  |

| 0Eh set    | USB interrupt mask true  | R/W  |

| 0Fh clearh | USB interrupt mask true  | R/W  |

| 10h        | USB_EN                   | R/W  |

Table 9.USB register address

Note:

A bit of register 1 is set at "1" by writing a "1" at address 04h, is reset at "0" by writing a "1" at address 05h. This is also applicable for USB control register 2 (06h, 07h), USB interrupt register (0Ah,0Bh), USB interrupt mask false register (0Ch, 0Dh) and USB interrupt mask true register (0Eh, 0Fh). Writing "0" at any address has not effect on the content of any register.

Table 10.Vendor ID and Product ID: Read only

| Name       | Address | Register value |

|------------|---------|----------------|

| Vendor ID  | 00h     | 83h            |

| Vendor ID  | 01h     | 04h            |

| Product ID | 02h     | 11h            |

|            | 03h     | 40h            |

# **USB control register 1**

| Table 11. | USB cont | rol registe | r 1 (addres | s = 04h set | and 05h cl | earh) |

|-----------|----------|-------------|-------------|-------------|------------|-------|

|           |          |             |             |             |            |       |

| 7        | 6       | 5         | 4                | 3        | 2       | 1       | 0     |

|----------|---------|-----------|------------------|----------|---------|---------|-------|

| Not used | uart_en | oe_int_en | bdis_<br>acon_en | not used | dat_se0 | suspend | speed |

| -        | R/W     | R/W       | R/W              | -        | R/W     | R/W     | R/W   |

| Bits | Name         | Value  | Settings                                                                             | Default |

|------|--------------|--------|--------------------------------------------------------------------------------------|---------|

| 6    | uart_en      | 0<br>1 | Inactive<br>UART logic buffers are enabled                                           | 0       |

| 5    | oe_int_en    | 0<br>1 | Inactive<br>Allow to send interruption through USBOEn                                | 0       |

| 4    | bdis_acon_en | 0<br>1 | Inactive (default)<br>Enable A-device to connect if B-device disconnect<br>detected: | 0       |

| 2    | dat_se0      | 0<br>1 | VP_VM USB mode<br>DAT_SE0 USB mode                                                   | 0       |

| 1    | suspend      | 0<br>1 | Inactive (default)<br>Put transceiver in low power mode                              | 0       |

| 0    | speed        | 0<br>1 | Set rise and fall times of transmit<br>Low speed<br>Full speed                       | 0       |

# **USB control register 2**

| 7     | 7            | 6                | 5        | 4                                 | 0                                                  |         |  |         |  |

|-------|--------------|------------------|----------|-----------------------------------|----------------------------------------------------|---------|--|---------|--|

| vbus_ | _chrg        | vbus_<br>dischrg | vbus_drv | id_gnd                            | id_gnd dn_ dp_ dn_pulldown dn_pulldown dn_pulldown |         |  |         |  |

| R/    | W            | R/W              | R/W      | R/W                               | R/W R/W R/W                                        |         |  |         |  |

| Bits  |              | Name             | Value    |                                   | Set                                                | tings   |  | Default |  |

| 7     | vbus <u></u> | _chrg            | 0<br>1   | Inactive<br>Charge VBL            | JS through a r                                     | esistor |  | 0       |  |

| 6     | vbus <u></u> | _dischrg         | 0<br>1   | Inactive<br>Discharge V           | 0                                                  |         |  |         |  |

| 5     | vbus <u></u> | _drv             | 0<br>1   | Inactive<br>Provide power to VBUS |                                                    |         |  | 0       |  |

| 4     | id_gr        | nd               | 0<br>1   | Inactive<br>Connect ID            | ball to ground                                     |         |  | 0       |  |

| 3     | dn_p         | ulldown          | 0<br>1   | Inactive<br>Connect DN            | pull-down                                          |         |  | 0       |  |

| 2     | dp_p         | ulldown          | 0<br>1   | Inactive<br>Connect DP            | 0                                                  |         |  |         |  |

| 1     | dn_p         | ullup            | 0<br>1   | Inactive<br>Connect DN pull-up    |                                                    |         |  | 0       |  |

| 0     | dp_p         | ullup            | 0<br>1   | Inactive<br>Connect DP            | Inactive<br>Connect DP pull-up                     |         |  |         |  |

Table 12.

USB control register 2 (address = 06h set and 07h clearh)

# USB interrupt source register

| 7    | 7      | 6         | 5        | 4 3 2 1                                                                             |                |                |        | 0       |

|------|--------|-----------|----------|-------------------------------------------------------------------------------------|----------------|----------------|--------|---------|

| cr_  | int    | bdis_acon | id_float | dn_hi                                                                               | vbus_vld       |                |        |         |

| F    | 1      | R         | R        | R                                                                                   | R              | R              | R      | R       |

| Bits |        | Name      | Value    |                                                                                     | Sett           | tings          |        | Default |

| 7    | cr_in  | t         | -        | Inactive<br>DP ball is abo                                                          | ove the carkit | interrupt thre | eshold | 0       |

| 6    | bdis_  | acon      | 1        | Inactive<br>Set when bdis<br>asserts dp_p<br>disconnect.                            | 0              |                |        |         |

| 5    | id_flo | pat       |          | Inactive<br>ID ball floating                                                        | g              |                |        | 0       |

| 4    | dn_h   | i         |          | Inactive<br>DN ball is hig                                                          | h              |                |        | 0       |

| 3    | id_gr  | nd_forced |          | Inactive<br>ID ball ground                                                          | led            |                |        | 0       |

| 2    | dp_h   | i         |          | Inactive<br>DP asserted during SRP,                                                 |                |                |        | 0       |

| 1    | sess   | _vld      |          | Session valid comparator threshold < 2V<br>2 V < Session valid comparator threshold |                |                | 0      |         |

| 0    | vbus   | _vld      |          | A-device VBL<br>A-device VBL                                                        |                |                |        | 0       |

Table 13.

USB Interrupt source register (address = 08h)

*USB interrupt source* register indicates the current state of the signals that can generate an interrupt.

# **USB** latch register

| Register | 7      | 6             | 5        | 4     | 3                 | 2     | 1            | 0            |

|----------|--------|---------------|----------|-------|-------------------|-------|--------------|--------------|

| Bit name | cr_int | bdis_<br>acon | id_float | dn_hi | id_gnd_<br>forced | dp_hi | sess_<br>vld | vbus_<br>vld |

| Default  | 0      | 0             | 0        | 0     | 0                 | 0     | 0            | 0            |

| Туре     | R/W    | R/W           | R/W      | R/W   | R/W               | R/W   | R/W          | R/W          |

USB interrupt latch register indicates which source has generated an interrupt.

## USB interrupt enable low register

| 7      | 6         | 5        | 4     | 3                 | 2     | 1        | 0            |

|--------|-----------|----------|-------|-------------------|-------|----------|--------------|

| cr_int | bdis_acon | id_float | dn_hi | id_gnd_<br>forced | dp_hi | sess_vld | vbus_<br>vld |

| 0      | 0         | 0        | 0     | 0                 | 0     | 0        | 0            |

| R/W    | R/W       | R/W      | R/W   | R/W               | R/W   | R/W      | R/W          |

Table 15. USB interrupt enable low register (address = 0Ch and 0Dh)

USB interrupt enable low register enables interrupts on transition from high to low.

#### USB interrupt enable high register

Table 16.

USB interrupt enable high register (address = 0Eh and 0Fh)

| 7      | 6         | 5        | 4     | 3                 | 2     | 1        | 0        |

|--------|-----------|----------|-------|-------------------|-------|----------|----------|

| cr_int | bdis_acon | id_float | dn_hi | id_gnd_<br>forced | dp_hi | sess_vld | vbus_vld |

| R/W    | R/W       | R/W      | R/W   | R/W               | R/W   | R/W      | R/W      |

USB interrupt enable high register enables interrupts on transition from low to high.

#### Interrupts

*Table 13* indicates the signals that can generate interrupts. Any of the signals given in *Table 13* can generate an interrupt when the signal becomes either low or high. After an interrupt, the OTG controller is able to read each signal status as well as the bit that indicates whether or not that signal generated the interrupt.

A bit in the *interrupt latch register* is set when any of the following occurs:

- writing "1" to its set address causes the corresponding bit to be set.

- the corresponding bit in the *interrupt enable high* register is set, and the associated signal changes from low to high

- the corresponding bit in the *interrupt enable low* register is set, and the associated signal changes from high to low

The *interrupt latch* register is cleared by writing "1" to its clear address.

1

2

6

usb\_en

th\_Bdevice

B\_sess\_end

0

0

0

# **USB EN register**

|          |                | - 3 ( |          | ,  |                |        |          |

|----------|----------------|-------|----------|----|----------------|--------|----------|

| 7        | 6              | 5     | 4        | 3  | 2              | 1      | 0        |

| Not used | B_sess_<br>end |       | Not used |    | th_<br>Bdevice | usb_en | not used |

| -        | R              | -     | -        | -  | R/W            | R/W    | -        |

| Bits     | Name           | Value |          | Se | ettings        |        | Default  |

Threshold for vbus\_valid = 4.4 V

Threshold for vbus\_valid = 3.87 V

Vbus voltage is below B\_session\_end threshold

Vbus voltage is above B\_session\_end threshold

Inactive

Enable USB PHY

(0.2 to 0.8 V)

(0.2 to 0.8 V)

0

1 0

1 0

1

#### Table 17. USB EN register (address = 10h)

# **Registers controlled by main I2C BUS**

I2C controlled registers are controlled through the main serial I2C interface, SCL and SDA balls.

# **Configuration 1 register**

| Table 18. Configuration 1 register ( |

|--------------------------------------|

|--------------------------------------|

| 7        | 6                | 5                             | 4                 | 3 2           |  | 1            | 0 |

|----------|------------------|-------------------------------|-------------------|---------------|--|--------------|---|

| pdn_vaux | it_warn          | monitoring_vio_<br>vmem_vcore | mmc_ls_<br>status | vmmc_sel[2:0] |  | pdn_<br>vmmc |   |

| R/W      | R <sup>(1)</sup> | R <sup>(1)</sup>              | R/W               | R/W           |  | R/W          |   |

1. These bits are reset (0) after reading

| Bits  | Name                          | Value                                                | Settings                                                                                                                                                                                                       | Default          |

|-------|-------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 7     | pdn_vaux                      | 0<br>1                                               | Inactive<br>Enable LDO vaux                                                                                                                                                                                    | 0 <sup>(1)</sup> |

| 6     | it_warn                       | 0<br>1                                               | Below temperature threshold<br>Above temperature threshold                                                                                                                                                     | 0                |

| 5     | monitoring_vio_<br>vmem_vcore | 0<br>1                                               | Outputs in the good range<br>Outputs lower than expected on vio_vmem or vcore                                                                                                                                  | 0                |

| 4     | mmc_ls_status                 | 0<br>1                                               | Level shifters ON, if 'pdn_vmmc' or<br>'external_vmmc' = 1<br>Level shifters High Impedance, if 'pdn_vmmc' or<br>'external_vmmc' =1                                                                            | 0                |

| [3:1] | vmmc_sel[2:0]                 | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | <ul> <li>1.8V selection</li> <li>1.8V selection</li> <li>2.85V selection</li> <li>3V selection</li> <li>1.85 V selection</li> <li>2.6 V selection</li> <li>2.7 V selection</li> <li>3.3 V selection</li> </ul> | 000              |

| 0     | pdn_vmmc                      | 0<br>1                                               | Inactive<br>Enable SD/MMC/SDIO function.                                                                                                                                                                       | 0                |

1. In STw4811M, pdn\_vaux = 0 is the default. In STw4811N, pdn\_vaux = 1 is the default.

In Flash OTP two registers allow to program STw4811 energy management part. These two registers are at addresses 1E and 1F and must be programmed with *1F* register first followed by *1E* register.

# Power control register at address 1Eh

| Table 19. | Power control register - General information (address = 1Eh) |

|-----------|--------------------------------------------------------------|

|-----------|--------------------------------------------------------------|

| 7      | 6             | 5     | 4 | 3  | 2   | 1 | 0 |

|--------|---------------|-------|---|----|-----|---|---|

| reg ac | ddress 3 bits | LSB's |   | EN |     |   |   |

|        | R/W           |       |   |    | R/W |   |   |

| Bits  | Name                     | Value  | Settings                               | Default |

|-------|--------------------------|--------|----------------------------------------|---------|

| [7:5] | reg address 3<br>bits    |        | See Table 21 "Address" column (LSB's). | 0       |

| [4:1] | data din/<br>dout 4 bits |        | See Table 21 control register          | 0       |

| 0     | EN                       | 0<br>1 | Read enabled<br>Write enabled          | 0       |

# Power control register at address 1Fh

## Table 20.Power control register - General information (address = 1Fh)

| 15       | 15 14 13 12 11 10 |    |   |  |  | 9 | 8                           |  |

|----------|-------------------|----|---|--|--|---|-----------------------------|--|

| Not used |                   |    |   |  |  |   | reg address 2 bits<br>MSB's |  |

|          |                   | R/ | W |  |  |   |                             |  |

| Bits  | Name                        | Value | Settings                               | Default |

|-------|-----------------------------|-------|----------------------------------------|---------|

| [9:8] | reg address 2<br>bits MSB's |       | See Table 21 "Address" column (MSB's). | 0       |

# Power control register mapping

### Table 21. Power control register mapping

|    |                       | Α  | ddre | ss 1F | ħ  |   |            |      |                 | Α | ddre                  | ss 1E | h |   |          |                          |  |  |

|----|-----------------------|----|------|-------|----|---|------------|------|-----------------|---|-----------------------|-------|---|---|----------|--------------------------|--|--|

|    |                       |    |      |       |    |   | reg        | addr | ess             |   |                       |       |   |   |          |                          |  |  |

|    | Not used 2 bit<br>MSB |    |      |       |    |   |            |      | 3 bits<br>LSB's | - | data din/dout<br>bits |       |   |   | EN       | Comments                 |  |  |

| 15 | 14                    | 13 | 12   | 11    | 10 | 9 | 8 7 6 5    |      |                 | 4 | 3                     | 2     | 1 | 0 |          |                          |  |  |

|    |                       |    |      |       |    |   | 00h to 04h |      |                 |   |                       |       |   |   | Reserved |                          |  |  |

|    |                       |    |      |       |    |   | 05h to 0Ah |      |                 |   | Setting               |       |   |   |          | See Table 22 to Table 27 |  |  |

|    |                       |    |      |       |    |   | 0Bh to 1E  |      |                 |   |                       |       |   |   |          | Reserved                 |  |  |

**Caution:** Only the latest value written in register at address 1E/1F can be read.

# Power control register at address 05h

|      |     | Α                                                                                                                       | ddre | ss 1F                                                                                                                 | ħ                                                                                                       |       |     |   |   |   | A      | ddress <sup>-</sup> | 1Eh       |   |         |

|------|-----|-------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------|-----|---|---|---|--------|---------------------|-----------|---|---------|

| 15   | 14  | 13                                                                                                                      | 12   | 11                                                                                                                    | 10                                                                                                      | 9     | 8   | 7 | 6 | 5 | 4      | 3                   | 2         | 1 | 0       |

|      |     | Not u                                                                                                                   | used |                                                                                                                       |                                                                                                         | 0     | 0   | 1 | 0 | 1 |        | vcore_s             | sel [3:0] |   | EN      |

| Bits | 6   | Na                                                                                                                      | ame  |                                                                                                                       | Va                                                                                                      | lue   |     |   |   |   | Settin | gs                  |           |   | Default |

| [4:1 | ] v | vcore_sel [3:0]<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001<br>1011<br>1010<br>1011<br>1100<br>1101 |      | = 1.0 $= 1.0$ $= 1.0$ $= 1.0$ $= 1.0$ $= 1.0$ $= 1.0$ $= 1.0$ $= 1.0$ $= 1.0$ $= 1.0$ $= 1.0$ $= 1.0$ $= 1.0$ $= 1.0$ | 05V<br>10V<br>15V<br>22V<br>24V<br>22V<br>24V<br>26V (<br>28V<br>30V<br>32V<br>34V<br>36V<br>38V<br>40V | defau | lt) |   |   |   |        | 0111                |           |   |         |

# Table 22. Power control register at address 05h

32/85

00

0

# Power control register at address 06h

|      |                                                  |    |      |       |    | <u> </u>                         |          |   |   |   |                 |            |              |                 |         |  |

|------|--------------------------------------------------|----|------|-------|----|----------------------------------|----------|---|---|---|-----------------|------------|--------------|-----------------|---------|--|

|      |                                                  | Α  | ddre | ss 1F | ħ  |                                  |          |   |   |   | Α               | ddress 1   | Eh           |                 |         |  |

| 15   | 14                                               | 13 | 12   | 11    | 10 | 9                                | 8        | 7 | 6 | 5 | 4               | 3          | 2            | 1               | 0       |  |

|      | Not used 0 0                                     |    |      |       |    |                                  |          | 1 | 1 | 0 | vpll_sel<br>[0] | vaux<br><1 | (_sel<br>:0> | usb_<br>i2c_ctr | I EN    |  |

| Bits | its Name Value                                   |    |      |       |    |                                  |          |   |   |   | Setting         | gs         |              |                 | Default |  |

| 4    | vpll_sel[1:0] 01<br>on 06h and 07h 10<br>address |    |      |       |    | = 1.0<br>= 1.2<br>= 1.3<br>= 1.8 | 2V<br>3V |   |   |   |                 |            |              | 11              |         |  |

#### Table 23. Power control register at address 06h

| [3:2] | vaux_sel[1:0] | 10<br>11 | = 2.5V<br>= 2.8V                                                                      |

|-------|---------------|----------|---------------------------------------------------------------------------------------|

| 1     | usb_i2c_ctrl  | 0<br>1   | USB I2C interface controls USB registers<br>Main I2C interface controls USB registers |

= 1.5V

= 1.8V

# Power control register at address 07h

[3:2] vaux\_sel[1:0]

#### Table 24. Power control register at address 07h

00

01

|    |                      | Α | ddres | ss 1F | ħ |   |   | Address 1Eh |         |             |              |                 |    |   |   |  |  |

|----|----------------------|---|-------|-------|---|---|---|-------------|---------|-------------|--------------|-----------------|----|---|---|--|--|

| 15 | 5 14 13 12 11 10 9 8 |   |       |       |   |   |   | 7           | 6       | 5           | 4            | 3               | 2  | 1 | 0 |  |  |

|    | Not used 0 0         |   |       |       |   | 1 | 1 | 1           | en_vpll | not<br>used | en_<br>vcore | vpll_sel<br>[1] | EN |   |   |  |  |

| Bits | Name        | Value  | Settings                                                      | Default |

|------|-------------|--------|---------------------------------------------------------------|---------|

| 4    | en_vpll     | 0<br>1 | Disabled / VPLL = OFF<br>Enabled / VPLL = ON <sup>(1)</sup>   | 1       |

| 2    | en_vcore    | 0<br>1 | Disabled / VCORE = OFF<br>Enabled / VCORE = ON <sup>(1)</sup> | 1       |

| 1    | vpll_sel[1] | -      | See Table 23                                                  | -       |

1. No soft start feature at supply enabled after a disabled/enabled sequence