#### 2. Internal peripheral resources

- · General-purpose ports : Maximum 108 ports

- DMAC (DMA Controller)

Maximum of 5 channels able to operate simultaneously

2 transfer sources (internal peripheral/software)

Activation source can be selected using software

Addressing mode specifies full 32-bit addresses (increment/decrement/fixed)

Transfer mode (demand transfer/burst transfer/step transfer/block transfer)

Transfer data size selectable from 8/16/32-bit

Multi-byte transfer enabled (by software)

DMAC descriptor in I/O areas (200<sub>H</sub> to 240<sub>H</sub>, 1000<sub>H</sub> to 1024<sub>H</sub>)

A/D converter (successive approximation type)

10-bit resolution: maximum 32 channels

Conversion time: minimum 1 µs

· External interrupt inputs : maximum 16 channels

3 channels shared with CAN RX or I2C pins

Bit search module (for REALOS)

Function to search the first bit position of "1", "0", "changed" from the MSB (most significant bit) within one word

• LIN-USART (full duplex double buffer): 4 or 7 channels

Clock synchronous/asynchronous selectable

Sync-break detection

Internal dedicated baud rate generator

• I2C\* bus interface (supports 400 kbps): 2 channels

Master/slave transmission and reception

Arbitration function, clock synchronization function

· CAN controller (C-CAN): 1 channel

Maximum transfer speed: 1 Mbps

32 transmission/reception message buffers

Sound generator: 1 channel

Tone frequency: PWM frequency divide-by-two (reload value + 1)

· Alarm comparator : 1 channel

Monitor external voltage

Generate an interrupt in case of voltage lower/higher than the defined thresholds (reference voltage)

- 16-bit PPG timer : maximum 16 channels

- · 16-bit reload timer: 8 channels

- 16-bit free-run timer: 8 channels (1 channel each for ICU and OCU)

- Input capture: maximum 8 channels (operates in conjunction with the free-run timer)

- Output compare: maximum 8 channels (operates in conjunction with the free-run timer)

- Up/Down counter: 2 channels (2\*8-bit or 1\*16-bit)

- · Watchdog timer

- · Real-time clock

- · Low-power consumption modes : Sleep/stop mode function

- Low voltage detection circuit

(Continued)

#### (Continued)

- Clock supervisor

- Monitors the sub-clock (32 kHz) and the main clock (4 MHz) , and switches to a recovery clock (CR oscillator, etc.) when the oscillations stop.

- · Clock modulator

- · Clock monitor

- Sub-clock calibration

- Corrects the real-time clock timer when operating with the 32 kHz or CR oscillator

- Main oscillator stabilization timer

Generates an interrupt in sub-clock mode after the stabilization wait time has elapsed on the 23-bit stabilization wait time counter

- Sub-oscillator stabilization timer

Generates an interrupt in main clock mode after the stabilization wait time has elapsed on the 15-bit stabilization wait time counter

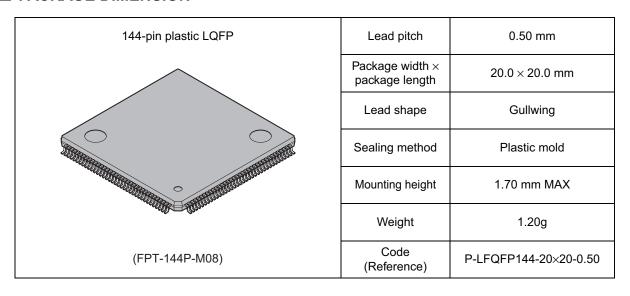

#### 3. Package and technology

- Package : QFP-144

- CMOS 180 nm technology

- Power supply range 3 V to 5 V (1.8 V internal logic provided by a step-down voltage converter)

- Operating temperature range: between 40°C and + 125°C

- Note \* Purchase of Fujitsu I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

### **■ PRODUCT LINEUP**

| Feature                            | MB91FV460B                                                                  | MB91F464HB                                                      | MB91F466HA                                                      |

|------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|

| Max. core frequency (CLKB)         | 100 MHz                                                                     | 100 MHz                                                         | 96 MHz                                                          |

| Max. resource frequency (CLKP)     | 50 MHz                                                                      | 50 MHz                                                          | 48 MHz                                                          |

| Max. external bus frequency (CLKT) | 50 MHz                                                                      | 50 MHz                                                          | 48 MHz                                                          |

| Max. CAN frequency (CLKCAN)        | 50 MHz                                                                      | 50 MHz                                                          | 48 MHz                                                          |

| Technology                         | 0.18um                                                                      | 0.18um                                                          | 0.18um                                                          |

| Watchdog                           | yes                                                                         | yes                                                             | yes                                                             |

| Watchdog (RC osc. based)           | yes (disengageable)                                                         | yes                                                             | yes                                                             |

| Bit Search                         | yes                                                                         | yes                                                             | yes                                                             |

| Reset input (INITX)                | yes                                                                         | yes                                                             | yes                                                             |

|                                    |                                                                             |                                                                 |                                                                 |

| Clock Modulator                    | yes                                                                         | yes                                                             | yes                                                             |

| Clock Monitor                      | yes                                                                         | yes                                                             | yes                                                             |

| Low Power Mode                     | yes                                                                         | yes                                                             | yes                                                             |

| DMA                                | 5 ch                                                                        | 5 ch                                                            | 5 ch                                                            |

| MMU/MPU                            | MPU (16 ch)*1                                                               | MPU (8 ch)*1                                                    | MPU (8 ch)*1                                                    |

|                                    |                                                                             |                                                                 |                                                                 |

| Flash memory                       | Internal Flash memory 2112KB + external emulation SRAM with 64bit read data | 416 KByte                                                       | 832 KByte                                                       |

| Flash Protection                   | yes                                                                         | yes                                                             | yes                                                             |

|                                    |                                                                             |                                                                 |                                                                 |

| D-RAM                              | 64 KByte                                                                    | 16 KByte                                                        | 24 KByte                                                        |

| ID-RAM                             | 64 KByte                                                                    | 16 KByte                                                        | 16 KByte                                                        |

| Flash-Cache (Instruction cache)    | 16 KByte                                                                    | 8 KByte                                                         | 8 KByte                                                         |

| Boot-ROM / BI-ROM                  | 16 KByte Boot Flash<br>+ 1KB Boot ROM                                       | 4 KByte                                                         | 4 KByte                                                         |

|                                    |                                                                             |                                                                 |                                                                 |

| RTC                                | 1 ch                                                                        | 1 ch                                                            | 1 ch                                                            |

| Free Running Timer                 | 12 ch                                                                       | 8 ch⁴²                                                          | 8 ch <sup>+2</sup>                                              |

| ICU                                | 10 ch                                                                       | MD_3=0: 8 ch<br>MD_3=1: 4 ch*3                                  | MD_3=0: 8 ch<br>MD_3=1: 4 ch*3                                  |

| OCU                                | 8 ch                                                                        | MD_3=0: 8 ch<br>MD_3=1: 4 ch <sup>-4</sup>                      | MD_3=0: 8 ch<br>MD_3=1: 4 ch*4                                  |

| Reload Timer                       | 16 ch                                                                       | 8 ch⁺⁵                                                          | 8 ch*5                                                          |

| PPG 16-bit                         | 32 ch                                                                       | MD_3=0: 16 ch<br>MD_3=1: 8 ch <sup>-6</sup>                     | MD_3=0: 16 ch<br>MD_3=1: 8 ch <sup>*6</sup>                     |

|                                    |                                                                             |                                                                 |                                                                 |

| Sound Generator                    | 1 ch (old) + 1 ch (new)                                                     | 1 ch (old)                                                      | 1 ch (old)                                                      |

| Up/Down Counter (8/16 bit)         | 4 ch (8-bit) / 2 ch (16-bit)                                                | MD_3=0: 2 ch (8-bit) / 1 ch (16bit)<br>MD_3=1: NA <sup>-7</sup> | MD_3=0: 2 ch (8-bit) / 1 ch (16bit)<br>MD_3=1: NA <sup>-7</sup> |

|                                    |                                                                             |                                                                 |                                                                 |

| C_CAN                              | 6 ch<br>(128msg)                                                            | 1 ch<br>(32msg)                                                 | 1 ch<br>(32msg)                                                 |

| LIN-USART                          | 16 ch (FIFO)                                                                | MD_3=0: 3 ch + 4 ch FIFO*8<br>MD_3=1: 4 ch FIFO                 | MD_3=0: 3 ch + 4 ch FIFO'8<br>MD_3=1: 4 ch FIFO                 |

| I <sup>2</sup> C (400K)            | 8 ch                                                                        | 2 ch                                                            | 2 ch                                                            |

|                                    |                                                                             |                                                                 |                                                                 |

| Feature                                  | MB91FV460B                   | MB91F464HB                                         | MB91F466HA                                         |  |

|------------------------------------------|------------------------------|----------------------------------------------------|----------------------------------------------------|--|

| R external bus                           | yes (32bit addr, 32bit data) | MD_3=0: no<br>MD_3=1: yes (22bit addr, 16bit data) | MD_3=0: no<br>MD_3=1: yes (22bit addr, 16bit data) |  |

| xternal Interrupts                       | 32 ch                        | MD_3=0: 16 ch<br>MD_3=1: 12 ch <sup>*9</sup>       | MD_3=0: 16 ch<br>MD_3=1: 12 ch <sup>*9</sup>       |  |

| MI Interrupts                            | 1 ch                         | 1 ch                                               | 1 ch                                               |  |

| DC (10-bit)                              | 32 ch + 22 ch                | MD_3=0: 32 ch<br>MD_3=1: 16 ch                     | MD_3=0: 32 ch<br>MD_3=1: 16 ch                     |  |

| larm Comparator                          | 2 ch                         | 1 ch                                               | 1 ch                                               |  |

| upply Supervisor (low voltage detection) | yes                          | yes                                                | yes                                                |  |

| lock Supervisor                          | yes                          | yes                                                | yes                                                |  |

| lain clock oscillator                    | 4 MHz                        | 4 MHz                                              | 4 MHz                                              |  |

| ub clock oscillator                      | 32kHz                        | 32kHz                                              | 32kHz                                              |  |

| C oscillator                             | 100kHz / 2MHz                | 100kHz / 2MHz                                      | 100kHz / 2MHz                                      |  |

| LL                                       | x 25                         | x 25                                               | x 25                                               |  |

| SU4                                      | yes                          | no                                                 | no                                                 |  |

| DSU                                      | yes (32 BP)*1                | yes (16 BP)*1                                      | yes (16 BP)*1                                      |  |

| upply voltage                            | 1.8V + 3V/5V                 | 3V/5V                                              | 3V/5V                                              |  |

| egulator                                 | no                           | yes                                                | yes                                                |  |

| ower consumption                         | 1.5 W                        | < 1.3 W                                            | < 1.3 W                                            |  |

| emperature Range (Ta)                    | 070 C                        | -40125 C                                           | -40125 C                                           |  |

| ackage                                   | BGA-896                      | QFP-144                                            | QFP-144                                            |  |

| ower on to PLL run                       | < 20 ms                      | < 20 ms                                            | < 20 ms                                            |  |

| ash Download Time                        | < 8 sec. typical             | < 5 sec. typical                                   | < 5 sec. typical                                   |  |

| ower on to PLL run                       | < 20 ms                      | < 20 ms                                            | < 20 ms                                            |  |

- \*1: MPU channels use EDSU breakpoint registers (shared operation between MPU and EDSU).

- \*2: Free Running Timer: MD3=0 : CH 1 and 0 cannot select external clock (bit7 of TCCS1,0) MD3=1: CH 3, 2, 1, and 0 cannot select external clock (bit7 of TCCS3,2,1,0)

- \*3: ICU: MD3=1: Do not set PFR = 1 & EPFR = 1 (for LIN Synch Field detect).

- \*4: OCU: MD3=1: You cannot use external out-port (but, OCU-function is active.)

- \*5: Reload Timer: MD3=1: CH 7, 6, 5, and 4 cannot select external event

- \*6: PPG: MD3=1: You can use CH15 to 8 of PPG. CH15 to12 cannot select external trigger.

- \*7: Up/Down Counter: MD3=1: You can use Timer-mode only.

- \*8: LIN-USART CH 0 (shared with external bus) can be used for asynchronous mode only.

- \*9: External Interrupts: INT7 to INT4(shared with external bus) can be used for MD3=0 mode only. INT0 (shared with external bus) can be used for MD3=0 mode only.

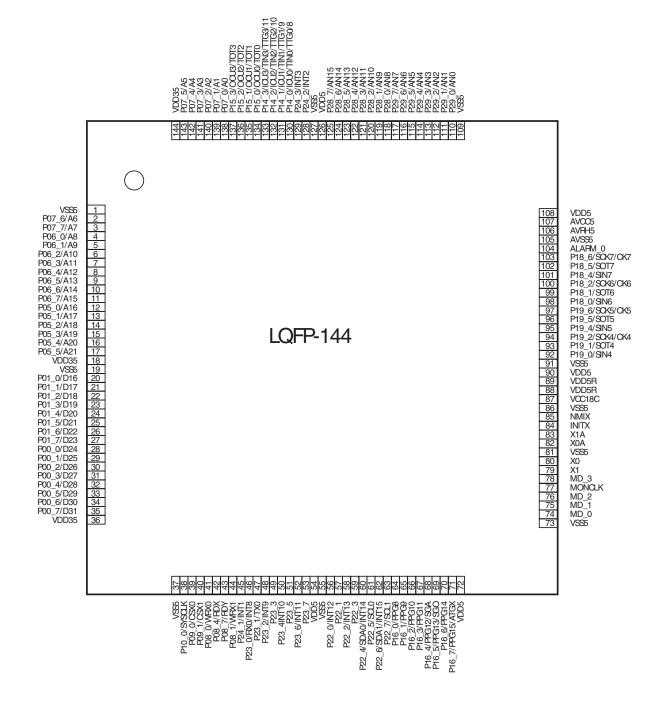

#### **■ PIN ASSIGNMENT**

1. MB91F464HB, MB91F466HA with MD 3=1

(TOP VIEW)

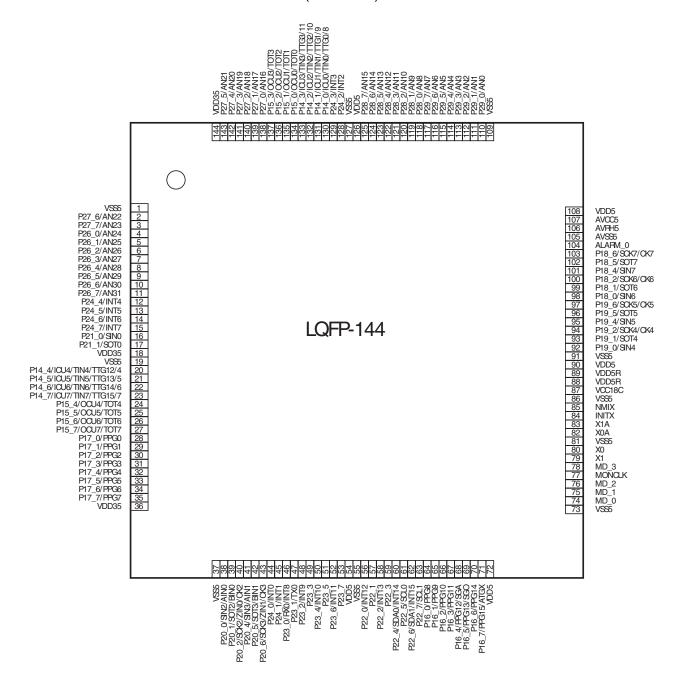

#### 2. MB91F46HB, MB91F466HA with MD\_3=0

(TOP VIEW)

### **■ PIN DESCRIPTION**

### 1. MB91F464HB, MB91F466HA with MD\_3=1

| Pin no.  | Pin name       | I/O | I/O circuit<br>type* | Function                                                                   |

|----------|----------------|-----|----------------------|----------------------------------------------------------------------------|

| 2, 3     | P07_6, P07_7   | I/O | В                    | General-purpose input/output port                                          |

| 2, 3     | A6, A7         |     |                      | Signal pins of external address bus (bit6 to bit7)                         |

| 4 to 11  | P06_0 to P06_7 | I/O | В                    | General-purpose input/output port                                          |

| 4 10 11  | A8 to A15      | 1/0 | Ь                    | Signal pins of external address bus (bit8 to bit15)                        |

| 12 to 17 | P05_0 to P05_5 | I/O | Α                    | General-purpose input/output port                                          |

| 12 10 17 | A16 to A21     | 1/0 |                      | Signal pins of external address bus (bit16 to bit21)                       |

| 20 to 27 | P01_0 to P01_7 | I/O | Α                    | General-purpose input/output port                                          |

| 20 10 27 | D16 to D23     | 1/0 |                      | Signal pins of external data bus (bit16 to bit23)                          |

| 28 to 35 | P00_0 to P00_7 | 1/0 | Α                    | General-purpose input/output port                                          |

| 20 10 33 | D24 to D31     | I/O | A                    | Signal pins of external data bus (bit24 to bit31)                          |

| 38       | P10_0          | I/O | ^                    | General-purpose input/output port                                          |

| 30       | SYSCLK         |     | A                    | External bus clock output pin                                              |

| 39       | P09_0          | I/O | I/O A                | General-purpose input/output port                                          |

| 39       | CSX0           |     |                      | Chip select output pins                                                    |

| 40       | P09_1          | I/O | А                    | General-purpose input/output port                                          |

| 40       | CSX1           |     |                      | Chip select output pins                                                    |

| 41       | P08_0          | I/O | А                    | General-purpose input/output port                                          |

| 41       | WRX0           | 1/0 |                      | External write strobe output pins                                          |

| 42       | P08_4          | 1/0 | I/O A                | General-purpose input/output port                                          |

| 42       | RDX            | 1/0 |                      | External read strobe output pin                                            |

| 43       | P08_7          | 1/0 | А                    | General-purpose input/output port                                          |

| 43       | RDY            | I/O |                      | External ready input pin                                                   |

|          | P08_1          |     |                      | General-purpose input/output port                                          |

| 44       | WRX1           | I/O | A                    | External write strobe output pins                                          |

| 11       | INT0           | 1/0 |                      | External interrupt input, can only be used in general-purpose IO port mode |

| 45       | P24_1          | 1/0 | ^                    | General-purpose input/output port                                          |

| 45       | INT1           | I/O | A                    | External interrupt input pins                                              |

|          | P23_0          |     |                      | General-purpose input/output port                                          |

| 46       | RX0            | I/O | Α                    | RX input pin of CAN0                                                       |

|          | INT8           |     |                      | External interrupt input pins                                              |

| 47       | P23_1          | 1/0 | _                    | General-purpose input/output port                                          |

| 47       | TX0            | I/O | Α                    | TX output pin of CAN0                                                      |

| Pin no. | Pin name | I/O   | I/O circuit<br>type* | Function                                                 |

|---------|----------|-------|----------------------|----------------------------------------------------------|

| 48      | P23_2    | I/O   | Δ.                   | General-purpose input/output port                        |

| 40      | INT9     | ] 1/0 | Α                    | External interrupt input pins                            |

| 49      | P23_3    | I/O   | Α                    | General-purpose input/output port                        |

| 50      | P23_4    | I/O   |                      | General-purpose input/output port                        |

| 50      | INT10    | ] 1/0 | A                    | External interrupt input pin                             |

| 51      | P23_5    | I/O   | Α                    | General-purpose input/output port                        |

| 50      | P23_6    | I/O   |                      | General-purpose input/output port                        |

| 52      | INT11    | ] 1/0 | A                    | External interrupt input pin                             |

| 53      | P23_7    | I/O   | Α                    | General-purpose input/output port                        |

| E.C.    | P22_0    | 1/0   | Λ.                   | General-purpose input/output port                        |

| 56      | INT12    | I/O   | A                    | External interrupt input pin                             |

| 57      | P22_1    | I/O   | Α                    | General-purpose input/output port                        |

| 50      | P22_2    | 1/0   |                      | General-purpose input/output port                        |

| 58      | INT13    | I/O   | A                    | External interrupt input pin                             |

| 59      | P22_3    | I/O   | Α                    | General-purpose input/output port                        |

|         | P22_4    | I/O   | С                    | General-purpose input/output port                        |

| 60      | SDA0     |       |                      | I <sup>2</sup> C bus DATA input/output pin (open drain)  |

|         | INT14    |       |                      | External interrupt input pin                             |

| 61      | P22_5    | I/O   | С                    | General-purpose input/output port                        |

| 01      | SCL0     | ] 1/0 |                      | I <sup>2</sup> C bus clock input/output pin (open drain) |

|         | P22_6    |       |                      | General-purpose input/output port                        |

| 62      | SDA1     | I/O   | С                    | I <sup>2</sup> C bus DATA input/output pin (open drain)  |

|         | INT15    |       |                      | External interrupt input pin                             |

| 60      | P22_7    | 1/0   |                      | General-purpose input/output port                        |

| 63      | SCL1     | I/O   | С                    | I <sup>2</sup> C bus clock input/output pin (open drain) |

| 0.4     | P16_0    | 1/0   |                      | General-purpose input/output port                        |

| 64      | PPG8     | I/O   | A                    | Output pins of PPG timer                                 |

| C.F.    | P16_1    | 1/0   |                      | General-purpose input/output port                        |

| 65      | PPG9     | I/O   | Α                    | Output pins of PPG timer                                 |

| 66      | P16_2    | 1/0   | Δ.                   | General-purpose input/output port                        |

| 66      | PPG10    | I/O   | Α                    | Output pins of PPG timer                                 |

| 67      | P16_3    | 1/0   | Λ                    | General-purpose input/output port                        |

| 67      | PPG11    | I/O   | A                    | Output pins of PPG timer                                 |

|         | P16_4    |       |                      | General-purpose input/output port                        |

| 68      | PPG12    | I/O   | Α                    | Output pins of PPG timer                                 |

|         | SGA      |       |                      | SGA output pin of sound generator                        |

| Pin no.  | Pin name     | I/O | I/O circuit<br>type* | Function                                     |

|----------|--------------|-----|----------------------|----------------------------------------------|

|          | P16_5        |     |                      | General-purpose input/output port            |

| 69       | PPG13        | I/O | Α                    | Output pins of PPG timer                     |

|          | SGO          |     |                      | SG0 output pin of sound generator            |

| 70       | P16_6        | I/O | ^                    | General-purpose input/output port            |

| 70       | PPG14        | 1/0 | A                    | Output pins of PPG timer                     |

|          | P16_7        |     |                      | General-purpose input/output port            |

| 71       | PPG15        | I/O | Α                    | Output pins of PPG timer                     |

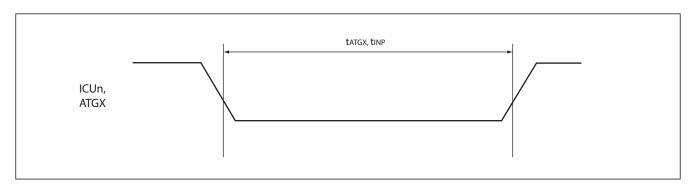

|          | ATGX         |     |                      | A/D converter external trigger input pin     |

| 74 to 76 | MD_0 to MD_2 | I   | G                    | Mode setting pins                            |

| 77       | MONCLK       | 0   | М                    | Clock monitor pin                            |

| 78       | MD_3         | I   | Н                    | Mode setting pin                             |

| 79       | X1           | _   | J1                   | Clock (oscillation) output                   |

| 80       | X0           | _   | J1                   | Clock (oscillation) input                    |

| 82       | X0A          | _   | J2                   | Sub clock (oscillation) input                |

| 83       | X1A          | _   | J2                   | Sub clock (oscillation) output               |

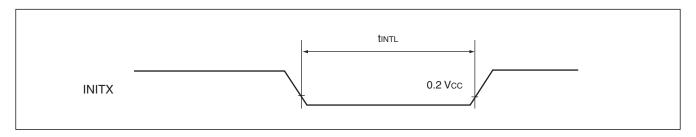

| 84       | INITX        | I   | Н                    | External reset input pin                     |

| 85       | NMIX         | I   | Н                    | Non-maskable interrupt input pin             |

| 00       | P19_0        | I/O | А                    | General-purpose input/output port            |

| 92       | SIN4         |     |                      | Data input pin of USART4                     |

| 00       | P19_1        | I/O | А                    | General-purpose input/output port            |

| 93       | SOT4         | 1/0 |                      | Data output pin of USART4                    |

|          | P19_2        |     | А                    | General-purpose input/output port            |

| 94       | SCK4         | I/O |                      | Clock input/output pin of USART4             |

|          | CK4          |     |                      | External clock input pin of free-run timer 4 |

| 05       | P19_4        | 1/0 | ^                    | General-purpose input/output port            |

| 95       | SIN5         | I/O | A                    | Data input pin of USART5                     |

| 00       | P19_5        | 1/0 | _                    | General-purpose input/output port            |

| 96       | SOT5         | I/O | A                    | Data output pin of USART5                    |

|          | P19_6        |     |                      | General-purpose input/output port            |

| 97       | SCK5         | I/O | Α                    | Clock input/output pin of USART5             |

|          | CK5          |     |                      | External clock input pin of free-run timer 5 |

| 00       | P18_0        | 1/0 |                      | General-purpose input/output port            |

| 98       | SIN6         | I/O | A                    | Data input pin of USART6                     |

| 00       | P18_1        | 1/0 | Δ.                   | General-purpose input/output port            |

| 99       | SOT6         | I/O | A                    | Data output pin of USART6                    |

| Pin no.    | Pin name          | I/O | I/O circuit<br>type* | Function                                           |

|------------|-------------------|-----|----------------------|----------------------------------------------------|

|            | P18_2             |     | А                    | General-purpose input/output port                  |

| 100        | SCK6              | I/O |                      | Clock input/output pin of USART6                   |

|            | CK6               |     |                      | External clock input pin of free-run timer 6       |

| 101        | P18_4             | I/O | А                    | General-purpose input/output port                  |

| 101        | SIN7              | 1/0 | A                    | Data input pin of USART7                           |

| 102        | P18_5             | I/O | ^                    | General-purpose input/output port                  |

| 102        | SOT7              | 1/0 | A                    | Data output pin of USART7                          |

|            | P18_6             | I/O |                      | General-purpose input/output port                  |

| 103        | SCK7              |     | Α                    | Clock input/output pin of USART7                   |

|            | CK7               |     |                      | External clock input pin of free-run timer 7       |

| 104        | ALARM_0           | 0   | N                    | Alarm comparator input pin                         |

| 110 to 117 | P29_0 to P29_7    | I/O | В                    | General-purpose input/output port                  |

| 110 10 117 | AN0 to AN7        |     |                      | Analog input pins of A/D converter                 |

| 118 to 125 | P28_0 to P28_7    | I/O | В                    | General-purpose input/output port                  |

| 110 10 123 | AN8 to AN15       | 1/0 |                      | Analog input pins of A/D converter                 |

| 128        | P24_2             | I/O | А                    | General-purpose input/output port                  |

| 120        | INT2              | 1/0 |                      | External interrupt input pin                       |

| 129        | P24_3             | I/O | Α                    | General-purpose input/output port                  |

| 129        | INT3              | 1/0 |                      | External interrupt input pin                       |

|            | P14_0 to P14_3    |     |                      | General-purpose input/output port                  |

| 130 to 133 | ICU0 to ICU3      | I/O | A                    | Input capture input pins                           |

| 130 10 133 | TIN0 to TIN3      | 1/0 | _ ^                  | External trigger input pins of reload timer        |

|            | TTG0/8 to TTG3/11 |     |                      | External trigger input pins of PPG timer           |

|            | P15_0 to P15_3    |     |                      | General-purpose input/output port                  |

| 134 to 137 | OCU0 to OCU3      | I/O | Α                    | Output compare output pins                         |

|            | TOT0 to TOT3      |     |                      | Reload timer output pins                           |

| 138 to 143 | P07_0 to P07_5    | I/O | В                    | General-purpose input/output port                  |

| 130 10 143 | A0 to A5          | 1/0 | В                    | Signal pins of external address bus (bit0 to bit5) |

[Power supply/Ground pins]

| i ower suppriy/cround pinsj                |          |        |                                                     |  |  |  |

|--------------------------------------------|----------|--------|-----------------------------------------------------|--|--|--|

| Pin no.                                    | Pin name | I/O    | Function                                            |  |  |  |

| 1, 19, 37, 55, 73, 81, 86,<br>91, 109, 127 | VSS5     |        | Ground pins                                         |  |  |  |

| 54, 72, 90, 108, 126                       | VDD5     |        | Power supply pins                                   |  |  |  |

| 88, 89                                     | VDD5R    |        | Power supply pins for internal regulator            |  |  |  |

| 105                                        | AVSS5    | Supply | Analog ground pin for A/D converter                 |  |  |  |

| 107                                        | AVCC5    |        | Power supply pin for A/D converter                  |  |  |  |

| 106                                        | AVRH5    |        | Reference power supply pin for A/D converter        |  |  |  |

| 87                                         | VCC18C   |        | Capacitor connection pin for internal regulator     |  |  |  |

| 18, 36, 144                                | VDD35    |        | Power supply pins for external bus part of I/O ring |  |  |  |

|                                            |          |        |                                                     |  |  |  |

### 2. MB91F464HB, MB91F466HA with MD\_3=0

| Pin no.     | Pin name      | I/O | I/O circuit<br>type* | Function                                     |

|-------------|---------------|-----|----------------------|----------------------------------------------|

| 2 to 3      | _6 to P27_7   | I/O | В                    | General-purpose input/output ports           |

| AN          | 22 to AN23    | 1/0 |                      | Analog input pins of A/D co                  |

| 4 to 11     | _0 to P26_7   | I/O | В                    | General-purpose input/output ports           |

| AN          | 24 to AN31    |     | Ь                    | Analog input pins of A/D converter           |

| 12 to 15    | _4 to P24_7   | I/O | ۸                    | General-purpose input/output ports           |

| 12 to 15    | T4 to INT7    | 1/0 | A                    | External interrupt input pins                |

| 16          | P21_0         | I/O | А                    | General-purpose input/output ports           |

| 10          | SIN0          | 1/0 | _ A                  | Data input pin of USART0                     |

| 17          | P21_1         | I/O | ۸                    | General-purpose input/output ports           |

|             | SOT0          |     | Α                    | Data output pin of USART0                    |

| P14         | _4 to P14_7   |     |                      | General-purpose input/output ports           |

| 20 to 23    | U4 to ICU7    | I/O | A                    | Input capture input pins                     |

| 20 to 23    | N4 to TIN7    | 1/0 | _ A                  | External trigger input pins of reload timer  |

| TTG4/       | 12 to TTG7/15 |     |                      | External trigger input pins of PPG timer     |

| P15         | _4 to P15_7   | I/O |                      | General-purpose input/output ports           |

| 24 to 27 OC | U4 to OCU7    |     |                      | Output compare output pins                   |

| ТО          | T4 to TOT7    |     |                      | Reload timer output pins                     |

| 28 to 35    | _0 to P17_7   | I/O | ) A                  | General-purpose input/output ports           |

| 28 to 33    | G0 to PPG7    | 1/0 |                      | Output pins of PPG timer                     |

|             | P20_0         |     |                      | General-purpose input/output ports           |

| 38          | SIN2          | I/O | A                    | Data input pin of USART2                     |

|             | AIN0          |     |                      | Up/down counter input pin                    |

|             | P20_1         |     |                      | General-purpose input/output ports           |

| 39          | SOT2          | I/O | Α                    | Data output pin of USART2                    |

|             | BIN0          |     |                      | Up/down counter input pin                    |

|             | P20_2         |     |                      | General-purpose input/output ports           |

| 40          | SCK2          | I/O | A                    | Clock input/output pin of USART2             |

| 40          | ZIN0          | 1/0 | _ A                  | Up/down counter input pin                    |

|             | CK2           |     |                      | External clock input pin of free-run timer 2 |

|             | P20_4         |     |                      | General-purpose input/output ports           |

| 41          | SIN3          | I/O | Α                    | Data input pin of USART3                     |

|             | AIN1          |     |                      | Up/down counter input pin                    |

|             | P20_5         |     |                      | General-purpose input/output ports           |

| 42          | SOT3          | I/O | Α                    | Data output pin of USART3                    |

|             | BIN1          |     |                      | Up/down counter input pin                    |

| Pin no. | Pin name | I/O   | I/O circuit<br>type* | Function                                                 |

|---------|----------|-------|----------------------|----------------------------------------------------------|

|         | P20_6    |       |                      | General-purpose input/output ports                       |

| 43      | SCK3     | I/O   | A                    | Clock input/output pin of USART3                         |

| 43      | ZIN1     |       |                      | Up/down counter input pin                                |

|         | CK3      |       |                      | External clock input pin of free-run timer 3             |

| 44      | P24_0    | I/O   | Α                    | General-purpose input/output ports                       |

| 44      | INT0     |       |                      | External interrupt input pin                             |

| 45      | P24_1    | I/O   | Α                    | General-purpose input/output ports                       |

| 45      | INT1     | 7 1/0 | _ ^                  | External interrupt input pin                             |

|         | P23_0    |       |                      | General-purpose input/output port                        |

| 46      | RX0      | I/O   | Α                    | RX input pin of CAN0                                     |

|         | INT8     |       |                      | External interrupt input pins                            |

| 47      | P23_1    | 1/0   | ^                    | General-purpose input/output port                        |

| 47      | TX0      | I/O   | A                    | TX output pin of CAN0                                    |

| 48      | P23_2    | I/O   | А                    | General-purpose input/output port                        |

| 40      | INT9     |       |                      | External interrupt input pins                            |

| 49      | P23_3    | I/O   | А                    | General-purpose input/output port                        |

| 50      | P23_4    | I/O   | A                    | General-purpose input/output port                        |

| 50      | INT10    | 7 1/0 |                      | External interrupt input pin                             |

| 51      | P23_5    | I/O   | А                    | General-purpose input/output port                        |

| 52      | P23_6    | I/O   | А                    | General-purpose input/output port                        |

| 52      | INT11    | 7 1/0 |                      | External interrupt input pin                             |

| 53      | P23_7    | I/O   | А                    | General-purpose input/output port                        |

| 56      | P22_0    | I/O   | A                    | General-purpose input/output port                        |

| 50      | INT12    | 7 1/0 |                      | External interrupt input pin                             |

| 57      | P22_1    | I/O   | А                    | General-purpose input/output port                        |

| 58      | P22_2    | I/O   | ^                    | General-purpose input/output port                        |

| 36      | INT13    | 7 1/0 | A                    | External interrupt input pin                             |

| 59      | P22_3    | I/O   | А                    | General-purpose input/output port                        |

|         | P22_4    |       |                      | General-purpose input/output ports                       |

| 60      | SDA0     | I/O   | С                    | I <sup>2</sup> C bus DATA input/output pin (open drain)  |

|         | INT14    |       |                      | External interrupt input pin                             |

| 61      | P22_5    | 1/0   | С                    | General-purpose input/output ports                       |

| 61      | SCL0     | I/O   |                      | I <sup>2</sup> C bus clock input/output pin (open drain) |

|         | P22_6    |       |                      | General-purpose input/output ports                       |

| 62      | SDA1     | I/O   | С                    | I <sup>2</sup> C bus DATA input/output pin (open drain)  |

|         | INT15    |       |                      | External interrupt input pin                             |

| Pin no.  | Pin name       | I/O | I/O circuit<br>type* | Function                                                 |

|----------|----------------|-----|----------------------|----------------------------------------------------------|

| 63       | P22_7          | I/O | С                    | General-purpose input/output ports                       |

| 03       | SCL1           | 1/0 |                      | I <sup>2</sup> C bus clock input/output pin (open drain) |

| 64 to 67 | P16_0 to P16_3 | 1/0 | ^                    | General-purpose input/output ports                       |

| 64 to 67 | PPG8 to PPG11  | I/O | A                    | Output pins of PPG timer                                 |

|          | P16_4          |     |                      | General-purpose input/output ports                       |

| 68       | PPG12          | I/O | Α                    | Output pins of PPG timer                                 |

|          | SGA            |     |                      | SGA output pin of sound generator                        |

|          | P16_5          |     |                      | General-purpose input/output ports                       |

| 69       | PPG13          | I/O | Α                    | Output pins of PPG timer                                 |

|          | SGO            |     |                      | SG0 output pin of sound generator                        |

| 70       | P16_6          | I/O | Δ.                   | General-purpose input/output ports                       |

| 70       | PPG14          | 1/0 | A                    | Output pins of PPG timer                                 |

|          | P16_7          |     |                      | General-purpose input/output ports                       |

| 71       | PPG15          | I/O | A                    | Output pins of PPG timer                                 |

|          | ATGX           |     |                      | A/D converter external trigger input pin                 |

| 74 to 76 | MD_0 to MD_2   | I   | G                    | Mode setting pins                                        |

| 77       | MONCLK         | 0   | М                    | Clock monitor pin                                        |

| 78       | MD_3           | I   | Н                    | Mode setting pins                                        |

| 79       | X1             | _   | J1                   | Clock (oscillation) output                               |

| 80       | X0             | _   | J1                   | Clock (oscillation) input                                |

| 82       | X0A            |     | J2                   | Sub clock (oscillation) input                            |

| 83       | X1A            | _   | J2                   | Sub clock (oscillation) output                           |

| 84       | INITX          | I   | Н                    | External reset input pin                                 |

| 85       | NMIX           | I   | Н                    | Non-maskable interrupt input pin                         |

| 00       | P19_0          | 1/0 | Δ.                   | General-purpose input/output ports                       |

| 92       | SIN4           | I/O | A                    | Data input pin of USART4                                 |

| 00       | P19_1          | 1/0 | Δ.                   | General-purpose input/output ports                       |

| 93       | SOT4           | I/O | A                    | Data output pin of USART4                                |

|          | P19_2          |     |                      | General-purpose input/output ports                       |

| 94       | SCK4           | I/O | Α                    | Clock input/output pin of USART4                         |

|          | CK4            |     |                      | External clock input pin of free-run timer 4             |

| 05       | P19_4          | 1/0 |                      | General-purpose input/output ports                       |

| 95       | SIN5           | I/O | A                    | Data input pin of USART5                                 |

| 00       | P19_5          | 1/0 | Δ.                   | General-purpose input/output ports                       |

| 96       | SOT5           | I/O | A                    | Data output pin of USART5                                |

| Pin no.    | Pin name          | I/O | I/O circuit<br>type* | Function                                     |

|------------|-------------------|-----|----------------------|----------------------------------------------|

|            | P19_6             |     |                      | General-purpose input/output ports           |

| 97         | SCK5              | I/O | Α                    | Clock input/output pin of USART5             |

|            | CK5               |     |                      | External clock input pin of free-run timer 5 |

| 98         | P18_0             | I/O | ^                    | General-purpose input/output ports           |

| 98         | SIN6              |     | A                    | Data input pin of USART6                     |

| 00         | P18_1             | 1/0 | ^                    | General-purpose input/output ports           |

| 99         | SOT6              | I/O | A                    | Data output pin of USART6                    |

|            | P18_2             |     |                      | General-purpose input/output ports           |

| 100        | SCK6              | I/O | Α                    | Clock input/output pin of USART6             |

|            | CK6               |     |                      | External clock input pin of free-run timer 6 |

| 404        | P18_4             | 1/0 |                      | General-purpose input/output ports           |

| 101        | SIN7              | I/O | A                    | Data input pin of USART7                     |

| 400        | P18_5             | 1/0 |                      | General-purpose input/output ports           |

| 102        | SOT7              | I/O | A                    | Data output pin of USART7                    |

|            | P18_6             | I/O | А                    | General-purpose input/output ports           |

| 103        | SCK7              |     |                      | Clock input/output pin of USART7             |

|            | CK7               |     |                      | External clock input pin of free-run timer 7 |

| 104        | ALARM_0           | I   | N                    | Alarm comparator input pin                   |

| 440 +- 447 | P29_0 to P29_7    | 1/0 | В                    | General-purpose input/output ports           |

| 110 to 117 | AN0 to AN7        | I/O |                      | Analog input pins of A/D converter           |

| 440 +- 405 | P28_0 to P28_7    | 1/0 |                      | General-purpose input/output ports           |

| 118 to 125 | AN8 to AN15       | I/O | В                    | Analog input pins of A/D converter           |

| 400        | P24_2             | 1/0 |                      | General-purpose input/output ports           |

| 128        | INT2              | I/O | A                    | External interrupt input pin                 |

| 400        | P24_3             | 1/0 |                      | General-purpose input/output ports           |

| 129        | INT3              | I/O | A                    | External interrupt input pin                 |

|            | P14_0 to P14_3    |     |                      | General-purpose input/output ports           |

| 400 ( 400  | ICU0 to ICU3      |     |                      | Input capture input pins                     |

| 130 to 133 | TIN0 to TIN3      | I/O | A                    | External trigger input pins of reload timer  |

|            | TTG0/8 to TTG3/11 |     |                      | External trigger input pins of PPG timer     |

|            | P15_0 to P15_3    |     |                      | General-purpose input/output ports           |

| 134 to 137 | OCU0 to OCU3      | I/O | A                    | Output compare output pins                   |

|            | TOT0 to TOT3      |     |                      | Reload timer output pins                     |

| 400 + 440  | P27_0 to P27_5    | 1/0 |                      | General-purpose input/output ports           |

| 138 to 143 | AN16 to AN21      | I/O | В                    | Analog input pins of A/D converter           |

<sup>\* :</sup> For information about the I/O circuit type, refer to "■ I/O CIRCUIT TYPES".

[Power supply/Ground pins]

| i ower suppry/Ground pinsj                 |          |        |                                                     |  |  |  |

|--------------------------------------------|----------|--------|-----------------------------------------------------|--|--|--|

| Pin no.                                    | Pin name | I/O    | Function                                            |  |  |  |

| 1, 19, 37, 55, 73, 81, 86,<br>91, 109, 127 | VSS5     |        | Ground pins                                         |  |  |  |

| 54, 72, 90, 108, 126                       | VDD5     |        | Power supply pins                                   |  |  |  |

| 88, 89                                     | VDD5R    |        | Power supply pins for internal regulator            |  |  |  |

| 105                                        | AVSS5    | Supply | Analog ground pin for A/D converter                 |  |  |  |

| 107                                        | AVCC5    |        | Power supply pin for A/D converter                  |  |  |  |

| 106                                        | AVRH5    |        | Reference power supply pin for A/D converter        |  |  |  |

| 87                                         | VCC18C   |        | Capacitor connection pin for internal regulator     |  |  |  |

| 18, 36, 144                                | VDD35    |        | Power supply pins for external bus part of I/O ring |  |  |  |

|                                            |          |        |                                                     |  |  |  |

<sup>\* :</sup> For information about the I/O circuit type, refer to "■ I/O CIRCUIT TYPES".

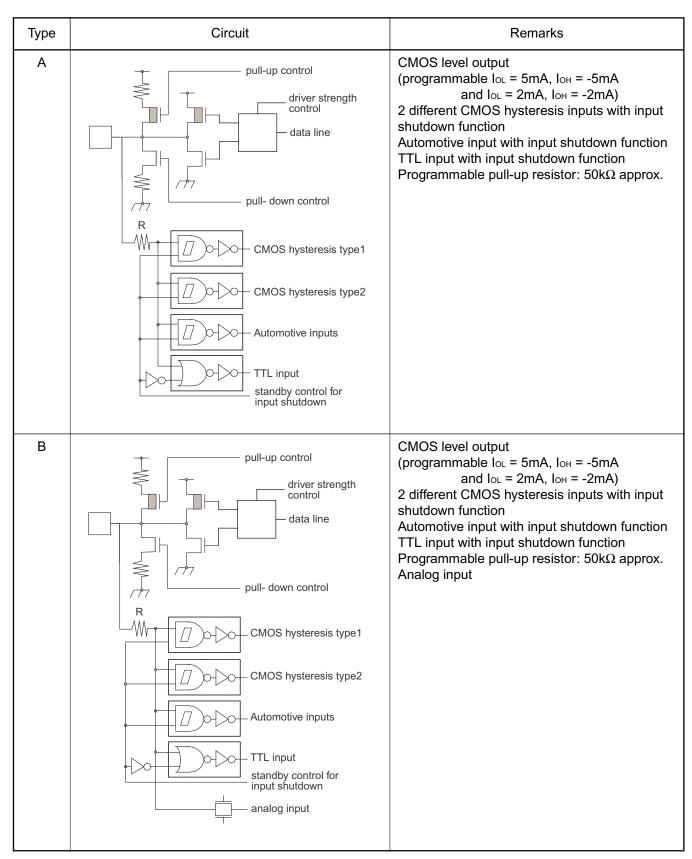

#### **■ I/O CIRCUIT TYPES**

| Туре | Circuit                                                                                                                                                              | Remarks                                                                                                                                                                                                                                                 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| С    | pull-up control  data line  pull- down control  R  CMOS hysteresis type1  CMOS hysteresis type2  Automotive inputs  TTL input standby control for input shutdown     | CMOS level output (Iol = 3mA, Ioh = -3mA) 2 different CMOS hysteresis inputs with input shutdown function Automotive input with input shutdown function TTL input with input shutdown function Programmable pull-up resistor: 50kΩ approx.              |

| D    | pull-up control  data line  pull- down control  R  CMOS hysteresis type1  CMOS hysteresis type2  Automotive inputs  standby control for input shutdown  analog input | CMOS level output (IoL = 3mA, IoH = -3mA) 2 different CMOS hysteresis inputs with input shutdown function Automotive input with input shutdown function TTL input with input shutdown function Programmable pull-up resistor: 50kΩ approx. Analog input |

| Туре | Circuit                                                                                                                                                                                       | Remarks                                                                                                                                                                                                                                                                                                                                                                                             |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E    | pull-up control  driver strength control  data line  pull- down control  R  CMOS hysteresis type1  CMOS hysteresis type2  Automotive inputs  TTL input  standby control for input shutdown    | CMOS level output (programmable IoL = 5mA, IoH = -5mA                                                                                                                                                                                                                                                                                                                                               |

| F    | pull-up control  driver strength control  data line  pull- down control  R  CMOS hysteresis type1  CMOS hysteresis type2  Automotive inputs  standby control for input shutdown  analog input | CMOS level output (programmable Io <sub>L</sub> = 5mA, Io <sub>H</sub> = -5mA and Io <sub>L</sub> = 2mA, Io <sub>H</sub> = -2mA, and Io <sub>L</sub> = 30mA, Io <sub>H</sub> = -30mA) 2 different CMOS hysteresis inputs with input shutdown function Automotive input with input shutdown function TTL input with input shutdown function Programmable pull-up resistor: 50kΩ approx. Analog input |

| Туре | Circuit                             | Remarks                                                                                                                                                                                                                                                                                                                                                                               |

|------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G    | R Hysteresis inputs                 | Mask ROM and EVA device: CMOS Hysteresis input pin Flash device: CMOS input pin 12 V withstand (for MD [2:0])                                                                                                                                                                                                                                                                         |

| Н    | Pull-up Resistor  Hysteresis inputs | CMOS Hysteresis input pin Pull-up resistor value: 50 kΩ approx.                                                                                                                                                                                                                                                                                                                       |

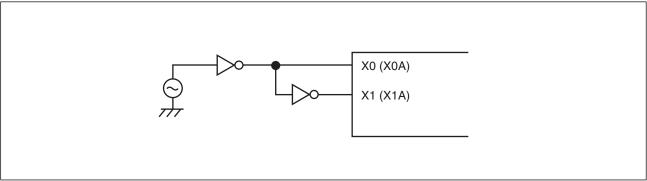

| J1   | X1 R O Xout FCI or osc disable      | <ul> <li>High-speed oscillation circuit:</li> <li>Programmable between oscillation mode (external crystal or resonator connected to X0/X1 pins) and Fast external Clock Input (FCI) mode (external clock connected to X0 pin)</li> <li>Feedback resistor = approx. 2 * 0.5 MΩ. Feedback resistor is grounded in the center when the oscillator is disabled or in FCI mode.</li> </ul> |

| J2   | X1A Xout  R  XOA  Osc disable       | <ul> <li>Low-speed oscillation circuit:</li> <li>Feedback resistor = approx. 2 * 5 MΩ.</li> <li>Feedback resistor is grounded in the center when the oscillator is disabled.</li> </ul>                                                                                                                                                                                               |

| Туре | Circuit                                                                                                                                                                                     | Remarks                                               |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| К    | pull-up control  driver strength control  data line  pull- down control  R  CMOS hysteresis type1  CMOS hysteresis type2  Automotive inputs  standby control for input shutdown LCD SEG/COM | CMOS level output (programmable IoL = 5mA, IoH = -5mA |

| L    | pull-up control  driver strength control  data line  pull- down control  R  CMOS hysteresis type1  CMOS hysteresis type2  Automotive inputs  standby control for input shutdown  VLCD       | CMOS level output (programmable IoL = 5mA, IoH = -5mA |

| Туре | Circuit                     | Remarks                                             |

|------|-----------------------------|-----------------------------------------------------|

| М    | tri-state control data line | CMOS level tri-state output (IoL = 5mA, IoH = -5mA) |

| N    | analog input line           | Analog input pin with protection                    |

#### **■ HANDLING DEVICES**

#### 1. Preventing Latch-up

Latch-up may occur in a CMOS IC if a voltage higher than ( $V_{DD}5$ ,  $V_{DD}35$  or  $HV_{DD}5$  \*1) or less than ( $V_{SS}5$  or  $HV_{SS}5$  \*1) is applied to an input or output pin or if a voltage exceeding the rating is applied between the power supply pins and ground pins. If latch-up occurs, the power supply current increases rapidly, sometimes resulting in thermal breakdown of the device. Therefore, be very careful not to apply voltages in excess of the absolute maximum ratings.

Note \*1: HV<sub>DD</sub>5, HV<sub>SS</sub>5 are available only on devices having Stepper Motor Controller.

#### 2. Handling of unused input pins

If unused input pins are left open, abnormal operation may result. Any unused input pins should be connected to pull-up or pull-down resistor ( $2K\Omega$  to  $10K\Omega$ ) or enable internal pullup or pulldown resisters (PPER/PPCR) before the input enable (PORTEN) is activated by software. The mode pins MD\_x can be connected to Vss5 or VDD5 directly. Unused ALARM input pins can be connected to AVss5 directly.

#### 3. Power supply pins

In MB91460 series, devices including multiple power supply pins and ground pins are designed as follows; pins necessary to be at the same potential are interconnected internally to prevent malfunctions such as latch-up. All of the power supply pins and ground pins must be externally connected to the power supply and ground respectively in order to reduce unnecessary radiation, to prevent strobe signal malfunctions due to the ground level rising and to follow the total output current ratings. Furthermore, the power supply pins and ground pins of the MB91460 series must be connected to the current supply source via a low impedance.

It is also recommended to connect a ceramic capacitor of approximately 0.1  $\mu$ F as a bypass capacitor between power supply pin and ground pin near this device.

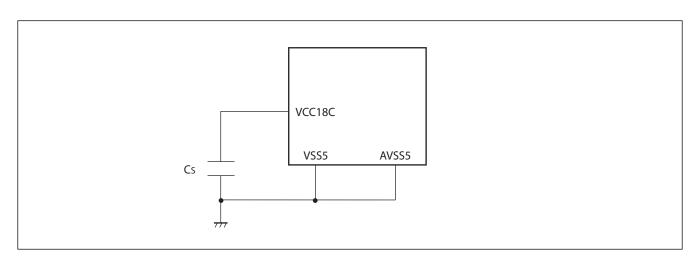

This series has a built-in step-down regulator. Connect a bypass capacitor of 4.7  $\mu$ F (use a X7R ceramic capacitator) to VCC18C pin for the regulator.

#### 4. Crystal oscillator circuit

Noise in proximity to the X0 (X0A) and X1 (X1A) pins can cause the device to operate abnormally. Printed circuit boards should be designed so that the X0 (X0A) and X1 (X1A) pins, and crystal oscillator, as well as bypass capacitors connected to ground, are located near the device and ground.

It is recommended that the printed circuit board layout be designed such that the X0 and X1 pins or X0A and X1A pins are surrounded by ground plane for the stable operation.

Please request the oscillator manufacturer to evaluate the oscillational characteristics of the crystal and this device.

#### 5. Notes on using external clock

When using the external clock, it is necessary to simultaneously supply the X0 (X0A) and the X1 (X1A) pins. In the described combination, X1 (X1A) should be supplied with a clock signal which has the opposite phase to the X0 (X0A) pins. At X0 and X1, a frequency up to 16 MHz is possible.

(Continued)

#### (Continued)

Example of using opposite phase supply

#### 6. Mode pins (MD\_x)

These pins should be connected directly to the power supply or ground pins. To prevent the device from entering test mode accidentally due to noise, minimize the lengths of the patterns between each mode pin and power supply pin or ground pin on the printed circuit board as possible and connect them with low impedance.

#### 7. Notes on operating in PLL clock mode

If the oscillator is disconnected or the clock input stops when the PLL clock is selected, the microcontroller may continue to operate at the free-running frequency of the self-oscillating circuit of the PLL. However, this self-running operation cannot be guaranteed.

#### 8. Pull-up control

The AC standard is not guaranteed in case a pull-up resistor is connected to the pin serving as an external bus pin.

#### **■ NOTES ON DEBUGGER**

#### 1. Execution of the RETI Command

If single-step execution is used in an environment where an interrupt occurs frequently, the corresponding interrupt handling routine will be executed repeatedly to the exclusion of other processing. This will prevent the main routine and the handlers for low priority level interrupts from being executed (For example, if the time-base timer interrupt is enabled, stepping over the RETI instruction will always break on the first line of the time-base timer interrupt handler).

Disable the corresponding interrupts when the corresponding interrupt handling routine no longer needs debugging.

#### 2. Break function

If the range of addresses that cause a hardware break (including event breaks) is set to the address of the current system stack pointer or to an area that contains the stack pointer, execution will break after each instruction regardless of whether the user program actually contains data access instructions.

To prevent this, do not set (word) access to the area containing the address of the system stack pointer as the target of the hardware break (including an event breaks).

#### 3. Operand break

It may cause malfunctions if a stack pointer exists in the area which is set as the DSU operand break. Do not set the access to the areas containing the address of system stack pointer as a target of data event break.

#### 4. Notes on PS register

As the PS register is processed in advance by some instructions, when the debugger is being used, the exception handling may result in execution breaking in an interrupt handling routine or the displayed values of the flags in the PS register being updated.

As the microcontroller is designed to carry out reprocessing correctly upon returning from such an EIT event, the operation before and after the EIT always proceeds according to specification.

#### The following behavior may occur if any of the following occurs in the instruction immediately after a DIV0U/DIV0S instruction:

- (a) a user interrupt or NMI is accepted;

- (b) single-step execution is performed;

- (c) execution breaks due to a data event or from the emulator menu.

- 1. D0 and D1 flags are updated in advance.

- 2. An EIT handling routine (user interrupt/NMI or emulator) is executed.

- 3. Upon returning from the EIT, the DIV0U/DIV0S instruction is executed and the D0 and D1 flags are updated to the same values as those in 1.

# • The following behavior occurs when an ORCCR, STILM, MOV Ri,PS instruction is executed to enable a user interrupt or NMI source while that interrupt is in the active state.

- 1. The PS register is updated in advance.

- 2. An EIT handling routine (user interrupt/NMI or emulator) is executed.

- 3. Upon returning from the EIT, the above instructions are executed and the PS register is updated to the same value as in 1.

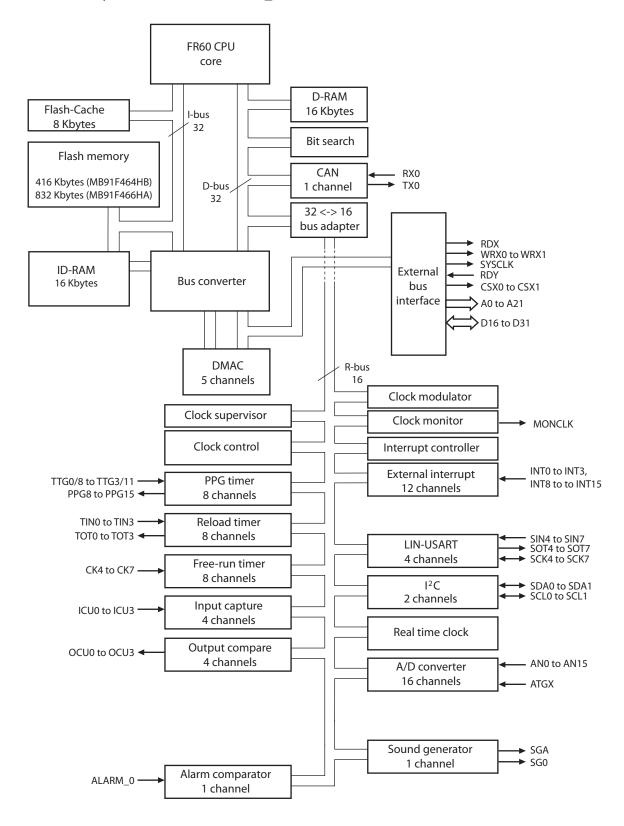

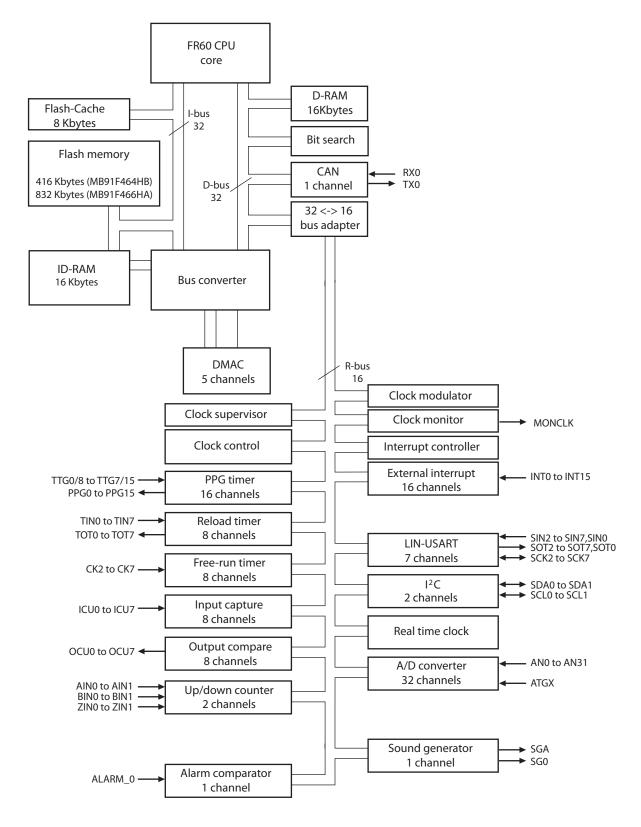

#### **■ BLOCK DIAGRAM**

### 1. MB91F464HB, MB91F466HA with MD\_3=1

### 2. MB91F464HB, MB91F466HA with MD\_3=0

#### **■ CPU AND CONTROL UNIT**

The FR family CPU is a high performance core that is designed based on the RISC architecture with advanced instructions for embedded applications.

#### 1. Features

· Adoption of RISC architecture

Basic instruction: 1 instruction per cycle

- General-purpose registers: 32-bit 16 registers

- · 4 Gbytes linear memory space

- · Multiplier installed

32-bit 32-bit multiplication: 5 cycles

16-bit 16-bit multiplication: 3 cycles

· Enhanced interrupt processing function

Quick response speed (6 cycles)

Multiple-interrupt support

Level mask function (16 levels)

• Enhanced instructions for I/O operation

Memory-to-memory transfer instruction

Bit processing instruction

Basic instruction word length: 16 bits

Low-power consumption Sleep mode/stop mode

#### 2. Internal architecture

- The FR family CPU uses the Harvard architecture in which the instruction bus and data bus are independent of each other.

- A 32-bit

← 16-bit buffer is connected to the 32-bit bus (D-bus) to provide an interface between the CPU and peripheral resources.

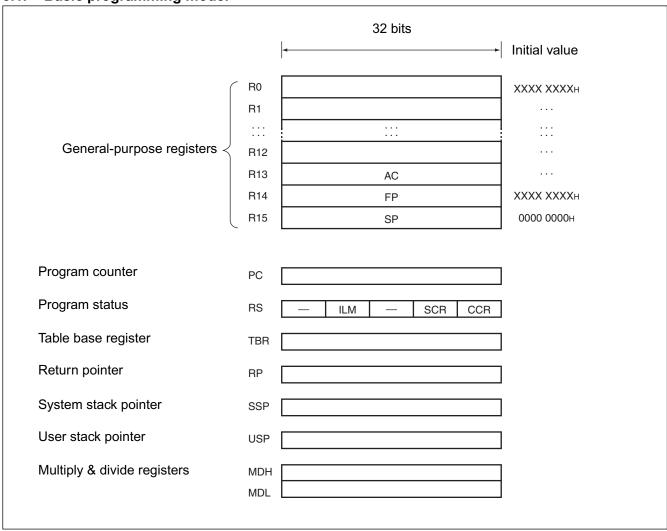

### 3. Programming model

3.1. Basic programming model

#### 4. Registers

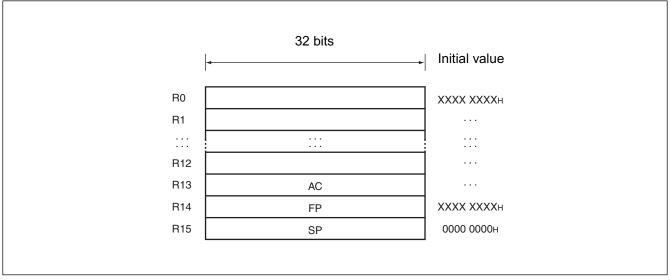

#### 4.1. General-purpose register

Registers R0 to R15 are general-purpose registers. These registers can be used as accumulators for computation operations and as pointers for memory access.

Of the 16 registers, enhanced commands are provided for the following registers to enable their use for particular applications.

R13: Virtual accumulator

R14 : Frame pointer R15 : Stack pointer

Initial values at reset are undefined for R0 to R14. The value for R15 is 00000000H (SSP value).

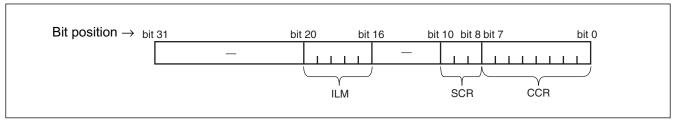

#### 4.2. PS (Program Status)

This register holds the program status, and is divided into three parts, ILM, SCR, and CCR.

All undefined bits (-) in the diagram are reserved bits. The read values are always "0". Write access to these bits is invalid.

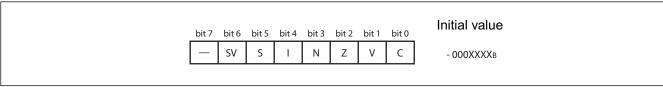

### 4.3. CCR (Condition Code Register)

SV: Supervisor flag

S : Stack flag

I : Interrupt enable flagN : Negative enable flag

Z : Zero flag

V : Overflow flag

C : Carry flag

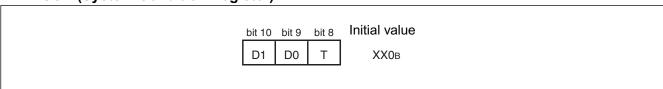

### 4.4. SCR (System Condition Register)

Flag for step division (D1, D0)

This flag stores interim data during execution of step division.

Step trace trap flag (T)

This flag indicates whether the step trace trap is enabled or disabled.

The step trace trap function is used by emulators. When an emulator is in use, it cannot be used in execution of user programs.

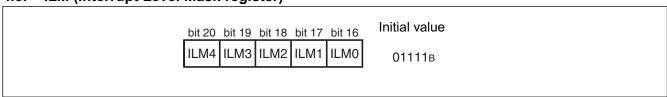

#### 4.5. ILM (Interrupt Level Mask register)

This register stores interrupt level mask values, and the values stored in ILM4 to ILM0 are used for level masking. The register is initialized to value "01111<sub>B</sub>" at reset.

#### 4.6. PC (Program Counter)

| bit 31 | bit 0 | Initial value |

|--------|-------|---------------|

|        |       |               |

The program counter indicates the address of the instruction that is being executed.

The initial value at reset is undefined.

| 4.7. TBR (Table Base Register)                                                                                           |  |

|--------------------------------------------------------------------------------------------------------------------------|--|

| bit 31 bit 0 Initial value                                                                                               |  |

| 000FFC00н                                                                                                                |  |

|                                                                                                                          |  |

| The table base register stores the starting address of the vector table used in EIT processing                           |  |

| The initial value at reset is 000FFC00н.                                                                                 |  |

|                                                                                                                          |  |

| 4.8. RP (Return Pointer)                                                                                                 |  |

| bit 31 bit 0 Initial value                                                                                               |  |

| XXXXXXXH                                                                                                                 |  |

| AAAAAAAII                                                                                                                |  |

| The return pointer stores the address for return from subroutines.                                                       |  |

| During execution of a CALL instruction, the PC value is transferred to this RP register.                                 |  |

| During execution of a RET instruction, the contents of the RP register are transferred to PC.                            |  |

| The initial value at reset is undefined.                                                                                 |  |

|                                                                                                                          |  |

| 4.9. USP (User Stack Pointer)                                                                                            |  |

| la itial valva                                                                                                           |  |

| bit 31 bit 0 Initial value                                                                                               |  |

| XXXXXXXH                                                                                                                 |  |

| T                                                                                                                        |  |

| The user stack pointer, when the S flag is "1", this register functions as the R15 register.                             |  |

| <ul> <li>The USP register can also be explicitly specified.</li> <li>The initial value at reset is undefined.</li> </ul> |  |

| This register cannot be used with RETI instructions.                                                                     |  |

| This register cannot be used with NETT instructions.                                                                     |  |

| 4.10. Multiply & divide registers                                                                                        |  |