available (EXTM). An appropriate DC blocking capacitor must be used to couple the modulating signal source to the EXTM pin. When external modulation is not used, the relevant pin can be left open.

Two pins are dedicated to the overcurrent protection/monitoring: CEXT and OLF. The overcurrent protection circuit works dynamically: as soon as an overload is detected in either LNB output, the output is shut-down for a time Toff determined by the capacitor connected between CEXT and GND. Simultaneously the OLF pin, that is an open collector diagnostic output flag, from HIGH IMPEDANCE state goes LOW.

After the time has elapsed, the output is resumed for a time  $t_{on}=1/15t_{off}$  (typ.) and OLF goes in HIGH

IMPEDANCE. If the overload is still present, the protection circuit will cycle again through  $t_{off}$  and ton until the overload is removed. Typical  $t_{on}+t_{off}$  value is 1200ms when a  $4.7\mu$ F external capacitor is used.

This dynamic operation can greatly reduce the power dissipation in short circuit condition, still ensuring excellent power-on start up even with highly capacitive loads on LNB outputs.

The device is packaged in Multiwatt15 for thru-holes mounting and in PowerSO-20 for surface mounting. When a limited functionality in a smaller package matches design needs, a range of cost-effective PowerSO-10 solutions is also offered. All versions have built-in thermal protection against overheating damage.

(\*): External components are needed to comply to level 2.x and above (bidirectiona) DiSEqC<sup>™</sup> bus hardware requirements. DiSEqC<sup>™</sup> is a trademark or EUTELSAT.

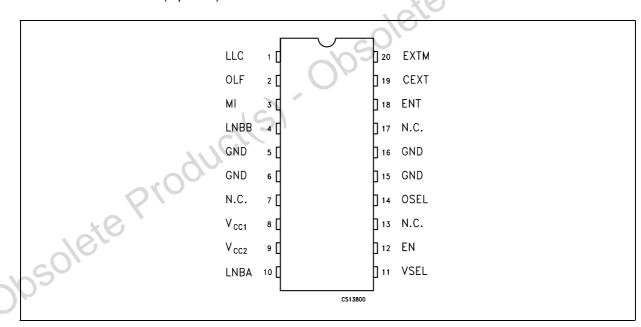

#### **PIN CONFIGURATION** (top view)

Downloaded from Arrow.com.

## TABLE A: PIN CONFIGURATIONS

| PIN N°          | SYMBOL           | NAME                                         | FUNCTION                                                                                                                             |  |  |  |

|-----------------|------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1               | LLC              | Line Length Compens.<br>(1V typ)             | Logic control input: see truth table                                                                                                 |  |  |  |

| 2               | OLF              | Over Load Flag                               | Logic output (open collector). Normally in HIGH<br>IMPEDANCE, goes LOW when current or thermal overload<br>occurs                    |  |  |  |

| 3               | MI               | Master Input                                 | In stand-by mode, the voltage on MI is routed to LNBA pin.<br>Can be left open if bypass function is not needed                      |  |  |  |

| 4               | LNBB             | Output Port                                  | See truth tables for voltage and port selection                                                                                      |  |  |  |

| 5, 6, 15,<br>16 | GND              | Ground                                       | Circuit Ground. It is internally connected to the die frame                                                                          |  |  |  |

| 7, 13           | N.C.             | Not Connected                                | 16                                                                                                                                   |  |  |  |

| 8               | V <sub>CC1</sub> | Supply Input 1                               | 15V to 27V supply. It is automatically selected when $V_{OUT}$ = 13 or 14V                                                           |  |  |  |

| 9               | V <sub>CC2</sub> | Supply Input 2                               | 22V to 27V supply. It is automatically selected when $V_{OUT}$ = 18 or 19V                                                           |  |  |  |

| 10              | LNBA             | Output Port                                  | See truth table voltage and port selection. In stand-by mode<br>this port is powered by the MI pin via the internal Bypass<br>Switch |  |  |  |

| 11              | V <sub>SEL</sub> | Output Voltage Selection:<br>13 or 18V (typ) | Logic control input: see truth table                                                                                                 |  |  |  |

| 12              | EN               | Port Enable                                  | Logic control input: see truth table                                                                                                 |  |  |  |

| 14              | OSEL             | Port Selection                               | Logic control input: see truth table                                                                                                 |  |  |  |

| 18              | ENT              | 22KHz Tone Enable                            | Logic control input: see truth table                                                                                                 |  |  |  |

| 19              | CEXT             | External Capacitor                           | Timing Capacitor used by the Dynamic Overload protection. Typical application is $4.7\mu F$ for a 1200ms cycle                       |  |  |  |

| 20              | EXTM             | External Modulator                           | External Modulation Input. Needs DC decoupling to the AC source. if not used, can be left open.                                      |  |  |  |

NOTE: the limited pin availability of the PowerSO-10 package leads to drop some functions.

## ABSOLUTE MAXIMUM RATINGS

| Symbol           | Parameter <sup>2</sup>                                      | Value              | Unit |

|------------------|-------------------------------------------------------------|--------------------|------|

| VI               | DC Input Voltage (V <sub>CC1</sub> , V <sub>CC2</sub> , MI) | 28                 | V    |

| I <sub>O</sub>   | Output Current (LNBA, LNBB)                                 | Internally Limited | mA   |

| CVI              | Logic Input Voltage (ENT, EN OSEL, VSEL, LLC)               | -0.5 to 7          | V    |

| T <sub>SW</sub>  | Bypass Switch Current                                       | 900                | mA   |

| PD               | Power Dissipation at T <sub>case</sub> < 85°C               | 3                  | W    |

| T <sub>stg</sub> | Storage Temperature Range                                   | -40 to +150        | °C   |

| T <sub>op</sub>  | Operating Junction Temperature Range                        | -40 to +125        | °C   |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these condition is not implied.

## THERMAL DATA

| Symbol                | Parameter                        | Value | Unit |

|-----------------------|----------------------------------|-------|------|

| R <sub>thj-case</sub> | Thermal Resistance Junction-case | 15    | °C/W |

# LNBK20D2

| CONTROL I/O    |                     | PIN NAME          |                     | L                                            | н                                    |  |

|----------------|---------------------|-------------------|---------------------|----------------------------------------------|--------------------------------------|--|

| OUT            |                     | OLF               |                     | $I_{OUT} > I_{OMAX}$ or $T_j > 150^{\circ}C$ | I <sub>OUT</sub> < I <sub>OMAX</sub> |  |

|                | IN                  | ENT               |                     | 22KHz tone OFF                               | 22KHz tone ON                        |  |

|                | IN                  | EN                |                     | See Table Below                              | See Table Below                      |  |

|                | IN                  | OSEL              |                     | See Table Below                              | See Table Below                      |  |

| IN             |                     | VSEL              |                     | See Table Below                              | See Table Below                      |  |

|                | IN                  | LLC               |                     | See Table Below                              | See Table Below                      |  |

| EN             | OSEL                | VSEL              | LLCO                | V <sub>LNBA</sub>                            | V <sub>LNBB</sub>                    |  |

| L              | Х                   | Х                 | Х                   | V <sub>MI</sub> - 0.4V (typ.)                | Disabled                             |  |

| Н              | L                   | L                 | L                   | 13V (typ.)                                   | Disabled                             |  |

| Н              | L                   | Н                 | L                   | 18V (typ.)                                   | Disabled                             |  |

| Н              | L                   | L                 | Н                   | 14V (typ.)                                   | Disabled                             |  |

| Н              | L                   | Н                 | Н                   | 19V (typ.)                                   | Disabled                             |  |

| Н              | Н                   | L                 | L                   | Disabled                                     | 13V (typ.)                           |  |

| Н              | Н                   | Н                 | L                   | Disabled                                     | 18V (typ.)                           |  |

| Н              | Н                   | L                 | Н                   | Disabled                                     | 14V (typ.)                           |  |

| Н              | Н                   | Н                 | Н                   | Disabled                                     | 19V (typ.)                           |  |

| DTE: All logic | input pins have int | ernal pull-down r | esistor (typ. = 250 |                                              |                                      |  |

#### LOGIC CONTROLS TRUTH TABLE

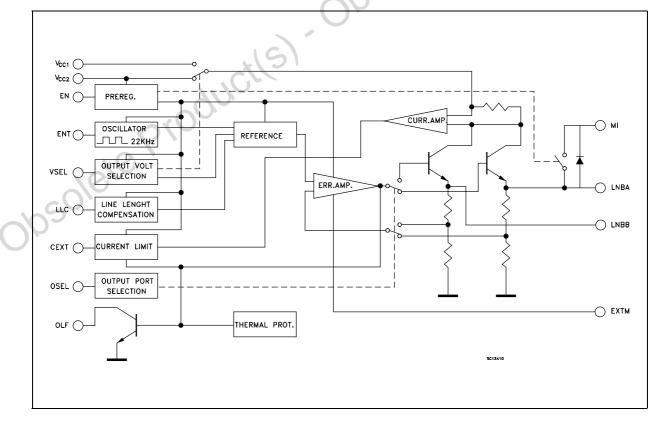

## **BLOCK DIAGRAM**

57

4/14

| Symbol                          | Parameter                                      | Test Conditions                                                                         | Min.          | Тур.                 | Max. | Unit |

|---------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------|---------------|----------------------|------|------|

| V <sub>IN1</sub>                | V <sub>CC1</sub> Supply Voltage                | I <sub>O</sub> = 400 mA ENT=H, VSEL=L, LLC=L                                            | 15            |                      | 27   | V    |

|                                 | I <sub>O</sub> = 400 mA ENT=H, VSEL=L,         |                                                                                         | 16            |                      | 27   | V    |

| V <sub>IN2</sub>                | V <sub>CC2</sub> Supply Voltage                | I <sub>O</sub> = 400 mA ENT=H, VSEL=L, LLC=L                                            | 22            |                      | 27   | V    |

|                                 |                                                | I <sub>O</sub> = 400 mA VSEL=L, LLC=H                                                   | 23            |                      | 27   | V    |

| V <sub>O1</sub>                 | Output Voltage                                 | I <sub>O</sub> = 400 mA VSEL=L, LLC=L                                                   | 17.3          | 18                   | 18.7 | V    |

|                                 |                                                | I <sub>O</sub> = 400 mA ENT=H, VSEL=L, LLC=H                                            |               | 19                   |      | V    |

| V <sub>O2</sub>                 | Output Voltage                                 | I <sub>O</sub> = 400 mA VSEL=L, LLC=L                                                   | 12.5          | 13                   | 13.5 | V    |

|                                 |                                                | I <sub>O</sub> = 400 mA ENT=H, VSEL=L, LLC=H                                            |               | 14                   |      | V    |

| $\Delta V_{O}$                  | Line Regulation                                | V <sub>IN1</sub> =15 to 18V V <sub>OUT</sub> =13V                                       |               | 5                    | 50   | mV   |

|                                 |                                                | V <sub>IN2</sub> =22 to 25V V <sub>OUT</sub> =18V                                       |               | 5                    | 50   | mV   |

| $\Delta V_{O}$                  | Load Regulation                                | $V_{IN1} = V_{IN2} = 22V$ $V_{OUT} = 13 \text{ or } 18V$<br>$I_{O} = 0 \text{ to } 3A$  |               | 65                   | 150  | mV   |

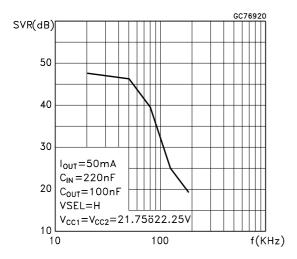

| SVR                             | Supply Voltage Rejection                       | V <sub>IN1</sub> = V <sub>IN2</sub> = 23 ± 0.5V <sub>ac</sub> f <sub>ac</sub> = 120 Hz, | $\mathcal{O}$ | 45                   |      | dB   |

| I <sub>MAX</sub>                | Output Current Limiting                        | ß                                                                                       | 500           | 650                  | 800  | mA   |

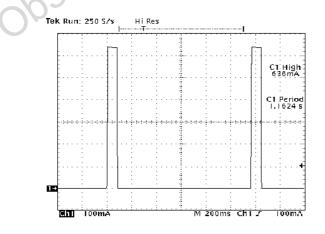

| t <sub>OFF</sub>                | Dynamic Overload<br>protection OFF Time        | Output Shorted $C_{EXT} = 4.7 \mu F$                                                    |               | 1100                 |      | ms   |

| t <sub>ON</sub>                 | Dynamic Overload<br>protection ON Time         | Output Shorted $C_{EXT} = 4.7 \mu F$                                                    |               | t <sub>OFF</sub> /15 |      | ms   |

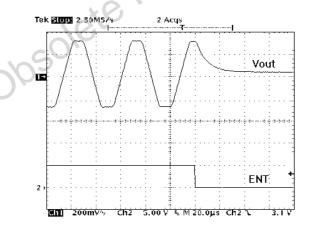

| f <sub>TONE</sub>               | Tone Frequency                                 | ENT=H                                                                                   | 20            | 22                   | 24   | KHz  |

| A <sub>TONE</sub>               | Tone Amplitude                                 | ENT=H                                                                                   | 0.55          | 0.72                 | 0.9  | Vpp  |

| D <sub>TONE</sub>               | Tone Duty Cycle                                | ENT=H                                                                                   | 40            | 50                   | 60   | %    |

| t <sub>r</sub> , t <sub>f</sub> | Tone Rise and Fall Time                        | ENT=H                                                                                   | 5             | 10                   | 15   | μs   |

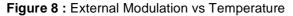

| G <sub>EXTM</sub>               | External Modulation Gain                       | $\Delta V_{OUT} / \Delta V_{EXTM}$ , f = 10Hz to 40KHz                                  |               | 5                    |      |      |

| V <sub>EXTM</sub>               | External Modulation Input<br>Voltage           | AC Coupling                                                                             |               |                      | 400  | mVpp |

| Z <sub>EXTM</sub>               | External Modulation<br>Impedance               | f = 10Hz to 40KHz                                                                       |               | 400                  |      | Ω    |

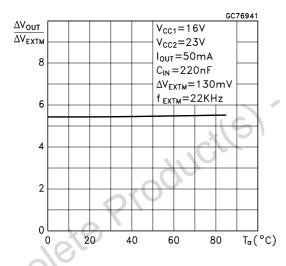

| V <sub>SW</sub>                 | Bypass Switch Voltage<br>Drop (MI to LNBA)     | EN=L, I <sub>SW</sub> =300mA, V <sub>CC2</sub> -V <sub>MI</sub> =4V                     |               | 0.35                 | 0.6  | V    |

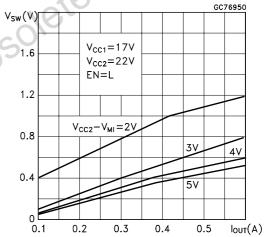

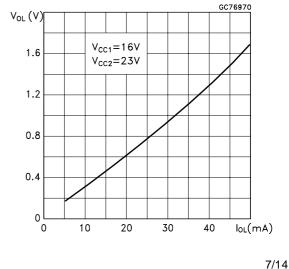

| VoL                             | Overload Flag Pin Logic<br>LOW                 | I <sub>OL</sub> =8mA                                                                    |               | 0.28                 | 0.5  | V    |

| loz                             | Overload Flag Pin OFF<br>State Leakage Current | V <sub>OH</sub> = 6V                                                                    |               |                      | 10   | μA   |

| V <sub>IL</sub>                 | Control Input Pin Logic<br>LOW                 |                                                                                         |               |                      | 0.8  | V    |

| $V_{IH}$                        | Control Input Pin Logic<br>HIGH                |                                                                                         | 2.5           |                      |      | V    |

| I <sub>IH</sub>                 | Control Pins Input Current                     | V <sub>IH</sub> = 5V                                                                    |               | 20                   |      | μΑ   |

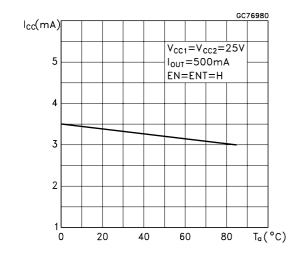

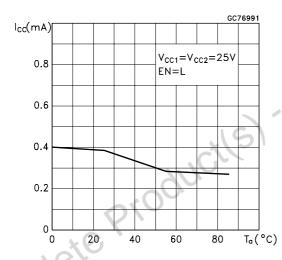

| I <sub>CC</sub>                 | Supply Current                                 | Output Disabled (EN=L)                                                                  |               | 0.3                  | 1    | mA   |

|                                 |                                                | ENT=H, I <sub>OUT</sub> =500mA                                                          |               | 3.1                  | 6    | mA   |

| I <sub>OBK</sub>                | Output Backward Current                        |                                                                                         |               | 0.2                  | 3    | mA   |

| T <sub>SHDN</sub>               | Temperature Shutdown<br>Threshold              |                                                                                         |               | 150                  |      | °C   |

**ELECTRICAL CHARACTERISTICS FOR LNBK SERIES** (T<sub>J</sub> = 0 to 85°C, C<sub>I</sub> =  $0.22\mu$ F, C<sub>O</sub> = $0.1\mu$ F, EN=H, ENT=L, LLC=L, V<sub>IN1</sub>=16V, V<sub>IN2</sub>=23V I<sub>OUT</sub>=50mA, unless otherwise specified.)

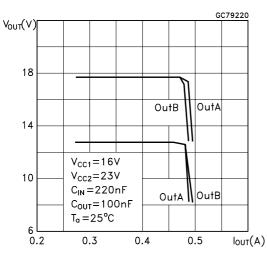

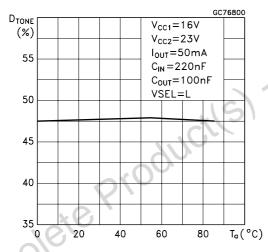

## **TYPICAL CHARACTERISTICS** (unless otherwise specified $T_i = 25^{\circ}C$ )

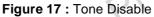

Figure 1 : Output Voltage vs Output Current

Figure 2 : Tone Duty Cycle vs Temperature

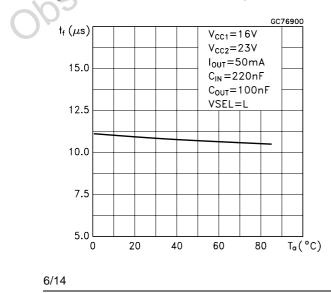

Figure 3 : Tone Fall Time vs Temperature

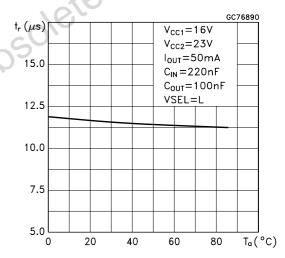

Figure 5 : Tone Rise Time vs Temperature

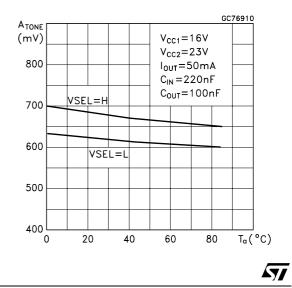

Figure 6 : Tone Amplitude vs Temperature

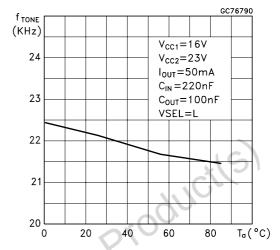

Figure 4 : Tone Frequency vs Temperature

Figure 7 : S.V.R. vs Frequency

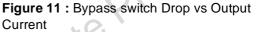

Figure 9 : Bypass Switch Drop vs Output Current

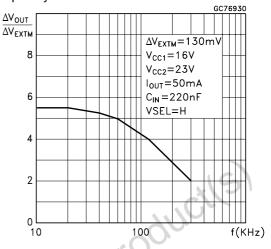

**Figure 10 :** LNBA External Modulation gain vs Frequency

Figure 13 : Supply Voltage vs Temperature

Figure 14 : Supply Current vs Temperature

Figure 15 : Dynamic Overload protection ( $I_{SC}$  vs Time)

8/14

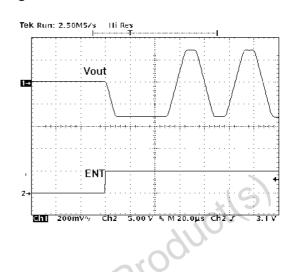

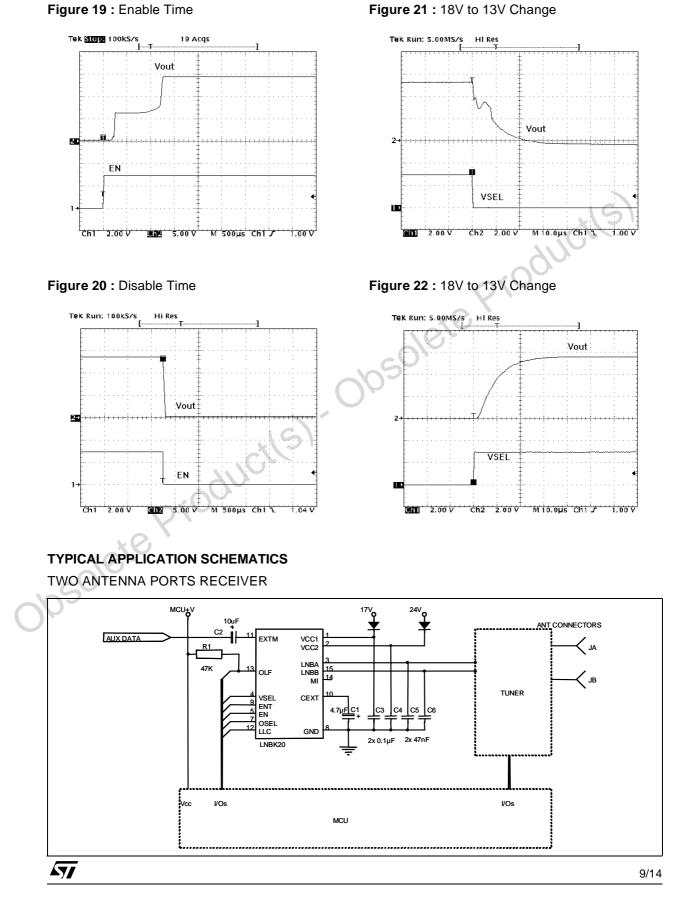

Figure 16 : Tone Enable

Figure 18: 22KHz Tone

Figure 19 : Enable Time

# LNBK20D2

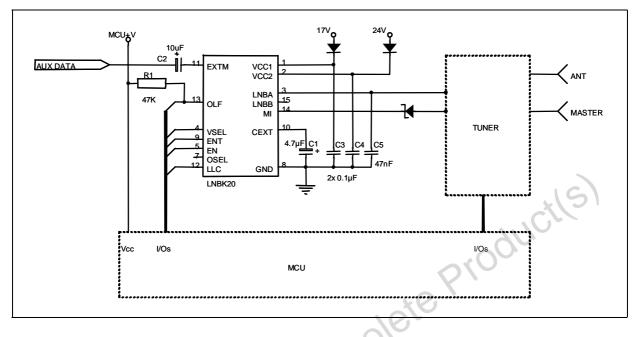

## SINGLE ANTENNA RECEIVER WITH MASTER RECEIVER PORT

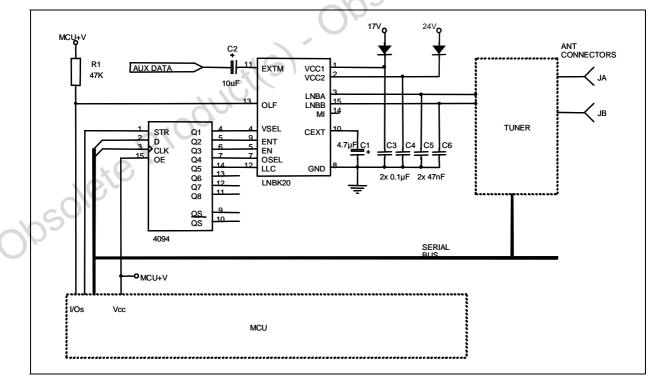

## USING SERIAL BUS TO SAVE MPU I/Os

57

#### 10/14

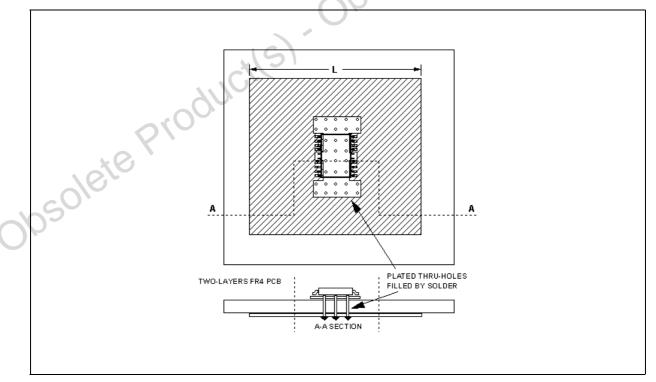

## THERMAL DESIGN NOTE

During normal operation, this device dissipates some power. At maximum rated output current (400mA), the voltage drop on the linear regulator lead to a total dissipated power that is of about 2W. The heat generated requires a suitable heatsink to keep the junction temperature below the over temperature protection threshold. Assuming a 40°C temperature inside the Set-Top-Box case, the total Rthj-amb has to be less than 43°C/W.

While this can be easily achieved using a through-hole power package that can be attached to a small heatsink or to the metallic frame of the receiver, a surface mount power package must rely on PCB solutions whose thermal efficiency is often limited. The simplest solution is to use a large, continuous copper area of the GND layer to dissipate the heat coming from the IC body.

The SO-20 package of this IC has 4 GND pins that are not just intended for electrical GND connection, but also to provide a low thermal resistance path between the silicon chip and the PCB heatsink. Given an Rthj-c equal to 15°C/W, a maximum of 28°C/W are left to the PCB heatsink. This figure is achieved if a minimum of 25cm<sup>2</sup> copper area is placed just below the IC body. This area can be the inner GND layer of a multi-layer PCB, or, in a dual layer PCB, an unbroken GND area even on the opposite side where the IC is placed. In both cases, the thermal path between the IC GND pins and the dissipating copper area must exhibit a low thermal resistance.

In figure 4, it is shown a suggested layout for the SO-20 package with a dual layer PCB, where the IC Ground pins and the square dissipating area are thermally connected through 32 vias holes, filled by solder. This arrangement, when L=50mm, achieves an Rthc-a of about 28°C/W.

Different layouts are possible, too. Basic principles, however, suggest to keep the IC and its ground pins approximately in the middle of the dissipating area; to provide as many vias as possible; to design a dissipating area having a shape as square as possible and not interrupted by other copper traces.

#### SO-20 SUGGESTED PCB HEATSINK LAYOUT

# LNBK20D2

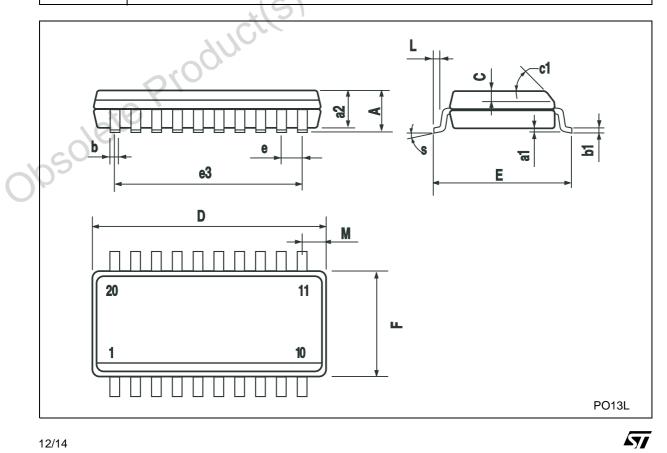

| SO-20 MECHANICAL DATA |       |       |               |       |       |       |  |  |

|-----------------------|-------|-------|---------------|-------|-------|-------|--|--|

|                       |       | mm.   |               |       | inch  |       |  |  |

| DIM.                  | MIN.  | ТҮР   | MAX.          | MIN.  | TYP.  | MAX.  |  |  |

| А                     |       |       | 2.65          |       |       | 0.104 |  |  |

| a1                    | 0.1   |       | 0.2           | 0.004 |       | 0.008 |  |  |

| a2                    |       |       | 2.45          |       |       | 0.096 |  |  |

| b                     | 0.35  |       | 0.49          | 0.014 |       | 0.019 |  |  |

| b1                    | 0.23  |       | 0.32          | 0.009 |       | 0.012 |  |  |

| С                     |       | 0.5   |               |       | 0.020 | 16    |  |  |

| c1                    |       |       | 45° (         | typ.) | 111   | 0     |  |  |

| D                     | 12.60 |       | 13.00         | 0.496 | 00    | 0.512 |  |  |

| Е                     | 10.00 |       | 10.65         | 0.393 |       | 0.419 |  |  |

| е                     |       | 1.27  |               | . 0.  | 0.050 |       |  |  |

| e3                    |       | 11.43 |               | 101   | 0.450 |       |  |  |

| F                     | 7.40  |       | 7.60          | 0.291 |       | 0.300 |  |  |

| L                     | 0.50  |       | 1.27          | 0.020 |       | 0.050 |  |  |

| М                     |       |       | 0.75          |       |       | 0.029 |  |  |

| M<br>S                |       |       | 0.75<br>8° (n |       |       | 0     |  |  |

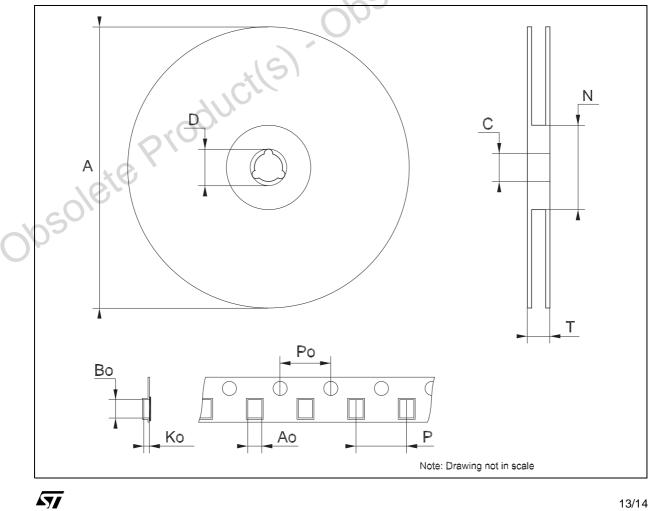

| DIM  | mm.  |     |      | inch  |      |        |

|------|------|-----|------|-------|------|--------|

| DIM. | MIN. | ТҮР | MAX. | MIN.  | TYP. | MAX.   |

| А    |      |     | 330  |       |      | 12.992 |

| С    | 12.8 |     | 13.2 | 0.504 |      | 0.519  |

| D    | 20.2 |     |      | 0.795 |      |        |

| Ν    | 60   |     |      | 2.362 |      |        |

| Т    |      |     | 30.4 |       |      | 1.197  |

| Ao   | 10.8 |     | 11   | 0.425 | 20   | 0.433  |

| Во   | 13.2 |     | 13.4 | 0.520 | 100  | 0.528  |

| Ko   | 3.1  |     | 3.3  | 0.122 |      | 0.130  |

| Po   | 3.9  |     | 4.1  | 0.153 |      | 0.161  |

| Р    | 11.9 |     | 12.1 | 0.468 |      | 0.476  |

Tape & Reel SO-20 MECHANICAL DATA

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

obsolete Product(s)- Obsolete Product(s)

© The ST logo is a registered trademark of STMicroelectronics

© 2003 STMicroelectronics - Printed in Italy - All Rights Reserved STMicroelectronics GROUP OF COMPANIES Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco

Singapore - Spain - Sweden - Switzerland - United Kingdom - United States. © http://www.st.com

@ mtp.//www.st.com