# Specifications

Absolute Maximum Ratings at Ta=25°C, VSS=0V. Items in parentheses refer to the LC72711LW.

| Parameter                        | Symbol          | Conditions                      | Ratings                      | Unit |

|----------------------------------|-----------------|---------------------------------|------------------------------|------|

| Maximum supply voltage           | V <sub>DD</sub> |                                 | (-0.3 to +5.5) -0.3 to +7.0  | V    |

| In put velte se                  | VIN1            | A0/CL, A1/CE, A2/DI, RST, STNBY | -0.3 to +7.0                 | V    |

| Input voltage                    | VIN2            | Pins other than VIN1            | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Output voltage                   | VOUT1           | DO                              | -0.3 to +7.0                 | V    |

|                                  | VOUT2           | Pins other than VOUT1           | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Output current                   | IOUT1           | INT, RDY, DREQ, and D0 to D15   | 0 to 4.0                     | mA   |

| Output current                   | IOUT2           | Pins other than IOUT1           | 0 to 2.0                     | mA   |

| Allowable output current (total) | ITTL            | Total for all the output pins   | 20                           | mA   |

| Allowable power dissipation      | Pd max          | Ta ≤ 85°C                       | 200                          | mW   |

| Operating temperature            | Topr            |                                 | -40 to +85                   | °C   |

| Storage temperature              | Tstg            |                                 | -55 to +125                  | °C   |

# [LC72711W] Allowable Operating Ranges at Ta=-40 to +85°C, VSS=0V

| Parameter                | Sumbol          | Conditions                                                                        |                    | Ratings |                    | Unit  |

|--------------------------|-----------------|-----------------------------------------------------------------------------------|--------------------|---------|--------------------|-------|

| Parameter                | Symbol          | Conditions                                                                        | min typ            |         | max                | Unit  |

| Supply voltage           | VDD             |                                                                                   | 4.5                |         | 5.5                | V     |

|                          | VIH1            | A0/CL, A1/CE, A2/DI, RST, STNBY                                                   | 0.7V <sub>DD</sub> |         | 5.5                | V     |

| High-level input voltage | VIH2            | DACK, WR, RD, CS, SP, BUSWD, A3, IOCNT1, IOCNT2                                   | 0.7VDD             |         | Vdd                | V     |

|                          | VIL1            | Pins for which VIH1 applies                                                       | VSS                |         | 0.3V <sub>DD</sub> | V     |

| Low-level input voltage  | VIL2            | Pins for which VIH2 applies                                                       | VSS                |         | 0.3V <sub>DD</sub> | V     |

| Oscillator frequency     | Fosc            | This IC operates with a frequency precision of ±250 ppm                           |                    | 7.2     |                    | MHz   |

| XIN input sensitivity    | V <sub>XI</sub> | With a sine wave input to XIN, capacitor coupling, V <sub>DD</sub> =+4.5 to +5.5V | 400                |         | 1500               | mVrms |

| Input amplitude          | VMPX            | With a 100% modulated composite signal input to MPXIN, VDD=+4.5 to +5.5V          | 150                |         | 400                | mVrms |

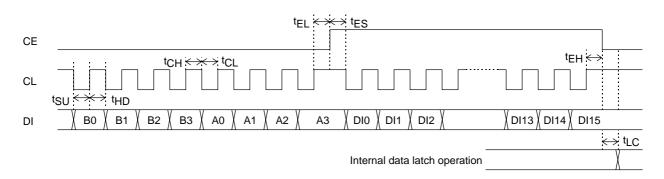

| [Serial I/O]             |                 | · · · · · ·                                                                       |                    | I       |                    |       |

| Clock low-level period   | tCL             | A0/CL                                                                             | 0.7                |         |                    | μS    |

| Clock high-level period  | tCH             | A0/CL                                                                             | 0.7                |         |                    | μS    |

| Data setup time          | tsu             | A0/CL, A2/DI                                                                      | 0.7                |         |                    | μS    |

| Data hold time           | tHD             | A0/CL, A2/DI                                                                      | 0.7                |         |                    | μS    |

| CE wait time             | tEL             | A0/CL, A1/CE                                                                      | 0.7                |         |                    | μS    |

| CE setup time            | tES             | A0/CL, A1/CE                                                                      | 0.7                |         |                    | μS    |

| CE hold time             | tEH             | A0/CL, A1/CE                                                                      | 0.7                |         |                    | μS    |

| Data latch change time   | tLC             | A1/CE                                                                             |                    |         | 0.7                | μS    |

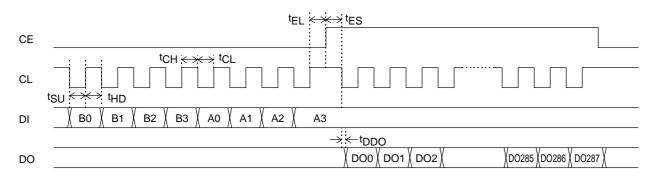

| Data output time         | tDDO            | DO, A0/CL                                                                         | 277                |         | 555                | nS    |

| CRC4 change time         | tCRC            | CRC4, A0/CL                                                                       |                    |         | 0.7                | μS    |

# [LC72711W]

# Allowable Operating Ranges: Parallel Interface at Ta=-40 to +85°C, VSS=0V

| Parameter                             | Symbol            | Conditions                                |     | Ratings |     | Unit |

|---------------------------------------|-------------------|-------------------------------------------|-----|---------|-----|------|

| Falameter                             | Symbol            | Conditions                                | min | typ     | max | Unit |

| [Parallel I/O]                        | ·                 |                                           |     |         |     |      |

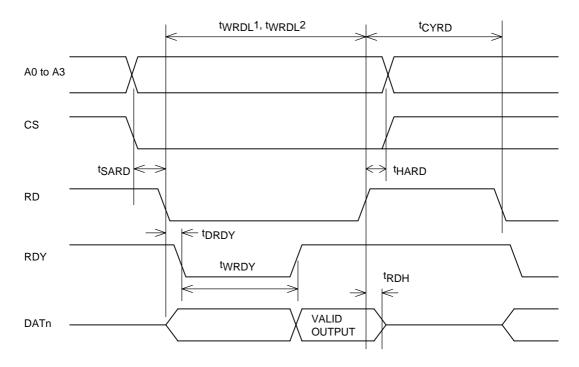

| Address to RD setup                   | <sup>t</sup> SARD | A0/CL, A1/CE, A2/DI, A3, RD               | 20  |         |     | nS   |

| RD to address hold                    | tHARD             | A0/CL, A1/CE, A2/DI, A3, RD, tWRDL=>250ns | -20 |         |     | nS   |

| RD low-level width                    | tWRDL1            | RD                                        | 250 |         |     | nS   |

| RD low-level width (when RDY is used) | tWRDL2            | RD                                        | 100 |         |     | nS   |

| RD cycle wait                         | tCYRD             | A0/CL, A1/CE, A2/DI, A3, RD               | 150 |         |     | nS   |

| RDY width (Register read)             | tWRDY             | RDY                                       | 60  |         | 210 | nS   |

| RD data hold                          | <sup>t</sup> RDH  | RD, DATn                                  | 0   |         |     | nS   |

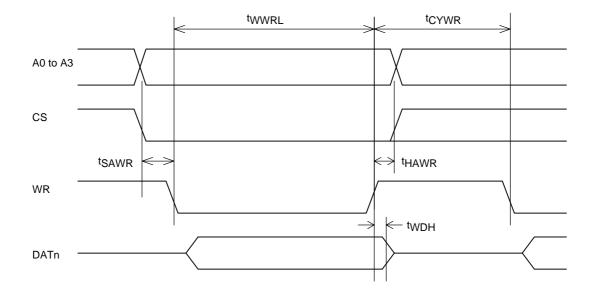

| Address to WR setup                   | tSAWR             | A0/CL, A1/CE, A2/DI, A3, WR               | 20  |         |     | nS   |

| WR to address hold                    | <sup>t</sup> HAWR | A0/CL, A1/CE, A2/DI, A3, WR               | 20  |         |     | nS   |

| WR cycle wait                         | tCYWR             | A0/CL, A1/CE, A2/DI, A3, WR               | 150 |         |     | nS   |

| WR low-level width                    | twwRL             | WR                                        | 200 |         |     | nS   |

| WR data hold                          | tWDH              | WR, DATn                                  | 0   |         |     | nS   |

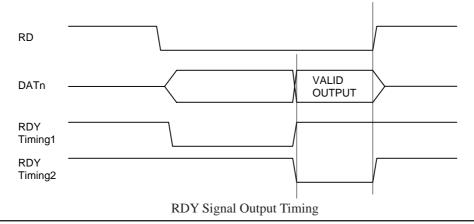

| RDY output delay                      | <sup>t</sup> DRDY | RD, RDY                                   | 0   |         | 30  | nS   |

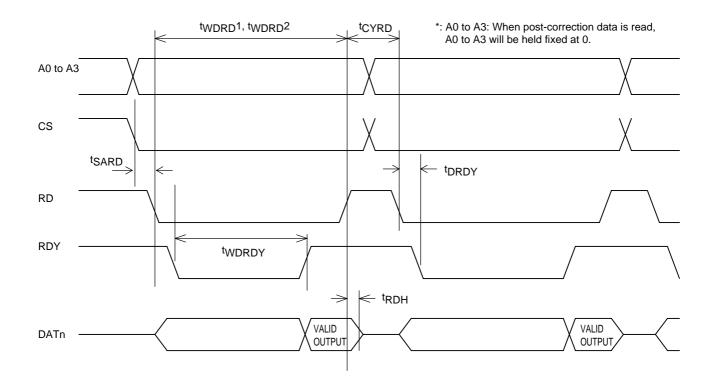

| Corrected autout DD width             | 4400001           | RD (BUSWD=L 8bits)                        | 300 |         |     | nS   |

| Corrected output RD width             | tWDRD1            | RD (BUSWD=H 16bits)                       | 540 |         |     | nS   |

| Corrected output RD width             | tur===2           | RD (BUSWD=L 8bits)                        | 100 |         |     | nS   |

| (when RDY is used)                    | tWDRD2            | RD (BUSWD=H 16bits)                       | 300 |         |     | nS   |

#### Continued from preceding page.

| Parameter                          | Symbol Conditions |                       |     | Ratings | Ratings |      |  |  |

|------------------------------------|-------------------|-----------------------|-----|---------|---------|------|--|--|

| Falanielei                         | Symbol            | Conditions            |     | typ     | max     | Unit |  |  |

| RDY width (corrected output read)  | twoppy            | RDY (BUSWD=L 8bits)   | 60  |         | 210     | nS   |  |  |

| (CDT width (confected output read) | tWDRDY            | RDY ((BUSWD=H 16bits) | 300 |         | 490     | nS   |  |  |

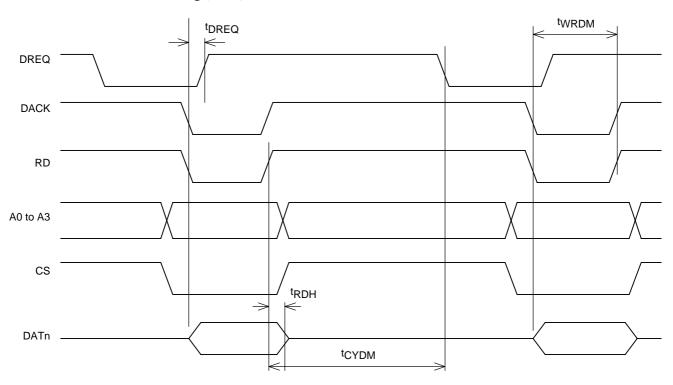

| DACK to DREQ delay                 | <sup>t</sup> DREQ | DREQ, DACK            |     |         | 260     | nS   |  |  |

| DMA cycle wait                     | <sup>t</sup> CYDM | RD, DREQ              |     |         | 420     | nS   |  |  |

| RD low-level width (DMA)           | tWRDM             | RD                    | 300 |         |         | nS   |  |  |

Notes: Application designs must take the RDY signal output delay into consideration if the RDY signal is used as the CPU bus wait signal.

If the RDY signal is not used, (that is, if no wait states are inserted) the value of the RD low-level width will be 250ns (minimum).

# [LC72711LW]

# Allowable Operating Ranges at Ta=-40 to +85°C, VSS=0V

| Parameter                       | Symbol | Conditions                                              |                    | Ratings |                    | Unit  |

|---------------------------------|--------|---------------------------------------------------------|--------------------|---------|--------------------|-------|

| Parameter                       | Symbol | Conditions                                              | min                | typ     | max                | Unit  |

| Supply voltage                  | VDD    |                                                         | 2.7                |         | 3.6                | V     |

| Link land in a track of the sec | VIH1   | A0/CL, A1/CE, A2/DI, RST, STNBY                         | 0.7VDD             |         | 5.5                | V     |

| High-level input voltage        | VIH2   | DACK, WR, RD, CS, SP, BUSWD, A3, IOCNT1, IOCNT2         | 0.7V <sub>DD</sub> |         | VDD                | V     |

|                                 | VIL1   | Pins for which VIH1 applies                             | VSS                |         | 0.3V <sub>DD</sub> | V     |

| Low-level input voltage         | VIL2   | Pins for which VIH2 applies                             | Vss                |         | 0.3VDD             | V     |

| Oscillator frequency            | Fosc   | This IC operates with a frequency precision of ±250 ppm |                    | 7.2     |                    | MHz   |

| VIN input consitivity           | Maria  | With a sine wave input to XIN, capacitor coupling,      | 400                |         | 000                |       |

| XIN input sensitivity           | VXI    | V <sub>DD</sub> =+2.7 to +3.6V                          |                    |         | 900                | mVrms |

|                                 | V/     | With a 100% modulated composite signal input to         | 120                |         | 350                | mVrms |

| Input amplitude                 | VMPX1  | MPXIN, V <sub>DD</sub> =+3.3V                           | 120                |         | 350                | mvrms |

|                                 | VMDV2  | With a 100% modulated composite signal input to         | 120                |         | 180                |       |

|                                 |        | MPXIN, V <sub>DD</sub> =+2.7V                           | 120                |         | 180                | mVrms |

| [Serial I/O]                    |        |                                                         |                    |         |                    |       |

| Clock low-level period          | tCL    | A0/CL                                                   | 0.7                |         |                    | μS    |

| Clock high-level period         | tCH    | A0/CL                                                   | 0.7                |         |                    | μS    |

| Data setup time                 | tSU    | A0/CL, A2/DI                                            | 0.7                |         |                    | μS    |

| Data hold time                  | tHD    | A0/CL, A2/DI                                            | 0.7                |         |                    | μS    |

| CE wait time                    | tEL    | A0/CL, A1/CE                                            | 0.7                |         |                    | μS    |

| CE setup time                   | tES    | A0/CL, A1/CE                                            | 0.7                |         |                    | μS    |

| CE hold time                    | tEH    | A0/CL, A1/CE                                            | 0.7                |         |                    | μS    |

| Data latch change time          | tLC    | A1/CE                                                   |                    |         | 0.7                | μS    |

| Data output time                | tDDO   | DO, A0/CL                                               | 277                |         | 555                | nS    |

| CRC4 change time                | tCRC   | CRC4, A0/CL                                             |                    |         | 0.7                | μS    |

# [LC72711LW]

# Allowable Operating Ranges: Parallel Interface at Ta=-40 to +85°C, VSS=0V

| Parameter                             | Symbol            | Conditions                                |     | Ratings |     | Unit |

|---------------------------------------|-------------------|-------------------------------------------|-----|---------|-----|------|

| Falameter                             | Symbol            | Conditions                                | min | typ     | max | Unit |

| [Parallel I/O]                        |                   |                                           |     |         |     |      |

| Address to RD setup                   | <sup>t</sup> SARD | A0/CL, A1/CE, A2/DI, A3, RD               | 20  |         |     | nS   |

| RD to address hold                    | tHARD             | A0/CL, A1/CE, A2/DI, A3, RD, tWRDL=>250ns | -20 |         |     | nS   |

| RD low-level width                    | tWRDL1            | RD                                        | 280 |         |     | nS   |

| RD low-level width (when RDY is used) | tWRDL2            | RD                                        | 100 |         |     | nS   |

| RD cycle wait                         | tCYRD             | A0/CL, A1/CE, A2/DI, A3, RD               | 150 |         |     | nS   |

| RDY width (Register read)             | tWRDY             | RDY                                       | 60  |         | 230 | nS   |

| RD data hold                          | <sup>t</sup> RDH  | RD, DATn                                  | 0   |         |     | nS   |

| Address to WR setup                   | <sup>t</sup> SAWR | A0/CL, A1/CE, A2/DI, A3, WR               | 20  |         |     | nS   |

| WR to address hold                    | <sup>t</sup> HAWR | A0/CL, A1/CE, A2/DI, A3, WR               | 20  |         |     | nS   |

| WR cycle wait                         | <sup>t</sup> CYWR | A0/CL, A1/CE, A2/DI, A3, WR               | 150 |         |     | nS   |

| WR low-level width                    | twwRL             | WR                                        | 200 |         |     | nS   |

| WR data hold                          | tWDH              | WR, DATn                                  | 0   |         |     | nS   |

| RDY output delay                      | <sup>t</sup> DRDY | RD, RDY                                   | 0   |         | 50  | nS   |

|                                       | t                 | RD (BUSWD=L 8bits)                        | 300 |         |     | nS   |

| Corrected output RD width             | tWDRD1            | RD (BUSWD=H 16bits)                       | 540 |         |     | nS   |

| Corrected output RD width             | t                 | RD (BUSWD=L 8bits)                        | 100 |         |     | nS   |

| (when RDY is used)                    | tWDRD2            | RD (BUSWD=H 16bits)                       | 300 |         |     | nS   |

|                                       | 4                 | RDY (BUSWD=L 8bits)                       | 60  |         | 230 | nS   |

| RDY width (corrected output read)     | tWDRDY            | RDY ((BUSWD=H 16bits)                     | 300 |         | 490 | nS   |

| DACK to DREQ delay                    | <sup>t</sup> DREQ | DREQ, DACK                                |     |         | 260 | nS   |

#### Continued from preceding page.

| Deremeter                | Daramatar Cumbal Canditiana |            |             | Ratings |     | Linit |

|--------------------------|-----------------------------|------------|-------------|---------|-----|-------|

| Parameter                | Symbol                      | Conditions | min typ max |         |     | Unit  |

| DMA cycle wait           | <sup>t</sup> CYDM           | RD, DREQ   |             |         | 420 | nS    |

| RD low-level width (DMA) | tWRDM                       | RD         | 300         |         |     | nS    |

Notes: Application designs must take the RDY signal output delay into consideration if the RDY signal is used as the CPU bus wait signal. If the RDY signal is not used, (that is, if no wait states are inserted) the value of the RD low-level width will be 280ns (minimum).

# [LC72711W]

**Electrical Characteristics** at  $V_{DD}$ =+4.5 to +5.5V, within the allowable operating ranges

| Parameter                        | Symbol            | Conditions                                                |                      | Ratings              |      | Unit                                                                                                                |

|----------------------------------|-------------------|-----------------------------------------------------------|----------------------|----------------------|------|---------------------------------------------------------------------------------------------------------------------|

| Falameter                        | Symbol            | Conditions                                                | min                  | typ                  | max  | Offic                                                                                                               |

|                                  | Vout              | IO=2mA, BCK, FCK, BLOCK, FLOCK,                           |                      |                      |      | V                                                                                                                   |

| High-level output voltage        | VOH1              | CRC4, CLK16, DATA                                         | VDD-0.4              |                      |      | V           V           V           V           μA           μA           μA           kΩ           V           kHz |

|                                  | V <sub>OH</sub> 2 | IO=4mA, INT, RDY, DREQ, D0 to D15                         | V <sub>DD</sub> -0.4 |                      |      | V                                                                                                                   |

|                                  | V <sub>OL</sub> 1 | IO=2mA, Pins for which VOH1 applies                       |                      |                      | 0.4  | V                                                                                                                   |

| Low-level output voltage         | VOL2              | IO=4mA, Pins for which VOH2 applies                       |                      |                      | 0.4  | V                                                                                                                   |

|                                  | VOL3              | I <sub>O</sub> =2mA, DO, INT                              |                      |                      | 0.4  | V                                                                                                                   |

| High-level input current         | liH1              | V <sub>IN</sub> =5.5V, A0/CL, A1/CE, A2/DI, RST,<br>STNBY |                      |                      | 1.0  | μΑ                                                                                                                  |

|                                  | I <sub>IH</sub> 2 | VIN=VDDD, All input pins other than IIH1                  |                      |                      | 1.0  | μΑ                                                                                                                  |

| Low-level input current          | ١L                | VIN=VSSD, All input pins                                  |                      |                      | -1.0 | μΑ                                                                                                                  |

| Input resistance                 | RMPX              | MPXIN -Vssa f=100kHz                                      |                      | 50                   |      | kΩ                                                                                                                  |

| Reference supply voltage output  | Vref              | Vref, Vdda=5V                                             |                      | 2.5                  |      | V                                                                                                                   |

| Bandpass filter center frequency | Fc                | FLOUT                                                     |                      | 76.0                 |      | kHz                                                                                                                 |

| -3 dB bandwidth                  | Fbw               | FLOUT                                                     |                      | 19.0                 |      | kHz                                                                                                                 |

| Group delay                      | Dgd               | FLOUT                                                     | -7.5                 |                      | +7.5 | μs                                                                                                                  |

| Gain                             | Gain              | FLOUT-MPXIN, f=76kHz                                      |                      | 20                   |      | dB                                                                                                                  |

|                                  | ATT1              | FLOUT, f=50kHz                                            | 25                   |                      |      | dB                                                                                                                  |

| Oten hand attenuetien            | ATT2              | FLOUT, f=100kHz                                           | 15                   |                      |      | dB                                                                                                                  |

| Stop band attenuation            | ATT3              | FLOUT, f=30kHz                                            | 50                   |                      |      | dB                                                                                                                  |

|                                  | ATT4              | FLOUT, f=150kHz                                           | 50                   |                      |      | dB                                                                                                                  |

| Output off leakage current       | IOFF              | VO=V <sub>DD</sub> D, DO                                  |                      |                      | 5.0  | μΑ                                                                                                                  |

| 11 A 1 B                         |                   | A0/CL, A1/CE, A2/DI, A3, CS, RD, WR,                      |                      | 0.41/ D              |      |                                                                                                                     |

| Hysteresis voltage               | VHYS              | DACK, IOCNT1, IOCNT2, RST, STNBY                          |                      | 0.1V <sub>DD</sub> D |      | V                                                                                                                   |

| Internal feedback resistor       | Rf                | XIN, XOUT                                                 |                      | 1.0                  |      | MΩ                                                                                                                  |

| Current drain                    | IDD               |                                                           |                      | 18                   | 25   | mA                                                                                                                  |

# [LC72711LW]

**Electrical Characteristics** at V<sub>DD</sub>=+2.7 to +3.6V, within the allowable operating ranges

| Parameter                        | Symbol            | Conditions                                                |                      | Ratings |      | Unit |

|----------------------------------|-------------------|-----------------------------------------------------------|----------------------|---------|------|------|

| Falameter                        | Symbol            | Conditions                                                | min                  | typ     | max  | Onit |

| High-level output voltage        | VOH1              | IO=1mA, BCK, FCK, BLOCK, FLOCK,<br>CRC4, CLK16, DATA      | V <sub>DD</sub> -0.4 |         |      | V    |

|                                  | V <sub>OH</sub> 2 | IO=2mA, INT, RDY, DREQ, D0 to D15                         | V <sub>DD</sub> -0.4 |         |      | V    |

|                                  | VOL1              | IO=1mA, Pins for which VOH1 applies                       |                      |         | 0.4  | V    |

| Low-level output voltage         | V <sub>OL</sub> 2 | IO=2mA, Pins for which VOH2 applies                       |                      |         | 0.4  | V    |

|                                  | V <sub>OL</sub> 3 | I <sub>O</sub> =1mA, DO, INT                              |                      |         | 0.4  | V    |

| High-level input current         | liH1              | V <sub>IN</sub> =5.5V, A0/CL, A1/CE, A2/DI, RST,<br>STNBY |                      |         | 1.0  | μΑ   |

|                                  | I <sub>IH</sub> 2 | VIN=VDDD, All input pins other than IIH1                  |                      |         | 1.0  | μΑ   |

| Low-level input current          | IL                | VIN=VSSD, All input pins                                  |                      |         | -1.0 | μΑ   |

| Input resistance                 | RMPX              | MPXIN -Vssa f=100kHz                                      |                      | 50      |      | kΩ   |

| Reference supply voltage output  | Vref              | Vref, Vdda=3V                                             |                      | 1.5     |      | V    |

| Bandpass filter center frequency | Fc                | FLOUT                                                     |                      | 76.0    |      | kHz  |

| -3 dB bandwidth                  | Fbw               | FLOUT                                                     |                      | 19.0    |      | kHz  |

| Group delay                      | Dgd               | FLOUT                                                     | -7.5                 |         | +7.5 | μs   |

| Gain                             | Gain              | FLOUT-MPXIN, f=76kHz                                      |                      | 20      |      | dB   |

|                                  | ATT1              | FLOUT, f=50kHz                                            | 25                   |         |      | dB   |

| Stan band attanuation            | ATT2              | FLOUT, f=100kHz                                           | 15                   |         |      | dB   |

| Stop band attenuation            | ATT3              | FLOUT, f=30kHz                                            | 50                   |         |      | dB   |

|                                  | ATT4              | FLOUT, f=150kHz                                           | 50                   |         |      | dB   |

| Output off leakage current       | IOFF              | VO=V <sub>DD</sub> D, DO                                  |                      |         | 1.0  | μΑ   |

#### Continued from preceding page.

| Parameter                               | Symbol Conditions |                                      |             | Ratings              |    |    |  |

|-----------------------------------------|-------------------|--------------------------------------|-------------|----------------------|----|----|--|

| i aldifieter                            | Gymbol            | Conditions                           | min typ max |                      |    |    |  |

| Hysteresis voltage                      | VHYS              | A0/CL, A1/CE, A2/DI, A3, CS, RD, WR, |             | 0.1V <sub>DD</sub> D |    | V  |  |

| , , , , , , , , , , , , , , , , , , , , |                   | DACK, IOCNT1, IOCNT2, RST, STNBY     |             |                      |    |    |  |

| Internal feedback resistor              | Rf                | XIN, XOUT                            |             | 1.0                  |    | MΩ |  |

| Current drain                           | IDD               |                                      |             | 12                   | 20 | mA |  |

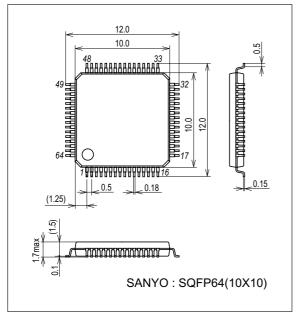

# **Package Dimensions**

unit : mm (typ) 3190A

# **Pin Assignment**

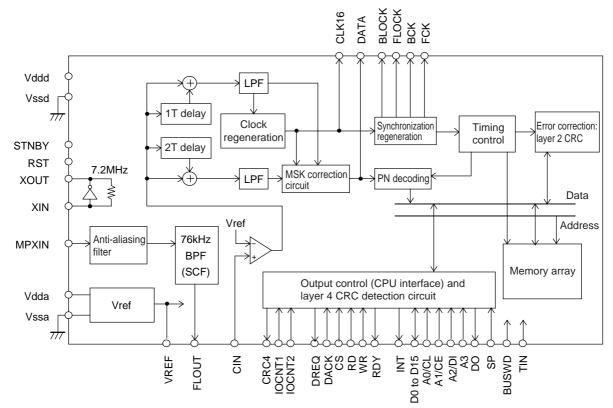

# **Block Diagram**

# **Pin Functions**

| Pin No. | Pin    | Function                                                                                        | I/O     | Pin circuit |

|---------|--------|-------------------------------------------------------------------------------------------------|---------|-------------|

| 3       | IOCNT1 | Data bus I/O control 1 (SP=low)*1                                                               |         |             |

| 4       | IOCNT2 | Data bus I/O control 2 (SP=low)*1                                                               |         |             |

| 13      | DACK   | DMA acknowledge (SP=low)*1                                                                      |         |             |

| 38      | WR     | Write control signal (SP=low)*1                                                                 |         |             |

| 39      | RD     | Read control signal (SP=low)*1                                                                  |         |             |

| 40      | A0/CL  | Address input 0 (SP=low) CCB CL input (SP=High)                                                 | Input   |             |

| 41      | A1/CE  | 1 (SP=low) CCB CE input (SP=High)                                                               |         |             |

| 42      | A2/DI  | 2 (SP=low) CCB DI input (SP=High)                                                               |         |             |

| 43      | A3     | 3 (SP=low)*1                                                                                    |         |             |

| 44      | CS     | Chip select input (SP=L)*1                                                                      |         |             |

| 46      | RST    | System reset input (negative logic)                                                             |         |             |

| 45      | STNBY  | Standby mode (positive logic)                                                                   |         |             |

| 47      | SP     | SP=low: parallel, SP=high: serial                                                               |         |             |

| 48      | BUSWD  | BUSWD=low: 8 bits, BUSWD=high: 16bits                                                           |         |             |

| 60      | TEST   | The test pin must be connected to the digital system ground (VSS).                              |         |             |

| 58      | TPC1   | Must be connected to the digital system power supply (VDD) or ground (VSS) in normal operation. | Input   |             |

| 59      | TPC2   | As above                                                                                        |         | -           |

| 61      | TOSEL1 | As above                                                                                        |         |             |

| 62      | TOSEL2 | As above                                                                                        |         |             |

| 49      | TIN    | As above                                                                                        |         |             |

| 5       | CLK16  | Clock regeneration monitor                                                                      |         |             |

| 6       | DATA   | Demodulated data monitor                                                                        |         |             |

| 9       | FCK    | Frame start signal output                                                                       |         |             |

| 10      | BCK    | Block start signal output                                                                       |         |             |

| 7       | FLOCK  | Outputs a high level during frame synchronization                                               | Outrast |             |

| 8       | BLOCK  | Outputs a high level during block synchronization                                               | Output  |             |

| 11      | CRC4   | Level 4 CRC detection result output                                                             |         |             |

| 33      | INT    | External CPU interrupt request output                                                           | 1       |             |

| 12      | DREQ   | DMA request signal                                                                              |         |             |

| 16      | RDY    | Read ready signal                                                                               |         |             |

#### Continued from preceding page.

| Pin No.                             | Pin                                                    | Function                                                                                                                                                        | I/O    | Pin circuit  |

|-------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------|

| 17 to 24                            | D0 to D7                                               | Data bus<br>The bus width can be set to be either 8 bits or 16bits by the BUSWD<br>pin (pin 48).<br>For data input, only the lower 8 bits (D0 to D7) are valid. | I/O    |              |

| 25 to 32                            | D8 to D15                                              | Data bus (in 16-bit mode)<br>These pins are held in the output off state when BUSWD is low.                                                                     | Output |              |

| 64<br>1                             | XIN<br>XOUT                                            | Connections for the system clock crystal oscillator circuit.<br>The XIN pin can also be used as an external clock signal input.                                 | I/O    |              |

| 53                                  | MPXIN                                                  | Baseband (multiplex) signal input                                                                                                                               | Input  |              |

| 55                                  | FLOUT                                                  | Subcarrier output (76kHz bandpass filter output)                                                                                                                | Output |              |

| 56                                  | CIN                                                    | Subcarrier input (comparator input)                                                                                                                             | Input  | Vref         |

| 52                                  | VREF                                                   | Reference voltage output (Vdda/2)                                                                                                                               | Output | Vdda<br>Vssa |

| 36                                  | DO                                                     | CCB serial interface data output                                                                                                                                | Output |              |

| 37<br>50<br>57                      | NC                                                     | This pin must be left open                                                                                                                                      |        |              |

| 54<br>51<br>2, 15, 34<br>14, 35, 63 | V <sub>DD</sub> A<br>VSSA<br>V <sub>DD</sub> D<br>VSSD | Analog system power supply<br>Analog system ground<br>Digital system power supply (+2.7V to +5.5V)<br>Digital system ground                                     | -      |              |

Notes: 1. This pin must be connected to VDDD or VSSD if the IC is used in serial interface mode (when SP is high).

2. A capacitor of at least 2000pF must be inserted between VDDD and VSSD.

# **Control Registers**

This IC includes both registers that can be read and registers that can be written. These registers can be accessed using either the serial interface (CCB) or the parallel interface. The SP pin switches between these interfaces.

The initial values of the write registers are the data loaded into internal registers when a reset signal (RST) is received. These values are recommended values that do not need to be changed during normal operation.

If the parallel interface is used, applications must hold the address fixed at 00H when reading out data to which error correction has been applied. If the CCB interface is used, the application needs only to specify the CCB address (#FB). The address 00H is an invalid address for writing.

The addresses other than those specified below are control addresses particular to the IC. Applications must not specify those addresses.

#### Continued from preceding page.

| Address | Register | Function                                      | R/W | Address | Register | Function              | R/W |

|---------|----------|-----------------------------------------------|-----|---------|----------|-----------------------|-----|

| 1       | BIC      | Number of allowable BIC errors                | W   | 1       | STAT     | Status register       | R   |

| 2       | SYNCB    | Block synchronization: error protection count | W   | 2       | BLNO     | Block number register | R   |

| 3       | SYNCF    | Frame synchronization: error protection count | W   |         |          |                       |     |

| 4       | CTL1     | Control register 1                            | W   |         |          |                       |     |

| 5       | CTL2     | Control register 2                            | W   |         |          |                       |     |

| 6       | CRC4     | Layer 4 CRC register                          | W   |         |          |                       |     |

#### Number of Allowable BIC Errors

| Address | Register | R/W | Initial value | BIT7            | BIT6 | BIT5 | BIT4  | BIT3 | BIT2      | BIT1       | BIT0  |

|---------|----------|-----|---------------|-----------------|------|------|-------|------|-----------|------------|-------|

| 01H     | BIC      | W   | 22H           | Back protection |      |      | (LSB) |      | Forward p | protection | (LSB) |

The synchronization circuit in this IC operates by recognizing a 16-bit BIC code. The number of allowable errors is the number of incorrect bits allowed in those 16 bits. This data sets up separate values for forward protection mode (when synchronized) and for back protection mode (when not synchronized).

The default value is to allow 2 incorrect bits in both forward and back modes. If the block synchronization discrimination output (BLOCK) is used for discriminating whether or not FM multiplex data is present, we recommend setting the back protection mode BIC allowable error count to 1 or 0.

#### **Block Synchronization: Error Protection Count**

|         | -        |     |               |      |                 |      |      |      |           |            |       |

|---------|----------|-----|---------------|------|-----------------|------|------|------|-----------|------------|-------|

| Address | Register | R/W | Initial value | BIT7 | BIT6            | BIT5 | BIT4 | BIT3 | BIT2      | BIT1       | BIT0  |

| 02H     | SYNCB    | W   | 17H           |      | Back protection |      |      |      | Forward p | protection | (LSB) |

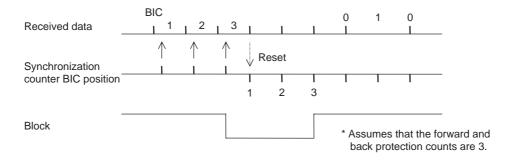

The synchronization protection count can be set separately for both forward and back protection. The count conditions for the protection counts are as follows.

• Back protection mode (not synchronized: BLOCK=low)

If the timing of the IC internal synchronization free-running counter matches the timing of the received BIC, the protection count is incremented by 1. Contrarily, if the timings of the IC internal counter and the received BIC do not match, the protection counter is cleared to 0. The timing of the count is the timing of the IC internal counter. • Forward protection mode (synchronized: BLOCK=high)

In reverse to the back protection mode, if the timing of the IC internal free-running counter does not match the detection timing of the received BIC, the protection counter is incremented, and if the timings match, the protection counter is cleared to 0.

Figure 1 shows the states of the protection counter for the cases where the forward and back protection counts are both 3. This IC defines the value of the protection counter to be 1 at the point that a match or a discrepancy occures between the IC internal timing and the timing of the received BIC occurs. For example, when the value of the back protection count is 2, the IC internal timing and the timing of the received BIC will have matched two times consecutively. If the protection data is set to new values, for example if the protection counts are set to 3 as assumed in figure 1, applications must send values which are 1 less than the intended value; in this case 22H. Similarly, if the value is set to 00H, the protection counts will, by definition, be set to 1 for both the forward and back directions. However, note that the resulting operation will be equivalent to there being no protection circuit. The default values are 8 for the forward protection count and 2 for the back protection count.

If the block synchronization output (BLOCK) is used for discriminating whether or not FM multiplex data is present, we recommend setting the block synchronization back protection count to a value that is more strict than the default value. (That is, we recommend replacing the default value of 2 with a value of 3 or higher.)

Figure 1 Block Synchronization Protection Operation (Forward  $\rightarrow$  Back  $\rightarrow$  Forward)

# Frame Synchronization: Error Protection Count

| i i anno |          |     |               |                 |      |      |       |      |           |            |       |

|----------|----------|-----|---------------|-----------------|------|------|-------|------|-----------|------------|-------|

| Address  | Register | R/W | Initial value | BIT7            | BIT6 | BIT5 | BIT4  | BIT3 | BIT2      | BIT1       | BIT0  |

| 03H      | SYNCF    | W   | 17H           | Back protection |      |      | (LSB) |      | Forward p | protection | (LSB) |

This IC detects the BIC characteristic inflection points which occur at four places in a single frame, and increments or decrements a protection counter depending on whether or not they match the IC internal frame synchronization timing counter.

As is the case with the block synchronization error protection value, applications must set these to values one less than the desired protection count. The default values are 8 for the frame synchronization forward protection count and 2 for the back protection count.

## **Control Register 1**

|         | -        |     |               |          |         |          |          |         |          |      |       |

|---------|----------|-----|---------------|----------|---------|----------|----------|---------|----------|------|-------|

| Address | Register | R/W | Initial value | BIT7     | BIT6    | BIT5     | BIT4     | BIT3    | BIT2     | BIT1 | BIT0  |

| 04H     | CTL1     | W   | 00H           | CRC4_RST | DO_MOVE | INT_MOVE | SYNC_RST | EC_STOP | VEC_HALT | RTIB | FRAME |

#### •FRAME

- 0: Specifies method B. (default)

- 1: Specifies method A.

• RTIB

- 0: Real-time information blocks present. (default)

- 1: No real-time information blocks.

In the ITU-R recommended frame structure method A, a total of 12 data blocks can be inserted in the parity data area (the area that consists of 82 consecutive blocks of parity packets). If this IC is used in a system that has no real-time information blocks (RTIB), this flag must be set.

Note that if this flag is changed, frame synchronization is retained in the synchronized state for the time corresponding to the forward protection count, and then switches to the unsynchronized state. To quickly reestablish frame synchronization, applications must reset the synchronization circuit using the SYNC\_RST flag.

## ·VEC\_HALT

- 0: Vertical correction and the second horizontal correction processing are performed. (default)

- 1: Vertical correction and the second horizontal correction processing are not performed.

All IC operations related to vertical correction and the second horizontal correction are stopped by setting this flag. Note that in data output, only data to which the first horizontal correction has been applied will be output.

• EC\_STOP

- 0: All functions operate. (default)

- 1: Only the MSK detection circuit and the synchronization regeneration circuit operate.

This flag stops all operations relating to error correction (including RAM access), data output, and other operations. While all IC operations are stopped in standby mode, MSK demodulation, the synchronization circuit, the serial data input circuit, and the layer 4 CRC circuit continue to operate in this mode.

## •SYNC\_RST

#### 0: (default)

1: Resets just the synchronization regeneration circuit.

Clears the synchronization status and the synchronization protection status in the synchronization circuit block, and sets the circuit to the unsynchronized state. This allows the circuit to quickly pull in to frame synchronization when the frame synchronization is incorrect for the new reception data following tuning, when the radio has been tuned to a new station. While this flag is used for synchronization related sections of the system, it does not initialize the registers that set the number of allowable BIC errors, the block synchronization forward and back protection counts, and the frame synchronization forward and back protection counts. Also note that during a synchronization block reset, the INT signal is not output and the DO pin outputs a high level (high-impedance).

This flag is not automatically reset to 0. Applications must send a 0 value after setting this flag.

#### ·INT\_MOVE

- 0: Data is only output when error correction has completed, layer 2 CRC has completed, and the data was received with the circuit synchronized. (default)

- 1: All data is output. (Operation is identical to that of the LC72700E.)

In the default state, this IC only outputs data that has been fully error corrected and that was received in both block and frame synchronization. (This also includes the layer 2 CRC check.)

To acquire all data as provided by the LC72700, applications must set both this flag and the VEC\_OUT (BIT2) flag in control register 2 as described below.

•DO\_MOVE (Valid only when SP is high.)

- 0: The high state (high impedance) is held at all times other than when data is being output. (default)

- 1: Operate identically to the LC72700 when changes are linked to the INT signal, i.e. when both INT\_MOVE and VEC\_OUT are set to 1.

- ·CRC4\_RST

- 0: (default)

- 1: Reset the layer 4 CRC detection circuit.

This flag is not automatically reset to 0. Applications must send a 0 value after setting this flag.

| Address | Register | R/W | Initial value | BIT7   | BIT6    | BIT5 | BIT4 | BIT3 | BIT2    | BIT1   | BIT0 |

|---------|----------|-----|---------------|--------|---------|------|------|------|---------|--------|------|

| 05H     | CTL2     | W   | 00H           | SUBBLK | BLK_RST | DACK | DREQ | RDY  | VEC_OUT | DMA_RD | DMA  |

- DMA (Valid only when SP is low.)

- 0: Do not use DMA transfer for readout of post-error correction data. (default)

1: Use DMA transfer for readout of post-error correction data.

- •DMA\_RD (Valid only when SP is low.)

- 0: Use the RD signal as the DMA transfer read control signal. (default)

1: Use the DACK signal as the DMA transfer read control signal.

• VEC\_OUT

- 0: Do not perform post-horizontal correction output when vertical correction processing is not performed. (default)

- 1: Output all data, even when vertical correction processing is not performed. (Operation identical to that of the LC72700E)

When this flag is set and a frame of data with absolutely no errors is received, data that is completely identical to the corresponding post-horizontal correction data is output with the timing of the output of post-vertical correction data, even if vertical correction is not performed.

- This flag must be set to create interface specifications identical to those of the LC72700.

- RDY (Valid only when SP is low.)

- 0: The RDY output is issued with timing 1. (default)

- 1: The RDY output is issued with timing 2.

- •DREQ (Valid only when SP is low.)

- 0: Negative logic is used for the polarity of the DREQ signal. (default)

- 1: Positive logic is used for the polarity of the DREQ signal.

- ·DACK (Valid only when SP is low.)

- 0: Negative logic is used for the polarity of the DACK signal. (default)

- 1: Positive logic is used for the polarity of the DACK signal.

- $\cdot$ BLK\_RST

- 0: (default)

- 1: Resets the block synchronization circuit only.

Sets the block synchronization status to unsynchronized and clears the block synchronization protection counter. However, note that this has no effect on the frame synchronization functions. Also note that during a synchronization block reset, the INT signal is not output and the DO pin outputs a high level (high-impedance). This flag is not automatically reset to 0. Applications must send a 0 value after setting this flag.

- SUBBLK

- 0: Normal status. (default)

- 1: Set to 1 when a substation is temporarily received.

## Layer 4 CRC Register

| Address | Register | R/W | Initial value | BIT7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | BIT0  |

|---------|----------|-----|---------------|------|------|------|------|------|------|------|-------|

| 06H     | CRC4     | W   | 00H           |      |      |      |      |      |      |      | (LSB) |

This is the data group write register used for the layer 4 CRC check. It is used only when the parallel interface is used. Applications should specify the dedicated CCB address when using the serial interface.

#### **Status Register**

| Address Register R/W Initial value BIT7 E | BIT6 BIT5 | BIT4 E | BIT3 BIT2 | BIT1 | BIT0 |

|-------------------------------------------|-----------|--------|-----------|------|------|

|                                           | BLK FRM   | ERR I  | PRI HEAD  | CRC4 | RTIB |

٠VH

0: Indicates data for which only horizontal correction was performed.

1: Indicates data for which after horizontal correction, vertical and then second horizontal correction were performed as well.

Packet data with an RTIB flag is output with VH set to 0.

•BLK

- 0: Indicates data that was received with block synchronization unsynchronized.

- 1: Indicates data that was received with block synchronization synchronized.

•FRM

- 0: Indicates data that was received with frame synchronization unsynchronized.

- 1: Indicates data that was received with frame synchronization synchronized.

•ERR

- 0: Indicates data for which error correction completed and no errors were detected in the level 2 CRC check.

- 1: Indicates data for which error correction was not possible or for which errors were detected in the level 2 CRC check.

#### • PRI

- 0: Indicates data that was inferred to be data block data by the frame synchronization circuit.

- 1: Indicates data that was inferred to be parity block data by the frame synchronization circuit.

Packet data with an RTIB flag is output with PRI set to 0.

• HEAD

0:

- 1: Indicates data that was inferred to be in the frame head block by the frame synchronization circuit.

- This flag is valid only when VH is 0.

#### •CRC4

- 0: Indicates that the layer 4 CRC detection circuit division registers were not all zeros.

- 1: Indicates that the layer 4 CRC detection circuit division registers were all zeros, i.e. that there were no errors.

- The result at the point immediately prior to register readout is loaded into this flag.

• RTIB

0:

- 1: Indicates the data is a real-time information block. (This bit is valid only in method A'.)

- This bit is fixed at 0 during method A and method B reception.

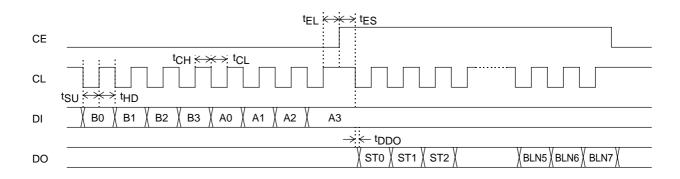

#### **Block Number Register**

| Address | Register | R/W | Initial value | BIT7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | BIT0 |

|---------|----------|-----|---------------|------|------|------|------|------|------|------|------|

| 02H     | BLNO     | R   | -             | BLN7 | BLN6 | BLN5 | BLN4 | BLN3 | BLN2 | BLN1 | BLN0 |

Indicates the block number or the parity block number of the output data.

A single frame consists of data blocks numbered 0 to 189 and parity blocks numbered 0 to 81. Output following vertical correction does not include parity block data.

The value of the block number register is undefined if VEC\_HALT (bit 2 in control register 1) is set to 1.

# Data Update Timing for Read Registers

The data in the two read registers (the status register at address 01H and the block number register at address 02H) is updated in the 1 ms interval between 1 ms prior to the output of the interrupt control signal (INT) and a point immediately before the INT output.

In normal processing, when an interrupt occurs, the application will first determine the nature of the data packet that will be output by the current interrupt signal by reading out the status register, and determine if it is necessary to read out that data. For example, if error correction failed and the erroneous data is not required, the application should simply wait for the next interrupt.

If the CCB interface is used, the application reads out the data from CCB address #FB, and determines the status from the additional 16 bits of data. It then either reads out the following data or sets the CE signal low to cancel the readout. Applications can also read out data asynchronously with respect to the interrupt signal. In this case, the application checks the current reception status by reading out the status register and checking bit 6 (data received in the block synchronized state) and bit 5 (data received in the frame synchronized state). In this case, using data for which bit 7 (VH) is 0 provides superior real time characteristics.

# CPU Interface Timing <Parallel Mode>

Register Read Timing

\* tHARD stipulates the earliest timing for A0 to A3 and CS.

•Register Write Timing

Post-Correction Data Read Timing

• Post-Correction Data Read Timing (DMA)

\*: A0 to A3: When post-correction data is read, A0 to A3 will be held fixed at 0.

\*: DREQ and DACK: The polarity of these signals can be set.

\*: Applications can select whether the DR or DACK signal is used for readout.

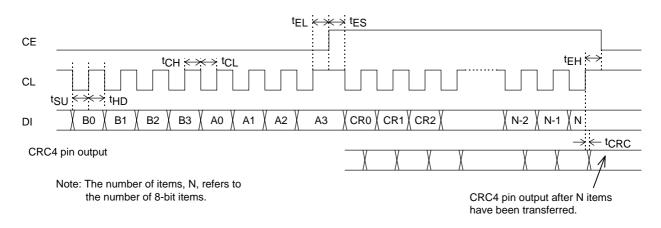

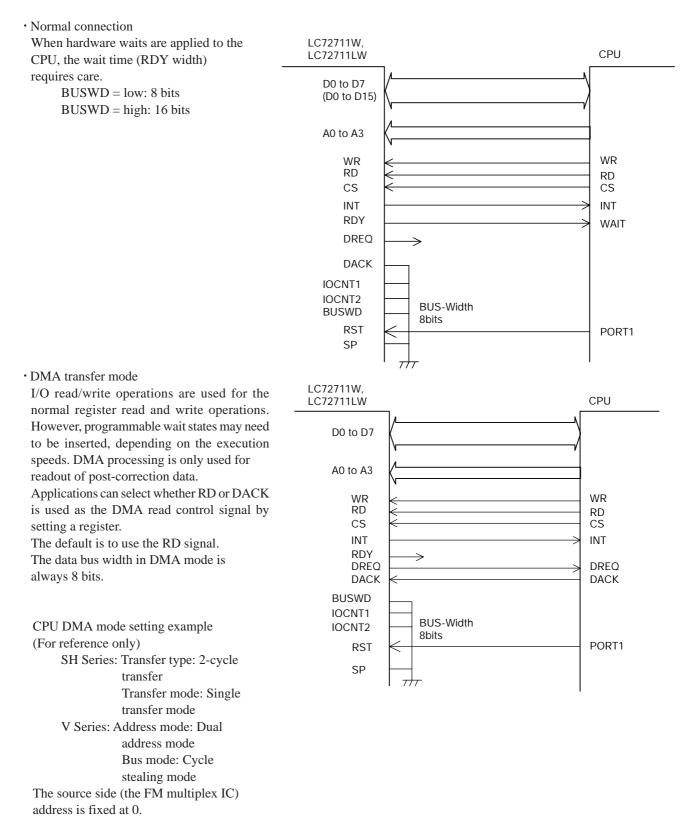

#### Layer 4 CRC Detection Circuit <Parallel Interface>

This function provides data group error detection, i.e. layer 4 CRC. When the stipulated number of bytes of data group data and the CRC detection word (16 bits) are written to the layer 4 CRC register (address 6), if either the CRC4 pin outputs a high level or the CRC4 flag (bit 1 in the status register at address 1) is set to 1 then there were no errors in the data. The CRC4 pin or CRC4 flag in the status register outputs a high level if the IC internal CRC detection register bits are all in the logic 0 state.

When this function is used to perform a layer 4 CRC check, applications must initialize the IC internal CRC detection register before transferring the data for a single data group. This initialization is performed by sending data for bit 7 (CRC4\_RST) in control register 1. Note that since this initialization flag is not automatically reset to 0, after the application sets this flag it must then send another data item that resets it to 0 before sending the layer 4 CRC check data.

If there were no errors in all the received data groups, the CRC register will, necessarily, be all zeros after the CRC check for a given data group. Therefore, as long as there are no errors detected in the layer 4 CRC check, the application does not need to initialize the CRC detection register again using the control register as described above. There is no upper limit on the total data length of data groups that can be transferred. Also, when the serial interface issued, the CCB transfers can be divided into multiple transfer operations. The generating polynomial G(x) for the CRC code is as follows.  $G(x) = X^{16} + X^{12} + X^5 + 1$

#### Structure of the Post-Correction Output Data <Parallel Interface>

The total length of the prepared output data is always 176 bits, i.e. 22 bytes. The layer 2 CRC data (14 bits) and the parity data (82 bits) are not output. The data in each packet in the post-correction data is output in order starting at the beginning in 8- or 16-bit units. BIC codes are not output.

When the CPU reads out the data, it can easily select the data by checking the status register first. The CPU can then simply ignore data determined to be unnecessary without having to read it out by simply waiting until the next interrupt arrives.

| Data block (176bits) Post-error correction data | Layer 2 CRC (14bits) | Parity (82bits)             |

|-------------------------------------------------|----------------------|-----------------------------|

|                                                 |                      | *: This data is not output. |

Structure of a Single Data Packet (Total length: 272bits. BIC is not included.)

# CPU Interface <CCB Mode>

# **CCB** Format

Data is input and output using the CCB (Computer Control Bus) format, which is Sanyo's audio IC serial bus format. This IC uses an 8-bit address CCB with the address shown below. The CCB address is sent while CE is low, and the CCB I/O mode is determined when CE is set high.

| I/O mode |    |    |    | CCB a | ddress |    |    |    | Item                                                                |

|----------|----|----|----|-------|--------|----|----|----|---------------------------------------------------------------------|

| i/O mode | B0 | B1 | B2 | B3    | A0     | A1 | A2 | A3 | liem                                                                |

| Input    | 0  | 1  | 0  | 1     | 1      | 1  | 1  | 1  | 16-bit control data input                                           |

| Output   | 1  | 1  | 0  | 1     | 1      | 1  | 1  | 1  | Data corresponding to the number of clock (CL) cycles is output     |

| Input    | 0  | 0  | 1  | 1     | 1      | 1  | 1  | 1  | Data input mode for the layer 4 CRC detection circuit (8-bit units) |

| Output   | 1  | 0  | 1  | 1     | 1      | 1  | 1  | 1  | Register output only                                                |

# Data input (Register write)

Data is stored in an IC internal register. The CCB address #FA and 16 bits of data (DI0 to DI15) are input to the DI pin. The bits are assigned as follows. Although DI12 to DI15 are unused data, arbitrary values must be provided to complete a full 16 bits of data.

See the "Control Register" section earlier in this document for details on the register contents and addresses. Details on writing to the layer 4 CRC check register are described later in this document. (The CCB address #FC is used for this function.)

| DI0   | DI1                       | DI2  | DI3  | DI4  | DI5  | DI6   | DI7              | DI8  | DI9  | DI10 | DI11        | DI12 to DI15 |  |

|-------|---------------------------|------|------|------|------|-------|------------------|------|------|------|-------------|--------------|--|

| BIT0  | BIT1                      | BIT2 | BIT3 | BIT4 | BIT5 | BIT6  | BIT7             | BIT0 | BIT1 | BIT2 | BIT3        | Unused data  |  |

| (LSB) | (LSB) Input data (8 bits) |      |      |      |      | (MSB) | Register address |      |      |      | Unused data |              |  |

# Data Output (Post-correction data output)

The IC outputs packet data to which error correction processing has be applied. The application inputs the CCB address #FB to DI.

\*: The DO pin is normally left open.

Since the DO pin is an n-channel open-drain output, the data change time from a low-level output to a high-level output differs due to the pull-up resistor.

# Structure of the Post-Correction Output Data <CCB Interface>

Post-error correction data can be output by using CCB address #FB. Although there are up to 288 bits of valid data that can be output, it is possible to stop clock input (CL input) and set CE to the low level, and output the remaining data on the next interrupt with no harmful effects whatsoever.

- The maximum amount of data that can be output is 288 bits (36 bytes), and the contents of the status register (STAT) and the block number register (BLNO) are added as the first two bytes.

- The contents of the STAT and BLNO registers are output LSB first.

- The post-correction data is output in order starting with the first bit in each single block of data.

- $\boldsymbol{\cdot}$  The BIC code is not output.

- The values of the output data are not guaranteed if multiple data read operations are performed for a single interrupt signal (INT).

| STAT (8 bits) | BLNO (8 bits) | Data section (176 bits) Post-error correction data | Layer 2 CRC (14 bits) | Parity (82 bits) |

|---------------|---------------|----------------------------------------------------|-----------------------|------------------|

| DO0 to DO7    | DO8 to DO15   | DO16 to DO191                                      | DO192 to DO205        | DO206 to DO287   |

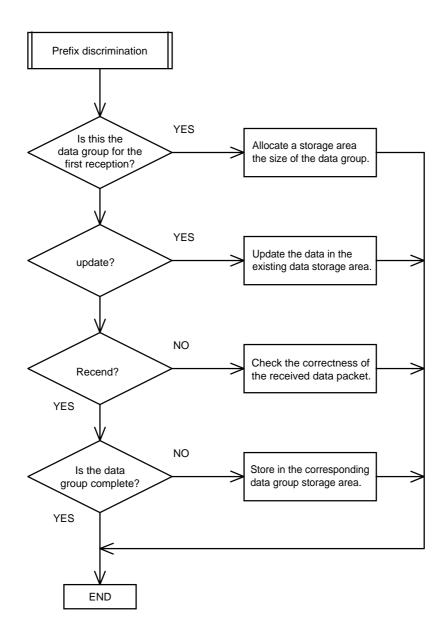

# Layer 4 CRC Check Circuit <CCB Interface>

The basic outline of this operation is the same as that described in the Layer 4 CRC Detection Circuit <Parallel Interface> section earlier in this document. The data group data used for this error detection operation is sent to the IC using the CCB interface. The value #FC is used as the CCB address.

The data group data is transferred in 8-bit units. There is no upper limit on the amount of data that can be transferred (the value N in the figure below), and the data transfer may be divided into multiple operations.

# **Register Output**

The IC internal status and block number registers are special-purpose registers that can be read out by applications. (See the discussion of the read register data update timing on page 12.)

The application inputs the CCB address #FD to DI. The status register data is output first followed by the block number register data.

# Notes on Operation during Resets and in Standby Mode

#### **Reset Signal**

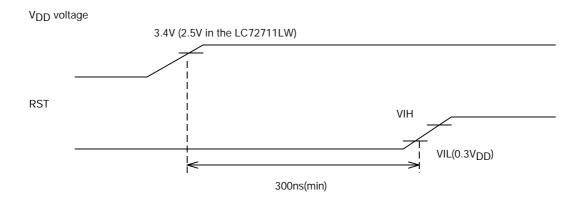

The reset operation is executed when the supply voltage (VDD) rises above 3.4V (2.5V in the LC72711LW) and the RST pin input level is held at or below  $V_{IL}$  for 300ns or longer. (See the figure below.)

When power is first applied, or when power is removed and applied again, always apply a reset before using this IC.

## Pin States during Reset

```

Low level:CLK16 (5), DATA (6), FLOCK (7), BLOCK (8), FCK (9), BCK (10)

High level: INT (33), RDY (16), CRC4 (11), DREQ (12)

Open: D0 (17) to D15 (32), DO (36)

```

## **Reset Operating Range**

The states of the output pins as the result of a reset signal are stipulated in the "Pin States during Reset" item above. The IC internal flip-flops are all reset. While the shift registers used for delay are also reset, the memory array is not influenced by this operation. However, since memory is not refreshed, data cannot be retained. The crystal oscillator circuit is not stopped.

# **Post-Reset Data Input**

After a reset operation has completed, if at least one clock cycle (about 278ns when the IC's main clock is 3.6MHz) elapses, the register write circuit will be functional. (That is, the IC can accept data.)

# Notes on Standby Mode

The IC is set to standby mode by applying a high level to the STNBY pin. Since all IC operations are stopped in this mode, the state is essentially equivalent to removing power from the IC. (Note that after clearing standby mode, applications must wait the oscillator stabilization time before using the IC.)

The pin output states during standby mode are the same as those states during a reset as described above.

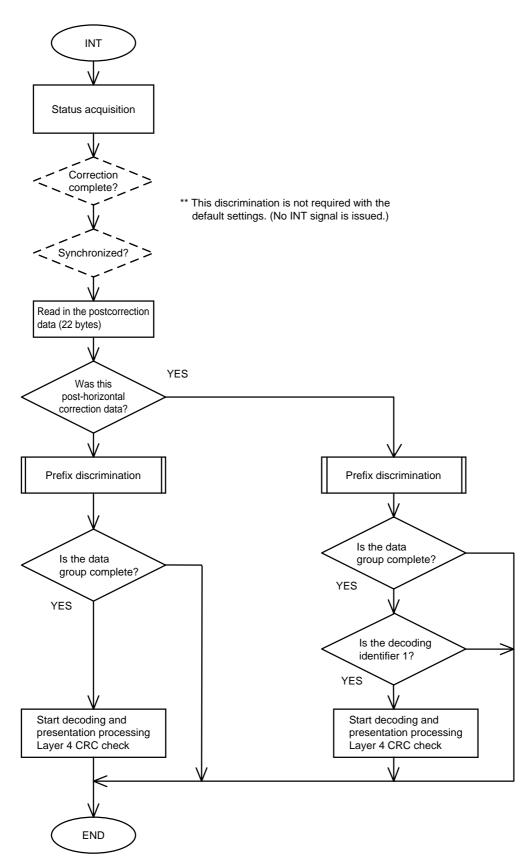

Output Conditions for Post-Error Correction Output (Default Mode)

- (1) For each block (272 bits) of received data, the IC applies (272, 190) code error correction and a layer 2 CRC error check. After the error correction has completed, the IC prepares to transfer the data to the CPU and outputs an interrupt signal from the INT pin. This is referred to as horizontal correction output.

- (2) Note that under the default operating conditions, this interrupt signal is not output unless the corresponding output data meets the following three conditions.

- Error correction completed correctly and no errors were discovered in the layer 2 CRC check.

- The data was received in both block and frame synchronization.

- The data is packet data.

- (3) If the data could not be corrected in horizontal correction, product code correction is performed in frame units and a second horizontal correction operation is performed for this data that could not be corrected by the first horizontal correction. This sequence of operations is called vertical correction.

The output conditions for data that can be acquired after vertical correction are as follows.

- The data that could not be corrected by horizontal correction only, but that was corrected by vertical correction.

- The data is packet data.

Continued from preceding page.

This means that data that was fully corrected by horizontal correction is not output. Also, packet data that could not be corrected by either horizontal correction or vertical correction is not output. Furthermore, post-vertical correction parity packet data is also not output.

- (4) Applications can clear the INT signal selection conditions described in (2) and (3) above by setting bit 5 (INT\_MOVE) in the control register.

- (5) Vertical correction is performed when all of the packet data in a frame is received in frame synchronization and furthermore when it was not possible to correct all of the packet (block) data with horizontal correction. Vertical correction is not performed if one frame of data with no errors was received or the receiver was not in frame synchronization during reception.

To prevent incorrect correction, error correction using vertical correction is not performed for packets error correction using horizontal correction fully completed and for packets that had no errors.

(6) Under the default settings, if vertical correction is not performed, the corresponding post-vertical correction output is not output.

Applications can specify the post-vertical correction data to be output regardless of whether or not vertical correction is performed by setting bit 2 (VEC\_OUT) in control register 2.

- Note 1. In this case, if data with absolutely no errors is received, completely identical data will be output twice, once as horizontal correction output, and once as vertical correction output. This status is identical to the output status of the LC72700E.

- Note 2. Immediately after power is applied, undefined data that is, in principle, not required by applications, will be output as post-vertical correction data.

## **CPU Interface Basic Limitations**

To save internal memory, this IC limits its output data buffer to the smallest size possible. Since the data received by the IC is written to memory continuously without interruption, the post-correction data in the output data buffer that should be read out may be overwritten by the following data if readout of the data is delayed.

The output timing for post-correction data, both horizontal and vertical, is stipulated as follows for this IC.

- (1) When the IC completes preparation of the output data, it drops the INT pin to the low level as a transfer request.

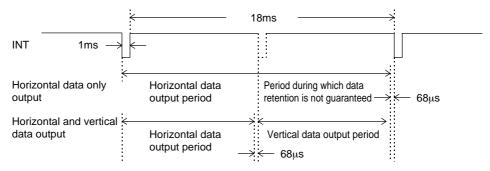

- (2) During data output, there are periods when only horizontal data can be read out, and there are other periods when both horizontal data and vertical data can be read out in a time-division multiplexed manner.

- (3) Applications must complete the data transfer operation within 9ms after the INT pin goes low. If only post-horizontal correction data is output, the data transfer may be performed within an 18ms period. After the stipulated period, the next data will be written to the output buffer replacing the previous data, even if the CPU is reading out the data.

- (4) The amount of data that can be read for a single transfer request (INT) for each of the horizontal and vertical data is one block only. The post-vertical correction data is output in order starting with block number 1 after vertical correction processing completes. The parity block data is not output.

Figure 2 External Interface - Basic Timing

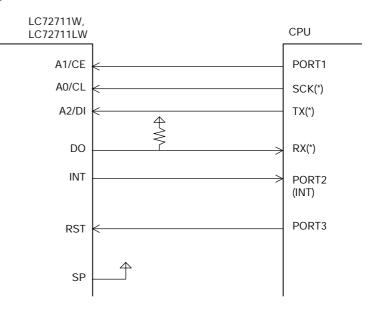

# Notes on Data Output Timing (Relationship with the received data)

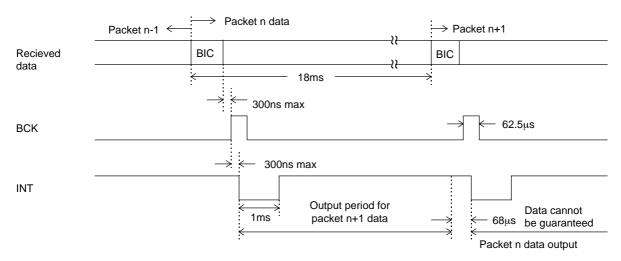

Figure 3 shows the timing relationship between the received data and the interrupt control signal (INT). However, the delay from the actual received signal due to demodulation operations in MSK demodulation blocks is ignored. Block synchronization is established by discriminating the BIC code. As shown in figure 3, the data for the nth packet can be output during reception of the following packet (number n+1).

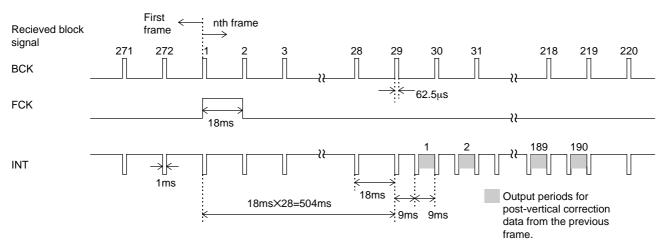

Figure 4 shows the output timing for post-vertical correction data. In vertical correction, the data for a single frame is stored in memory and the correction operation is performed if frame synchronization was established and it was not possible to correct all the packet data in horizontal correction. The timing with which vertical correction is started is the start of the frame. Horizontal correction is performed for each packet while packets 1 through 28 in the nth frame are being received, and this data is passed to the CPU interface. Vertical correction is performed for the data from the previous frame (frame n-1) in the unused time periods during that processing.

The vertical correction data consists of 190 blocks that are output, and this data is output at the rate of one block for every block received, in order starting at the time the 29th packet (block) is received. Only data from the data blocks in the FM multiplex broadcast frame structure is output, and the last block (block 190) is output during reception of the 218th block.

As indicated previously (page 17) packet data that was, for example, corrected completely by horizontal correction, is not output in the vertical correction output data. (The INT signal is not issued.) However, the order in which the horizontal output is produced is not speeded up by the amount of the packet data that is not output. For example, if data packets 1 to 100 were corrected by horizontal correction, output of the post-vertical correction packet data for packet 101 will not occur at the reception position of block number 29 in figure 4, but at the reception position for packet data number 129.

Figure 3 Received Data, Block Synchronization, and Data Output Timing

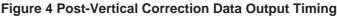

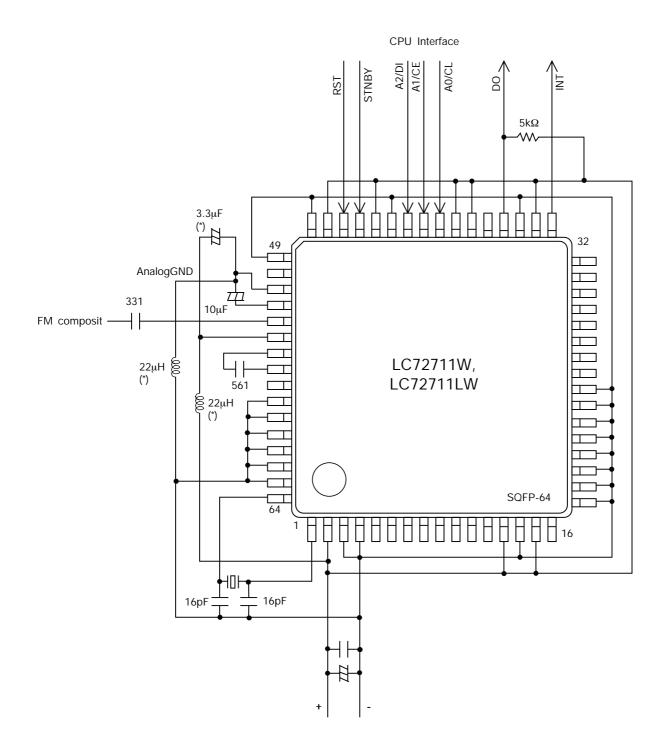

# CPU Connection Example <Parallel Interface>

This section presents examples of the connection of this IC to a CPU.

Note that care is required with respect to read timing, since the time required to read a register, and the time required to read a post-correction data packet (22 bytes) are different.

• Data bus I/O control block

The data bus (D0 to D15) can be controlled with two control signals: IOCNT1 and IOCNT2. These pins must be held low if unused.

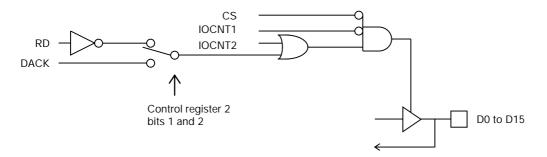

CPU Connection example <CCB Interface>

\* SCK, TX, and RX are the CPU serial interface channel. Normally, I/O port pins may be used for these lines. \* The resistance of the DO pin pull-up resistor must be selected according to the transfer clock speed.

# **Control Program Compatibility**

This IC allows the majority of the control software used to be compatible with Sanyo's other FM multiplex ICs, in particular, the LC72700E, LC72705E, LC72706E, LC72708E, and LC72709E(W). However, the following aspects of the control software require modification.

• Values of the register addresses

The addresses of the allowable BIC error count, synchronization error protection count, control registers, the layer 4 CRC register, and other registers have been modified.

The CCB address for serial I/O over a CCB bus has not been changed.

# • INT signal output timing

The INT signal output timing for data output is as follows. A circle ("O") indicates that INT is output, and a cross ("X") indicates that the signal is not output.

|               | Control                          | Control                         |                                                                                                                                              | Horizontal correction output |                   |        | Vertical correction output |    |

|---------------|----------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------|--------|----------------------------|----|