# **Document History Information**

| Revision   | Data         | Description                                                                                                                                                                                                                                                                                                                                        |

|------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ver. 1.0.0 | OCT 27, 2005 | Release with W3150A Launching                                                                                                                                                                                                                                                                                                                      |

| Ver. 1.0.1 | NOV 21, 2005 | Replace, 1.8V operation → 3.3V operation (p.3) Change block diagram (p.4) Change figure (p.32) Replace, g_Sn_TX_BASE → g_Sn_RX_BASE (p.33) Replace, memcpy( , ,left_size) → in memcpy( , ,upper_size) (p.40, p.41, p.47, p.48, p.49) Replace, get_offset = Sn_TX_RR & → get_offset = Sn_TX_WR & (p.41, p.49) Replace, SOCK_UDP → SOCK_IPRAW (p.51) |

| Ver. 1.0.2 | DEC 28, 2005 | Add 7.3 Power Dissipation (p.56)                                                                                                                                                                                                                                                                                                                   |

| Ver. 2.0.0 | AUG 15, 2006 | New version release (W3150A -> W3150A+) Add SPI Information Added ND option in socket mode register Remove Memory test mode Add MACRAW mode                                                                                                                                                                                                        |

| Ver. 2.0.1 | JAN 8, 2007  | LB bit in Mode register is not used .<br>W3150A+ used in Big-endian ordering only.                                                                                                                                                                                                                                                                 |

| Ver. 2.0.2 | APR 5, 2007  | Change Operating temperature value (p.57)                                                                                                                                                                                                                                                                                                          |

| Ver. 2.0.3 | May 2, 2007  | Modify explanation of RECV_INT in Sn_IR register (P. 27) Replace reset value of Sn_DHAR register (0x00 to 0xFF, P. 30) Modify explanation of Sn_DIPR, Sn_DPORT register(P. 30) Replace reset value of Sn_MSS register (0xFFFF to 0x00000, P. 31) Modify figure of W3150A+ AC Characteristics(P. 58,59,60,62,63)                                    |

| Ver. 2.0.4 | Oct 5, 2007  | Modify figure of W3150A+ AC Characteristics (Added item NO.7 SCLK high to /SS high, P. 61)                                                                                                                                                                                                                                                         |

| Ver. 2.0.5 | Oct 5, 2015  | Not support SPI mode 3                                                                                                                                                                                                                                                                                                                             |

## WIZnet's Online Technical Support

If you have something to ask about WIZnet Products, Write down your question on <u>Q&A Board</u> of 'Support' menu in WIZnet website (<u>www.wiznet.co.kr</u>). WIZnet Engineer will give an answer as soon as possible.

## W3150A+ Datasheet

## Description

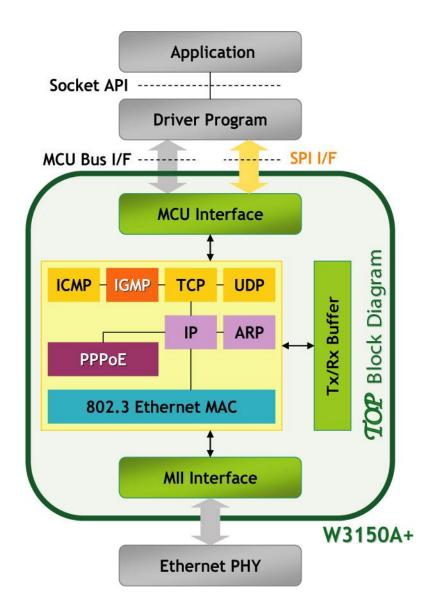

The W3150A+ is an LSI of hardware protocol stack that provides an easy, low-cost solution for high-speed Internet connectivity for digital devices by allowing simple installation of TCP/IP stack in the hardware.

The W3150A+ offers a quick and easy way to add Ethernet networking functionality to any products. Implementing this LSI into a system can completely provide Internet connectivity and process standard protocols by significantly reducing the software development cost as well development time which is most important in today time-to market.

The W3150A+ contains TCP/IP Protocol Stacks such as TCP, UDP, ICMP, IPv4, ARP and PPPoE protocols, as well as Ethernet protocols such as MAC protocol. The total internal memory size is 16Kbytes, which is used as the buffer for data transmission and receipt.

The W3150A+ provides three different interfaces like direct, indirect bus interfaces and SPI(Serial Peripheral Interface) to connect with MCUs and standard MII(Media Independent Interface) composed of nibble data bus to connect with Ethernet PHY devices.

The W3150A+ is a best-fitted device for embedded application including IP-Settop Box, Internet-DVR, Internet phones, VoIP SOC chips, Internet MP3 players, handheld medical devices, various industrial system for monitoring and metering, and any other non-portable electronic devices such as large consumer electronic products.

### **Features**

- Support Hardwired TCP/IP Protocols: TCP, UDP, ICMP, IGMP, IPv4, ARP, PPPoE, Ethernet

- Support ADSL connection (with support PPPoE Protocol with PAP/CHAP Authentication mode)

- Supports 4 independent sockets simultaneously

- Not support IP Fragmentation

- Standard MII Interface for Ethernet-PHY chip

- Supports 10BaseT/100BaseTX

- Supports full-duplex mode

- Internal 16Kbytes Memory for Tx/Rx Buffers

- 0.18 µm CMOS technology

- 3.3V operation with 5V I/O signal tolerance

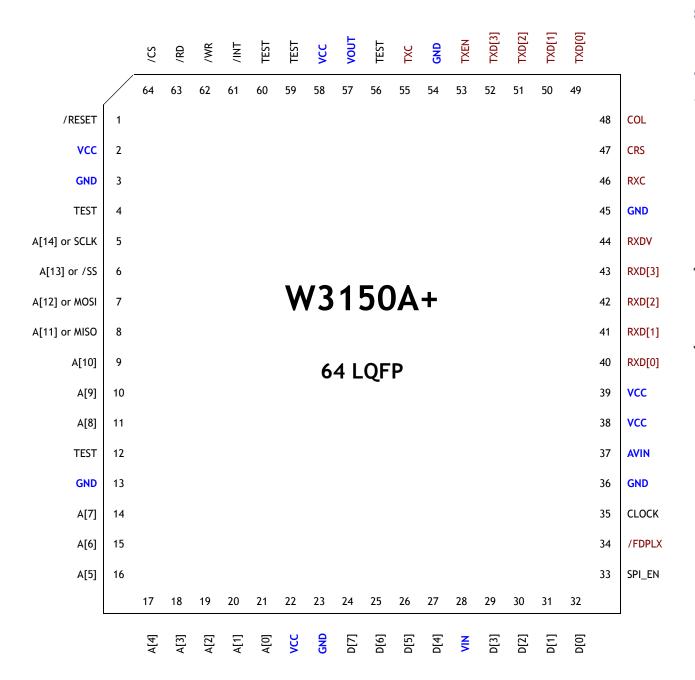

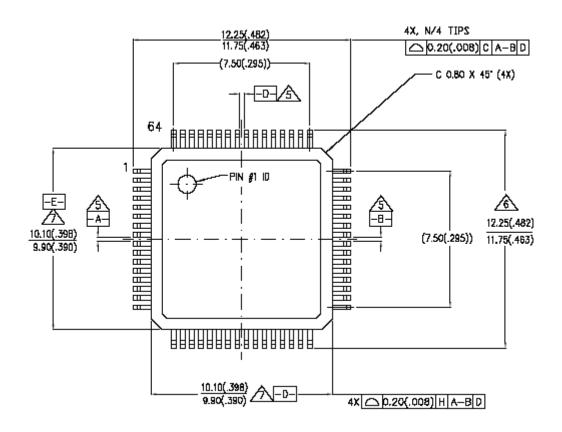

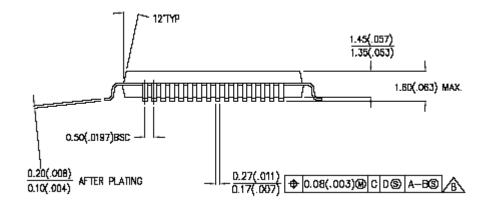

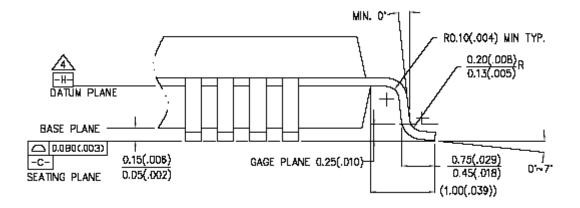

- Small 64 Pin LQFP Package

- Lead-Free Package

- Support Serial Peripheral Interface(SPI MODE 0)

## **Block Diagram**

# **Table of Contents**

| Des                           | cription.      |                       |                                    | 3    |  |  |  |  |

|-------------------------------|----------------|-----------------------|------------------------------------|------|--|--|--|--|

| Fea                           | tures          |                       |                                    | 3    |  |  |  |  |

| Blo                           | ck Diagra      | ım                    |                                    | 4    |  |  |  |  |

| Tab                           | le of Con      | tents                 |                                    | 5    |  |  |  |  |

| 1.                            | Pin Assignment |                       |                                    |      |  |  |  |  |

| 1.1. MII Signal Description   |                |                       |                                    |      |  |  |  |  |

|                               | 1.2.           | MCl                   | J Interface Signal Description     | 9    |  |  |  |  |

|                               | 1.3.           | Misc                  | cellaneous Signal Description      | 11   |  |  |  |  |

|                               | 1.4.           | Pow                   | ver Supply Signal Description      | 12   |  |  |  |  |

| 2.                            | Memory         | / map                 |                                    | 13   |  |  |  |  |

| 3.                            | W3150A         | \+ Reg                | gisters                            | 14   |  |  |  |  |

|                               | 3.1.           | Con                   | nmon Registers                     | 14   |  |  |  |  |

|                               | 3.2.           | Soc                   | ket Registers                      | 15   |  |  |  |  |

| 4.                            | Registe        | r Desc                | riptions                           | 19   |  |  |  |  |

|                               | 4.1.           | Con                   | nmon Registers                     | 19   |  |  |  |  |

|                               | 4.2.           | Soc                   | ket Registers                      | 25   |  |  |  |  |

| 5.                            | Functio        | nal De                | escription                         | 37   |  |  |  |  |

|                               | 5.1.           | Init                  | ialization                         | 37   |  |  |  |  |

|                               | 5.2.           | Dat                   | a communication                    | 39   |  |  |  |  |

|                               | 5.2            | .1.                   | TCP                                | . 39 |  |  |  |  |

|                               | 5.2            | .2.                   | UDP                                | . 47 |  |  |  |  |

|                               | 5.2            | .3.                   | IP raw                             | . 52 |  |  |  |  |

|                               | 5.2            | .4.                   | MAC raw                            | . 54 |  |  |  |  |

| 6.                            | Applica        | tion lı               | nformation                         | 55   |  |  |  |  |

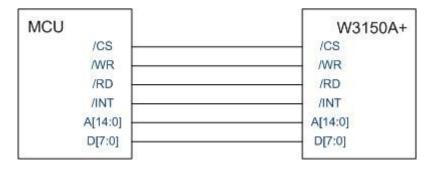

|                               | 6.1.           | Dire                  | ect Bus I/F Mode                   | 55   |  |  |  |  |

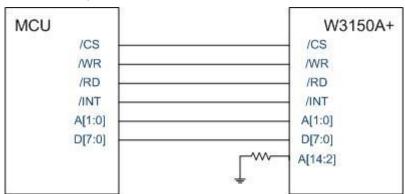

|                               | 6.2.           | Indi                  | rect Bus I/F Mode                  | 55   |  |  |  |  |

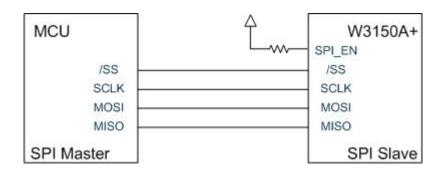

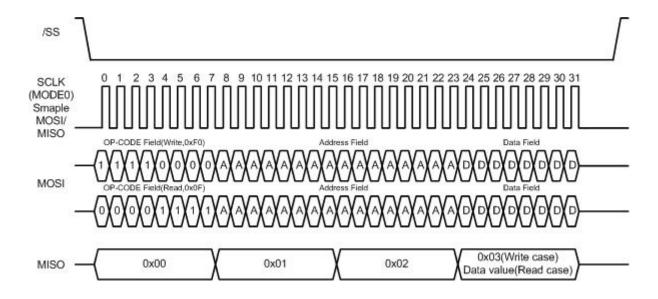

|                               | 6.3.           | Seri                  | al Peripheral Interface (SPI) Mode | 56   |  |  |  |  |

|                               | 6.4.           | MII                   | (Media Independent Interface)      | 58   |  |  |  |  |

| 7. Electrical Specification   |                | ecification           | 59                                 |      |  |  |  |  |

| 7.1. Absolute Maximum Ratings |                | olute Maximum Ratings | 59                                 |      |  |  |  |  |

| 7.2. DC Characteristics       |                | Characteristics       | 59                                 |      |  |  |  |  |

| 7.3. POWER DISSIPATION        |                | VER DISSIPATION       | 59                                 |      |  |  |  |  |

|                               | 7.4.           | AC                    | Characteristics                    | 60   |  |  |  |  |

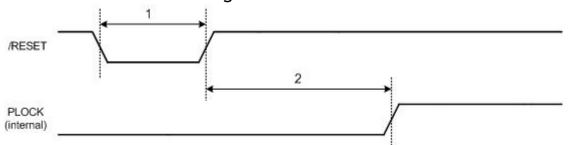

|                               | 7.4            | .1.                   | Reset Timing                       | . 60 |  |  |  |  |

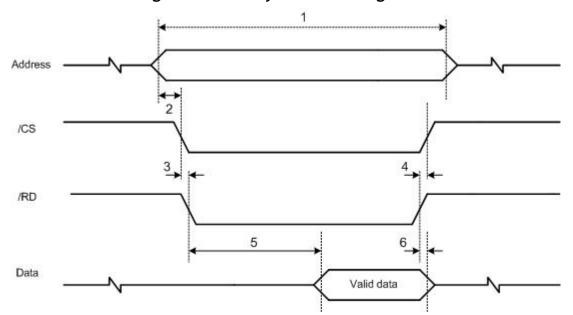

|                               | 7 4            | 2                     | Register/Memory READ Timing        | 61   |  |  |  |  |

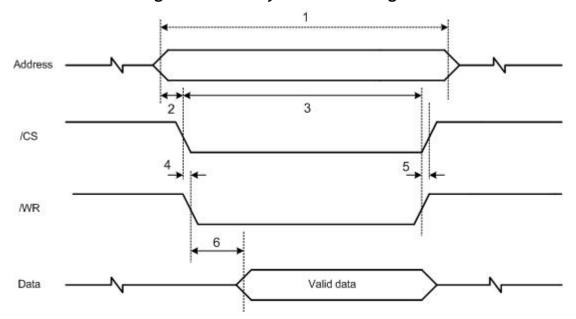

|    | 7.4.3.        | Register/Memory WRITE Timing            | 62   |

|----|---------------|-----------------------------------------|------|

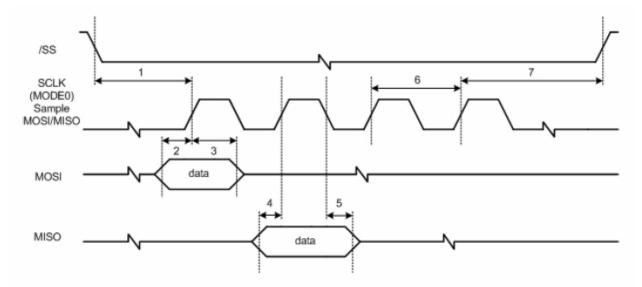

|    | 7.4.4.        | SPI Timing                              | 63   |

|    | 7.4.5.        | MII(Media Independent Interface) Timing | 64   |

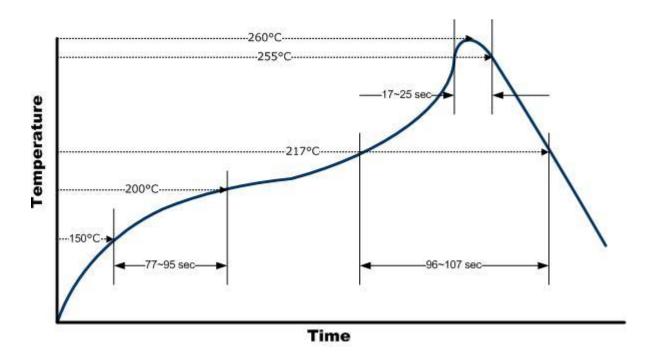

| 8. | IR Reflow Ter | nperature Profile (Lead-Free)           | . 66 |

| a  | Package Dose  | rintion                                 | 6-   |

## 1. Pin Assignment

# 1.1. MII Signal Description

| Pin# | Signal | I/O | Description                                                                    |  |  |

|------|--------|-----|--------------------------------------------------------------------------------|--|--|

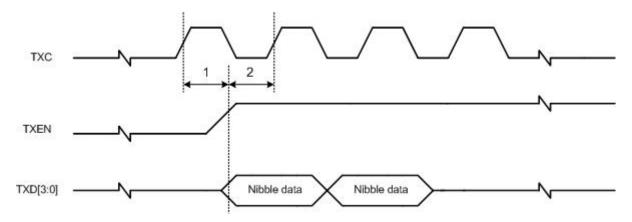

|      |        |     | Transmit Clock                                                                 |  |  |

| EE . | TXC    | ı   | This input pin needs a continuous clock as timing reference for TXD[3:0] and   |  |  |

| 55   | IAC    | ı   | TXEN. TXC is supplied by the PHY. TXC is 2.5 MHz in 10 BASE-T nibble mode,     |  |  |

|      |        |     | and 25MHz in 100BASE-TX nibble mode.                                           |  |  |

|      |        |     | Transmit Enable                                                                |  |  |

|      |        |     | This output signal indicates the presence of a valid nibble data on TXD[3:0].  |  |  |

| 53   | TXEN   | 0   | It becomes active when the first nibble data of the packet is valid on         |  |  |

| 33   | IALIN  | U   | TXD[3:0] and goes low after the last nibble data of the packet is clocked out  |  |  |

|      |        |     | of TXD[3:0]. This signal connects directly to the PHY device. This signal is   |  |  |

|      |        |     | active high.                                                                   |  |  |

| 52   | TXD[3] |     | Transmit Data                                                                  |  |  |

| 51   | TXD[2] | 0   | These pins transmit Nibble NRZ data to the PHY synchronously with TXC          |  |  |

| 50   | TXD[1] | U   | when TXEN is asserted.                                                         |  |  |

| 49   | TXD[0] |     |                                                                                |  |  |

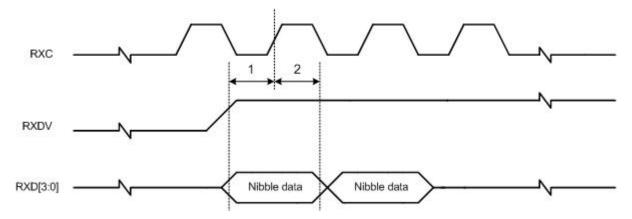

|      | RXC    | I   | Receive Clock                                                                  |  |  |

| 46   |        |     | This input pin needs a continuous clock as timing reference for RXDV and       |  |  |

| 40   |        |     | RXD[3:0] signals. RXC is supplied by the PHY. RXC is 2.5MHz in 10BASE-T        |  |  |

|      |        |     | nibble mode, and 25MHz in 100BASE-TX nibble mode.                              |  |  |

|      |        |     | Collision Detect                                                               |  |  |

| 48   | COL    | I   | The active high signal at this input pin indicates that a collision has been   |  |  |

| 10   |        |     | detected in Half-Duplex modes. This signal is asynchronous and is ignored      |  |  |

|      |        |     | during full-duplex operation.                                                  |  |  |

| 47   | CRS    |     | Carrier Sense                                                                  |  |  |

| 47   | 4/ CK3 |     | The active high signal at this input pin detects that carrier is present.      |  |  |

|      |        |     | Receive Data Valid                                                             |  |  |

| 44   | RXDV   | ı   | If signal is detected high on this input pin, valid data is present on the     |  |  |

| 44   | KXDV   | l   | RXD[3:0]. If signal is detected low at the end of the valid packet, the signal |  |  |

|      |        |     | is valid on the rising of the RXC.                                             |  |  |

| 43   | RXD[3] |     | Receive Data                                                                   |  |  |

| 42   | RXD[2] | ı   | These pins receive Nibble NRZ data from the PHY device synchronously with      |  |  |

| 41   | RXD[1] | •   | RXC when RXDV is asserted.                                                     |  |  |

| 40   | RXD[0] |     |                                                                                |  |  |

# 1.2. MCU Interface Signal Description

| Pin#   | Signal         | 1/0 | Description                                                                  |  |  |

|--------|----------------|-----|------------------------------------------------------------------------------|--|--|

|        |                |     | RESET                                                                        |  |  |

|        |                |     | This pin is active Low input to initialize or re-initialize W3150A+.         |  |  |

| 1      | /RESET         | I   | Asserting this pin low for at least 2us will force a reset process to occur  |  |  |

|        |                |     | which will result in all internal registers re-initializing to their default |  |  |

|        |                |     | states.                                                                      |  |  |

|        |                |     | CLOCK                                                                        |  |  |

|        |                |     | This pin is the Primary clock required for internal operation of W3150A+.    |  |  |

|        |                |     | 25MHz is required. In general, PHY driving clock can be shared for saving    |  |  |

| 35     | CLOCK          |     | cost.                                                                        |  |  |

| 33     | CLOCK          | l   | Note) Sharing crystal source clock with multiple devices may cause some      |  |  |

|        |                |     | troubles. In our reference design, we used one crystal for both PHY and      |  |  |

|        |                |     | W3150A+ with verification.                                                   |  |  |

|        |                |     | But for other kind of PHY, please confirm safety prior to decision.          |  |  |

|        | A [ 4 A ] /    |     | ADDRESS PIN or SCLK (Serial Clock) *                                         |  |  |

| 5      | A[14]/<br>SCLK | I   | This pin is used to select a register or memory.                             |  |  |

|        |                |     | When asserting SPI_EN pin high, this pin is used to SPI Clock signal Pin.    |  |  |

|        |                | 1   | ADDRESS PIN or /SS (Slave Select) *                                          |  |  |

| 4      | A[13]/         |     | This pin is used to select a register or memory.                             |  |  |

| 6      | /SS            |     | When asserting SPI_EN pin high, this pin is used to SPI Slave Select signal  |  |  |

|        |                |     | Pin. In only SPI Mode, this pin is active low                                |  |  |

|        | A[12]/<br>MOSI |     | ADDRESS PIN or MOSI (Master Out Slave In) *                                  |  |  |

| 7      |                |     | This pin is used to select a register or memory.                             |  |  |

|        |                |     | When asserting SPI_EN pin high, this pin is used to SPI MOSI signal pin.     |  |  |

|        | A[44]/         |     | ADDRESS PIN or MISO (Master In Slave Out) *                                  |  |  |

| 8      | A[11]/<br>MISO | 1/0 | This pin is used to select a register or memory.                             |  |  |

|        |                |     | When asserting SPI_EN pin high, this pin is used to SPI MISO signal pin.     |  |  |

| 9:11   | A[10:8]        | 1   | ADDRESS PINS                                                                 |  |  |

| 14:21  | A[7:0]         | I   | These pins are used to select a register or memory.                          |  |  |

| 24:27, | D[7:4]         | 1/0 | DATA PINS                                                                    |  |  |

| 29:32  | D[3:0]         | 1/0 | These pins are used to read and write register or memory data.               |  |  |

<sup>\*\*</sup> Difference from W3150A

|    |      |       | INTERRUPT                                                                      |

|----|------|-------|--------------------------------------------------------------------------------|

|    |      | 0     | This pin Indicates that W3150A+ requires MCU attention after socket            |

| 61 | /INT |       | connecting, disconnecting, receiving data or timeout. The interrupt is         |

|    |      |       | cleared by writing IR(Interrupt Register) or Sn_IR (Socket nth Interrupt       |

|    |      |       | Register). All interrupts are maskable. This signal is active low.             |

|    |      | I     | CHIP SELECT                                                                    |

| 64 | /CS  |       | Chip Select is for MCU access to internal registers/memory. /WR and /RD        |

|    |      |       | select direction of data transfer. This signal is active low.                  |

|    | /WR  | I     | WRITE ENABLE                                                                   |

| 62 |      |       | Strobe from MCU to write an internal register/memory selected by A[14:0].      |

| 02 |      |       | Data is latched into the W3150A+ on the rising edge of this input. This signal |

|    |      |       | is active low.                                                                 |

|    | /RD  | /RD I | READ ENABLE                                                                    |

| 63 |      |       | Strobe from MCU to read an internal register/memory selected by A[14:0].       |

|    |      |       | This signal is active low.                                                     |

# 1.3. Miscellaneous Signal Description

| Pin#              | Signal  | I/O  | Description                                                                           |

|-------------------|---------|------|---------------------------------------------------------------------------------------|

|                   |         | I    | FULL/HALF DUPLEX SELECT                                                               |

|                   |         |      | This pin selects Half/Full Duplex operation mode.                                     |

| 34                | /FDPI X |      | This pin must be externally pulled low (typically x $k\Omega$ ) in order to configure |

| 34                | /I DPLX |      | the W3150A+ for Full Duplex operation.                                                |

|                   |         |      | Low = Full Duplex                                                                     |

|                   |         |      | High = Half Duplex                                                                    |

|                   | SPI_EN  | I    | SPI Enable*                                                                           |

|                   |         |      | This pin selects Enable/disable of the SPI Mode.                                      |

|                   |         |      | This pin is internally pulled down for previous W3150A users. Even if there           |

| 33                |         |      | is no signal connection to this pin, it asserts low internally. Thereby, in case      |

|                   |         |      | of change to W3150A+, there is no effort to change previous board design.             |

|                   |         |      | Low = SPI Mode Disable                                                                |

|                   |         |      | High = SPI Mode Enable                                                                |

| 4,12,56,<br>59,60 | TEST    | ST I | FACTORY TEST INPUT                                                                    |

|                   |         |      | Used to check the chip's internal functions. This should be tied low (pull-           |

|                   |         |      | down) during normal operation.                                                        |

<sup>\* \*</sup> Difference from W3150A

# 1.4. Power Supply Signal Description

| Pin#                  | Signal | I/O | Description                                                    |

|-----------------------|--------|-----|----------------------------------------------------------------|

| 2, 22, 38, 39, 58     | VCC    |     | POSITIVE 3.3V SUPPLY PINS                                      |

| 28                    | VIN    |     | 1.8V power input                                               |

| 20                    | VIN    |     | 1.8V power supply                                              |

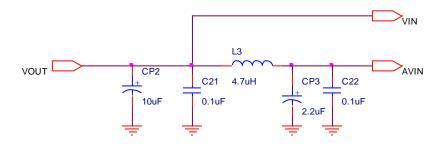

|                       |        |     | 1.8V Analog power input                                        |

| 37                    | AVIN   |     | 1.8V power supply for analog circuit ; should be well          |

| 37                    |        |     | decoupled.                                                     |

|                       |        |     | Refer Figure 1-1. Reference Schematic for Power input.         |

|                       |        |     | 1.8V power out                                                 |

| 57                    | VOLIT  |     | Be sure to connect 10uF tantalum capacitor and a 0.1uF         |

| 57                    | VOUT   |     | capacitor for noise de-coupling. Then connect this pin through |

|                       |        |     | a ferrite bead to VIN and AVIN.                                |

| 3, 13, 23, 36, 45, 54 | GND    |     | NEGATIVE (GROUND) SUPPLY PINS                                  |

Figure 1-1. Reference Schematic for Power input

## 2. Memory map

W3150A+ is composed of Common Register, Socket Register, TX Memory, and RX Memory. Each fields are shown as below.

| 0x0000 | Common Registers |

|--------|------------------|

| 0x0030 | Reserved         |

| 0x0400 | Socket Registers |

| 0x0800 |                  |

|        | Reserved         |

| 0x4000 |                  |

|        | TX memory        |

| 0x6000 | RX memory        |

| 0x8000 |                  |

# 3. W3150A+ Registers

## 3.1. Common Registers

| Address | Register                |

|---------|-------------------------|

| 0x0000  | Mode (MR)               |

|         | Gateway Address         |

| 0x0001  | (GAR0)                  |

| 0x0002  | (GAR1)                  |

| 0x0003  | (GAR2)                  |

| 0x0004  | (GAR3)                  |

|         | Subnet mask Address     |

| 0x0005  | (SUBRO)                 |

| 0x0006  | (SUBR1)                 |

| 0x0007  | (SUBR2)                 |

| 0x0008  | (SUBR3)                 |

|         | Source Hardware Address |

| 0x0009  | (SHARO)                 |

| 0x000A  | (SHAR1)                 |

| 0x000B  | (SHAR2)                 |

| 0x000C  | (SHAR3)                 |

| 0x000D  | (SHAR4)                 |

| 0x000E  | (SHAR5)                 |

|         | Source IP Address       |

| 0x000F  | (SIPRO)                 |

| 0x0010  | (SIPR1)                 |

| 0x0011  | (SIPR2)                 |

| 0x0012  | (SIPR3)                 |

| 0x0013  | Reserved                |

| 0x0014  |                         |

| 0x0015  | Interrupt (IR)          |

| 0x0016  | Interrupt Mask (IMR)    |

|         | Retry Time              |

| 0x0017  | (RTR0)                  |

| 0x0018  | (RTR1)                  |

| 0x0019  | Retry Count (RCR)       |

| Address | Register                       |

|---------|--------------------------------|

| 0x001A  | RX Memory Size (RMSR)          |

| 0x001B  | TX Memory Size (TMSR)          |

|         | Authentication Type in PPPoE   |

| 0x001C  | (PATRO)                        |

| 0x001D  | (PATR1)                        |

| 0x001E  |                                |

| ~       | Reserved                       |

| 0x0027  |                                |

| 0x0028  | PPP LCP Request Timer (PTIMER) |

| 0x0029  | PPP LCP Magic number (PMAGIC)  |

|         | Unreachable IP Address         |

| 0x002A  | (UIPR0)                        |

| 0x002B  | (UIPR1)                        |

| 0x002C  | (UIPR2)                        |

| 0x002D  | (UIPR3)                        |

|         | Unreachable Port               |

| 0x002E  | (UPORT0)                       |

| 0x002F  | (UPORT1)                       |

| 0x0030  |                                |

| ~       | Reserved                       |

| 0x03FF  |                                |

# 3.2. Socket Registers

| Address | Register                              |

|---------|---------------------------------------|

| 0x0400  | Socket 0 Mode (S0_MR)                 |

| 0x0401  | Socket 0 Command (S0_CR)              |

| 0x0402  | Socket 0 Interrupt (S0_IR)            |

| 0x0403  | Socket 0 Status (S0_SR)               |

|         | Socket 0 Source Port                  |

| 0x0404  | (S0_PORT0)                            |

| 0x0405  | (S0_PORT1)                            |

|         | Socket 0 Destination Hardware Address |

| 0x0406  | (SO_DHARO)                            |

| 0x0407  | (SO_DHAR1)                            |

| 0x0408  | (SO_DHAR2)                            |

| 0x0409  | (SO_DHAR3)                            |

| 0x040A  | (SO_DHAR4)                            |

| 0x040B  | (SO_DHAR5)                            |

|         | Socket 0 Destination IP Address       |

| 0x040C  | (SO_DIPRO)                            |

| 0x040D  | (SO_DIPR1)                            |

| 0x040E  | (SO_DIPR2)                            |

| 0x040F  | (SO_DIPR3)                            |

|         | Socket 0 Destination Port             |

| 0x0410  | (SO_DPORTO)                           |

| 0x0411  | (S0_DPORT1)                           |

|         | Socket 0 Maximum Segment Size         |

| 0x0412  | (S0_MSSR0)                            |

| 0x0413  | (S0_MSSR1)                            |

|         | Socket 0 Protocol in IP Raw mode      |

| 0x0414  | (SO_PROTO)                            |

| Address | Register                  |

|---------|---------------------------|

| 0x0415  | Socket 0 IP TOS (S0_TOS)  |

| 0x0416  | Socket 0 IP TTL (S0_TTL)  |

| 0x0417  |                           |

| ~       | Reserved                  |

| 0x041F  |                           |

|         | Socket 0 TX Free Size     |

| 0x0420  | (SO_TX_FSRO)              |

| 0x0421  | (S0_TX_FSR1)              |

|         | Socket 0 TX Read Pointer  |

| 0x0422  | (S0_TX_RD0)               |

| 0x0423  | (S0_TX_RD1)               |

|         | Socket 0 TX Write Pointer |

| 0x0424  | (S0_TX_WR0)               |

| 0x0425  | (S0_TX_WR1)               |

|         | Socket 0 RX Received Size |

| 0x0426  | (SO_RX_RSRO)              |

| 0x0427  | (SO_RX_RSR1)              |

|         | Socket 0 RX Read Pointer  |

| 0x0428  | (S0_RX_RD0)               |

| 0x0429  | (S0_RX_RD1)               |

| 0x042A  | Reserved                  |

| 0x042B  |                           |

| 0x042C  |                           |

| ~       | Reserved                  |

| 0x04FF  |                           |

| Address | Register                              |  |  |

|---------|---------------------------------------|--|--|

| 0x0500  | Socket 1 Mode (S1_MR)                 |  |  |

| 0x0501  | Socket 1 Command (S1_CR)              |  |  |

| 0x0502  | Socket 1 Interrupt (S1_IR)            |  |  |

| 0x0503  | Socket 1 Status (S1_SR)               |  |  |

|         | Socket 1 Source Port                  |  |  |

| 0x0504  | (S1_PORT0)                            |  |  |

| 0x0505  | (S1_PORT1)                            |  |  |

|         | Socket 1 Destination Hardware Address |  |  |

|         | (S1_DHAR0)                            |  |  |

| 0x0506  | (S1_DHAR1)                            |  |  |

| 0x0507  | (S1_DHAR2)                            |  |  |

| 0x0508  | (S1_DHAR3)                            |  |  |

| 0x0509  | (S1_DHAR4)                            |  |  |

| 0x050A  | (S1_DHAR5)                            |  |  |

| 0x050B  |                                       |  |  |

|         | Socket 1 Destination IP Address       |  |  |

| 0x050C  | (S1_DIPRO)                            |  |  |

| 0x050D  | (S1_DIPR1)                            |  |  |

| 0x050E  | (S1_DIPR2)                            |  |  |

| 0x050F  | (S1_DIPR3)                            |  |  |

|         | Socket 1 Destination Port             |  |  |

| 0x0510  | (S1_DPORT0)                           |  |  |

| 0x0511  | (S1_DPORT1)                           |  |  |

|         | Socket 1 Maximum Segment Size         |  |  |

| 0x0512  | (S1_MSSR0)                            |  |  |

| 0x0513  | (S1_MSSR1)                            |  |  |

|         | Socket 1 Protocol in IP Raw mode      |  |  |

| 0x0514  | (S1_PROTO)                            |  |  |

| Address | Register                  |

|---------|---------------------------|

| 0x0515  | Socket 1 IP TOS (S1_TOS)  |

| 0x0516  | Socket 1 IP TTL (S1_TTL)  |

| 0x0517  |                           |

| ~       | Reserved                  |

| 0x051F  |                           |

|         | Socket 1 TX Free Size     |

| 0x0520  | (S1_TX_FSR0)              |

| 0x0521  | (S1_TX_FSR1)              |

|         | Socket 1 TX Read Pointer  |

| 0x0522  | (S1_TX_RD0)               |

| 0x0523  | (S1_TX_RD1)               |

|         | Socket 1 TX Write Pointer |

| 0x0524  | (S1_TX_WR0)               |

| 0x0525  | (S1_TX_WR1)               |

|         | Socket 1 RX Received Size |

| 0x0526  | (S1_RX_RSR0)              |

| 0x0527  | (S1_RX_RSR1)              |

|         | Socket 1 RX Read Pointer  |

| 0x0528  | (S1_RX_RD0)               |

| 0x0529  | (S1_RX_RD1)               |

| 0x052A  | Reserved                  |

| 0x052B  |                           |

| 0x052C  |                           |

| ~       | Reserved                  |

| 0x05FF  |                           |

| Address | Register                              |

|---------|---------------------------------------|

| 0x0600  | Socket 2 Mode (S2_MR)                 |

| 0x0601  | Socket 2 Command (S2_CR)              |

| 0x0602  | Socket 2 Interrupt (S2_IR)            |

| 0x0603  | Socket 2 Status (S2_SR)               |

|         | Socket 2 Source Port                  |

| 0x0604  | (S2_PORT0)                            |

| 0x0605  | (S2_PORT1)                            |

|         | Socket 2 Destination Hardware Address |

|         | (S2_DHAR0)                            |

| 0x0606  | (S2_DHAR1)                            |

| 0x0607  | (S2_DHAR2)                            |

| 0x0608  | (S2_DHAR3)                            |

| 0x0609  | (S2_DHAR4)                            |

| 0x060A  | (S2_DHAR5)                            |

| 0x060B  |                                       |

|         | Socket 2 Destination IP Address       |

| 0x060C  | (S2_DIPR0)                            |

| 0x060D  | (S2_DIPR1)                            |

| 0x060E  | (S2_DIPR2)                            |

| 0x060F  | (S2_DIPR3)                            |

|         | Socket 2 Destination Port             |

| 0x0610  | (S2_DPORT0)                           |

| 0x0611  | (S2_DPORT1)                           |

|         | Socket 2 Maximum Segment Size         |

| 0x0612  | (S2_MSSR0)                            |

| 0x0613  | (S2_MSSR1)                            |

|         | Socket 2 Protocol in IP Raw mode      |

| 0x0614  | (S2_PROTO)                            |

| Address | Register                  |

|---------|---------------------------|

| 0x0615  | Socket 2 IP TOS (S2_TOS)  |

| 0x0616  | Socket 2 IP TTL (S2_TTL)  |

| 0x0617  |                           |

| ~       | Reserved                  |

| 0x061F  |                           |

|         | Socket 2 TX Free Size     |

| 0x0620  | (S2_TX_FSR0)              |

| 0x0621  | (S2_TX_FSR1)              |

|         | Socket 2 TX Read Pointer  |

| 0x0622  | (S2_TX_RD0)               |

| 0x0623  | (S2_TX_RD1)               |

|         | Socket 2 TX Write Pointer |

| 0x0624  | (S2_TX_WR0)               |

| 0x0625  | (S2_TX_WR1)               |

|         | Socket 2 RX Received Size |

| 0x0626  | (S2_RX_RSR0)              |

| 0x0627  | (S2_RX_RSR1)              |

|         | Socket 2 RX Read Pointer  |

| 0x0628  | (S2_RX_RD0)               |

| 0x0629  | (S2_RX_RD1)               |

| 0x062A  | Reserved                  |

| 0x062B  |                           |

| 0x062C  |                           |

| ~       | Reserved                  |

| 0x06FF  |                           |

| Address | Register                              |

|---------|---------------------------------------|

| 0x0700  | Socket 3 Mode (S3_MR)                 |

| 0x0701  | Socket 3 Command (S3_CR)              |

| 0x0702  | Socket 3 Interrupt (S3_IR)            |

| 0x0703  | Socket 3 Status (S3_SR)               |

|         | Socket 3 Source Port                  |

| 0x0704  | (S3_PORT0)                            |

| 0x0705  | (S3_PORT1)                            |

|         | Socket 3 Destination Hardware Address |

|         | (S3_DHAR0)                            |

| 0x0706  | (S3_DHAR1)                            |

| 0x0707  | (S3_DHAR2)                            |

| 0x0708  | (S3_DHAR3)                            |

| 0x0709  | (S3_DHAR4)                            |

| 0x070A  | (S3_DHAR5)                            |

| 0x070B  |                                       |

|         | Socket 3 Destination IP Address       |

| 0x070C  | (S3_DIPRO)                            |

| 0x070D  | (S3_DIPR1)                            |

| 0x070E  | (S3_DIPR2)                            |

| 0x070F  | (S3_DIPR3)                            |

|         | Socket 3 Destination Port             |

| 0x0710  | (S3_DPORT0)                           |

| 0x0711  | (S3_DPORT1)                           |

|         | Socket 3 Maximum Segment Size         |

| 0x0712  | (S3_MSSR0)                            |

| 0x0713  | (S3_MSSR1)                            |

|         | Socket 3 Protocol in IP Raw mode      |

| 0x0714  | (S3_PROTO)                            |

| Address | Register                  |  |

|---------|---------------------------|--|

| 0x0715  | Socket 3 IP TOS (S3_TOS)  |  |

| 0x0716  | Socket 3 IP TTL (S3_TTL)  |  |

| 0x0717  |                           |  |

| ~       | Reserved                  |  |

| 0x071F  |                           |  |

|         | Socket 3 TX Free Size     |  |

| 0x0720  | (S3_TX_FSR0)              |  |

| 0x0721  | (S3_TX_FSR1)              |  |

|         | Socket 3 TX Read Pointer  |  |

| 0x0722  | (S3_TX_RD0)               |  |

| 0x0723  | (S3_TX_RD1)               |  |

|         | Socket 3 TX Write Pointer |  |

| 0x0724  | (S3_TX_WR0)               |  |

| 0x0725  | (S3_TX_WR1)               |  |

|         | Socket 3 RX Received Size |  |

| 0x0726  | (S3_RX_RSR0)              |  |

| 0x0727  | (S3_RX_RSR1)              |  |

|         | Socket 3 RX Read Pointer  |  |

| 0x0728  | (S3_RX_RD0)               |  |

| 0x0729  | (S3_RX_RD1)               |  |

| 0x072A  | Reserved                  |  |

| 0x072B  |                           |  |

| 0x072C  |                           |  |

| ~       | Reserved                  |  |

| 0x07FF  |                           |  |

## 4. Register Descriptions

## 4.1. Common Registers

#### MR (Mode Register) [R/W] [0x0000] [0x00]<sup>1</sup>

This register is used for S/W Reset, memory test mode, ping block mode, PPPoE mode and Indirect bus I/F.

| 7   | 6 | 5 | 4  | 3     | 2 | 1  | 0   |

|-----|---|---|----|-------|---|----|-----|

| RST |   |   | РВ | PPPoE |   | Al | IND |

| Bit | Symbol   | Description                                                                                 |

|-----|----------|---------------------------------------------------------------------------------------------|

| 7   |          | S/W Reset                                                                                   |

| 7   | RST      | If this bit is '1', internal register will be initialized. It will be automatically cleared |

|     |          | after reset.                                                                                |

| 6   | Reserved | Reserved                                                                                    |

| 5   | Reserved | Reserved                                                                                    |

|     |          | Ping Block Mode                                                                             |

| 4   | PB       | 0 : Disable Ping block                                                                      |

| 4   | PD       | 1 : Enable Ping block                                                                       |

|     |          | If the bit is set as '1', there is no response to the ping request.                         |

|     |          | PPPoE Mode                                                                                  |

|     |          | 0 : Disable PPPoE mode                                                                      |

| 3   | PPPoE    | 1 : Enable PPPoE mode                                                                       |

| 3   | PPPOE    | If you use ADSL without router or etc, you should set the bit as '1', and connect to ADSL   |

|     |          | Server. For more detail, refer to the application note, "How to connect ADSL".              |

|     |          |                                                                                             |

| 2   | Not used | Not used.                                                                                   |

|     |          | Address Auto-Increment in Indirect Bus I/F                                                  |

|     |          | 0 : Disable auto-increment                                                                  |

|     | 4.1      | 1 : Enable auto-increment                                                                   |

| 1   | Al       | At the Indirect Bus I/F mode, if this bit is set as '1', the address will be automatically  |

|     |          | increased by 1 whenever Read and Write are performed. For more detail, refer to 6.1.2       |

|     |          | Indirect Bus IF Mode.                                                                       |

|     | INID     | Indirect Bus I/F mode                                                                       |

| 0   | IND      | 0 : Disable Indirect bus I/F mode                                                           |

<sup>\* [</sup>Read/Write] [Address] [Reset value]

1: Enable Indirect bus I/F mode

If this bit is set as '1', Indirect BUS I/F mode is set. For more detail, refer to 6. Application Information, 6.1.2. Indirect Bus IF Mode.

#### GWR (Gateway IP Address Register) [R/W] [0x0001 - 0x0004] [0x00]

This Register sets up the default gateway address.

Ex) in case of "192.168.0.1"

| 0x0001 |            | 0x0002     | 0x0003   | 0x0004   |

|--------|------------|------------|----------|----------|

|        | 192 (0xC0) | 168 (0xA8) | 0 (0x00) | 1 (0x01) |

#### SUBR (Subnet Mask Register) [R/W] [0x0005 - 0x0008] [0x00]

This register sets up the subnet mask address.

Ex) in case of "255.255.255.0"

| 0x0005     | 0x0006     | 0x0007     | 0x0008   |

|------------|------------|------------|----------|

| 255 (0xFF) | 255 (0xFF) | 255 (0xFF) | 0 (0x00) |

#### SHAR (Source Hardware Address Register) [R/W] [0x0009 - 0x000E] [0x00]

This register sets up the Source Hardware address.

Ex) In case of "00.08.DC.01.02.03"

| 0x0009 | 0x000A | 0x000B | 0x000C | 0x000D | 0x000E |

|--------|--------|--------|--------|--------|--------|

| 0x00   | 0x08   | 0xDC   | 0x01   | 0x02   | 0x03   |

### SIPR (Source IP Address Register) [R/W] [0x000F - 0x0012] [0x00]

This register sets up the Source IP address.

Ex) in case of "192.168.0.3"

| 0x000F     | 0x0010     | 0x0011   | 0x0012   |  |

|------------|------------|----------|----------|--|

| 192 (0xC0) | 168 (0xA8) | 0 (0x00) | 3 (0x03) |  |

#### IR (Interrupt Register) [R] [0x0015] [0x00]

This register is accessed by the host processor to know the cause of an interrupt.

Any interrupt can be masked in the Interrupt Mask Register (IMR). The /INT signal retain low as long as any masked signal is set, and will not go high until all masked bits in this Register have been cleared.

| 7        | 6       | 5     | 4        | 3      | 2      | 1      | 0      |

|----------|---------|-------|----------|--------|--------|--------|--------|

| CONFLICT | UNREACH | PPPoE | Reserved | S3_INT | S2_INT | S1_INT | SO_INT |

| Bit | Symbol              | Description                                                                                |  |  |

|-----|---------------------|--------------------------------------------------------------------------------------------|--|--|

|     | ,                   | IP Conflict                                                                                |  |  |

| 7   | CONFLICT            | It is set as '1', when there is ARP request with same IP address as Source IP address.     |  |  |

|     |                     | This bit is cleared to '0' by writing '1' to this bit.*                                    |  |  |

|     |                     | Destination unreachable                                                                    |  |  |

|     |                     | W3150A+ will receive ICMP(Destination Unreachable) packet if not-existing destination      |  |  |

|     | III IDEA CII        | IP address is transmitted during UDP data transmission. (Refer to 5.2.2. UDP). In this     |  |  |

| 6   | UNREACH             | case, the IP address and the port number will be saved in Unreachable IP Address (UIPR)    |  |  |

|     |                     | and Unreachable Port Register (UPORT), and the bit will be set as '1'. This bit will be    |  |  |

|     |                     | cleared to '0' by writing '1' to this bit.*                                                |  |  |

|     |                     | PPPoE Close                                                                                |  |  |

| 5   | PPPoE               | In the PPPoE Mode, if the PPPoE connection is closed, '1' is set. This bit will be cleared |  |  |

|     |                     | to '0' by writing '1' to this bit.*                                                        |  |  |

| 4   | 4 Reserved Reserved |                                                                                            |  |  |

|     | S3_INT              | Occurrence of Socket 3 Socket Interrupt                                                    |  |  |

| 3   |                     | It is set in case that interrupt occurs at the socket 3. For more detailed information of  |  |  |

| ٥   |                     | socket interrupt, refer to "Socket 3 Interrupt Register (S3_IR). This bit will be          |  |  |

|     |                     | automatically cleared when S3_IR is cleared to 0x00.                                       |  |  |

|     |                     | Occurrence of Socket 2 Socket Interrupt                                                    |  |  |

| 2   | S2_INT              | It is set in case that interrupt occurs at the socket 2. For more detailed information of  |  |  |

|     | 32_1111             | socket interrupt, refer to "Socket 2 Interrupt Register(S2_IR). This bit will be           |  |  |

|     |                     | automatically cleared when S2_IR is cleared to 0x00.                                       |  |  |

|     |                     | Occurrence of Socket 1 Socket Interrupt                                                    |  |  |

| 1   | S1_INT              | It is set in case that interrupt occurs at the socket 1. For more detailed information of  |  |  |

| '   | 31_1111             | socket interrupt, refer to "Socket 1 Interrupt Register (S1_IR). This bit will be          |  |  |

|     |                     | automatically cleared when S1_IR is cleared to 0x00.                                       |  |  |

<sup>\*</sup> Difference from W3150A

|   | S0_INT | Occurrence of Socket 0 Socket Interrupt                                                   |

|---|--------|-------------------------------------------------------------------------------------------|

|   |        | It is set in case that interrupt occurs at the socket 0. For more detailed information of |

| 0 |        | socket interrupt, refer to "Socket 0 Interrupt Register (SO_IR). This bit will be         |

|   |        | automatically cleared when SO_IR is cleared to 0x00.                                      |

#### IMR (Interrupt Mask Register) [R/W] [0x0016] [0x00]

The Interrupt Mask Register is used to mask interrupts. Each interrupt mask bit corresponds to a bit in the Interrupt Register (IR). If an interrupt mask bit is set, an interrupt will be issued whenever the corresponding bit in the IR is set. If any bit in the IMR is set as '0', an interrupt will not occur though the bit in the IR is set.

| 7      | 6      | 5      | 4        | 3      | 2      | 1      | 0      |

|--------|--------|--------|----------|--------|--------|--------|--------|

| IM_IR7 | IM_IR6 | IM_IR5 | Reserved | IM_IR3 | IM_IR2 | IM_IR1 | IM_IR0 |

| Bit | Symbol   | Description                                    |  |  |

|-----|----------|------------------------------------------------|--|--|

| 7   | IM_IR7   | IP Conflict Enable                             |  |  |

| 6   | IM_IR6   | Destination unreachable Enable                 |  |  |

| 5   | IM_IR5   | PPPoE Close Enable                             |  |  |

| 4   | Reserved | It should be set as '0'                        |  |  |

| 3   | IM_IR3   | Occurrence of Socket 3 Socket Interrupt Enable |  |  |

| 2   | IM_IR2   | Occurrence of Socket 2 Socket Interrupt Enable |  |  |

| 1   | IM_IR1   | Occurrence of Socket 1 Socket Interrupt Enable |  |  |

| 0   | IM_IR0   | Occurrence of Socket 0 Socket Interrupt Enable |  |  |

#### RTR (Retry Time-value Register) [R/W] [0x0017 - 0x0018] [0x07D0]

This register sets the period of timeout. Value 1 means 100us. The initial value is 2000(0x07D0). That will be set as 200ms.

Ex) For 400ms configuration, set as 4000(0x0FA0)

| 0x0017 | 0x0018 |

|--------|--------|

| 0x0F   | 0xA0   |

Re-transmission will occur if there is no response from the remote peer to the commands of CONNECT, DISCON, CLOSE, SEND, SEND\_MAC and SEND\_KEEP, or the response is delayed.

#### RCR (Retry Count Register) [R/W] [0x0019] [0x08]

This register sets the number of re-transmission. If retransmission occurs more than the number recorded in RCR, Timeout Interrupt (TIMEOUT bit of Socket n Interrupt Register (Sn\_IR) is set as '1') will occur.

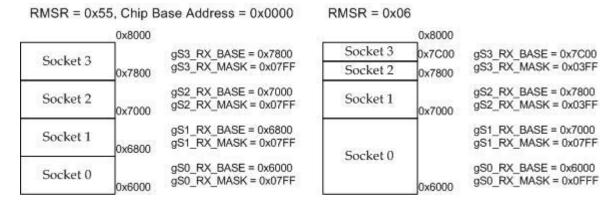

#### RMSR(RX Memory Size Register) [R/W] [0x001A] [0x55]

This register assigns total 8K RX Memory to each socket.

| 7          | 6     | 5    | 4     | 3    | 2     | 1          | 0     |

|------------|-------|------|-------|------|-------|------------|-------|

| Soc        | ket 3 | Sock | ket 2 | Sock | ket 1 | Sock       | ket 0 |

| <b>S</b> 1 | S0    | S1   | S0    | S1   | S0    | <b>S</b> 1 | S0    |

The memory size according to the configuration of S1, S0, is as below.

| <b>S1</b> | S0 | Memory size |  |

|-----------|----|-------------|--|

| 0         | 0  | 1KB         |  |

| 0         | 1  | 2KB         |  |

| 1         | 0  | 4KB         |  |

| 1         | 1  | 8KB         |  |

According to the value of S1 and S0, the memory is assigned to the sockets from socket 0 within the range of 8KB. If there is not enough memory to be assigned, the socket should not be used. The initial value is 0x55 and the 2K memory is assigned to each 4 sockets respectively.

Ex) When setting as 0xAA, the 4KB memory should be assigned to each socket.

However, the total memory size is 8KB. The memory is normally assigned to the socket 0 and 1, but not to the socket 2 and 3. Therefore, socket 2 and 3 are not absolutely used.

| Socket 3 | Socket 2 | Socket 1 | Socket 0 |  |

|----------|----------|----------|----------|--|

| 0KB      | 0KB      | 4KB      | 4KB      |  |

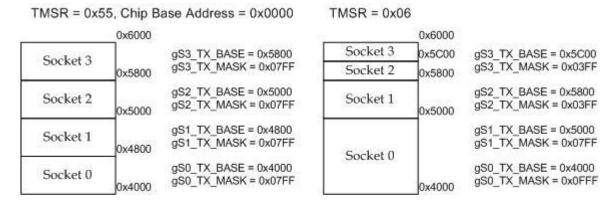

#### TMSR(TX Memory Size Register) [R/W] [0x001B] [0x55]

This register is used in assigning total 8K TX Memory to sockets. Configuration can be done in the same way of RX Memory Size Register (RMSR). The initial value is 0x55 and it is to assign 2K memory to 4 sockets respectively.

#### PATR (Authentication Type in PPPoE mode) [R] [0x001C-0x001D] [0x0000]

This register notifies authentication method that has been agreed at the connection with PPPoE Server. W3150A+ supports two types of Authentication method - PAP and CHAP.

| Value  | Authentication Type |  |

|--------|---------------------|--|

| 0xC023 | PAP                 |  |

| 0xC223 | СНАР                |  |

#### PTIMER (PPP Link Control Protocol Request Timer Register) [R/W] [0x0028] [0x28]

This register indicates the duration for sending LCP Echo Request. Vaule 1 is about 25ms.

Ex) in case that PTIMER is 200,

200 \* 25(ms) = 5000(ms) = 5 seconds

#### PMAGIC (PPP Link Control Protocol Magic number Register) [R/W] [0x0029] [0x001

This register is used in Magic number option during LCP negotiation. Refer to the application note, "How to connect ADSL".

#### UIPR (Unreachable IP Address Register) [R] [0x002A - 0x002D] [0x00]

In case of data transmission by using UDP (refer to 5.2.2. UDP), if transmitting to non-existing IP address, ICMP (Destination Unreachable) packet will be received. In this case, that IP address and port number will be respectively saved in the Unreachable IP Address Register(UIPR) and Unreachable Port Register(UPORT). Ex) in case of "192.168.0.11",

| 0x002A 0x002B |            | 0x002C   | 0x002D    |  |

|---------------|------------|----------|-----------|--|

| 192 (0xC0)    | 168 (0xA8) | 0 (0x00) | 11 (0x0B) |  |

#### UPORT (Unreachable Port Register) [R] [0x002E - 0x002F] [0x0000]

Refer to Unreachable IP Address Register (UIPR)

Ex) In case of 5000(0x1388),

| 0x002E | 0x002F |

|--------|--------|

| 0x13   | 0x88   |

## 4.2. Socket Registers

Sn<sup>1</sup>\_MR (Socket n Mode Register) [R/W] [0x0400, 0x0500, 0x0600, 0x0700] [0x00]<sup>2</sup>

This register sets up socket option or protocol type for each socket.

| 7     | 6 | 5       | 4 | 3  | 2  | 1  | 0  |

|-------|---|---------|---|----|----|----|----|

| MULTI |   | ND / MC |   | P3 | P2 | P1 | Р0 |

| Bit | Symbol   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | MULTI    | <ul> <li>Multicasting</li> <li>0: disable Multicasting</li> <li>1: enable Multicasting</li> <li>It is applied only in case of UDP.</li> <li>For using multicasting, write multicast group address to Socket n Destination IP and multicast group port number to Socket n Destination Port Register, before OPEN command.</li> </ul>                                                                                                          |

| 6   | Reserved | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5   | ND/MC    | Use No Delayed ACK  0: Disable No Delayed ACK option  1: Enable No Delayed ACK option,  It is applied only in case of TCP. If this bit is set as '1', ACK packet is transmitted whenever receiving data packet from the peer. If this bit is cleared to '0', ACK packet is transmitted according to internal Timeout mechanism.  Multicast  0: using IGMP version 2  1: using IGMP version 1  It is applied only in case of MULTI bit is '1' |

| 4   | Reserved | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                     |

<sup>&</sup>lt;sup>1</sup> *n* is socket number (0, 1, 2, 3).

<sup>&</sup>lt;sup>2</sup> [Read/Write] [address of socket 0, address of socket 1, address of socket 2, address of socket 3] [Reset value]

|   | P3 | Protoco                                                  | ol |    |    |         |  |  |

|---|----|----------------------------------------------------------|----|----|----|---------|--|--|

| 3 |    | Sets up corresponding socket as TCP, UDP, or IP RAW mode |    |    |    |         |  |  |

|   |    | Р3                                                       | P2 | P1 | P0 | Meaning |  |  |

|   |    | 0                                                        | 0  | 0  | 0  | Closed  |  |  |

| 2 | P2 | 0                                                        | 0  | 0  | 1  | ТСР     |  |  |

|   |    | 0                                                        | 0  | 1  | 0  | UDP     |  |  |

| 1 | P1 | 0                                                        | 0  | 1  | 1  | IPRAW   |  |  |

| ' | PI |                                                          |    |    |    |         |  |  |

|   |    | * In case of socket 0, MACRAW and PPPoE mode exist.      |    |    |    |         |  |  |

|   |    | P3                                                       | P2 | P1 | P0 | Meaning |  |  |

| 0 | P0 | 0                                                        | 1  | 0  | 0  | MACRAW  |  |  |

|   |    | 0                                                        | 1  | 0  | 1  | PPPoE   |  |  |

### Sn\_CR (Socket n Command Register) [R/W] [0x0401, 0x0501, 0x0601, 0x0701] [0x00]

This register is utilized for socket n initialization, close, connection establishment, termination, data transmission and command receipt. After performing the commands, the register value will be automatically cleared to 0x00.

| Value | Symbol  | Description                                                                             |

|-------|---------|-----------------------------------------------------------------------------------------|

|       |         | It is used to initialize the socket. According to the value of Socket $n$ Mode Register |

| 0x01  | OPEN    | $(Sn\_MR)$ , Socket $n$ Status Register $(Sn\_SR)$ value is changed to SOCK_INIT,       |

| UXU1  | OPEN    | SOCK_UDP, SOCK_IPRAW, or SOCK_MACRAW.                                                   |

|       |         | For more detail, refer to 5. Functional Description.                                    |

|       |         | It is only used in TCP mode.                                                            |

| 0x02  | LISTEN  | It changes the value of Socket <i>n</i> Status Register (Sn_SR) to SOCK_LISTEN in order |

| 0.002 | LISTLIN | to wait for a connection request from any remote peer (TCP Client).                     |

|       |         | For more detail, refer to 5.2.1.1. SERVER.                                              |

|       | CONNECT | It is only used in TCP mode.                                                            |

| 0x04  |         | It sends a connection request to remote peer(TCP SERVER). If the connection is          |

| 0.04  |         | failed, Timeout interrupt will occur.                                                   |

|       |         | For more detail, refer to 5.2.1.2. CLIENT.                                              |

|       |         | It is only used in TCP mode.                                                            |

|       |         | It sends a connection termination request. If connection termination is failed,         |

| 0x08  | DISCON  | Timeout interrupt will occur. For more detail, refer to 5.2.1.1. SERVER.                |

| 0.000 | DISCON  | * In case of using CLOSE command instead of DISCON, only the value of Socket n          |

|       |         | Status Register(Sn_SR) is changed to SOCK_CLOSED without the connection                 |

|       |         | termination process.                                                                    |

| 0x10 | CLOSE     | It is used to close the socket. It changes the value of Socket $n$ Status Register(S $n$ _SR) to SOCK_CLOSED.                                                                                                                                                                                                                 |  |  |  |  |

|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0x20 | SEND      | It transmits the data as much as the increased size of Socket $n$ TX Write Pointer. For more detail, refert to Socket $n$ TX Free Size Register ( $Sn_TX_FSR$ ), Socket $n$ TX Write Pointer Register( $Sn_TX_WR$ ), and Socket $n$ TX Read Pointer Register( $Sn_TX_RR$ ) or 5.2.1.1. SERVER.                                |  |  |  |  |

| 0x21 | SEND_MAC  | It is used in UDP mode.  The basic operation is same as SEND. Normally SEND operation needs Destination Hardware Address that is received in ARP(Address Resolution Protocol) process.  SEND_MAC uses Socket <i>n</i> Destination Hardware Address(S <i>n</i> _DHAR) that is written by users without ARP process.            |  |  |  |  |

| 0x22 | SEND_KEEP | It is only used in TCP mode.  It checks the connection status by sending 1byte data. If the connection is already terminated or peer has no response, Timeout interrupt will occur.                                                                                                                                           |  |  |  |  |

| 0x40 | RECV      | Receiving is processed with the value of Socket $n$ RX Read Pointer Register( $Sn_RX_RD$ ).  For more detail, refer to 5.2.1.1. SERVER Receiving Process with Socket $n$ RX Received Size Register ( $Sn_RX_RSR$ ), Socket $n$ RX Write Pointer Register( $Sn_RX_WR$ ), and Socket $n$ RX Read Pointer Register( $Sn_RX_RD$ ) |  |  |  |  |

#### Sn\_IR (Socket n Interrupt Register) [R] [0x0402, 0x0502, 0x0602, 0x0702] [0x00]

This register is used for notifying connection establishment and termination, receiving data and Timeout. The Socket *n* Interrupt Register must be cleared by writing '1'. \*

| 7        | 6        | 5        | 4       | 3       | 2    | 1      | 0   |

|----------|----------|----------|---------|---------|------|--------|-----|

| Reserved | Reserved | Reserved | SEND_OK | TIMEOUT | RECV | DISCON | CON |

| Bit | Symbol   | Description                                                                                           |  |  |  |

|-----|----------|-------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | Reserved | Reserved                                                                                              |  |  |  |

| 6   | Reserved | leserved                                                                                              |  |  |  |

| 5   | Reserved | Reserved                                                                                              |  |  |  |

| 4   | SEND_OK  | It is set as '1' if send operation is completed.**                                                    |  |  |  |

| 3   | TIMEOUT  | It is set as '1' if Timeout occurs during connection establishment or terminat and data transmission. |  |  |  |

| 2   | RECV     | It is set as '1' whenever w3150a+ receives data.                                                      |  |  |  |

<sup>\*</sup> Difference from W3150A \*\* SEND\_OK Interrupt is added in W3150A+

|  |  | And it is also set as '1' if received data remains after CMD_RECV executes. |

|--|--|-----------------------------------------------------------------------------|

|--|--|-----------------------------------------------------------------------------|

| 1 | DISCON | It is set as '1' if connection termination is requested or finished. |

|---|--------|----------------------------------------------------------------------|

| 0 | CON    | It is set as '1' if connection is established.                       |

#### Sn\_SR (Socket n Status Register) [R] [0x0403, 0x0503, 0x0603, 0x0703] [0x00]

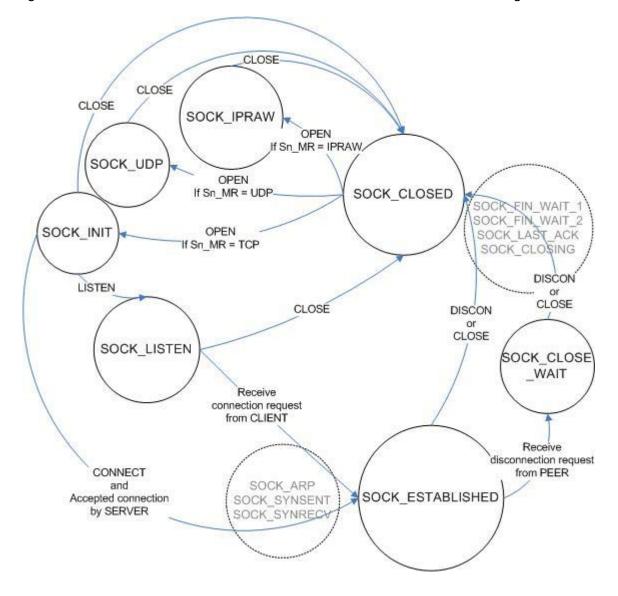

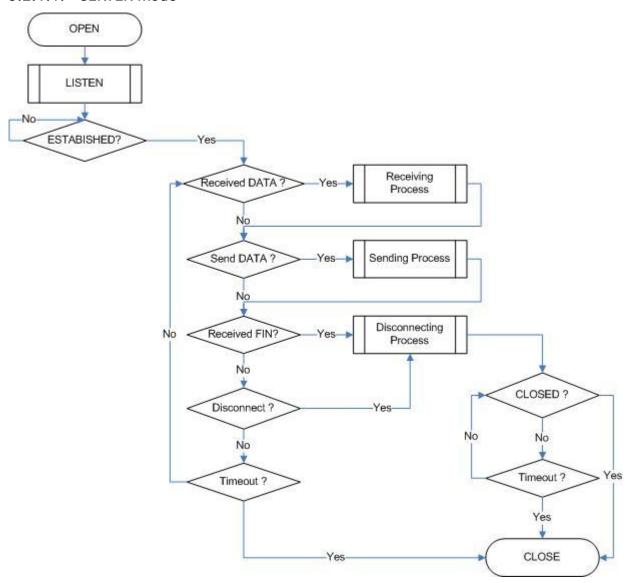

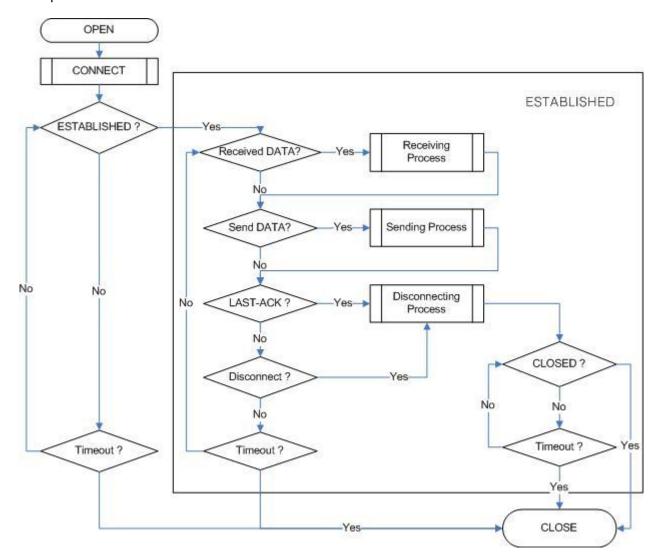

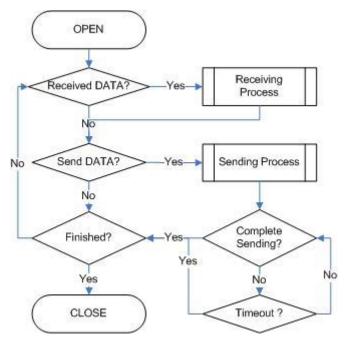

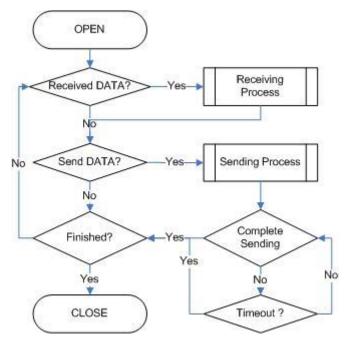

This register has the status vaule of socket n. The main status is shown in the below diagram.

Figure 4-1. State Diagram

| Value | Symbol           | Description                                                              |

|-------|------------------|--------------------------------------------------------------------------|

| 0x00  | SOCK_CLOSED      | It is shown in case that CLOSE commands are given to $Sn_{CR}$ , and     |

|       |                  | Timeout interrupt is asserted or connection is terminated.               |

| 0x13  | SOCK_INIT        | It is shown in case that Sn_MR is set as TCP and OPEN commands are       |

|       |                  | given to Sn_CR.                                                          |

| 0x14  | SOCK_LISTEN      | It is shown in case that LISTEN commands are given to Sn_CR at the       |

|       |                  | SOCK_INIT status                                                         |

| 0x17  | SOCK_ESTABLISHED | It is shown in case that connection is established.                      |

| 0x1C  | SOCK_CLOSE_WAIT  | It is shown in case that connection termination request is received from |

|       |                  | peer host.                                                               |

|       |                  |                                                                          |

| 0x22  | SOCK_UDP         | It is shown in case that OPEN commands are given to $Sn_CR$ when $Sn_MR$ |

|       |                  | is set as UDP.                                                           |

| 0x32  | SOCK_IPRAW       | It is shown in case that OPEN commands are given to Sn_CR when Sn_MR     |

|       |                  | is set as IPRAW.                                                         |

| 0x42  | SOCK_MACRAW      | It is shown in case that OPEN commands are given to SO_CR when SO_MR     |

|       |                  | is set as MACRAW.                                                        |

| 0x5F  | SOCK_PPPOE       | It is shown in case that OPEN commands are given to SO_CR when SO_MR     |

|       |                  | is set as PPPoE.                                                         |

### Below is shown during changing the status.

| Value | Symbol         | Description                                                                                           |  |  |  |

|-------|----------------|-------------------------------------------------------------------------------------------------------|--|--|--|

| 0x15  | SOCK_SYNSENT   | It is shown in case that CONNECT commands are given to Socket $n$                                     |  |  |  |

|       |                | Command Register(Sn_CR) at the SOCK_INIT status. It is automatically                                  |  |  |  |

|       |                | changed to SOCK_ESTABLISH when the connection is established.                                         |  |  |  |

| 0x16  | SOCK_SYNRECV   | It is shown in case that connection request is received from remote                                   |  |  |  |

|       |                | peer(CLIENT). It normally responds to the requests and changes to                                     |  |  |  |

|       |                | SOCK_ESTABLISH.                                                                                       |  |  |  |

| 0x18  | SOCK_FIN_WAIT  | It is shown in the process of connection termination. If the termination                              |  |  |  |

| 0x1A  | SOCK_CLOSING   | It is shown in the process of connection termination. If the terminati                                |  |  |  |

| 0X1B  | SOCK_TIME_WAIT | is normally processed or Timeout interrupt is asserted, it will automatically changed to SOCK_CLOSED. |  |  |  |

| 0X1D  | SOCK_LAST_ACK  | automatically changed to SOCK_CLOSED.                                                                 |  |  |  |

| 0x11  | SOCK_ARP       | It is shown when ARP Request is sent in order to acquire Hardware                                     |  |  |  |

| 0x21  |                | Address of remote peer when it sends connection request in TCP mode                                   |  |  |  |

| 0x31  |                | or sends data in UDP mode. If ARP Reply is received, it changes to the                                |  |  |  |

|       |                | status, SOCK_SYNSENT, SOCK_UDP or SOCK_ICMP, for the next operation.                                  |  |  |  |

## Sn\_PORT (Socket n Source Port Register) [R/W] [0x0404-0x0405, 0x0504-0x0505, 0x0604-0x0605, 0x0704-0x0705] [0x00]

This register sets the Source Port number for each Socket when using TCP or UDP mode, and the set-up needs to be made before executing the OPEN Command.

Ex) In case of Socket 0 Port = 5000(0x1388), configure as below,

| 0x0404 | 0x0405 |

|--------|--------|

| 0x13   | 0x88   |

## Sn\_DHAR (Socket n Destination Hardware Address Register) [R/W] [0x0406-0x040B, 0x0506-0x050B, 0x0606-0x060B, 0x0706-0x070B] [0xFF]

This register sets the Destination Hardware address of each Socket.

Ex) In case of Socket 0 Destination Hardware address = 08.DC.00.01.02.10, configuration is as below,

| 0x0406 | 0x0407 | 0x0408 | 0x0409 | 0x040A | 0x040B |

|--------|--------|--------|--------|--------|--------|

| 0x08   | 0xDC   | 0×00   | 0x01   | 0x02   | 0x0A   |

### Sn\_DIPR (Socket n Destination IP Address Register) [R/W] [0x040C-0x040F, 0x050C-0x050F, 0x060C-0x060F, 0x070C-0x070F] [0x00]

This register sets the Destination IP Address of each Socket to be used in setting the TCP connection. In active mode, IP address needs to be set before executing the Connect command. In passive mode, W3150A+ sets up the connection and then is internally updated with peer IP.

In UDP mode, this register value decided to user's written value after receiving peer's ARP response. Before receving peer's ARP response, this register has reset value.

Ex) In case of Socket 0 Destination IP address = 192.168.0.11, configure as below.

| 0x040C     | 0x040D     | 0x040E   | 0x040F    |

|------------|------------|----------|-----------|

| 192 (0xC0) | 168 (0xA8) | 0 (0x00) | 11 (0x0B) |

### Sn\_DPORT (Socket n Destination Port Register) [R/W] [0x0410-0x0411, 0x0510-0x0511, 0x0610-0x0611, 0x0710-0x0711] [0x00]

This register sets the Destination Port number of each socket to be used in setting the TCP connection. In active mode, port number needs to be set before executing the Connect command. In passive mode,

W3150A+ sets up the connection and then is internally updated with peer port number.

In UDP mode, this register value decided to user's written value after receiving peer's ARP response. Before receving peer's ARP response, this register has reset value.

Ex) In case of Socket 0 Destination Port = 5000(0x1388), configure as below,

| 0x0410 | 0x0411 |

|--------|--------|

| 0x13   | 0x88   |

## Sn\_MSS (Socket n Maximum Segment Size Register) [R/W] [0x0412-0x0413, 0x0512-0x0513, 0x0612-0x0613, 0x0712-0x0713] [0x0000]

This register is used for MSS (Maximum Segment Size) of a Packet.

According to communication mode, this register has different values.

- Ex) 1. In normal TCP mode, MSS = 1460(0x05B4)

- 2. In PPPoE-TCP mode, MSS = 1452(0x05AC)

- 3. In normal UDP mode, MSS = 1472(0x05C0)

- 4. In PPPoE-UDP mode, MSS = 1464(0x05B8)

Normal TCP mode configure as below,

| 0x0412 | 0x0413 |

|--------|--------|

| 0x05   | 0xB4   |

#### Sn\_PROTO (Socket n IP Protocol Register) [R/W] [0x0414, 0x0514, 0x0614, 0x0714] [0x00]

This IP Protocol Register is used to set up the Protocol Field of IP Header at the IP Layer RAW Mode. There are several protocol numbers defined in advance by registering to IANA. For the overall list of upper level protocol identification number that IP is using, refer to online documents of IANA (http://www.iana.org/assignments/protocol-numbers).

Ex) Internet Control Message Protocol (ICMP) = 0x01, Internet Group Management Protocol = 0x02

Sn\_TOS (Socket n IP Type Of Service Register) [R/W] [0x0415,0x0515,0x0615,0x0715] [0x00] This register sets up at the TOS Field of IP Header.

Sn\_TTL (Socket n IP Time To Live Register) [R/W] [0x0416,0x0516,0x0616,0x0716] [0x80]

This register sets up at the TTL Field of IP Header.

### Sn\_TX\_FSR (Socket n TX Free Size Register) [R] [0x0420-0x0421, 0x0520-0x0521, 0x0620-0x0621, 0x0720-0x0721] [0x0800]

This register notifies the information of data size that user can transmit. For data transmission, user should check this value first and control the size of transmitting data. When checking this register, user should upper byte(0x0420,0x0520,0x0620,0x0720) first and lower byte(0x0421,0x0521,0x0621,0x0721) later to get the correct value.

Ex) In case of 2048(0x0800) in S0\_TX\_FSR,

| 0x0420 | 0x0421 |

|--------|--------|

| 0x08   | 0x00   |

Total size can be decided according to the value of TX Memory Size Register. In the process of transmission, it will be reduced by the size of transmitting data, and automatically increased after transmission finished.

### Sn\_TX\_RR (Socket n TX Read Pointer Register) [R] [0x0422-0x0423, 0x0522-0x0523, 0x0622-0x0623, 0x0722-0x0723] [0x0000]

This register shows the address that transmission is finished at the TX Memory. With the SEND command of Socket n Command Register, it transmits data from current  $Sn_TX_RR$  to  $Sn_TX_WR$  and automatically changes after transmission is finished. Therefore, after transmission is finished, Sn\_TX\_RR and Sn\_TX\_WR will have same value. When reading this register, user should read upper byte (0x0422, 0x0522, 0x0622, 0x0722) first and lower byte (0x0423, 0x0523, 0x0623, 0x0723) later to get the correct value.

## Sn\_TX\_WR (Socket n TX Write Pointer Register) [R/W] [0x0424-0x0425, 0x0524-0x0525, 0x0624-0x0625, 0x0724-0x0725] [0x0000]

This register offers the location information to write the transmission data. When reading this register, user should read upper byte (0x0424, 0x0524, 0x0624, 0x0724) first and lower byte (0x0425, 0x0525, 0x0625, 0x0725) later to get the correct value.

Ex) In case of 2048(0x0800) in S0\_TX\_WR,

| 0x0424 | 0x0425 |

|--------|--------|

| 0x08   | 0x00   |

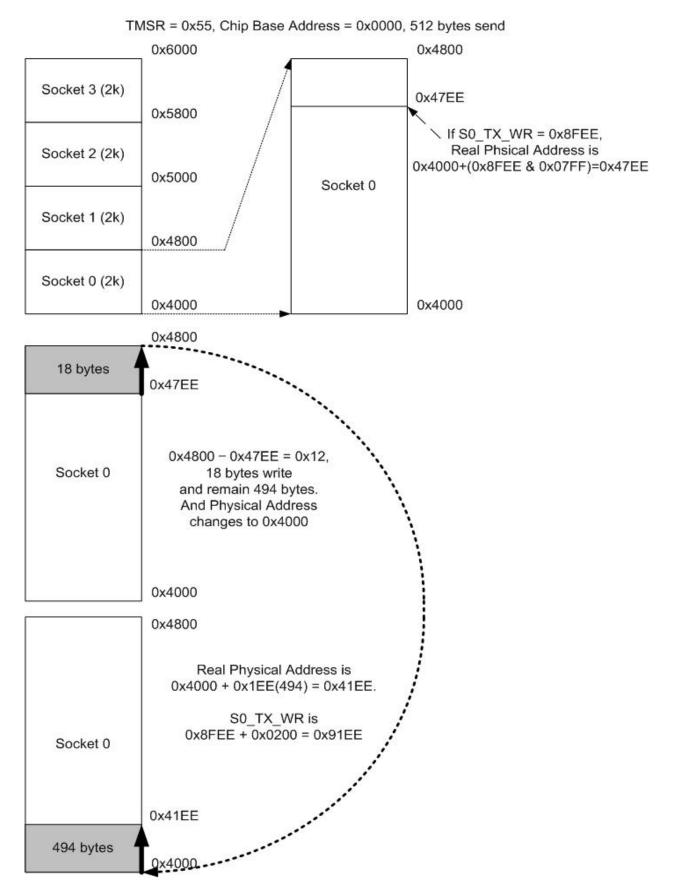

But this value itself is not the physical address to write. So, the physical address should be calculated as follow.