Contents SPEAR-09-P022

## **Contents**

| Referen | ce doc | umentation                         | 6          |  |  |  |  |  |  |

|---------|--------|------------------------------------|------------|--|--|--|--|--|--|

| 1       | Proc   | uct overview                       | 7          |  |  |  |  |  |  |

|         | 1.1    | Features                           | 7          |  |  |  |  |  |  |

|         | 1.2    | Architecture properties            | 8          |  |  |  |  |  |  |

|         | 1.3    | Block diagram                      | 9          |  |  |  |  |  |  |

| 2       | Pin (  | lescription1                       | 0          |  |  |  |  |  |  |

|         | 2.1    | Functional pin group               | 0          |  |  |  |  |  |  |

|         | 2.2    | Special IOs                        | :1         |  |  |  |  |  |  |

|         |        | 2.2.1 USB 2.0 transceiver          | 11         |  |  |  |  |  |  |

|         |        | 2.2.2 SSTL_2/SSTL_182              | 11         |  |  |  |  |  |  |

|         |        | 2.2.3 LVDS                         | 1:1        |  |  |  |  |  |  |

| 3       | Men    | ory map                            | 2          |  |  |  |  |  |  |

|         | 3.1    | Main memory map                    |            |  |  |  |  |  |  |

|         | 3.2    | ICM1 - low speed connection        | 2:2        |  |  |  |  |  |  |

|         | 3.3    | ICM2 - application subsystem       | :3         |  |  |  |  |  |  |

|         | 3.4    | ICM4 - high speed connection       | :3         |  |  |  |  |  |  |

|         | 3.5    | ML1, 2 - multi layer CPU subsystem | <u>'</u> 4 |  |  |  |  |  |  |

|         | 3.6    | ICM3 - basic subsystem             | :4         |  |  |  |  |  |  |

| 4       | Mair   | blocks 2                           | 5          |  |  |  |  |  |  |

|         | 4.1    | 7.1 CPU subsystem                  | :5         |  |  |  |  |  |  |

|         |        | 4.1.1 Overview                     | 25         |  |  |  |  |  |  |

|         |        | 4.1.2 CPU ARM 926EJ-S              | 25         |  |  |  |  |  |  |

|         | 4.2    | Clock and reset system             | :6         |  |  |  |  |  |  |

|         | 4.3    | Main oscillator 2                  | :6         |  |  |  |  |  |  |

|         |        | 4.3.1 Crystal connection           | 26         |  |  |  |  |  |  |

|         |        | 4.3.2 Crystal equivalent model     | 27         |  |  |  |  |  |  |

|         | 4.4    | RTC oscillator                     | .7         |  |  |  |  |  |  |

|         |        | 4.4.1 RTC crystal connection       | 27         |  |  |  |  |  |  |

|         |        | 4.4.2 RTC crystal equivalent model | 28         |  |  |  |  |  |  |

| 2/40    |        |                                    | 7          |  |  |  |  |  |  |

|   | 4.5    | Ethernet of | controller                             | 29 |

|---|--------|-------------|----------------------------------------|----|

|   | 4.6    | USB2 hos    | t controller                           | 29 |

|   | 4.7    | USB2 dev    | ice controller                         | 30 |

|   | 4.8    | Low jitter  | PLL                                    | 30 |

|   | 4.9    | Reconfigu   | rable logic array                      | 31 |

|   |        | 4.9.1 C     | verview                                | 31 |

|   |        | 4.9.2 C     | ustom project development              | 31 |

|   |        | 4.9.3 C     | sustomization process                  | 31 |

|   |        | 4.9.4 A     | DC controller                          | 32 |

|   | 4.10   | Other inte  | rfaces                                 | 32 |

|   |        | 4.10.1 U    | ART                                    | 32 |

|   |        | 4.10.2 S    | PI                                     | 32 |

| 5 | Electi | rical chara | acteristics                            | 33 |

|   | 5.1    | Absolute i  | naximum ratings                        | 33 |

|   | 5.2    | DC electri  | cal characteristics                    | 34 |

|   | 5.3    | General p   | urpose I/O characteristics             | 35 |

|   | 5.4    | LVDS elec   | ctrical characteristics                | 35 |

|   | 5.5    | DDR I & E   | DDR II pads electrical characteristics | 36 |

| 6 | Packa  | ige inforn  | nation                                 | 38 |

| 7 | Revis  | ion histo   | γ                                      | 39 |

List of tables SPEAR-09-P022

## List of tables

| Table 1.  | Device summary                                                                                  | 1  |

|-----------|-------------------------------------------------------------------------------------------------|----|

| Table 2.  | Pin description by functional group                                                             |    |

| Table 3.  | Power supply                                                                                    | 20 |

| Table 4.  | Main memory map                                                                                 | 22 |

| Table 5.  | ICM1 - low speed connection                                                                     | 22 |

| Table 6.  | ICM2 - application subsystem                                                                    | 23 |

| Table 7.  | ICM4 - high speed connection                                                                    | 23 |

| Table 8.  | ML1, 2 - multi layer CPU subsystem                                                              | 24 |

| Table 9.  | ICM3 - basic subsystem                                                                          | 24 |

| Table 10. | Main oscillator characteristics                                                                 | 27 |

| Table 11. | RTC oscillator characteristics                                                                  | 28 |

| Table 12. | Absolute maximum ratings                                                                        | 33 |

| Table 13. | DC electrical characteristics                                                                   | 34 |

| Table 14. | Low voltage TTL DC input specification (3V <vdde3v3<3.6v)< td=""><td> 35</td></vdde3v3<3.6v)<>  | 35 |

| Table 15. | Low voltage TTL DC output specification (3V <vdde3v3<3.6v)< td=""><td> 35</td></vdde3v3<3.6v)<> | 35 |

| Table 16. | Pull-up and pull-down characteristics                                                           |    |

| Table 17. | Driver specification                                                                            |    |

| Table 18. | AC output specification (2.2V <vdde2v5<2.7v)< td=""><td> 35</td></vdde2v5<2.7v)<>               | 35 |

| Table 19. | Receiver specification                                                                          |    |

| Table 20. | DC characteristics                                                                              |    |

| Table 21. | Driver characteristics                                                                          |    |

| Table 22. | On die termination                                                                              |    |

| Table 23. | Reference voltage                                                                               | 37 |

| Table 24  | Document revision history                                                                       | 30 |

SPEAR-09-P022 List of figures

# **List of figures**

| Figure 1. | Main SPEAr Plus600 functional interfaces       | 7    |

|-----------|------------------------------------------------|------|

| Figure 2. | Block diagram                                  | 9    |

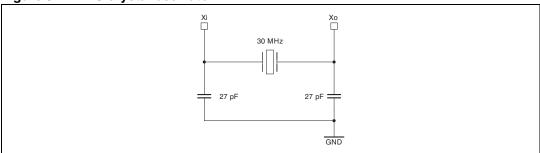

| Figure 3. | Crystal connection                             | . 26 |

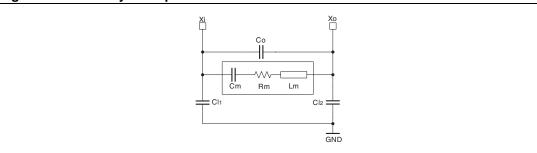

| Figure 4. | Crystal equivalent model                       | . 27 |

| Figure 5. | RTC crystal oscillator                         | . 27 |

| Figure 6. | RTC crystal equivalent model                   | . 28 |

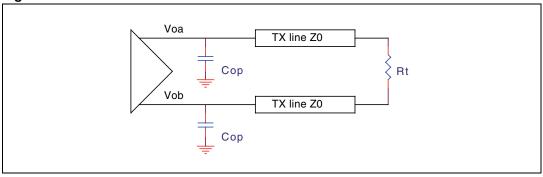

| Figure 7. | Test circuit                                   | . 36 |

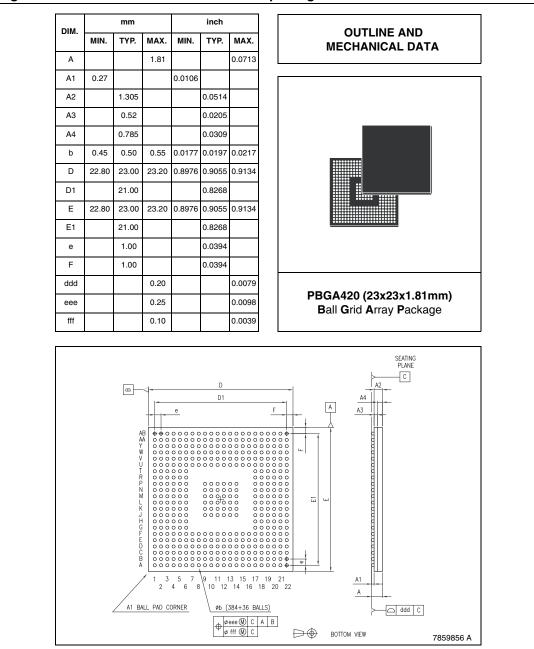

| Figure 8. | PBGA420 mechanical data and package dimensions | . 38 |

## **Reference documentation**

- 1. ARM926EJ-S technical reference manual

- 2. AMBA 2.0 specification

- 3. EIA/JESD8-9 specification

- 4. USB2.0 specification

- 5. OHCI specification

- 6. EHCI specification

- 7. USB specification

- 8. IEEE 802.3 specification

- 9. I<sup>2</sup>C bus specification

577

SPEAR-09-P022 Product overview

### 1 Product overview

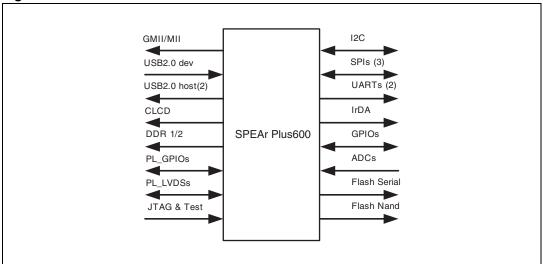

An outline picture of the main SPEAr Plus600 functional interfaces is shown in Figure 1.

Figure 1. Main SPEAr Plus600 functional interfaces

### 1.1 Features

The following main functionalities are implemented in the SPEAr Plus600 SoC device:

- Dual ARM926EJ-S core @333 MHz, 16 Kbyte-I/D cache, configurable TMC-I/D size, MMU, TLB, JTAG and ETM trace module (multiplexed interfaces)

- 600 Kbyte reconfigurable logic array (programmable through 4 Metal and 4 Vias)

- 128 Kbyte configurable internal memory pool (single and dual port memory)

- 32 Kbyte ROM (code customizable) 8 Kbyte common SRAM

- Dynamic power save features

- High performance linked list 8 channels DMA

- Ethernet GMII/MII (IEEE802.3/3x/1Q), management i/f

- USB2.0 device (high-full speed), integrated PHY transceiver

- 2-USB2.0 host (high-full-low speed), integrated PHY transceiver

- Ext. memory i/f: 8/16-bit DDR1@200 MHz/DDR2@333 MHz

- Flash interface: nand 8/16-bit and serial (up to 50 Mbps)

- 3-SPI master/slave (motorola-texas-national) up to 40 Mbps

- I<sup>2</sup>C (high-fast-slow speed) master/slave

- 2-UART (speed rate up to 460.8 Kbps)

- IrDA (Fir-Mir-Sir) from 9.6 Kbps to 4 Mbps speed-rate

- Color LCD up to 1024x768 resolutions, 24 bpp true colour, STN/TFT display panel

- 10 GPIOs bidirectional signals with interrupt capability

- 9 LVDS (8 out and 1 input) signals, customizable interface through programmable logic

- 88 RAS-GPIOs user customizable bidirectional signals (up to 4 clocks)

**577**

Product overview SPEAR-09-P022

- ADC (1 µs/1MSPS) 8 analog input channel, 10-bit approximation

- JPEG codec accelerator 1clock/pixel

- 10 independent timers with programmable prescaler

- RTC WDOG SYSCTR MISC internal control registers

- JTAG (IEEE1149.1) interface

### 1.2 Architecture properties

- Dual symmetric processor architecture:

- All internal peripherals are shared, allowing flexible and efficient SW partitions

- High throughput can be sustained in aggregate way splitting critical tasks either onto additional CPUs and optional HW accelerators engines

- Critical resources are private to each CPU (interrupt controller and OS timers)

- Both processors are equipped with ICE and ETM configurable debug interfaces

- Power save features:

- Operating frequency SW programmable

- Clock gating functionality

- Low frequency operating mode

- Automatic power saving controlled from application activity demands

- Customizable logic to embed the customer real 'core competence':

- 600Kgate standard cell array

- Internal memory pool (128 Kbyte) full configurable

- Up to 16 external/internal source clock (some of these programmable)

- Three memory path toward the SDRAM controller to ensure a good bandwidth

- Architecture easily extensible

- External memory bandwidth of each master tuneable to meet the target performances of different applications

SPEAR-09-P022 Product overview

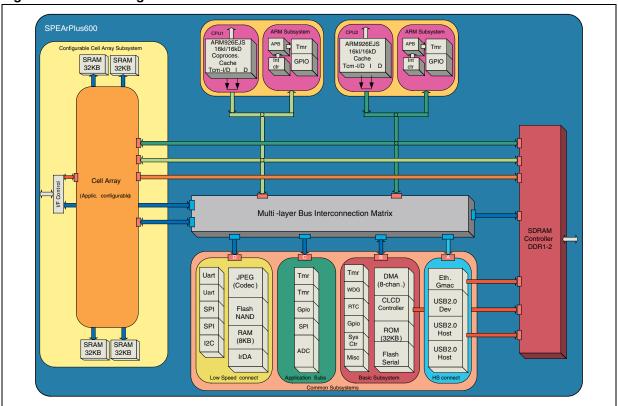

## 1.3 Block diagram

Figure 2. Block diagram

**577**

Pin description SPEAR-09-P022

## 2 Pin description

## 2.1 Functional pin group

With reference to figure package schematic in *Section 6*, here follows the pin list, sorted by their belonging IP. All supply and ground pins are classified as power signals and gathered in the *Table 3*.

Table 2. Pin description by functional group

| Group | Signal name | Ball | Direction | Function                                                                   | Pin type                                                      |

|-------|-------------|------|-----------|----------------------------------------------------------------------------|---------------------------------------------------------------|

|       | AIN_0       | W11  |           |                                                                            |                                                               |

|       | AIN_1       | V11  |           |                                                                            |                                                               |

|       | AIN_2       | V12  |           |                                                                            |                                                               |

|       | AIN_3       | W12  |           | ADC analog input                                                           |                                                               |

|       | AIN_4       | W13  |           | channel                                                                    |                                                               |

| ADC   | AIN_5       | V13  | Input     |                                                                            | Analog buffer<br>2.5 V tolerant                               |

|       | AIN_6       | V14  |           |                                                                            | 2.5 V tolerant                                                |

|       | AIN_7       | W14  |           |                                                                            |                                                               |

|       | ADC_VREFN   | W15  |           | ADC negative voltage reference                                             |                                                               |

|       | ADC_VREFP   | V15  |           | ADC positive voltage reference                                             |                                                               |

|       | TEST_0      | E15  |           | Test configuration ports. For functional mode they have to be set to zero. | TTL input buffer,<br>3.3 V tolerant, PD                       |

|       | TEST_1      | E14  | Input     |                                                                            |                                                               |

|       | TEST_2      | D14  |           |                                                                            |                                                               |

|       | TEST_3      | D13  |           |                                                                            |                                                               |

|       | TEST_4      | E13  |           |                                                                            |                                                               |

|       | TEST_5      | D12  |           |                                                                            |                                                               |

| DEBUG | nTRST       | D17  | Input     | Test reset input                                                           | TTL Schmitt trigger input buffer, 3.3 V tolerant, PU          |

|       | TDO         | E17  | Output    | Test data output                                                           | TTL output buffer,<br>3.3 V capable,4 mA                      |

|       | TCK         | E16  | Input     | Test clock                                                                 | TTL Schmitt trigger input buffer, 3.3 V tolerant, PU          |

|       | TDI         | D16  | Input     | Test data input                                                            |                                                               |

|       | TMS         | D15  | Input     | Test mode select                                                           |                                                               |

| PL    | PL_GPIO_0   | P4   | I/O       | Programmable logic I/O                                                     | TTL BIDIR buffer,<br>3.3 V capable, 4mA<br>3.3 V tolerant, PU |

SPEAR-09-P022 Pin description

Table 2. Pin description by functional group (continued)

| Group | Signal name | Ball | Direction | Function               | Pin type                                                       |

|-------|-------------|------|-----------|------------------------|----------------------------------------------------------------|

|       | PL_GPIO_1   | N4   |           |                        |                                                                |

|       | PL_GPIO_2   | N5   |           |                        |                                                                |

|       | PL_GPIO_3   | N6   |           |                        |                                                                |

|       | PL_GPIO_4   | M5   |           |                        |                                                                |

|       | PL_GPIO_5   | M4   |           |                        |                                                                |

|       | PL_GPIO_6   | МЗ   |           |                        |                                                                |

|       | PL_GPIO_7   | M2   |           |                        |                                                                |

|       | PL_GPIO_8   | M1   |           |                        |                                                                |

|       | PL_GPIO_9   | L1   |           |                        |                                                                |

|       | PL_GPIO_10  | L2   |           |                        |                                                                |

|       | PL_GPIO_11  | L3   |           |                        |                                                                |

|       | PL_GPIO_12  | L4   |           |                        | TTL BIDIR buffer,<br>3.3 V capable, 4 mA<br>3.3 V tolerant, PU |

|       | PL_GPIO_13  | L5   |           | Programmable logic I/O |                                                                |

|       | PL_GPIO_14  | K6   |           |                        |                                                                |

|       | PL_GPIO_15  | K5   |           |                        |                                                                |

|       | PL_GPIO_16  | K4   |           |                        |                                                                |

|       | PL_GPIO_17  | K3   |           |                        |                                                                |

| PL    | PL_GPIO_18  | K2   | I/O       |                        |                                                                |

|       | PL_GPIO_19  | K1   |           |                        |                                                                |

|       | PL_GPIO_20  | J1   |           |                        |                                                                |

|       | PL_GPIO_21  | J2   |           |                        |                                                                |

|       | PL_GPIO_22  | J3   |           |                        |                                                                |

|       | PL_GPIO_23  | J4   |           |                        |                                                                |

|       | PL_GPIO_24  | J5   |           |                        |                                                                |

|       | PL_GPIO_25  | H5   |           |                        |                                                                |

|       | PL_GPIO_26  | H4   |           |                        |                                                                |

|       | PL_GPIO_27  | НЗ   |           |                        |                                                                |

|       | PL_GPIO_28  | H2   |           |                        |                                                                |

|       | PL_GPIO_29  | H1   |           |                        |                                                                |

|       | PL_GPIO_30  | G1   |           |                        |                                                                |

|       | PL_GPIO_31  | G2   |           |                        |                                                                |

|       | PL_GPIO_32  | G3   |           |                        |                                                                |

|       | PL_GPIO_33  | G4   |           |                        |                                                                |

|       | PL_GPIO_34  | G5   |           |                        |                                                                |

|       | PL_GPIO_35  | F5   |           |                        |                                                                |

Pin description SPEAR-09-P022

Table 2. Pin description by functional group (continued)

| Group | Signal name | Ball | Direction | Function               | Pin type                                                       |

|-------|-------------|------|-----------|------------------------|----------------------------------------------------------------|

|       | PL_GPIO_36  | F4   |           |                        |                                                                |

|       | PL_GPIO_37  | F3   |           |                        |                                                                |

|       | PL_GPIO_38  | F2   |           |                        |                                                                |

|       | PL_GPIO_39  | F1   |           |                        |                                                                |

|       | PL_GPIO_40  | E4   |           |                        |                                                                |

|       | PL_GPIO_41  | E3   |           |                        |                                                                |

|       | PL_GPIO_42  | E2   |           |                        |                                                                |

|       | PL_GPIO_43  | E1   |           |                        |                                                                |

|       | PL_GPIO_44  | D3   |           |                        |                                                                |

|       | PL_GPIO_45  | D2   |           |                        |                                                                |

|       | PL_GPIO_46  | D1   |           |                        | TTL BIDIR buffer,<br>3.3 V capable, 4 mA<br>3.3 V tolerant, PU |

|       | PL_GPIO_47  | C2   |           | Programmable logic I/O |                                                                |

|       | PL_GPIO_48  | C1   |           |                        |                                                                |

|       | PL_GPIO_49  | B1   |           |                        |                                                                |

|       | PL_GPIO_50  | A1   |           |                        |                                                                |

|       | PL_GPIO_51  | B2   |           |                        |                                                                |

|       | PL_GPIO_52  | A2   |           |                        |                                                                |

| PL    | PL_GPIO_53  | C3   | I/O       |                        |                                                                |

|       | PL_GPIO_54  | В3   |           |                        |                                                                |

|       | PL_GPIO_55  | A3   |           |                        |                                                                |

|       | PL_GPIO_56  | B4   |           |                        |                                                                |

|       | PL_GPIO_57  | C4   |           |                        |                                                                |

|       | PL_GPIO_58  | D4   |           |                        |                                                                |

|       | PL_GPIO_59  | E5   |           |                        |                                                                |

|       | PL_GPIO_60  | D5   |           |                        |                                                                |

|       | PL_GPIO_61  | C5   |           |                        |                                                                |

|       | PL_GPIO_62  | B5   |           |                        |                                                                |

|       | PL_GPIO_63  | B6   |           |                        |                                                                |

|       | PL_GPIO_64  | C6   |           |                        |                                                                |

|       | PL_GPIO_65  | D6   |           |                        |                                                                |

|       | PL_GPIO_66  | E6   |           |                        |                                                                |

|       | PL_GPIO_67  | F6   |           |                        |                                                                |

|       | PL_GPIO_68  | F7   |           |                        |                                                                |

|       | PL_GPIO_69  | E7   |           |                        |                                                                |

|       | PL_GPIO_70  | D7   |           |                        |                                                                |

SPEAR-09-P022 Pin description

Table 2. Pin description by functional group (continued)

| Group    | Signal name   | Ball       | Direction | Function                          | Pin type                                                       |

|----------|---------------|------------|-----------|-----------------------------------|----------------------------------------------------------------|

|          | PL_GPIO_71    | C7         |           |                                   |                                                                |

|          | PL_GPIO_72    | В7         |           |                                   |                                                                |

|          | PL_GPIO_73    | E8         |           |                                   |                                                                |

|          | PL_GPIO_74    | D8         |           |                                   |                                                                |

|          | PL_GPIO_75    | C8         |           |                                   |                                                                |

|          | PL_GPIO_76    | B8         |           |                                   | TTL output buffer                                              |

|          | PL_GPIO_77    | A8         |           | Programmable logic I/O            | 3.3 V capable, 4 mA TTL input buffer                           |

|          | PL_GPIO_78    | C9         |           |                                   | 3.3 V tolerant, PU                                             |

| PL       | PL_GPIO_79    | D9         | I/O       |                                   |                                                                |

|          | PL_GPIO_80    | E9         |           |                                   |                                                                |

|          | PL_GPIO_81    | E10        |           |                                   |                                                                |

|          | PL_GPIO_82    | D10        |           |                                   |                                                                |

|          | PL_GPIO_83    | C10        |           |                                   |                                                                |

|          | PL_CLK_1      | A7         |           | Programmable Logic external clock | TTL BIDIR buffer,<br>3.3 V capable, 8 mA<br>3.3 V tolerant, PU |

|          | PL_CLK_2      | A6         |           |                                   |                                                                |

|          | PL_CLK_3      | <b>A</b> 5 |           |                                   |                                                                |

|          | PL_CLK_4      | A4         |           |                                   |                                                                |

|          | GMII_TXCLK    | F22        | Output    | Transmit clock (GMII)             | TTL output buffer 3.3 V capable, 8 mA                          |

|          | GMII_TXCLK125 | E22        | Input     | Ext. clock                        | TTL input buffer, 3.3 V                                        |

|          | MII_TXCLK     | D22        | mput      | Transmit Clock MII                | tolerant, PD                                                   |

|          | TXD_0         | F21        |           | - Transmit data                   |                                                                |

|          | TXD_1         | E21        | Output    |                                   | TTL output buffer                                              |

|          | TXD_2         | F20        | Output    |                                   | 3.3 V capable, 8 mA                                            |

|          | TXD_3         | E20        |           |                                   |                                                                |

|          | GMII_TXD_4    | D21        |           | Transmit data                     |                                                                |

| Ethernet | GMII_TXD_5    | D20        | I/O       |                                   | TTL BIDIR buffer<br>3.3 V capable, 8 mA                        |

|          | GMII_TXD_6    | C22        | 1/0       |                                   | 3.3 V tolerant, PD                                             |

|          | GMII_TXD_7    | C21        |           |                                   |                                                                |

|          | TX_ER         | D18        | Output    | Transmit error                    | TTL output buffer                                              |

|          | TX_EN         | D19        | Output    | Transmit enable                   | 3.3 V capable, 8 mA                                            |

|          | RX_ER         | C20        |           | Receive error                     |                                                                |

|          | RX_DV         | C19        | Input     | Receive data valid                | TTL input buffer                                               |

|          | RX_CLK        | A22        | при       | Receive clock                     | 3.3 V tolerant, PD                                             |

|          | RXD_0         | B22        |           | Receive data                      |                                                                |

Pin description SPEAR-09-P022

Table 2. Pin description by functional group (continued)

| Group    | Signal name | Ball | Direction | Function              | Pin type                                                      |

|----------|-------------|------|-----------|-----------------------|---------------------------------------------------------------|

|          | RXD_1       | B21  |           |                       | TTL input buffer<br>3.3 V tolerant, PD                        |

|          | RXD_2       | A21  | Input     |                       |                                                               |

|          | RXD_3       | B20  |           |                       |                                                               |

|          | GMII_RXD_4  | A20  |           | Receive data          |                                                               |

|          | GMII_RXD_5  | B19  | I/O       |                       | TTL BIDIR buffer<br>3.3 V capable, 8 mA                       |

|          | GMII_RXD_6  | A18  | 1/0       |                       | 3.3 V tolerant, PD                                            |

| Ethernet | GMII_RXD_7  | A19  |           |                       |                                                               |

|          | COL         | A17  | Input     | Collision detect      | TTL input buffer                                              |

|          | CRS         | B17  | mput      | Carrier sense         | 3.3 V tolerant, PD                                            |

|          | MDIO        | B18  | I/O       | Management data I/O   | TTL BIDIR buffer 3.3 V capable, 4 mA 3.3 V tolerant, PD       |

|          | MDC         | C18  | Output    | Management data clock | TTL output buffer 3.3 V capable, 8 mA                         |

|          | GPIO_0      | W18  |           | General purpose I/O   | TTL BIDIR buffer<br>3.3 V capable, 8 mA<br>3.3 V tolerant, PU |

|          | GPIO_1      | V18  | I/O       |                       |                                                               |

|          | GPIO_2      | U18  |           |                       |                                                               |

|          | GPIO_3      | T18  |           |                       |                                                               |

| GPIO     | GPIO_4      | W19  |           |                       |                                                               |

| di io    | GPIO_5      | V19  |           |                       |                                                               |

|          | GPIO_6      | U19  |           |                       |                                                               |

|          | GPIO_7      | T19  |           |                       |                                                               |

|          | GPIO_8      | R19  |           |                       |                                                               |

|          | GPIO_9      | R18  |           |                       |                                                               |

|          | CLD_0       | Y20  |           |                       | TT                                                            |

|          | CLD_1       | Y21  |           |                       | TTL output buffer 3.3 V capable, 8 mA                         |

|          | CLD_2       | Y22  |           |                       | olo v dapablo, o liliv                                        |

|          | CLD_3       | W22  |           |                       |                                                               |

|          | CLD_4       | W21  |           |                       |                                                               |

| LCD I/F  | CLD_5       | W20  | Output    | LCD data              |                                                               |

|          | CLD_6       | V20  |           |                       | TTL output buffer                                             |

|          | CLD_7       | V21  |           |                       | 3.3 V capable, 8 mA                                           |

|          | CLD_8       | V22  |           |                       |                                                               |

|          | CLD_9       | U22  |           |                       |                                                               |

|          | CLD_10      | U21  |           |                       |                                                               |

SPEAR-09-P022 Pin description

Table 2. Pin description by functional group (continued)

| Group   | Signal name | Ball | Direction | Function                              | Pin type                              |

|---------|-------------|------|-----------|---------------------------------------|---------------------------------------|

|         | CLD_11      | U20  |           |                                       |                                       |

|         | CLD_12      | T20  |           |                                       |                                       |

|         | CLD_13      | T21  |           |                                       |                                       |

|         | CLD_14      | R21  |           |                                       |                                       |

|         | CLD_15      | R20  |           |                                       |                                       |

|         | CLD_16      | P19  |           |                                       |                                       |

|         | CLD_17      | P20  |           | LCD data                              |                                       |

|         | CLD_18      | P21  |           |                                       |                                       |

|         | CLD_19      | N21  |           |                                       |                                       |

|         | CLD_20      | N20  |           |                                       |                                       |

| LCD I/F | CLD_21      | N19  |           |                                       | TTL output buffer 3.3 V capable, 8 mA |

|         | CLD_22      | M20  |           |                                       | 5.5 v capable, o ma                   |

|         | CLD_23      | M21  |           |                                       |                                       |

|         | CLAC        | T22  |           | STN AC bias drive<br>TFT data enable  |                                       |

|         | CLCP        | R22  | Output    | LCD panel clock                       |                                       |

|         | CLFP        | P22  |           | STN frame pulse TFT vertical sync     |                                       |

|         | CLLP        | N22  |           | STN line pulse<br>TFT horizontal sync |                                       |

|         | CLLE        | M22  |           | Line end                              |                                       |

|         | CLPOWER     | M19  |           | LCD power enable                      |                                       |

|         | DDR_ADD_0   | AB3  |           |                                       |                                       |

|         | DDR_ADD_1   | AB4  |           |                                       |                                       |

|         | DDR_ADD_2   | AA4  |           |                                       |                                       |

|         | DDR_ADD_3   | Y4   |           |                                       |                                       |

|         | DDR_ADD_4   | W4   |           |                                       |                                       |

|         | DDR_ADD_5   | W5   |           |                                       |                                       |

| DDR I/F | DDR_ADD_6   | Y5   |           | Address line                          | CCTI 2/CCTI 10                        |

| ו אטט   | DDR_ADD_7   | AA5  |           | Address line                          | SSTL_2/SSTL_18                        |

|         | DDR_ADD_8   | AB5  |           |                                       |                                       |

|         | DDR_ADD_9   | AB6  |           |                                       |                                       |

|         | DDR_ADD_10  | AA6  |           |                                       |                                       |

|         | DDR_ADD_11  | Y6   |           |                                       |                                       |

|         | DDR_ADD_12  | W6   |           |                                       |                                       |

|         | DDR_ADD_13  | W7   |           |                                       |                                       |

Pin description SPEAR-09-P022

Table 2. Pin description by functional group (continued)

| Group   | Signal name | Ball | Direction | Function                   | Pin type                       |

|---------|-------------|------|-----------|----------------------------|--------------------------------|

|         | DDR_ADD_14  | Y7   |           | Address line               |                                |

|         | DDR_BA_0    | Y9   |           | Bank select                |                                |

|         | DDR_BA_1    | W9   |           | Bank select                |                                |

|         | DDR_BA_2    | W10  |           | Bank select                | SSTL_2/SSTL_18                 |

|         | DDR_RAS     | AB7  |           | Row strobe                 | - 331L_2/331L_16               |

|         | DDR_CAS     | AA7  |           | Column strobe              |                                |

|         | DDR_WE      | AA8  |           | Write enable               |                                |

|         | DDR_CLKEN   | AB8  | Output    | Clock enable               |                                |

|         | DDR_CLK_P   | AA9  |           | Differential clock         | Differential<br>SSTL_2/SSTL_18 |

|         | DDR_CLK_N   | AB9  |           |                            |                                |

|         | DDR_CS_0    | Y8   |           | Chip select                | SSTL_2/SSTL_18                 |

|         | DDR_CS_1    | W8   |           | Chip select                |                                |

|         | DDR_ODT_0   | AB2  |           | On-die termination         |                                |

|         | DDR_ODT_1   | AB1  |           | enable lines               |                                |

|         | DDR_DATA_0  | AB11 |           | Data lines<br>(lower byte) |                                |

| DDR I/F | DDR_DATA_1  | AA10 |           |                            | 0071 0/0071 40                 |

|         | DDR_DATA_2  | AB10 |           |                            | SSTL_2/SSTL_18                 |

|         | DDR_DATA_3  | Y10  | I/O       |                            |                                |

|         | DDR_DATA_4  | Y11  |           |                            |                                |

|         | DDR_DATA_5  | Y12  |           |                            |                                |

|         | DDR_DATA_6  | AB12 |           |                            |                                |

|         | DDR_DATA_7  | AA12 |           |                            |                                |

|         | DDR_DQS_0   | AB13 |           | Differential lower         | Differential                   |

|         | DDR_nDQS_0  | AA13 |           | data strobe                | SSTL_2/SSTL_18                 |

|         | DDR_DM_0    | AA11 | Output    | Lower data mask            |                                |

|         | DDR_GATE_0  | Y13  |           | Lower gate open            |                                |

|         | DDR_DATA_8  | AB15 |           |                            |                                |

|         | DDR_DATA_9  | AA16 |           |                            |                                |

|         | DDR_DATA_10 | AB16 | I/O       | Data lines                 | SSTL_2/SSTL_18                 |

|         | DDR_DATA_11 | Y16  | ","       | (upper byte)               |                                |

|         | DDR_DATA_12 | Y15  |           |                            |                                |

|         | DDR_DATA_13 | Y14  |           |                            |                                |

|         | DDR_DATA_14 | AB14 |           |                            |                                |

SPEAR-09-P022 Pin description

Table 2. Pin description by functional group (continued)

| Group   | Signal name  | Ball | Direction | Function                         | Pin type                               |

|---------|--------------|------|-----------|----------------------------------|----------------------------------------|

|         | DDR_DATA_15  | AA14 | 1/0       | Data lines<br>(upper byte)       | SSTL_2/SSTL_18                         |

|         | DDR_DQS_1    | AB17 | I/O       | Differential upper               | Differential                           |

|         | DDR_nDQS_1   | AA17 |           | data strobe                      | SSTL_2/SSTL_18                         |

|         | DDR_DM_1     | AA15 | Output    | Upper data mask                  | SSTL 2/SSTL 18                         |

|         | DDR_GATE_1   | Y17  | I/O       | Upper gate open                  | 331L_2/331L_10                         |

| DDR I/F | DDR_VREF     | V10  | Input     | Reference voltage                | Analog                                 |

|         | DDR_COMP_2V5 | V9   | Output    | Ext. resistor 2.5 V              | Analog                                 |

|         | DDR_COMP_GND | V8   | -         | Common return for ext. resistors | Power                                  |

|         | DDR_COMP_1V8 | V7   | Output    | Ext. resistor 1.8 V              | Analog                                 |

|         | DDR2_EN      | D11  | input     | Configuration                    | TTL input buffer 3.3 V tolerant, PU    |

|         | DEV_DP       | V1   |           | USB device D+                    | Bidirectional analog                   |

|         | DEV_DM       | V2   | I/O       | USB device D-                    | buffer<br>5 V tolerant                 |

|         | DEV_VBUS     | R4   | Input     | USB device VBUS                  | TTL input buffer 3.3 V tolerant, PD    |

|         | HOST1_DP     | T1   |           | USB HOST1 D+                     | Bidirectional analog                   |

|         | HOST1_DM     | T2   | I/O       | USB HOST1 D-                     | buffer<br>5 V tolerant                 |

|         | HOST1_VBUS   | P5   | Output    | USB HOST1 VBUS                   | TTL output buffer 3.3 V capable, 4 mA  |

| USB     | HOST1_OVRC   | P6   | Input     | USB host1<br>over-current        | TTL input buffer<br>3.3 V tolerant, PD |

|         | HOST2_DP     | P1   | I/O       | USB HOST2 D+                     | Bidirectional analog                   |

|         | HOST2_DM     | P2   |           | USB HOST2 D-                     | buffer<br>5 V tolerant                 |

|         | HOST2_VBUS   | R5   | Output    | USB HOST2 VBUS                   | TTL output buffer 3.3 V capable, 4 mA  |

|         | HOST2_OVRC   | R6   | Input     | USB host2<br>over-current        | TTL input buffer 3.3 V tolerant, PD    |

|         | USB_RREF     | U4   | Output    | Reference resistor               | Analog                                 |

| Master  | MCLK_XI      | Y1   | Input     | 30 MHz crystal I                 | Oscillator                             |

| Clock   | MCLK_XO      | Y2   | Output    | 30 MHz crystal O                 | 2.5 V capable                          |

| RTC     | RTC_XI       | A9   | Input     | 32KHz crystal I                  | Oppillator 1 V acrabla                 |

| RIC     | RTC_XO       | В9   | Output    | 32 KHz crystal O                 | Oscillator 1 V capable                 |

| SMI     | SMI_DATAIN   | L21  | Input     | Serial Flash<br>input data       | TTL input buffer<br>3.3 V tolerant, PU |

Pin description SPEAR-09-P022

Table 2. Pin description by functional group (continued)

| Group                | Signal name | Ball | Direction | Function                 | Pin type                                                      |

|----------------------|-------------|------|-----------|--------------------------|---------------------------------------------------------------|

|                      | SMI_DATAOUT | L20  |           | Serial Flash output data |                                                               |

| SMI                  | SMI_CLK     | L22  | Output    | Serial Flash clock       | TTL output buffer  3.3 V capable, 4 mA                        |

|                      | SMI_CS_0    | L19  |           | Serial Flash             | 3.3 v capable, 4 ma                                           |

|                      | SMI_CS_1    | L18  |           | chip selects             |                                                               |

|                      | SSP_1_MOSI  | AA21 | I/O       | Master out slave in      |                                                               |

|                      | SSP_1_MISO  | AB21 | I/O       | Master in slave out      |                                                               |

|                      | SSP_1_SCLK  | AB22 | I/O       | Serial clock             |                                                               |

|                      | SSP_1_SS    | AA22 | I/O       | Slave select             |                                                               |

|                      | SSP_2_MOSI  | K20  | I/O       | Master out slave in      |                                                               |

| SPI                  | SSP_2_MISO  | K21  | I/O       | Master in slave out      | TTL BIDIR buffer<br>3.3 V capable, 8 mA                       |

|                      | SSP_2_SCLK  | K22  | I/O       | Serial clock             | 3.3 V tolerant, PU                                            |

|                      | SSP_2_SS_0  | K19  | I/O       | Slave select             |                                                               |

|                      | SSP_2_SS_1  | K18  | I/O       | Slave select             |                                                               |

|                      | SSP_3_MOSI  | J20  | I/O       | Master out slave in      |                                                               |

|                      | SSP_3_MISO  | J21  | I/O       | Master in slave out      |                                                               |

|                      | SSP_3_SCLK  | J22  | I/O       | Serial clock             |                                                               |

|                      | SSP_3_SS    | J19  | I/O       | Slave select             |                                                               |

|                      | UART1_TXD   | AA19 | Output    | - Serial data out        | TTL output buffer                                             |

| UART                 | UART2_TXD   | AA20 | Output    | - Seriai data odi        | 3.3 V capable, 4 mA                                           |

| OAITI                | UART1_RXD   | AB19 | Input     | - Serial data In         | TTL input buffer                                              |

|                      | UART2_RXD   | AB20 | Input     | - Serial data III        | 3.3 V tolerant, PD                                            |

| FIRDA                | FIRDA_TXD   | AA18 | Output    | Serial data out          | TTL output buffer 3.3 V capable, 4 mA                         |

| FINDA                | FIRDA_RXD   | AB18 | Input     | Serial data in           | TTL input buffer 3.3 V tolerant, PU                           |

|                      | SDA         | Y18  | I/O       | Serial data in/out       | TTL BIDIR buffer                                              |

| I <sup>2</sup> C     | SCL         | Y19  | I/O       | Serial clock             | 3.3 V capable, 4 mA<br>3.3 V tolerant, PU                     |

| NAND<br>FLASH<br>I/F | NF_IO_0     | H19  | I/O       | Data                     | TTL BIDIR buffer<br>3.3 V capable, 4 mA<br>3.3 V tolerant, PU |

SPEAR-09-P022 Pin description

Table 2. Pin description by functional group (continued)

| Group       | Signal name | Ball | Direction | Function                                  | Pin type                                             |  |

|-------------|-------------|------|-----------|-------------------------------------------|------------------------------------------------------|--|

|             | NF_IO_1     | H18  |           |                                           | TTL BIDIR buffer                                     |  |

|             | NF_IO_2     | G19  |           |                                           |                                                      |  |

|             | NF_IO_3     | G18  |           |                                           |                                                      |  |

|             | NF_IO_4     | F19  | I/O       | Data                                      | 3.3 V capable, 4 mA                                  |  |

|             | NF_IO_5     | F18  |           |                                           | 3.3 V tolerant, PU                                   |  |

| NAND        | NF_IO_6     | E18  |           |                                           |                                                      |  |

|             | NF_IO_7     | E19  |           |                                           |                                                      |  |

| FLASH       | NF_CE       | G20  |           | Chip enable                               |                                                      |  |

| I/F         | NF_RE       | G22  |           | Read enable                               |                                                      |  |

|             | NF_WE       | H20  | Output    | Write enable                              | TTL output buffer                                    |  |

|             | NF_ALE      | H21  | Output    | Address latch enable                      | 3.3 V capable, 4 mA                                  |  |

|             | NF_CLE      | G21  |           | Command latch enable                      |                                                      |  |

|             | NF_WP       | J18  |           | Write protect                             |                                                      |  |

|             | NF_RB       | H22  | Input     | Read/busy                                 | TTL input buffer 3.3 V tolerant PU                   |  |

|             | MRESET      | C17  | Input     | Main reset                                | TTL Schmitt trigger input buffer, 3.3 V tolerant, PU |  |

|             | PH0         | A16  |           |                                           |                                                      |  |

|             | PH0n        | B16  |           |                                           |                                                      |  |

|             | PH1         | C16  |           |                                           |                                                      |  |

|             | PH1n        | C15  |           |                                           |                                                      |  |

|             | PH2         | A15  |           |                                           |                                                      |  |

|             | PH2n        | B15  |           |                                           |                                                      |  |

|             | PH3         | A14  |           |                                           |                                                      |  |

| LVDO        | PH3n        | B14  | Output    |                                           | LVDS driver                                          |  |

| LVDS<br>I/F | PH4         | C14  | Output    | General purpose I/O with LVDS transceiver | LVD3 driver                                          |  |

|             | PH4n        | C13  |           |                                           |                                                      |  |

|             | PH5         | A13  |           |                                           |                                                      |  |

|             | PH5n        | B13  |           |                                           |                                                      |  |

|             | PH6         | A12  |           |                                           |                                                      |  |

|             | PH6n        | B12  |           |                                           |                                                      |  |

|             | PH7         | C12  |           |                                           |                                                      |  |

|             | PH7n        | C11  |           |                                           |                                                      |  |

|             | PH8         | A11  | Input     |                                           | LVDS receiver                                        |  |

Pin description SPEAR-09-P022

Table 2. Pin description by functional group (continued)

| Group       | Signal name  | Ball | Direction | Function                                  | Pin type                |

|-------------|--------------|------|-----------|-------------------------------------------|-------------------------|

| LVDS<br>I/F | PH8n         | B11  | Input     | General purpose I/O with LVDS transceiver | LVDS receiver           |

|             | DIGITAL_REXT | E11  | Output    | Configuration                             | Analog<br>3.3 V capable |

Note: PU means pull up and PD means pull down

Table 3. Power supply

| Signal name     | Ball                                                                                                                                                                                                                                                             | Value     |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| GND             | J9, J10, J11, J12, J13, J14, K9, K10, K11, K12, K13, K14, L9, L10, L11, L12, L13, L14, M9, M10, M11, M12, M13, M14, N9, N10, N11, N12, N13, N14, P9, P10, P11, P12, P13, P14, M18, N18, P18, T5, V6, N2, R1, U2, T4, W3, W2, Y3, AA3, V5, U5, V17, U17, A10, E12 | 0 V       |

| AGND            | V16                                                                                                                                                                                                                                                              | 0 V       |

| VDD3            | J6, H6, F8, F9, F16, H17, K17, L17, N17, P17, M6, F17                                                                                                                                                                                                            | 3.3 V     |

| VDD             | G6, L6, G17, M17, R17, F10, F13, F15, J17, T6, U13, U10, U16                                                                                                                                                                                                     | 1.0 V     |

| HOST2_VDDbc     | N1                                                                                                                                                                                                                                                               | 2.5 V     |

| HOST2_VDDbs     | N3                                                                                                                                                                                                                                                               | 1.0 V     |

| HOST2_VDDb3     | R3                                                                                                                                                                                                                                                               | 3.3 V     |

| HOST1_VDDbc     | P3                                                                                                                                                                                                                                                               | 2.5 V     |

| HOST1_VDDbs     | R2                                                                                                                                                                                                                                                               | 1.0 V     |

| HOST1_VDDb3     | R3                                                                                                                                                                                                                                                               | 3.3 V     |

| DEVICE_VDDbc    | U1                                                                                                                                                                                                                                                               | 2.5 V     |

| DEVICE_VDDbs    | U3                                                                                                                                                                                                                                                               | 1.0 V     |

| DEVICE_VDDb3    | Т3                                                                                                                                                                                                                                                               | 3.3 V     |

| USB_PLL_VDDp    | V3                                                                                                                                                                                                                                                               | 1.0 V     |

| USB_PLL_VDDp2v5 | W1                                                                                                                                                                                                                                                               | 2.5 V     |

| MCLK_VDD        | AA1                                                                                                                                                                                                                                                              | 1.0 V     |

| MCLK_VDD2v5     | AA2                                                                                                                                                                                                                                                              | 2.5 V     |

| DITH_VDD2v5     | V4                                                                                                                                                                                                                                                               | 2.5 V     |

| DITH_VDD        | U6                                                                                                                                                                                                                                                               | 1.0 V     |

| SSTL_VDDe       | U7, U8, U9, U11, U12, U14, U15                                                                                                                                                                                                                                   | 1.8/2.5 V |

| ADC_AVDD        | W16                                                                                                                                                                                                                                                              | 2.5 V     |

| DDR_PLL_AVDD    | W17                                                                                                                                                                                                                                                              | 2.5 V     |

| DDR_PLL_VDD     | T17                                                                                                                                                                                                                                                              | 1.0 V     |

| LVDS_VDD        | F11, F12, F14                                                                                                                                                                                                                                                    | 2.5 V     |

| RTC_VDD         | B10                                                                                                                                                                                                                                                              | 1.0 V     |

SPEAR-09-P022 Pin description

## 2.2 Special IOs

### 2.2.1 USB 2.0 transceiver

SPEAr Plus600 has three USB 2.0 multimode ATX transceivers. One transceiver will be used by the USB device controller, and two will be used by the hosts. These are all integrated into a single USB three-PHY macro.

### 2.2.2 SSTL\_2/SSTL\_18

T.B.D.

### 2.2.3 LVDS

T.B.D.

Memory map SPEAR-09-P022

## 3 Memory map

## 3.1 Main memory map

Table 4. Main memory map

| Start address | End address | Peripheral              | Notes                     |

|---------------|-------------|-------------------------|---------------------------|

| 0x0000.0000   | 0x3FFF.FFFF | External SDRAM          | DDR1 or DDR2              |

| 0x4000.0000   | 0xBFFF.FFFF | RAS_N/M                 | Programmable logic array  |

| 0xC000.0000   | 0xCFFF.F7FF | AHB_EH2H exp. interface |                           |

| 0xCFFF.F800   | 0xCFFF.FFFF | AHB_EH2H registers      |                           |

| 0xD000.0000   | 0xD7FF.FFFF | ICM1                    | Low speed connection      |

| 0xD800.0000   | 0xDFFF.FFFF | ICM2                    | Application subsystem     |

| 0xE000.0000   | 0xE7FF.FFFF | ICM4                    | High speed connection     |

| 0xE800.0000   | 0xEFFF.FFFF | Reserved                |                           |

| 0xF000.0000   | 0xF7FF.FFFF | ML1,2                   | Multi layer CPU subsystem |

| 0xF800.0000   | 0xFFFF.FFFF | ICM3                    | Basic subsystem           |

## 3.2 ICM1 - low speed connection

Table 5. ICM1 - low speed connection

| Start address | End address | Peripheral | Notes                          | Bus |

|---------------|-------------|------------|--------------------------------|-----|

| 0xD000.0000   | 0xD007.FFFF | UART 1     |                                | APB |

| 0xD008.0000   | 0xD00F.FFFF | UART 2     |                                | APB |

| 0xD010.0000   | 0xD017.FFFF | SPI 1      |                                | APB |

| 0xD018.0000   | 0xD01F.FFFF | SPI 2      |                                | APB |

| 0xD020.0000   | 0xD027.FFFF | I2C        |                                | APB |

| 0xD028.0000   | 0xD07F.FFFF | -          | Reserved                       | -   |

| 0xD080.0000   | 0xD0FF.FFFF | JPEG codec |                                | AHB |

| 0xD100.0000   | 0xD17F.FFFF | IrDA       |                                | AHB |

| 0xD180.0000   | 0xD1FF.FFFF | FSMC       | NAND Flash controller          | AHB |

| 0xD200.0000   | 0xD27F.FFFF | FSMC       | NAND Flash memory              | AHB |

| 0xD280.0000   | 0xD7FF.FFFF | SRAM       | Static ram shared memory (8KB) | AHB |

**577**

SPEAR-09-P022 Memory map

## 3.3 ICM2 - application subsystem

Table 6. ICM2 - application subsystem

| Start address | End address | Peripheral | Notes    | Bus |

|---------------|-------------|------------|----------|-----|

| 0xD800.0000   | 0xD807.FFFF | Timer 1    |          | APB |

| 0xD808.0000   | 0xD80F.FFFF | Timer 2    |          | APB |

| 0xD810.0000   | 0xD817.FFFF | GPIO       |          | APB |

| 0xD818.0000   | 0xD81F.FFFF | SPI 3      |          | APB |

| 0xD820.0000   | 0xD827.FFFF | ADC        |          | APB |

| 0xD828.0000   | 0xDFFF.FFFF | -          | Reserved |     |

## 3.4 ICM4 - high speed connection

Table 7. ICM4 - high speed connection

| Start address | End address | Peripheral    | Notes                   | Bus |

|---------------|-------------|---------------|-------------------------|-----|

| 0xE000.0000   | 0xe07F.FFFF | -             | Reserved                | APB |

| 0xE080.0000   | 0xE0FF.FFFF | Ethernet ctrl | GMAC                    | AHB |

| 0xE100.0000   | 0xE10F.FFFF | USB2.0 device | FIFO                    | AHB |

| 0xE110.0000   | 0xE11F.FFFF | USB2.0 device | Configuration registers | AHB |

| 0xE120.0000   | 0xE12F.FFFF | USB2.0 device | Plug detect             | AHB |

| 0xE130.0000   | 0xE17F.FFFF | -             | Reserved                | AHB |

| 0xE180.0000   | 0xE18F.FFFF | USB2.0 EHCl 1 |                         | AHB |

| 0xE190.0000   | 0xE19F.FFFF | USB2.0 OHCl 1 |                         | AHB |

| 0xE1A0.0000   | 0xE1FF.FFFF | -             | Reserved                | AHB |

| 0xE200.0000   | 0xE20F.FFFF | USB2.0 EHCl 2 |                         | AHB |

| 0xE210.0000   | 0xE21F.FFFF | USB2.0 OHCl 2 |                         | AHB |

| 0xE220.0000   | 0xE2FF.FFFF | -             | Reserved                | AHB |

| 0xE280.0000   | 0xE280.FFFF | ML USB ARB    | Configuration register  | AHB |

| 0xE290.0000   | 0xE7FF.FFFF | -             | Reserved                | AHB |

Memory map SPEAR-09-P022

## 3.5 ML1, 2 - multi layer CPU subsystem

Table 8. ML1, 2 - multi layer CPU subsystem

| Start address | End address | Peripheral    | Notes    | Bus |

|---------------|-------------|---------------|----------|-----|

| 0xF000.0000   | 0xF00F.FFFF | Timer         |          | APB |

| 0xF010.0000   | 0xF01F.FFFF | GPIO          |          | APB |

| 0xF020.0000   | 0xF0FF.FFFF | -             | Reserved | AHB |

| 0xF100.0000   | 0xF10F.FFFF | ITC secondary |          | AHB |

| 0xF110.0000   | 0xF11F.FFFF | ITC primary   |          | AHB |

| 0xF120.0000   | 0xF7FF.FFFF | -             | Reserved | AHB |

## 3.6 ICM3 - basic subsystem

Table 9. ICM3 - basic subsystem

| Start address | End address | Peripheral              | Notes    |

|---------------|-------------|-------------------------|----------|

| 0xF800.0000   | 0xFBFF.FFFF | Serial Flash memory     |          |

| 0xFC00.0000   | 0xFC1F.FFFF | Serial Flash controller |          |

| 0xFC20.0000   | 0xFC3F.FFFF | LCD controller          |          |

| 0xFC40.0000   | 0xFC5F.FFFF | DMA controller          |          |

| 0xFC60.0000   | 0xFC7F.FFFF | SDRAM controller        |          |

| 0xFC80.0000   | 0xFC87.FFFF | Timer                   |          |

| 0xFC88.0000   | 0xFC8F.FFFF | Watch dog timer         |          |

| 0xFC90.0000   | 0xFC97.FFFF | Real time clock         |          |

| 0xFC98.0000   | 0xFC9F.FFFF | General purpose I/O     |          |

| 0xFCA0.0000   | 0xFCA7.FFFF | System controller       |          |

| 0xFCA8.0000   | 0xFCAF.FFFF | Miscellaneous registers |          |

| 0xFCB0.0000   | 0xFEFF.FFFF | -                       | Reserved |

| 0xFF00.0000   | 0xFFFF.FFFF | Internal ROM            | Boot     |

Downloaded from Arrow.com.

SPEAR-09-P022 Main blocks

### 4 Main blocks

### 4.1 7.1 CPU subsystem

#### 4.1.1 Overview

Each CPU sub-system includes the following blocks:

- ARM 926EJS

- Two timer channels

- One GPIO block (8 I/O lines)

- Two interrupt controller (32 IRQ lines)

#### 4.1.2 CPU ARM 926EJ-S

The processor is the powerful ARM926EJ-S, targeted for multi-tasking applications.

Belonging to ARM9 general purposes family microprocessor, it principally stands out for the memory management unit, which provides virtually memory features, making it also compliant with WindowsCE, linux and SymbianOS operating systems.

The ARM926EJ-S supports the 32-bit ARM and 16-bit thumb instruction sets, enabling the user to trade off between high performance and high code density and includes features for efficient execution of java byte codes.

Besides, it has the ARM debug architecture and includes logic to assist in software debug.

Its main features are:

- Core f<sub>MAX</sub> 333 MHz independent programmable for each CPU

- Memory management unit

- 16 Kbyte of instruction cache

- 16 Kbyte of data cache

- Configurable tightly coupled memory (I/D) size trough the configurable logic array

- ARM-V5TEJ instructions set architecture:

- ARM (32-bit), thumb<sup>®</sup> (16-bit)

- DSP extensions

- JAVA™ (8-bit) instructions

- AMBA bus interface

- Coprocessor interface (only for the 1<sup>st</sup> processor)

- EmbeddedICE-RT

- Single mode (two connectors)

- Two processor daisy chained

- ETM9 (embedded trace macro-cell)

- Single ETM mode (single or double packet configurable)

- Dual ETM mode (both processors ETM are available in single packet mode)

577

Main blocks SPEAR-09-P022

### 4.2 Clock and reset system

The clock system block is a fully programmable block able to generate all clocks necessary at the chip.

The clocks, at default operative frequency, are:

- Clock @ 333 MHz for the CPUs (Note 1)

- Clock @ 166 MHz for AHB bus and AHB peripherals (Note 1)

- Clock @ 83 MHz for, APB bus and APB peripherals (*Note 1*)

- Clock @ 100-333 MHz for DDR memory interface (Note 2)

The frequencies are the maximum allowed value and the user can modify them by programming dedicated registers.

The clock system consists of 2 main parts: a multi-clock generator block and an two internal PLL.

The multi-clock generator block, starting from a reference signal (which generally is delivered from the PLL), generates all clocks for the IPs of SPEAr Plus600 according to dedicated programmable registers.

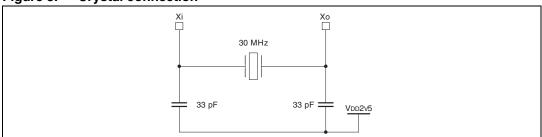

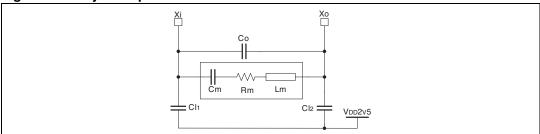

Each PLL, starting from the oscillator input of 30 MHz, generates a clock signal at a frequency corresponding at the highest of the group, which is the reference signal used by the multi-clock generator block to obtain all the other requested clocks for the group. Its main features is the electro-magnetic interference reduction capability: user has the possibility to set up the PLL in order to modulate with a triangular wave to the VCO clock, the resulting signal will have the spectrum (and the power) spread on a small range (programmable) of frequencies centered on F0 (VCO Freq.), obtaining minimum electromagnetic emissions. This method replace all the other traditional methods of E.M.I. reduction, as filtering, ferrite beads, chokes, adding power layers and ground planets to PCBs, metal shielding etc., allowing sensible cost saving for customers.