#### 8XC54/58 8XC51FA/FB/FC/80C51FA 8XC51RA+/RB+/RC+/RD+/80C51RA+

#### DESCRIPTION

Three different Single-Chip 8-Bit Microcontroller families are presented in this datasheet:

- 8XC54/8XC58

- 80C51FA/8XC51FA/8XC51FB/8XC51FC

- 80C51RA+/8XC51RA+/8XC51RB+/8XC51RC+/8XC51RD+

For applications requiring 4K ROM/EPROM, see the 8XC51/80C31 8-bit CMOS (low voltage, low power, and high speed) microcontroller families datasheet.

All the families are Single-Chip 8-Bit Microcontrollers manufactured in advanced CMOS process and are derivatives of the 80C51 microcontroller family. All the devices have the same instruction set as the 80C51.

These devices provide architectural enhancements that make them applicable in a variety of applications for general control systems.

| ROM/EPROM<br>Memory Size<br>(X by 8) | RAM Size<br>(X by 8) | Programmable<br>Timer Counter<br>(PCA) | Hardware<br>Watch Dog<br>Timer |

|--------------------------------------|----------------------|----------------------------------------|--------------------------------|

| 80C31/8XC51                          |                      |                                        |                                |

| 0K/4K                                | 128                  | No                                     | No                             |

| 8XC54/58                             |                      |                                        |                                |

| 0K/8K/16K/32K                        | 256                  | No                                     | No                             |

| 80C51FA/8XC51                        | FA/FB/FC             |                                        |                                |

| 0K/8K/16K/32K                        | 256                  | Yes                                    | No                             |

| 80C51RA+/8XC5                        | 51RA+/RB+/RC+        | ÷                                      |                                |

| 0K/8K/16K/32K                        | 512                  | Yes                                    | Yes                            |

| 8XC51RD+                             |                      |                                        |                                |

| 64K                                  | 1024                 | Yes                                    | Yes                            |

The ROMless devices, 80C51FA, and 80C51RA+ can address up to 64K of external memory. All the devices have four 8-bit I/O ports, three 16-bit timer/event counters, a multi-source, four-priority-level, nested interrupt structure, an enhanced UART and on-chip oscillator and timing circuits. For systems that require extra memory capability up to 64k bytes, each can be expanded using standard TTL-compatible memories and logic.

Its added features make it an even more powerful microcontroller for applications that require pulse width modulation, high-speed I/O and up/down counting capabilities such as motor control. It also has a more versatile serial channel that facilitates multiprocessor communications.

#### **FEATURES**

- 80C51 Central Processing Unit

- Speed up to 33 MHz

- Full static operation

- Operating voltage range: 2.7 V to 5.5 V @ 16 MHz

- Security bits:

- ROM 2 bits

- OTP-EPROM 3 bits

- Encryption array 64 bytes

- RAM expandable to 64K bytes

- 4 level priority interrupt

- 6 or7 interrupt sources, depending on device

- Four 8-bit I/O ports

- Full-duplex enhanced UART

- Framing error detection

- Automatic address recognition

- Power control modes

- Clock can be stopped and resumed

- Idle mode

- Power down mode

- Programmable clock out

- Second DPTR register

- Asynchronous port reset

- Low EMI (inhibit ALE)

#### 8XC54/58 8XC51FA/FB/FC/80C51FA 8XC51RA+/RB+/RC+/RD+/80C51RA+

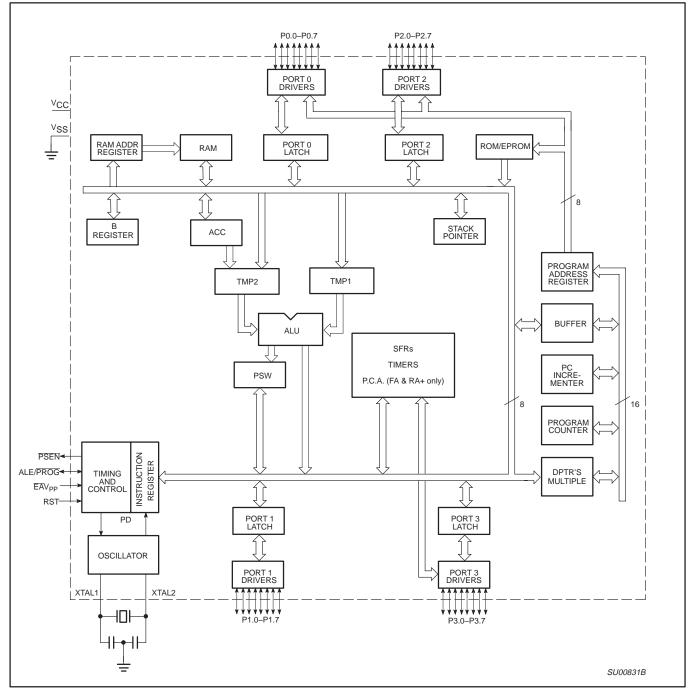

# **BLOCK DIAGRAM**

#### 8XC54/58 8XC51FA/FB/FC/80C51FA 8XC51RA+/RB+/RC+/RD+/80C51RA+

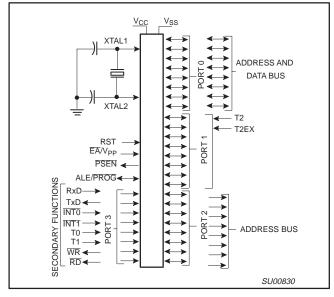

# LOGIC SYMBOL

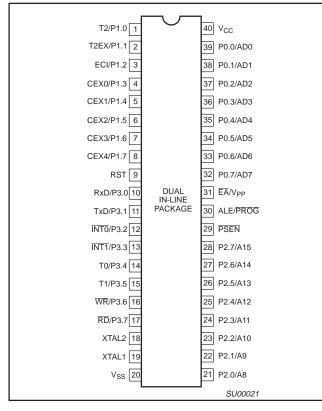

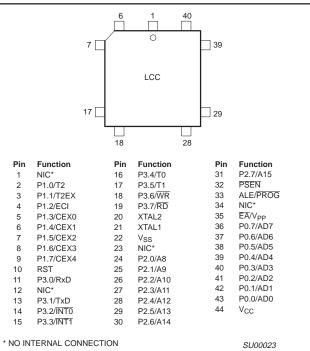

# PIN CONFIGURATIONS

# **DUAL IN-LINE PACKAGE PIN FUNCTIONS**

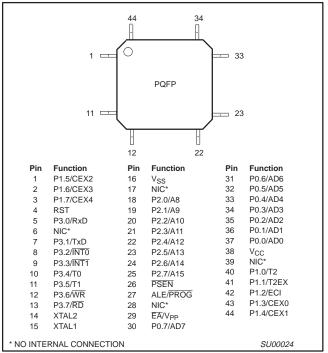

# PLASTIC LEADED CHIP CARRIER PIN FUNCTIONS

# PLASTIC QUAD FLAT PACK PIN FUNCTIONS

#### 8XC54/58 8XC51FA/FB/FC/80C51FA 8XC51RA+/RB+/RC+/RD+/80C51RA+

# **PIN DESCRIPTIONS**

|                 | PI         | N NUMB       | ER            |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------|------------|--------------|---------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC        | DIP        | LCC          | QFP           | TYPE       | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>SS</sub> | 20         | 22           | 16            | I          | Ground: 0 V reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>CC</sub> | 40         | 44           | 38            | I.         | Power Supply: This is the power supply voltage for normal, idle, and power-down operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P0.0-0.7        | 39–32      | 43–36        | 37–30         | I/O        | <b>Port 0:</b> Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory. In this application, it uses strong internal pull-ups when emitting 1s. Port 0 also outputs the code bytes during program verification and received code bytes during EPROM programming. External pull-ups are required during program verification.                                                                                                                                                                                                                  |

| P1.0-P1.7       | 1–8        | 2–9          | 40–44,<br>1–3 | I/O        | <b>Port 1:</b> Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 1 pins that are externally pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: $I_{ L}$ ). Port 1 also receives the low-order address byte during program memory verification.                                                                                                                                                                                                                                                                                                     |

|                 |            |              |               |            | Alternate functions for 8XC51FX and 8XC51RX+ Port 1 include:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

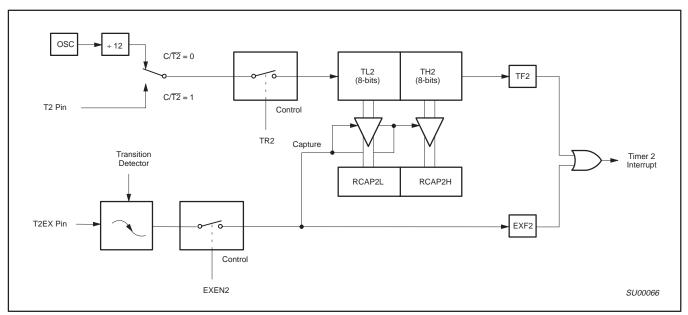

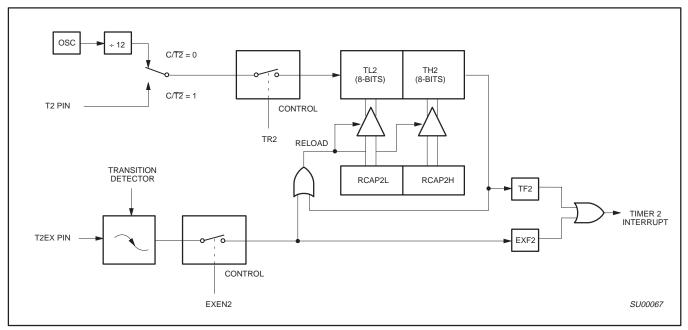

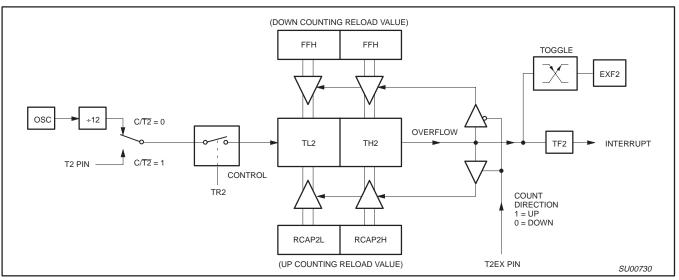

|                 | 1          | 2            | 40            | I/O        | T2 (P1.0): Timer/Counter 2 external count input/Clockout (see Programmable Clock-Out)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | 2          | 3            | 41            | I          | T2EX (P1.1): Timer/Counter 2 Reload/Capture/Direction Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 | 3          | 4            | 42            |            | ECI (P1.2): External Clock Input to the PCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | 4          | 5            | 43            | I/O        | CEX0 (P1.3): Capture/Compare External I/O for PCA module 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 | 5          | 6            | 44            | I/O        | CEX1 (P1.4): Capture/Compare External I/O for PCA module 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 | 6<br>7     | 7            | 1<br>2        | 1/O<br>1/O | CEX2 (P1.5): Capture/Compare External I/O for PCA module 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 | 8          | 8<br>9       | 2             | 1/O        | CEX3 (P1.6): Capture/Compare External I/O for PCA module 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P2.0-P2.7       | o<br>21–28 | 9<br>24–31   |               | 1/O        | <b>CEX4 (P1.7):</b> Capture/Compare External I/O for PCA module 4<br><b>Port 2:</b> Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1 2.0 1 2.1     | 21 20      | 24 01        | 10 20         | "          | written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 2 pins that are externally being pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: $I_{IL}$ ). Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOV @Ri), port 2 emits the contents of the P2 special function register. Some Port 2 pins receive the high order address bits during EPROM programming and verification. |

| P3.0–P3.7       | 10–17      | 11,<br>13–19 | 5,<br>7–13    | I/O        | <b>Port 3</b> : Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 3 pins that are externally being pulled low will source current because of the pull-ups. (See DC Electrical Characteristics: $I_{IL}$ ). Port 3 also serves the special features of the 80C51 family, as listed below:                                                                                                                                                                                                                                                                                                             |

|                 | 10         | 11           | 5             | I.         | RxD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 | 11         | 13           | 7             | 0          | TxD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 | 12         | 14           | 8             |            | INTO (P3.2): External interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                 | 13         | 15           | 9             |            | INT1 (P3.3): External interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                 | 14         | 16<br>17     | 10            |            | T0 (P3.4): Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | 15<br>16   | 17<br>18     | 11<br>12      | 0          | T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | 16<br>17   | 18<br>19     | 12            | 0          | WR (P3.6): External data memory write strobe<br>RD (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RST             | 9          | 19           | 4             | I          | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal diffused resistor to $V_{SS}$ permits a power-on reset using only an external capacitor to $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

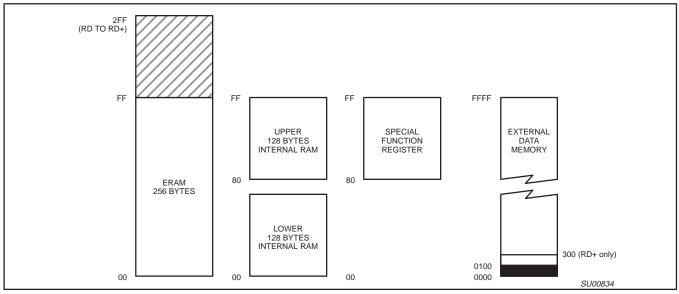

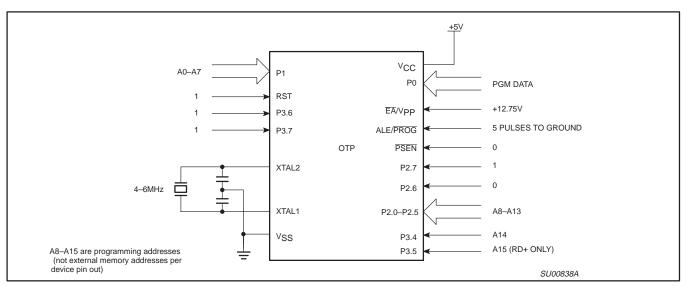

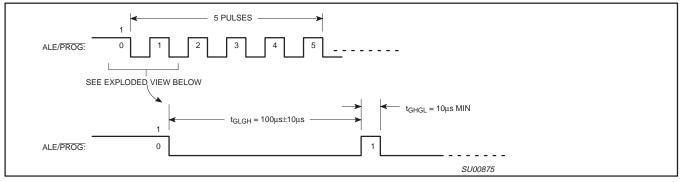

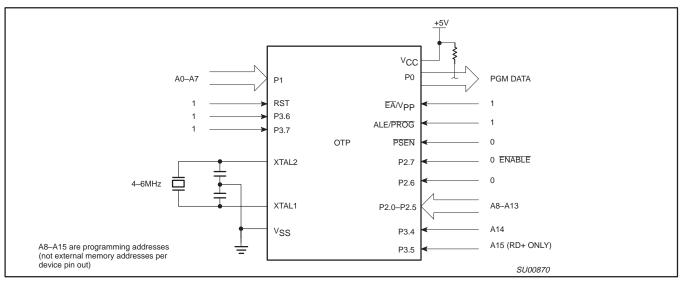

| ALE/PROG        | 30         | 33           | 27            | 0          | Address Latch Enable/Program Pulse: Output pulse for latching the low byte of the address during an access to external memory. In normal operation, ALE is emitted at a constant rate of 1/6 the oscillator frequency, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory. This pin is also the program pulse input (PROG) during EPROM programming. ALE can be disabled by setting SFR auxiliary.0. With this bit set, ALE will be active only during a MOVX instruction.                                                                                                                                                                                            |

### PIN DESCRIPTIONS (Continued)

|                    | PI  | N NUMB | ER  |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------|-----|--------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC           | DIP | LCC    | QFP | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PSEN               | 29  | 32     | 26  | 0    | <b>Program Store Enable:</b> The read strobe to external program memory. When executing code from the external program memory, <b>PSEN</b> is activated twice each machine cycle, except that two <b>PSEN</b> activations are skipped during each access to external data memory. <b>PSEN</b> is not activated during fetches from internal program memory.                                                                                                                                                                                                                                                                                                                              |

| EA/V <sub>PP</sub> | 31  | 35     | 29  | I    | <b>External Access Enable/Programming Supply Voltage:</b> EA must be externally held low to enable the device to fetch code from external program memory locations starting with 0000H. If EA is held high, the device executes from internal program memory unless the program counter contains an address greater than 8k Devices (IFFFH), 16k Devices (3FFFH) or 32k Devices (7FFFH). Since the RD+ has 64k Internal Memory, the RD+ will execute only from internal memory when EA is held high. This pin also receives the 12.75 V programming supply voltage (V <sub>PP</sub> ) during EPROM programming. If security bit 1 is programmed, EA will be internally latched on Reset. |

| XTAL1              | 19  | 21     | 15  | I    | Crystal 1: Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| XTAL2              | 18  | 20     | 14  | 0    | Crystal 2: Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

NOTE:

To avoid "latch-up" effect at power-on, the voltage on any pin at any time must not be higher than  $V_{CC}$  + 0.5 V or  $V_{SS}$  – 0.5 V, respectively.

# 8XC54/58 ORDERING INFORMATION

|     | MEMORY SIZE<br>16K × 8 | MEMORY SIZE<br>32K × 8 | TEMPERATURE RANGE °C<br>AND PACKAGE        | VOLTAGE<br>RANGE | FREQ.<br>(MHz) | DWG.<br># |

|-----|------------------------|------------------------|--------------------------------------------|------------------|----------------|-----------|

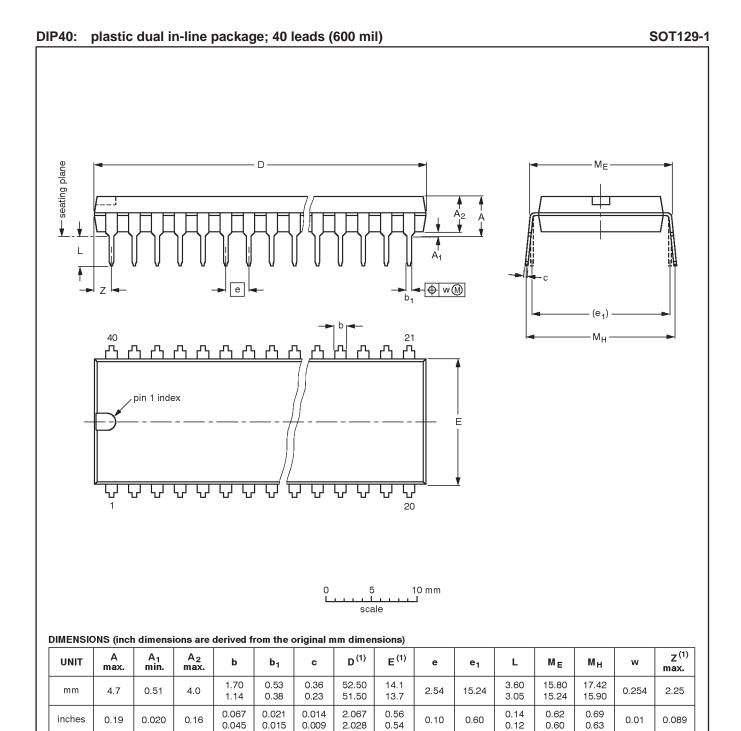

| ROM | P80C54SBPN             | P80C58SBPN             | 0 to +70, Plastic Dual In-line Package     | 2.7 V to         | 0 to 16        | SOT129-1  |

| OTP | P87C54SBPN             | P87C58SBPN             | 0 to +70, Plastic Dual III-IIIle Package   | 5.5 V            | 01010          | 301129-1  |

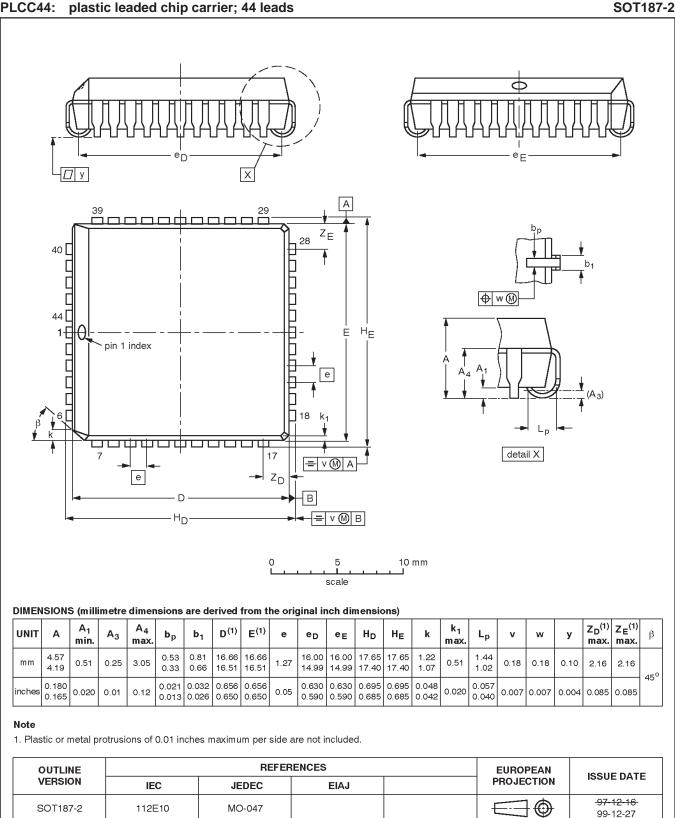

| ROM | P80C54SBAA             | P80C58SBAA             | 0 to +70, Plastic Leaded Chip Carrier      | 2.7 V to         | 0 to 16        | SOT187-2  |

| OTP | P87C54SBAA             | P87C58SBAA             | 0 to +70, Plastic Leaded Chip Carrier      | 5.5 V            | 01010          | 301107-2  |

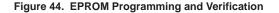

| ROM | P80C54SBBB             | P80C58SBBB             | 0 to +70, Plastic Quad Flat Pack           | 2.7 V to         | 0 to 16        | SOT307-2  |

| OTP | P87C54SBBB             | P87C58SBBB             |                                            | 5.5 V            | 01010          | 301307-2  |

| ROM | P80C54SFPN             | P80C58SFPN             | -40 to +85, Plastic Dual In-line Package   | 2.7 V to         | 0 to 16        | SOT129-1  |

| OTP | P87C54SFPN             | P87C58SFPN             | -40 to +65, Flastic Dual III-lille Fackage | 5.5 V            | 01010          | 301129-1  |

| ROM | P80C54SFA A            | P80C58SFA A            | -40 to +85, Plastic Leaded Chip Carrier    | 2.7 V to         | 0 to 16        | SOT187-2  |

| OTP | P87C54SFA A            | P87C58SFA A            |                                            | 5.5 V            | 01010          | 501107-2  |

| ROM | P80C54SFBB             | P80C58SFBB             | –40 to +85, Plastic Quad Flat Pack         | 2.7 V to         | 0 to 16        | SOT307-2  |

| OTP | P87C54SFBB             | P87C58SFBB             |                                            | 5.5 V            | 01010          | 301307-2  |

| ROM | P80C54UBAA             | P80C58UBAA             | 0 to +70, Plastic Leaded Chip Carrier      | 5 V              | 0 to 33        | SOT187-2  |

| OTP | P87C54UBAA             | P87C58UBAA             | 0 to +70, Flastic Leaded Chip Carrier      | 5 V              | 0 10 33        | 301107-2  |

| ROM | P80C54UBPN             | P80C58UBPN             | 0 to +70, Plastic Dual In-line Package     | 5 V              | 0 to 33        | SOT129-1  |

| OTP | P87C54UBPN             | P87C58UBPN             |                                            | 5.0              | 0 10 33        | 301129-1  |

| ROM | P80C54UBBB             | P80C58UBBB             | 0 to +70, Plastic Quad Flat Pack           | 5 V              | 0 to 33        | SOT307-2  |

| OTP | P87C54UBBB             | P87C58UBBB             | 0 to +70, Flastic Quad Flat Fack           | 5 V              | 0 10 33        | 301307-2  |

| ROM | P80C54UFAA             | P80C58UFA A            | -40 to +85, Plastic Leaded Chip Carrier    | 5 V              | 0 to 33        | SOT187-2  |

| OTP | P87C54UFAA             | P87C58UFA A            | -40 to +65, Plastic Leaded Chip Carrier    | 5 V              | 0 10 33        | 301107-2  |

| ROM | P80C54UFPN             | P80C58UFPN             | -40 to +85, Plastic Dual In-line Package   | 5 V              | 0 to 33        | SOT129-1  |

| OTP | P87C54UFPN             | P87C58UFPN             |                                            | 5 V              | 01033          | 301129-1  |

| ROM | P80C54UFBB             | P80C58UFBB             | -40 to +85, Plastic Quad Flat Pack         | 5 V              | 0 to 33        | SOT307-2  |

| OTP | P87C54UFBB             | P87C58UFBB             |                                            | 5 V              | 0 10 33        | 301307-2  |

Note: For Multi Time Programmable devices, See P89C51RX+

Flash datasheet.

| 8XC51    | 8XC51FA/FB/FC AND 80C51FA OKDEKI                                          | 80C51FA OKL            | JEKING INFORMATION     | NALION       |                                                    |                  |                |           |

|----------|---------------------------------------------------------------------------|------------------------|------------------------|--------------|----------------------------------------------------|------------------|----------------|-----------|

|          | MEMORY SIZE<br>8K × 8                                                     | MEMORY SIZE<br>16K × 8 | MEMORY SIZE<br>32K × 8 | ROMIess      | TEMPERATURE RANGE ∘C<br>AND PACKAGE                | VOLTAGE<br>RANGE | FREQ.<br>(MHz) | DWG.<br># |

| ROM      | P83C51FA-4N                                                               | P83C51FB-4N            | P83C51FC-4N            | DOUGELEV IN  | 270 July 20 July Dissipation Dissipation (2 - 04 0 | 0 7// to E E//   | 0 +0 16        | SOT120.1  |

| ОТР      | P87C51FA-4N                                                               | P87C51FB-4N            | P87C51FC-4N            |              | 0 (0 ± / 0, +0-FIII Flastic Dual III-III E FNG.    | V C U V 1.2      |                | 1-871100  |

| ROM      | P83C51FA-4A                                                               | P83C51FB-4A            | P83C51FC-4A            |              | C to 170 14 Discolorid Charles                     | 0 7// to E E//   | 0+046          | C 101102  |

| ОТР      | P87C51FA4A                                                                | P87C51FB-4A            | P87C51FC4A             | POUCOIFA-4A  |                                                    | 1 V U U U V V V  |                | 7-101100  |

| ROM      | P83C51FA-4B                                                               | P83C51FB-4B            | P83C51FC4B             |              |                                                    | 0 71/10 5 57/    | 01010          |           |

| ОТР      | P87C51FA4B                                                                | P87C51FB-4B            | P87C51FC4B             | POUCOTFA-4B  | U to +/U, 44-Pin Plastic Quad Flat Pack            | VC.C 01 V 1.2    |                | 2-100100  |

| ROM      | P83C51FA-5N                                                               | P83C51FB-5N            | P83C51FC5N             |              | 201 - 10 - 10 - 10 - 10 - 10 - 10 - 10 -           | 0 71/ to E EV    | 01040          | 50T120 1  |

| ОТР      | P87C51FA–5N                                                               | P87C51FB-5N            | P87C51FC5N             |              | -40 to +60, 40-Pin Plastic Dual In-line PKg.       | AC.C 01 A 1.2    |                | 1-871100  |

| ROM      | P83C51FA5A                                                                | P83C51FB-5A            | P83C51FC5A             |              | 10 to 10E 11 Disciple in Disciple                  | 0 711 to E EVI   | 0 10 10        | SOT107 0  |

| ОТР      | P87C51FA5A                                                                | P87C51FB–5A            | P87C51FC5A             |              |                                                    |                  |                | 7-101100  |

| ROM      | P83C51FA-5B                                                               | P83C51FB-5B            | P83C51FC-5B            |              | Apped to 10 piccelo aid 11 - 30, of 01             | 0 711 to E EVI   | 01010          | C 202303  |

| ОТР      | P87C51FA-5B                                                               | P87C51FB-5B            | P87C51FC5B             |              |                                                    |                  |                | z-100100  |

| ROM      | P83C51FA–IN                                                               | P83C51FB-IN            | P83C51FC-IN            |              | original privacijanja operation (1990). Operation  | <u>د</u> //      | 0 0 00         | SOT120 1  |

| ОТР      | P87C51FA–IN                                                               | P87C51FB-IN            | P87C51FC-IN            |              | 0 (0 + / 0, +0-FIII Flastic Dual III-IIIIE FKg.    | ۸c               |                | 1-871100  |

| ROM      | P83C51FA–IA                                                               | P83C51FB–IA            | P83C51FC-IA            |              | C to 170 Al Discolo Lottonia Al OT 1 of O          | 277              |                | SOT107 2  |

| ОТР      | P87C51FA–IA                                                               | P87C51FB–IA            | P87C51FC–IA            |              |                                                    | <u>&gt;</u>      | U TO 33        | 7-191100  |

| ROM      | P83C51FA-IB                                                               | P83C51FB-IB            | P83C51FC-IB            |              | Acceleration Control and 110 ctots                 | <u>د</u> //      | 0 0 0 00       | SOT207 2  |

| ОТР      | P87C51FA–IB                                                               | P87C51FB–IB            | P87C51FC-IB            |              | U (U T/ U, 44-FIII FIASIU QUAU FIAL FAUN           | <u>ک</u>         |                | 7-100100  |

| ROM      | P83C51FA-JN                                                               | P83C51FB–JN            | P83C51FC-JN            | DOUCE1EA IN  | 270                                                | 577              | 0 0 0 0 0      | SOT120 1  |

| ОТР      | P87C51FA-JN                                                               | P87C51FB–JN            | P87C51FC-JN            |              | -40 to +00, 40-Fill Flastic Dual III-III E FKg.    | ۸C               |                | 1-871100  |

| ROM      | P83C51FA-JA                                                               | P83C51FB-JA            | P83C51FC-JA            |              | 10 to to 12 history of the sector                  | 277              |                | C 101103  |

| ОТР      | P87C51FA–JA                                                               | P87C51FB–JA            | P87C51FC–JA            |              |                                                    | ۸C               |                | 7-101100  |

| ROM      | P83C51FA-JB                                                               | P83C51FB-JB            | P83C51FC-JB            |              | 7004 to 100 min official of 000                    | <u>د</u> //      | 0 40 00        | SOT207 2  |

| ОТР      | P87C51FA–JB                                                               | P87C51FB-JB            | P87C51FC-JB            |              | -40 נט 400, 44-רוון רומצווט עעמע רומו רמטא         | ۸C               | 0 10 33        | 7-100100  |

| Note: Fc | Note: For Multi Time Programmable devices, See P89C51RX+ Flash datasheet. | mmable devices, Se     | e P89C51RX+ Flas       | h datasheet. |                                                    |                  |                |           |

8XC51FA/FB/FC AND 80C51FA ORDERING INFORMATION

Philips Semiconductors

Product specification

| 87C51    | 87C51RA+/RB+/RC+/RD+ AND 80C51RA+                                         | 3D+ AND 80C5           |                        | ORDERING INFORMATION   | lion                                     |                                     |                  |                |             |

|----------|---------------------------------------------------------------------------|------------------------|------------------------|------------------------|------------------------------------------|-------------------------------------|------------------|----------------|-------------|

|          | MEMORY SIZE<br>8K × 8                                                     | MEMORY SIZE<br>16K × 8 | MEMORY SIZE<br>32K × 8 | MEMORY SIZE<br>64K × 8 | ROMIess                                  | TEMPERATURE RANGE ∘C<br>AND PACKAGE | VOLTAGE<br>RANGE | FREQ.<br>(MHz) | DWG.<br>#   |

| ROM      | P83C51RA+4N                                                               | P83C51RB+4N            | P83C51RC+4N            | P83C51RD+4N            | DBOCEADA : AN                            | 0 to +70,                           | 0 7\/ to E E//   | 91 010         | COT100 1    |

| ОТР      | P87C51RA+4N                                                               | P87C51RB+4N            | P87C51RC+4N            | P87C51RD+4N            |                                          | 40-Pin Plastic Dual In-line Pkg.    | VC.C UI V 1.2    | 0 10 10        | 1-671100    |

| ROM      | P83C51RA+4A                                                               | P83C51RB+4A            | P83C51RC+4A            | P83C51RD+4A            | BSOCE1DA:1A                              | 0 to +70,                           | 0 7\/ to E E//   | 0 to 16        | CUT107 0    |

| ОТР      | P87C51RA+4A                                                               | P87C51RB+4A            | P87C51RC+4A            | P87C51RD+4A            |                                          | 44-Pin Plastic Leaded Chip Carrier  | 7.7 V LU 3.3V    | 0 10 10        | 7-101100    |

| ROM      | P83C51RA+4B                                                               | P83C51RB+4B            | P83C51RC+4B            | P83C51RD+4B            | 07 - 7 - 7 - 7 - 7 - 7 - 7 - 7 - 7 - 7 - | 0 to +70,                           |                  | 0 10 40        | 0 200203    |

| ОТР      | P87C51RA+4B                                                               | P87C51RB+4B            | P87C51RC+4B            | P87C51RD+4B            | P80C51KA+4B                              | 44-Pin Plastic Quad Flat Pack       | VC.C 01 V 1.2    | 91. 01 N       | 2-/02100    |

| ROM      | P83C51RA+5N                                                               | P83C51RB+5N            | P83C51RC+5N            | P83C51RD+5N            |                                          | -40 to +85,                         | 0 71/ to E EV    | 0 10 10        | COT100 1    |

| ОТР      | P87C51RA+5N                                                               | P87C51RB+5N            | P87C51RC+5N            | P87C51RD+5N            |                                          | 40-Pin Plastic Dual In-line Pkg.    | VC.C UI V 1.2    | 0 10 10        | 1-671100    |

| ROM      | P83C51RA+5A                                                               | P83C51RB+5A            | P83C51RC+5A            | P83C51RD+5A            |                                          | -40 to +85,                         | 0 71/ to E EV    | 0 10 10        | C T 1 0 7 0 |

| ОТР      | P87C51RA+5A                                                               | P87C51RB+5A            | P87C51RC+5A            | P87C51RD+5A            |                                          | 44-Pin Plastic Leaded Chip Carrier  | VC.C UI V 1.2    | 0 10 10        | 7-101100    |

| ROM      | P83C51RA+5B                                                               | P83C51RB+5B            | P83C51RC+5B            | P83C51RD+5B            |                                          | -40 to +85,                         | 0 71/ to E EV    | 0 10 10        | 0 200203    |

| ОТР      | P87C51RA+5B                                                               | P87C51RB+5B            | P87C51RC+5B            | P87C51RD+5B            |                                          | 44-Pin Plastic Quad Flat Pack       | VC.C UI V 1.2    | 0 10 10        | 7-100100    |

| ROM      | P83C51RA+IN                                                               | P83C51RB+IN            | P83C51RC+IN            | P83C51RD+IN            | DBACE1DA - INI                           | 0 to +70,                           | EV               | 0 40 33        | COT100 1    |

| ОТР      | P87C51RA+IN                                                               | P87C51RB+IN            | P87C51RC+IN            | P87C51RD+IN            |                                          | 40-Pin Plastic Dual In-line Pkg.    | ۸<br>د           | 0 10 23        | 1-671100    |

| ROM      | P83C51RA+IA                                                               | P83C51RB+IA            | P83C51RC+IA            | P83C51RD+IA            |                                          | 0 to +70,                           | EV               | ee ⊶ 0         | C T 1 07 0  |

| ОТР      | P87C51RA+IA                                                               | P87C51RB+IA            | P87C51RC+IA            | P87C51RD+IA            |                                          | 44-Pin Plastic Leaded Chip Carrier  | ۸ <u>۵</u>       |                | 7-101100    |

| ROM      | P83C51RA+IB                                                               | P83C51RB+IB            | P83C51RC+IB            | P83C51RD+IB            |                                          | 0 to +70,                           | 577              | 00 00 0        | 0 200203    |

| ОТР      | P87C51RA+IB                                                               | P87C51RB+IB            | P87C51RC+IB            | P87C51RD+IB            |                                          | 44-Pin Plastic Quad Flat Pack       | >c               | U TO 33        | 2-/02100    |

| ROM      | P83C51RA+JN                                                               | P83C51RB+JN            | P83C51RC+JN            | P83C51RD+JN            |                                          | -40 to +85,                         | 111              |                | 1 00 T      |

| OTP      | P87C51RA+JN                                                               | P87C51RB+JN            | P87C51RC+JN            | P87C51RD+JN            |                                          | 40-Pin Plastic Dual In-line Pkg.    | ><br>C           | U TO 33        | 1-671100    |

| ROM      | P83C51RA+JA                                                               | P83C51RB+JA            | P83C51RC+JA            | P83C51RD+JA            | DBACE1DA                                 | -40 to +85,                         | EV               | 0 40 33        | CUT107 0    |

| ОТР      | P87C51RA+JA                                                               | P87C51RB+JA            | P87C51RC+JA            | P87C51RD+JA            |                                          | 44-Pin Plastic Leaded Chip Carrier  | <u>ک</u>         |                | 7-101100    |

| ROM      | P83C51RA+JB                                                               | P83C51RB+JB            | P83C51RC+JB            | P83C51RD+JB            |                                          | -40 to +85,                         | ΕV               | 0 to 33        | CT307-0     |

| ОТР      | P87C51RA+JB                                                               | P87C51RB+JB            | P87C51RC+JB            | P87C51RD+JB            |                                          | 44-Pin Plastic Quad Flat Pack       | 2                | 0 0 0          | 7-100100    |

| Note: Fo | Note: For Multi Time Programmable devices, See P89C51RX+ Flash datasheet. | nmable devices, Se     | e P89C51RX+ Flas       | sh datasheet.          |                                          |                                     |                  |                |             |

9

#### 8XC54/58 8XC51FA/FB/FC/80C51FA 8XC51RA+/RB+/RC+/RD+/80C51RA+

#### Table 1. 8XC54/58 Special Function Registers

| SYMBOL             | DESCRIPTION             | DIRECT<br>ADDRESS |        |       | , SYMBO | L, OR AL          | FERNATIV | E PORT | FUNCTIC | DN<br>LSB | RESET<br>VALUE |

|--------------------|-------------------------|-------------------|--------|-------|---------|-------------------|----------|--------|---------|-----------|----------------|

| ACC*               | Accumulator             | E0H               | E7     | E6    | E5      | E4                | E3       | E2     | E1      | E0        | 00H            |

| AUXR#              | Auxiliary               | 8EH               | -      | -     | -       | -                 | -        | -      | -       | AO        | xxxxxxx0B      |

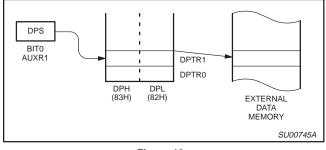

| AUXR1#             | Auxiliary 1             | A2H               | -      | -     | -       | LPEP <sup>3</sup> | GF3      | 0      | -       | DPS       | xxx0xxx0B      |

| B*                 | B register              | F0H               | F7     | F6    | F5      | F4                | F3       | F2     | F1      | F0        | 00H            |

| DPTR:              | Data Pointer (2 bytes)  |                   |        |       |         |                   |          |        |         |           |                |

| DPH                | Data Pointer High       | 83H               |        |       |         |                   |          |        |         |           | 00H            |

| DPL                | Data Pointer Low        | 82H               |        |       |         |                   |          |        |         |           | 00H            |

|                    |                         |                   | AF     | AE    | AD      | AC                | AB       | AA     | A9      | A8        |                |

| IE*                | Interrupt Enable        | A8H               | EA     | -     | ET2     | ES                | ET1      | EX1    | ET0     | EX0       | 0x000000B      |

|                    |                         |                   | BF     | BE    | BD      | BC                | BB       | BA     | B9      | B8        | ]              |

| IP*                | Interrupt Priority      | B8H               | -      | -     | PT2     | PS                | PT1      | PX1    | PT0     | PX0       | xx000000B      |

|                    |                         |                   | B7     | B6    | B5      | B4                | B3       | B2     | B1      | B0        | 1              |

| IPH#               | Interrupt Priority High | B7H               | -      | -     | PT2H    | PSH               | PT1H     | PX1H   | PT0H    | PX0H      | xx000000B      |

|                    |                         |                   | 87     | 86    | 85      | 84                | 83       | 82     | 81      | 80        | 1              |

| P0*                | Port 0                  | 80H               | AD7    | AD6   | AD5     | AD4               | AD3      | AD2    | AD1     | AD0       | FFH            |

|                    |                         |                   | 97     | 96    | 95      | 94                | 93       | 92     | 91      | 90        | 1              |

| P1*                | Port 1                  | 90H               | _      | -     | -       | -                 | -        | -      | T2EX    | T2        | FFH            |

|                    |                         |                   | A7     | A6    | A5      | A4                | A3       | A2     | A1      | A0        |                |

| P2*                | Port 2                  | A0H               | AD15   | AD14  | AD13    | AD12              | AD11     | AD10   | AD9     | AD8       | FFH            |

| . –                |                         |                   | B7     | B6    | B5      | B4                | B3       | B2     | B1      | B0        | 1              |

| P3*                | Port 3                  | B0H               | RD     | WR    | T1      | ТО                | INT1     | INTO   | TxD     | RxD       | FFH            |

| 10                 |                         | Don               |        | WIX   |         | 10                |          | iiiio  |         | TOD       |                |

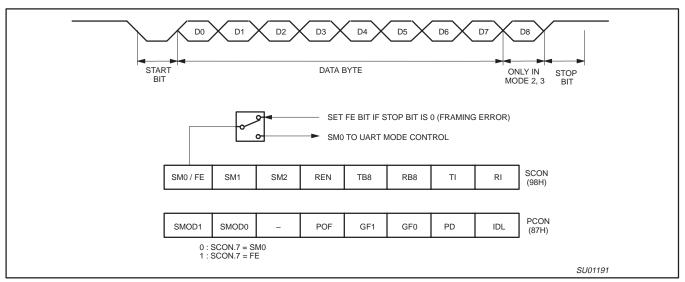

| PCON# <sup>1</sup> | Power Control           | 87H               | SMOD1  | SMOD0 | -       | POF <sup>2</sup>  | GF1      | GF0    | PD      | IDL       | 00xx0000B      |

|                    |                         |                   | D7     | D6    | D5      | D4                | D3       | D2     | D1      | D0        |                |

| PSW*               | Program Status Word     | D0H               | CY     | AC    | F0      | RS1               | RS0      | OV     | -       | P         | 000000x0B      |

| RCAP2H#            | Timer 2 Capture High    | CBH               | 01     | 7.0   | 10      |                   | 1100     | 0.     |         |           | 00H            |

| RCAP2L#            | Timer 2 Capture Low     | CAH               |        |       |         |                   |          |        |         |           | 00H            |

| SADDR#             | Slave Address           | A9H               |        |       |         |                   |          |        |         |           | 00H            |

| SADEN#             | Slave Address Mask      | B9H               |        |       |         |                   |          |        |         |           | 00H            |

| SBUF               | Serial Data Buffer      | 99H               |        |       |         |                   |          |        |         |           | xxxxxxxB       |

|                    |                         |                   | 9F     | 9E    | 9D      | 9C                | 9B       | 9A     | 99      | 98        |                |

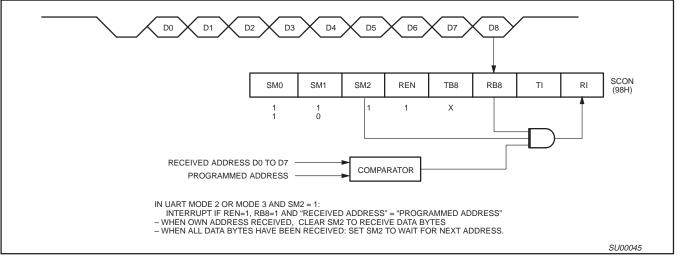

| SCON*              | Serial Control          | 98H               | SM0/FE | SM1   | SM2     | REN               | TB8      | RB8    | TI      | RI        | 00H            |

| SP                 | Stack Pointer           | 81H               |        |       |         |                   | 1        |        |         |           | 07H            |

|                    |                         |                   | 8F     | 8E    | 8D      | 8C                | 8B       | 8A     | 89      | 88        |                |

| TCON*              | Timer Control           | 88H               | TF1    | TR1   | TF0     | TR0               | IE1      | IT1    | IE0     | IT0       | 00H            |

|                    |                         |                   | CF     | CE    | CD      | СС                | СВ       | СА     | C9      | C8        | 1              |

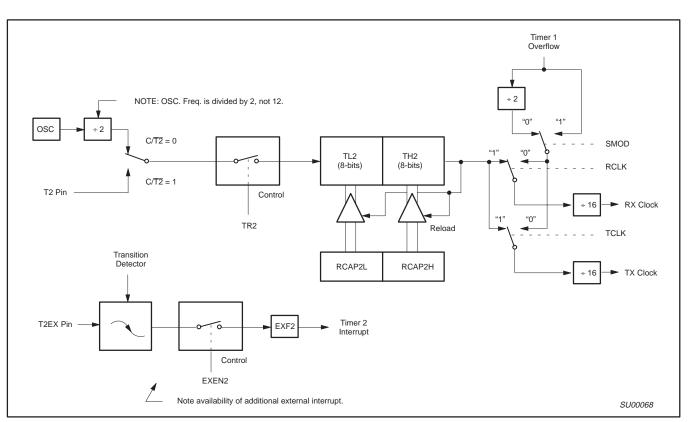

| T2CON*             | Timer 2 Control         | C8H               | TF2    | EXF2  | RCLK    | TCLK              | EXEN2    | TR2    | C/T2    | CP/RL2    | 00H            |

| T2MOD#             | Timer 2 Mode Control    | C9H               | _      | _     | _       | _                 | -        | -      | T2OE    | DCEN      | xxxxxx00B      |

| TH0                | Timer High 0            | 8CH               |        |       |         |                   |          |        |         |           | 00H            |

| TH1                | Timer High 1            | 8DH               |        |       |         |                   |          |        |         |           | 00H            |

| TH2#               | Timer High 2            | CDH               |        |       |         |                   |          |        |         |           | 00H            |

| TL0                | Timer Low 0             | 8AH               |        |       |         |                   |          |        |         |           | 00H            |

| TL1                | Timer Low 1             | 8BH               |        |       |         |                   |          |        |         |           | 00H            |

| TL2#               | Timer Low 2             | ССН               |        | _ =   |         |                   | L        |        | 1       |           | 00H            |

| TMOD               | Timer Mode              | 89H               | GATE   | C/T   | M1      | M0                | GATE     | C/T    | M1      | MO        | 00H            |

\* SFRs are bit addressable.

# SFRs are modified from or added to the 80C51 SFRs.

- Reserved bits.

1. Reset value depends on reset source.

2. Bit will not be affected by Reset.

3. LPEP - Low Power OTP-EPROM only operation.

#### Table 2. 8XC51FA/FB/FC, 8XC51RA+/RB+/RC+/RD+ Special Function Registers

| SYMBOL              | DESCRIPTION                                                     | DIRECT<br>ADDRESS | BIT A<br>MSB | DDRESS    | , SYMBO   | L, OR AL          | TERNATIV  | 'E PORT     | FUNCTIO              | N<br>LSB  | RESET<br>VALUE |

|---------------------|-----------------------------------------------------------------|-------------------|--------------|-----------|-----------|-------------------|-----------|-------------|----------------------|-----------|----------------|

| ACC*                | Accumulator                                                     | E0H               | E7           | E6        | E5        | E4                | E3        | E2          | E1                   | E0        | 00H            |

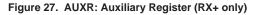

| AUXR#               | Auxiliary                                                       | 8EH               | -            | -         | -         | -                 | -         | -           | EXTRAM<br>(RX+ only) | AO        | xxxxxx00B      |

| AUXR1#              | Auxiliary 1                                                     | A2H               | -            | -         | -         | LPEP <sup>3</sup> | GF3       | 0           | -                    | DPS       | xxx0xxx0B      |

| B*                  | B register                                                      | F0H               | F7           | F6        | F5        | F4                | F3        | F2          | F1                   | F0        | 00H            |

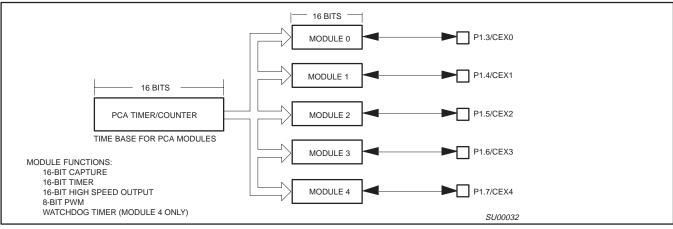

| CCAP0H#             | Module 0 Capture High                                           | FAH               |              |           |           |                   |           |             |                      |           | xxxxxxxB       |

| CCAP1H#             | Module 1 Capture High                                           | FBH               |              |           |           |                   |           |             |                      |           | xxxxxxxB       |

| CCAP2H#             | Module 2 Capture High                                           | FCH               |              |           |           |                   |           |             |                      |           | xxxxxxxB       |

| CCAP3H#             | Module 3 Capture High                                           | FDH               |              |           |           |                   |           |             |                      |           | xxxxxxxB       |

| CCAP4H#             | Module 4 Capture High                                           | FEH               |              |           |           |                   |           |             |                      |           | xxxxxxxB       |

| CCAP0L#             | Module 0 Capture Low                                            | EAH               |              |           |           |                   |           |             |                      |           | xxxxxxxB       |

| CCAP1L#             | Module 1 Capture Low                                            | EBH               |              |           |           |                   |           |             |                      |           | xxxxxxxB       |

| CCAP2L#             | Module 2 Capture Low                                            | ECH               |              |           |           |                   |           |             |                      |           | xxxxxxxB       |

| CCAP3L#             | Module 3 Capture Low                                            | EDH               |              |           |           |                   |           |             |                      |           | xxxxxxxB       |

| CCAP4L#             | Module 4 Capture Low                                            | EEH               |              |           |           |                   |           |             |                      |           | xxxxxxxB       |

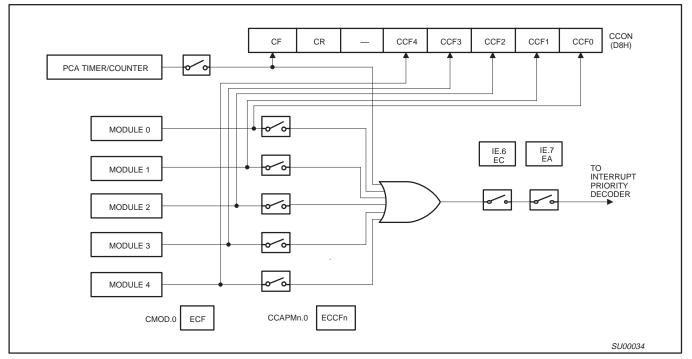

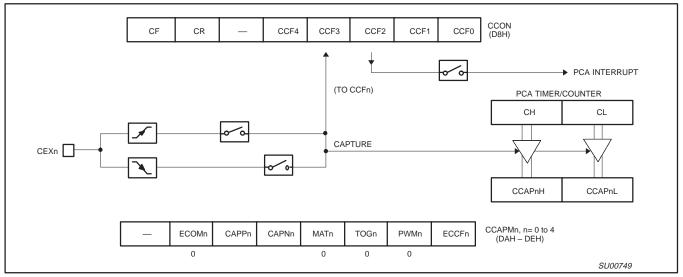

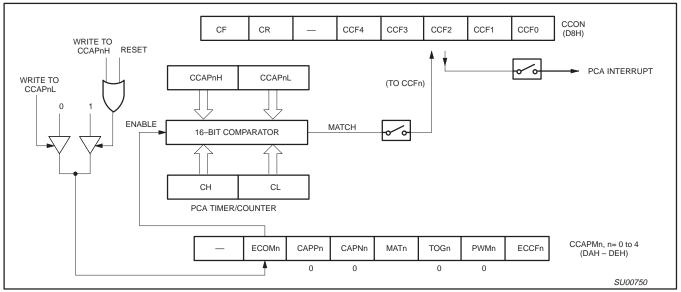

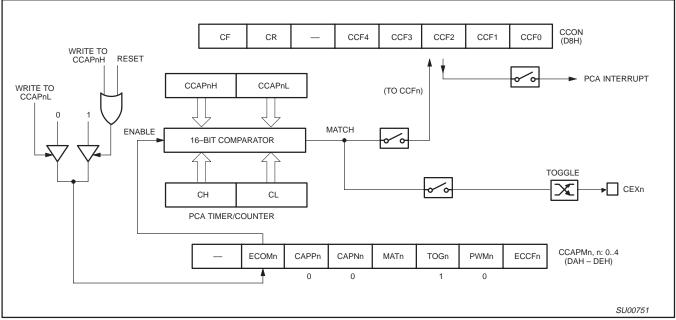

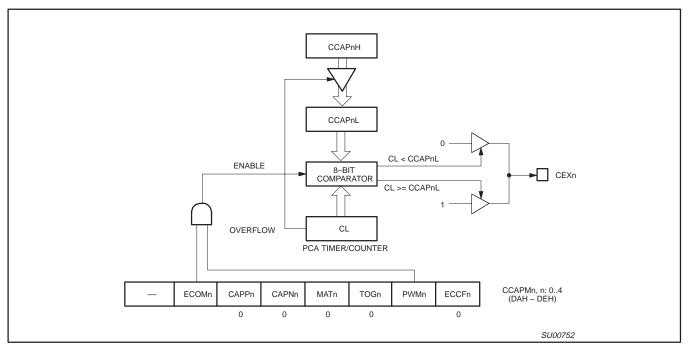

| CCAPM0#             | Module 0 Mode                                                   | DAH               | -            | ECOM      | CAPP      | CAPN              | MAT       | TOG         | PWM                  | ECCF      | x0000000E      |

| CCAPM1#             | Module 1 Mode                                                   | DBH               | -            | ECOM      | CAPP      | CAPN              | MAT       | TOG         | PWM                  | ECCF      | x0000000E      |

| CCAPM2#             | Module 2 Mode                                                   | DCH               | -            | ECOM      | CAPP      | CAPN              | MAT       | TOG         | PWM                  | ECCF      | x000000B       |

| CCAPM3#             | Module 3 Mode                                                   | DDH               | -            | ECOM      | CAPP      | CAPN              | MAT       | TOG         | PWM                  | ECCF      | x0000000E      |

| CCAPM4#             | Module 4 Mode                                                   | DEH               | -            | ECOM      | CAPP      | CAPN              | MAT       | TOG         | PWM                  | ECCF      | x0000000E      |

|                     |                                                                 |                   | DF           | DE        | DD        | DC                | DB        | DA          | D9                   | D8        |                |

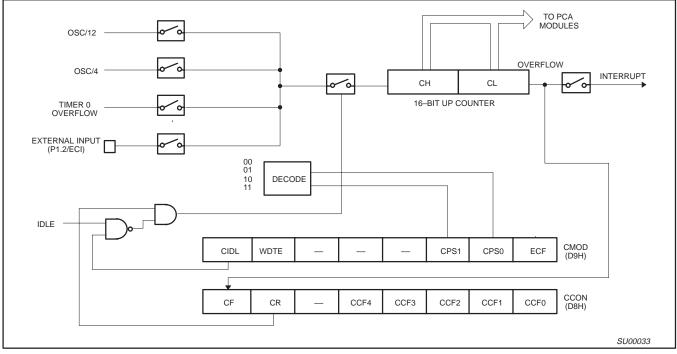

| CCON*#              | PCA Counter Control                                             | D8H               | CF           | CR        | -         | CCF4              | CCF3      | CCF2        | CCF1                 | CCF0      | 00x00000E      |

| CH#<br>CL#          | PCA Counter High<br>PCA Counter Low                             | F9H<br>E9H        |              |           |           | •                 | •         |             |                      |           | 00H<br>00H     |

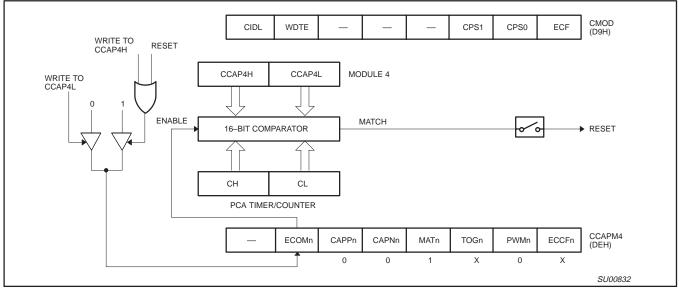

| CMOD#               | PCA Counter Mode                                                | D9H               | CIDL         | WDTE      | -         | -                 | -         | CPS1        | CPS0                 | ECF       | 00xxx000B      |

| DPTR:<br>DPH<br>DPL | Data Pointer (2 bytes)<br>Data Pointer High<br>Data Pointer Low | 83H<br>82H        | 45           |           |           |                   |           |             | 4.0                  | 4.0       | 00H<br>00H     |

| . <b></b> +         | later wat Eachte                                                | 4.011             | AF           | AE        | AD        | AC                | AB        | AA          | A9                   | A8        | 0011           |

| IE*                 | Interrupt Enable                                                | A8H               | EA           | EC        | ET2       | ES                | ET1       | EX1         | ET0                  | EX0       | 00H            |

| IP*                 | Interrupt Priority                                              | B8H               | BF<br>_      | BE<br>PPC | BD<br>PT2 | BC<br>PS          | BB<br>PT1 | BA<br>PX1   | B9<br>PT0            | B8<br>PX0 | x0000000E      |

|                     | Interrupt Frionty                                               | Боп               | <br>B7       | B6        | B5        | РЗ<br>В4          | B3        | B2          | B1                   | B0        |                |

| IPH#                | Interrupt Priority High                                         | B7H               |              | PPCH      | PT2H      | PSH               | PT1H      | PX1H        | РТОН                 | PX0H      | x0000000E      |

|                     | interrupt i nenty i ngri                                        | Bill              | 87           | 86        | 85        | 84                | 83        | 82          | 81                   | 80        |                |

| P0*                 | Port 0                                                          | 80H               | AD7          | AD6       | AD5       | AD4               | AD3       | AD2         | AD1                  | AD0       | FFH            |

|                     |                                                                 | 0011              | 97           | 96        | 95        | 94                | 93        | 92          | 91                   | 90        |                |

| P1*                 | Port 1                                                          | 90H               | CEX4         | CEX3      | CEX2      | CEX1              | CEX0      | ECI         | T2EX                 | T2        | FFH            |

|                     |                                                                 |                   | A7           | A6        | A5        | A4                | A3        | A2          | A1                   | A0        |                |

| P2*                 | Port 2                                                          | A0H               | AD15         | AD14      | AD13      | AD12              | AD11      | AD10        | AD9                  | AD8       | FFH            |

|                     |                                                                 |                   | B7           | B6        | B5        | B4                | B3        | B2          | B1                   | B0        | 1              |

| P3*                 | Port 3                                                          | B0H               | RD           | WR        | T1        | TO                | INT1      | <b>INTO</b> | TxD                  | RxD       | FFH            |

|                     |                                                                 |                   |              |           |           |                   |           |             |                      |           | 1              |

| PCON#1              | Power Control                                                   | 87H               | SMOD1        | SMOD0     | _         | POF <sup>2</sup>  | GF1       | GF0         | PD                   | IDL       | 00xx0000B      |

# SFRs are modified from or added to the 80C51 SFRs.

- Reserved bits.

1. Reset value depends on reset source.

2. Bit will not be affected by Reset.

3. LPEP - Low Power OTP-EPROM only operation.

Downloaded from Arrow.com.

#### 8XC54/58 8XC51FA/FB/FC/80C51FA 8XC51RA+/RB+/RC+/RD+/80C51RA+

# Table 2. 8XC51FA/FB/FC, 8XC51RA+/RB+/RC+/RD+ Special Function Registers (Continued)

| SYMBOL      | DESCRIPTION                            | DIRECT<br>ADDRESS | BIT A<br>MSB | ADDRESS | , SYMBO | L, OR AL | TERNATIV | E PORT | FUNCTIO | ON<br>LSB | RESET<br>VALUE |

|-------------|----------------------------------------|-------------------|--------------|---------|---------|----------|----------|--------|---------|-----------|----------------|

|             |                                        |                   | D7           | D6      | D5      | D4       | D3       | D2     | D1      | D0        |                |

| PSW*        | Program Status Word                    | D0H               | CY           | AC      | F0      | RS1      | RS0      | OV     | -       | Р         | 000000x0B      |

| RACAP2H#    | Timer 2 Capture High                   | СВН               |              |         |         |          |          |        |         |           | 00H            |

| RACAP2L#    | Timer 2 Capture Low                    | CAH               |              |         |         |          |          |        |         |           | 00H            |

| SADDR#      | Slave Address                          | A9H               |              |         |         |          |          |        |         |           | 00H            |

| SADEN#      | Slave Address Mask                     | B9H               |              |         |         |          |          |        |         |           | 00H            |

| SBUF        | Serial Data Buffer                     | 99H               |              |         |         |          |          |        |         |           | xxxxxxxB       |

|             |                                        |                   | 9F           | 9E      | 9D      | 9C       | 9B       | 9A     | 99      | 98        |                |

| SCON*       | Serial Control                         | 98H               | SM0/FE       | SM1     | SM2     | REN      | TB8      | RB8    | TI      | RI        | 00H            |

| SP          | Stack Pointer                          | 81H               |              |         |         |          |          |        |         |           | 07H            |

|             |                                        |                   | 8F           | 8E      | 8D      | 8C       | 8B       | 8A     | 89      | 88        |                |

| TCON*       | Timer Control                          | 88H               | TF1          | TR1     | TF0     | TR0      | IE1      | IT1    | IE0     | IT0       | 00H            |

|             |                                        |                   | CF           | CE      | CD      | СС       | СВ       | CA     | C9      | C8        |                |

| T2CON*      | Timer 2 Control                        | C8H               | TF2          | EXF2    | RCLK    | TCLK     | EXEN2    | TR2    | C/T2    | CP/RL2    | 00H            |

| T2MOD#      | Timer 2 Mode Control                   | С9Н               | _            | -       | -       | -        | -        | -      | T2OE    | DCEN      | xxxxxx00B      |

| TH0         | Timer High 0                           | 8CH               |              |         |         |          |          |        |         |           | 00H            |

| TH1         | Timer High 1                           | 8DH               |              |         |         |          |          |        |         |           | 00H            |

| TH2#        | Timer High 2                           | CDH               |              |         |         |          |          |        |         |           | 00H            |

| TL0         | Timer Low 0                            | 8AH               |              |         |         |          |          |        |         |           | 00H            |

| TL1<br>TL2# | Timer Low 1<br>Timer Low 2             | 8BH<br>CCH        |              |         |         |          |          |        |         |           | 00H<br>00H     |

| 1 L2#       |                                        | ССП               |              |         |         |          |          |        |         |           | 000            |

| TMOD        | Timer Mode                             | 89H               | GATE         | C/T     | M1      | M0       | GATE     | C/T    | M1      | MO        | 00H            |

| WDTRST      | HDW Watchdog<br>Timer Reset (RX+ only) | 0A6H              |              |         |         |          |          |        |         |           |                |

\* SFRs are bit addressable.

# SFRs are modified from or added to the 80C51 SFRs.

Reserved bits.

# **OSCILLATOR CHARACTERISTICS**

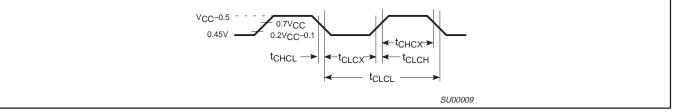

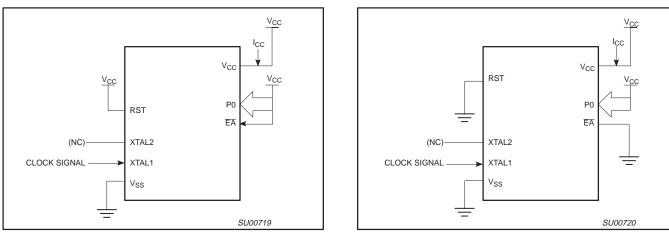

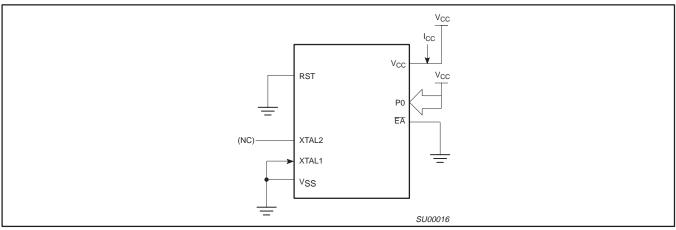

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier. The pins can be configured for use as an on-chip oscillator.

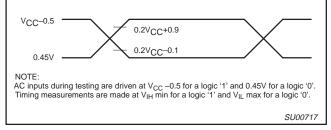

To drive the device from an external clock source, XTAL1 should be driven while XTAL2 is left unconnected. There are no requirements on the duty cycle of the external clock signal, because the input to the internal clock circuitry is through a divide-by-two flip-flop. However, minimum and maximum high and low times specified in the data sheet must be observed.

# RESET

A reset is accomplished by holding the RST pin high for at least two machine cycles (24 oscillator periods), while the oscillator is running. To insure a good power-on reset, the RST pin must be high long enough to allow the oscillator time to start up (normally a few milliseconds) plus two machine cycles. At power-on, the voltage on  $V_{CC}$  and RST must come up at the same time for a proper start-up. Ports 1, 2, and 3 will asynchronously be driven to their reset condition when a voltage above  $V_{IH1}$  (min.) is applied to RESET.

# LOW POWER MODES

#### Stop Clock Mode

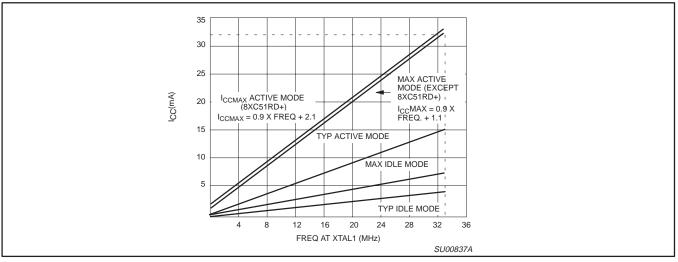

The static design enables the clock speed to be reduced down to 0 MHz (stopped). When the oscillator is stopped, the RAM and Special Function Registers retain their values. This mode allows step-by-step utilization and permits reduced system power consumption by lowering the clock frequency down to any value. For lowest power consumption the Power Down mode is suggested.

#### Idle Mode

In the idle mode (see Table 3), the CPU puts itself to sleep while all of the on-chip peripherals stay active. The instruction to invoke the idle mode is the last instruction executed in the normal operating mode before the idle mode is activated. The CPU contents, the on-chip RAM, and all of the special function registers remain intact during this mode. The idle mode can be terminated either by any enabled interrupt (at which time the process is picked up at the interrupt service routine and continued), or by a hardware reset which starts the processor in the same manner as a power-on reset.

#### **Power-Down Mode**

To save even more power, a Power Down mode (see Table 3) can be invoked by software. In this mode, the oscillator is stopped and the instruction that invoked Power Down is the last instruction executed. The on-chip RAM and Special Function Registers retain their values down to 2.0V and care must be taken to return  $V_{CC}$  to the minimum specified operating voltages before the Power Down Mode is terminated.

Either a hardware reset or external interrupt can be used to exit from Power Down. Reset redefines all the SFRs but does not change the on-chip RAM. An external interrupt allows both the SFRs and the on-chip RAM to retain their values.

To properly terminate Power Down the reset or external interrupt should not be executed before  $V_{CC}$  is restored to its normal operating level and must be held active long enough for the oscillator to restart and stabilize (normally less than 10ms).

With an external interrupt, INT0 and INT1 must be enabled and configured as level-sensitive. Holding the pin low restarts the oscillator but bringing the pin back high completes the exit. Once the interrupt is serviced, the next instruction to be executed after RETI will be the one following the instruction that put the device into Power Down.

#### LPEP

The LPEP bit (AUXR.4), only needs to be set for applications operating at  $V_{CC}$  less than 4V.

#### **POWER OFF FLAG**