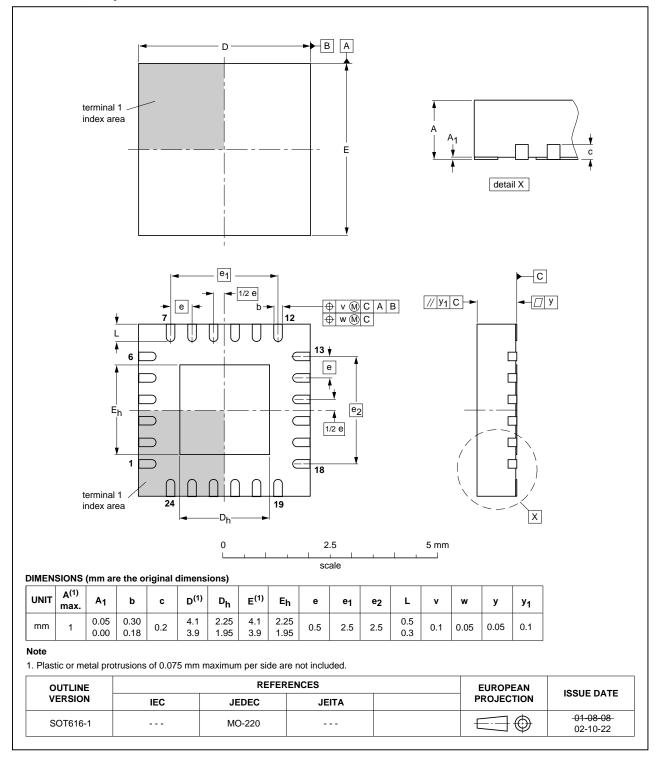

■ Available in a small HVQFN24 (4 × 4 mm<sup>2</sup>) halogen-free and lead-free package

# 3. Applications

- Mobile phone

- Digital camera

- Personal digital assistant

- Digital video recorder

# 4. Ordering information

#### Table 1. Ordering information

| Commercial product code | Package description                    | Packing                           | Minimum sellable quantity |

|-------------------------|----------------------------------------|-----------------------------------|---------------------------|

| ISP1301BSTS             | HVQFN24; $4 \times 4 \times 0.85$ mm   | 7 inch tape and reel non-dry pack | 1500 pieces               |

| ISP1301BSFA             | HVQFN24, 4 $\times$ 4 $\times$ 0.85 mm | single tray non-dry pack          | 490 pieces                |

**ISP1301**

**USB OTG transceiver**

# 5. Block diagram

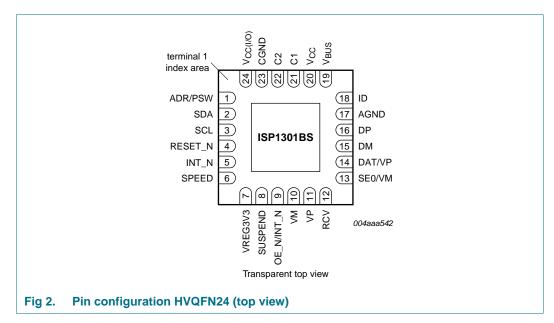

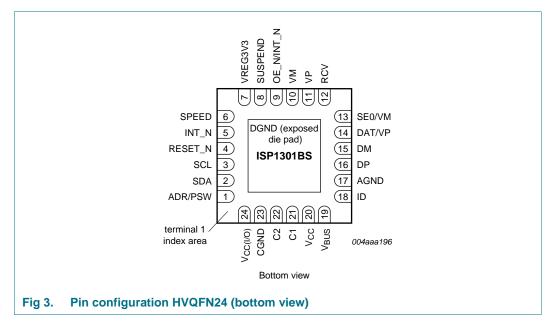

# 6. Pinning information

### 6.1 Pinning

# 6.2 Pin description

|                       | in descrip |                     |                |                                                                                                                                                                                                                                                                                |

|-----------------------|------------|---------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol <sup>[1]</sup> | Pin        | Type <sup>[2]</sup> | Reset<br>state | Description <sup>[3]</sup>                                                                                                                                                                                                                                                     |

| ADR/PSW               | 1          | I/O                 | high-Z         | ADR input — sets the least-significant l <sup>2</sup> C-bus<br>address bit of the ISP1301; latched-on reset<br>(including power-on reset)<br><b>PSW output</b> — enables or disables the external<br>charge pump after reset<br>bidirectional; push-pull input; 3-state output |

| SDA                   | 2          | I/OD                | high-Z         | serial I <sup>2</sup> C-bus data input and output<br>bidirectional; push-pull input; open-drain output                                                                                                                                                                         |

| SCL                   | 3          | I/OD                | high-Z         | serial I <sup>2</sup> C-bus clock input and output                                                                                                                                                                                                                             |

| RESET_N               | 4          | I                   | -              | bidirectional; push-pull input; open-drain output<br>asynchronous reset; active LOW                                                                                                                                                                                            |

| INT_N                 | 5          | OD                  | high-Z         | push-pull input<br>interrupt output; active LOW                                                                                                                                                                                                                                |

|                       |            |                     |                | open-drain output                                                                                                                                                                                                                                                              |

| SPEED                 | 6          | I                   | -              | speed selection input for the ATX; effective when<br>bit SPD_SUSP_CTRL = 0:                                                                                                                                                                                                    |

|                       |            |                     |                | LOW: low-speed                                                                                                                                                                                                                                                                 |

|                       |            |                     |                | HIGH: full-speed                                                                                                                                                                                                                                                               |

|                       |            |                     |                | push-pull input                                                                                                                                                                                                                                                                |

| VREG3V3               | 7          | Ρ                   | -              | output of the internal voltage regulator; an external decoupling capacitor of 0.1 $\mu F$ is required                                                                                                                                                                          |

| SUSPEND               | 8          | I                   | -              | suspend selection input for the ATX; effective when bit SPD_SUSP_CTRL = 0:                                                                                                                                                                                                     |

|                       |            |                     |                | <ul> <li>LOW: normal operating</li> </ul>                                                                                                                                                                                                                                      |

|                       |            |                     |                | HIGH: suspend                                                                                                                                                                                                                                                                  |

|                       |            |                     |                | push-pull input                                                                                                                                                                                                                                                                |

| OE_N/<br>INT_N        | 9          | I/O                 | high-Z         | <b>OE_N input</b> — enables driving DP and DM when in USB mode                                                                                                                                                                                                                 |

|                       |            |                     |                | <pre>INT_N output — interrupt (push pull) when suspended and bit OE_INT_EN = 1</pre>                                                                                                                                                                                           |

|                       |            |                     |                | bidirectional; push-pull input; 3-state output                                                                                                                                                                                                                                 |

| VM                    | 10         | 0                   | -              | single-ended DM receiver output push-pull output                                                                                                                                                                                                                               |

| VP                    | 11         | 0                   | -              | single-ended DP receiver output<br>push-pull output                                                                                                                                                                                                                            |

| RCV                   | 12         | 0                   | 0              | differential receiver output; reflects the differential value of DP and DM                                                                                                                                                                                                     |

|                       |            |                     |                | push-pull output                                                                                                                                                                                                                                                               |

| SE0/VM                | 13         | I/O                 | <u>[4]</u>     | <b>SE0 (input and output)</b> — SE0 functions in DAT_SE0 USB mode                                                                                                                                                                                                              |

|                       |            |                     |                | VM (input and output) — VM functions in VP_VM                                                                                                                                                                                                                                  |

|                       |            |                     |                | USB mode<br>bidirectional; push-pull input; 3-state output                                                                                                                                                                                                                     |

ISP1301\_5

# **ISP1301**

#### **USB OTG transceiver**

| Symbol <sup>[1]</sup> | Pin                | Type <sup>[2]</sup> | Reset<br>state | Description <sup>[3]</sup>                                                                                                    |

|-----------------------|--------------------|---------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------|

| DAT/VP                | 14                 | I/O                 | - <u>[4]</u>   | DAT (input and output) — DAT functions in<br>DAT_SE0 USB mode                                                                 |

|                       |                    |                     |                | VP (input and output) — VP functions in VP_VM USB mode                                                                        |

|                       |                    |                     |                | bidirectional; push-pull input; 3-state output                                                                                |

| DM                    | 15                 | AI/O                | -              | USB data minus pin (D–)                                                                                                       |

| DP                    | 16                 | AI/O                | -              | USB data plus pin (D+)                                                                                                        |

| AGND                  | 17                 | Р                   | -              | analog ground                                                                                                                 |

| ID                    | 18                 | AI/O                | -              | identification detector input and output; connected to the ID pin of the USB mini receptacle                                  |

| V <sub>BUS</sub>      | 19                 | AI/O                | -              | $V_{BUS}$ line input and output of the USB interface; place an external decoupling capacitor of 0.1 $\mu F$ close to this pin |

| V <sub>CC</sub>       | 20                 | Р                   | -              | supply voltage (2.7 V to 4.5 V)                                                                                               |

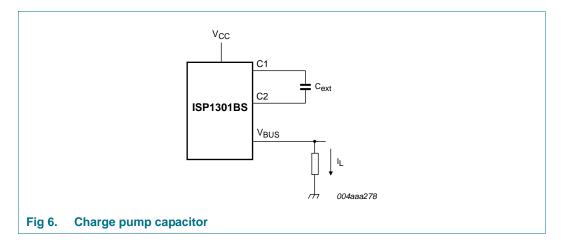

| C1                    | 21                 | AI/O                | -              | charge pump capacitor pin 1; typically use a 100 nF capacitor between pins C1 and C2                                          |

| C2                    | 22                 | AI/O                | -              | charge pump capacitor pin 2; typically use a 100 nF capacitor between pins C1 and C2                                          |

| CGND                  | 23                 | Р                   | -              | ground for the charge pump                                                                                                    |

| V <sub>CC(I/O)</sub>  | 24                 | Ρ                   | -              | supply voltage for the interface logic signals (1.65 V to 3.6 V)                                                              |

| DGND                  | exposed<br>die pad | Ρ                   | -              | digital ground                                                                                                                |

#### Table 2 Pin description continued

[1] Symbol names ending with underscore N (for example, NAME\_N) indicate active LOW signals.

[2] I = input; O = output; I/O = digital input/output; OD = open-drain output; AI/O = analog input/output; P = power or ground pin.

[3] A detailed description of these pins can be found in <u>Section 7.10</u>.

[4] High-Z when pin OE\_N/INT\_N is LOW. Driven LOW when pin OE\_N/INT\_N is HIGH.

# 7. Functional description

## 7.1 Serial controller

The serial controller includes the following functions:

- I<sup>2</sup>C-bus slave interface

- Interrupt generator

- Mode Control registers

- OTG registers

- Interrupt related registers

- Device identification registers

The serial controller acts as an  ${\rm I}^2{\rm C}\mbox{-}{\rm bus}$  slave, and uses the SCL and SDA pins to communicate with the OTG Controller.

For details on serial controller, see <u>Section 10</u>.

# 7.2 V<sub>BUS</sub> charge pump

The charge pump supplies current to the  $V_{\text{BUS}}$  line. It can operate in any of the following modes:

- Output 5 V at current greater than 8 mA

- Pull-up  $V_{BUS}$  to 3.3 V through a resistor ( $R_{UP(VBUS)}$ ) to initiate  $V_{BUS}$  pulsing SRP

- Pull-down V\_{BUS} to ground through a resistor (R\_{DN(VBUS)}) to discharge V\_{BUS} before initiating SRP

### 7.3 V<sub>BUS</sub> comparators

$V_{\text{BUS}}$  comparators provide indications regarding the voltage level on  $V_{\text{BUS}}.$

### 7.3.1 $V_{BUS}$ valid comparator

This comparator is used by an A-device to determine whether the voltage on  $V_{BUS}$  is at a valid level for operation. The minimum threshold for the  $V_{BUS}$  valid comparator is 4.4 V. Any voltage on  $V_{BUS}$  below this threshold is considered to be a fault. During power-up, it is expected that the comparator output will be ignored.

### 7.3.2 Session valid comparator

The session valid comparator is a TTL-level input that determines when  $V_{BUS}$  is high enough for a session to start. Both the A-device and the B-device use this comparator to detect when a session is started. The A-device also uses this comparator to indicate when a session is completed. The session valid threshold of the ISP1301 is between 0.8 V and 2.0 V.

### 7.3.3 Session end comparator

The session end comparator determines when  $V_{\text{BUS}}$  is below the B-device session end threshold of 0.2 V to 0.8 V.

### 7.4 ID detector

In either active or suspended power mode, the ID detector senses the condition of the ID line and differentiates between the following three conditions:

- Pin ID is floating; bit ID\_FLOAT = 1

- Pin ID is shorted to ground; bit ID\_GND = 1

- Pin ID is connected to ground through resistor R<sub>ACC\_ID</sub>; bit ID\_FLOAT = 0 and bit ID\_GND = 0

The ID detector also has a switch that can be used to ground pin ID. This switch is controlled by bit ID\_PULLDOWN in the serial controller.

### 7.5 Pull-up and pull-down resistors

The pull-up and pull-down resistors include the following switchable resistors:

- Pin DP pull-up

- Pin DP pull-down

- Pin DM pull-up

- Pin DM pull-down

The pull-up resistor is a context variable as described in the *ECN\_27%\_Resistor* document. The variable pull-up resistor hardware is implemented to meet the USB ECN\_27% specification.

### 7.6 Analog USB Transceiver (ATX)

The behavior of the USB transceiver depends on operation mode of the ISP1301:

- In USB mode, the USB transceiver block performs USB full-speed or low-speed transceiver functions. This includes differential driver, differential receiver and single-ended receivers.

- In transparent general purpose buffer mode or UART mode, USB transceiver block functions as a level shifter between pins DAT/VP and SE0/VM and pins DP and DM.

### 7.7 3.3 V DC-DC regulator

The built-in 3.3 V DC-DC regulator conditions the supply voltage (V<sub>CC</sub>) for use in the ISP1301:

- V<sub>CC</sub> = 3.6 V to 4.5 V: the regulator will output 3.3 V  $\pm$  10 %

- V<sub>CC</sub> < 3.6 V: the regulator will be bypassed

The output of the regulator can be monitored on the VREG3V3 pin.

### 7.8 Carkit interrupt detector

The carkit interrupt detector is a comparator that detects when the DP line is below the carkit interrupt threshold  $V_{PH_{CR_{INT}}}$  (0.4 V to 0.6 V). The carkit interrupt detector is enabled in audio mode only (bit AUDIO\_EN = 1).

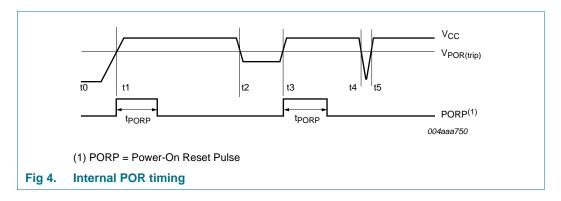

# 7.9 Power-On Reset (POR)

When  $V_{CC}$  is powered on, an internal POR is generated. The internal POR pulse width (t<sub>PORP</sub>) will be typically 200 ns. The pulse is started when  $V_{CC}$  rises above  $V_{POR(trip)}$ .

The POR function can be explained by viewing dips at t2 to t3 and t4 to t5 on the  $V_{CC}$  curve (Figure 4).

t0 — The internal POR starts with a LOW level.

t1 — The detector will see the passing of the trip level and a delay element will add another  $t_{PORP}$  before it drops to LOW.

t2-t3 — The internal POR pulse will be generated whenever  $V_{CC}$  drops below  $V_{POR(trip)}$  for more than 11  $\mu s.$

t4-t5 — The dip is too short (< 11  $\mu s)$  and the internal POR pulse will not react and will remain LOW.

### 7.10 Detailed description of pins

### 7.10.1 ADR/PSW

The ADR/PSW pin has two functions. On reset (including power-on reset), the level on this pin is latched as ADR\_REG, which represents the Least Significant Bit (LSB) of the I<sup>2</sup>C-bus address of the ISP1301. If bit ADR\_REG = 0, the I<sup>2</sup>C-bus address for the ISP1301 is 010 1100 (2Ch); if bit ADR\_REG = 1, the I<sup>2</sup>C-bus address for the ISP1301 is 010 1101 (2Ch).

After reset, the ADR/PSW pin can be programmed as an output. If in the Mode Control 2 register bit  $PSW_OE = 1$ , then the ADR/PSW output will be enabled. The logic level will be determined by bit ADR\_REG. If bit ADR\_REG = 0, then the ADR/PSW pin will be driven HIGH. If bit ADR\_REG = 1, then the ADR/PSW pin will be driven LOW.

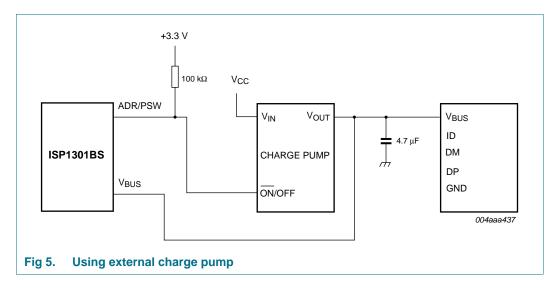

The ADR/PSW pin can be used to turn on or off the external charge pump. The ISP1301 built-in charge pump supports V<sub>BUS</sub> current at 8 mA. If the application needs more current support (for example, 50 mA), an external charge pump may be needed. In this case, the ADR/PSW pin can act as a power switch for the external charge pump. Figure 5 shows an example of using external charge pump.

**ISP1301**

**USB OTG transceiver**

#### 7.10.2 SCL and SDA

The SCL (serial clock) and SDA (serial data) signals implement a two-wire serial I<sup>2</sup>C-bus.

#### 7.10.3 RESET\_N

Active LOW asynchronous reset for all digital logic. Either connect this pin to  $V_{CC(I/O)}$  for power-on reset or apply a minimum of 10  $\mu$ s LOW pulse for hardware reset.

#### 7.10.4 INT\_N

The INT\_N (interrupt) pin is asserted while an interrupt condition exists. It is de-asserted when the Interrupt Latch register is cleared. The INT\_N pin is open-drain, and, therefore, can be connected using a wired-AND with other interrupt signals.

#### 7.10.5 OE\_N/INT\_N

Pin OE\_N/INT\_N is normally an input to the ISP1301.

When bit TRANSP\_EN = 0 and bit UART\_EN = 0, the OE\_N/INT\_N pin controls the direction of DAT/VP, SE0/VM, DP and DM as indicated in Table 4.

When suspended (either pin SUSPEND = HIGH or bit SUSPEND\_REG = 1) and bit  $OE_INT_EN = 1$ , pin  $OE_N/INT_N$  becomes a push-pull output (active LOW) to indicate the interrupt condition.

#### 7.10.6 SE0/VM, DAT/VP, RCV, VM and VP

The ISP1301 transmits USB data on the USB line under the following conditions:

- Bit TRANSP\_EN = 0

- Bit UART\_EN = 0

- Pin OE\_N/INT\_N = LOW

<u>Table 10</u> shows the operation of the SE0/VM and DAT/VP pins during the transmit operation. The RCV pin is not used during transmit.

The ISP1301 receives USB data from the USB line under the following conditions:

ISP1301\_5 Product data sheet

- Bit TRANSP\_EN = 0

- Bit UART\_EN = 0

- Pin OE\_N/INT\_N = HIGH

Table 12 shows the operation of the SE0/VM, DAT/VP and RCV pins during the receive operation.

The VP and VM pins are single-ended receiver outputs of the DP and DM pins, respectively.

#### 7.10.7 DP and DM

The DP (data plus) and DM (data minus) pins implement the USB data signals. When in transparent general-purpose buffer mode, the ISP1301 operates as a level shifter between the (DAT/VP, SE0/VM) and (DP, DM) pins.

### 7.10.8 ID

The ID (identification) pin is connected to the ID pin on the USB mini receptacle. An internal pull-up resistor (to VREG3V3) is connected to this pin. When bit ID\_PULLDOWN is set, the ID pin will be shorted to ground.

### 7.10.9 V<sub>BUS</sub>

This pin acts as an input to the V<sub>BUS</sub> comparator or an output from the charge pump.

When the VBUS\_DRV bit of the OTG Control register is asserted, the ISP1301 tries to drive  $V_{BUS}$  to a voltage of 4.4 V to 5.25 V, with an output current capability of at least 8 mA.

### 7.10.10 V<sub>CC</sub>

This pin is an input and supplies power to the ISP1301. The ISP1301 operates when  $V_{CC}$  is between 2.7 V and 4.5 V.

#### 7.10.11 C1 and C2

The C1 and C2 pins are to connect the flying capacitor of the charge pump. The output current capacity of the charge pump depends on the value of the capacitor. For maximum efficiency, place capacitors as close as possible to the pins.

| Table 5.         | Recommended charge pump capacitor value |                                     |  |  |  |  |  |

|------------------|-----------------------------------------|-------------------------------------|--|--|--|--|--|

| C <sub>ext</sub> | V <sub>CC</sub>                         | I <sub>L</sub> (max) <sup>[1]</sup> |  |  |  |  |  |

| 47 nF            | 2.7 V to 4.5 V                          | 8 mA                                |  |  |  |  |  |

| 100 nF           | 2.7 V to 4.5 V                          | 8 mA                                |  |  |  |  |  |

|                  | 3.0 V to 4.5 V                          | 18 mA                               |  |  |  |  |  |

|                  |                                         |                                     |  |  |  |  |  |

Table 3.

Recommended charge pump capacitor value

[1] For output voltage  $V_{BUS} > 4.7 \text{ V}$  (bit VBUS\_VLD = 1).

# 7.10.12 V<sub>CC(I/O)</sub>

This pin is an input and sets logic thresholds. It also powers the pads of the following logic pins:

- ADR/PSW

- DAT/VP, SE0/VM and RCV

- VM and VP

- INT\_N

- OE\_N/INT\_N

- RESET\_N

- SPEED

- SUSPEND

- SCL and SDA

### 7.10.13 AGND, CGND and DGND

AGND, CGND and DGND are ground pins for analog, charge pump and digital circuits, respectively. These pins can be connected separately or together depending on the system performance requirements.

## 8. Modes of operation

There are four types of modes in the ISP1301:

- Power modes

- Direct I<sup>2</sup>C-bus mode

- USB modes

- Transparent modes

### 8.1 Power modes

Power modes of the ISP1301 are as follows:

- Active power mode: power is on.

- USB suspend mode: to reduce power consumption, the USB differential receiver is powered down.

- Global power-down mode: set bit GLOBAL\_PWR\_DN = 1 of the Mode Control 2 register; the differential transmitter and receiver, clock generator, charge pump, and all biasing circuits are turned off to reduce power consumption to the minimum possible; for details on waking up the clock, see <u>Section 11</u>.

ISP1301\_5 Product data sheet

### 8.2 Direct I<sup>2</sup>C-bus mode

In direct I<sup>2</sup>C-bus mode, an external I<sup>2</sup>C-bus master (OTG Controller) directly communicates with the serial controller through the SCL and SDA lines. The serial controller has a built-in I<sup>2</sup>C-bus slave function.

In this mode, an external I<sup>2</sup>C-bus master can access the internal registers of the device (Status, Control, Interrupt, and so on) through the I<sup>2</sup>C-bus interface.

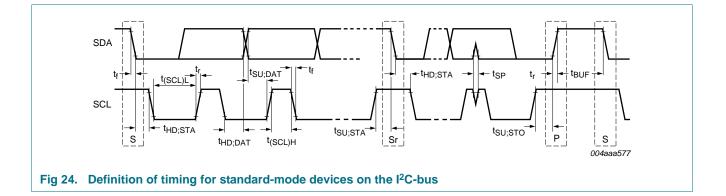

The supported I<sup>2</sup>C-bus bit rate is 100 kbit/s (maximum).

The ISP1301 is in direct I<sup>2</sup>C-bus mode when either bit TRANSP\_EN bit = 0 or pin  $OE_N/INT_N$  is de-asserted.

### 8.3 USB modes

The four USB modes of the ISP1301 are:

- VP\_VM unidirectional mode

- VP\_VM bidirectional mode

- DAT\_SE0 unidirectional mode

- DAT\_SE0 bidirectional mode

In VP\_VM USB mode, the DAT/VP pin is used for the VP function, the SE0/VM pin is used for the VM function, and the RCV pin is used for the RCV function.

In DAT\_SE0 USB mode, the DAT/VP pin is used for the DAT function, the SE0/VM pin is used for the SE0 function, and the RCV pin is not used.

In unidirectional mode, the DAT/VP and SE0/VM pins are always inputs. In bidirectional mode, the direction of these signals depends on the OE\_N/INT\_N input.

Table 6 specifies the functionality of the device during the four USB modes.

The ISP1301 is in USB mode when both the TRANSP\_EN and UART\_EN bits are cleared.

### 8.4 Transparent modes

#### 8.4.1 Transparent general-purpose buffer mode

In transparent general-purpose buffer mode, the DAT/VP and SE0/VM pins are connected to the DP and DM pins, respectively. Using bits TRANSP\_BDIR1 and TRANSP\_BDIR0 of the Mode Control 2 register as specified in <u>Table 8</u>, you can control the direction of data transfer. The ISP1301 is in transparent general-purpose buffer mode if bit TRANSP\_EN = 1 and bit DAT\_SE0 = 1.

#### 8.4.2 Transparent UART mode

When in transparent UART mode, the ATX behaves as two logic level translator between the following pins:

- For the TxD signal: from SE0/VM (V<sub>CC(I/O)</sub> level) to DM (+3.3 V level).

- For the RxD signal: from DP (+3.3 V level) to DAT/VP (V<sub>CC(I/O)</sub> level).

ISP1301\_5 Product data sheet

In UART mode, the OTG Controller is allowed to connect a UART to the DAT/VP and SE0/VM pins of the ISP1301.

UART mode is entered by setting the UART\_EN bit in the Mode Control 1 register. UART mode is equivalent to one of transparent general purpose buffer mode (bit TRANSP\_BDIR1 = 1, bit TRANSP\_BDIR0 = 0).

### 8.4.3 Summary tables

| Mode                                          | USB<br>suspend<br>condition <sup>[1]</sup> | Bit<br>DAT<br>_SE0 | Pin<br>OE_N/<br>INT_N | Bit<br>TRANSP<br>_EN | Bit<br>UART<br>_ EN | Description                                                                                                           |

|-----------------------------------------------|--------------------------------------------|--------------------|-----------------------|----------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------|

| Direct I <sup>2</sup> C-bus mode              |                                            |                    |                       |                      |                     |                                                                                                                       |

| Direct I <sup>2</sup> C-bus mode              | Х                                          | Х                  | Х                     | 0                    | Х                   | -                                                                                                                     |

|                                               | Х                                          | Х                  | HIGH                  | 1                    | Х                   |                                                                                                                       |

|                                               | Х                                          | 1                  | Х                     | 1                    | Х                   |                                                                                                                       |

| USB modes                                     |                                            |                    |                       |                      |                     |                                                                                                                       |

| USB suspend mode                              | 1                                          | Х                  | Х                     | 0                    | 0                   | see <u>Table 5</u> and <u>Table 7</u>                                                                                 |

| USB functional mode                           | 0                                          | Х                  | Х                     | 0                    | 0                   | ATX is fully functional; see Table 6                                                                                  |

| Transparent modes                             |                                            |                    |                       |                      |                     |                                                                                                                       |

| Transparent<br>general-purpose buffer<br>mode | Х                                          | 1                  | Х                     | 1                    | 0                   | ATX is not functional; see Table 8                                                                                    |

| Transparent UART mode                         | X                                          | Х                  | Х                     | Х                    | 1                   | DAT/VP $\leftarrow$ DP (RxD signal of UART)<br>SE0/VM $\rightarrow$ DM (TxD signal of UART);<br>ATX is not functional |

[1] Conditions:

a) bit SPD\_SUSP\_CTRL = 0 and pin SUSPEND = HIGH, or

b) bit SPD\_SUSP\_CTRL = 1 and bit SUSPEND\_REG = 0.

#### Table 5. USB suspend mode: I/O

| Pin              | Function                                                                       |

|------------------|--------------------------------------------------------------------------------|

| DP as output     | can be driven if pin OE_N/INT_N is active LOW, otherwise high-Z <sup>[1]</sup> |

| DM as output     | can be driven if pin OE_N/INT_N is active LOW, otherwise high-Z <sup>[1]</sup> |

| V <sub>BUS</sub> | can be driven depending on bit VBUS_DRV                                        |

| SCL              | connected to SCL I/O of the I <sup>2</sup> C-bus slave                         |

| SDA              | connected to SDA I/O of the I <sup>2</sup> C-bus slave                         |

[1] In USB suspend mode, the ISP1301 can drive the DP and DM lines, if the OE\_N/INT\_N input (when the OE\_INT\_EN bit is not set) is LOW. In such a case, these outputs are driven as in USB functional modes, but with the full-speed characteristics, irrespective of the value of the SPEED input pin or the SPEED\_REG bit.

| USB mode      | [1]              | Bit     | Bit   |                | Pin     |                 |         |                 |                      |  |

|---------------|------------------|---------|-------|----------------|---------|-----------------|---------|-----------------|----------------------|--|

|               |                  | DAT_SE0 | BI_DI | OE_N/<br>INT_N | DAT/VP  | SE0/VM          | VP      | VM              | RCV                  |  |

| VP_VM         | M unidirectional | 0       | 0     | Х              | TxD+[2] | TxD-[2]         | RxD+[3] | RxD_[ <u>3]</u> | RxD <mark>[6]</mark> |  |

| bidirectional | 0                | 1       | LOW   | TxD+[2]        | TxD-[2] |                 |         |                 |                      |  |

|               |                  | 0       | 1     | HIGH           | RxD+[3] | RxD-[ <u>3]</u> |         |                 |                      |  |

| DAT_SE0       | unidirectional   | 1       | 0     | Х              | TxD[4]  | FSE0[5]         |         |                 |                      |  |

| bidirectional | 1                | 1       | LOW   | TxD[4]         | FSE0[5] |                 |         |                 |                      |  |

|               |                  | 1       | 1     | HIGH           | RxD[6]  | RSE0[7]         |         |                 |                      |  |

#### Table 6. USB functional modes: I/O values

[1] Some of the modes and signals are provided to achieve backward compatibility with IP cores.

[2] TxD+ and TxD– are single-ended inputs to drive the DP and DM outputs, respectively, in single-ended mode.

[3] RxD+ and RxD- are the outputs of the single-ended receivers connected to DP and DM, respectively.

[4] TxD is the input to drive DP and DM in DAT\_SE0 mode.

[5] FSE0 is to force an SE0 on the DP and DM lines in DAT\_SE0 mode.

[6] RxD is the output of the differential receiver.

[7] RSE0 is an output indicating that an SE0 has been received on the DP and DM lines.

#### Table 7. USB suspend mode: I/O values

| USB suspend mode  | Input p | in   | Output pin |        |      |      |     |  |

|-------------------|---------|------|------------|--------|------|------|-----|--|

|                   | DP      | DM   | DAT/VP     | SE0/VM | VP   | VM   | RCV |  |

| DAT_SE0           | LOW     | LOW  | LOW        | HIGH   | LOW  | LOW  | Х   |  |

| (bit DAT_SE0 = 1) | HIGH    | LOW  | HIGH       | LOW    | HIGH | LOW  | Х   |  |

|                   | LOW     | HIGH | LOW        | LOW    | LOW  | HIGH | Х   |  |

|                   | HIGH    | HIGH | HIGH       | LOW    | HIGH | HIGH | Х   |  |

| VP_VM             | LOW     | LOW  | LOW        | LOW    | LOW  | LOW  | Х   |  |

| (bit DAT_SE0 = 0) | HIGH    | LOW  | HIGH       | LOW    | HIGH | LOW  | Х   |  |

|                   | LOW     | HIGH | LOW        | HIGH   | LOW  | HIGH | Х   |  |

|                   | HIGH    | HIGH | HIGH       | HIGH   | HIGH | HIGH | Х   |  |

#### Table 8. Transparent general-purpose buffer mode

| Bit<br>TRANSP_BDIR[1:0] | Direction of the data flow |                         |  |  |

|-------------------------|----------------------------|-------------------------|--|--|

| 00                      | $DAT/VP \to DP$            | $SE0/VM \rightarrow DM$ |  |  |

| 01                      | $DAT/VP \to DP$            | $SE0/VM \leftarrow DM$  |  |  |

| 10                      | $DAT/VP \leftarrow DP$     | $SE0/VM \rightarrow DM$ |  |  |

| 11                      | $DAT/VP \leftarrow DP$     | $SE0/VM \leftarrow DM$  |  |  |

### 9. USB transceiver

### 9.1 Differential driver

The operation of the driver is described in <u>Table 9</u>. The register bits and the pins used in the column heading are described in <u>Section 10.1</u> and <u>Section 7.10</u>, respectively.

ISP1301\_5 Product data sheet

| Suspend <sup>[1]</sup> | Bit<br>TRANSP_<br>EN | Pin<br>OE_N/<br>INT_N | Bit<br>DAT_SE0 | Differential driver                                                                       |

|------------------------|----------------------|-----------------------|----------------|-------------------------------------------------------------------------------------------|

| 0                      | 0                    | LOW                   | 0              | output value from DAT/VP to DP and SE0/VM to DM                                           |

| 0                      | 0                    | LOW                   | 1              | output value from DAT/VP to DP and DM if SE0/VM is 0; otherwise, drive both DP and DM LOW |

| 1                      | 0                    | LOW                   | Х              | output value from DAT/VP to DP and DM                                                     |

| Х                      | Х                    | HIGH                  | Х              | high-Z                                                                                    |

| Х                      | 1                    | Х                     | Х              | high-Z                                                                                    |

#### Transcoiver driver operation setting

[1] Can be controlled by using either the SUSPEND pin or the SUSPEND\_REG bit.

#### Table 10. USB functional mode: transmit operation

| USB mode | Input pin |        | Output pin | Output pin |  |  |

|----------|-----------|--------|------------|------------|--|--|

|          | DAT/VP    | SE0/VM | DP         | DM         |  |  |

| DAT_SE0  | LOW       | LOW    | LOW        | HIGH       |  |  |

|          | HIGH      | LOW    | HIGH       | LOW        |  |  |

|          | LOW       | HIGH   | LOW        | LOW        |  |  |

|          | HIGH      | HIGH   | LOW        | LOW        |  |  |

| VP_VM    | LOW       | LOW    | LOW        | LOW        |  |  |

|          | HIGH      | LOW    | HIGH       | LOW        |  |  |

|          | LOW       | HIGH   | LOW        | HIGH       |  |  |

|          | HIGH      | HIGH   | HIGH       | HIGH       |  |  |

#### 9.2 Differential receiver

Table 11 describes the operation of the differential receiver. The register bits and the pins used in the column heading are described in <u>Section 10.1</u> and <u>Section 7.10</u>, respectively.

The detailed behavior of the receive transceiver operation is given in Table 12.

|                        |                  |                   | -              |                                                            |

|------------------------|------------------|-------------------|----------------|------------------------------------------------------------|

| Suspend <sup>[1]</sup> | Bit<br>TRANSP_EN | Pin<br>OE_N/INT_N | Bit<br>DAT_SE0 | Differential receiver                                      |

| 1                      | Х                | Х                 | Х              | Х                                                          |

| Х                      | Х                | LOW               | Х              | 0                                                          |

| Х                      | 1                | Х                 | Х              | 0                                                          |

| 0                      | 0                | HIGH              | 1              | output differential value from DP and DM to DAT/VP and RCV |

| 0                      | 0                | HIGH              | 0              | output differential value from DP and DM to RCV            |

#### Table 11. Differential receiver operation settings

[1] Can be controlled by using either the SUSPEND pin or the SUSPEND\_REG bit.

| Table 12. U |                        |           |      |           |        |                   |  |

|-------------|------------------------|-----------|------|-----------|--------|-------------------|--|

| USB mode    | Suspend <sup>[1]</sup> | Input pin |      | Output pi | n      |                   |  |

|             |                        | DP        | DM   | DAT/VP    | SE0/VM | RCV               |  |

| DAT_SE0     | 0                      | LOW       | LOW  | RCV       | HIGH   | last value of RCV |  |

| DAT_SE0     | 0                      | HIGH      | LOW  | HIGH      | LOW    | HIGH              |  |

| DAT_SE0     | 0                      | LOW       | HIGH | LOW       | LOW    | LOW               |  |

| DAT_SE0     | 0                      | HIGH      | HIGH | RCV       | LOW    | last value of RCV |  |

| DAT_SE0     | 1                      | LOW       | LOW  | LOW       | HIGH   | Х                 |  |

| DAT_SE0     | 1                      | HIGH      | LOW  | HIGH      | LOW    | Х                 |  |

| DAT_SE0     | 1                      | LOW       | HIGH | LOW       | LOW    | Х                 |  |

| DAT_SE0     | 1                      | HIGH      | HIGH | HIGH      | LOW    | Х                 |  |

| VP_VM       | 0                      | LOW       | LOW  | LOW       | LOW    | last value of RCV |  |

| VP_VM       | 0                      | HIGH      | LOW  | HIGH      | LOW    | HIGH              |  |

| VP_VM       | 0                      | LOW       | HIGH | LOW       | HIGH   | LOW               |  |

| VP_VM       | 0                      | HIGH      | HIGH | HIGH      | HIGH   | last value of RCV |  |

| VP_VM       | 1                      | LOW       | LOW  | LOW       | LOW    | Х                 |  |

| VP_VM       | 1                      | HIGH      | LOW  | HIGH      | LOW    | Х                 |  |

| VP_VM       | 1                      | LOW       | HIGH | LOW       | HIGH   | Х                 |  |

| VP_VM       | 1                      | HIGH      | HIGH | HIGH      | HIGH   | Х                 |  |

|             |                        |           |      |           |        |                   |  |

### Table 12. USB functional mode: receive operation

[1] Can be controlled by using either the SUSPEND pin or the SUSPEND\_REG bit.

# **10. Serial controller**

### 10.1 Register map

Table 13 provides an overview of the serial controller registers.

| Register              | Width<br>(bits) | Access <sup>[1]</sup> | Memory address                         | Functionality                   | Reference                 |  |

|-----------------------|-----------------|-----------------------|----------------------------------------|---------------------------------|---------------------------|--|

| Vendor ID             | 16              | R                     | 00h to 01h                             | device identification registers | Section 10.1.1 on page 18 |  |

| Product ID            | 16              | R                     | 02h to 03h                             |                                 |                           |  |

| Version ID            | 16              | R                     | 14h to 15h                             |                                 |                           |  |

| Mode Control 1        | 8               | R/S/C                 | <b>Set</b> — 04h<br><b>Clear</b> — 05h | mode control registers          | Section 10.1.2 on page 19 |  |

| Mode Control 2        | 8               | R/S/C                 | <b>Set —</b> 12h<br><b>Clear —</b> 13h |                                 |                           |  |

| OTG Control           | 8               | R/S/C                 | <b>Set —</b> 06h<br><b>Clear —</b> 07h | OTG registers                   | Section 10.1.3 on page 20 |  |

| OTG Status            | 8               | R                     | 10h                                    |                                 |                           |  |

| Interrupt Source      | 8               | R                     | 08h                                    | interrupt related registers     | Section 10.1.4 on page 21 |  |

| Interrupt Latch       | 8               | R/S/C                 | Set — 0Ah<br>Clear — 0Bh               |                                 |                           |  |

| Interrupt Enable Low  | 8 R/S/C         |                       | Set — 0Ch<br>Clear — 0Dh               |                                 |                           |  |

| Interrupt Enable High | 8               | R/S/C                 | Set — 0Eh<br>Clear — 0Fh               |                                 |                           |  |

[1] The R/S/C access type represents a field that can be read, set or cleared (set to 0). A register can be read from either of the indicated addresses: set or clear. Writing logic 1 to the set address causes the associated bit to be set. Writing logic 1 to the clear address causes the associated bit to be cleared. Writing logic 0 to an address has no effect.

### **10.1.1** Device identification registers

#### 10.1.1.1 Vendor ID register (Read: 00h to 01h)

Table 14 provides the bit description of the Vendor ID register.

| Bit              | Symbol           | Access         | Value            | Description                   |  |

|------------------|------------------|----------------|------------------|-------------------------------|--|

| 15 to 0          | VENDORID[15:0]   | R              | 04CCh            | ST-Ericsson' Vendor ID        |  |

|                  | 10112 Broduct    |                | r (Deed, 02h     | (a. 0.2h)                     |  |

|                  | 10.1.1.2 Product | •              | •                |                               |  |

|                  |                  | •              | •                | is given in <u>Table 15</u> . |  |

| Table 15.        | The bit o        | description of | of this register |                               |  |

| Table 15.<br>Bit | The bit o        | description of | of this register |                               |  |

#### 10.1.1.3 Version ID register (Read: 14h to 15h)

Table 16 shows the bit description of this register.

ISP1301\_5

#### Table 16. Version ID register: bit description

Table 17. Mode Control 1 register: bit allocation

| Bit     | Symbol          | Access | Value | Description                   |

|---------|-----------------|--------|-------|-------------------------------|

| 15 to 0 | VERSIONID[15:0] | R      | 0210h | Version number of the ISP1301 |

#### **10.1.2 Mode control registers**

#### 10.1.2.1 Mode Control 1 register (Set/Clear: 04h/05h)

The bit allocation of the Mode Control 1 register is given in Table 17.

|        |       | riegister. bit | anocation     |                  |               |         |                 |               |

|--------|-------|----------------|---------------|------------------|---------------|---------|-----------------|---------------|

| Bit    | 7     | 6              | 5             | 4                | 3             | 2       | 1               | 0             |

| Symbol | -     | UART_EN        | OE_INT_<br>EN | BDIS_<br>ACON_EN | TRANSP_<br>EN | DAT_SE0 | SUSPEND<br>_REG | SPEED_<br>REG |

| Reset  | -     | 0              | 0             | 0                | 0             | 0       | 0               | 0             |

| Access | R/S/C | R/S/C          | R/S/C         | R/S/C            | R/S/C         | R/S/C   | R/S/C           | R/S/C         |

| Table 18. | Mode Control 1 register: bit description |                                                                                                                  |  |  |  |  |  |

|-----------|------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit       | Symbol                                   | Description                                                                                                      |  |  |  |  |  |

| 7         | -                                        | reserved                                                                                                         |  |  |  |  |  |

| 6         | UART_EN                                  | When set, the ATX is in transparent UART mode.                                                                   |  |  |  |  |  |

| 5         | OE_INT_EN                                | When set and when in suspend mode, pin OE_N/INT_N becomes<br>an output and is asserted when an interrupt occurs. |  |  |  |  |  |

| 4         | BDIS_ACON_EN                             | Enables the A-device to connect if the B-device disconnect is detected; see Section 10.3.                        |  |  |  |  |  |

| 3         | TRANSP_EN                                | When set, the ATX is in transparent mode.                                                                        |  |  |  |  |  |

| 2         | DAT_SE0                                  | 0 — VP_VM mode                                                                                                   |  |  |  |  |  |

|           |                                          | 1 — DAT_SE0 mode; see <u>Table 6</u> and <u>Table 7</u>                                                          |  |  |  |  |  |

| 1         | SUSPEND_REG                              | Sets the ISP1301 in suspend mode, if bit SPD_SUSP_CTRL = 1                                                       |  |  |  |  |  |

|           |                                          | 0 — active-power mode                                                                                            |  |  |  |  |  |

|           |                                          | 1 — USB suspend mode                                                                                             |  |  |  |  |  |

| 0         | SPEED_REG                                | Sets the rise time and the fall time of the transmit driver in USB modes, if bit SPD_SUSP_CTRL = 1.              |  |  |  |  |  |

|           |                                          | 0 — USB low-speed mode                                                                                           |  |  |  |  |  |

|           |                                          | 1 — USB full-speed mode                                                                                          |  |  |  |  |  |

#### 10.1.2.2 Mode Control 2 register (Set/Clear: 12h/13h)

For the bit allocation of this register, see <u>Table 19</u>.

#### Table 19. Mode Control 2 register: bit allocation

| Bit    | 7     | 6      | 5        | 4                | 3                | 2     | 1                 | 0                 |

|--------|-------|--------|----------|------------------|------------------|-------|-------------------|-------------------|

| Symbol | EN2V7 | PSW_OE | AUDIO_EN | TRANSP_<br>BDIR1 | TRANSP_<br>BDIR0 | BI_DI | SPD_SUSP<br>_CTRL | GLOBAL_P<br>WR_DN |

| Reset  | 0     | 0      | 0        | 0                | 0                | 1     | 0                 | 0                 |

| Access | R/S/C | R/S/C  | R/S/C    | R/S/C            | R/S/C            | R/S/C | R/S/C             | R/S/C             |

ISP1301\_5

| Bit    | Symbol           | Description                                                                                                                                                                                                                                                                                          |

|--------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | EN2V7            | $0 - V_{CC} = 3.0 \text{ V to } 4.5 \text{ V}$                                                                                                                                                                                                                                                       |

|        |                  | <b>1</b> — $V_{CC}$ = 2.7 V to 4.5 V                                                                                                                                                                                                                                                                 |

|        |                  | <b>Remark:</b> For the operating condition to be USB compliant, it is recommended to always set this bit as logic 0. Setting this bit as logic 1 may not cause any functional problems, but it might cause some USB specification violation in terms of voltage levels required for the USB signals. |

| 6      | PSW_OE           | 0 — ADR/PSW pin acts as an input                                                                                                                                                                                                                                                                     |

|        |                  | 1 — ADR/PSW pin is driven                                                                                                                                                                                                                                                                            |

| 5      | AUDIO_EN         | 0 — SE receiver is enabled; cr_int detector is disabled                                                                                                                                                                                                                                              |

|        |                  | 1 — SE receiver is turned off (pin VP = LOW, pin VM = LOW);<br>cr_int detector is enabled                                                                                                                                                                                                            |

| 4 to 3 | TRANSP_BDIR[1:0] | controls the direction of data transfer in transparent general-purpose buffer mode; see <u>Table 8</u>                                                                                                                                                                                               |

| 2      | BI_DI            | 0 — direction of DAT/VP and SE0/VM are fixed (transmit only)                                                                                                                                                                                                                                         |

|        |                  | 1 — direction of DAT/VP and SE0/VM are controlled by<br>pin OE_N/INT_N; see <u>Table 6</u>                                                                                                                                                                                                           |

| 1      | SPD_SUSP_CTRL    | control of speed and suspend in USB modes:                                                                                                                                                                                                                                                           |

|        |                  | 0 — controlled by pins SPEED and SUSPEND                                                                                                                                                                                                                                                             |

|        |                  | 1 — controlled by bit SPEED_REG and bit SUSPEND_REG of<br>the Mode Control 1 register                                                                                                                                                                                                                |

| 0      | GLOBAL_PWR_DN    | 0 — normal operation                                                                                                                                                                                                                                                                                 |

|        |                  | 1 — sets the ISP1301 to Power-down mode                                                                                                                                                                                                                                                              |

|        |                  | Activities on the I <sup>2</sup> C-bus or any OTG event can wake-up the chip; see Section 11                                                                                                                                                                                                         |

#### Table 20. Mode Control 2 register: bit description

### 10.1.3 OTG registers

### 10.1.3.1 OTG Control register (Set/Clear: 06h/07h)

Table 21 provides the bit allocation of the OTG Control register.

| Table 21. | OTG | Control | register: | bit | allocation |

|-----------|-----|---------|-----------|-----|------------|

|-----------|-----|---------|-----------|-----|------------|

| Bit    | 7             | 6                | 5            | 4               | 3               | 2               | 1             | 0             |

|--------|---------------|------------------|--------------|-----------------|-----------------|-----------------|---------------|---------------|

| Symbol | VBUS_<br>CHRG | VBUS_<br>DISCHRG | VBUS_<br>DRV | ID_PULL<br>DOWN | DM_PULL<br>DOWN | DP_PULL<br>DOWN | DM_PULL<br>UP | DP_PULL<br>UP |

| Reset  | 0             | 0                | 0            | 0               | 1               | 1               | 0             | 0             |

| Access | R/S/C         | R/S/C            | R/S/C        | R/S/C           | R/S/C           | R/S/C           | R/S/C         | R/S/C         |

#### Table 22. OTG Control register: bit description

| Bit | Symbol       | Description                                             |

|-----|--------------|---------------------------------------------------------|

| 7   | VBUS_CHRG    | charge $V_{BUS}$ through a resistor to 3.3 V            |

| 6   | VBUS_DISCHRG | discharge V <sub>BUS</sub> through a resistor to ground |

| 5   | VBUS_DRV     | drive $V_{BUS}$ to 5 V through the charge pump          |

| 4   | ID_PULLDOWN  | connect the ID pin to ground                            |

| 3   | DM_PULLDOWN  | connect the DM pull-down resistor to ground             |

ISP1301\_5

|  | Table 22. | OTG Control register: bit description continued |

|--|-----------|-------------------------------------------------|

|--|-----------|-------------------------------------------------|

| Bit | Symbol      | Description                                 |

|-----|-------------|---------------------------------------------|

| 2   | DP_PULLDOWN | connect the DP pull-down resistor to ground |

| 1   | DM_PULLUP   | connect the DM pull-up resistor to 3.3 V    |

| 0   | DP_PULLUP   | connect the DP pull-up resistor to 3.3 V    |

#### 10.1.3.2 OTG Status register (Read: 10h)

Table 23 shows the bit allocation of the OTG Status register.

#### Table 23. OTG Status register: bit allocation

| Bit    | 7              | 6              | 5 | 4 | 3    | 2    | 1 | 0 |

|--------|----------------|----------------|---|---|------|------|---|---|

| Symbol | B_SESS_<br>VLD | B_SESS_<br>END |   |   | rese | rved |   |   |

| Reset  | 0              | 0              | 0 | 0 | 0    | 0    | 0 | 0 |

| Access | R              | R              | R | R | R    | R    | R | R |

| BitSymbolDescription7B_SESS_VLDset when the V <sub>BUS</sub> voltage is above the B-device session valid<br>threshold (2.0 V to 4.0 V)6B_SESS_ENDset when the V <sub>BUS</sub> voltage is below the B-device session end<br>threshold (0.2 V to 0.8 V)5 to 0-reserved | Table 24. | OTG Status reg | OTG Status register: bit description |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------|--------------------------------------|--|--|--|--|--|

| 6       B_SESS_END       set when the V <sub>BUS</sub> voltage is below the B-device session end threshold (0.2 V to 0.8 V)                                                                                                                                           | Bit       | Symbol         | Description                          |  |  |  |  |  |

| threshold (0.2 V to 0.8 V)                                                                                                                                                                                                                                            | 7         | B_SESS_VLD     |                                      |  |  |  |  |  |

| 5 to 0 - reserved                                                                                                                                                                                                                                                     | 6         | B_SESS_END     |                                      |  |  |  |  |  |

|                                                                                                                                                                                                                                                                       | 5 to 0    | -              | reserved                             |  |  |  |  |  |

### 10.1.4 Interrupt related registers

#### 10.1.4.1 Interrupt Source register (Read: 08h)

This register indicates the current state of the signals that can generate an interrupt. The bit allocation of the Interrupt Source register is given in <u>Table 25</u>.

Table 25. Interrupt Source register: bit allocation

| Bit    | 7      | 6             | 5        | 4     | 3      | 2     | 1        | 0        |

|--------|--------|---------------|----------|-------|--------|-------|----------|----------|

| Symbol | CR_INT | BDIS_<br>ACON | ID_FLOAT | DM_HI | ID_GND | DP_HI | SESS_VLD | VBUS_VLD |

| Reset  | 0      | 0             | 0        | 0     | 0      | 0     | 0        | 0        |

| Access | R      | R             | R        | R     | R      | R     | R        | R        |

### Table 26. Interrupt Source register: bit description

| Bit | Symbol    | Description                                                                                                        |

|-----|-----------|--------------------------------------------------------------------------------------------------------------------|

| 7   | CR_INT    | DP pin is above the carkit interrupt threshold (0.4 V to 0.6 V)                                                    |

| 6   | BDIS_ACON | set when bit BDIS_ACON_EN is set, and the ISP1301 asserts bit<br>DP_PULLUP after detecting the B-device disconnect |

| 5   | ID_FLOAT  | ID pin is floating                                                                                                 |

| 4   | DM_HI     | DM pin is HIGH                                                                                                     |

| 3   | ID_GND    | ID pin is connected to ground                                                                                      |

| 2   | DP_HI     | DP pin is HIGH                                                                                                     |

| 1   | SESS_VLD  | session valid comparator; threshold = $0.8$ V to $2.0$ V                                                           |

| 0   | VBUS_VLD  | A-device $V_{BUS}$ valid comparator; threshold > 4.4 V                                                             |

|     |           |                                                                                                                    |

#### 10.1.4.2 Interrupt Latch register (Set/Clear: 0Ah/0Bh)

This register indicates the source that generated the interrupt. The bit allocation of the Interrupt Latch register is given in Table 27.

| Table 27. Interrupt Latch register: bit allocation |

|----------------------------------------------------|

|----------------------------------------------------|

| Bit    | 7      | 6             | 5        | 4     | 3      | 2     | 1        | 0        |

|--------|--------|---------------|----------|-------|--------|-------|----------|----------|

| Symbol | CR_INT | BDIS_<br>ACON | ID_FLOAT | DM_HI | ID_GND | DP_HI | SESS_VLD | VBUS_VLD |

| Reset  | 0      | 0             | 0        | 0     | 0      | 0     | 0        | 0        |

| Access | R/S/C  | R/S/C         | R/S/C    | R/S/C | R/S/C  | R/S/C | R/S/C    | R/S/C    |

#### Table 28. Interrupt Latch register: bit description

| Bit | Symbol    | Description                           |

|-----|-----------|---------------------------------------|

| 7   | CR_INT    | interrupt for CR_INT status change    |

| 6   | BDIS_ACON | interrupt for BDIS_ACON status change |

| 5   | ID_FLOAT  | interrupt for ID_FLOAT status change  |

| 4   | DM_HI     | interrupt for DM_HI status change     |

| 3   | ID_GND    | interrupt for ID_GND status change    |

| 2   | DP_HI     | interrupt for DP_HI status change     |

| 1   | SESS_VLD  | interrupt for SESS_VLD status change  |

| 0   | VBUS_VLD  | interrupt for VBUS_VLD status change  |

|     |           |                                       |

#### 10.1.4.3 Interrupt Enable Low register (Set/Clear: 0Ch/0Dh)

This register enables interrupts on transition from true to false. For the bit allocation of this register, see <u>Table 29</u>.

|        |        | 0             |          |       |        |       |          |          |

|--------|--------|---------------|----------|-------|--------|-------|----------|----------|

| Bit    | 7      | 6             | 5        | 4     | 3      | 2     | 1        | 0        |

| Symbol | CR_INT | BDIS_<br>ACON | ID_FLOAT | DM_HI | ID_GND | DP_HI | SESS_VLD | VBUS_VLD |

| Reset  | 0      | 0             | 0        | 0     | 0      | 0     | 0        | 0        |

| Access | R/S/C  | R/S/C         | R/S/C    | R/S/C | R/S/C  | R/S/C | R/S/C    | R/S/C    |

Table 29.

Interrupt Enable Low register: bit allocation

ISP1301\_5

#### Table 30. Interrupt Enable Low register: bit description

| Bit | Symbol    | Description                                              |

|-----|-----------|----------------------------------------------------------|

| 7   | CR_INT    | interrupt enable for CR_INT status change from 1 to 0    |

| 6   | BDIS_ACON | interrupt enable for BDIS_ACON status change from 1 to 0 |

| 5   | ID_FLOAT  | interrupt enable for ID_FLOAT status change from 1 to 0  |

| 4   | DM_HI     | interrupt enable for DM_HI status change from 1 to 0     |

| 3   | ID_GND    | interrupt enable for ID_GND status change from 1 to 0    |

| 2   | DP_HI     | interrupt enable for DP_HI status change from 1 to 0     |

| 1   | SESS_VLD  | interrupt enable for SESS_VLD status change from 1 to 0  |

| 0   | VBUS_VLD  | interrupt enable for VBUS_VLD status change from 1 to 0  |

#### 10.1.4.4 Interrupt Enable High register (Set/Clear: 0Eh/0Fh)

The Interrupt Enable High register enables interrupts on transition from FALSE to TRUE. <u>Table 31</u> provides the bit allocation of this register.

Table 31. Interrupt Enable High register: bit allocation

| Bit    | 7      | 6             | 5        | 4     | 3      | 2     | 1        | 0        |

|--------|--------|---------------|----------|-------|--------|-------|----------|----------|

| Symbol | CR_INT | BDIS_<br>ACON | ID_FLOAT | DM_HI | ID_GND | DP_HI | SESS_VLD | VBUS_VLD |

| Reset  | 0      | 0             | 0        | 0     | 0      | 0     | 0        | 0        |

| Access | R/S/C  | R/S/C         | R/S/C    | R/S/C | R/S/C  | R/S/C | R/S/C    | R/S/C    |

#### Table 32. Interrupt Enable High register: bit description

| mbol     | Description                                              |

|----------|----------------------------------------------------------|

|          |                                                          |

| R_INT    | interrupt enable for CR_INT status change from 0 to 1    |

| DIS_ACON | interrupt enable for BDIS_ACON status change from 0 to 1 |

| _FLOAT   | interrupt enable for ID_FLOAT status change from 0 to 1  |

| Л_HI     | interrupt enable for DM_HI status change from 0 to 1     |

| _GND     | interrupt enable for ID_GND status change from 0 to 1    |

| P_HI     | interrupt enable for DP_HI status change from 0 to 1     |

| SS_VLD   | interrupt enable for SESS_VLD status change from 0 to 1  |

| BUS VLD  | interrupt enable for VBUS_VLD status change from 0 to 1  |

| >.       | _<br>GND<br>_HI<br>SS_VLD                                |

#### 10.2 Interrupts

Table 26 indicates the signals that can generate interrupts. Any of the signals given in Table 26 can generate an interrupt when the signal becomes either LOW or HIGH. After an interrupt has been generated, the OTG Controller should be able to read the status of each signal and the bit that indicates whether that signal generated the interrupt.

A bit in the Interrupt Latch register is set when any of these occurs:

- Writing logic 1 to its set address causes the corresponding bit to be set.

- The corresponding bit in the Interrupt Enable High register is set, and the associated signal changes from LOW to HIGH.

- The corresponding bit in the Interrupt Enable Low register is set, and the associated signal changes from HIGH to LOW.

ISP1301\_5 Product data sheet

The Interrupt Latch register bit is cleared by writing logic 1 to its clear address.

### 10.3 Auto-connect

The Host Negotiation Protocol (HNP) in the OTG supplement specifies the following sequence of events to transfer the role of the host from the A-device to the B-device:

- 1. The A-device puts the bus in the suspend state.

- 2. The B-device simulates a disconnect by de-asserting its DP pull-up.

- 3. The A-device detects SE0 on the bus, and asserts its DP pull-up.

- 4. The B-device detects that the DP line is HIGH, and takes the role of the host.

The OTG supplement specifies that the time between the B-device de-asserting its DP pull-up and the A-device asserting its pull-up must be less than 3 ms. For an A-device with a slow interrupt response time, 3 ms may not be enough time to write an I<sup>2</sup>C-bus command to the ISP1301 to assert the DP pull-up. An alternative method is for the A-device transceiver to automatically assert the DP pull-up after detecting an SE0 from the B-device.

The sequence of events is: After finishing data transfers between the A-device and the B-device and before suspending the bus, the A-device sends SOFs. The B-device receives these SOFs, and does not transmit any packet back to the A-device. During this time, the A-device sets the BDIS\_ACON\_EN bit in the ISP1301. This enables the ISP1301 to look for SE0 whenever the A-device is not transmitting (that is, whenever the OE\_N/INT\_N pin of the ISP1301 is not asserted). After the BDIS\_ACON\_EN bit is set, the A-device stops transmitting SOFs and allows the bus to go to the idle state. If the B-device disconnects, the bus goes to SE0, and the ISP1301 logic automatically turns on the A-device pull-up.

**ST** FRICSSON

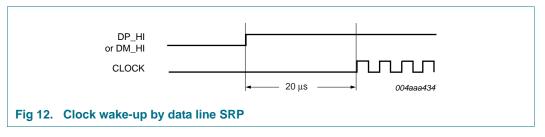

# 11. Clock wake-up scheme

The following subsections explain the ISP1301 clock stop timing, events triggering the clock to wake up, and the timing of the clock wake-up.

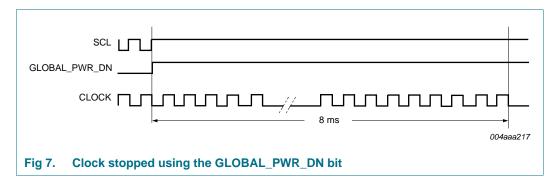

### **11.1 Power-down event**

The clock is stopped when the GLOBAL\_PWR\_DN bit is set. It takes approximately 8 ms for the clock to stop from the time the power-down condition is detected. The clock always stops at its falling edge. The waveform is given in <u>Figure 7</u>.

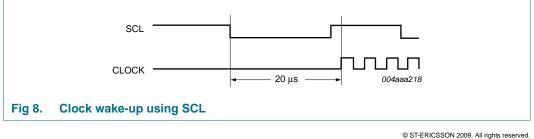

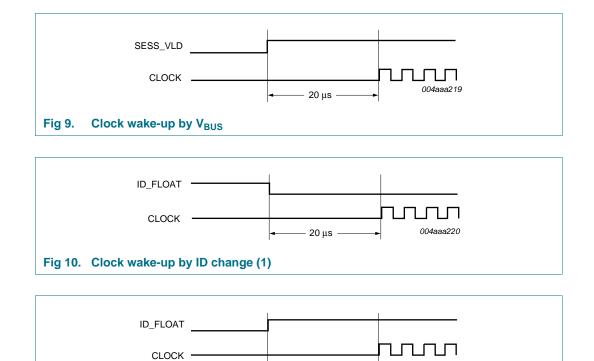

### 11.2 Clock wake-up events

The clock wakes up when any of the following events occur on the ISP1301 pins:

- SCL goes LOW.

- V<sub>BUS</sub> goes above the session valid threshold (0.8 V to 2.0 V), provided the SESS\_VLD bit in the Interrupt Enable High register is set.

- ID changes when mini-A plug is inserted, provided the ID\_FLOAT bit in the Interrupt Enable Low register is set.

- ID changes when mini-A plug is removed, provided the ID\_FLOAT bit in the Interrupt Enable High register is set.

- DP goes HIGH, provided the DP\_HI bit in the Interrupt Enable High register is set.

- DM goes HIGH, provided the DM\_HI bit in the Interrupt Enable High register is set.

The event triggers the clock to start and a stable clock is guaranteed after about six clock periods, which is approximately 8  $\mu$ s. The startup analog clock time is 10  $\mu$ s. Therefore, the total estimated start time after a triggered event is about 20  $\mu$ s. The clock will always start at its rising edge.

Waveforms of the clock wake-up because of different events are given in <u>Figure 8</u>, <u>Figure 9</u>, <u>Figure 10</u>, <u>Figure 11</u> and <u>Figure 12</u>.

ISP1301\_5

ISP1301

**USB OTG transceiver**

Fig 11. Clock wake-up by ID change (2)

20 µs

004aaa221

When an event is triggered and the clock is started, it will remain active for 8 ms. If the GLOBAL\_PWR\_DN bit is not cleared within this 8 ms period, the clock will stop. If the clock wakes up because of any event other than SCL going LOW, an interrupt will be generated once the clock is active.

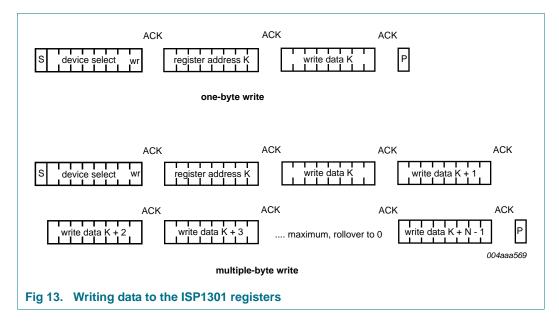

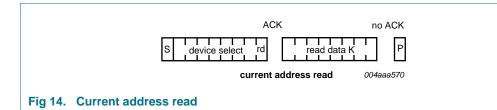

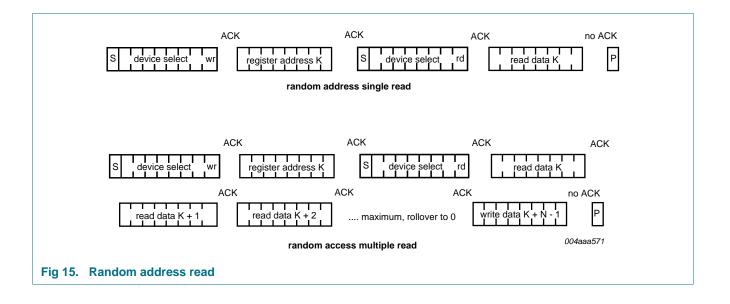

# 12. I<sup>2</sup>C-bus protocol

For detailed information, refer to The I<sup>2</sup>C-bus specification; version 2.1.

### 12.1 I<sup>2</sup>C-bus byte transfer format

| Table 33. | I <sup>2</sup> C-bus by | yte transfe        | r format |                    |        |                    |                        |                    |

|-----------|-------------------------|--------------------|----------|--------------------|--------|--------------------|------------------------|--------------------|

| S[1]      | Byte 1                  | A <mark>[2]</mark> | Byte 2   | A <mark>[2]</mark> | Byte 3 | A <mark>[2]</mark> | <br>A <mark>[2]</mark> | P <mark>[3]</mark> |

|           | 8 bits                  |                    | 8 bits   |                    | 8 bits |                    |                        |                    |

[1] S = Start.

[2] A = Acknowledge.

[3] P = Stop.

### **12.2** I<sup>2</sup>C-bus device address

#### Table 34. I<sup>2</sup>C-bus device address byte 1 bit allocation

| Bit    | 7  | 6  | 5  | 4  | 3  | 2  | 1          | 0     |

|--------|----|----|----|----|----|----|------------|-------|

| Symbol | A6 | A5 | A4 | A3 | A2 | A1 | A0         | R/W_N |

| Value  | 0  | 1  | 0  | 1  | 1  | 0  | <u>[1]</u> | Х     |

[1] The value of A0 (LSB) is loaded from pin ADR/PSW during reset (including power-on reset). If pin ADR/PSW = HIGH, bit A0 = 1; otherwise bit A0 = 0.

#### Table 35. I<sup>2</sup>C-bus device address byte 1 bit description

| Bit    | Symbol | Description                                                         |

|--------|--------|---------------------------------------------------------------------|

| 7 to 1 | A[6:0] | Device address: The device address of the ISP1301 is: 01 0110 (A0). |

| 0      | R/W_N  | Read or write command.                                              |

|        |        | 0 — write                                                           |