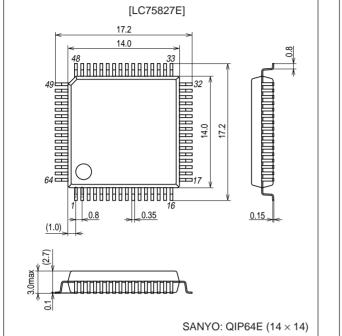

# **Package Dimensions**

unit: mm

# 3159A-QIP64E

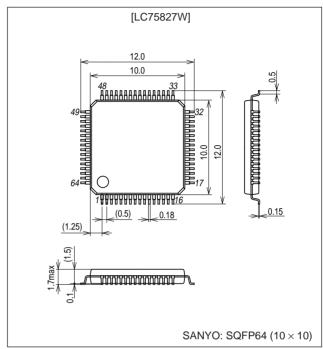

## unit: mm

# 3190A-SQFP64

# **Specifications**

# Absolute Maximum Ratings at Ta = 25°C, $V_{SS}$ = 0 V

| Parameter                   | Symbol               | Conditions                             | Ratings                        | Unit |  |

|-----------------------------|----------------------|----------------------------------------|--------------------------------|------|--|

|                             | V <sub>DD</sub> max  | V <sub>DD</sub> max V <sub>DD</sub>    |                                | v    |  |

| Maximum supply voltage      | V <sub>LCD</sub> max | V <sub>LCD</sub>                       | -0.3 to +7.0                   |      |  |

|                             | V <sub>IN</sub> 1    | CE, CL, DI, INH                        | -0.3 to +7.0                   |      |  |

| Input voltage               | V <sub>IN</sub> 2    | OSC                                    | -0.3 to V <sub>DD</sub> + 0.3  | V    |  |

|                             | V <sub>IN</sub> 3    | V <sub>LCD</sub> 1, V <sub>LCD</sub> 2 | -0.3 to V <sub>LCD</sub> + 0.3 | 1    |  |

| Output voltage              | V <sub>OUT</sub> 1   | V <sub>OUT</sub> 1 OSC                 |                                | V    |  |

|                             | V <sub>OUT</sub> 2   | S1 to S51, COM1 to COM4, P1 to P12     | -0.3 to V <sub>LCD</sub> + 0.3 |      |  |

|                             | I <sub>OUT</sub> 1   | S1 to S51                              | 300                            | μA   |  |

| Output current              | I <sub>OUT</sub> 2   | COM1 to COM4                           | 3                              |      |  |

|                             | I <sub>OUT</sub> 3   | P1 to P12                              | 5                              | mA   |  |

| Allowable power dissipation | Pd max               | Ta = 85°C                              | 200                            | mW   |  |

| Operating temperature       | Topr                 |                                        | -40 to +85                     | °C   |  |

| Storage temperature         | Tstg                 |                                        | -55 to +125                    | °C   |  |

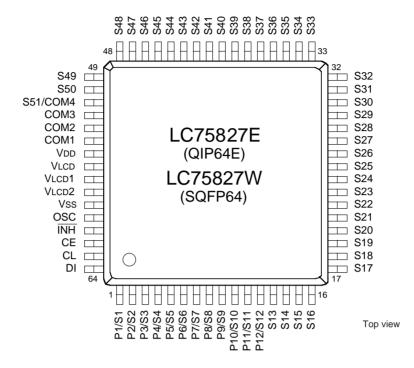

# **Pin Assignment**

## Allowable Operating Ranges at Ta = -40 to $+85^{\circ}$ C, V<sub>SS</sub> = 0 V

| Parameter                                     | Symbol             | Conditions                        |                     | Ratings              |                     |        |  |  |  |

|-----------------------------------------------|--------------------|-----------------------------------|---------------------|----------------------|---------------------|--------|--|--|--|

| Parameter                                     | Symbol             |                                   |                     | typ                  | max                 | - Unit |  |  |  |

| Cupply voltoge                                | V <sub>DD</sub>    | V <sub>DD</sub>                   | 2.7                 |                      | 6.0                 | v      |  |  |  |

| Supply voltage                                | V <sub>LCD</sub>   | V <sub>LCD</sub>                  | 2.7                 |                      | 6.0                 | V      |  |  |  |

| Innut voltore                                 | V <sub>LCD</sub> 1 | V <sub>LCD</sub> 1                |                     | 2/3 V <sub>LCD</sub> | V <sub>LCD</sub>    | v      |  |  |  |

| Input voltage                                 | V <sub>LCD</sub> 2 | V <sub>LCD</sub> 2                |                     | 1/3 V <sub>LCD</sub> | V <sub>LCD</sub>    | 1 V    |  |  |  |

| land high land on the se                      | V <sub>IH</sub> 1  | CE, CL, DI, INH                   | 0.8 V <sub>DD</sub> |                      | 6.0                 | v      |  |  |  |

| Input high level voltage                      | V <sub>IH</sub> 2  | OSC: external clock mode          | 0.7 V <sub>DD</sub> |                      | V <sub>DD</sub>     |        |  |  |  |

| 1                                             | V <sub>IL</sub> 1  | CE, CL, DI, INH                   | 0                   |                      | 0.2 V <sub>DD</sub> | v      |  |  |  |

| Input low level voltage                       | V <sub>IL</sub> 2  | OSC: external clock mode          | 0                   |                      | 0.3 V <sub>DD</sub> |        |  |  |  |

| Recommended external R <sub>OSC</sub>         |                    | OSC: RC oscillation mode          |                     | 39                   |                     | kΩ     |  |  |  |

| Recommended external COSC                     |                    | OSC: RC oscillation mode          |                     | 1000                 |                     | pF     |  |  |  |

| Guaranteed oscillation range f <sub>OSC</sub> |                    | OSC: RC oscillation mode          | 19                  | 38                   | 76                  | kHz    |  |  |  |

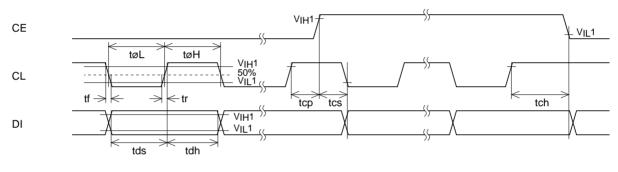

| External clock frequency f <sub>CK</sub>      |                    | OSC: external clock mode Figure 4 | 19                  | 38                   | 76                  | kHz    |  |  |  |

| External clock duty                           | D <sub>CK</sub>    | OSC: external clock mode Figure 4 | 30                  | 50                   | 70                  | %      |  |  |  |

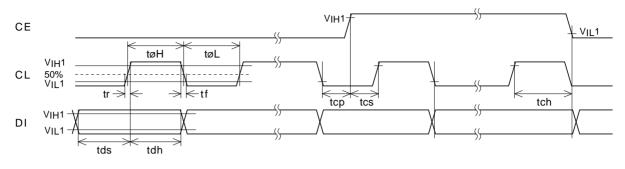

| Data setup time                               | t <sub>ds</sub>    | CL, DI: Figure 2, 3               | 160                 |                      |                     | ns     |  |  |  |

| Data hold time                                | t <sub>dh</sub>    | CL, DI: Figure 2, 3               | 160                 |                      |                     | ns     |  |  |  |

| CE wait time                                  | t <sub>cp</sub>    | CE, CL: Figure 2, 3               | 160                 |                      |                     | ns     |  |  |  |

| CE setup time                                 | t <sub>cs</sub>    | CE, CL: Figure 2, 3               | 160                 |                      |                     | ns     |  |  |  |

| CE hold time                                  | t <sub>ch</sub>    | CE, CL: Figure 2, 3               | 160                 |                      |                     | ns     |  |  |  |

| High level clock pulse width                  | t <sub>øH</sub>    | CL: Figure 2, 3                   | 160                 |                      |                     | ns     |  |  |  |

| Low level clock pulse width                   | tøL                | CL: Figure 2, 3                   | 160                 |                      |                     | ns     |  |  |  |

| Rise time                                     | tr                 | CE, CL, DI: Figure 2, 3           |                     | 160                  |                     | ns     |  |  |  |

| Fall time                                     | t <sub>f</sub>     | CE, CL, DI: Figure 2, 3           |                     | 160                  |                     | ns     |  |  |  |

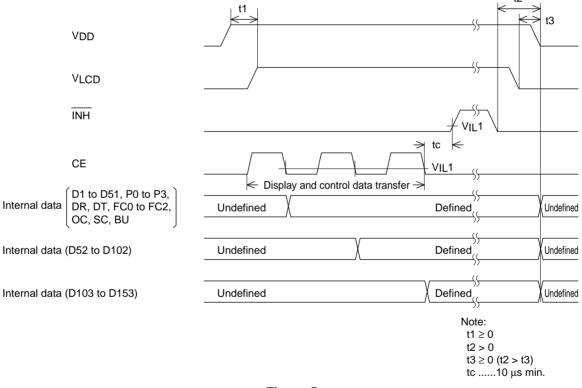

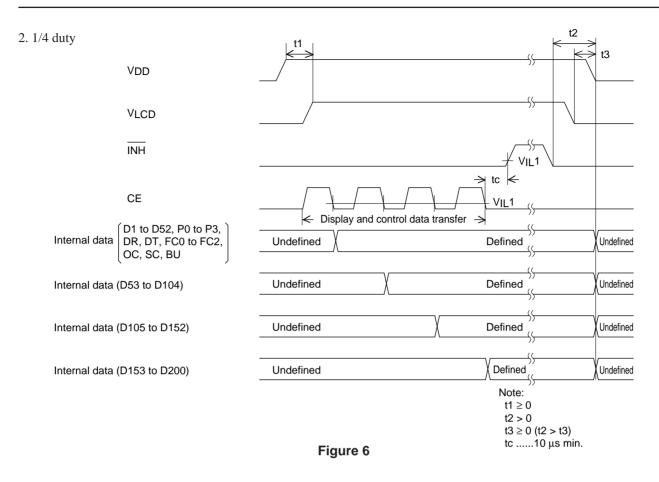

| INH switching time                            | tc                 | INH, CE: Figure 5, 6              | 10                  |                      |                     | μs     |  |  |  |

| Parameter                     | Symbol             | Conditions                                                                          |                            | Ratings             |                            |      |  |  |

|-------------------------------|--------------------|-------------------------------------------------------------------------------------|----------------------------|---------------------|----------------------------|------|--|--|

| Parameter                     | Symbol             |                                                                                     |                            | typ                 | max                        | Unit |  |  |

| Hysteresis                    | V <sub>H</sub>     | CE, CL, DI, INH                                                                     |                            | 0.1 V <sub>DD</sub> |                            | V    |  |  |

| Innut high lovel ourrest      | I <sub>IH</sub> 1  | CE, CL, DI, $\overline{\text{INH}}$ : V <sub>I</sub> = 6.0 V                        |                            |                     | 5.0                        |      |  |  |

| Input high level current      | I <sub>IH</sub> 2  | OSC: V <sub>I</sub> = V <sub>DD</sub> , external clock mode                         |                            |                     | 5.0                        | μA   |  |  |

| Innut loud ourrant            | I <sub>IL</sub> 1  | CE, CL, DI, $\overline{\text{INH}}$ : V <sub>I</sub> = 0 V                          | -5.0                       |                     |                            |      |  |  |

| Input low level current       | I <sub>IL</sub> 2  | OSC: V <sub>I</sub> = 0 V, external clock mode                                      | -5.0                       |                     |                            | μA   |  |  |

|                               | V <sub>OH</sub> 1  | S1 to S51: I <sub>O</sub> = -20 μA                                                  | V <sub>LCD</sub> - 0.9     |                     |                            |      |  |  |

| Output high level voltage     | V <sub>OH</sub> 2  | COM1 to COM4: $I_0 = -100 \mu A$                                                    | V <sub>LCD</sub> - 0.9     |                     |                            | V    |  |  |

|                               | V <sub>OH</sub> 3  | P1 to P12: I <sub>O</sub> = -1 mA                                                   | V <sub>LCD</sub> – 0.9     |                     |                            |      |  |  |

|                               | V <sub>OL</sub> 1  | S1 to S51: I <sub>O</sub> = 20 μA                                                   |                            |                     | 0.9                        |      |  |  |

| Output low level voltage      | V <sub>OL</sub> 2  | COM1 to COM4: $I_0 = 100 \ \mu A$                                                   |                            |                     | 0.9                        | V    |  |  |

|                               | V <sub>OL</sub> 3  | P1 to P12: I <sub>O</sub> = 1 mA                                                    |                            |                     | 0.9                        |      |  |  |

|                               | V <sub>MID</sub> 1 | COM1 to COM4: 1/2 bias, $I_0 = \pm 100 \ \mu A$                                     | 1/2 V <sub>LCD</sub> – 0.9 |                     | 1/2 V <sub>LCD</sub> + 0.9 |      |  |  |

|                               | V <sub>MID</sub> 2 | S1 to S51: 1/3 bias, I <sub>O</sub> = ±20 μA                                        | 2/3 V <sub>LCD</sub> – 0.9 |                     | 2/3 V <sub>LCD</sub> + 0.9 |      |  |  |

| Output middle level voltage*1 | V <sub>MID</sub> 3 | S1 to S51: 1/3 bias, I <sub>O</sub> = ±20 μA                                        | 1/3 V <sub>LCD</sub> – 0.9 |                     | 1/3 V <sub>LCD</sub> + 0.9 | V    |  |  |

|                               | V <sub>MID</sub> 4 | COM1 to COM4: 1/3 bias, $I_0 = \pm 100 \ \mu A$                                     | 2/3 V <sub>LCD</sub> – 0.9 |                     | 2/3 V <sub>LCD</sub> + 0.9 |      |  |  |

|                               | V <sub>MID</sub> 5 | COM1 to COM4: 1/3 bias, $I_0 = \pm 100 \ \mu A$                                     | 1/3 V <sub>LCD</sub> – 0.9 |                     | 1/3 V <sub>LCD</sub> + 0.9 |      |  |  |

| Oscillator frequency          | fosc               | OSC: $R_{OSC} = 39 \text{ k}\Omega$ , $C_{OSC} = 1000 \text{ pF}$                   | 30.4                       | 38                  | 45.6                       | kHz  |  |  |

|                               | I <sub>DD</sub> 1  | V <sub>DD</sub> : Power-saving mode                                                 |                            |                     | 5                          |      |  |  |

|                               | I <sub>DD</sub> 2  | V <sub>DD</sub> : V <sub>DD</sub> = 6.0 V, outputs open, f <sub>OSC</sub> = 38 kHz  |                            | 250                 | 500                        |      |  |  |

| Current drain                 | I <sub>LCD</sub> 1 | V <sub>LCD</sub> : Power-saving mode                                                |                            |                     | 5                          |      |  |  |

|                               | I <sub>LCD</sub> 2 | $V_{LCD}$ : $V_{LCD}$ = 6.0 V, outputs open, 1/2 bias,<br>f <sub>OSC</sub> = 38 kHz |                            | 100                 | 200                        | μA   |  |  |

|                               | I <sub>LCD</sub> 3 | $V_{LCD}$ : $V_{LCD}$ = 6.0 V, outputs open, 1/3 bias,<br>f <sub>OSC</sub> = 38 kHz |                            | 60                  | 120                        |      |  |  |

# **Electrical Characteristics** for the Allowable Operating Ranges

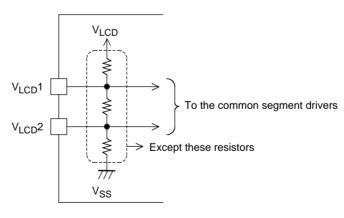

Note: \*1 Excluding the bias voltage generation divider resistors built in the V<sub>LCD</sub>1 and V<sub>LCD</sub>2. (See Figure 1.)

Figure 1

1. When CL is stopped at the low level

2. When CL is stopped at the high level

Figure 3

3. OSC Pin Clock Timing in External Clock Mode

Figure 4

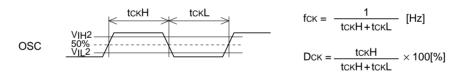

# **Block Diagram**

# **Pin Functions**

| Pin                            | Pin No.             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Active | I/O | Handling when<br>unused |

|--------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------------------------|

| S1/P1 to S12/P12<br>S13 to S50 | 1 to 12<br>13 to 50 | Segment outputs for displaying the display data transferred by serial data input. The pins S1/P1 to S12/P12 can be used as general-purpose output ports when so set up by the control data.                                                                                                                                                                                                                                                                                                                                                               |        | 0   | Open                    |

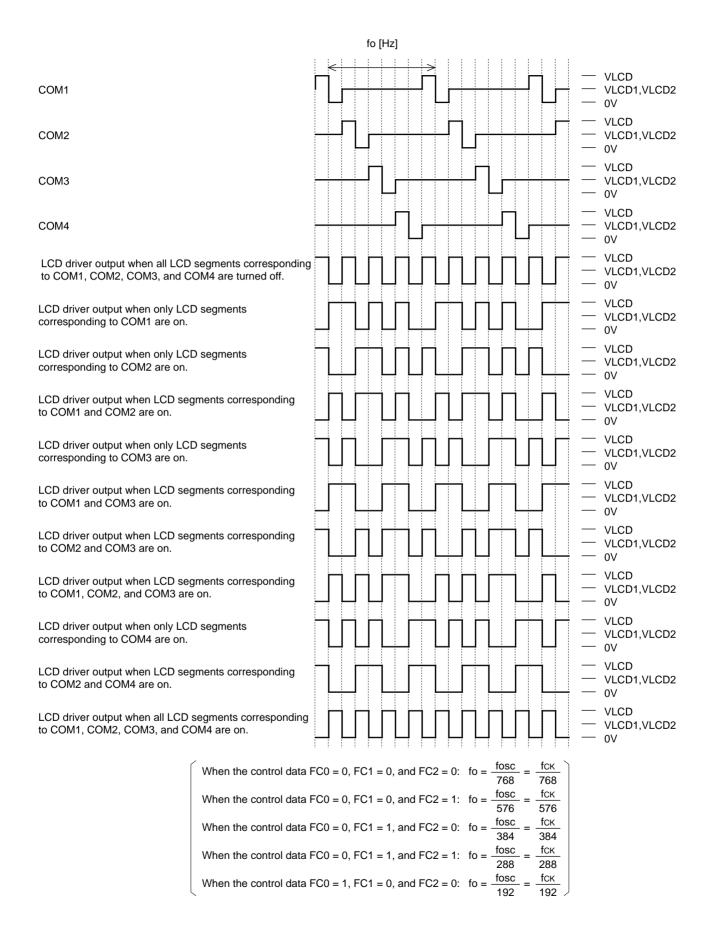

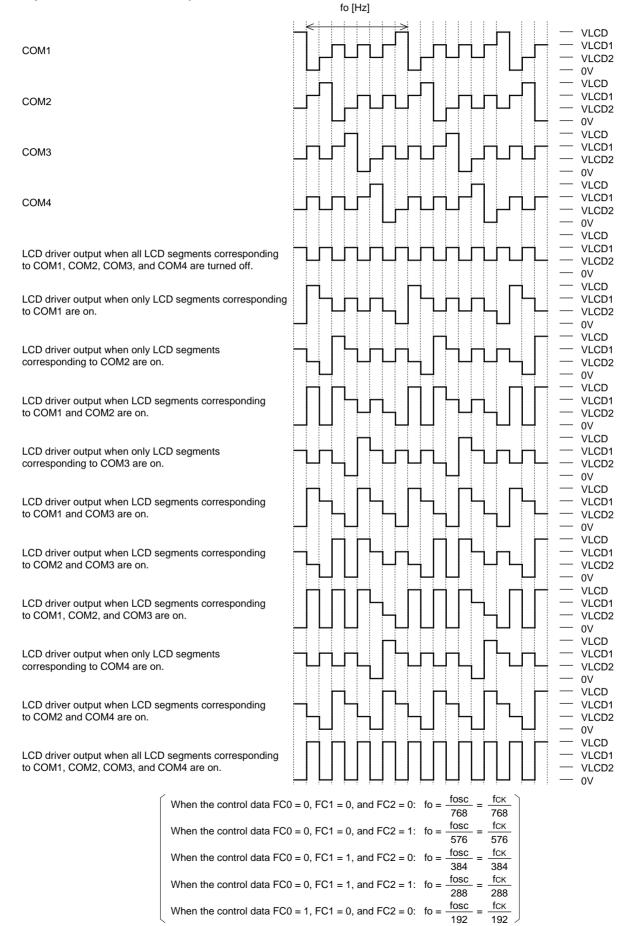

| COM1 to COM3<br>COM4/S51       | 54 to 52<br>51      | Common driver outputs.<br>The frame frequency is f <sub>O</sub> Hz.<br>The COM4/S51 can be used for segment output in 1/3 duty.                                                                                                                                                                                                                                                                                                                                                                                                                           | _      | 0   | Open                    |

| OSC                            | 60                  | Oscillator connection. An oscillator circuit is formed by connecting an external resistor and capacitor to this pin.<br>This pin can be used as the external clock input pin if external clock mode is selected with the control data.                                                                                                                                                                                                                                                                                                                    | _      | I/O | V <sub>DD</sub>         |

| CE                             | 62                  | Serial data transfer inputs. These pins are connected to the control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | н      | I   |                         |

| CL                             | 63                  | microprocessor.<br>CE: Chip enable<br>CL: Synchronization clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        | I   | GND                     |

| DI                             | 64                  | DI: Transfer data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _      | I   |                         |

| ĪNH                            | 61                  | $\label{eq:state} \begin{array}{ c c c c } \hline Display off control input \\ \bullet \ \overline{INH} = low (V_{SS})Off \\ & S1/P1 to S12/P12 = low (V_{SS}) \\ & (These pins are forcibly set to the segment output port function and fixed at the V_{SS} level.) \\ & S13 to S50 = low (V_{SS}) \\ & COM1 to COM3 = low (V_{SS}) \\ & COM4/S51 = low (V_{SS}) \\ & OSC = Z (High impedance) \\ \hline \ \overline{INH} = high (V_{DD})On \\ Note that serial data transfers can be performed when the display is forced off by this pin. \end{array}$ | L      | I   | GND                     |

| V <sub>LCD</sub> 1             | 57                  | Used to apply the LCD drive 2/3 bias voltage externally. This pin must be connected to $V_{LCD}2$ when 1/2 bias drive is used.                                                                                                                                                                                                                                                                                                                                                                                                                            | _      | I   | Open                    |

| V <sub>LCD</sub> 2             | 58                  | Used to apply the LCD drive $1/3$ bias voltage externally. This pin must be connected to V <sub>LCD</sub> 1 when $1/2$ bias drive is used.                                                                                                                                                                                                                                                                                                                                                                                                                | _      | I   | Open                    |

| V <sub>DD</sub>                | 55                  | Logic block power supply. Provide a voltage in the range 2.7 to 6.0 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _      | _   |                         |

| V <sub>LCD</sub>               | 56                  | LCD driver block power supply. Provide a voltage in the range 2.7 to 6.0 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _      | _   | _                       |

| V <sub>SS</sub>                | 59                  | Ground pin. Connect to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _      | _   | _                       |

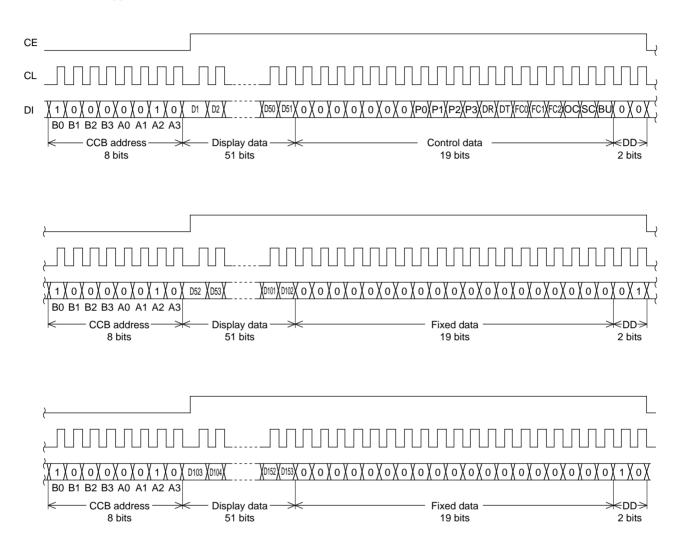

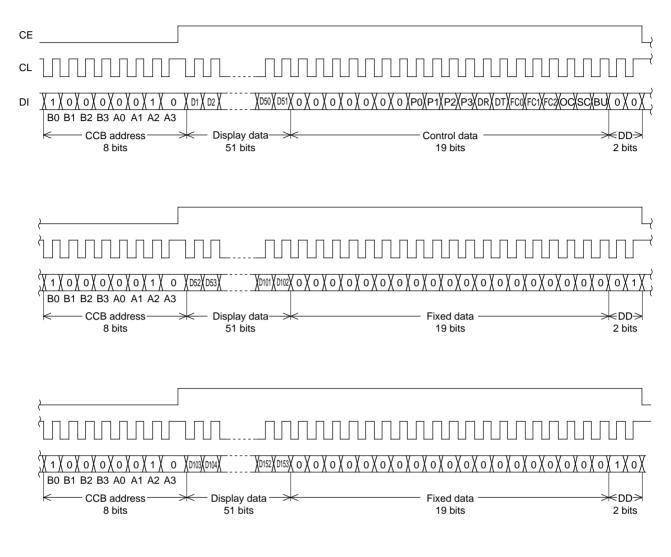

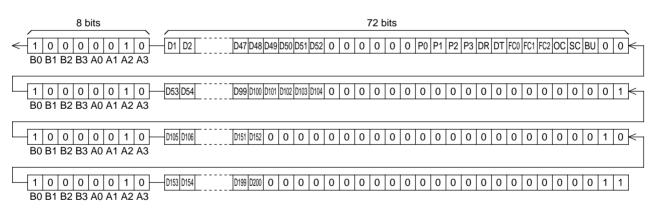

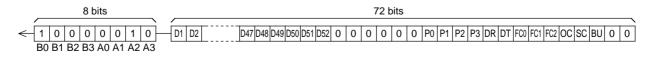

## Serial Data Transfer Format

1. 1/3 duty

① When CL is stopped at the low level

<sup>(2)</sup> When CL is stopped at the high level

- CCB address......41H

- D1 to D153.....Display data

- P0 to P3 .....Segment output port/general-purpose output port switching control data

- DR ......1/2 bias drive or 1/3 bias drive switching control data

- DT ......1/3 duty drive or 1/4 duty drive switching control data

- FC0 to FC2.....Common and segment output waveforms frame frequency setting control data

- OC.....Switches between RC oscillation mode and external clock mode

- SC.....Segments on/off control data

- BU .....Normal mode/power-saving mode control data

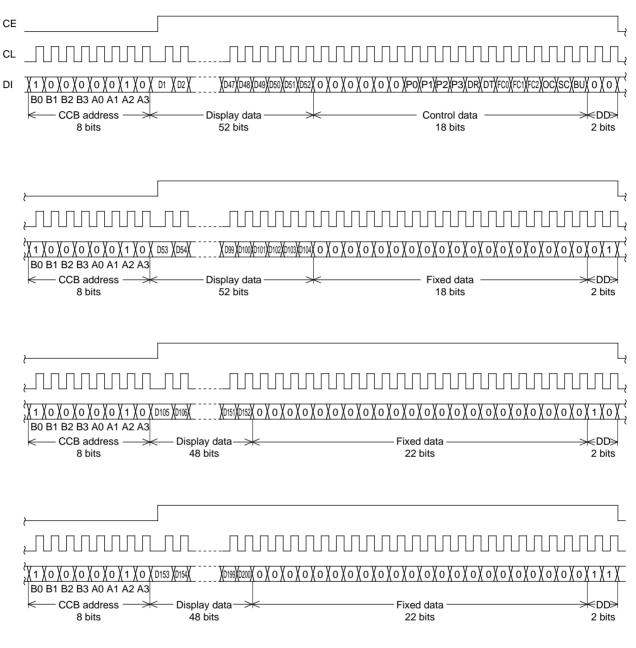

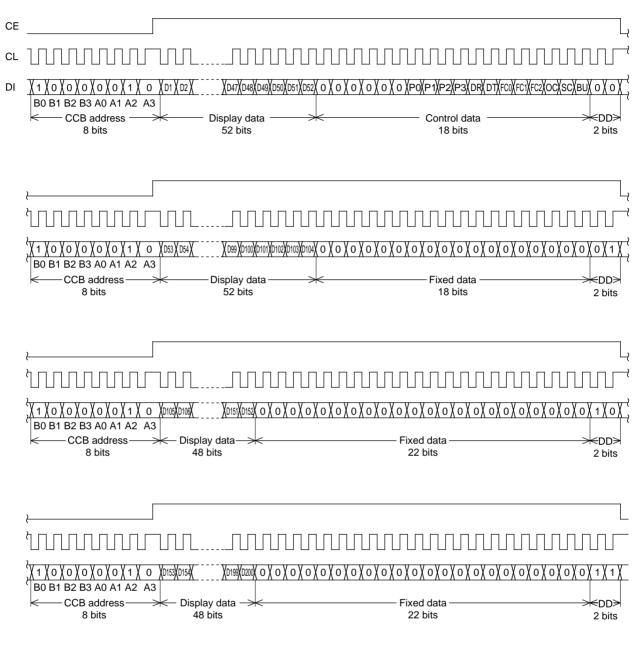

2. 1/4 duty

① When CL is stopped at the low level

<sup>(2)</sup> When CL is stopped at the high level

- CCB address......41H

- D1 to D200.....Display data

- P0 to P3 .....Segment output port/general-purpose output port switching control data

- DR ......1/2 bias drive or 1/3 bias drive switching control data

- DT ......1/3 duty drive or 1/4 duty drive switching control data

- FC0 to FC2.....Common and segment output waveforms frame frequency setting control data

- OC ......Switches between RC oscillation mode and external clock mode

- SC.....Segments on/off control data

- BU .....Normal mode/power-saving mode control data

## Serial Data Transfer Example

1. 1/3 duty

1 When 103 or more segments are used

All 216 bits of serial data must be sent.

| 8 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 72 bits                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 1 0 0 0 0 1 0 D1 D2 B0 B1 B2 B3 A0 A1 A2 A3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                |

| 1     0     0     0     1     0     D52     D53       B0     B1     B2     B3     A0     A1     A2     A3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                |

| 1     0     0     0     1     0     0     0     1     0     0     0     1     0     0     0     1     0     0     0     1     0     0     0     1     0     0     0     1     0     0     0     1     0     0     0     1     0     0     0     1     0     0     0     1     0     0     0     1     0     0     0     1     0     0     0     1     0     0     0     1     0     0     0     1     0     0     0     1     0     0     0     1     0     0     0     1     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0 | D149 D150 D151 D152 D153 O O O O O O O O O O O O O O O O O O O |

<sup>(2)</sup> When fewer than 103 segments are used

Either 72 or 144 bits of serial data may be sent, depending on the number of segments used. However, the serial data shown below (the D1 to D51 display data and the control data) must be sent.

| 8 bits                                       | 72 bits                                                                      |   |

|----------------------------------------------|------------------------------------------------------------------------------|---|

|                                              |                                                                              |   |

| ← 1 0 0 0 0 0 1 0<br>B0 B1 B2 B3 A0 A1 A2 A3 | 2 D47 D48 D49 D50 D51 0 0 0 0 0 0 0 P0 P1 P2 P3 DR DT FC0 FC1 FC2 OC SC BU 0 | 0 |

2. 1/4 duty

① When 153 or more segments are used

All 288 bits of serial data must be sent.

<sup>(2)</sup> When fewer than 153 segments are used

Either 72, 144, or 216 bits of serial data may be sent, depending on the number of segments used. However, the serial data shown below (the D1 to D52 display data and the control data) must be sent.

# **Control Data Functions**

P0 to P3: Segment output port/general-purpose output port switching control data These control data bits switch the S1/P1 to S12/P12 output pins between their segment output port and generalpurpose output port functions.

|    | Contro | ol data |    |       |       |       |       |       | Output p | oin state |       |       |         |         |         |

|----|--------|---------|----|-------|-------|-------|-------|-------|----------|-----------|-------|-------|---------|---------|---------|

| P0 | P1     | P2      | P3 | S1/P1 | S2/P2 | S3/P3 | S4/P4 | S5/P5 | S6/P6    | S7/P7     | S8/P8 | S9/P9 | S10/P10 | S11/P11 | S12/P12 |

| 0  | 0      | 0       | 0  | S1    | S2    | S3    | S4    | S5    | S6       | S7        | S8    | S9    | S10     | S11     | S12     |

| 0  | 0      | 0       | 1  | P1    | S2    | S3    | S4    | S5    | S6       | S7        | S8    | S9    | S10     | S11     | S12     |

| 0  | 0      | 1       | 0  | P1    | P2    | S3    | S4    | S5    | S6       | S7        | S8    | S9    | S10     | S11     | S12     |

| 0  | 0      | 1       | 1  | P1    | P2    | P3    | S4    | S5    | S6       | S7        | S8    | S9    | S10     | S11     | S12     |

| 0  | 1      | 0       | 0  | P1    | P2    | P3    | P4    | S5    | S6       | S7        | S8    | S9    | S10     | S11     | S12     |

| 0  | 1      | 0       | 1  | P1    | P2    | P3    | P4    | P5    | S6       | S7        | S8    | S9    | S10     | S11     | S12     |

| 0  | 1      | 1       | 0  | P1    | P2    | P3    | P4    | P5    | P6       | S7        | S8    | S9    | S10     | S11     | S12     |

| 0  | 1      | 1       | 1  | P1    | P2    | P3    | P4    | P5    | P6       | P7        | S8    | S9    | S10     | S11     | S12     |

| 1  | 0      | 0       | 0  | P1    | P2    | P3    | P4    | P5    | P6       | P7        | P8    | S9    | S10     | S11     | S12     |

| 1  | 0      | 0       | 1  | P1    | P2    | P3    | P4    | P5    | P6       | P7        | P8    | P9    | S10     | S11     | S12     |

| 1  | 0      | 1       | 0  | P1    | P2    | P3    | P4    | P5    | P6       | P7        | P8    | P9    | P10     | S11     | S12     |

| 1  | 0      | 1       | 1  | P1    | P2    | P3    | P4    | P5    | P6       | P7        | P8    | P9    | P10     | P11     | S12     |

| 1  | 1      | 0       | 0  | P1    | P2    | P3    | P4    | P5    | P6       | P7        | P8    | P9    | P10     | P11     | P12     |

Note: Sn (n = 1 to 12): Segment output ports

Pn (n = 1 to 12): General-purpose output ports

Also note that when the general-purpose output port function is selected, the output pins and the display data will have the correspondences listed in the tables below.

| Output pip | Correspondin | g display data |

|------------|--------------|----------------|

| Output pin | 1/3 duty     | 1/4 duty       |

| S1/P1      | D1           | D1             |

| S2/P2      | D4           | D5             |

| S3/P3      | D7           | D9             |

| S4/P4      | D10          | D13            |

| S5/P5      | D13          | D17            |

| S6/P6      | D16          | D21            |

| S7/P7      | D19          | D25            |

| S8/P8      | D22          | D29            |

| S9/P9      | D25          | D33            |

| S10/P10    | D28          | D37            |

| S11/P11    | D31          | D41            |

| S12/P12    | D34          | D45            |

For example, when 1/4 duty drive scheme is used, if the general-purpose output port function is selected for the S4/P4 output pin, that output pin will output a high level ( $V_{LCD}$ ) when the display data D13 is 1, and a low level ( $V_{SS}$ ) when D13 is 0.

2. DR: 1/2 bias drive or 1/3 bias drive switching control data This control data bit selects either 1/2 bias drive or 1/3 bias drive.

| DR | Bias drive scheme |

|----|-------------------|

| 0  | 1/3 bias drive    |

| 1  | 1/2 bias drive    |

3. DT: 1/3 duty drive or 1/4 duty drive switching control data This control data bit selects either 1/3 duty drive or 1/4 duty drive.

| DT | Duty drive scheme | Output pin (COM4/S51) state |

|----|-------------------|-----------------------------|

| 0  | 1/4 duty drive    | COM4                        |

| 1  | 1/3 duty drive    | S51                         |

Note: COM4: Common output S51: Segment output

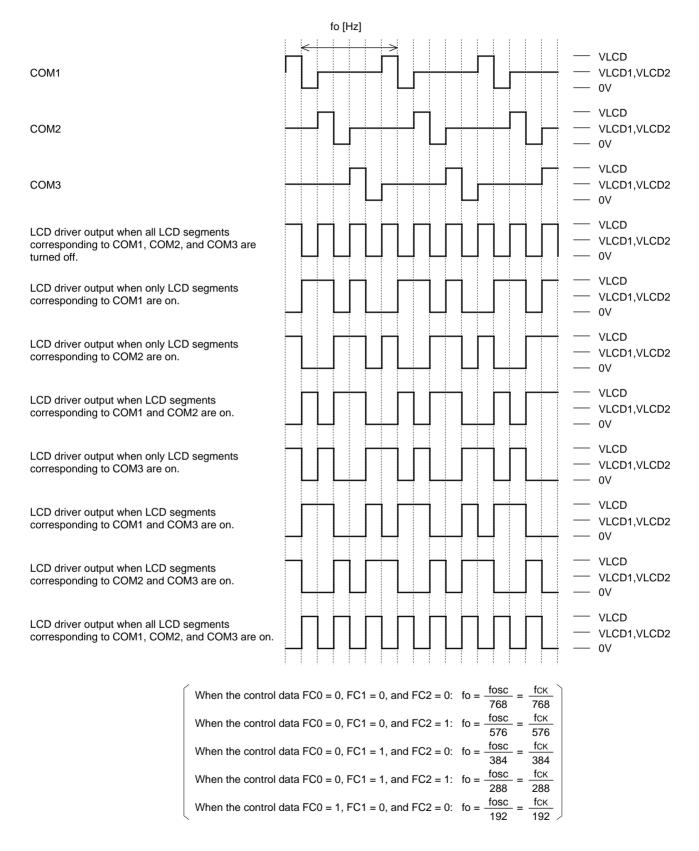

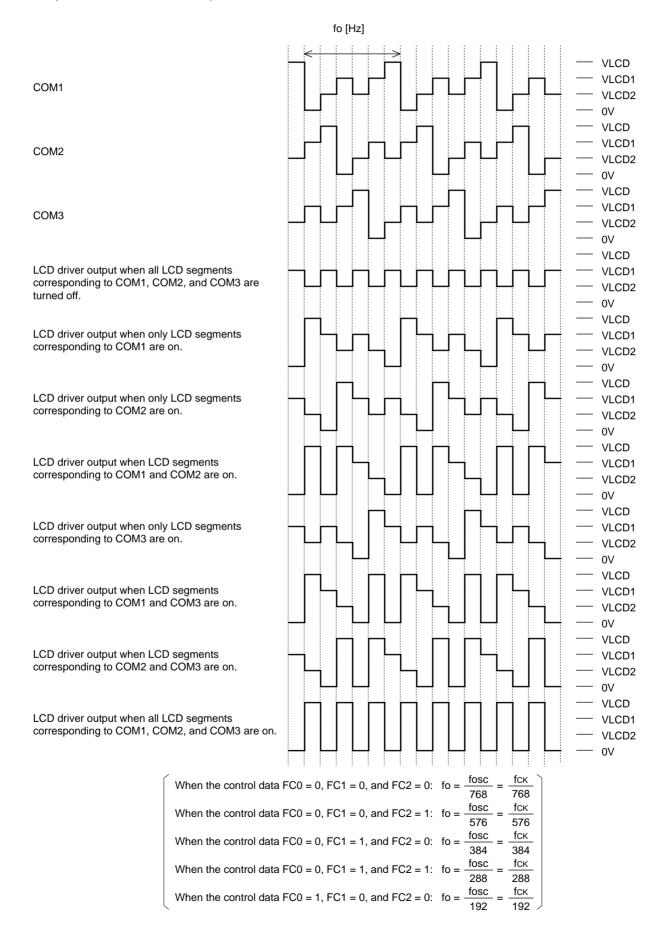

4. FC0 to FC2: Common and segment output waveforms frame frequency setting control data These control data bits set the frame frequency for common and segment output waveforms.

|     | Control data | Frame frequency fo [Hz] |                                |

|-----|--------------|-------------------------|--------------------------------|

| FC0 | FC1          | FC2                     |                                |

| 0   | 0            | 0                       | fosc/768, f <sub>CK</sub> /768 |

| 0   | 0            | 1                       | fosc/576, f <sub>CK</sub> /576 |

| 0   | 1            | 0                       | fosc/384, f <sub>CK</sub> /384 |

| 0   | 1            | 1                       | fosc/288, f <sub>CK</sub> /288 |

| 1   | 0            | 0                       | fosc/192, f <sub>CK</sub> /192 |

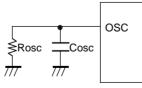

5. OC: Switches between RC oscillation mode and external clock mode.

This control data bit selects the OSC pin function (RC oscillation mode or external clock mode).

| OC                    | OSC pin function    |  |  |  |

|-----------------------|---------------------|--|--|--|

| 0                     | RC oscillation mode |  |  |  |

| 1 External clock mode |                     |  |  |  |

Note: An external resistor, Rosc, and an external capacitor, Cosc, must be connected to the OSC pin if RC oscillation mode is selected.

#### 6. SC: Segments on/off control data

This control data bit controls the on/off state of the segments.

| SC | Display state |  |  |  |

|----|---------------|--|--|--|

| 0  | On            |  |  |  |

| 1  | Off           |  |  |  |

However, note that when the segments are turned off by setting SC to 1, the segments are turned off by outputting segment off waveforms from the segment output pins.

#### 7. BU: Normal mode/power-saving mode control data

This control data bit selects either normal mode or power-saving mode.

| BU | Mode                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | Normal mode                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1  | Power-saving mode<br>[In RC oscillation mode (OC = 0), the OSC pin oscillator is stopped, and in external clock mode (OC = 1), acceptance of the external clock signal is stopped. In this mode the common and segment output pins go to the $V_{SS}$ levels. However, the S1/P1 to S12/P12 output pins that are set to be general-purpose output ports by the control data P0 to P3 can be used as general-purpose output ports.] |

# Display Data to Segment Output Pin Correspondence

# 1. 1/3 duty

| Segment<br>output pin |     |     | СОМЗ |

|-----------------------|-----|-----|------|

| S1/P1                 | D1  | D2  | D3   |

| S2/P2                 | D4  | D5  | D6   |

| S3/P3                 | D7  | D8  | D9   |

| S4/P4                 | D10 | D11 | D12  |

| S5/P5                 | D13 | D14 | D15  |

| S6/P6                 | D16 | D17 | D18  |

| S7/P7                 | D19 | D20 | D21  |

| S8/P8                 | D22 | D23 | D24  |

| S9/P9                 | D25 | D26 | D27  |

| S10/P10               | D28 | D29 | D30  |

| S11/P11               | D31 | D32 | D33  |

| S12/P12               | D34 | D35 | D36  |

| S13                   | D37 | D38 | D39  |

| S14                   | D40 | D41 | D42  |

| S15                   | D43 | D44 | D45  |

| S16                   | D46 | D47 | D48  |

| S17                   | D49 | D50 | D51  |

| S18                   | D52 | D53 | D54  |

| S19                   | D55 | D56 | D57  |

| S20                   | D58 | D59 | D60  |

| S21                   | D61 | D62 | D63  |

| S22                   | D64 | D65 | D66  |

| S23                   | D67 | D68 | D69  |

| S24                   | D70 | D71 | D72  |

| S25                   | D73 | D74 | D75  |

| S26                   | D76 | D77 | D78  |

| Segment<br>output pin | COM1 | COM2 | СОМЗ |  |

|-----------------------|------|------|------|--|

| S27                   | D79  | D80  | D81  |  |

| S28                   | D82  | D83  | D84  |  |

| S29                   | D85  | D86  | D87  |  |

| S30                   | D88  | D89  | D90  |  |

| S31                   | D91  | D92  | D93  |  |

| S32                   | D94  | D95  | D96  |  |

| S33                   | D97  | D98  | D99  |  |

| S34                   | D100 | D101 | D102 |  |

| S35                   | D103 | D104 | D105 |  |

| S36                   | D106 | D107 | D108 |  |

| S37                   | D109 | D110 | D111 |  |

| S38                   | D112 | D113 | D114 |  |

| S39                   | D115 | D116 | D117 |  |

| S40                   | D118 | D119 | D120 |  |

| S41                   | D121 | D122 | D123 |  |

| S42                   | D124 | D125 | D126 |  |

| S43                   | D127 | D128 | D129 |  |

| S44                   | D130 | D131 | D132 |  |

| S45                   | D133 | D134 | D135 |  |

| S46                   | D136 | D137 | D138 |  |

| S47                   | D139 | D140 | D141 |  |

| S48                   | D142 | D143 | D144 |  |

| S49                   | D145 | D146 | D147 |  |

| S50                   | D148 | D149 | D150 |  |

| COM4/S51              | D151 | D152 | D153 |  |

Note: This applies to the case where the S1/P1 to S12/P12, and COM4/S51 output pins are set to be segment output ports.

For example, the table below lists the segment output states for the S21 output pin.

| Display data |     |     | Segment output pin (S21) state                                  |

|--------------|-----|-----|-----------------------------------------------------------------|

| D61          | D62 | D63 | Segment output pin (S21) state                                  |

| 0            | 0   | 0   | The LCD segments corresponding to COM1, COM2, and COM3 are off. |

| 0            | 0   | 1   | The LCD segment corresponding to COM3 is on.                    |

| 0            | 1   | 0   | The LCD segment corresponding to COM2 is on.                    |

| 0            | 1   | 1   | The LCD segments corresponding to COM2 and COM3 are on.         |

| 1            | 0   | 0   | The LCD segment corresponding to COM1 is on.                    |

| 1            | 0   | 1   | The LCD segments corresponding to COM1 and COM3 are on.         |

| 1            | 1   | 0   | The LCD segments corresponding to COM1 and COM2 are on.         |

| 1            | 1   | 1   | The LCD segments corresponding to COM1, COM2, and COM3 are on.  |

# 2. 1/4 duty

| Segment<br>output pin | COM1 | COM2 | COM3 | COM4 | Segment<br>output pin | COM1 | COM2 | COM3 | COM4 |

|-----------------------|------|------|------|------|-----------------------|------|------|------|------|

| S1/P1                 | D1   | D2   | D3   | D4   | S26                   | D101 | D102 | D103 | D104 |

| S2/P2                 | D5   | D6   | D7   | D8   | S27                   | D105 | D106 | D107 | D108 |

| S3/P3                 | D9   | D10  | D11  | D12  | S28                   | D109 | D110 | D111 | D112 |

| S4/P4                 | D13  | D14  | D15  | D16  | S29                   | D113 | D114 | D115 | D116 |

| S5/P5                 | D17  | D18  | D19  | D20  | S30                   | D117 | D118 | D119 | D120 |

| S6/P6                 | D21  | D22  | D23  | D24  | S31                   | D121 | D122 | D123 | D124 |

| S7/P7                 | D25  | D26  | D27  | D28  | S32                   | D125 | D126 | D127 | D128 |

| S8/P8                 | D29  | D30  | D31  | D32  | S33                   | D129 | D130 | D131 | D132 |

| S9/P9                 | D33  | D34  | D35  | D36  | S34                   | D133 | D134 | D135 | D136 |

| S10/P10               | D37  | D38  | D39  | D40  | S35                   | D137 | D138 | D139 | D140 |

| S11/P11               | D41  | D42  | D43  | D44  | S36                   | D141 | D142 | D143 | D144 |

| S12/P12               | D45  | D46  | D47  | D48  | \$37                  | D145 | D146 | D147 | D148 |

| S13                   | D49  | D50  | D51  | D52  | S38                   | D149 | D150 | D151 | D152 |

| S14                   | D53  | D54  | D55  | D56  | S39                   | D153 | D154 | D155 | D156 |

| S15                   | D57  | D58  | D59  | D60  | S40                   | D157 | D158 | D159 | D160 |

| S16                   | D61  | D62  | D63  | D64  | S41                   | D161 | D162 | D163 | D164 |

| S17                   | D65  | D66  | D67  | D68  | S42                   | D165 | D166 | D167 | D168 |

| S18                   | D69  | D70  | D71  | D72  | S43                   | D169 | D170 | D171 | D172 |

| S19                   | D73  | D74  | D75  | D76  | S44                   | D173 | D174 | D175 | D176 |

| S20                   | D77  | D78  | D79  | D80  | S45                   | D177 | D178 | D179 | D180 |

| S21                   | D81  | D82  | D83  | D84  | S46                   | D181 | D182 | D183 | D184 |

| S22                   | D85  | D86  | D87  | D88  | S47                   | D185 | D186 | D187 | D188 |

| S23                   | D89  | D90  | D91  | D92  | S48                   | D189 | D190 | D191 | D192 |

| S24                   | D93  | D94  | D95  | D96  | S49                   | D193 | D194 | D195 | D196 |

| S25                   | D97  | D98  | D99  | D100 | S50                   | D197 | D198 | D199 | D200 |

Note: This applies to the case where the S1/P1 to S12/P12 output pins are set to be segment output ports.

# For example, the table below lists the segment output states for the S21 output pin.

| Display data |     |     | Comment output his (C21) state |                                                                       |

|--------------|-----|-----|--------------------------------|-----------------------------------------------------------------------|

| D81          | D82 | D83 | D84                            | Segment output pin (S21) state                                        |

| 0            | 0   | 0   | 0                              | The LCD segments corresponding to COM1, COM2, COM3, and COM4 are off. |

| 0            | 0   | 0   | 1                              | The LCD segment corresponding to COM4 is on.                          |

| 0            | 0   | 1   | 0                              | The LCD segment corresponding to COM3 is on.                          |

| 0            | 0   | 1   | 1                              | The LCD segments corresponding to COM3 and COM4 are on.               |

| 0            | 1   | 0   | 0                              | The LCD segment corresponding to COM2 is on.                          |

| 0            | 1   | 0   | 1                              | The LCD segments corresponding to COM2 and COM4 are on.               |

| 0            | 1   | 1   | 0                              | The LCD segments corresponding to COM2 and COM3 are on.               |

| 0            | 1   | 1   | 1                              | The LCD segments corresponding to COM2, COM3, and COM4 are on.        |

| 1            | 0   | 0   | 0                              | The LCD segment corresponding to COM1 is on.                          |

| 1            | 0   | 0   | 1                              | The LCD segments corresponding to COM1 and COM4 are on.               |

| 1            | 0   | 1   | 0                              | The LCD segments corresponding to COM1 and COM3 are on.               |

| 1            | 0   | 1   | 1                              | The LCD segments corresponding to COM1, COM3, and COM4 are on.        |

| 1            | 1   | 0   | 0                              | The LCD segments corresponding to COM1 and COM2 are on.               |

| 1            | 1   | 0   | 1                              | The LCD segments corresponding to COM1, COM2, and COM4 are on.        |

| 1            | 1   | 1   | 0                              | The LCD segments corresponding to COM1, COM2, and COM3 are on.        |

| 1            | 1   | 1   | 1                              | The LCD segments corresponding to COM1, COM2, COM3, and COM4 are on.  |

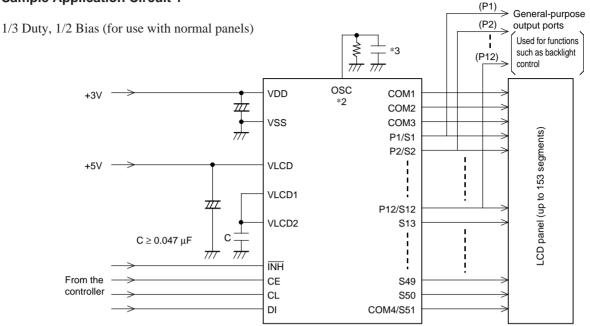

## 1/3 Duty, 1/2 Bias Drive Technique

## 1/3 Duty, 1/3 Bias Drive Technique

## 1/4 Duty, 1/2 Bias Drive Technique

#### 1/4 Duty, 1/3 Bias Drive Technique

# The INH pin and Display Control

Since the IC internal data (1/3 duty: the display data D1 to D153 and the control data, 1/4 duty: the display data D1 to D200 and the control data) is undefined when power is first applied, applications should set the  $\overline{INH}$  pin low at the same time as power is applied to turn off the display (This sets the S1/P1 to S12/P12, S13 to S50, COM1 to COM3, and COM4/S51 to the V<sub>SS</sub> level.) and during this period send serial data from the controller. The controller should then set the  $\overline{INH}$  pin high after the data transfer has completed. This procedure prevents meaningless displays at power on. (See Figures 5and 6.)

## Notes on the Power On/Off Sequences

Applications should observe the following sequences when turning the LC75827E and LC75827W power on and off.

- At power on: Logic block power supply  $(V_{DD})$  on  $\rightarrow$  LCD driver block power supply  $(V_{LCD})$  on

- At power off: LCD driver block power supply (V<sub>LCD</sub>) off  $\rightarrow$  Logic block power supply (V<sub>DD</sub>) off

However, if the logic and LCD driver block use a shared power supply, then the power supplies can be turned on and off at the same time.

1. 1/3 duty

Figure 5

## Notes on Controller Transfer of Display Data

Since the LC75827E and LC75827W accept the display data (D1 to D153) divided into three separate transfer operations when using 1/3 duty drive scheme and the data (D1 to D200) divided into four separate transfer operations when 1/4 duty drive, we recommend that applications transfer all of the display data within a period of less than 30 ms to prevent observable degradation of display quality.

## **OSC Pin Peripheral Circuit**

1. RC oscillation mode (control data OC = 0)

When RC oscillation mode is selected, an external resistor, Rosc, and an external capacitor, Cosc, must be connected between the OSC pin and ground.

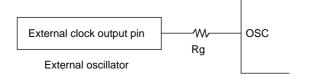

2. External clock mode (control data OC = 1)

When external clock mode is selected, a current protection resistor, Rg (4.7 to 47 k $\Omega$ ) must be inserted between the external clock output pin (on the external oscillator) and the OSC pin. The value of this resistor is determined by the allowable current capacity of the external clock output pin. Note that the value must also be chosen so that the external clock waveform is not deformed significantly.

Note: The allowable current rating of the external clock output pin must be greater than VDD/Rg.

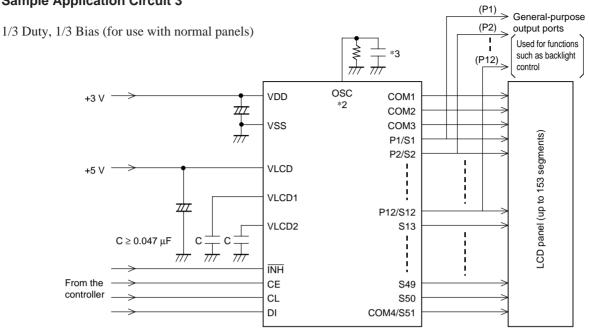

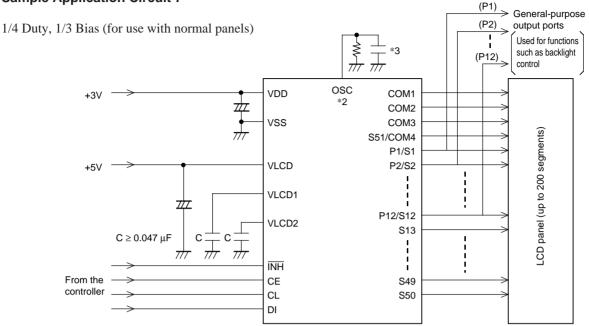

\*2 In RC oscillation mode, an external resistor, Rosc, and an external capacitor, Cosc, must be connected between the OSC pin and ground. In external clock mode is selected, a current protection resistor, Rg (4.7 to 47 kΩ) must be inserted between the external clock output pin (on the external oscillator) and the OSC pin. (See the "OSC Pin Peripheral Circuit" section.)

\*3 When a capacitor except the recommended external capacitance (Cosc = 1000 pF) is connected the OSC pin, we recommend that applications connect the OSC pin with a capacitor in the range 220 to 2200 pF.

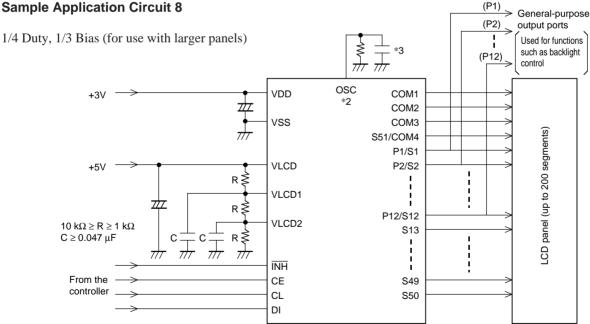

- \*2 In RC oscillation mode, an external resistor, Rosc, and an external capacitor, Cosc, must be connected between the OSC pin and ground. In external clock mode is selected, a current protection resistor, Rg (4.7 to 47 kΩ) must be inserted between the external clock output pin (on the external oscillator) and the OSC pin. (See the "OSC Pin Peripheral Circuit" section.)

- \*3 When a capacitor except the recommended external capacitance (Cosc = 1000 pF) is connected the OSC pin, we recommend that applications connect the OSC pin with a capacitor in the range 220 to 2200 pF.

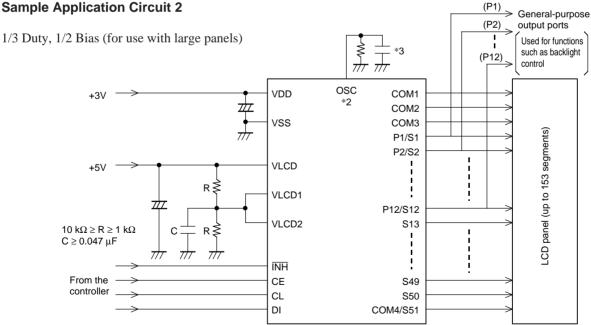

# **Sample Application Circuit 2**

\*2 In RC oscillation mode, an external resistor, Rosc, and an external capacitor, Cosc, must be connected between the OSC pin and ground. In external clock mode is selected, a current protection resistor, Rg (4.7 to 47 kΩ) must be inserted between the external clock output pin (on the external oscillator) and the OSC pin. (See the "OSC Pin Peripheral Circuit" section.)

\*3 When a capacitor except the recommended external capacitance (Cosc = 1000 pF) is connected the OSC pin, we recommend that applications connect the OSC pin with a capacitor in the range 220 to 2200 pF.

- \*2 In RC oscillation mode, an external resistor, Rosc, and an external capacitor, Cosc, must be connected between the OSC pin and ground. In external clock mode is selected, a current protection resistor, Rg (4.7 to 47 kΩ) must be inserted between the external clock output pin (on the external oscillator) and the OSC pin. (See the "OSC Pin Peripheral Circuit" section.)

- \*3 When a capacitor except the recommended external capacitance (Cosc = 1000 pF) is connected the OSC pin, we recommend that applications connect the OSC pin with a capacitor in the range 220 to 2200 pF.

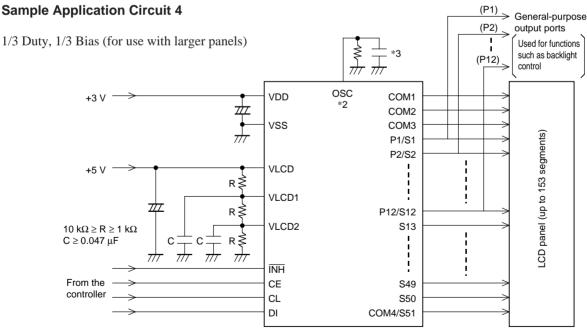

# **Sample Application Circuit 4**

\*2 In RC oscillation mode, an external resistor, Rosc, and an external capacitor, Cosc, must be connected between the OSC pin and ground. In external clock mode is selected, a current protection resistor, Rg (4.7 to 47 kΩ) must be inserted between the external clock output pin (on the external oscillator) and the OSC pin. (See the "OSC Pin Peripheral Circuit" section.)

\*3 When a capacitor except the recommended external capacitance (Cosc = 1000 pF) is connected the OSC pin, we recommend that applications connect the OSC pin with a capacitor in the range 220 to 2200 pF.

- \*2 In RC oscillation mode, an external resistor, Rosc, and an external capacitor, Cosc, must be connected between the OSC pin and ground. In external clock mode is selected, a current protection resistor, Rg (4.7 to 47 kΩ) must be inserted between the external clock output pin (on the external oscillator) and the OSC pin. (See the "OSC Pin Peripheral Circuit" section.)

- \*3 When a capacitor except the recommended external capacitance (Cosc = 1000 pF) is connected the OSC pin, we recommend that applications connect the OSC pin with a capacitor in the range 220 to 2200 pF.

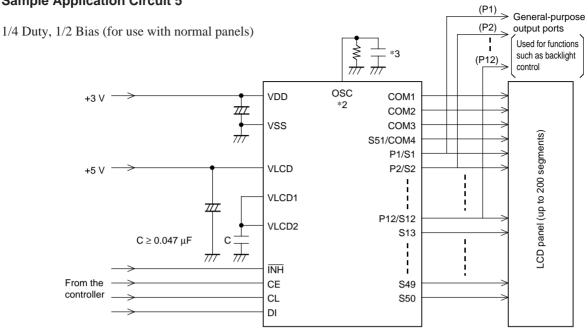

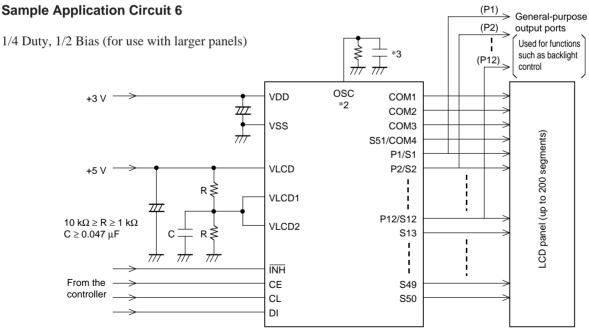

\*2 In RC oscillation mode, an external resistor, Rosc, and an external capacitor, Cosc, must be connected between the OSC pin and ground. In external clock mode is selected, a current protection resistor, Rg (4.7 to 47 kΩ) must be inserted between the external clock output pin (on the external oscillator) and the OSC pin. (See the "OSC Pin Peripheral Circuit" section.)

\*3 When a capacitor except the recommended external capacitance (Cosc = 1000 pF) is connected the OSC pin, we recommend that applications connect the OSC pin with a capacitor in the range 220 to 2200 pF.

- \*2 In RC oscillation mode, an external resistor, Rosc, and an external capacitor, Cosc, must be connected between the OSC pin and ground. In external clock mode is selected, a current protection resistor, Rg (4.7 to 47 kΩ) must be inserted between the external clock output pin (on the external oscillator) and the OSC pin. (See the "OSC Pin Peripheral Circuit" section.)

- \*3 When a capacitor except the recommended external capacitance (Cosc = 1000 pF) is connected the OSC pin, we recommend that applications connect the OSC pin with a capacitor in the range 220 to 2200 pF.

#### **Sample Application Circuit 8**

Downloaded from Arrow.com.

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any and all SANYO products described or contained herein fall under strategic products (including services) controlled under the Foreign Exchange and Foreign Trade Control Law of Japan, such products must not be exported without obtaining export license from the Ministry of International Trade and Industry in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of August, 2004. Specifications and information herein are subject to change without notice.