# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

### Most Current Documentation

To obtain the most up-to-date version of this documentation, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS3000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; <a href="http://www.microchip.com">http://www.microchip.com</a>

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# Table of Contents

| I.0 Preface                                       | 4   |

|---------------------------------------------------|-----|

| 2.0 Introduction                                  | 7   |

| 3.0 Ball Descriptions and Configuration           | 9   |

| 1.0 Register Map                                  | 19  |

| 5.0 I2C Slave Controller (UPD360-A/UPD360-B Only) | 20  |

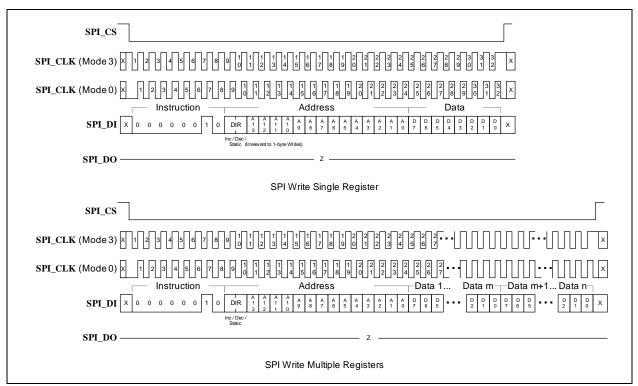

| 6.0 SPI Slave Controller (UPD360-C Only)          | 26  |

| 7.0 Clocks, Resets, and Power Management          | 31  |

| 3.0 System Control                                | 35  |

| 9.0 Cable Plug Orientation and Detection          | 68  |

| 0.0 Baseband CC Interface (BCI)                   | 107 |

| 1.0 Power Delivery MAC                            | 111 |

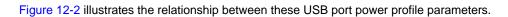

| 2.0 USB Port Power Controller (PPC)               | 171 |

| 3.0 Power Switch                                  | 182 |

| 14.0 DisplayPort Hot Plug Detect (HPD)            | 195 |

| 15.0 Watchdog Timer (WDT)                         | 202 |

| 6.0 Operational Characteristics                   | 206 |

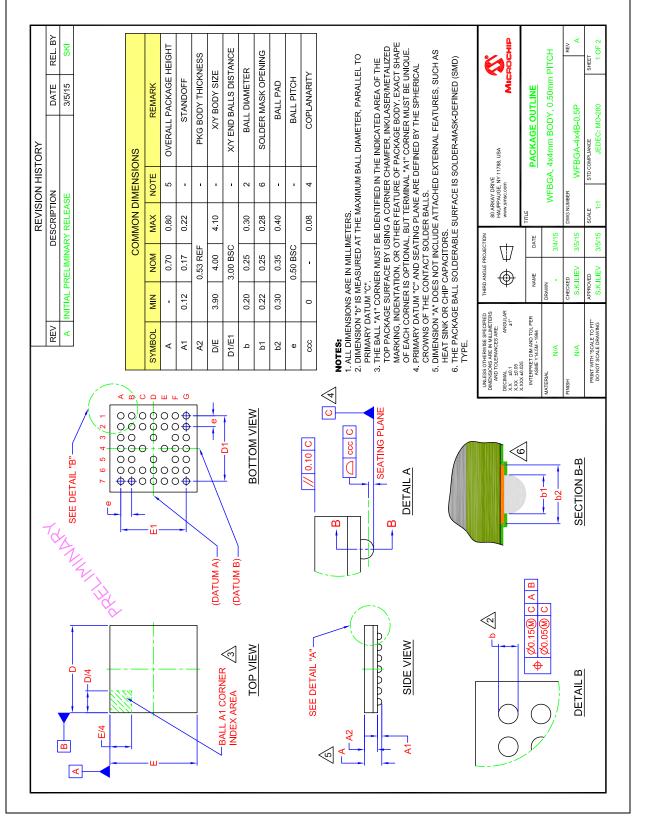

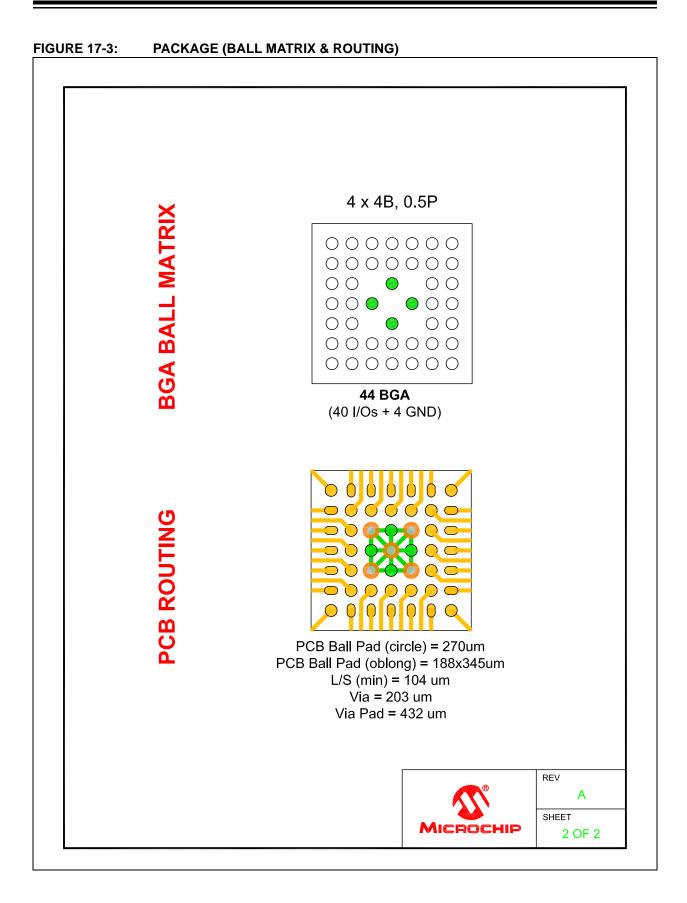

| 7.0 Package Information                           | 214 |

| Appendix A: Data Sheet Revision History           | 217 |

| The Microchip Web Site                            | 218 |

| Customer Change Notification Service              | 218 |

| Customer Support                                  | 218 |

| Customer Support                                  | 219 |

# 1.0 PREFACE

# 1.1 Glossary of Terms

## TABLE 1-1: GLOSSARY OF TERMS

| Term      | Definition                                                                                                                                        |  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ADC       | Analog to Digital Converter                                                                                                                       |  |  |

| AFE       | Analog Front End                                                                                                                                  |  |  |

| BCI       | Baseband CC Interface                                                                                                                             |  |  |

| Billboard | USB Billboard Device. A required USB device class for UFPs which support Alternate Modes in order to provide product information to the USB Host. |  |  |

| BIST      | Built-In Self Test                                                                                                                                |  |  |

| BMC       | Bi-phase Mark Coding                                                                                                                              |  |  |

| Byte      | 8-bits                                                                                                                                            |  |  |

| CC        | Generic reference to USB Type-C <sup>™</sup> Cable / Connector CC1/CC2 pins                                                                       |  |  |

| CSR       | Control and Status Register                                                                                                                       |  |  |

| DB        | Dead Battery                                                                                                                                      |  |  |

| DFP       | Downstream Facing Port (USB Type-C <sup>™</sup> Specification definition)                                                                         |  |  |

| DP        | DisplayPort (a VESA standard interface)                                                                                                           |  |  |

| DPM       | Device Policy Manager (PD Specification definition)                                                                                               |  |  |

| DRP       | Dual Role Power (USB Type-C <sup>™</sup> Specification definition)                                                                                |  |  |

| DWORD     | 32-bits                                                                                                                                           |  |  |

| EC        | Embedded Controller                                                                                                                               |  |  |

| EP        | USB Endpoint                                                                                                                                      |  |  |

| FIFO      | First In First Out buffer                                                                                                                         |  |  |

| FW        | Firmware                                                                                                                                          |  |  |

| FS        | Full-Speed                                                                                                                                        |  |  |

| Host      | External system (Includes processor, application software, etc.)                                                                                  |  |  |

| HPD       | Hot-Plug Detect functionality as defined by DisplayPort and DisplayPort Alternate Mode speci-<br>fications                                        |  |  |

| HS        | High-Speed                                                                                                                                        |  |  |

| HW        | Hardware (Refers to function implemented by the device)                                                                                           |  |  |

| IC        | Integrated Circuit                                                                                                                                |  |  |

| IFC       | InterFrame Gap                                                                                                                                    |  |  |

| LDO       | Linear Drop-Out regulator                                                                                                                         |  |  |

| MAC       | Media Access Controller                                                                                                                           |  |  |

| Microchip | Microchip Technology Incorporated                                                                                                                 |  |  |

| N/A       | Not Applicable                                                                                                                                    |  |  |

| OCS       | Over-Current Sense                                                                                                                                |  |  |

| PCS       | Physical Coding Sublayer                                                                                                                          |  |  |

| PD / UPD  | USB Power Delivery                                                                                                                                |  |  |

| PIO       | General Purpose I/O                                                                                                                               |  |  |

| PMIC      | Power Management Integrated Circuit                                                                                                               |  |  |

| POR       | Power-On Reset                                                                                                                                    |  |  |

| PRBS      | Pseudo Random Binary Sequence                                                                                                                     |  |  |

| QWORD     | 64-bits                                                                                                                                           |  |  |

| SA        | Source Address                                                                                                                                    |  |  |

| Term        | Definition                                                    |  |  |

|-------------|---------------------------------------------------------------|--|--|

| SBU         | SideBand Use                                                  |  |  |

| SCSR        | System Control and Status Register                            |  |  |

| SPM         | ystem Policy Manager (PD Specification definition)            |  |  |

| SS          | SuperSpeed                                                    |  |  |

| SVDM        | Standard/Vendor Defined Message (PD Specification definition) |  |  |

| SVID        | tandard/Vendor IDentity (PD Specification definition)         |  |  |

| TCPC        | JSB Type-C <sup>™</sup> Port Controller                       |  |  |

| UFP         | Upstream Facing Port (USB Type-C™ Specification definition)   |  |  |

| USB         | Universal Serial Bus                                          |  |  |

| USB Type-C™ | USB Type-C <sup>™</sup> Cable / Connector                     |  |  |

| VDO         | Vendor-defined Object (PD Specification definition)           |  |  |

| VSM         | Vendor Specific Messaging                                     |  |  |

| WORD        | 16-bits                                                       |  |  |

| ZLP         | Zero Length USB Packet                                        |  |  |

# TABLE 1-1: GLOSSARY OF TERMS (CONTINUED)

# 1.2 Buffer Types

## TABLE 1-2:BUFFER TYPES

| Buffer Type | Description                                                                                                                                                                                                                                          |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| IS          | Schmitt-triggered input                                                                                                                                                                                                                              |  |  |

| I2C         | I <sup>2</sup> C interface                                                                                                                                                                                                                           |  |  |

| O8          | Output with 8 mA sink and 8 mA source                                                                                                                                                                                                                |  |  |

| OD8         | Open-drain output with 8 mA sink                                                                                                                                                                                                                     |  |  |

| PU          | 70k (typical) internal pull-up. Unless otherwise noted in the pin description, internal pull-ups are always enabled.                                                                                                                                 |  |  |

|             | <b>Note:</b> Internal pull-up resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled high, an external resistor must be added.  |  |  |

| PD          | 70k (typical) internal pull-down. Unless otherwise noted in the pin description, internal pull-<br>downs are always enabled.                                                                                                                         |  |  |

|             | <b>Note:</b> Internal pull-down resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled low, an external resistor must be added. |  |  |

| AIO         | Analog bidirectional                                                                                                                                                                                                                                 |  |  |

| Р           | Power pin                                                                                                                                                                                                                                            |  |  |

Note: Digital signals are not 5V tolerant unless specified.

**Note:** Refer to Section 16.5, "DC Characteristics," on page 208 for the electrical characteristics of the various buffers.

<sup>© 2016-2017</sup> Microchip Technology Inc.

# 1.3 Register Nomenclature

| Register Bit Type Notation | Register Bit Description                                                                                                                                                                                                                                                                                                         |  |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| R                          | Read: A register or bit with this attribute can be read.                                                                                                                                                                                                                                                                         |  |  |

| W                          | Write: A register or bit with this attribute can be written.                                                                                                                                                                                                                                                                     |  |  |

| RO                         | Read only: Read only. Writes have no effect.                                                                                                                                                                                                                                                                                     |  |  |

| RS                         | Read to Set: This bit is set on read.                                                                                                                                                                                                                                                                                            |  |  |

| WO                         | Write only: If a register or bit is write-only, reads will return unspecified data.                                                                                                                                                                                                                                              |  |  |

| W1S                        | Write One to Set: Writing a one sets the value. Writing a zero has no effect.                                                                                                                                                                                                                                                    |  |  |

| W1C                        | Write One to Clear: Writing a one clears the value. Writing a zero has no effect.                                                                                                                                                                                                                                                |  |  |

| WC                         | Write Anything to Clear: Writing anything clears the value.                                                                                                                                                                                                                                                                      |  |  |

| LL                         | Latch Low: Clear on read of register.                                                                                                                                                                                                                                                                                            |  |  |

| LH                         | Latch High: Clear on read of register.                                                                                                                                                                                                                                                                                           |  |  |

| SC                         | <b>Self-Clearing:</b> Contents are self-cleared after the being set. Writes of zero have no effect. Contents can be read.                                                                                                                                                                                                        |  |  |

| RO/LH                      | <b>Read Only, Latch High:</b> Bits with this attribute will stay high until the bit is read. After it is read, the bit will remain high, but will change to low if the condition that caused the bit to go high is removed. If the bit has not been read, the bit will remain high regardless of a change to the high condition. |  |  |

| NASR                       | Not Affected by Software Reset. The state of NASR bits do not change on assertion of a software reset.                                                                                                                                                                                                                           |  |  |

| RESERVED                   | <b>Reserved Field:</b> Reserved fields must be written with zeros, unless otherwise indi-<br>cated, to ensure future compatibility. The value of reserved bits is not guaranteed on a<br>read.                                                                                                                                   |  |  |

## TABLE 1-3: REGISTER NOMENCLATURE

## 1.4 References

- NXP I<sup>2</sup>C-Bus Specification (UM10204, April 4, 2014): www.nxp.com/documents/user\_manual/UM10204.pdf

- USB Power Delivery and USB Type-C<sup>™</sup> Specifications: http://www.usb.org/developers/docs/usb\_31\_102015.zip

- VESA DisplayPort Alternate Mode Specification 1.0: http://www.vesa.org

# 2.0 INTRODUCTION

# 2.1 General Description

The UPD360 is a highly integrated, small form factor USB Type-C Power Delivery (PD) Port Controller designed to adhere to the USB Type-C<sup>™</sup> Cable and Connector Specification and USB Power Delivery 2.0 Specification. The UPD360 provides cable plug orientation and detection for a USB Type-C receptacle and implements baseband communication with a partner USB Type-C device via the integrated USB Power Delivery 2.0 MAC. The device can function in Standalone UFP/DFP modes, or utilize the integrated I<sup>2</sup>C/SPI interface to connect to a companion CPU/SoC (dependent on device version, see Section 2.2, "UPD360 Family Differences Summary").

Additionally, the UPD360 integrates many of the analog discrete components required for USB Type-C PD applications, including two VCONN FETs with Rp/Rd switching, a port power controller that supports up to 5V/3A on VBUS, and current and voltage sense circuitry for over-voltage/current detection. By integrating many of the analog discrete components required for USB Type-C PD applications, the UPD360 provides a low cost, low power, small footprint (4 x 4 mm) solution for consumer (notebooks, desktop PCs, smartphones, tablets, monitors, docking stations) applications.

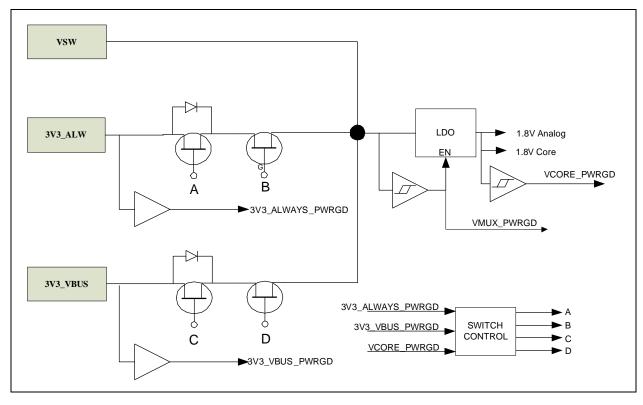

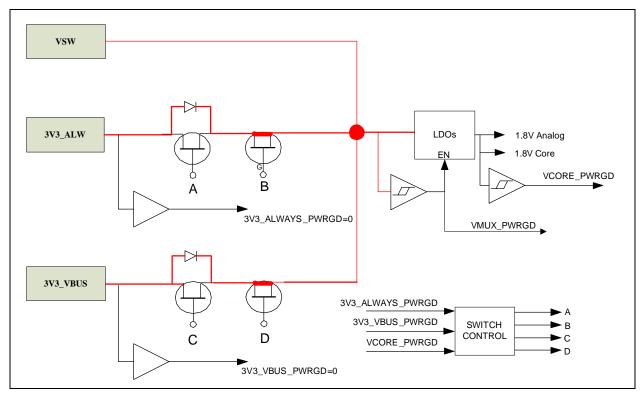

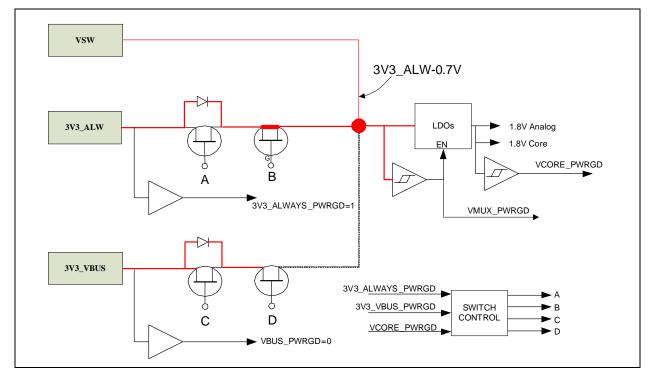

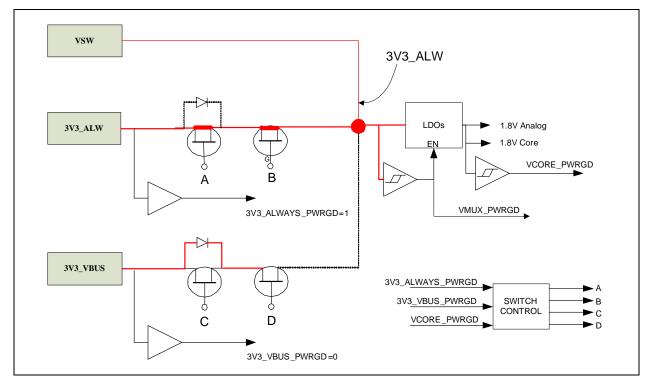

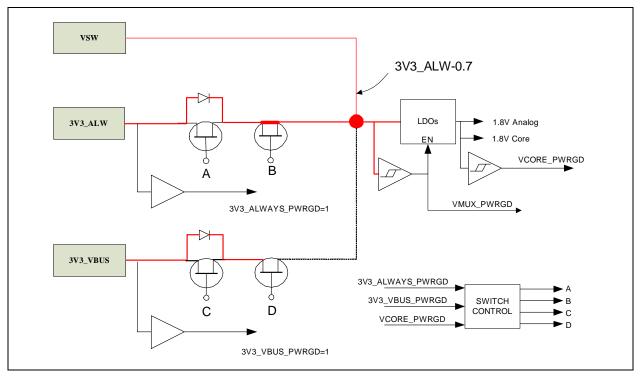

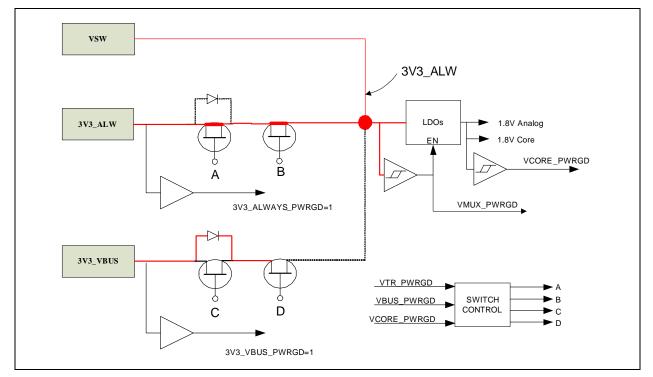

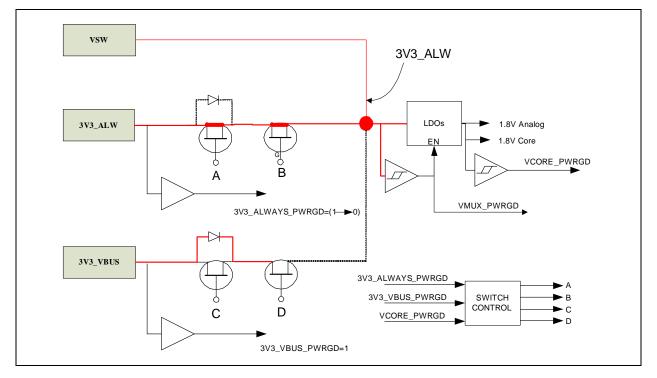

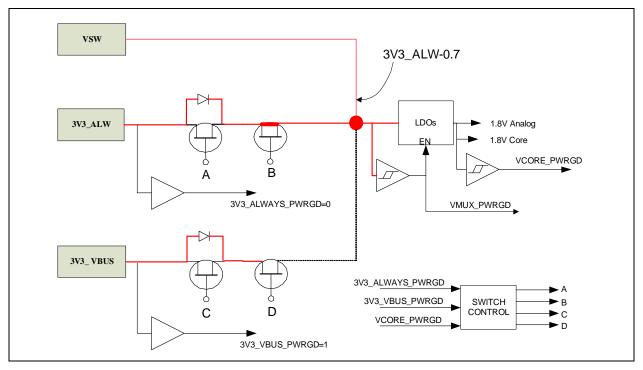

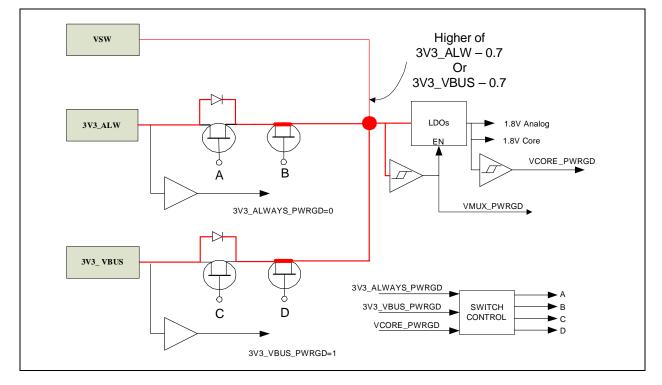

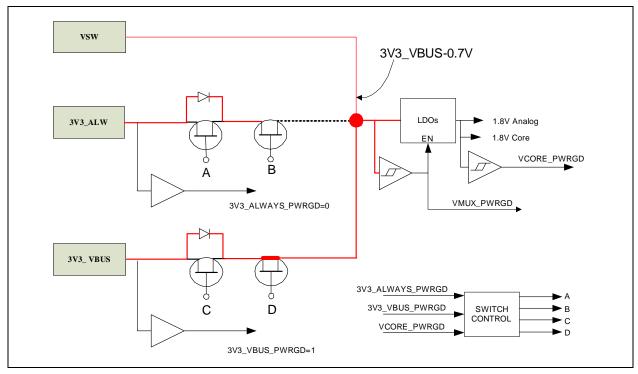

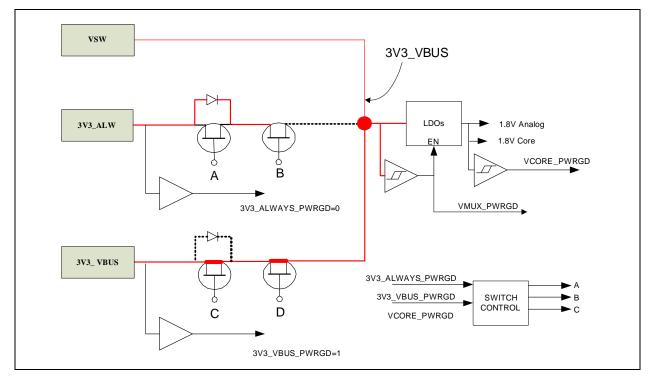

To enable the UPD360 to efficiently support dead battery use cases, an integrated power switch is provided to select between two external 3.3V supplies (VBUS and main). This effectively allows connection detection and system wakeup without external processor intervention (external processor in sleep mode).

The UPD360 is also capable of negotiating alternate modes over USB Type-C connectors using the Power Delivery 2.0 protocol. Both DisplayPort and Thunderbolt operation over USB Type-C connectors are supported in addition to other major protocols.

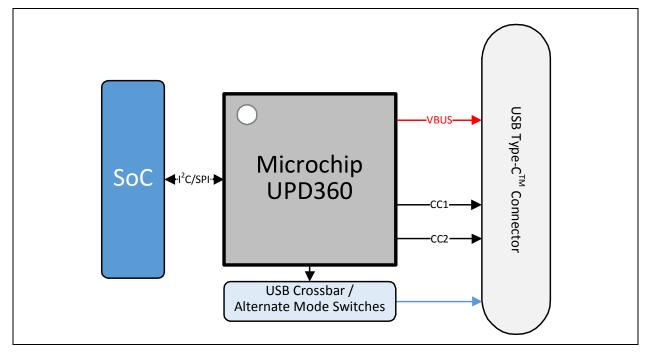

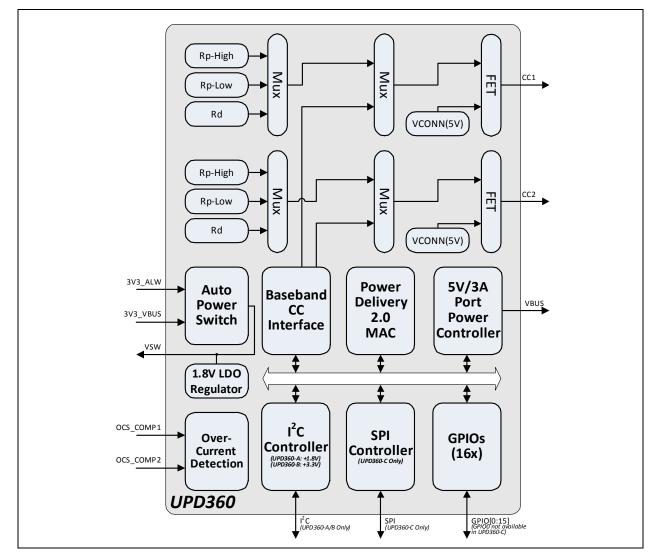

A system diagram utilizing the UPD360 is shown in Figure 2-1. An internal block diagram of the UPD360 is shown in Figure 2-2.

# FIGURE 2-1: SYSTEM BLOCK DIAGRAM

<sup>© 2016-2017</sup> Microchip Technology Inc.

FIGURE 2-2: INTERNAL BLOCK DIAGRAM

# 2.2 UPD360 Family Differences Summary

The UPD360 is available in three versions:

- UPD360-A

- UPD360-B

- UPD360-C

A summary of the differences between these versions is provided in Table 2-1. Device specific features that do no pertain to the entire UPD360 family are called out independently throughout this document. For ordering information, refer to the Product Identification System on page 219.

TABLE 2-1: UPD360 FAMILY DIFFERENCES

| Device   | +1.8V I <sup>2</sup> C Interface | +3.3V I <sup>2</sup> C Interface | SPI Interface | Standalone UFP/DFP Mode |

|----------|----------------------------------|----------------------------------|---------------|-------------------------|

| UPD360-A | X                                |                                  |               | X                       |

| UPD360-B |                                  | Х                                |               | X                       |

| UPD360-C |                                  |                                  | Х             |                         |

DS00002084C-page 8

# 3.0 BALL DESCRIPTIONS AND CONFIGURATION

# 3.1 Ball Assignments

The ball assignments for the UPD360-A/UPD360-B are detailed in Section 3.1.1, "UPD360-A/UPD360-B Ball Assignments," on page 9. The ball assignments for the UPD360-C are detailed in Section 3.1.1, "UPD360-A/UPD360-B Ball Assignments," on page 9. For information on the differences between the UPD360 family of devices, refer to Section 2.2, "UPD360 Family Differences Summary," on page 8.

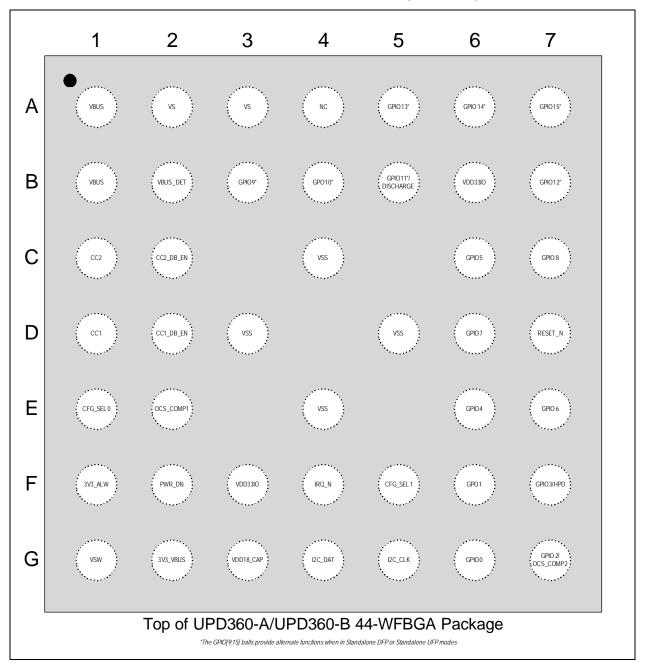

## 3.1.1 UPD360-A/UPD360-B BALL ASSIGNMENTS

The device ball diagram for the UPD360-A/UPD360-B can be seen in Figure 3-1. Table 3-1 provides a UPD360-A/UPD360-B ball assignment table. Ball descriptions are provided in Section 3.2, "Ball Descriptions".

FIGURE 3-1: UPD360-A/UPD360-B BALL ASSIGNMENTS (TOP VIEW)

© 2016-2017 Microchip Technology Inc.

| I. OFD300-A/OFD300-B BALL A33IGNIVIEN I 3 |                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                  | Ball                                                                                                                                                                                                | Pin Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VBUS                                      | D5                                                                                                                                                                                                  | VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VS                                        | D6                                                                                                                                                                                                  | GPIO7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VS                                        | D7                                                                                                                                                                                                  | RESET_N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| NC                                        | E1                                                                                                                                                                                                  | CFG_SEL0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GPIO13 (Note 3-1)                         | E2                                                                                                                                                                                                  | OCS_COMP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| GPIO14 (Note 3-1)                         | E4                                                                                                                                                                                                  | VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GPIO15 (Note 3-1)                         | E6                                                                                                                                                                                                  | GPIO4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VBUS                                      | E7                                                                                                                                                                                                  | GPIO6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VBUS_DET                                  | F1                                                                                                                                                                                                  | 3V3_ALW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| GPIO9 (Note 3-1)                          | F2                                                                                                                                                                                                  | PWR_DN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| GPO10 (Note 3-1) (Note 3-2)               | F3                                                                                                                                                                                                  | VDD33IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| GPIO11/DISCHARGE (Note 3-1)               | F4                                                                                                                                                                                                  | IRQ_N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VDD33IO                                   | F5                                                                                                                                                                                                  | CFG_SEL1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GPIO12 (Note 3-1)                         | F6                                                                                                                                                                                                  | GPO1 (Note 3-2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CC2                                       | F7                                                                                                                                                                                                  | GPIO3/HPD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CC2_DB_EN                                 | G1                                                                                                                                                                                                  | VSW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VSS                                       | G2                                                                                                                                                                                                  | 3V3_VBUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GPIO5                                     | G3                                                                                                                                                                                                  | VDD18_CAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| GPIO8                                     | G4                                                                                                                                                                                                  | I2C_DAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CC1                                       | G5                                                                                                                                                                                                  | I2C_CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CC1_DB_EN                                 | G6                                                                                                                                                                                                  | GPIO0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VSS                                       | G7                                                                                                                                                                                                  | GPIO2/OCS_COMP2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                           | Pin NameVBUSVSVSNCGPIO13 (Note 3-1)GPIO14 (Note 3-1)GPIO15 (Note 3-1)VBUS_DETGPIO9 (Note 3-1)GPIO10 (Note 3-1)GPIO11/DISCHARGE (Note 3-1)VDD33IOGPIO12 (Note 3-1)CC2CC2_DB_ENVSSGPIO5GPIO8CC1_DB_EN | Pin Name         Ball           VBUS         D5           VS         D6           VS         D7           NC         E1           GPIO13 (Note 3-1)         E2           GPIO14 (Note 3-1)         E4           GPIO15 (Note 3-1)         E6           VBUS         E7           VBUS_DET         F1           GPIO10 (Note 3-1)         F2           GPO10 (Note 3-1)         F2           GPO10 (Note 3-1)         F4           VDD33IO         F5           GPIO12 (Note 3-1)         F6           CC2         F7           CC2_DB_EN         G1           VSS         G2           GPIO5         G3           GPIO8         G4           CC1_DB_EN         G6 |

TABLE 3-1: UPD360-A/UPD360-B BALL ASSIGNMENTS

**Note 3-1** This ball provides alternate functions when in Standalone DFP and Standalone UFP Modes. Refer to Section 3.1.1.1, "UPD360-A/UPD360-B GPIO[9:15] Functions in Standalone DFP/UFP Modes" for additional information.

Note 3-2 This general purpose signal can only function as an output and must not be pulled-up externally during RESET\_N assertion.

## 3.1.1.1 UPD360-A/UPD360-B GPIO[9:15] Functions in Standalone DFP/UFP Modes

When the UPD360-A/UPD360-B is configured in Standalone DFP or Standalone UFP modes, the following GPIO balls are assigned specific alternate functions, as detailed in Table 3-2.

| Ball | I <sup>2</sup> C Companion Mode | Standalone DFP Mode | Standalone UFP Mode |

|------|---------------------------------|---------------------|---------------------|

| B3   | GPIO9                           | ORIENTATION         | ORIENTATION         |

| B4   | GPO10                           | ATTACH              | ATTACH              |

| B5   | GPIO11                          | OCS_N               | GPIO11              |

| B7   | GPIO12                          | PWR_EN              | SINK_5V_LEGACY_N    |

| A5   | GPIO13                          | PWR_CAP0            | SINK_5V_1A5_N       |

| A6   | GPIO14                          | PWR_CAP1            | SINK_5V_3A0_N       |

| A7   | GPIO15                          | ERR_RECOVER         | GPIO15              |

#### TABLE 3-2: ALTERNATE GPIO[9:15] FUNCTIONS IN STANDALONE DFP/UFP MODES

<sup>© 2016-2017</sup> Microchip Technology Inc.

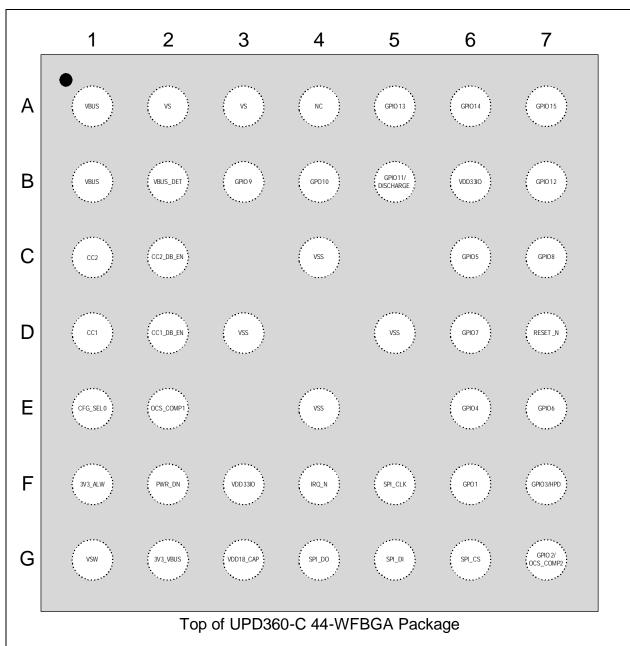

# 3.1.2 UPD360-C BALL ASSIGNMENTS

The device ball diagram for the UPD360-C can be seen in Figure 3-2. Table 3-3 provides a UPD360-C ball assignment table. Ball descriptions are provided in Section 3.2, "Ball Descriptions".

FIGURE 3-2: UPD360-C BALL ASSIGNMENTS (TOP VIEW)

| IADEE 5-5. |                  | 0    |                 |

|------------|------------------|------|-----------------|

| Ball       | Pin Name         | Ball | Pin Name        |

| A1         | VBUS             | D5   | VSS             |

| A2         | VS               | D6   | GPIO7           |

| A3         | VS               | D7   | RESET_N         |

| A4         | NC               | E1   | CFG_SEL0        |

| A5         | GPIO13           | E2   | OCS_COMP1       |

| A6         | GPIO14           | E4   | VSS             |

| A7         | GPIO15           | E6   | GPIO4           |

| B1         | VBUS             | E7   | GPIO6           |

| B2         | VBUS_DET         | F1   | 3V3_ALW         |

| B3         | GPIO9            | F2   | PWR_DN          |

| B4         | GPO10 (Note 3-3) | F3   | VDD33IO         |

| B5         | GPIO11/DISCHARGE | F4   | IRQ_N           |

| B6         | VDD33IO          | F5   | SPI_CLK         |

| B7         | GPIO12           | F6   | GPO1 (Note 3-3) |

| C1         | CC2              | F7   | GPIO3/HPD       |

| C2         | CC2_DB_EN        | G1   | VSW             |

| C4         | VSS              | G2   | 3V3_VBUS        |

| C6         | GPIO5            | G3   | VDD18_CAP       |

| C7         | GPIO8            | G4   | SPI_DO          |

| D1         | CC1              | G5   | SPI_DI          |

| D2         | CC1_DB_EN        | G6   | SPI_CS          |

| D3         | VSS              | G7   | GPIO2/OCS_COMP2 |

| IADLE 3-3. UPD300-C DALL ASSIGNWIEN IS | TABLE 3-3: | UPD360-C BALL ASSIGNMENTS |

|----------------------------------------|------------|---------------------------|

|----------------------------------------|------------|---------------------------|

Note 3-3 This general purpose signal can only function as an output and must not be pulled-up externally during RESET\_N assertion.

# 3.2 Ball Descriptions

This sections details the functions of the various device signals.

| TADLE 3-4:                    |                        |                |                                                                                                                                                                                                                   |  |  |

|-------------------------------|------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                          | SYMBOL                 | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                       |  |  |

|                               |                        | USB            | Type-C™                                                                                                                                                                                                           |  |  |

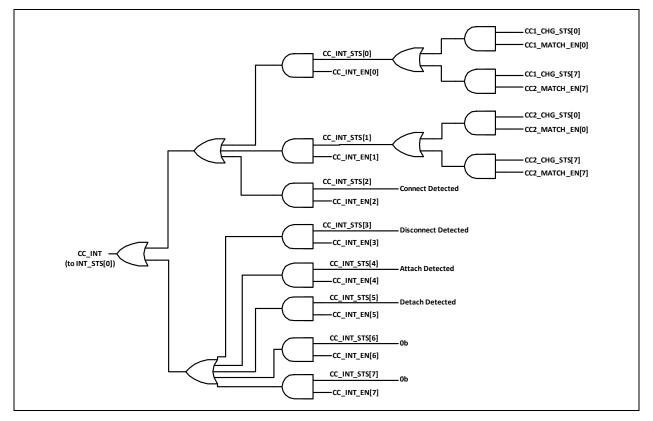

| Configuration<br>Channel 1    | CC1                    | AIO            | Configuration Channel (CC) used in the discovery, configu-<br>ration and management of connections across a USB<br>Type-C cable. Refer to Section 9.1, "CC Comparator," on<br>page 68 for additional information. |  |  |

| Configuration<br>Channel 2    | CC2                    | AIO            | Configuration Channel (CC) used in the discovery, configu-<br>ration and management of connections across a USB<br>Type-C cable. Refer to Section 9.1, "CC Comparator," on<br>page 68 for additional information. |  |  |

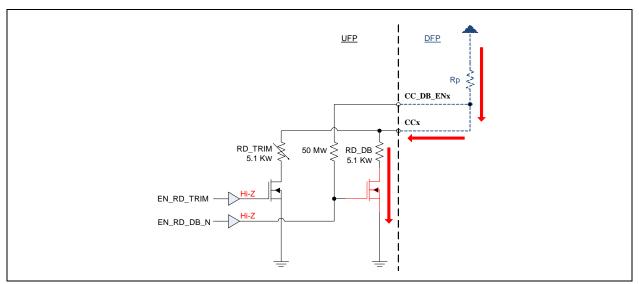

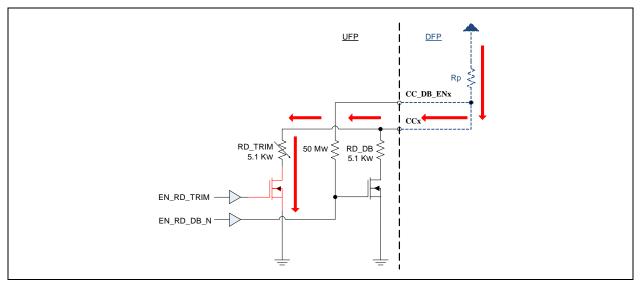

| CC1<br>Dead Battery<br>Enable | CC1_DB_EN              | AIO            | Determines whether CC1 broadcasts Rd pull-down<br>or Hi-Z. Refer to Section 9.6, "Dead Battery," on page 77 for<br>additional information.                                                                        |  |  |

|                               |                        |                | Note: Tie to CC1 if dead battery is supported. Otherwise, tie to ground.                                                                                                                                          |  |  |

| CC2<br>Dead Battery<br>Enable | CC2_DB_EN              | AIO            | Determines whether CC2 broadcasts Rd pull-down<br>or Hi-Z. Refer to Section 9.6, "Dead Battery," on page 77 for<br>additional information.                                                                        |  |  |

|                               |                        |                | Note: Tie to CC2 if dead battery is supported. Otherwise, tie to ground.                                                                                                                                          |  |  |

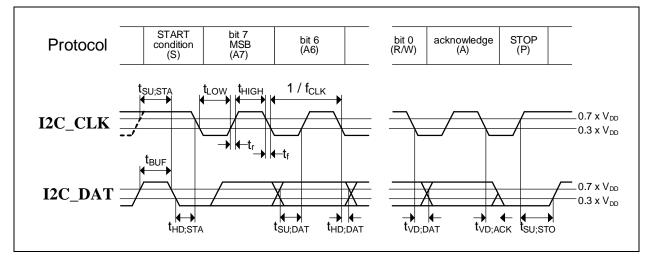

|                               | I <sup>2</sup> C Int   | erface (UPD    | 360-A/UPD360-B Only)                                                                                                                                                                                              |  |  |

| I <sup>2</sup> C Clock        | I2C_CLK                | I2C            | I <sup>2</sup> C clock signal<br>(+1.8V for UPD360-A, +3.3V for UPD360-B)                                                                                                                                         |  |  |

| I <sup>2</sup> C Data         | I2C_DAT                | I2C            | I <sup>2</sup> C data signal<br>(+1.8V for UPD360-A, +3.3V for UPD360-B)                                                                                                                                          |  |  |

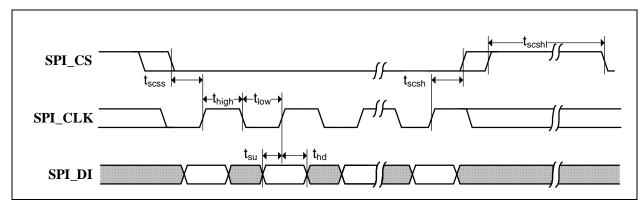

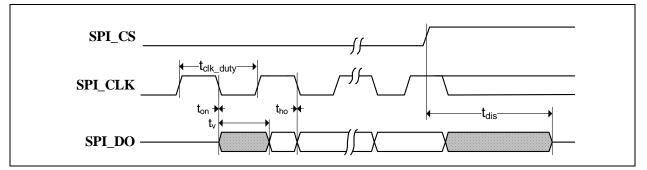

|                               | SPI                    | Interface Pi   | ns (UPD360-C Only)                                                                                                                                                                                                |  |  |

| SPI Clock                     | SPI_CLK                | IS             | SPI clock.<br>The maximum supported SPI clock frequency is 25 MHz.                                                                                                                                                |  |  |

| SPI Data Out                  | SPI_DO                 | O8             | SPI output data.                                                                                                                                                                                                  |  |  |

| SPI Data In                   | SPI_DI                 | IS             | SPI input data.                                                                                                                                                                                                   |  |  |

| SPI Chip<br>Enable            | SPI_CS                 | IS             | Active low SPI chip enable input.                                                                                                                                                                                 |  |  |

|                               | Power Delivery Control |                |                                                                                                                                                                                                                   |  |  |

| Hot Plug Detect               | HPD                    | IS/O8          | DisplayPort Hot Plug Detection. Refer to Section 14.0, "DisplayPort Hot Plug Detect (HPD)," on page 195 for additional information.                                                                               |  |  |

| Discharge                     | DISCHARGE              | O8             | VBUS Discharge. Enables external VBUS discharge circuit when commanded by USB PD software.                                                                                                                        |  |  |

# TABLE 3-4: BALL DESCRIPTIONS

|                       | BALL DESCRIPTIONS | BUFFER |                                                                                                                                                                                                                                                                         |

|-----------------------|-------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                  | SYMBOL            | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                             |

| Type-C<br>Attach      | ATTACH            | O8     | In the Standalone UFP and Standalone DFP modes ( <i>UPD360-A/UPD360-B only</i> ), this signal indicates that the USB Type-C receptacles at the near and far end of the cable both have a plug-in. This pin is autonomously driven by the device in DFP standalone mode. |

|                       |                   |        | 0b: Nothing attached<br>1b: USB Type-C port has an end-end attached                                                                                                                                                                                                     |

|                       |                   |        | Refer to Section 9.10, "Standalone DFP (UPD360-A/<br>UPD360-B Only)" and Section 9.11, "Standalone UFP<br>(UPD360-A/UPD360-B Only)"for additional information.                                                                                                          |

|                       |                   |        | Note: Float this signal when unused.                                                                                                                                                                                                                                    |

|                       |                   |        | Note: This signal is not available in the UPD360-C.                                                                                                                                                                                                                     |

| Type-C<br>Orientation | ORIENTATION       | O8     | In the Standalone UFP and Standalone DFP modes (UPD360-A/UPD360-B only), this signal is used to indicate which CC pin is terminated by the attached DFP/UFP and is autonomously driven by the device in DFP standalone mode.                                            |

|                       |                   |        | DFP:<br>0b: CC1 pin is terminated by Rd.<br>1b: CC2 pin is terminated by Rd.                                                                                                                                                                                            |

|                       |                   |        | UFP:<br>0b: CC1 pin is pulled to a higher voltage than CC2.<br>1b: CC2 pin is pulled to a higher voltage than CC1.                                                                                                                                                      |

|                       |                   |        | Refer to Section 9.10, "Standalone DFP (UPD360-A/<br>UPD360-B Only)" and Section 9.11, "Standalone UFP<br>(UPD360-A/UPD360-B Only)"for additional information.                                                                                                          |

|                       |                   |        | Note: Float this signal when unused.                                                                                                                                                                                                                                    |

|                       |                   |        | <b>Note:</b> This signal is not available in the UPD360-C.                                                                                                                                                                                                              |

| Over-current<br>sense | OCS_N             | OD8    | In the Standalone DFP mode ( <i>UPD360-A/UPD360-B only</i> ), this active-low signal indicates over-current sense. This signal maps to the PPC_INT interrupt.                                                                                                           |

|                       |                   |        | Note: This signal is active-low. Float this signal when unused.                                                                                                                                                                                                         |

|                       |                   |        | <b>Note:</b> This signal is not available in the UPD360-C.                                                                                                                                                                                                              |

| VBUS Power<br>Enable  | PWR_EN            | IS     | In the Standalone DFP mode (UPD360-A/UPD360-B only), this signal is used as a port power switch enable for USB hubs.                                                                                                                                                    |

|                       |                   |        | <b>Note:</b> This signal should be tied to the Power Good signal from the VS supply.                                                                                                                                                                                    |

|                       |                   |        | <b>Note:</b> Tie this signal to ground when unused.                                                                                                                                                                                                                     |

|                       |                   |        | Note: This signal is not available in the UPD360-C.                                                                                                                                                                                                                     |

# TABLE 3-4: BALL DESCRIPTIONS (CONTINUED)

# **UPD360**

| TABLE 3-4:                | BALL DESCRIPTIONS | CONTINU        | ועסי                                                                                                                                                                                                                                |  |  |

|---------------------------|-------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                      | SYMBOL            | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                         |  |  |

| Power<br>Capability 0     | PWR_CAP0          | IS             | In the Standalone DFP mode, these signals define the charging current supported by the device.                                                                                                                                      |  |  |

| Power<br>Capability 1     | PWR_CAP1          | IS             | 00b: USB 2.0 Default Current<br>01b: USB 3.0 Default Current<br>10b: 1.5 A<br>11b: 3.0 A                                                                                                                                            |  |  |

|                           |                   |                | <b>Note:</b> It is not valid to change the state of PWR_CAP0 and PWR_CAP1 pins after reset is de-asserted.                                                                                                                          |  |  |

|                           |                   |                | Note: These signals are not available in the UPD360-<br>C.                                                                                                                                                                          |  |  |

| Error<br>Recovery         | ERR_RECOVER       | IS             | In Standalone DFP mode (UPD360-A/UPD360-B only), this<br>pin determines whether or not the USB Type-C logic shall<br>attempt to auto-recover from an OCS or other error.<br>Sources from either the Port Power Switch or VCONN FET. |  |  |

|                           |                   |                | Note: This signal is not available in the UPD360-C.                                                                                                                                                                                 |  |  |

| Sink Legacy<br>Current    | SINK_5V_LEGACY_N  | OD8            | In the Standalone UFP mode (UPD360-A/UPD360-B only), this pin asserts autonomously when a source has been detected that provides legacy USB current.                                                                                |  |  |

|                           |                   |                | <b>Note:</b> Float this signal when unused.                                                                                                                                                                                         |  |  |

|                           |                   |                | <b>Note:</b> This signal is not available in the UPD360-C.                                                                                                                                                                          |  |  |

| Sink 1.5A<br>Current      | SINK_5V_1A5_N     | OD8            | In the Standalone UFP mode (UPD360-A/UPD360-B only), this pin asserts autonomously when a source has been detected that provides 1.5A USB current.                                                                                  |  |  |

|                           |                   |                | <b>Note:</b> Float this signal when unused.                                                                                                                                                                                         |  |  |

|                           |                   |                | <b>Note:</b> This signal is not available in the UPD360-C.                                                                                                                                                                          |  |  |

| Sink 3A<br>Current        | SINK_5V_3A0_N     | OD8            | In the Standalone UFP mode (UPD360-A/UPD360-B only), this pin asserts autonomously when a source has been detected that provides 3.0A USB current.                                                                                  |  |  |

|                           |                   |                | Note: Float this signal when unused.                                                                                                                                                                                                |  |  |

|                           |                   |                | Note: This signal is not available in the UPD360-C.                                                                                                                                                                                 |  |  |

|                           |                   | Misce          | ellaneous                                                                                                                                                                                                                           |  |  |

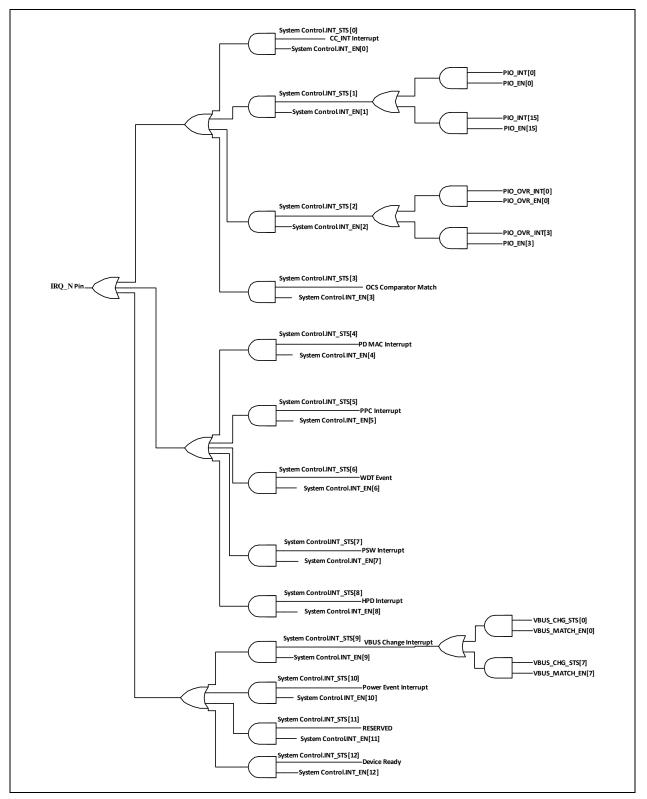

| Interrupt                 | IRQ_N             | OD8            | Active low interrupt signal.                                                                                                                                                                                                        |  |  |

|                           |                   |                | <b>Note:</b> Float this signal when unused.                                                                                                                                                                                         |  |  |

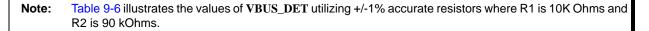

| VBUS<br>Detection         | VBUS_DET          | AIO            | Scaled down version of VBUS. Tie this signal to VBUS via a resistor divider.                                                                                                                                                        |  |  |

| Configuration<br>Select 0 | CFG_SEL0          | AIO            | This multi-level configuration signal is sampled after a sys-<br>tem reset to select the device's default mode of operation<br>based on the connected 1% precision resistor value.                                                  |  |  |

|                           |                   |                | Refer to Section 9.8.1, "Configuration Selection," on page 81 for additional information.                                                                                                                                           |  |  |

# TABLE 3-4: BALL DESCRIPTIONS (CONTINUED)

| NAME                           | SYMBOL                                         | BUFFER<br>TYPE        | DESCRIPTION                                                                                                                                                                                                                                  |  |  |  |

|--------------------------------|------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Configuration<br>Select 1      | CFG_SEL1                                       | AIO                   | This multi-level configuration signal is sampled after a system reset to select the device's default I <sup>2</sup> C slave address based on the connected 1% precision resistor value <i>(UPD360-A/UPD360-B only)</i> .                     |  |  |  |

|                                |                                                |                       | Refer to Section 9.8.1, "Configuration Selection," on page 81 for additional information.                                                                                                                                                    |  |  |  |

|                                |                                                |                       | Note: This signal is not available in the UPD360-C.                                                                                                                                                                                          |  |  |  |

| General<br>Purpose I/O<br>0-15 | GPIO0,<br>GPO1,<br>GPIO2,<br>GPIO3,            | IS/O8/<br>OD8<br>(PU) | The general purpose I/O signals are fully programmable as<br>either a push-pull output, an open-drain output, or a<br>Schmitt-triggered input (except <b>GPO1</b> and <b>GPO10</b> ). A pro-<br>grammable pull-up may optionally be enabled. |  |  |  |

|                                | GPIO4,<br>GPIO5,<br>GPIO6,<br>GPIO7,<br>GPIO8, |                       | Note: The GPO1 and GPO10 general purpose sig-<br>nals can only function as outputs and must<br>be kept in a low state coincident with de-<br>asserting RESET_N.                                                                              |  |  |  |

|                                | GPIO9,                                         |                       | Note: Tie these signals to ground when unused.                                                                                                                                                                                               |  |  |  |

|                                | GPO10                                          |                       | <b>Note:</b> External pull-ups and pull-downs shall be placed on GPIO pins to ensure that when in the reset state the inputs to external devices are driven to a valid state.                                                                |  |  |  |

|                                |                                                |                       | Note: GPIO0 is not available in the UPD360-C.                                                                                                                                                                                                |  |  |  |

|                                |                                                |                       | Note: In Standalone DFP/UFP modes (UPD360-A/<br>UPD360-B only), GPIOs 9-15 have alternate<br>dedicated functions, as defined in Section<br>3.1.1.1, "UPD360-A/UPD360-B GPIO[9:15]<br>Functions in Standalone DFP/UFP Modes," on<br>page 11.  |  |  |  |

|                                |                                                |                       | Refer to Section 8.2, "General Purpose I/O," on page 37 for additional information.                                                                                                                                                          |  |  |  |

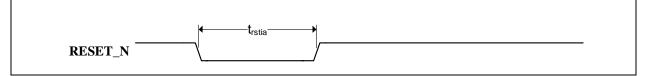

| System Reset                   | RESET_N                                        | IS                    | Active low system reset.                                                                                                                                                                                                                     |  |  |  |

|                                |                                                |                       | Note: If this signal is unused, it must be pulled up to VDD33IO.                                                                                                                                                                             |  |  |  |

|                                |                                                |                       | Refer to Section 7.7, "Reset Operation," on page 34 for additional information.                                                                                                                                                              |  |  |  |

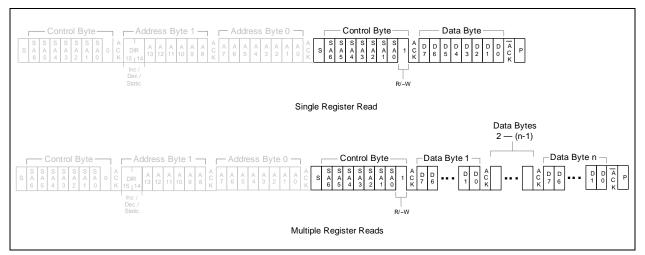

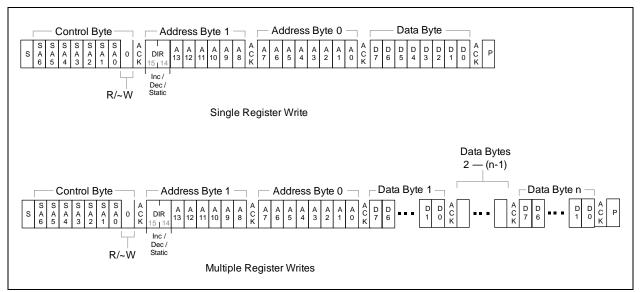

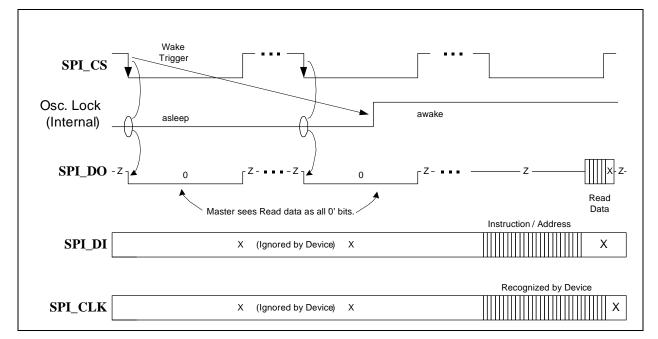

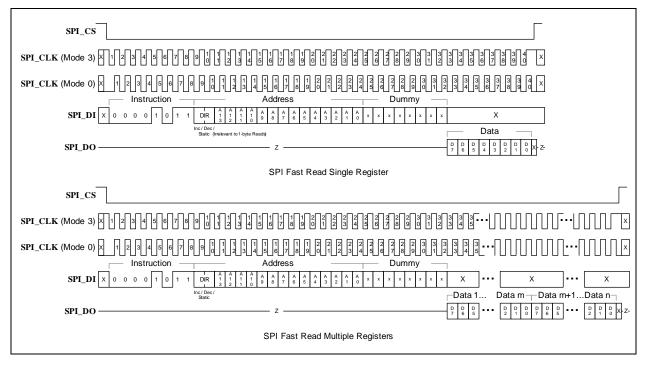

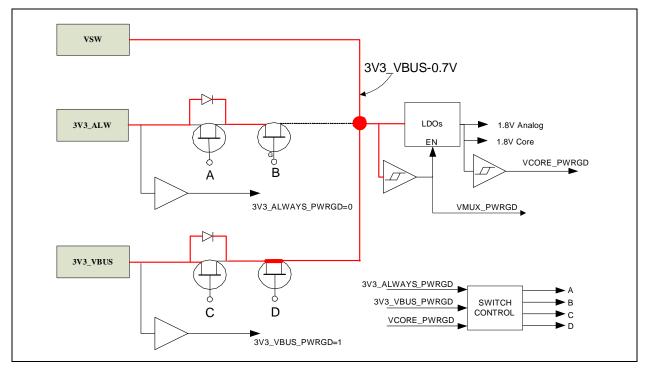

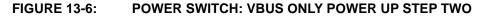

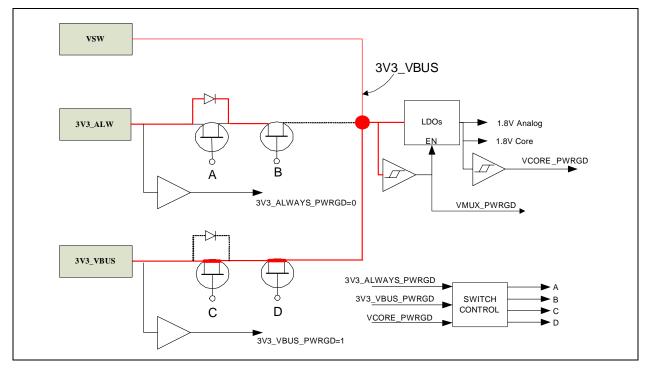

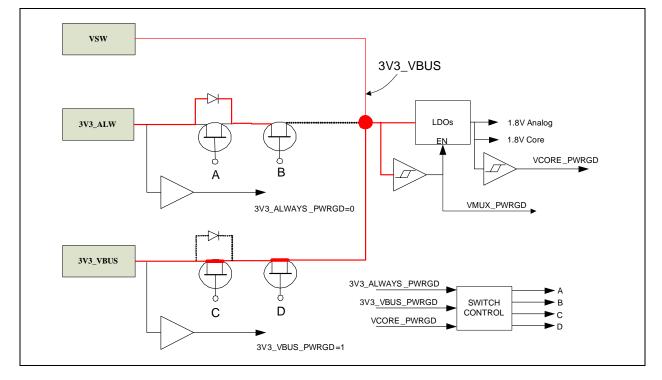

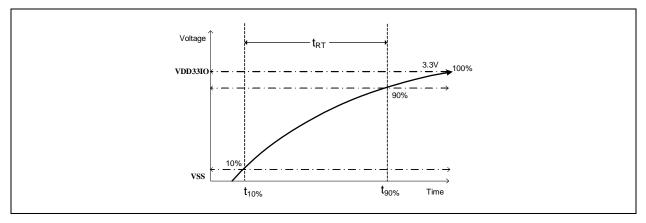

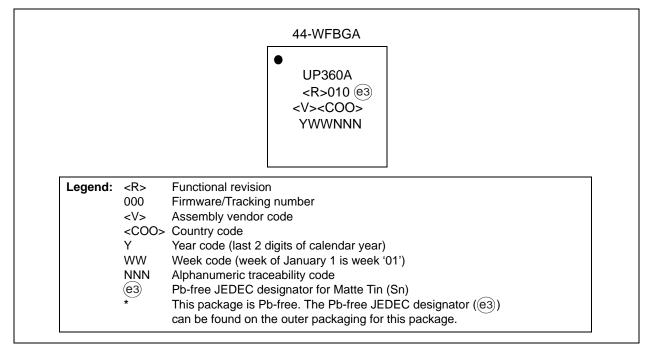

| Power Down                     | PWR_DN                                         | AI                    | When asserted, this signal places the device into the SLEEP state.                                                                                                                                                                           |  |  |  |