## Contents

| 1  | Турі  | Typical application                                   |  |  |  |  |  |  |

|----|-------|-------------------------------------------------------|--|--|--|--|--|--|

| 2  | Abso  | Absolute maximum ratings and operating conditions     |  |  |  |  |  |  |

| 3  | Elec  | trical characteristics5                               |  |  |  |  |  |  |

| 4  | Safe  | operating area                                        |  |  |  |  |  |  |

| 5  | Inter | modulation distortion product 17                      |  |  |  |  |  |  |

| 6  | Prin  | ted circuit board layout considerations               |  |  |  |  |  |  |

|    | 6.1   | Thermal information                                   |  |  |  |  |  |  |

| 7  | Nois  | e measurements                                        |  |  |  |  |  |  |

|    | 7.1   | Measurement of eN 24                                  |  |  |  |  |  |  |

|    | 7.2   | Measurement of iNn 25                                 |  |  |  |  |  |  |

|    | 7.3   | Measurement of iNp 25                                 |  |  |  |  |  |  |

| 8  | Pow   | er supply bypassing                                   |  |  |  |  |  |  |

|    | 8.1   | Single power supply 26                                |  |  |  |  |  |  |

|    | 8.2   | Channel separation and crosstalk 27                   |  |  |  |  |  |  |

| 9  | Cho   | osing the feedback circuit 28                         |  |  |  |  |  |  |

|    | 9.1   | The bias of an inverting amplifier 29                 |  |  |  |  |  |  |

|    | 9.2   | Active filtering                                      |  |  |  |  |  |  |

| 10 | Incre | easing the line level using active impedance matching |  |  |  |  |  |  |

| 11 | Pack  | Package information                                   |  |  |  |  |  |  |

| 12 | Orde  | Ordering information                                  |  |  |  |  |  |  |

| 13 | Revi  | sion history                                          |  |  |  |  |  |  |

## 1 Typical application

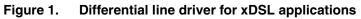

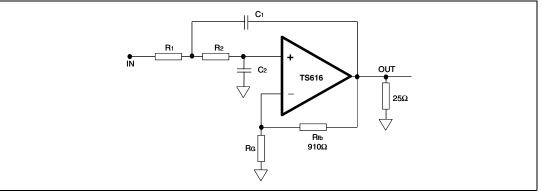

*Figure 1* shows a schematic of a typical xDSL application using the TS616.

8 +Vcc <u>12.5Ω</u> 1/2TS616 Vi Vo R2 1:2 R1 25Ω 100Ω GND R4 R3 Vi Vo 12.5Ω 1/2TS61 4-Vcc

## 2 Absolute maximum ratings and operating conditions

|                   | Absolute maximum ratings                                                          |             |      |

|-------------------|-----------------------------------------------------------------------------------|-------------|------|

| Symbol            | Parameter                                                                         | Value       | Unit |

| V <sub>CC</sub>   | Supply voltage <sup>(1)</sup>                                                     | ±7          | V    |

| V <sub>id</sub>   | Differential input voltage (2)                                                    | ±2          | V    |

| V <sub>in</sub>   | Input voltage range <sup>(3)</sup>                                                | ±6          | V    |

| T <sub>oper</sub> | Operating free air temperature range                                              | -40 to + 85 | °C   |

| T <sub>std</sub>  | Storage temperature                                                               | -65 to +150 | °C   |

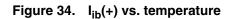

| Тj                | Maximum junction temperature                                                      | 150         | °C   |

| R <sub>thjc</sub> | Thermal resistance junction to case                                               | 16          | °C/W |

| R <sub>thja</sub> | Thermal resistance junction to ambient area                                       | 60          | °C/W |

| P <sub>max</sub>  | Maximum power dissipation (at $T_{amb} = 25^{\circ}$ C) for $T_j = 150^{\circ}$ C | 2           | w    |

| ESD               | HBM: human body model <sup>(4)</sup>                                              | 1.5         | kV   |

| only pins         | MM: machine model <sup>(5)</sup>                                                  | 2           | kV   |

| 1, 4, 7, 8        | CDM: charged device model <sup>(6)</sup>                                          | 200         | V    |

| ESD               | HBM: human body model <sup>(4)</sup>                                              | 1.5         | kV   |

| only pins         | MM: machine model <sup>(5)</sup>                                                  | 2           | kV   |

| 2, 3, 5, 6        | CDM: charged device model <sup>(6)</sup>                                          | 100         | V    |

|                   | Output short circuit                                                              | (7)         |      |

#### Table 1. Absolute maximum ratings

1. All voltage values, except differential voltage are with respect to network terminal.

- 2. Differential voltages are non-inverting input terminal with respect to the inverting input terminal.

- 3. The magnitude of input and output voltage must never exceed V<sub>CC</sub> +0.3 V.

- 4. Human body model: a 100 pF capacitor is charged to the specified voltage, then discharged through a 1.5 kΩ resistor between two pins of the device. This is done for all couples of connected pin combinations while the other pins are floating.

- 5. Machine model: a 200 pF capacitor is charged to the specified voltage, then discharged directly between two pins of the device with no external series resistor (internal resistor < 5  $\Omega$ ). This is done for all couples of connected pin combinations while the other pins are floating.

- 6. Charged device model: all pins and the package are charged together to the specified voltage and then discharged directly to the ground through only one pin. This is done for all pins.

- 7. An output current limitation protects the circuit from transient currents. Short-circuits can cause excessive heating. Destructive dissipation can result from short-circuits on amplifiers.

Table 2.Operating conditions

| Symbol           | Parameter                 | Value                                              | Unit |

|------------------|---------------------------|----------------------------------------------------|------|

| V <sub>CC</sub>  | Power supply voltage      | ±2.5 to ±6                                         | V    |

| V <sub>icm</sub> | Common mode input voltage | -V <sub>CC</sub> +1.5 V to +V <sub>CC</sub> -1.5 V | V    |

### TS616

## 3 Electrical characteristics

| Table 3.         | $V_{CC} = \pm 6 V, R_{fb} = 910 \Omega, I_{amb}$                        | = 25° C (unless otherwise spec                                                                 | cified) | 1    |      |        |

|------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------|------|------|--------|

| Symbol           | Parameter                                                               | Test conditions                                                                                | Min.    | Тур. | Max. | Unit   |

| DC perfor        | rmance                                                                  |                                                                                                |         |      |      |        |

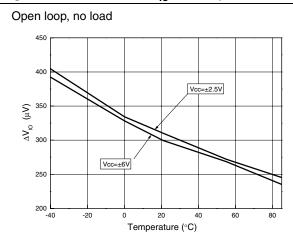

| V <sub>io</sub>  | Input offset voltage                                                    | T <sub>amb</sub>                                                                               |         | 1    | 3.5  |        |

|                  |                                                                         | T <sub>min</sub> < T <sub>amb</sub> < T <sub>max</sub>                                         |         | 1.6  |      | mV     |

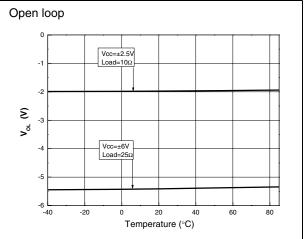

| $\Delta V_{io}$  | Differential input offset voltage                                       | T <sub>amb</sub> = 25°C                                                                        |         |      | 2.5  | mV     |

|                  | Positive input biss surrent                                             | T <sub>amb</sub>                                                                               |         | 5    | 30   |        |

| I <sub>ib+</sub> | Positive input bias current                                             | T <sub>min</sub> < T <sub>amb</sub> < T <sub>max</sub>                                         |         | 7.2  |      | μA     |

|                  | Negative input hise surrent                                             | T <sub>amb</sub>                                                                               |         | 3    | 15   |        |

| I <sub>ib-</sub> | Negative input bias current                                             | T <sub>min</sub> < T <sub>amb</sub> < T <sub>max</sub>                                         |         | 3.1  |      | μA     |

| Z <sub>IN+</sub> | Input(+) impedance                                                      |                                                                                                |         | 82   |      | kΩ     |

| Z <sub>IN-</sub> | Input(-) impedance                                                      |                                                                                                |         | 54   |      | Ω      |

| C <sub>IN+</sub> | Input(+) capacitance                                                    |                                                                                                |         | 1    |      | pF     |

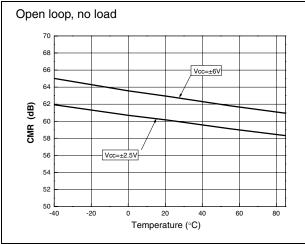

|                  | Common mode rejection ratio<br>20 log ( $\Delta V_{ic}/\Delta V_{io}$ ) | $\Delta V_{ic} = \pm 4.5 V$                                                                    | 58      | 64   |      | dB     |

| CMR              |                                                                         | T <sub>min</sub> < T <sub>amb</sub> < T <sub>max</sub>                                         |         | 62   |      |        |

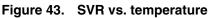

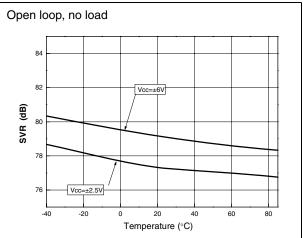

|                  | Supply voltage rejection ratio 20 log ( $\Delta V_{CC}/\Delta V_{io}$ ) | $\Delta V_{CC} = \pm 2.5 V$ to $\pm 6 V$                                                       | 72      | 81   |      | dB     |

| SVR              |                                                                         | T <sub>min</sub> < T <sub>amb</sub> < T <sub>max</sub>                                         |         | 80   |      |        |

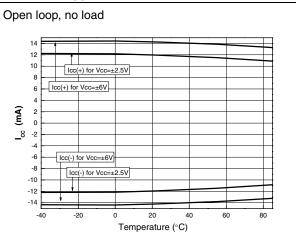

| I <sub>CC</sub>  | Total supply current per operator                                       | No load                                                                                        |         | 13.5 | 17   | mA     |

| Dynamic          | performance and output characte                                         | ristics                                                                                        |         | •    |      |        |

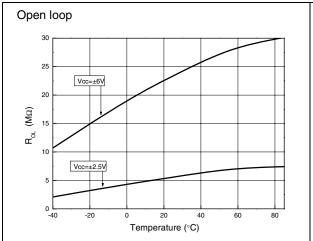

| P                | Open loop transimpedance                                                | $V_{out} = 7Vp-p, R_L = 25\Omega$                                                              | 5       | 13.5 |      | Мо     |

| R <sub>OL</sub>  |                                                                         | T <sub>min</sub> < T <sub>amb</sub> < T <sub>max</sub>                                         |         | 5.7  |      | MΩ     |

|                  | -3dB bandwidth                                                          | Small signal $V_{out} < 20mVp$<br>A <sub>V</sub> = 12dB, R <sub>L</sub> = 25 $\Omega$          | 25      | 40   |      | NAL I- |

| BW               | Full power bandwidth                                                    | Large signal V <sub>out</sub> = $3Vp$<br>A <sub>V</sub> = $12dB$ , R <sub>L</sub> = $25\Omega$ |         | 26   |      | MHz    |

|                  | Gain flatness @ 0.1dB                                                   | Small signal T <sub>amb</sub> <20mVp<br>A <sub>V</sub> = 12dB, R <sub>L</sub> = $25\Omega$     |         | 7    |      | MHz    |

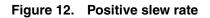

| T <sub>r</sub>   | Rise time                                                               | $V_{out} = 6Vp-p, A_V = 12dB, R_L = 25\Omega$                                                  |         | 10.6 |      | ns     |

| Т <sub>f</sub>   | Fall time                                                               | $V_{out} = 6Vp-p, A_V = 12dB, R_L = 25\Omega$                                                  |         | 12.2 |      | ns     |

| Ts               | Settling time                                                           | $V_{out} = 6Vp-p, A_V = 12dB, R_L = 25\Omega$                                                  |         | 50   |      | ns     |

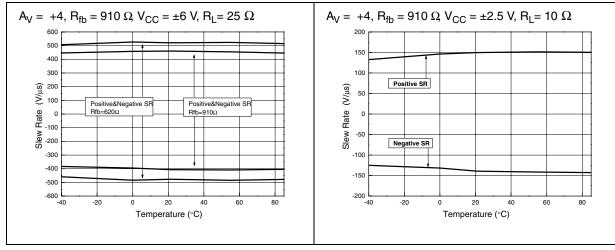

| SR               | Slew rate                                                               | $V_{out} = 6Vp-p, A_V = 12dB, R_L = 25\Omega$                                                  | 330     | 420  |      | V/µs   |

| V <sub>OH</sub>  | High level output voltage                                               | $R_L = 25\Omega$ connected to GND                                                              | 4.8     | 5.05 |      | V      |

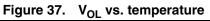

| V <sub>OL</sub>  | Low level output voltage                                                | $R_{\rm I} = 25\Omega$ Connected to GND                                                        |         | -5.3 | -5.1 | V      |

| Table 3. | $V_{CC} = \pm 6 V$ , $R_{fb} = 910 \Omega$ , $T_{amb} = 25^{\circ} C$ (unless otherwise specified) |

|----------|----------------------------------------------------------------------------------------------------|

|----------|----------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                                                      | Test conditions                                                                                                                                            | Min.   | Тур. | Max. | Unit       |  |

|------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|------------|--|

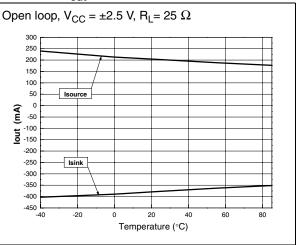

|                  | Output sink current                                            | V <sub>out</sub> = -4Vp                                                                                                                                    | -320   | -490 |      |            |  |

|                  |                                                                | T <sub>min</sub> < T <sub>amb</sub> < T <sub>max</sub>                                                                                                     |        | -395 |      | <b>m</b> ( |  |

| l <sub>out</sub> | Output source current                                          | $V_{out} = +4Vp$                                                                                                                                           | 330    | 420  |      | mA         |  |

|                  |                                                                | T <sub>min</sub> < T <sub>amb</sub> < T <sub>max</sub>                                                                                                     |        | 370  |      |            |  |

| Noise and        | d distortion                                                   |                                                                                                                                                            |        |      |      |            |  |

| eN               | Equivalent input noise voltage                                 | F = 100kHz                                                                                                                                                 |        | 2.5  |      | nV/√Hz     |  |

| iNp              | Equivalent input noise current (+)                             | F = 100kHz                                                                                                                                                 |        | 15   |      | pA/√Hz     |  |

| iNn              | Equivalent input noise current (-)                             | F = 100kHz                                                                                                                                                 |        | 21   |      | pA/√Hz     |  |

| HD2              | 2nd harmonic distortion<br>(differential configuration)        | $V_{out}$ = 14Vp-p, A <sub>V</sub> = 12dB<br>F= 110kHz, R <sub>L</sub> = 50 $\Omega$ diff.                                                                 |        | -87  |      | dBc        |  |

| HD3              | 3rd harmonic distortion<br>(differential configuration)        | $V_{out}$ = 14Vp-p, A <sub>V</sub> = 12dB<br>F= 110kHz, R <sub>L</sub> = 50 $\Omega$ diff.                                                                 |        | -83  |      | dBc        |  |

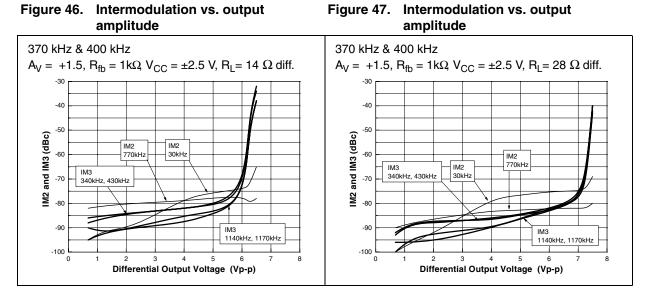

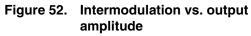

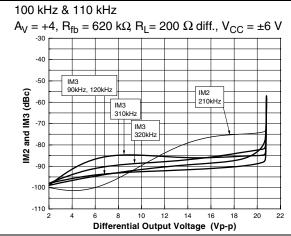

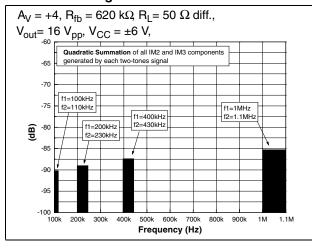

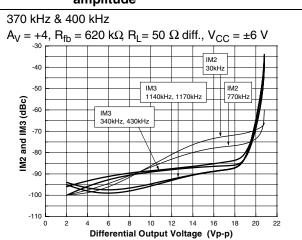

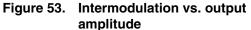

| IM2              | 2nd order intermodulation product                              | $\label{eq:F1} \begin{array}{l} F1=100 \text{kHz}, F2=110 \text{kHz}\\ V_{out}=16 \text{Vp-p}, A_V=12 \text{dB}\\ R_L=50\Omega \text{ diff}. \end{array}$  |        | -76  |      | dBc        |  |

| 111/2            | (differential configuration)                                   | $\label{eq:F1} \begin{array}{l} F1=370 \text{kHz}, F2=400 \text{kHz}\\ V_{out}=16 \text{Vp-p}, A_V=12 \text{dB}\\ R_L=50 \Omega \text{ diff}. \end{array}$ | 400kHz |      | uвс  |            |  |

| IM3              | 3rd order intermodulation product (differential configuration) | $\label{eq:F1} \begin{array}{l} F1 = 100 kHz, \ F2 = 110 kHz \\ V_{out} = 16 Vp\text{-p}, \ A_{V} = 12 dB \\ R_{L} = 50 \Omega \ diff. \end{array}$        |        | -88  |      | 15         |  |

| IIVIO            |                                                                | $\label{eq:Vout} \begin{array}{l} F1=370kHz,F2=400kHz\\ V_{out}=16Vp\text{-p},A_{V}=12\;B\\ R_{L}=50\Omega\;diff. \end{array}$                             |        | -87  |      | dBc        |  |

Table 3. $V_{CC} = \pm 6 V$ ,  $R_{fb} = 910 \Omega$ ,  $T_{amb} = 25^{\circ} C$  (unless otherwise specified) (continued)

| Symbol             | Parameter                                                            | Test conditions                                                       | Min. | Тур. | Max. | Unit |  |

|--------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------|------|------|------|------|--|

| DC perfo           | ormance                                                              |                                                                       |      |      |      |      |  |

| N/                 | have the standard sector                                             | T <sub>amb</sub>                                                      |      | 0.2  | 2.5  |      |  |

| V <sub>io</sub>    | Input offset voltage                                                 | T <sub>min</sub> < T <sub>amb</sub> < T <sub>max</sub>                |      | 1    |      | mV   |  |

| $\Delta V_{i_{0}}$ | Differential input offset voltage                                    | $T_{amb} = 25^{\circ}C$                                               |      |      | 2.5  | mV   |  |

|                    | Desitive input bios surrent                                          | T <sub>amb</sub>                                                      |      | 4    | 30   |      |  |

| I <sub>ib+</sub>   | Positive input bias current                                          | T <sub>min</sub> < T <sub>amb</sub> < T <sub>max</sub>                |      | 7    |      | μA   |  |

| I                  | Negative input bios ourrent                                          | T <sub>amb</sub>                                                      |      | 1.1  | 11   |      |  |

| I <sub>ib-</sub>   | Negative input bias current                                          | T <sub>min</sub> < T <sub>amb</sub> < T <sub>max</sub>                |      | 1.2  |      | μA   |  |

| Z <sub>IN+</sub>   | Input(+) impedance                                                   |                                                                       |      | 71   |      | kΩ   |  |

| Z <sub>IN-</sub>   | Input(-) impedance                                                   |                                                                       |      | 62   |      | Ω    |  |

| C <sub>IN+</sub>   | Input(+) capacitance                                                 |                                                                       |      | 1.5  |      | pF   |  |

| CMR                | Common mode rejection ratio 20 log ( $\Delta V_{ic}/\Delta V_{io}$ ) | $\Delta V_{ic} = \pm 1 V$                                             | 55   | 61   |      | dB   |  |

| CIMIT              |                                                                      | T <sub>min</sub> < T <sub>amb</sub> < T <sub>max</sub>                |      | 60   |      |      |  |

| SVR                | Supply voltage rejection ratio                                       | $\Delta V_{CC}$ = ±2V to ±2.5V                                        | 63   | 79   |      | dB   |  |

| 374                | 20 log ( $\Delta V_{cc}/\Delta V_{io}$ )                             | T <sub>min</sub> < T <sub>amb</sub> < T <sub>max</sub>                |      | 78   |      |      |  |

| I <sub>CC</sub>    | Total supply current per<br>operator                                 | No load                                                               |      | 11.5 | 15   | mA   |  |

| Dynamic            | performance and output chara                                         | acteristics                                                           | L    | L    |      |      |  |

| Р                  | Open loop transimpedance                                             | $V_{out} = 2V_{p-p}, R_L = 10\Omega$                                  | 2    | 4.2  |      | Mo   |  |

| R <sub>OL</sub>    |                                                                      | T <sub>min</sub> < T <sub>amb</sub> < T <sub>max</sub>                |      | 1.5  |      | MΩ   |  |

|                    | -3dB bandwidth                                                       | Small signal V <sub>out</sub> < 20mVp $A_V = 12$ dB, $R_L = 10\Omega$ | 20   | 28   |      |      |  |

| BW                 | Full power bandwidth                                                 | Large signal $V_{out}$ = 1.4 $V_p A_V$ = 12dB, $R_L$ = 10 $\Omega$    |      | 20   |      | MHz  |  |

|                    | Gain flatness @ 0.1dB                                                | Small signal V <sub>out</sub> < 20mVp $A_V = 12dB, R_L = 10\Omega$    |      | 5.7  |      | MHz  |  |

| T <sub>r</sub>     | Rise time                                                            | $V_{out}$ = 2.8Vp-p, $A_V$ = 12dB $R_L$ = 10 $\Omega$                 |      | 11   |      | ns   |  |

| Τ <sub>f</sub>     | Fall time                                                            | $V_{out}$ = 2.8Vp-p, $A_V$ = 12dB $R_L$ = 10 $\Omega$                 |      | 11.5 |      | ns   |  |

| Τs                 | Settling time                                                        | $V_{out}$ = 2.2Vp-p, $A_V$ = 12dB $R_L$ = 10 $\Omega$                 |      | 39   |      | ns   |  |

| SR                 | Slew rate                                                            | $V_{out}$ = 2.2Vp-p, $A_V$ = 12dB $R_L$ =10 $\Omega$                  | 100  | 130  |      | V/µs |  |

| V <sub>OH</sub>    | High level output voltage                                            | $R_L=10\Omega$ connected to GND                                       | 1.5  | 1.7  |      | V    |  |

| V <sub>OL</sub>    | Low level output voltage                                             | $R_L=10\Omega$ connected to GND                                       |      | -1.9 | -1.7 | V    |  |

|                    | Output sink surrent                                                  | $V_{out} = -1.25V_p$                                                  | -300 | -400 |      |      |  |

| 1                  | Output sink current                                                  | T <sub>min</sub> < T <sub>amb</sub> < T <sub>max</sub>                |      | -360 |      |      |  |

| l <sub>out</sub>   |                                                                      | $V_{-} = +1.25V_{-}$                                                  | 200  | 270  |      | - mA |  |

| out                | Output source current                                                | $V_{out} = +1.25V_p$                                                  | 200  | 210  |      |      |  |

| Table 4. | V <sub>CC</sub> = ±2.5 V, R <sub>fb</sub> = 910 Ω | , T <sub>amb</sub> = 25° C (unless otherwise | specified) |

|----------|---------------------------------------------------|----------------------------------------------|------------|

|          |                                                   |                                              |            |

Noise and distorsion

product

product

(differential configuration)

3rd order intermodulation

(differential configuration)

Symbol

eN

iNp

iNn

HD2

HD3

IM2

IM3

| Parameter                                               | Test conditions                                                                                                                                                                | Min. | Тур. | Max. | Unit   |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------|

| d distorsion                                            |                                                                                                                                                                                |      |      |      |        |

| Equivalent input noise voltage                          | F = 100kHz                                                                                                                                                                     |      | 2.5  |      | nV/√Hz |

| Equivalent input noise current (+)                      | F = 100kHz                                                                                                                                                                     |      | 15   |      | pA/√Hz |

| Equivalent input noise current (-)                      | F = 100kHz                                                                                                                                                                     |      | 21   |      | pA/√Hz |

| 2nd harmonic distortion<br>(differential configuration) |                                                                                                                                                                                |      | -97  |      | dBc    |

| 3rd harmonic distortion<br>(differential configuration) | $\label{eq:Vout} \begin{array}{l} V_{out}=6V_{p\text{-}p}, \ A_V=12dB\\ F=110 \ \text{kHz}, \ R_L=20\Omega \ \ \text{diff}. \end{array}$                                       |      | -98  |      | dBc    |

| 2nd order intermodulation                               | $\label{eq:states} \begin{array}{l} F1=100 \text{ kHz}, F2=110 \text{ kHz} \\ V_{out}=6  V_{p\text{-}p\text{,}}  A_V=12 \text{ dB} \\ R_L=20 \Omega \text{ diff.} \end{array}$ |      | -86  |      | dRo    |

#### Table 4. $V_{CC} = \pm 2$

F1= 370kHz, F2 = 400kHz

F1 = 100 kHz, F2 = 110 kHz $V_{out} = 6V_{p-p}, A_V = 12dB$  $R_L = 20\Omega \text{ diff.}$

F1 = 370kHz, F2 = 400kHz

$$\label{eq:Vout} \begin{split} V_{out} &= 6 V_{p\text{-}p}, \, A_V \text{=} \, 12 \text{dB} \\ R_L &= 20 \Omega \, \text{diff.} \end{split}$$

$V_{out} = 6V_{p-p}, A_V = 12dB$  $R_L = 20\Omega$  diff.

dBc

dBc

-88

-90

-85

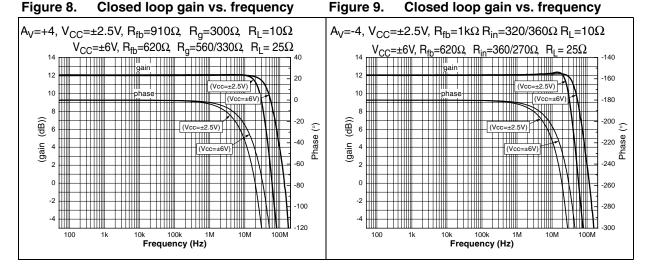

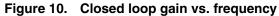

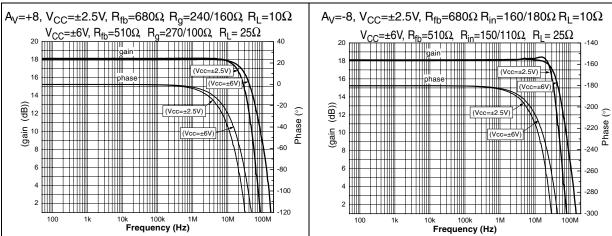

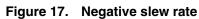

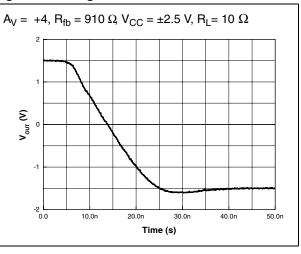

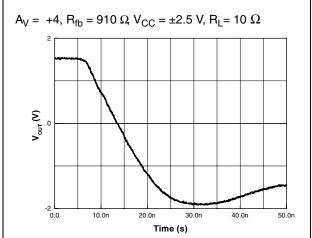

Figure 11. Closed loop gain vs. frequency

Ē

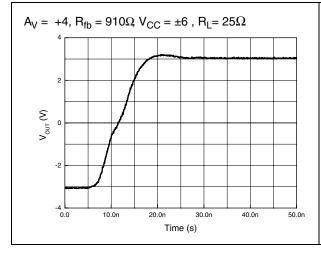

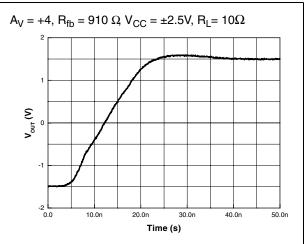

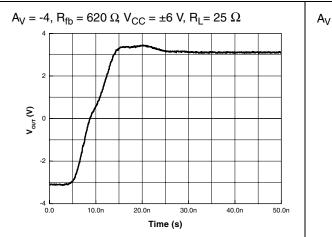

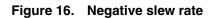

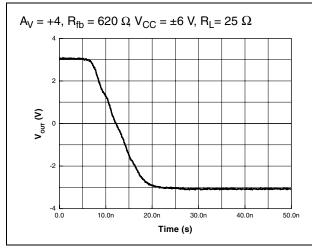

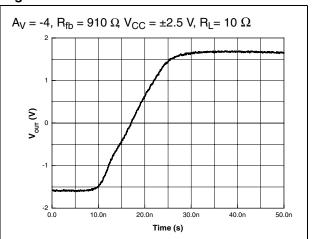

### Figure 14. Positive slew rate

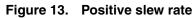

#### Figure 15. Positive slew rate

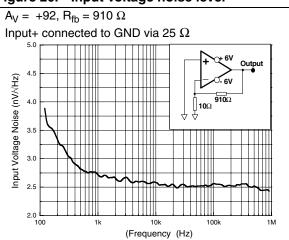

Figure 20. Input voltage noise level

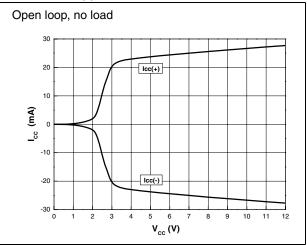

## Figure 21. I<sub>CC</sub> vs. power supply

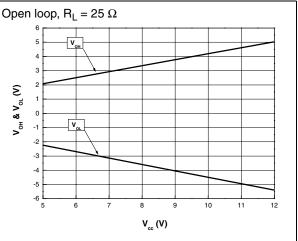

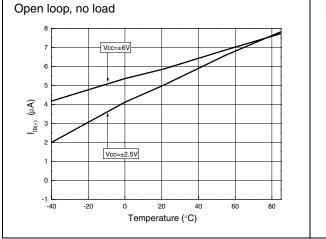

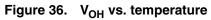

Figure 23.  $V_{OH} \& V_{OL}$  vs. power supply

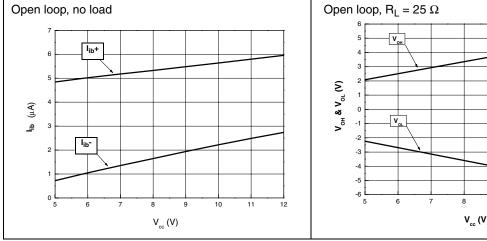

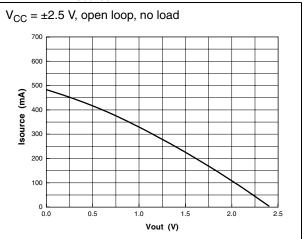

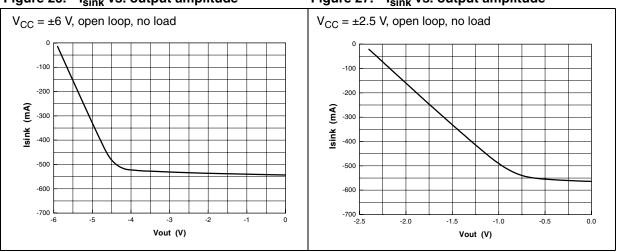

### Figure 26. $I_{sink}$ vs. output amplitude

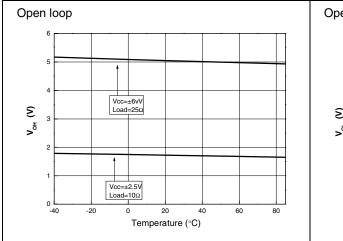

### Figure 31. I<sub>CC</sub> vs. temperature

#### Figure 32. Slew rate vs. temperature

### Figure 35. I<sub>ib</sub>(+) vs. temperature

Figure 33. Slew rate vs. temperature

### Figure 38. Differential V<sub>io</sub> vs. temperature

### Figure 39. V<sub>io</sub> vs. temperature

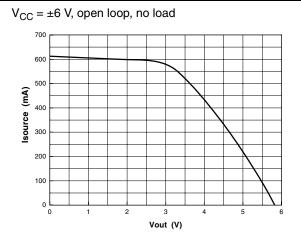

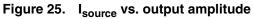

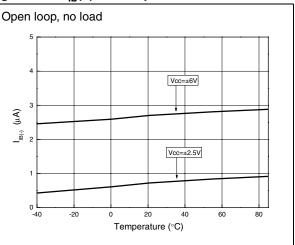

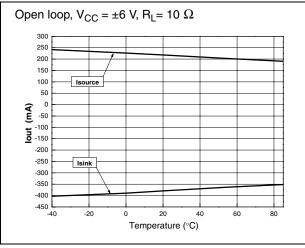

Figure 40. I<sub>out</sub> vs. temperature

### Figure 41. I<sub>out</sub> vs. temperature

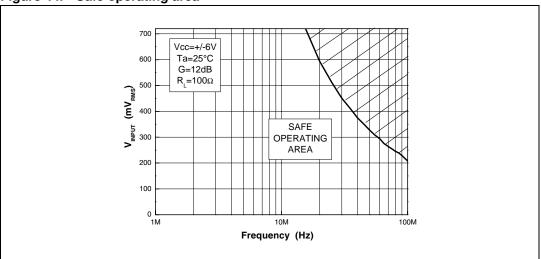

## 4 Safe operating area

*Figure 44* shows the safe operating zone for the TS616. The curve shows the input level vs. the input frequency—a characteristic curve which must be considered in order to ensure a good application design. In the dash-lined zone, the consumption increases, and this increased consumption could do damage to the chip if the temperature increases.

Figure 44. Safe operating area

## 5 Intermodulation distortion product

The non-ideal output of the amplifier can be described by the following series, due to a nonlinearity in the input-output amplitude transfer:

$$V_{out} = C_0 + C_1 V_{in} + C_2 V_{in}^2 + C_n V_{in}^n$$

where the single-tone input is  $V_{in}$ =Asin $\alpha$ t, and C<sub>0</sub> is the DC component, C<sub>1</sub>(V<sub>in</sub>) is the fundamental, C<sub>n</sub> is the amplitude of the harmonics of the output signal V<sub>out</sub>.

A one-frequency (one-tone) input signal contributes to a harmonic distortion. A two-tone input signal contributes to a harmonic distortion and an intermodulation product.

This intermodulation product, or rather, the study of the intermodulation distortion of a twotone input signal is the first step in characterizing the amplifiers capability for driving multitone signals.

The two-tone input is equal to:

$$V_{in} = A \sin \omega_1 t + B \sin \omega_2 t$$

giving:

$$= C_0 + C_1 (A \sin \omega_1 t + B \sin \omega_2 t) + C_2 (A \sin \omega_1 t + B \sin \omega_2 t)^2 \dots + C_n (A \sin \omega_1 t + B \sin \omega_2 t)^n$$

In this expression, we can extract distortion terms and intermodulation terms from a single sine wave: second-order intermodulation terms IM2 by the frequencies ( $\omega_1 - \omega_2$ ) and ( $\omega_1 + \omega_2$ ) with an amplitude of C2A<sup>2</sup> and third-order intermodulation terms IM3 by the frequencies ( $2\omega_1 - \omega_2$ ), ( $2\omega_1 + \omega_2$ ), ( $-\omega_1 + 2\omega_2$ ) and ( $\omega_1 + 2\omega_2$ ) with an amplitude of (3/4)C3A<sup>3</sup>.

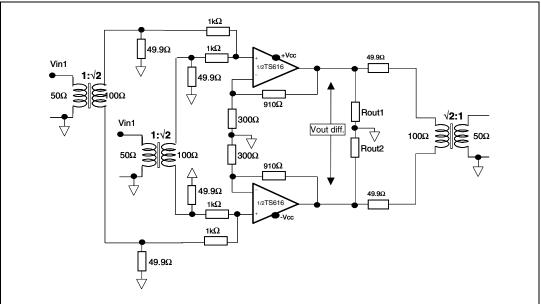

We can measure the intermodulation product of the driver by using the driver as a mixer via a summing amplifier configuration. In doing this, the non-linearity problem of an external mixing device is avoided.

Figure 45. Non-inverting summing amplifier for intermodulation measurements

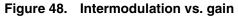

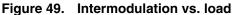

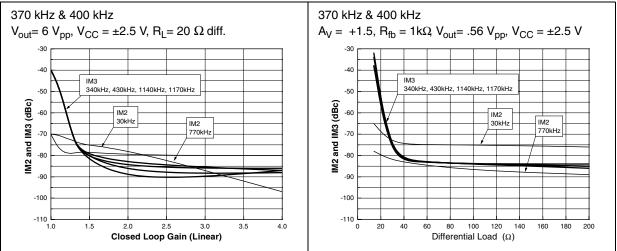

The following graphs show the IM2 and the IM3 of the amplifier in different configurations. The two-tone input signal was generated by the multisource generator Marconi 2026. Each tone has the same amplitude. The measurement was performed using a HP3585A spectrum analyzer.

## Figure 50. Intermodulation vs. output amplitude

Figure 54. Intermodulation vs. frequency range

57

## Figure 51. Intermodulation vs. output amplitude

TS616

## 6 Printed circuit board layout considerations

In the ADSL frequency range, printed circuit board parasites can affect the closed-loop performance.

The use of a proper ground plane on both sides of the PCB is necessary to provide low inductance and a low resistance common return. The most important factors affecting gain flatness and bandwidth are stray capacitance at the output and inverting input. To minimize capacitance, the space between signal lines and ground plane should be maximized. Feedback component connections must be as short as possible in order to decrease the associated inductance which affects high-frequency gain errors. It is very important to choose the smallest possible external components—for example, surface mounted devices (SMD)—in order to minimize the size of all DC and AC connections.

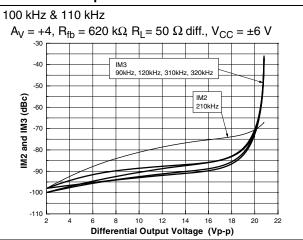

## 6.1 Thermal information

The TS616 is housed in an exposed-pad plastic package. As described in *Figure 55*, this package has a lead frame upon which the dice is mounted. This lead frame is exposed as a thermal pad on the underside of the package. The thermal contact is direct with the dice. This thermal path provides an excellent thermal performance.

The thermal pad is electrically isolated from all pins in the package. It must be soldered to a copper area of the PCB underneath the package. Through these thermal paths within this copper area, heat can be conducted away from the package. The copper area **must** be connected to  $-V_{CC}$  available on pin 4.

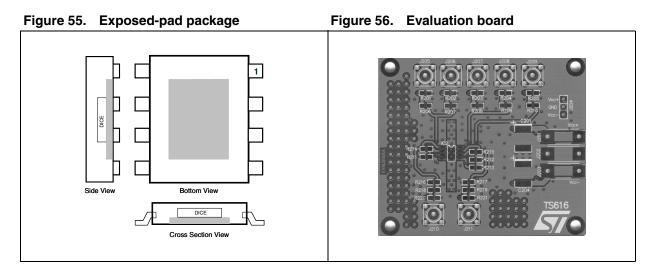

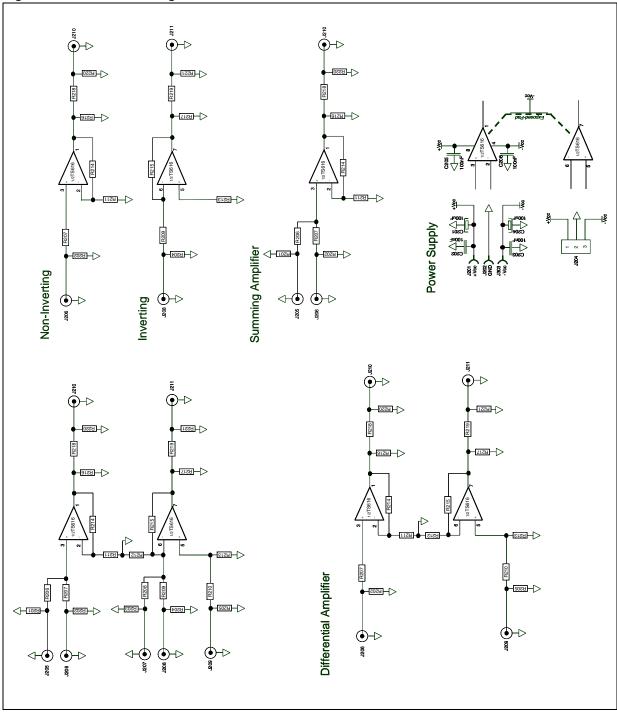

#### Figure 57. Schematic diagram

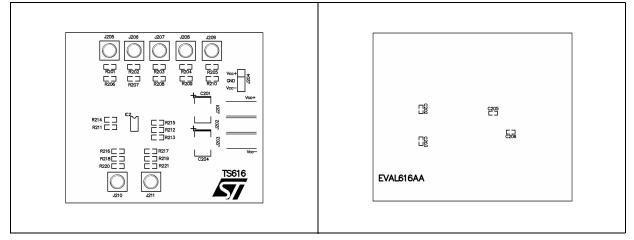

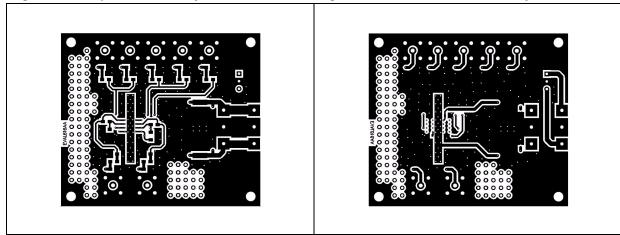

### Figure 58. Component locations - top side Figure 59. Component locations - bottom side

Figure 60. Top side board layout

Figure 61. Bottom side board layout

## 7 Noise measurements

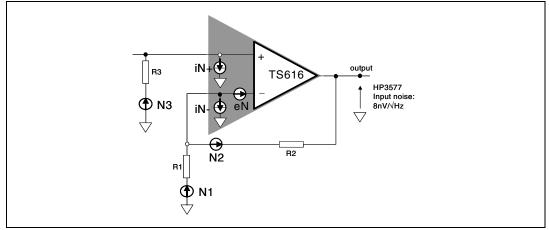

The noise model is shown in *Figure 62*, where:

- eN: input voltage noise of the amplifier

- iNn: negative input current noise of the amplifier

- iNp: positive input current noise of the amplifier

#### Figure 62. Noise model

The closed loop gain is:

$$A_{V} = g = 1 + \frac{R_{fb}}{R_{g}}$$

The six noise sources are:

$$V1 = eN \times \left(1 + \frac{R2}{R1}\right)$$

$$V2 = iNn \times R2$$

$$V3 = iNp \times R3 \times \left(1 + \frac{R2}{R1}\right)$$

$$V4 = -\frac{R2}{R1} \times \sqrt{4kTR1}$$

$$V5 = \sqrt{4kTR2}$$

$$V6 = \left(1 + \frac{R2}{R1}\right)\sqrt{4kTR3}$$

We assume that the thermal noise of a resistance R is:

$\sqrt{4kTR\Delta F}$

where  $\Delta F$  is the specified bandwidth.

On a 1 Hz bandwidth the thermal noise is reduced to:

$\sqrt{4kTR}$

where k is Boltzmann's constant, equal to 1374.10<sup>-23</sup>J/°K. T is the temperature (°K).

The output noise eNo is calculated using the Superposition Theorem. However eNo is not the sum of all noise sources, but rather the square root of the sum of the square of each noise source, as shown in *Equation 1*.

#### **Equation 1**

$$vo = \sqrt{V1^2 + V2^2 + V3^2 + V4^2 + V5^2 + V6^2}$$

**Equation 2**

$$No^{2} = eN^{2} \times g^{2} + iNn^{2} \times R2^{2} + iNp^{2} \times R3^{2} \times g^{2}$$

$$\dots + \left(\frac{R2}{R1}\right)^{2} \times 4kTR1 + 4kTR2 + \left(1 + \frac{R2}{R1}\right)^{2} \times 4kTR3$$

The input noise of the instrumentation must be extracted from the measured noise value. The real output noise value of the driver is:

#### **Equation 3**

$$eNo = \sqrt{(Measured)^2 - (instrumentation)^2}$$

The input noise is called the Equivalent Input Noise as it is not directly measured but is evaluated from the measurement of the output divided by the closed loop gain (eNo/g).

After simplification of the fourth and the fifth term of *Equation 2* we obtain:

#### **Equation 4**

$$= eN^{2} \times g^{2} + iNn^{2} \times R2^{2} + iNp^{2} \times R3^{2} \times g^{2} \dots + g \times 4kTR2 + \left(1 + \frac{R2}{R1}\right)^{2} \times 4kTR2$$

### 7.1 Measurement of *eN*

If we assume a short-circuit on the non-inverting input (R3=0), *Equation 4* becomes:

#### **Equation 5**

No =

$$\sqrt{eN^2 \times g^2 + iNn^2 \times R2^2 + g \times 4kTR2}$$

In order to easily extract the value of eN, the resistance R2 will be chosen as low as possible. On the other hand, the gain must be large enough:

- R1=10 Ω, R2=910 Ω, R3=0, Gain=92

- Equivalent input noise: 2.57 nV/√Hz

- Input voltage noise: eN=2.5 nV/√Hz

## 7.2 Measurement of *iNn*

To measure the negative input current noise iNn, we set R3=0 and use *Equation 5*. This time the gain must be lower in order to decrease the thermal noise contribution:

- R1=100 Ω, R2=910 Ω, R3=0, gain= 10.1

- Equivalent input noise: 3.40 nV/√Hz

- Negative input current noise:  $iNn = 21 pA/\sqrt{Hz}$

## 7.3 Measurement of *iNp*

To extract iNp from *Equation 3*, a resistance R3 is connected to the non-inverting input. The value of R3 must be chosen in order to keep its thermal noise contribution as low as possible against the iNp contribution.

- R1=100 Ω, R2=910 Ω, R3=100 Ω, Gain=10.1

- Equivalent input noise: 3.93 nV/√Hz

- Positive input current noise: iNp=15 pA/√Hz

- Conditions: Frequency=100 kHz, V<sub>CC</sub> = ±2.5 V

- Instrumentation: HP3585A Spectrum Analyzer (the input noise of the HP3585A is 8 nV/ $\sqrt{Hz}$ )

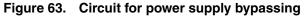

## 8 Power supply bypassing

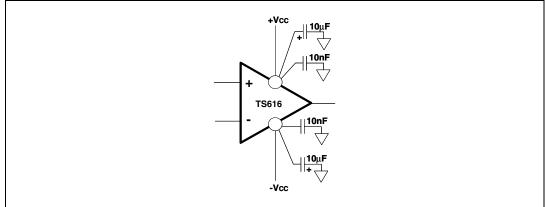

Correct power supply bypassing is very important for optimizing performance in high-frequency ranges. Bypass capacitors should be placed as close as possible to the IC pins to improve high-frequency bypassing. A capacitor greater than 1  $\mu$ F is necessary to minimize the distortion. For better quality bypassing, a capacitor of 10 nF is added using the same implementation conditions. Bypass capacitors must be incorporated for both the negative and the positive supply.

## 8.1 Single power supply

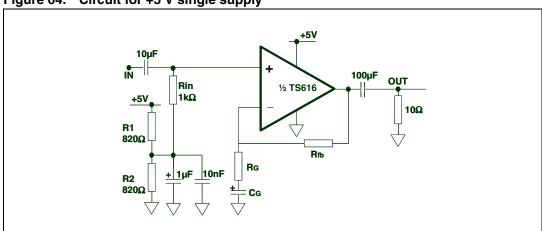

The TS616 can operate with power supplies ranging from 12 V to 5 V. The power supply can either be single (12 V or 5 V referenced to ground), or dual (such as  $\pm$ 6 V and  $\pm$ 2.5 V).

In the event that a single supply system is used, new biasing is necessary to assume a positive output dynamic range between 0 V and +V<sub>CC</sub> supply rails. Considering the values of V<sub>OH</sub> and V<sub>OL</sub>, the amplifier will provide an output dynamic from +0.5 V to 10.6 V on 25  $\Omega$  load for a 12 V supply and from 0.45 V to 3.8 V on 10  $\Omega$  load for a 5 V supply.

The amplifier must be biased with a mid-supply (nominally +V<sub>CC</sub>/2), in order to maintain the DC component of the signal at this value. Several options are possible to provide this bias supply, such as a virtual ground using an operational amplifier or a two-resistance divider (which is the cheapest solution). A high resistance value is required to limit the current consumption. On the other hand, the current must be high enough to bias the non-inverting input of the amplifier. If we consider this bias current (30  $\mu$ A max.) as the 1% of the current through the resistance divider to keep a stable mid-supply, two resistances of 2.2 k $\Omega$  can be used in the case of a 12 V power supply and two resistances of 820  $\Omega$  can be used in the case of a 5 V power supply.

The input provides a high-pass filter with a break frequency below 10 Hz which is necessary to remove the original 0 volt DC component of the input signal, and to fix it at  $+V_{CC}/2$ .

*Figure 64* shows a schematic of a 5 V single power supply configuration.

Figure 64. Circuit for +5 V single supply

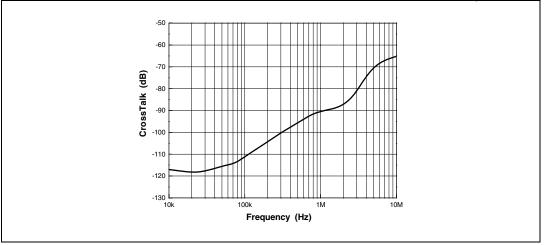

## 8.2 Channel separation and crosstalk

*Figure 65* shows an example of crosstalk from one amplifier to a second amplifier. This phenomenon, accentuated at high frequencies, is unavoidable and intrinsic to the circuit itself.

Nevertheless, the PCB layout also has an effect on the crosstalk level. Capacitive coupling between signal wires, distance between critical signal nodes and power supply bypassing are the most significant factors.

Figure 65. Crosstalk vs. frequency: A<sub>V</sub>=+4, R<sub>fb</sub>=620 Ω, V<sub>CC</sub>= ±6 V, V<sub>out</sub>= 2 V<sub>p</sub>

## 9 Choosing the feedback circuit

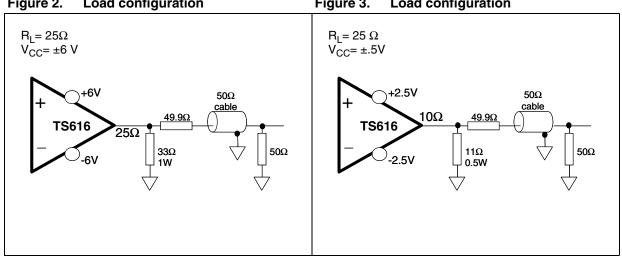

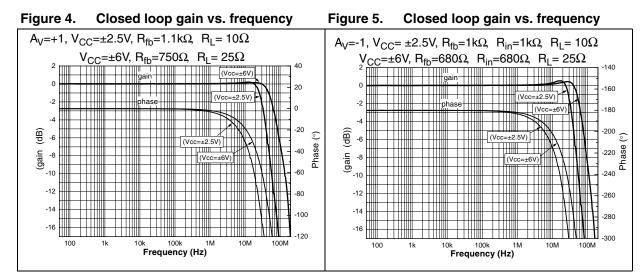

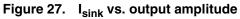

As described in *Figure 67* on page 29, the TS616 requires a  $620\Omega$  feedback resistor to optimize the bandwidth with a gain of 12 dB for a 12 V power supply. Nevertheless, due to production test constraints, the TS616 is tested with the same feedback resistor for 12 V and 5 V power supplies (910  $\Omega$ ).

| V <sub>CC</sub> (V) | Gain | R <sub>fb</sub> (Ω) |

|---------------------|------|---------------------|

|                     | +1   | 750                 |

|                     | +2   | 680                 |

|                     | +4   | 620                 |

| . 6                 | +8   | 510                 |

| ±6                  | -1   | 680                 |

|                     | -2   | 680                 |

|                     | -4   | 620                 |

|                     | -8   | 510                 |

|                     | +1   | 1.1k                |

|                     | +2   | 1k                  |

|                     | +4   | 910                 |

| .05                 | +8   | 680                 |

| ±2.5                | -1   | 1k                  |

|                     | -2   | 1k                  |

|                     | -4   | 910                 |

|                     | -8   | 680                 |

Table 5.Closed-loop gain - feedback components

28/37

## 9.1 The bias of an inverting amplifier

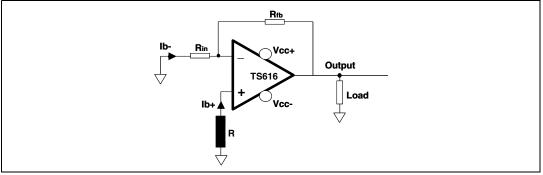

A resistance is necessary to achieve good input biasing, such as resistance R, shown in *Figure 66*.

The magnitude of this resistance is calculated by assuming the negative and positive input bias current. The aim is to compensate for the offset bias current, which could affect the input offset voltage and the output DC component. Assuming Ib-, Ib+,  $R_{in}$ ,  $R_{fb}$  and a zero volt output, the resistance R is:

$R = R_{in} // R_{fb}$

#### Figure 66. Compensation of the input bias current

## 9.2 Active filtering

#### Figure 67. Low-pass active filtering - Sallen-Key

From the resistors  $R_{fb}$  and  $R_{G}$ , we can directly calculate the gain of the filter in a classic non-inverting amplification configuration:

$$A_{V} = g = 1 + \frac{R_{fb}}{R_{g}}$$

We assume the following expression as the response of the system:

$$T_{j\omega} = \frac{Vout_{j\omega}}{Vin_{j\omega}} = \frac{g}{1 + 2\zeta \frac{j\omega}{\omega_c} + \frac{(j\omega)^2}{\omega_c^2}}$$

The cutoff frequency is not gain-dependent and so becomes:

$$\omega_{\rm c} = \frac{1}{\sqrt{\rm R1R2C1C2}}$$

The damping factor is calculated by the following expression:

$$\zeta = \frac{1}{2}\omega_{c}(C_{1}R_{1} + C_{1}R_{2} + C_{2}R_{1} - C_{1}R_{1}g)$$

The higher the gain the more sensitive the damping factor is. When the gain is higher than 1, it is preferable to use some very stable resistor and capacitor values. In the case of R1 = R2:

$$\zeta = \frac{2C_2 - C_1 \frac{R_{fb}}{R_g}}{2\sqrt{C_1C_2}}$$

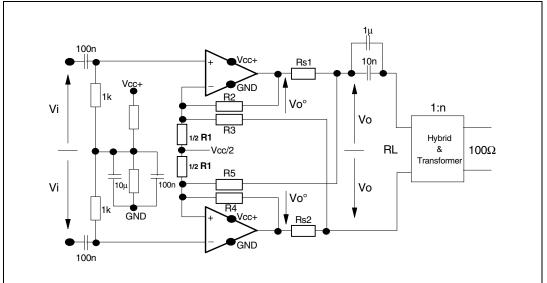

# 10 Increasing the line level using active impedance matching

With passive matching, the output signal amplitude of the driver must be twice the amplitude on the load. To go beyond this limitation an active matching impedance can be used. With this technique, it is possible to maintain good impedance matching with an amplitude on the load higher than half of the output driver amplitude. This concept is shown in *Figure 68* for a differential line.

Figure 68. TS616 as a differential line driver with active impedance matching

### **Component calculation**

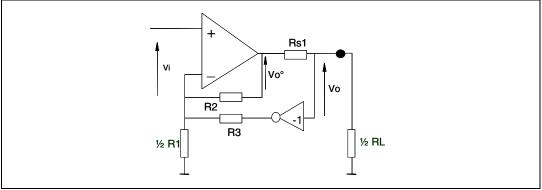

Let us consider the equivalent circuit for a single-ended configuration, as shown in *Figure 69*.

First let's consider the unloaded system. We can assume that the currents through R1, R2 and R3 are respectively:

$$\frac{2Vi}{R1},\;\frac{(Vi-Vo^\circ)}{R2}and\frac{(Vi+Vo)}{R3}$$

As Vo<sup>°</sup> equals Vo without load, the gain in this case becomes:

$$G = \frac{Vo(noload)}{Vi} = \frac{1 + \frac{2R2}{R1} + \frac{R2}{R3}}{1 - \frac{R2}{R3}}$$

The gain, for the loaded system is given by Equation 6:

#### **Equation 6**

$$GL = \frac{Vo(withload)}{Vi} = \frac{1}{2} \frac{1 + \frac{2R2}{R1} + \frac{R2}{R3}}{1 - \frac{R2}{R3}}$$

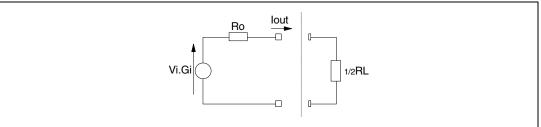

The system shown in *Figure 70* is an ideal generator with a synthesized impedance acting as the internal impedance of the system. From this, the output voltage becomes:

#### **Equation 7**

$$Vo = (ViG) - (Ro \cdot lout)$$

where Ro is the synthesized impedance and lout the output current.

On the other hand Vo can be expressed as:

#### **Equation 8**

$$Vo = \frac{Vi\left(1 + \frac{2R2}{R1} + \frac{R2}{R3}\right)}{1 - \frac{R2}{R3}} - \frac{Rs1lout}{1 - \frac{R2}{R3}}$$

By identification of both *Equation 7* and *Equation 8*, the synthesized impedance is, with Rs1 = Rs2 = Rs:

#### **Equation 9**

$$Ro = \frac{Rs}{1 - \frac{R2}{R3}}$$

#### Figure 70. Equivalent schematic - Ro is the synthesized impedance

Let us write  $Vo^{\circ}=kVo$ , where k is the matching factor varying between 1 and 2. If we assume that the current through R3 is negligible, we can calculate the output resistance, Ro:

$$Ro = \frac{kVoRL}{RL + 2Rs1}$$

After choosing the k factor, Rs will be equal to 1/2RL(k-1).

For a good impedance matching we assume that:

#### **Equation 10**

$$Ro = \frac{1}{2}RL$$

From *Equation 9* and *Equation 10*, we derive:

#### **Equation 11**

$$\frac{R2}{R3} = 1 - \frac{2Rs}{RL}$$

By fixing an arbitrary value of R2, *Equation 11* becomes:

$$R3 = \frac{R2}{1 - \frac{2Rs}{RL}}$$

Finally, the values of R2 and R3 allow us to extract R1 from *Equation 6*, so that:

#### **Equation 12**

$$R1 = \frac{2R2}{2(1 - \frac{R2}{R3})GL - 1 - \frac{R2}{R3}}$$

with GL the required gain.

#### Table 6. Components calculation for impedance matching implementation

| GL (gain for the loaded system) | GL is fixed for the application requirements<br>GL= Vo/Vi= 0.5(1+2R2/R1+R2/R3)/(1-R2/R3) |

|---------------------------------|------------------------------------------------------------------------------------------|

| R1                              | 2R2/[2(1-R2/R3)GL-1-R2/R3]                                                               |

| R2 (= R4)                       | Arbitrarily fixed                                                                        |

| R3 (= R5)                       | R2/(1-Rs/0.5RL)                                                                          |

| Rs                              | 0.5RL(k-1)                                                                               |

| Load viewed by each driver      | kRL/2                                                                                    |

## 11 Package information

In order to meet environmental requirements, ST offers these devices in ECOPACK<sup>®</sup> packages. These packages have a Lead-free second level interconnect. The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com

34/37

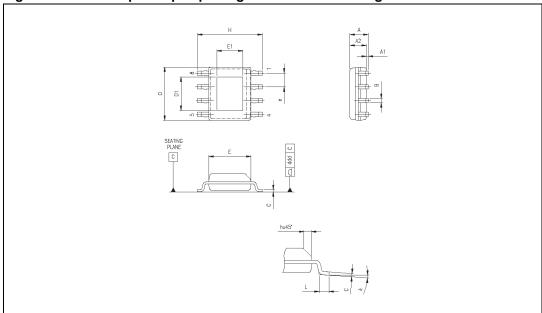

Figure 71. SO-8 exposed pad package mechanical drawing

| Table 7. | SO-8 exposed pad package mechanical data |

|----------|------------------------------------------|

|----------|------------------------------------------|

| Dimensions |             |      |       |        |       |        |  |

|------------|-------------|------|-------|--------|-------|--------|--|

| Ref.       | Millimeters |      |       | Inches |       |        |  |

|            | Min.        | Тур. | Max.  | Min.   | Тур.  | Max.   |  |

| А          | 1.350       |      | 1.750 | 0.053  |       | 0.069  |  |

| A1         | 0.000       |      | 0.150 | 0.001  |       | 0.0059 |  |

| A2         | 1.100       |      | 1.650 | 0.043  |       | 0.065  |  |

| В          | 0.330       |      | 0.510 | 0.013  |       | 0.020  |  |

| С          | 0.190       |      | 0.250 | 0.007  |       | 0.010  |  |

| D          | 4.800       |      | 5.000 | 0.189  |       | 0.197  |  |

| D1         |             | 3.10 |       |        | 0.122 |        |  |

| E          | 3.800       |      | 4.000 | 0.150  |       | 0.157  |  |

| E1         |             | 2.41 |       |        | 0.095 |        |  |

| е          | 1.270       |      |       | 0.050  |       |        |  |

| Н          | 5.800       |      | 6.200 | 0.228  |       | 0.244  |  |

| h          | 0.250       |      | 0.500 | 0.010  |       | 0.020  |  |

| L          | 0.400       |      | 1.270 | 0.016  |       | 0.050  |  |

| k          | 0d          |      | 8d    | 0d     |       | 8d     |  |

| ddd        |             |      | 0.100 |        |       | 0.004  |  |

## 12 Ordering information

### Table 8. Order codes

| Part number | Temperature range | Package | Packaging   | Marking |

|-------------|-------------------|---------|-------------|---------|

| TS616IDW    | -40°C to +85°C    | SO-8    | Tube        | TS616   |

| TS616IDWT   | -40 C 10 +65 C    | 30-8    | Tape & reel | TS616   |

## 13 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1-Nov-2002  | 1        | First release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 03-Dec-2004 | 2        | Moved note in <i>Table 3</i> to <i>Section 9: Choosing the feedback circuit on page 28.</i><br>Figure 43 in Revision 1, entitled <i>Group Delay</i> , has been removed because the results presented were not technically meaningful.<br>Simplified mathematical representations of the intermodulation product in <i>Section 5: Intermodulation distortion product on page 17.</i><br>In <i>Section 6: Printed circuit board layout considerations on page 20,</i> change from "The copper area <i>can</i> be connected to (-Vcc) available on pin 4." to "The copper area <b>must</b> be connected to -Vcc available on pin 4.".<br>In <i>Section 9.1: The bias of an inverting amplifier on page 29,</i> change of section title, and correction of referred figure to <i>Figure 66.</i> |  |

| 24-Oct-2006 | 3        | Format update.<br>Corrected package mechanical data for SO-8 exposed pad.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 16-Apr-2007 | 4        | Corrected package error in Table 8: Order codes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 26-Sep-2008 | 5        | Corrected package error in Table 8: Order codes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

Please Read Carefully:

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

time, without notice.