| Current Version: 1.1 as of October 2001                                                                                    |                                                 |                                                        |  |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------|--|

| Previous Versi                                                                                                             | on: 1.0, March 200                              | 01                                                     |  |

| Page Page (in previous Version) Subjects (major changes since last revision)  Subjects (major changes since last revision) |                                                 |                                                        |  |

| 2-2, 5-3, 5-6                                                                                                              | 2-2, 5-3, 5-6                                   | Frequency range increased                              |  |

| 3-3 3-6                                                                                                                    | 3-3 3-6                                         | ESD-structures added to interface schematics           |  |

| 3-10, 5-3                                                                                                                  | 3-10, 5-3                                       | Typical value for Power-Down-Mode current added        |  |

| 4-8 4-10                                                                                                                   | . 4-10 Description of Application board deleted |                                                        |  |

| 5-2                                                                                                                        | 5-2                                             | Supply voltage range added to Absolute Maximum Ratings |  |

| 5-2                                                                                                                        | 5-2                                             | ESD integrity specified in detail                      |  |

| 5-3, 5-6                                                                                                                   | 5-3, 5-6                                        | Loop filter voltages adapted                           |  |

| 5-4, 5-7                                                                                                                   | 5-4, 5-7                                        | Saturation voltage of Clock Driver Output reduced      |  |

| 5-5, 5-8                                                                                                                   | 5-5, 5-8                                        | Output Power Tolerances reduced                        |  |

ABM®, AOP®, ARCOFI®, ARCOFI®-BA, ARCOFI®-SP, DigiTape®, EPIC®-1, EPIC®-S, ELIC®, FALC®-54, FALC®-56, FALC®-E1, FALC®-LH, IDEC®, IOM®, IOM®-1, IOM®-2, IPAT®-2, ISAC®-P, ISAC®-S, ISAC®-S TE, ISAC®-P TE, ITAC®, IWE®, MUSAC®-A, OCTAT®-P, QUAT®-S, SICAT®, SICOFI®-2, SICOFI®-4, SICOFI®-4, SICOFI®-4, SLICOFI® are registered trademarks of Infineon Technologies AG.

ACE™, ASM™, ASP™, POTSWIRE™, QuadFALC™, SCOUT™ are trademarks of Infineon Technologies AG.

Edition 15.02.2001 Published by Infineon Technologies AG, Balanstraße 73, 81541 München

© Infineon Technologies AG 2001.

All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Infineon Technologies AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Infineon Technologies AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

## Table of Contents

| 1 | Table | of Contents                                | 1-i |

|---|-------|--------------------------------------------|-----|

| 2 | Produ | uct Description                            | 2-1 |

|   | 2.1   | Overview                                   | 2-2 |

|   | 2.2   | Applications                               | 2-2 |

|   | 2.3   | Features                                   | 2-2 |

|   | 2.4   | Package Outlines                           | 2-3 |

| 3 | Funct | tional Description                         | 3-1 |

|   | 3.1   | Pin Configuration                          | 3-2 |

|   | 3.2   | Pin Definitions and Functions              | 3-3 |

|   | 3.3   | Functional Block diagram                   | 3-7 |

|   | 3.4   | Functional Blocks                          | 3-8 |

| 4 | Appli | cations                                    | 4-1 |

|   | 4.1   | 50 Ohm-Output Testboard Schematic          | 4-2 |

|   | 4.2   | 50 Ohm-Output Testboard Layout             | 4-3 |

|   | 4.3   | Bill of material (50 Ohm-Output Testboard) | 4-4 |

|   | 4.4   | Hints                                      | 4-5 |

| 5 | Refer | ence                                       | 5-1 |

|   | 5.1   | Absolute Maximum Ratings                   | 5-2 |

|   | 5.2   | Operating Range                            | 5-2 |

|   | 5.3   | AC/DC Characteristics                      | 5-3 |

**Product Info**

### **Product Info**

#### **General Description**

The TDA 5102 is a single chip ASK/ Package FSK transmitter for the frequency band 905-925 MHz. The IC offers a high level of integration and needs only a few external components. The device contains a fully integrated PLL synthesizer and a high efficiency power amplifier to drive a loop antenna. A special circuit design and an unique power amplifier design are used to save current consumption and therefore to save battery life. Additionally features like a power down mode, a low power detect, a selectable crystal oscillator frequency and a divided clock output are implemented. The IC can be used for both ASK and FSK modulation.

#### **Features**

- fully integrated frequency synthesizer

- VCO without external components

- high efficiency power amplifier

- frequency range 905-925 MHz

- ASK/FSK modulation

- low supply current (typically 7mA)

- voltage supply range 2.1 4 V

- power down mode

- low voltage sensor

- selectable crystal oscillator 7.15 MHz/14.3 MHz

- programmable divided clock output for µC

- low external component count

#### **Applications**

- Keyless entry systems

- Remote control systems

- Alarm systems

- Communication systems

#### **Ordering Information**

| Туре                       | Ordering Code | Package    |  |

|----------------------------|---------------|------------|--|

| TDA 5102                   | Q67036-A1175  | P-TSSOP-16 |  |

| available on tape and reel |               |            |  |

# Product Description

| Con | Contents of this Chapter |       |  |

|-----|--------------------------|-------|--|

|     |                          |       |  |

| 2.1 | Overview                 | . 2-2 |  |

| 2.2 | Applications             | . 2-2 |  |

| 2.3 | Features                 | . 2-2 |  |

| 2.4 | Package Outlines         | . 2-3 |  |

#### 2.1 Overview

The TDA 5102 is a single chip ASK/FSK transmitter for the frequency band 905-925 MHz. The IC offers a high level of integration and needs only a few external components. The device contains a fully integrated PLL synthesizer and a high efficiency power amplifier to drive a loop antenna. A special circuit design and an unique power amplifier design are used to save current consumption and therefore to save battery life. Additional features like a power down mode, a low power detect, a selectable crystal oscillator frequency and a divided clock output are implemented. The IC can be used for both ASK and FSK modulation.

### 2.2 Applications

- Keyless entry systems

- Remote control systems

- Alarm systems

- Communication systems

#### 2.3 Features

- fully integrated frequency synthesizer

- VCO without external components

- high efficiency power amplifier

- frequency range 905-925 MHz

- ASK/FSK modulation

- low supply current (typically 7 mA)

- voltage supply range 2.1 4 V

- power down mode

- low voltage sensor

- selectable crystal oscillator 7.15 MHz/14.3 MHz

- programmable divided clock output for μC

- low external component count

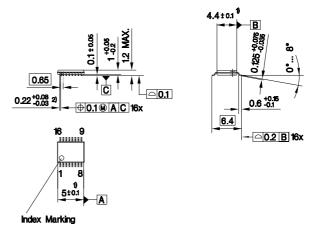

## 2.4 Package Outlines

- 1) Does not include plastic or metal protrusion of 0.15 max. per side

- 2) Does not include dambar protrusion

Figure 2-1 P-TSSOP-16

| Contents of this Chapter |                                                              |  |

|--------------------------|--------------------------------------------------------------|--|

|                          |                                                              |  |

| 3.1                      | Pin Configuration                                            |  |

| 3.2                      | Pin Definitions and Functions                                |  |

| 3.3                      | Functional Block diagram3-7                                  |  |

| 3.4                      | Functional Blocks                                            |  |

| 3.4.1                    | PLL Synthesizer                                              |  |

| 3.4.2                    | Crystal Oscillator                                           |  |

| 3.4.3                    | Power Amplifier                                              |  |

| 3.4.4                    | Low Power Detect                                             |  |

| 3.4.5                    | Power Modes3-10                                              |  |

| 3.4.5.1                  | Power Down Mode                                              |  |

| 3.4.5.2                  | PLL Enable Mode                                              |  |

| 3.4.5.3                  | Transmit Mode                                                |  |

| 3.4.5.4                  | Power mode control3-10                                       |  |

| 3.4.6                    | Recommended timing diagrams for ASK- and FSK-Modulation 3-12 |  |

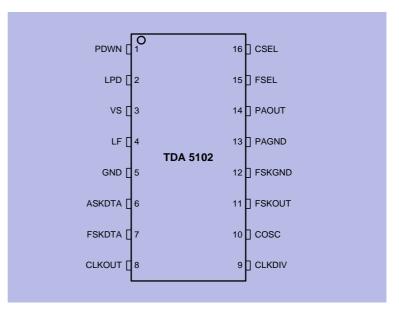

## 3.1 Pin Configuration

Pin\_config.wmf

Figure 3-1 IC Pin Configuration

| Table 3-1 |        |                                                                      |

|-----------|--------|----------------------------------------------------------------------|

| Pin No.   | Symbol | Function                                                             |

| 1         | PDWN   | Power Down Mode Control                                              |

| 2         | LPD    | Low Power Detect Output                                              |

| 3         | VS     | Voltage Supply                                                       |

| 4         | LF     | Loop Filter                                                          |

| 5         | GND    | Ground                                                               |

| 6         | ASKDTA | Amplitude Shift Keying Data Input                                    |

| 7         | FSKDTA | Frequency Shift Keying Data Input                                    |

| 8         | CLKOUT | Clock Driver Output                                                  |

| 9         | CLKDIV | Clock Divider Control                                                |

| 10        | COSC   | Crystal Oscillator Input                                             |

| 11        | FSKOUT | Frequency Shift Keying Switch Output                                 |

| 12        | FSKGND | Frequency Shift Keying Ground                                        |

| 13        | PAGND  | Power Amplifier Ground                                               |

| 14        | PAOUT  | Power Amplifier Output                                               |

| 15        | FSEL   | Frequency Range Selection: Has to be left open for 915 MHz operation |

| 16        | CSEL   | Crystal Frequency Selection (7.15 or 14.3 MHz)                       |

## 3.2 Pin Definitions and Functions

| Table      | Table 3-2 |                                                    |                                                                                                                                                                                                                                                                                                        |  |  |  |

|------------|-----------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin<br>No. | Symbol    | Interface Schematic                                | Function                                                                                                                                                                                                                                                                                               |  |  |  |

| 1          | PDWN      | $V_S$ 0 40 μA * (ASKDTA+FSKDTA) 5 kΩ 150 kΩ 250 kΩ | Disable pin for the complete transmitter circuit.  A logic low (PDWN < 0.7 V) turns off all transmitter functions.  A logic high (PDWN > 1.5 V) gives access to all transmitter functions.  PDWN input will be pulled up by 40 µA internally by either setting FSKDTA or ASKDTA to a logic high-state. |  |  |  |

| 2          | LPD       | V <sub>S</sub><br>40 μA<br>2                       | This pin provides an output indicating the low-voltage state of the supply voltage VS.  VS < 2.15 V will set LPD to the low-state.  An internal pull-up current of 40 µA gives the output a high-state at supply voltages above 2.15 V.                                                                |  |  |  |

| 3          | VS        |                                                    | This pin is the positive supply of the transmitter electronics.  An RF bypass capacitor should be connected directly to this pin and returned to GND (pin 5) as short as possible.                                                                                                                     |  |  |  |

| 4 | LF     | V <sub>S</sub> 140 pF 15 pF 10 kΩ  V <sub>S</sub> 4 V <sub>S</sub> 4 V <sub>S</sub> 7 10 kΩ | Output of the charge pump and input of the VCO control voltage.  The loop bandwidth of the PLL is 150 kHz when only the internal loop filter is used.  The loop bandwidth may be reduced by applying an external RC network referencing to the positive supply VS (pin 3).                                                                                                                                                                                                                                                 |

|---|--------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5 | GND    |                                                                                             | General ground connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6 | ASKDTA | 60 kΩ<br>90 kΩ<br>50 pF 30 μA                                                               | Digital amplitude modulation can be imparted to the Power Amplifier through this pin.  A logic high (ASKDTA > 1.5 V or open) enables the Power Amplifier.  A logic low (ASKDTA < 0.5 V) disables the Power Amplifier.                                                                                                                                                                                                                                                                                                      |

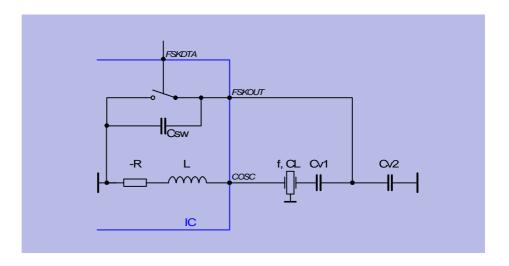

| 7 | FSKDTA | 7<br>90 kΩ 0<br>30 μA                                                                       | Digital frequency modulation can be imparted to the Xtal Oscillator by this pin. The VCO-frequency varies in accordance to the frequency of the reference oscillator.  A logic high (FSKDTA > 1.5V or open) sets the FSK switch to a high impedance state.  A logic low (FSKDTA < 0.5 V) closes the FSK switch from FSKOUT (pin 11) to FSKGND (pin 12).  A capacitor can be switched to the reference crystal network this way. The Xtal Oscillator frequency will be shifted giving the designed FSK frequency deviation. |

| 8  | CLKOUT | V <sub>s</sub> ° 8                             | Clock output to supply an external device. An external pull-up resistor has to be added in accordance to the driving requirements of the external device. A clock frequency of 3.57 MHz is selected by a logic low at CLKDIV input (pin9). A clock frequency of 894 kHz is selected by a logic high at CLKDIV input (pin9).                                                                                                     |

|----|--------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9  | CLKDIV | 9 60 kΩ +1.2 V γ 5 μΑ 60 kΩ +0.8 V             | This pin is used to select the desired clock division rate for the CLKOUT signal.  A logic low (CLKDIV < 0.2 V) applied to this pin selects the 3.57 MHz output signal at CLKOUT (pin 8).  A logic high (CLKDIV open) applied to this pin selects the 894 kHz output signal at CLKOUT (pin 8).                                                                                                                                  |

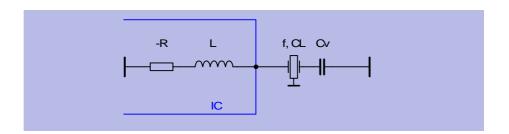

| 10 | COSC   | V <sub>S</sub> V <sub>S</sub> 100 μA           | This pin is connected to the reference oscillator circuit.  The reference oscillator is working as a negative impedance converter. It presents a negative resistance in series to an inductance at the COSC pin.                                                                                                                                                                                                                |

| 11 | FSKOUT | V <sub>S</sub> V <sub>S</sub> 200 μA 1.5 kΩ 11 | This pin is connected to a switch to FSKGND (pin 12).  The switch is closed when the signal at FSKDTA (pin 7) is in a logic low state.  The switch is open when the signal at FSKDTA (pin 7) is in a logic high state.  FSKOUT can switch an additional capacitor to the reference crystal network to pull the crystal frequency by an amount resulting in the desired FSK frequency shift of the transmitter output frequency. |

| 12 | FSKGND |                                | Ground connection for FSK modulation output FSKOUT.                                                                                                                                                                                                                                                                         |

|----|--------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13 | PAGND  |                                | Ground connection of the power amplifier.  The RF ground return path of the power amplifier output PAOUT (pin 14) has to be concentrated to this pin.                                                                                                                                                                       |

| 14 | PAOUT  | 13                             | RF output pin of the transmitter.  A DC path to the positive supply VS has to be supplied by the antenna matching network.                                                                                                                                                                                                  |

| 15 | FSEL   | 15<br>90 kΩ<br>30 μΑ           | This pin has to be left open to select the 915 MHz transmitter frequency range.  A logic low (FSEL < 0.5 V) applied to this pin sets the transmitter to the 457 MHz frequency range.  A logic high (FSEL open) applied to this pin sets the transmitter to the 915 MHz frequency range.                                     |

| 16 | CSEL   | 16 +1.2 V Vs 5 μΑ 60 kΩ +0.8 V | This pin is used to select the desired reference frequency.  A logic low (CSEL < 0.2 V) applied to this pin sets the internal frequency divider to accept a reference frequency of 7.15 MHz.  A logic high (CSEL open) applied to this pin sets the internal frequency divider to accept a reference frequency of 14.3 MHz. |

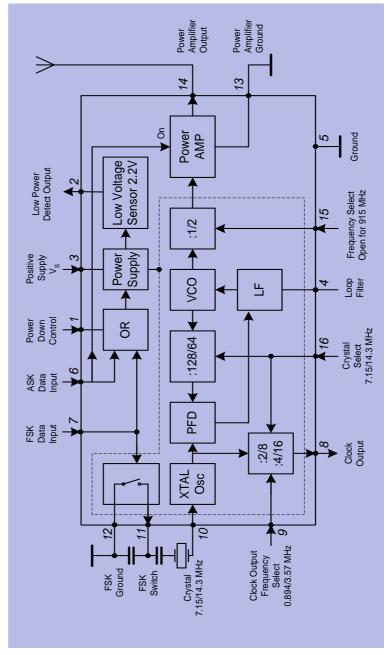

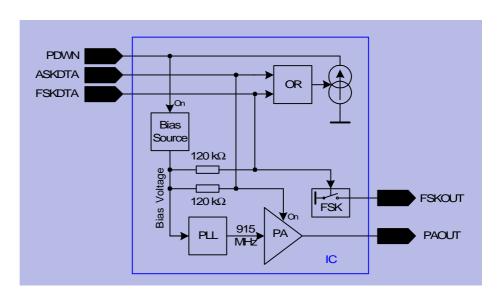

## 3.3 Functional Block diagram

Funct\_Block\_Diagram.wmf

Figure 3-2 Functional Block diagram

#### 3.4 Functional Blocks

#### 3.4.1 PLL Synthesizer

The Phase Locked Loop synthesizer consists of a Voltage Controlled Oscillator (VCO), an asynchronous divider chain, a phase detector, a charge pump and a loop filter. It is fully implemented on chip. The tuning circuit of the VCO consisting of spiral inductors and varactor diodes is on chip, too. Therefore no additional external components are necessary. The nominal center frequency of the VCO is 915 MHz. The oscillator signal is fed both, to the synthesizer divider chain and to the power amplifier. The overall division ratio of the asynchronous divider chain is 128 in case of a 7.15 MHz crystal or 64 in case of a 14.3 MHz crystal and can be selected via CSEL (pin 16). The phase detector is a Type IV PD with charge pump. The passive loop filter is realized on chip.

#### 3.4.2 Crystal Oscillator

The crystal oscillator operates either at 7.15 MHz or at 14.3 MHz.

The reference frequency can be chosen by the signal at CSEL (pin 16).

| Table 3-3          |                   |

|--------------------|-------------------|

| CSEL (pin 16)      | Crystal Frequency |

| Low <sup>1)</sup>  | 7.15 MHz          |

| Open <sup>2)</sup> | 14.3 MHz          |

1) Low: Voltage at pin < 0.2 V

2) Open: Pin open

For both quartz frequency options, 894 kHz or 3.57 MHz are available as output frequencies of the clock output CLKOUT (pin 8) to drive the clock input of a micro controller.

The frequency at CLKOUT (pin 8) is controlled by the signal at CLKDIV (pin 9)

| Table 3-4          |                  |  |  |

|--------------------|------------------|--|--|

| CLKDIV (pin 9)     | CLKOUT Frequency |  |  |

| Low <sup>1)</sup>  | 3.57 MHz         |  |  |

| Open <sup>2)</sup> | 894 kHz          |  |  |

1) Low: Voltage at pin < 0.2 V

2) Open: Pin open

To achieve FSK transmission, the oscillator frequency can be detuned by a fixed amount by switching an external capacitor via FSKOUT (pin 11).

The condition of the switch is controlled by the signal at FSKDTA (pin 7).

| Table 3-5                               |            |

|-----------------------------------------|------------|

| FSKDTA (pin7)                           | FSK Switch |

| Low <sup>1)</sup>                       | CLOSED     |

| Open <sup>2)</sup> , High <sup>3)</sup> | OPEN       |

1) Low: Voltage at pin < 0.5 V

2) Open: Pin open

3) High: Voltage at pin > 1.5 V

#### 3.4.3 Power Amplifier

For operation at 915 MHz, the power amplifier is fed directly from the voltage controlled oscillator. It is possible to feed the power amplifier with the VCO frequency divided by 2. This is controlled by FSEL (pin 15) as described in the table below.

| Table 3-6          |                         |

|--------------------|-------------------------|

| FSEL (pin 15)      | Radiated Frequency Band |

| Low <sup>1)</sup>  | 457 MHz                 |

| Open <sup>2)</sup> | 915 MHz                 |

1) Low: Voltage at pin < 0.5 V

2) Open: Pin open

The Power Amplifier can be switched on and off by the signal at ASKDTA (pin 6).

| Table 3-7                               |                 |

|-----------------------------------------|-----------------|

| ASKDTA (pin 6)                          | Power Amplifier |

| Low <sup>1)</sup>                       | OFF             |

| Open <sup>2)</sup> , High <sup>3)</sup> | ON              |

1) Low: Voltage at pin < 0.5 V

2) Open: Pin open

3) High: Voltage at pin > 1.5 V

The Power Amplifier has an Open Collector output at PAOUT (pin 14) and requires an external pull-up coil to provide bias. The coil is part of the tuning and matching LC circuitry to get best performance with the external loop antenna. To achieve the best power amplifier efficiency, the high frequency voltage swing at PAOUT (pin 14) should be twice the supply voltage.

The power amplifier has its own ground pin PAGND (pin 13) in order to reduce the amount of coupling to the other circuits.

#### 3.4.4 Low Power Detect

The supply voltage is sensed by a low power detector. When the supply voltage drops below 2.15 V, the output LPD (pin 2) switches to the low-state. To minimize the external component count, an internal pull-up current of 40  $\mu$ A gives the output a high-state at supply voltages above 2.15 V.

The output LPD (pin 2) can either be connected to ASKDTA (pin 6) to switch off the PA as soon as the supply voltage drops below 2.15 V or it can be used to inform a micro-controller to stop the transmission after the current data packet.

#### 3.4.5 Power Modes

The IC provides three power modes, the POWER DOWN MODE, the PLL ENABLE MODE and the TRANSMIT MODE.

#### 3.4.5.1 Power Down Mode

In the POWER DOWN MODE the complete chip is switched off.

The current consumption is typically 0.3 nA at 3 V 25°C.

#### 3.4.5.2 PLL Enable Mode

In the PLL ENABLE MODE the PLL is switched on but the power amplifier is turned off to avoid undesired power radiation during the time the PLL needs to settle. The turn on time of the PLL is determined mainly by the turn on time of the crystal oscillator and is typically less than 1 msec, depending on the crystal.

The current consumption is typically 3.5 mA.

#### 3.4.5.3 Transmit Mode

In the TRANSMIT MODE the PLL is switched on and the power amplifier is turned on too.

The current consumption of the IC is typically 7 mA when using a proper transforming network at PAOUT, see Figure 4-1.

#### 3.4.5.4 Power mode control

The bias circuitry is powered up via a voltage V > 1.5 V at the pin PDWN (pin 1). When the bias circuitry is powered up, the pins ASKDTA and FSKDTA are pulled up internally.

Forcing the voltage at the pins low overrides the internally set state.

Alternatively, if the voltage at ASKDTA or FSKDTA is forced high externally, the PDWN pin is pulled up internally via a current source. In this case, it is not necessary to connect the PDWN pin, it is recommended to leave it open.

The principle schematic of the power mode control circuitry is shown in Figure 3-5.

Power\_Mode.wmf

Figure 3-5 Power mode control circuitry

Table 3-8 provides a listing of how to get into the different power modes

| Table 3-8          |                 |            |              |

|--------------------|-----------------|------------|--------------|

| PDWN               | FSKDTA          | ASKDTA     | MODE         |

| Low <sup>1)</sup>  | Low, Open       | Low, Open  | POWER DOWN   |

| Open <sup>2)</sup> | Low             | Low        | POWER DOWN   |

| High <sup>3)</sup> | Low, Open, High | Low        | PLL ENABLE   |

| Open               | High            | Low        | I LE LINABLE |

| High               | Low, Open, High | Open, High |              |

| Open               | High            | Open, High | TRANSMIT     |

| Open               | Low, Open, High | High       |              |

1) Low: Voltage at pin < 0.7 V (PDWN)

Voltage at pin < 0.5 V (FSKDTA, ASKDTA)

2) Open: Pin open

3) High: Voltage at pin > 1.5 V

Other combinations of the control pins PDWN, FSKDTA and ASKDTA are not recommended.

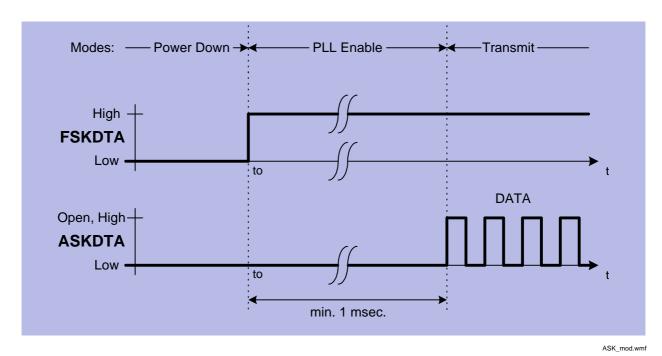

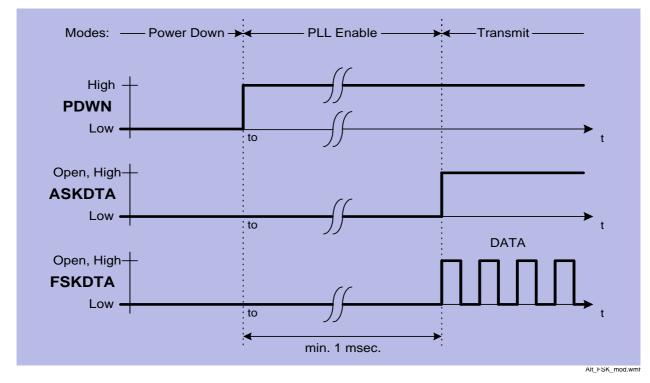

#### 3.4.6 Recommended timing diagrams for ASK- and FSK-Modulation

ASK Modulation using FSKDTA and ASKDTA, PDWN not connected

Figure 3-6 ASK Modulation

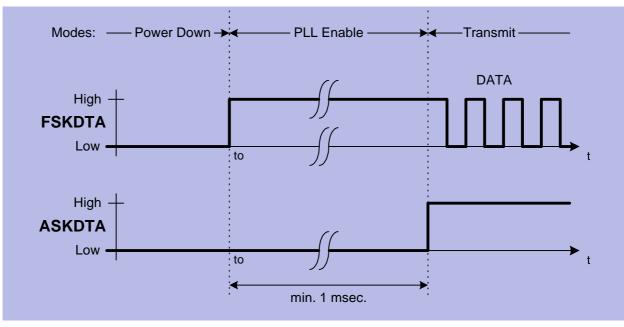

FSK Modulation using FSKDTA and ASKDTA, PDWN not connected

Figure 3-7 FSK Modulation

FSK\_mod.wmf

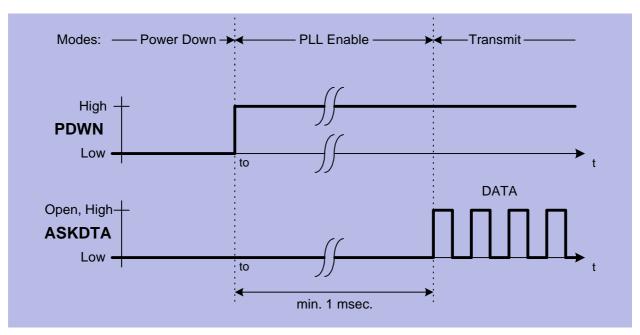

#### Alternative ASK Modulation, FSKDTA not connected.

Alt\_ASK\_mod.wmf

Figure 3-8 Alternative ASK Modulation

#### Alternative FSK Modulation

Figure 3-9 Alternative FSK Modulation

| ontents | or this C | napter |  |

|---------|-----------|--------|--|

|         |           |        |  |

|         |           |        |  |

|         |           |        |  |

| 1.1 | 50 Ohm-Output Testboard Schematic          | . 4-2 |

|-----|--------------------------------------------|-------|

| 4.2 | 50 Ohm-Output Testboard Layout             | . 4-3 |

| 4.3 | Bill of material (50 Ohm-Output Testboard) | . 4-4 |

| 1.4 | Hints                                      | . 4-5 |

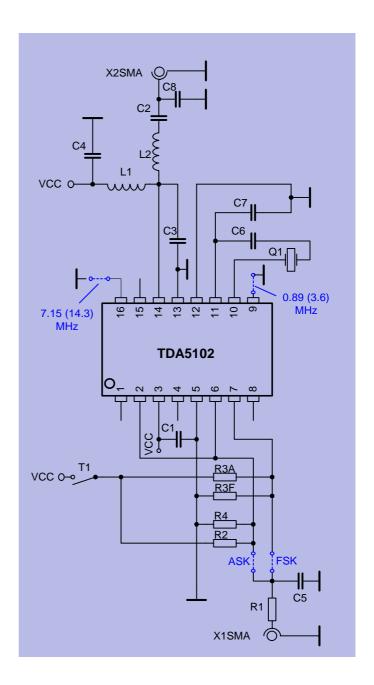

## 4.1 50 Ohm-Output Testboard Schematic

50ohm\_test\_v5.wmf

Figure 4-1 50  $\Omega$ -Output testboard schematic

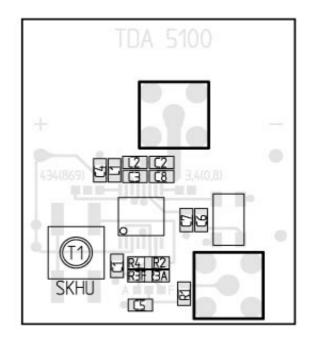

### 4.2 50 Ohm-Output Testboard Layout

#### Oben (3.00 09/14/99 tda5100\_v5.tc)

Figure 4-2 Top Side of TDA 5102-Testboard with 50  $\Omega$ -Output. It is the same testboard as for the TDA 5100.

Unten (3.00 09/14/99 tda5100\_v5.tc)

Figure 4-3 Bottom Side of TDA 5102-Testboard with 50  $\Omega$ -Output. It is the same testboard as for the TDA 5100.

## 4.3 Bill of material (50 Ohm-Output Testboard)

| Table 4-1 | Bill of material |              |                                    |

|-----------|------------------|--------------|------------------------------------|

| Part      | ASK              | FSK          | Specification                      |

|           | 915 MHz          | 915 MHz      |                                    |

| R1        | 4.7 kΩ           | 4.7 kΩ       | 0805, ± 5%                         |

| R2        |                  | 12 kΩ        | 0805, ± 5%                         |

| R3A       | 15 kΩ            |              | 0805, ± 5%                         |

| R3F       |                  | 15 kΩ        | 0805, ± 5%                         |

| R4        | open             | open         | 0805, ± 5%                         |

| C1        | 47 nF            | 47 nF        | 0805, X7R, ± 10%                   |

| C2        | 47 pF            | 47 pF        | 0805, COG, ± 5%                    |

| C3        | 2.7 pF           | 2.7 pF       | 0805, COG, ± 0.1 pF                |

| C4        | 100 pF           | 100 pF       | 0805, COG, ± 5%                    |

| C5        | 1 nF             | 1 nF         | 0805, X7R, ± 10%                   |

| C6        | 5.6 pF           | 5.6 pF       | 0805, COG, ± 0.1 pF                |

| C7        | 0 Ω Jumper       | 47 pF        | 0805, COG, ± 5%<br>0805, 0Ω Jumper |

| C8        | 8.2 pF           | 8.2 pF       | 0805, COG, ± 5%                    |

| L1        | 33 nH            | 33 nH        | TOKO LL2012-J                      |

| L2        | 15 nH            | 15 nH        | TOKO LL1608-J                      |

| Q3        | 14.3 MHz         | 14.3 MHz     |                                    |

| IC1       | TDA 5102         | TDA 5102     |                                    |

| B1        | Battery clip     | Battery clip | HU2031-1, RENATA                   |

| T1        | Push-button      | Push-button  | replaced by a short                |

| X1        | SMA-S            | SMA-S        | SMA standing                       |

| X2        | SMA-S            | SMA-S        | SMA standing                       |

#### 4.4 Hints

#### 1. Application Hints on the crystal oscillator

As mentioned before, the crystal oscillator achieves a turn on time less than 1 msec. To achieve this, a NIC oscillator type is implemented in the TDA 5102. The input impedance of this oscillator is a negative resistance in series to an inductance. Therefore the load capacitance of the crystal CL (specified by the crystal supplier) is transformed to the capacitance Cv.

$$Cv = \frac{1}{\frac{1}{CL} + \omega^2 L}$$

Formula 1)

CL: crystal load capacitance for nominal frequency

ω: angular frequency

L: inductivity of the crystal oscillator

#### **Example for the ASK-Mode:**

Referring to the application circuit, in ASK-Mode the capacitance C7 is replaced by a short to ground. Assume a crystal frequency of 14.3 MHz and a crystal load capacitance of CL = 20 pF. The inductance L is specified within the electrical characteristics at 14.3 MHz to a value of 11  $\mu H$ . Therefore C6 is calculated to 7.2 pF.

$$Cv = \frac{1}{\frac{1}{CL} + \omega^2 L} = C6$$

#### **Example for the FSK-Mode:**

FSK modulation is achieved by switching the load capacitance of the crystal as shown below.

The frequency deviation of the crystal oscillator is multiplied with the divider factor N of the Phase Locked Loop to the output of the power amplifier. In case of small frequency deviations (up to +/- 1000 ppm), the two desired load capacitances can be calculated with the formula below.

$$CL \pm = \frac{CL \mp C0 \frac{\Delta f}{N * f1} (1 + \frac{2(C0 + CL)}{C1})}{1 \pm \frac{\Delta f}{N * f1} (1 + \frac{2(C0 + CL)}{C1})}$$

C<sub>L</sub>: crystal load capacitance for nominal frequency

C<sub>0</sub>: shunt capacitance of the crystal

f: frequency

$\omega: \qquad \omega = 2\pi f: \mbox{ angular frequency} \\ N: \qquad \mbox{ division ratio of the PLL} \\ df: \qquad \mbox{ peak frequency deviation}$

Because of the inductive part of the TDA 5102, these values must be corrected by formula 1). The value of Cv± can be calculated.

If the FSK switch is closed, Cv- is equal to Cv1 (C6 in the application diagram). If the FSK switch is open, Cv2 (C7 in the application diagram) can be calculated.

$$Cv2 = C7 = \frac{Csw * Cv1 - (Cv+) * (Cv1 + Csw)}{(Cv+) - Cv1}$$

Csw: parallel capacitance of the FSK switch (3 pF)

Remark: These calculations are only approximations. The necessary values depend on the layout also and must be adapted for the specific application board.

#### 2. Design hints on the buffered clock output (CLKOUT)

The CLKOUT pin is an open collector output. An external pull up resistor (RL) should be connected between this pin and the positive supply voltage. The value of RL is depending on the clock frequency and the load capacitance CLD (PCB board plus input capacitance of the microcontroller). RL can be calculated to:

$$RL = \frac{1}{fCLKOUT *8*CLD}$$

| Table 4-2 |             |                      |     |  |

|-----------|-------------|----------------------|-----|--|

|           | OUT=<br>kHz | fCLKOUT=<br>3.57 MHz |     |  |

| CLD[pF]   | RL[kOhm]    | CLD[pF] RL[kOhm]     |     |  |

| 5         | 27          | 5                    | 6.8 |  |

| 10        | 12          | 10                   | 3.3 |  |

| 20        | 6.8         | 20                   | 1.8 |  |

Remark: To achieve a low current consumption and a low spurious radiation, the largest possible RL should be chosen.

| Cont  | ents of this Chapter                                |     |

|-------|-----------------------------------------------------|-----|

|       |                                                     |     |

| 5.1   | Absolute Maximum Ratings                            | 5-2 |

| 5.2   | Operating Range                                     | 5-2 |

| 5.3   | AC/DC Characteristics                               | 5-3 |

| 5.3.1 | AC/DC Characteristics at 3V, 25°C                   | 5-3 |

| 5.3.2 | AC/DC Characteristics at 2.1 V 4.0 V, -25°C +85°C 5 | 5-6 |

## 5.1 Absolute Maximum Ratings

The AC / DC characteristic limits are not guaranteed. The maximum ratings must not be exceeded under any circumstances, not even momentarily and individually, as permanent damage to the IC may result.

| Table 5-1                                   |                  |         |        |      |                |

|---------------------------------------------|------------------|---------|--------|------|----------------|

| Parameter                                   | Symbol           | Limit \ | /alues | Unit | Remarks        |

|                                             |                  | Min     | Max    |      |                |

| Junction Temperature                        | $T_J$            | -40     | 150    | °C   |                |

| Storage Temperature                         | T <sub>s</sub>   | -40     | 125    | °C   |                |

| Thermal Resistance                          | $R_{thJA}$       |         | 230    | K/W  |                |

| Supply voltage                              | V <sub>S</sub>   | -0.3    | 4.0    | V    |                |

| ESD integrity, all pins                     | V <sub>ESD</sub> | -1      | +1     | kV   | 100 pF, 1500 Ω |

| ESD integrity,<br>pins 11 and 14 not tested | V <sub>ESD</sub> | -2      | +2     | kV   | 100 pF, 1500 Ω |

Ambient Temperature under bias: T<sub>A</sub>=-25 to +85°C

### 5.2 Operating Range

Within the operational range the IC operates as described in the circuit description.

| Table 5-2           |                |              |     |      |                 |

|---------------------|----------------|--------------|-----|------|-----------------|

| Parameter           | Symbol         | Limit Values |     | Unit | Test Conditions |

|                     |                | Min          | Max |      |                 |

| Supply voltage      | V <sub>S</sub> | 2.1          | 4.0 | V    |                 |

| Ambient temperature | T <sub>A</sub> | -25          | 85  | °C   |                 |

## 5.3 AC/DC Characteristics

### 5.3.1 AC/DC Characteristics at 3V, 25°C

| Table 5-3 Supply Voltage V <sub>S</sub> = 3 V, Ambient temperature T <sub>amb</sub> = 25°C |                       |                      |             |                      |          |                                                                             |

|--------------------------------------------------------------------------------------------|-----------------------|----------------------|-------------|----------------------|----------|-----------------------------------------------------------------------------|

| Parameter                                                                                  | Symbol                | l                    | imit Values |                      | Unit     | Test Conditions                                                             |

|                                                                                            |                       | Min                  | Тур         | Max                  |          |                                                                             |

| Current consumption                                                                        |                       |                      |             |                      |          |                                                                             |

| Power down mode                                                                            | I <sub>S PDWN</sub>   |                      | 0.3         | 100                  | nA       | V (Pins 1, 6, and 7)<br>< 0.2 V                                             |

| PLL enable mode                                                                            | I <sub>S PLL_EN</sub> |                      | 3.3         | 4.2                  | mA       |                                                                             |

| Transmit mode                                                                              | I <sub>S TRANSM</sub> |                      | 7           | 9                    | mA       | Load tank see<br>Figure 4-1                                                 |

| Power Down Mode Control (F                                                                 | Pin 1)                |                      |             |                      |          |                                                                             |

| Power down mode                                                                            | V <sub>PDWN</sub>     | 0                    |             | 0.7                  | V        | V <sub>ASKDTA</sub> < 0.2 V<br>V <sub>FSKDTA</sub> < 0.2 V                  |

| PLL enable mode                                                                            | V <sub>PDWN</sub>     | 1.5                  |             | V <sub>S</sub>       | V        | V <sub>ASKDTA</sub> < 0.5 V                                                 |

| Transmit mode                                                                              | V <sub>PDWN</sub>     | 1.5                  |             | V <sub>S</sub>       | V        | V <sub>ASKDTA</sub> > 1.5 V                                                 |

| Input bias current PDWN                                                                    | I <sub>PDWN</sub>     |                      |             | 30                   | μΑ       | V <sub>PDWN</sub> = V <sub>S</sub>                                          |

| Low Power Detect Output (Pi                                                                | n 2)                  |                      |             |                      |          |                                                                             |

| Internal pull up current                                                                   | I <sub>LPD1</sub>     | 30                   |             |                      | μΑ       | V <sub>S</sub> = 2.3 V V <sub>S</sub>                                       |

| Input current low voltage                                                                  | I <sub>LPD2</sub>     | 1                    |             |                      | mA       | V <sub>S</sub> = 1.9 V 2.1 V                                                |

| Loop Filter (Pin 4)                                                                        |                       |                      |             |                      |          |                                                                             |

| VCO tuning voltage                                                                         | $V_{LF}$              | V <sub>S</sub> - 1.5 |             | V <sub>S</sub> - 0.7 | V        | $f_{VCO} = 915 \text{ MHz}$                                                 |

| Output frequency range<br>915 MHz-band                                                     | f <sub>OUT, 915</sub> | 902                  | 915         | 928                  | MHz      | V <sub>S</sub> -V <sub>LF</sub> =<br>0.54V1.76V<br>V <sub>FSEL</sub> = open |

| ASK Modulation Data Input (Pin 6)                                                          |                       |                      |             |                      |          |                                                                             |

| ASK Transmit disabled                                                                      | V <sub>ASKDTA</sub>   | 0                    |             | 0.5                  | V        |                                                                             |

|                                                                                            | V <sub>ASKDTA</sub>   | 1.5                  |             | V <sub>S</sub>       | V        |                                                                             |

| ASK Transmit enabled                                                                       | 710112171             |                      |             |                      |          |                                                                             |

| ASK Transmit enabled  Input bias current ASKDTA                                            | I <sub>ASKDTA</sub>   |                      |             | 30                   | μA       | $V_{ASKDTA} = V_{S}$                                                        |

|                                                                                            |                       | -20                  |             | 30                   | μA<br>μA | $V_{ASKDTA} = V_{S}$<br>$V_{ASKDTA} = 0 V$                                  |

| Parameter                                                             | Symbol Limit Values  |     |     |                |     | Test Conditions                      |

|-----------------------------------------------------------------------|----------------------|-----|-----|----------------|-----|--------------------------------------|

|                                                                       |                      | Min | Тур | Max            |     |                                      |

| FSK Modulation Data Input (I                                          | Pin 7)               |     |     |                |     |                                      |

| FSK Switch on                                                         | V <sub>FSKDTA</sub>  | 0   |     | 0.5            | V   |                                      |

| FSK Switch off                                                        | V <sub>FSKDTA</sub>  | 1.5 |     | V <sub>S</sub> | V   |                                      |

| Input bias current FSKDTA                                             | I <sub>FSKDTA</sub>  |     |     | 30             | μΑ  | V <sub>FSKDTA</sub> = V <sub>S</sub> |

| Input bias current FSKDTA                                             | I <sub>FSKDTA</sub>  | -20 |     |                | μΑ  | V <sub>FSKDTA</sub> = 0 V            |

| FSK data rate                                                         | f <sub>FSKDTA</sub>  |     |     | 20             | kHz |                                      |

| Clock Driver Output (Pin 8)                                           |                      |     |     |                |     |                                      |

| Output current (Low)                                                  | I <sub>CLKOUT</sub>  | 1   |     |                | mA  | V <sub>CLKOUT</sub> = V <sub>S</sub> |

| Output current (High)                                                 | I <sub>CLKOUT</sub>  |     |     | 5              | μΑ  | V <sub>CLKOUT</sub> = 0 V            |

| Saturation Voltage (Low)                                              | V <sub>SATL</sub>    |     |     | 0.56           | V   | I <sub>CLKOUT</sub> = 1 mA           |

| Clock Divider Control (Pin 9)                                         |                      |     |     |                |     |                                      |

| Setting Clock Driver output frequency f <sub>CLKOUT</sub> =3.57 MHz   | V <sub>CLKDIV</sub>  | 0   |     | 0.2            | V   |                                      |

| Setting Clock Driver output<br>frequency f <sub>CLKOUT</sub> =894 kHz | V <sub>CLKDIV</sub>  |     |     |                | V   | pin open                             |

| Input bias current CLKDIV                                             | I <sub>CLKDIV</sub>  |     |     | 30             | μΑ  | V <sub>CLKDIV</sub> = V <sub>S</sub> |

| Input bias current CLKDIV                                             | I <sub>CLKDIV</sub>  | -20 |     |                | μΑ  | V <sub>CLKDIV</sub> = 0 V            |

| Crystal Oscillator Input (Pin                                         | 10)                  |     |     |                |     |                                      |

| Load capacitance                                                      | C <sub>COSCmax</sub> |     |     | 5              | pF  |                                      |

| Serial Resistance of the crystal                                      |                      |     |     | 100            | Ω   | f = 7.15 MHz                         |

| Input inductance of the<br>COSC pin                                   |                      |     | 12  |                | μН  | f = 7.15 MHz                         |

| Serial Resistance of the crystal                                      |                      |     |     | 100            | Ω   | f = 14.3 MHz                         |

| Input inductance of the<br>COSC pin                                   |                      |     | 11  |                | μН  | f = 14.3 MHz                         |

| FSK Switch Output (Pin 11)                                            |                      |     |     |                |     | -                                    |

| On resistance                                                         | R <sub>FSKOUT</sub>  |     |     | 220            | Ω   | V <sub>FSKDTA</sub> = 0 V            |

| On capacitance                                                        | C <sub>FSKOUT</sub>  |     |     | 6              | pF  | V <sub>FSKDTA</sub> = 0 V            |

| Off resistance                                                        | R <sub>FSKOUT</sub>  | 10  |     |                | kΩ  | V <sub>FSKDTA</sub> = V <sub>S</sub> |

| Off capacitance                                                       | C <sub>FSKOUT</sub>  |     |     | 1.5            | pF  | V <sub>FSKDTA</sub> = V <sub>S</sub> |

| Table 5-3 Supply Voltage V <sub>S</sub>             | ; = 3 V, Ambi       | ent tempera | ture T <sub>amb</sub> = 2 | 5°C |      |                                                        |

|-----------------------------------------------------|---------------------|-------------|---------------------------|-----|------|--------------------------------------------------------|

| Parameter                                           | Symbol              | I           | Limit Values              |     | Unit | Test Conditions                                        |

|                                                     |                     | Min         | Тур                       | Max |      |                                                        |

| Power Amplifier Output (Pin                         | 14)                 |             |                           |     |      |                                                        |

| Output Power <sup>1)</sup><br>transformed to 50 Ohm | P <sub>OUT915</sub> | 0           | 2                         | 4   | dBm  | f <sub>OUT</sub> = 915 MHz<br>V <sub>FSEL</sub> = open |

| Frequency Range Selection (                         | Pin 15)             |             |                           |     |      |                                                        |

| Transmit frequency 915 MHz                          | V <sub>FSEL</sub>   |             |                           |     | V    | pin open                                               |

| Transmit frequency 457 MHz                          | V <sub>FSEL</sub>   | 0           |                           | 0.5 | V    |                                                        |

| Input bias current FSEL                             | I <sub>FSEL</sub>   |             |                           | 30  | μΑ   | $V_{FSEL} = V_{S}$                                     |

| Input bias current FSEL                             | I <sub>FSEL</sub>   | -20         |                           |     | μΑ   | V <sub>FSEL</sub> = 0 V                                |

| Crystal Frequency Selection                         | (Pin 16)            |             |                           |     |      |                                                        |

| Crystal frequency 7.15 MHz                          | V <sub>CSEL</sub>   | 0           |                           | 0.2 | V    |                                                        |

| Crystal frequency 14.3 MHz                          | V <sub>CSEL</sub>   |             |                           |     | V    | pin open                                               |

| Input bias current CSEL                             | I <sub>CSEL</sub>   |             |                           | 50  | μΑ   | V <sub>CSEL</sub> = V <sub>S</sub>                     |

| Input bias current CSEL                             | I <sub>CSEL</sub>   | -25         |                           |     | μΑ   | V <sub>CSEL</sub> = 0 V                                |

Power amplifier in overcritical C-operation.

Matching circuitry as used in the 50 Ohm-Output Testboard.

Tolerances of the passive elements not taken into account.

### 5.3.2 AC/DC Characteristics at 2.1 V ... 4.0 V, -25°C ... +85°C

| Parameter                              | s = 2.1 V 4.0 V, Ambient temperature T <sub>amb</sub> = -25<br>Symbol Limit Values |                       |     | Unit                  | Test Conditions |                                                            |

|----------------------------------------|------------------------------------------------------------------------------------|-----------------------|-----|-----------------------|-----------------|------------------------------------------------------------|

|                                        |                                                                                    | Min                   | Тур | Max                   |                 |                                                            |

| Current consumption                    |                                                                                    |                       |     |                       |                 |                                                            |

| Power down mode                        | I <sub>S PDWN</sub>                                                                |                       |     | 250                   | nA              | V (Pins 1, 6, and 7) < 0.2 V                               |

| PLL enable mode                        | I <sub>S PLL_EN</sub>                                                              |                       | 3.3 | 4.6                   | mA              |                                                            |

| Transmit mode                          | I <sub>S TRANSM</sub>                                                              |                       | 7   | 9.5                   | mA              | Load tank see<br>Figure 4-1 and 4-2                        |

| Power Down Mode Control (              | Pin 1)                                                                             |                       |     |                       |                 |                                                            |

| Power down mode                        | $V_{PDWN}$                                                                         | 0                     |     | 0.5                   | V               | V <sub>ASKDTA</sub> < 0.2 V<br>V <sub>FSKDTA</sub> < 0.2 V |

| PLL enable mode                        | V <sub>PDWN</sub>                                                                  | 1.5                   |     | V <sub>S</sub>        | V               | V <sub>ASKDTA</sub> < 0.5 V                                |

| Transmit mode                          | V <sub>PDWN</sub>                                                                  | 1.5                   |     | V <sub>S</sub>        | V               | V <sub>ASKDTA</sub> > 1.5 V                                |

| Input bias current PDWN                | I <sub>PDWN</sub>                                                                  |                       |     | 30                    | μA              | $V_{PDWN} = V_{S}$                                         |

| Low Power Detect Output (P             | in 2)                                                                              |                       |     |                       |                 |                                                            |

| Internal pull up current               | I <sub>LPD1</sub>                                                                  | 30                    |     |                       | μΑ              | V <sub>S</sub> = 2.3 V V <sub>S</sub>                      |

| Input current low voltage              | I <sub>LPD2</sub>                                                                  | 1                     |     |                       | mA              | V <sub>S</sub> = 1.9 V 2.1 V                               |

| Loop Filter (Pin 4)                    |                                                                                    |                       |     |                       |                 |                                                            |

| VCO tuning voltage                     | $V_{LF}$                                                                           | V <sub>S</sub> - 1.74 |     | V <sub>S</sub> - 0.52 | V               | f <sub>VCO</sub> = 915 MHz                                 |

| Output frequency range<br>915 MHz-band | f <sub>OUT, 915</sub>                                                              | 905                   | 915 | 925                   | MHz             | $V_S$ - $V_{LF}$ = 0.4 $V$ 1.95 $V$<br>$V_{FSEL}$ = open   |

| ASK Modulation Data Input (            | Pin 6)                                                                             |                       |     |                       |                 |                                                            |

| ASK Transmit disabled                  | V <sub>ASKDTA</sub>                                                                | 0                     |     | 0.5                   | V               |                                                            |

| ASK Transmit enabled                   | V <sub>ASKDTA</sub>                                                                | 1.5                   |     | V <sub>S</sub>        | V               |                                                            |

| Input bias current ASKDTA              | I <sub>ASKDTA</sub>                                                                |                       |     | 30                    | μΑ              | V <sub>ASKDTA</sub> = V <sub>S</sub>                       |

| Input bias current ASKDTA              | I <sub>ASKDTA</sub>                                                                | -20                   |     |                       | μA              | V <sub>ASKDTA</sub> = 0 V                                  |

| ASK data rate                          | f <sub>ASKDTA</sub>                                                                |                       |     | 20                    | kHz             |                                                            |

| Parameter                                                           | Symbol               |     | Limit Values |                | Unit | Test Conditions                      |

|---------------------------------------------------------------------|----------------------|-----|--------------|----------------|------|--------------------------------------|

|                                                                     |                      | Min | Тур          | Max            |      |                                      |

| FSK Modulation Data Input (F                                        | Pin 7)               |     |              |                |      |                                      |

| FSK Switch on                                                       | V <sub>FSKDTA</sub>  | 0   |              | 0.5            | V    |                                      |

| FSK Switch off                                                      | V <sub>FSKDTA</sub>  | 1.5 |              | ٧ <sub>s</sub> | V    |                                      |

| Input bias current FSKDTA                                           | I <sub>FSKDTA</sub>  |     |              | 30             | μΑ   | V <sub>FSKDTA</sub> = V <sub>S</sub> |

| Input bias current FSKDTA                                           | I <sub>FSKDTA</sub>  | -20 |              |                | μΑ   | V <sub>FSKDTA</sub> = 0 V            |

| FSK data rate                                                       | f <sub>FSKDTA</sub>  |     |              | 20             | kHz  |                                      |

| Clock Driver Output (Pin 8)                                         |                      |     |              |                |      |                                      |

| Output current (Low)                                                | I <sub>CLKOUT</sub>  | 1   |              |                | mA   | V <sub>CLKOUT</sub> = V <sub>S</sub> |

| Output current (High)                                               | I <sub>CLKOUT</sub>  |     |              | 5              | μΑ   | V <sub>CLKOUT</sub> = 0 V            |

| Saturation Voltage (Low) <sup>1)</sup>                              | V <sub>SATL</sub>    |     |              | 0.5            | V    | I <sub>CLKOUT</sub> = 0.8 mA         |

| Clock Divider Control (Pin 9)                                       |                      |     |              |                |      |                                      |

| Setting Clock Driver output frequency f <sub>CLKOUT</sub> =3.57 MHz | V <sub>CLKDIV</sub>  | 0   |              | 0.2            | V    |                                      |

| Setting Clock Driver output frequency f <sub>CLKOUT</sub> =894 kHz  | V <sub>CLKDIV</sub>  |     |              |                | V    | pin open                             |

| Input bias current CLKDIV                                           | I <sub>CLKDIV</sub>  |     |              | 30             | μΑ   | V <sub>CLKDIV</sub> = V <sub>S</sub> |

| Input bias current CLKDIV                                           | I <sub>CLKDIV</sub>  | -20 |              |                | μΑ   | V <sub>CLKDIV</sub> = 0 V            |

| Crystal Oscillator Input (Pin 1                                     | 10)                  |     |              |                |      |                                      |

| Load capacitance                                                    | C <sub>COSCmax</sub> |     |              | 5              | pF   |                                      |

| Serial Resistance of the crystal                                    |                      |     |              | 100            | Ω    | f = 7.15 MHz                         |

| Input inductance of the COSC pin                                    |                      |     | 12           |                | μH   | f = 7.15 MHz                         |

| Serial Resistance of the crystal                                    |                      |     |              | 100            | Ω    | f = 14.3 MHz                         |

| Input inductance of the COSC pin                                    |                      |     | 11           |                | μH   | f = 14.3 MHz                         |

| FSK Switch Output (Pin 11)                                          |                      |     |              |                |      |                                      |

| On resistance                                                       | R <sub>FSKOUT</sub>  |     |              | 220            | Ω    | V <sub>FSKDTA</sub> = 0 V            |

| On capacitance                                                      | C <sub>FSKOUT</sub>  |     |              | 6              | pF   | V <sub>FSKDTA</sub> = 0 V            |

| Off resistance                                                      | R <sub>FSKOUT</sub>  | 10  |              |                | kΩ   | V <sub>FSKDTA</sub> = V <sub>S</sub> |

| Off capacitance                                                     | C <sub>FSKOUT</sub>  |     |              | 1.5            | pF   | V <sub>FSKDTA</sub> = V <sub>S</sub> |

| Table 5-4 Supply Voltage V <sub>S</sub> = 2.1 V 4.0 V, Ambient temperature T <sub>amb</sub> = -25°C +85°C |                       |              |     |     |      |                                    |

|-----------------------------------------------------------------------------------------------------------|-----------------------|--------------|-----|-----|------|------------------------------------|

| Parameter                                                                                                 | Symbol                | Limit Values |     |     | Unit | Test Conditions                    |

|                                                                                                           |                       | Min          | Тур | Max |      |                                    |

| Power Amplifier Output (Pin                                                                               | 14)                   |              |     |     |      |                                    |

| Output Power <sup>2)</sup> at 915 MHz                                                                     | P <sub>OUT, 915</sub> | -2.3         | 0.2 | 1.8 | dBm  | $V_{S} = 2.1 \text{ V}$            |

| transformed to 50 Ohm.                                                                                    | P <sub>OUT, 915</sub> | -2.0         | 2   | 4.9 | dBm  | V <sub>S</sub> = 3.0 V             |

| V <sub>FSEL</sub> = open                                                                                  | P <sub>OUT, 915</sub> | -1.7         | 3.2 | 7.2 | dBm  | V <sub>S</sub> = 4.0 V             |

| Frequency Range Selection                                                                                 | (Pin 15)              |              |     |     |      |                                    |

| Transmit frequency 915 MHz                                                                                | V <sub>FSEL</sub>     |              |     |     | V    | pin open                           |

| Transmit frequency 457 MHz                                                                                | V <sub>FSEL</sub>     | 0            |     | 0.5 | V    |                                    |

| Input bias current FSEL                                                                                   | I <sub>FSEL</sub>     |              |     | 30  | μΑ   | V <sub>FSEL</sub> = V <sub>S</sub> |

| Input bias current FSEL                                                                                   | I <sub>FSEL</sub>     | -20          |     |     | μΑ   | V <sub>FSEL</sub> = 0 V            |

| <b>Crystal Frequency Selection</b>                                                                        | (Pin 16)              |              |     |     |      |                                    |

| Crystal frequency 7.15 MHz                                                                                | V <sub>CSEL</sub>     | 0            |     | 0.2 | V    |                                    |

| Crystal frequency 14.3 MHz                                                                                | V <sub>CSEL</sub>     |              |     |     | V    | pin open                           |

| Input bias current CSEL                                                                                   | I <sub>CSEL</sub>     |              |     | 50  | μΑ   | V <sub>CSEL</sub> = V <sub>S</sub> |

| Input bias current CSEL                                                                                   | I <sub>CSEL</sub>     | -25          |     |     | μΑ   | V <sub>CSEL</sub> = 0 V            |

- 1) Derating linearly to a saturation voltage of max. 140 mV at  $I_{CLKOUT} = 0$  mA

- 2) Matching circuitry as used in the 50 Ohm-Output Testboard for 915 MHz operation.

Range @ 2.1 V, +25°C: 0.2 dBm +/- 1.0 dBm Temperature dependency at 2.1 V: +0.6 dBm@-25°C and -1.5 dBm@+85°C, reference +25°C.

Range @ 3.0 V, +25°C: 2.0 dBm +/- 2.0 dBm

Temperature dependency at 3.0 V: +0.9 dBm@-25°c and -2.0 dBm@+85°C, reference +25°C.

Range @ 4.0 V, +25°C: 3.2 dBm +/- 2.7 dBm

Temperature dependency at 4.0 V: +1.3 dBm@-25°c and -2.2 dBm@+85°C, reference +25°C. Tolerances of the passive elements not taken into account.

A smaller load impedance reduces the supply-voltage dependency.

A higher load impedance reduces the temperature dependency.